(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6266872号

(P6266872)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G02F 1/1368 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 525

GO2F 1/133 550

GO2F 1/1368

GO9G 3/20 621A

請求項の数 3 (全 45 頁) 最終頁に続く

(21) 出願番号

特願2012-238776 (P2012-238776)

(22) 出願日

平成24年10月30日 (2012.10.30)

(65) 公開番号

特開2013-122581 (P2013-122581A)

(43) 公開日

平成25年6月20日 (2013.6.20)

審査請求日

平成27年9月28日 (2015.9.28)

審判番号

不服2016-17782 (P2016-17782/J1)

審判請求日

平成28年11月29日 (2016.11.29)

(31) 優先権主張番号

特願2011-247262 (P2011-247262)

(32) 優先日

平成23年11月11日 (2011.11.11)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 井上 聖子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

合議体

審判長 中塚 直樹

審判官 関根 洋之

審判官 須原 宏光

最終頁に続く

(54) 【発明の名称】信号線駆動回路及び液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

シフトレジスタと、

第1のクロック信号及び第2のクロック信号に従い、前記シフトレジスタから入力されるパルス信号を、第1のパルス信号とみなして出力するか第2のパルス信号とみなして出力するかを選択する機能を有する選択回路と、

前記選択回路から入力される前記第1のパルス信号及び前記第2のパルス信号、並びに第1の制御信号乃至第5の制御信号に従い、信号線の電位を制御するための駆動信号を生成して出力する機能を有する駆動信号出力回路と、を備え、

前記駆動信号出力回路は、

前記第1のパルス信号及び前記第2のパルス信号に従い、第1のデータ及び第2のデータを書き換え、記憶する第1のラッチ部と、

前記第1のパルス信号及び前記第2のパルス信号に従い、第3のデータ及び第4のデータを書き換え、記憶する第2のラッチ部と、

前記第1のデータ及び前記第2のデータに従い第1の信号の電位を設定し、該第1の信号を出力する機能を有する第1のバッファ部と、

前記第3のデータ及び前記第4のデータに従い第2の信号の電位を設定し、該第2の信号を出力する機能を有する第2のバッファ部と、

前記第1の制御信号及び前記第2の制御信号に従ってオン状態又はオフ状態になることにより、前記第1のデータの再書き込みを制御する第1のスイッチ部と、

10

20

前記第1の制御信号及び前記第3の制御信号に従ってオン状態又はオフ状態になることにより、前記第3のデータの再書き込みを制御する第2のスイッチ部と、

第4の制御信号として前記第2の信号が入力され、前記第4の制御信号に従ってオン状態又はオフ状態になることにより、前記第1のラッチ部に記憶された前記第2のデータの再書き込みを制御する第3のスイッチ部と、

第5の制御信号として前記第1の信号が入力され、前記第5の制御信号に従ってオン状態又はオフ状態になることにより、前記第2のラッチ部に記憶された前記第4のデータの再書き込みを制御する第4のスイッチ部と、

前記第1の信号及び前記第2の信号に従い、前記駆動信号の電位を設定し、該駆動信号を出力する第3のバッファ部と、を含む信号線駆動回路。

10

#### 【請求項2】

請求項1に記載の信号線駆動回路と、

データ信号線と、

ゲート信号線と、

前記信号線駆動回路から出力される前記駆動信号により電位が制御される共通信号線と

、

画素回路と、を備え、

前記画素回路は、

ソース及びドレインの一方が前記データ信号線に電気的に接続され、ゲートが前記ゲート信号線に電気的に接続される電界効果トランジスタと、

20

一対の電極の一方が前記電界効果トランジスタが有するソース及びドレインの他方に電気的に接続され、前記一対の電極の他方が前記共通信号線に電気的に接続される液晶素子と、を備える液晶表示装置。

#### 【請求項3】

前記電界効果トランジスタは、チャネル形成領域を酸化物半導体層に有する請求項2に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の一態様は、信号線駆動回路に関する。また、本発明の一態様は、液晶表示装置に関する。

30

##### 【背景技術】

##### 【0002】

近年、液晶表示装置などの半導体装置の開発が進められている。

##### 【0003】

上記液晶表示装置の一つとして、行列方向に配列された複数の画素回路において、各行の画素回路毎に、液晶素子が有する一対の電極の一方の電位と、他方の電位の極性をフレーム期間毎に反転させる駆動方法を用いた液晶表示装置が知られている（例えば特許文献1）。

40

##### 【0004】

上記駆動方法を用いることにより、液晶素子による表示画像の焼き付きを抑制しつつ、液晶表示装置が備える信号線駆動回路の駆動電圧を低減できる。

##### 【0005】

例えば、特許文献1では、共通信号線駆動回路などの信号線駆動回路を用いて複数の共通信号線の電位を制御することにより、液晶素子が有する上記一対の電極の他方の電位をフレーム期間毎に反転する技術が開示されている。

##### 【0006】

特許文献1に示す信号線駆動回路は、シフトレジスタと、ラッチ部及びバッファ部を含む複数の回路と、を備える。特許文献1に示す信号線駆動回路は、バッファ部において、ラッチ部に記憶されたデータに従って電位が制御された信号を共通信号として出力する。

50

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006-276541号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来の信号線駆動回路では、動作不良が起こりやすいといった問題があった。

【0009】

例えば、特許文献1に示す信号線駆動回路では、信号線駆動回路を構成する電界効果トランジスタのリーク電流などによりラッチ部に記憶されたデータである電位が変動してしまい、出力される信号の電位が所望の値にならず、所望の動作が行えなくなるといった問題があった。

【0010】

以上を鑑みて、本発明の一態様では、動作不良の発生を抑制することを課題の一つとする。

【課題を解決するための手段】

【0011】

本発明の一態様では、ラッチ部と、バッファ部と、該ラッチ部に記憶されるデータの再書き込みを制御するためのスイッチ部と、を含む回路により、駆動信号としての機能を有する信号を生成することにより、ラッチ部に記憶されたデータの変動の抑制を図る。

【0012】

上記スイッチ部は、第1の制御信号及び第2の制御信号に従ってラッチ部に記憶されたデータの再書き込みを制御する機能を有する。これにより、セット信号及びリセット信号のパルスが入力されない期間にデータの再書き込みを行い、ラッチ部に記憶されたデータとなる電位の変動の抑制を図る。

【0013】

本発明の一態様は、シフトレジスタと、第1のクロック信号及び第2のクロック信号に従い、シフトレジスタから入力されるパルス信号を、第1のパルス信号とみなして出力するか第2のパルス信号とみなして出力するかを選択する機能を有する選択回路と、選択回路から入力される第1のパルス信号及び第2のパルス信号、並びに第1の制御信号及び第2の制御信号に従い、信号線の電位を制御するための駆動信号を生成して出力する機能を有する駆動信号出力回路と、を備え、駆動信号出力回路は、第1のパルス信号及び第2のパルス信号に従い、第1のデータ及び第2のデータを書き換え、記憶するラッチ部と、第1のデータ及び第2のデータに従い駆動信号の電位を設定し、該駆動信号を出力するバッファ部と、第1の制御信号及び第2の制御信号に従ってオン状態又はオフ状態になることにより、第1のデータの再書き込みを制御するスイッチ部と、を含む信号線駆動回路である。

【0014】

また、本発明の一態様は、シフトレジスタと、第1のクロック信号及び第2のクロック信号に従い、シフトレジスタから入力されるパルス信号を、第1のパルス信号とみなして出力するか第2のパルス信号とみなして出力するかを選択する機能を有する選択回路と、選択回路から入力される第1のパルス信号及び第2のパルス信号、並びに第1の制御信号乃至第5の制御信号に従い、信号線の電位を制御するための駆動信号を生成して出力する機能を有する駆動信号出力回路と、を備え、駆動信号出力回路は、第1のパルス信号及び第2のパルス信号に従い、第1のデータ及び第2のデータを書き換え、記憶する第1のラッチ部と、第1のパルス信号及び第2のパルス信号に従い、第3のデータ及び第4のデータを書き換え、記憶する第2のラッチ部と、第1のデータ及び第2のデータに従い第1の信号の電位を設定し、該第1の信号を出力する機能を有する第1のバッファ部と、第3のデ

10

20

30

40

50

ータ及び第4のデータに従い第2の信号の電位を設定し、該第2の信号を出力する機能を有する第2のバッファ部と、第1の制御信号及び第2の制御信号に従ってオン状態又はオフ状態になることにより、第1のデータの再書き込みを制御する第1のスイッチ部と、第1の制御信号及び第3の制御信号に従ってオン状態又はオフ状態になることにより、第3のデータの再書き込みを制御する第2のスイッチ部と、第4の制御信号として第2の信号が入力され、第4の制御信号に従ってオン状態又はオフ状態になることにより、第1のラッチ部に記憶された第2のデータの再書き込みを制御する第3のスイッチ部と、第5の制御信号として第1の信号が入力され、第5の制御信号に従ってオン状態又はオフ状態になることにより、第2のラッチ部に記憶された第4のデータの再書き込みを制御する第4のスイッチ部と、第1の信号及び第2の信号に従い、駆動信号の電位を設定し、該駆動信号を出力する第3のバッファ部と、を含む信号線駆動回路である。

#### 【0015】

さらに、本発明の一態様では、上記信号線駆動回路を用いて、画素回路の液晶素子が有する一対の電極の他方の電位を制御する。これにより、行列方向に配列された複数の画素回路において、各行の画素回路毎に液晶素子が有する一対の電極の一方の電位と、他方の電位の極性をフレーム期間毎に反転させる駆動方法を行い、ゲート信号の電圧の低下を図る。

#### 【0016】

さらに、本発明の一態様では、上記液晶素子をブルー相を示す液晶を用いて構成する。これにより、液晶表示装置の動作を速くさせる。

#### 【発明の効果】

#### 【0017】

本発明の一態様により、ラッチ部に記憶されたデータとなる電位の変動を抑制でき、信号線駆動回路から出力される信号の電位の変動を抑制できるため、動作不良の発生を抑制できる。

#### 【図面の簡単な説明】

#### 【0018】

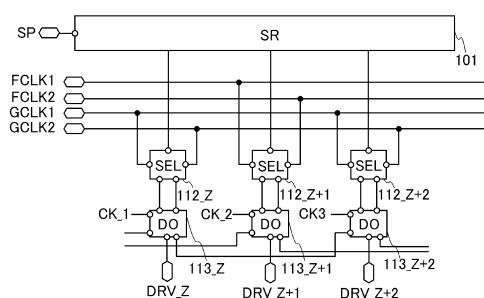

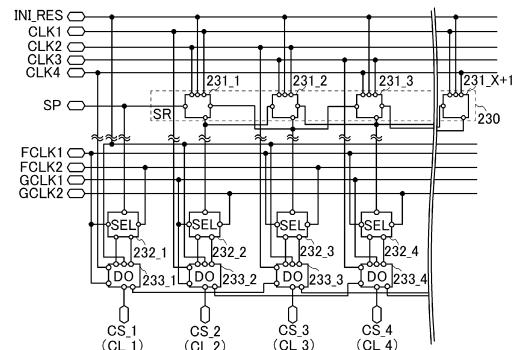

【図1】信号線駆動回路の例を説明するための図。

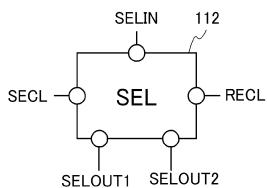

【図2】選択回路の例を説明するための図。

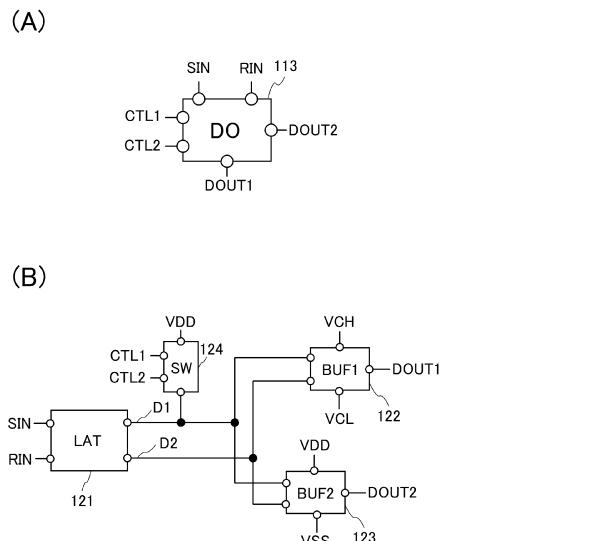

【図3】駆動信号出力回路の例を説明するための図。

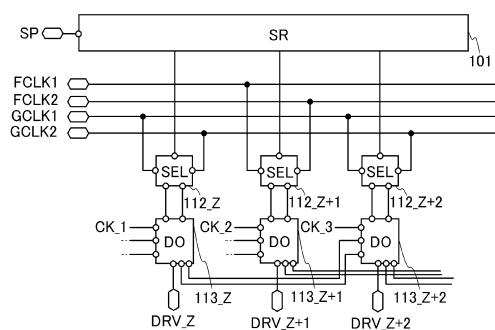

【図4】信号線駆動回路の例を説明するための図。

【図5】駆動信号出力回路の例を説明するための図。

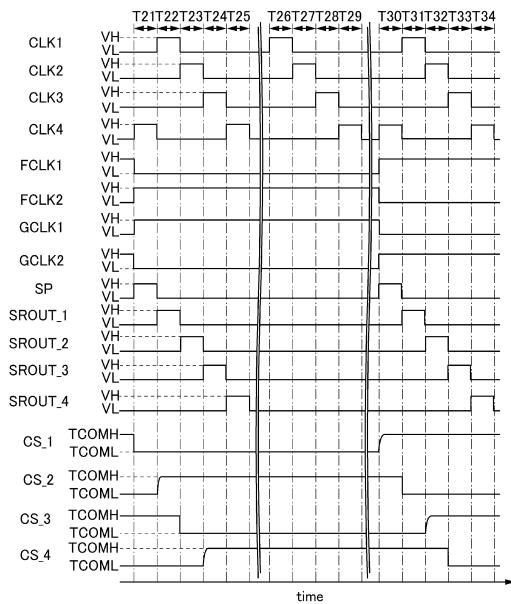

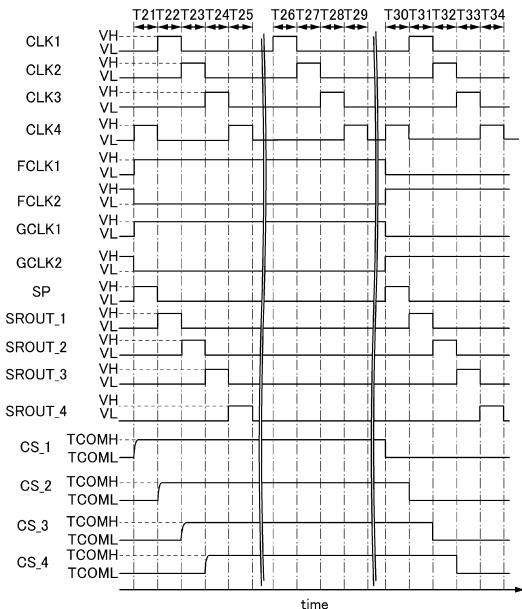

【図6】信号線駆動回路の駆動方法例を説明するためのタイミングチャート。

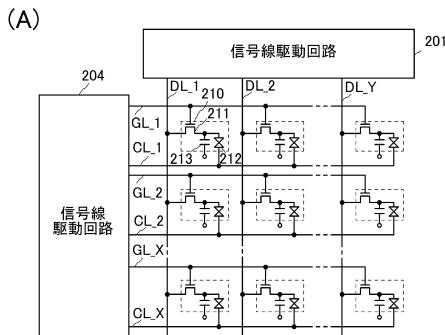

【図7】液晶表示装置の例を説明するための図。

【図8】パルス出力回路の例を説明するための図。

【図9】選択回路の例を説明するための図。

【図10】駆動信号出力回路の例を説明するための図。

【図11】液晶表示装置の例を説明するための図。

【図12】液晶表示装置の例を説明するための図。

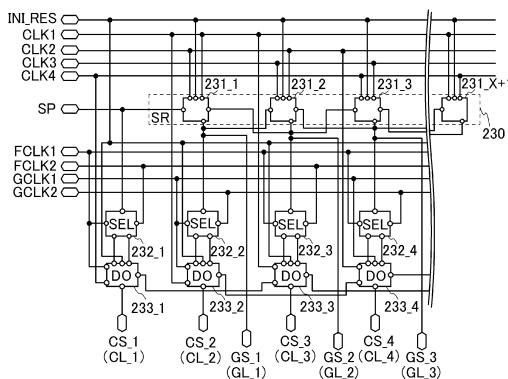

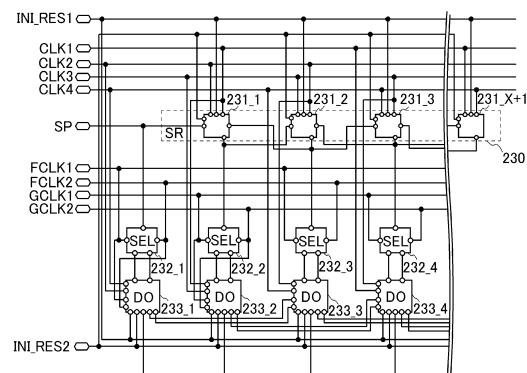

【図13】信号線駆動回路の例を説明するための図。

【図14】パルス出力回路の例を説明するための図。

【図15】駆動信号出力回路の例を説明するための図。

【図16】信号線駆動回路の駆動方法例を説明するためのタイミングチャート。

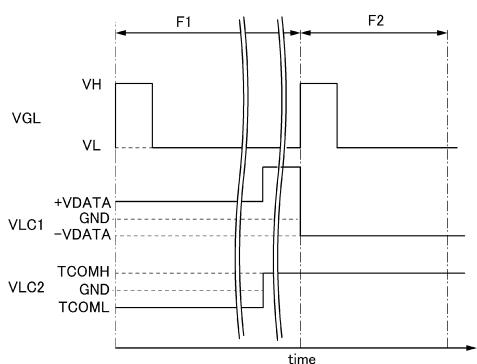

【図17】信号線駆動回路の駆動方法例を説明するためのタイミングチャート。

【図18】画素回路の動作例を説明するためのタイミングチャート。

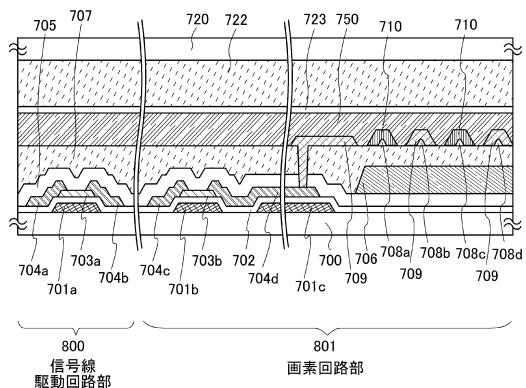

【図19】液晶表示装置の構造例を説明するための断面模式図。

【図20】電子機器の例を説明するための図。

#### 【発明を実施するための形態】

#### 【0019】

本発明の実施形態の例について説明する。なお、本発明の趣旨及び範囲から逸脱すること

10

20

30

40

50

なく実施形態の内容を変更することは、当業者であれば容易である。よって、例えば本発明は、下記実施形態の記載内容に限定されない。

**【 0 0 2 0 】**

なお、各実施形態の内容を互いに適宜組み合わせることができる。また、各実施形態の内容を互いに適宜置き換えることができる。

**【 0 0 2 1 】**

また、第1、第2などの序数は、構成要素の混同を避けるために付しており、各構成要素の数は、序数の数に限定されない。

**【 0 0 2 2 】**

(実施形態1)

10

本実施形態では、複数の駆動信号を出力する機能を有する信号線駆動回路の例について、図1乃至図6を用いて説明する。

**【 0 0 2 3 】**

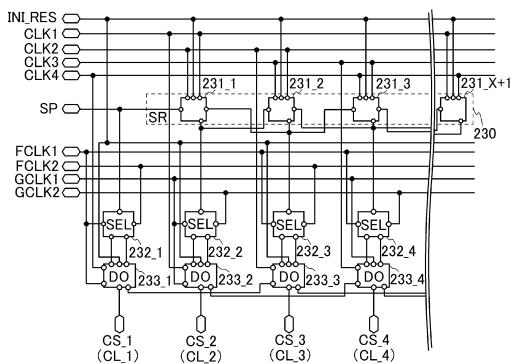

本実施形態の信号線駆動回路は、図1に示すように、シフトレジスタ(SRともいう)101と、複数の選択回路(SELともいう)112(図1では選択回路112\_Z(Zは自然数)、選択回路112\_Z+1、及び選択回路112\_Z+2)と、複数の駆動信号出力回路(DOともいう)113(図1では駆動信号出力回路113\_Z、駆動信号出力回路113\_Z+1、及び駆動信号出力回路113\_Z+2)と、を備える。選択回路112及び駆動信号出力回路113は、例えば信号線毎に設けられる。駆動信号出力回路113により生成されたパルス信号は、対応する信号線を介して出力される。

20

**【 0 0 2 4 】**

シフトレジスタ101には、スタートパルス信号SPが入力される。

**【 0 0 2 5 】**

シフトレジスタ101は、スタートパルス信号SPに従って電位が制御された複数のパルス信号(SROUTともいう)を出力する機能を有する。

**【 0 0 2 6 】**

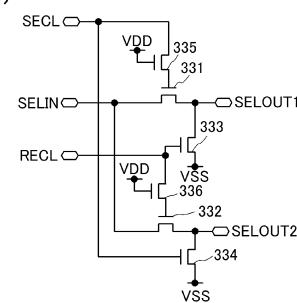

選択回路112には、図2に示すように、パルス信号SELINとしてシフトレジスタ101からパルス信号が入力され、且つクロック信号SECL及びクロック信号RECLが入力される。複数の選択回路112のそれぞれには、例えば互いに異なるパルス信号が入力される。また、選択回路112は、図2に示すように、パルス信号SELOUT1及びパルス信号SELOUT2を出力する。

30

**【 0 0 2 7 】**

選択回路112は、パルス信号SELIN、クロック信号SECL、及びクロック信号RECLに従って、パルス信号SELINを、パルス信号SELOUT1とみなして出力するかパルス信号SELOUT2とみなして出力するかを選択する機能を有する。

**【 0 0 2 8 】**

選択回路112は、例えば複数の電界効果トランジスタを用いて構成される。このとき、複数の電界効果トランジスタのオン状態及びオフ状態を切り換えることにより、パルス信号SELINを、パルス信号SELOUT1とみなして出力するかパルス信号SELOUT2とみなして出力するか、切り換えることができる。

40

**【 0 0 2 9 】**

さらに、図1に示す選択回路112\_Z及び選択回路112\_Z+2において、クロック信号SECLとしてクロック信号GCLK1が入力され、クロック信号RECLとしてクロック信号GCLK2が入力される。また、選択回路112\_Z+1において、クロック信号SECLとしてクロック信号FCLK1が入力され、クロック信号RECLとしてクロック信号FCLK2が入力される。

**【 0 0 3 0 】**

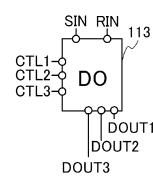

駆動信号出力回路113には、図3(A)に示すように、セット信号SIN、リセット信号RIN、制御信号CTL1、及び制御信号CTL2が入力される。また、駆動信号出力回路113は、図3(A)に示すように、信号DOUT1及び信号DOUT2を出力する

50

。信号 DOUT1 は駆動信号となる。駆動信号出力回路 113 は、セット信号 SIN、リセット信号 RIN、制御信号 CTL1、及び制御信号 CTL2 に従い、駆動信号を生成して出力する機能を有する。このとき、駆動信号は、例えば信号線の電位を制御するための配線に出力される。

**【0031】**

駆動信号出力回路 113 は、例えば複数の電界効果トランジスタを用いて構成される。

**【0032】**

さらに、駆動信号出力回路 113 は、図 3 (B) に示すように、ラッチ部 (LATともいう) 121 と、第 1 のバッファ部 (BUF1ともいう) 122 と、第 2 のバッファ部 (BUF2ともいう) 123 と、スイッチ部 (SWともいう) 124 と、を含む。

10

**【0033】**

ラッチ部 121 には、セット信号 SIN 及びリセット信号 RIN が入力される。

**【0034】**

ラッチ部 121 は、セット信号 SIN 及びリセット信号 RIN に従ってデータ D1 及びデータ D2 を書き換え、記憶する機能を有する。

**【0035】**

第 1 のバッファ部 122 は、ラッチ部 121 に記憶されたデータ D1 及びデータ D2 に従い信号 DOUT1 の電位を設定し、信号 DOUT1 を出力する機能を有する。信号 DOUT1 は、電位 VCH から電位 VLC (電位 VCH よりも低い値の電位) までの間で電位が变化する信号である。

20

**【0036】**

第 2 のバッファ部 123 は、ラッチ部 121 に記憶されたデータ D1 及びデータ D2 に従い信号 DOUT2 の電位を設定し、信号 DOUT2 を出力する機能を有する。信号 DOUT2 は、電位 VDD から電位 VSS までの間で電位が変化する信号である。電位 VDD は、電位 VSS よりも高い電位であり、ハイレベルの信号の電位 (電位 VH ともいう) となる。また、電位 VSS は、接地電位以下の電位であり、ローレベルの信号の電位 (電位 VL ともいう) となる。

**【0037】**

スイッチ部 124 には、制御信号 CTL1 及び制御信号 CTL2 が入力される。

**【0038】**

スイッチ部 124 は、制御信号 CTL1 及び制御信号 CTL2 に従ってオン状態又はオフ状態になることにより、ラッチ部 121 に記憶されたデータ D1 の再書き込みを制御する機能を有する。

30

**【0039】**

なお、制御信号 CTL1 としては、例えばスタートパルス信号よりも、連続する複数のパルスの間隔が短い期間を有する信号を用いることができる。

**【0040】**

また、駆動信号出力回路 113 には、セット信号 SIN として選択回路 112 からパルス信号 SELOUT1 が入力され、リセット信号 RIN として選択回路 112 からパルス信号 SELOUT2 が入力される。このとき、ラッチ部 121 は、パルス信号 SELOUT1 及びパルス信号 SELOUT2 に従い、データ D1 及びデータ D2 を書き換え、記憶する機能を有する。

40

**【0041】**

また、図 1 に示す駆動信号出力回路 113\_Z の制御信号 CTL1 として、クロック信号 CK\_1 が入力される。また、駆動信号出力回路 113\_Z+1 の制御信号 CTL1 として、クロック信号 CK\_2 が入力される。また、駆動信号出力回路 113\_Z+2 の制御信号 CTL1 として、クロック信号 CK\_3 が入力される。

**【0042】**

また、図 1 に示す駆動信号出力回路 113\_Z の信号 DOUT1 が駆動信号 DRV\_Z となる。また、駆動信号出力回路 113\_Z+1 の信号 DOUT1 が駆動信号 DRV\_Z+1 となる。

50

1となる。また、駆動信号出力回路 113\_Z + 2 の信号 DOUT 1 が駆動信号DRV\_Z + 2 となる。

**【0043】**

また、図1に示す駆動信号出力回路 113\_Z + 2 の制御信号 CTL2 として、駆動信号出力回路 113\_Z の信号 DOUT 2 が入力される。これにより、クロック信号 GCLK1 を入力する場合と比較してデータ D1 の再書き込みが可能な期間を長くできるため、信号線駆動回路の動作不良をより抑制できる。

**【0044】**

なお、図1に示す信号線駆動回路が備える複数の駆動信号出力回路 113 の接続関係を、図4に示すようにしてもよい。

10

**【0045】**

また、図4に示す構成において、駆動信号出力回路 113 には、図5(A)に示すように、セット信号 SIN、リセット信号 RIN、制御信号 CTL1、制御信号 CTL2、及び制御信号 CTL3 が入力される。また、駆動信号出力回路 113 は、図5(A)に示すように、信号 DOUT 1、信号 DOUT 2、及び信号 DOUT 3 を出力する。駆動信号出力回路 113 は、セット信号 SIN、リセット信号 RIN、制御信号 CTL1 乃至制御信号 CTL5 に従い、駆動信号を生成して出力する機能を有する。

**【0046】**

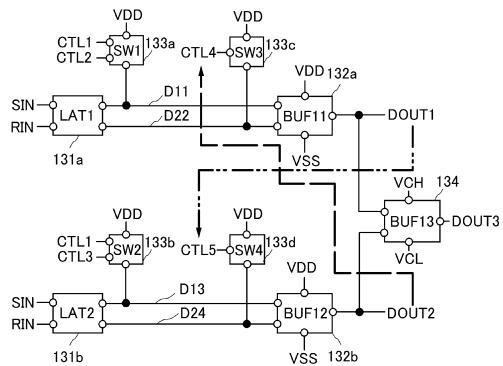

さらに、駆動信号出力回路 113 は、図5(B)に示すように、第1のラッチ部(LAT1ともいう)131aと、第2のラッチ部(LAT2ともいう)131bと、第1のバッファ部(BUF11ともいう)132aと、第2のバッファ部(BUF12ともいう)132bと、第1のスイッチ部(SW1ともいう)133aと、第2のスイッチ部(SW2ともいう)133bと、第3のスイッチ部(SW3ともいう)133cと、第4のスイッチ部(SW4ともいう)133dと、第3のバッファ部(BUF13ともいう)134と、を含む。

20

**【0047】**

第1のラッチ部 131a には、セット信号 SIN 及びリセット信号 RIN が入力される。

**【0048】**

第1のラッチ部 131a は、セット信号 SIN 及びリセット信号 RIN に従ってデータ D11 及びデータ D22 を書き換え、記憶する機能を有する。

30

**【0049】**

第2のラッチ部 131b には、セット信号 SIN 及びリセット信号 RIN が入力される。

**【0050】**

第2のラッチ部 131b は、セット信号 SIN 及びリセット信号 RIN に従ってデータ D13 及びデータ D24 を書き換え、記憶する機能を有する。

**【0051】**

第1のバッファ部 132a は、第1のラッチ部 131a に記憶されたデータ D11 及びデータ D22 に従って信号 DOUT 1 の電位を設定し、信号 DOUT 1 を出力する機能を有する。信号 DOUT 1 は、電位 VDD(VH) から電位 VSS(VL) までの間で変化する信号である。

40

**【0052】**

第2のバッファ部 132b は、第2のラッチ部 131b に記憶されたデータ D13 及びデータ D24 に従って信号 DOUT 2 の電位を設定し、信号 DOUT 2 を出力する機能を有する。信号 DOUT 2 は、電位 VDD(VH) から電位 VSS(VL) までの間で変化する信号である。

**【0053】**

第1のスイッチ部 133a には、制御信号 CTL1 及び制御信号 CTL2 が入力される。第1のスイッチ部 133a は、制御信号 CTL1 及び制御信号 CTL2 に従ってオン状態又はオフ状態になることにより、第1のラッチ部 131a に記憶されたデータ D11 の再書き込みを制御する機能を有する。

50

**【 0 0 5 4 】**

第2のスイッチ部133bには、制御信号CTL1及び制御信号CTL3が入力される。第2のスイッチ部133bは、制御信号CTL1及び制御信号CTL3に従ってオン状態又はオフ状態になることにより、第2のラッチ部131bに記憶されたデータD13の再書き込みを制御する機能を有する。

**【 0 0 5 5 】**

第3のスイッチ部133cには、制御信号CTL4として信号DOU T2が入力される。第3のスイッチ部133cは、制御信号CTL4に従ってオン状態又はオフ状態になることにより、第1のラッチ部131aに記憶されたデータD22の再書き込みを制御する機能を有する。

10

**【 0 0 5 6 】**

第4のスイッチ部133dには、制御信号CTL5として信号DOU T1が入力される。第4のスイッチ部133dは、制御信号CTL5に従ってオン状態又はオフ状態になることにより、第2のラッチ部131bに記憶されたデータD24の再書き込みを制御する機能を有する。

**【 0 0 5 7 】**

第3のスイッチ部133cの制御信号CTL4として信号DOU T2を入力し、第4のスイッチ部133dの制御信号CTL5として信号DOU T1を入力することにより、第1のラッチ部のデータD22となる電位及び第2のラッチ部のデータD24となる電位として電位VDD又は電位VSSを与え続けることができるため、第1のラッチ部のデータD22となる電位及び第2のラッチ部のデータD24となる電位を保持できる。

20

**【 0 0 5 8 】**

第3のバッファ部134は、信号DOU T1及び信号DOU T2に従って信号DOU T3の電位を設定し、信号DOU T3を出力する機能を有する。信号DOU T3は、電位が電位VCHから電位VCLまでの間で変化する駆動信号である。

**【 0 0 5 9 】**

また、図4に示す複数の駆動信号出力回路113のそれぞれには、セット信号SINとして複数の選択回路112のパルス信号SEL OUT1のうちの一つが入力され、リセット信号RINとして複数の選択回路112のパルス信号SEL OUT2のうちの一つが入力される。例えば、駆動信号出力回路113\_Z+1には、セット信号SINとして選択回路112\_Z+1のパルス信号SEL OUT1が入力され、リセット信号RINとして選択回路112\_Z+1のパルス信号SEL OUT2が入力される。

30

**【 0 0 6 0 】**

また、図4に示す駆動信号出力回路113\_Zの制御信号CTL1として、クロック信号CK\_1が入力される。また、駆動信号出力回路113\_Z+1の制御信号CTL1として、クロック信号CK\_2が入力される。また、駆動信号出力回路113\_Z+2の制御信号CTL1として、クロック信号CK\_3が入力される。

**【 0 0 6 1 】**

また、図4に示す駆動信号出力回路113\_Z+2の制御信号CTL2として、駆動信号出力回路113\_Zの信号DOU T1が入力される。また、駆動信号出力回路113\_Z+2の制御信号CTL3として、駆動信号出力回路113\_Zの信号DOU T2が入力される。これにより、駆動信号出力回路113\_Z+2の制御信号CTL2としてクロック信号GCLK1を入力し、駆動信号出力回路113\_Z+2の制御信号CTL3としてクロック信号GCLK2を入力する場合と比較して、図5(B)に示すデータD11及びデータD13の再書き込みが可能な期間を長くできるため、信号線駆動回路の動作不良をより抑制できる。

40

**【 0 0 6 2 】**

また、図4に示す駆動信号出力回路113\_Zの信号DOU T3が駆動信号DRV\_Zとなる。また、駆動信号出力回路113\_Z+1の信号DOU T3が駆動信号DRV\_Z+1となる。また、駆動信号出力回路113\_Z+2の信号DOU T3が駆動信号DRV\_

50

$Z + 2$  となる。

【0063】

なお、シフトレジスタ101、選択回路112、及び駆動信号出力回路113のそれぞれを、互いに同一の導電型である電界効果トランジスタを用いて構成してもよい。これにより、複数の導電型である電界効果トランジスタを用いて信号線駆動回路を構成する場合と比較して製造工程を簡略にすることができる。

【0064】

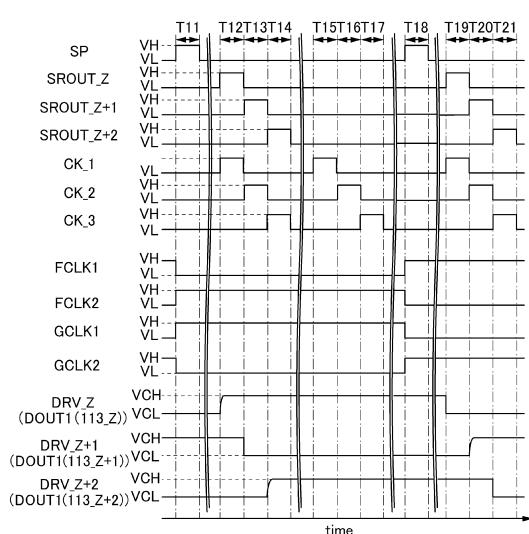

次に、本実施形態の信号線駆動回路の駆動方法例として、図1に示す信号線駆動回路の駆動方法例について図6のタイミングチャートを用いて説明する。なお、一例として、クロック信号CK\_1乃至クロック信号CK\_3のそれぞれを、デューティ比が25%であり、順に1/4周期ずつずれているクロック信号とする。また、クロック信号FCLK1、クロック信号FCLK2、クロック信号GCLK1、及びクロック信号GCLK2のそれぞれをデューティ比が50%であるクロック信号とし、クロック信号FCLK2はクロック信号FCLK1の反転信号とし、クロック信号GCLK2はクロック信号GCLK1の反転信号とする。また、タイミングチャートにおける二重波線は、省略記号を表す。

【0065】

図6に示すように、図1に示す信号線駆動回路の駆動方法例では、期間T11にスタートパルス信号SPのパルスをシフトレジスタ101に入力する。

【0066】

この場合、クロック信号CK\_1乃至クロック信号CK\_3に従って、期間T12にパルス信号SROUT\_Zのパルスが選択回路112\_Zに入力され、期間T13にパルス信号SROUT\_Z+1のパルスが選択回路112\_Z+1に入力され、期間T14にパルス信号SROUT\_Z+2のパルスが選択回路112\_Z+2に入力される。なお、期間T11乃至期間T17において、クロック信号FCLK1がローレベルになり、クロック信号FCLK2がハイレベルになり、クロック信号GCLK1がハイレベルになり、クロック信号GCLK2がローレベルになる。

【0067】

このとき、選択回路112\_Z及び選択回路112\_Z+2のそれぞれは、入力されたパルス信号SROUT\_Z又はパルス信号SROUT\_Z+2のパルスをパルス信号SROUT1のパルスとみなして出力する。

【0068】

また、選択回路112\_Z+1は、入力されたパルス信号SROUT\_Z+1のパルスをパルス信号SROUT2のパルスとみなして出力する。

【0069】

上記パルス信号SROUT1のパルスは、セット信号SINのパルスとして駆動信号出力回路113\_Z及び駆動信号出力回路113\_Z+2に入力される。セット信号SINのパルスが入力された駆動信号出力回路113では、データD1として電位VDDが書き込まれ、データD2として電位VSSが書き込まれる。よって、信号DOUT1の電位は電位VCHとなり、信号DOUT2の電位は電位VHとなる。例えば、駆動信号出力回路113\_Zの信号DOUT1(駆動信号DRV\_Z)は、期間T12に電位VCHとなり、駆動信号出力回路113\_Z+2の信号DOUT1(駆動信号DRV\_Z+2)は、期間T14に電位VCHとなる。

【0070】

また、上記パルス信号SROUT2のパルスは、リセット信号RINのパルスとして駆動信号出力回路113\_Z+1に入力される。リセット信号RINのパルスが入力された駆動信号出力回路113では、データD1として電位VSSが書き込まれ、データD2として電位VDDが書き込まれる。よって、信号DOUT1の電位は電位VCLとなり、信号DOUT2の電位は電位VLとなる。例えば、駆動信号出力回路113\_Z+1の信号DOUT1(駆動信号DRV\_Z+1)は、期間T13に電位VCLとなる。

【0071】

10

20

30

40

50

さらに、期間T15乃至期間T17では、クロック信号CK\_1乃至クロック信号CK\_3、クロック信号FCLK1及びクロック信号FCLK2、並びにクロック信号GCLK1及びクロック信号GCLK2に従って、セット信号SINのパルスが入力された駆動信号出力回路113に入力される制御信号CTL1及び制御信号CTL2がハイレベルになる。これにより、データD1として電位VDDが書き込まれた駆動信号出力回路113に、データの再書き込みとして電位VDDの書き込みが行われる。これにより、再度スタートパルス信号SPのパルスをシフトレジスタ101に入力するまでの間、データD1の電位の変動を少なくできる。

## 【0072】

さらに、期間T18に再度スタートパルス信号SPのパルスをシフトレジスタ101に入力する。 10

## 【0073】

このとき、クロック信号CK\_1乃至クロック信号CK\_3に従って期間T19にパルス信号SROUT\_Zのパルスが選択回路112\_Zに入力され、期間T20にパルス信号SROUT\_Z+1のパルスが選択回路112\_Z+1に入力され、期間T21にパルス信号SROUT\_Z+2のパルスが選択回路112\_Z+2に入力される。なお、期間T18乃至期間T21において、クロック信号FCLK1がハイレベルになり、クロック信号FCLK2がローレベルになり、クロック信号GCLK1がローレベルになり、クロック信号GCLK2がハイレベルになる。 20

## 【0074】

このとき、選択回路112\_Z及び選択回路112\_Z+2のそれぞれは、入力されたパルス信号SROUT\_Z又はパルス信号SROUT\_Z+2のパルスをパルス信号SELOUT2のパルスとみなして出力する。

## 【0075】

また、選択回路112\_Z+1は、入力されたパルス信号SROUT\_Z+1のパルスをパルス信号SELOUT1のパルスとみなして出力する。

## 【0076】

セット信号SINのパルスが入力された駆動信号出力回路113では、データD1として電位VDDが書き込まれ、データD2として電位VSSが書き込まれる。よって、信号DOUT1の電位は電位VCNとなり、信号DOUT2の電位は電位VNとなる。 30

## 【0077】

リセット信号RINのパルスが入力された駆動信号出力回路113では、データD1として電位VSSが書き込まれ、データD2として電位VDDが書き込まれる。よって、信号DOUT1の電位は電位VCLとなり、信号DOUT2の電位は電位VLとなる。

## 【0078】

なお、クロック信号FCLK1とクロック信号GCLK1を同じ信号にし、クロック信号FCLK2とクロック信号GCLK2を同じ信号にしてもよい。このとき、信号DRV\_Z+1は、第Zの信号DRV\_Zがシフトした信号となる。

## 【0079】

以上が図1に示す信号線駆動回路の駆動方法例の説明である。 40

## 【0080】

図1乃至図6を用いて説明したように、本実施形態の信号線駆動回路の一例では、シフトレジスタ、それぞれシフトレジスタから異なるパルス信号が入力され、入力されたパルス信号を第1のパルス信号とみなして出力するか第2のパルス信号とみなして出力するかを選択する複数の選択回路、及びそれぞれ異なる選択回路の第1のパルス信号及び第2のパルス信号が入力される駆動信号出力回路を備える構成にすることにより、複数の駆動信号を出力することができる。

## 【0081】

また、本実施形態の信号線駆動回路の一例では、駆動信号出力回路において、ラッチ部に記憶されたデータの再書き込みを制御するスイッチ部を設けることにより、シフトレジス 50

タからパルス信号のパルスが出力されない期間であっても該データの再書き込みを行うことができる。よって、例えば駆動信号出力回路を構成する電界効果トランジスタのリーク電流による、第1のデータとなる電位の変動を抑制できる。よって、信号線駆動回路の動作不良を抑制できる。

#### 【0082】

また、例えば、液晶表示装置又は電子ペーパーなど、複数の信号線を用いて複数の回路の駆動を制御する半導体装置に本実施形態の信号線駆動回路を適用できる。

#### 【0083】

(実施形態2)

本実施形態では、共通信号線を介して駆動信号を出力する信号線駆動回路、及び該信号線駆動回路を備える液晶表示装置の例について説明する。

10

#### 【0084】

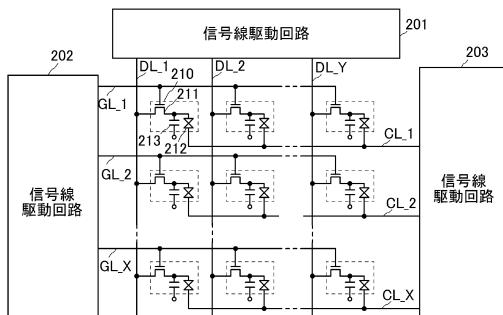

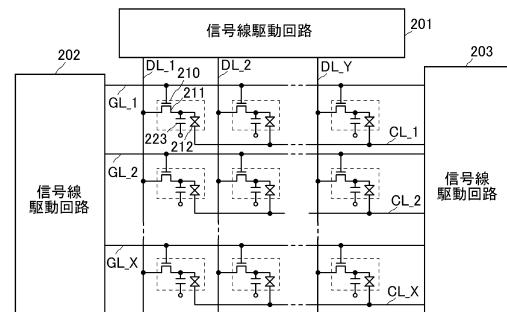

まず、液晶表示装置の構成例について図7(A)を用いて説明する。

#### 【0085】

図7(A)に示す液晶表示装置は、信号線駆動回路201と、信号線駆動回路202と、信号線駆動回路203と、データ信号線DL\_1乃至データ信号線DL\_Y(Yは2以上の自然数)と、ゲート信号線GL\_1乃至ゲート信号線GL\_X(Xは2以上の自然数)と、共通信号線CL\_1乃至共通信号線CL\_Xと、X行Y列に配列された複数の画素回路210と、を具備する。

20

#### 【0086】

信号線駆動回路201は、複数のデータ信号DS(データ信号DS\_1乃至データ信号DS\_Y)を生成する機能を有する。信号線駆動回路201は、複数のデータ信号DSにより複数のデータ信号線DL(データ信号線DL\_1乃至データ信号線DL\_Y)の電位を制御することにより、画素回路210の駆動を制御する機能を有する。

#### 【0087】

信号線駆動回路202は、複数のゲート信号GS(ゲート信号GS\_1乃至ゲート信号GS\_X)を生成する機能を有する。信号線駆動回路202は、複数のゲート信号GSにより複数のゲート信号線GL(ゲート信号線GL\_1乃至ゲート信号線GL\_X)の電位を制御することにより、画素回路210の駆動を制御する機能を有する。

#### 【0088】

30

信号線駆動回路203は、複数の共通信号CS(共通信号CS\_1乃至共通信号CS\_X)を生成する機能を有する。信号線駆動回路203は、複数の共通信号CSにより複数の共通信号線CL(共通信号線CL\_1乃至共通信号線CL\_X)の電位を制御することにより、画素回路210の駆動を制御する機能を有する。

#### 【0089】

信号線駆動回路203としては、例えば実施形態1に示す信号線駆動回路を用いることができる。

#### 【0090】

複数の画素回路210のそれぞれは、電界効果トランジスタ211と、一対の電極及び液晶層を有する液晶素子212と、容量素子213と、を備える。なお、必ずしも容量素子213を設けなくてもよい。

40

#### 【0091】

さらに、M行N列(MはX以下の自然数、NはY以下の自然数)の画素回路210において、電界効果トランジスタ211が有するソース及びドレインの一方は、データ信号線DL\_N(複数のデータ信号線DLの一つ)に電気的に接続される。また、M行N列の画素回路210において、電界効果トランジスタ211が有するゲートは、ゲート信号線GL\_M(複数のゲート信号線GLの一つ)に電気的に接続される。

#### 【0092】

また、M行N列の画素回路210において、液晶素子212が有する一対の電極の一方は、M行N列の画素回路210の電界効果トランジスタ211が有するソース及びドレイン

50

の他方に電気的に接続される。また、M行N列の画素回路210において、液晶素子212が有する一対の電極の他方は、共通信号線CL\_M（複数の共通信号線CLの一つ）に電気的に接続される。

#### 【0093】

液晶素子212は、一対の電極の間に印加される電圧に応じて液晶層に含まれる液晶の配向が制御される。

#### 【0094】

また、M行N列の画素回路210において、容量素子213が有する一対の電極の一方は、M行N列の画素回路210の電界効果トランジスタ211が有するソース及びドレインの他方に電気的に接続される。また、M行N列の画素回路210において、容量素子213が有する一対の電極の他方には、電位VSSが与えられる。

10

#### 【0095】

次に、信号線駆動回路203の構成例について図7(B)を用いて説明する。

#### 【0096】

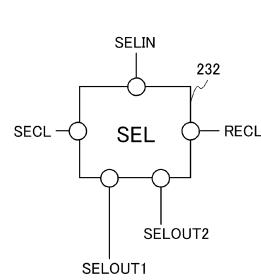

信号線駆動回路203は、シフトレジスタ230(図7(B)のシフトレジスタ230)と、複数の選択回路232(図7(B)では、選択回路232\_1乃至選択回路232\_4のみを図示)と、複数の駆動信号出力回路233(図7(B)では、駆動信号出力回路233\_1乃至駆動信号出力回路233\_4のみを図示)と、を備える。さらに、シフトレジスタ230は、パルス出力回路231\_1乃至パルス出力回路231\_Xを備える。なお、本実施形態では、選択回路232\_1乃至選択回路232\_Xと駆動信号出力回路233\_1乃至駆動信号出力回路233\_Xを設ける場合について説明する。なお、図7(A)及び図7(B)では、一例としてXが3以上の自然数の場合を示す。

20

#### 【0097】

さらに、図7(B)に示す信号線駆動回路の各構成要素について図8乃至図10を用いて説明する。

#### 【0098】

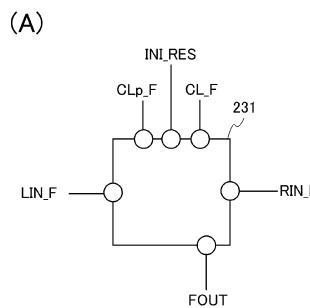

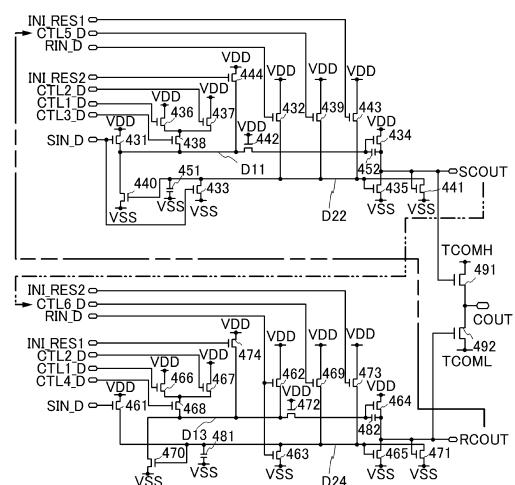

図8は、図7(B)に示すシフトレジスタ230のパルス出力回路の構成例を説明するための図である。

#### 【0099】

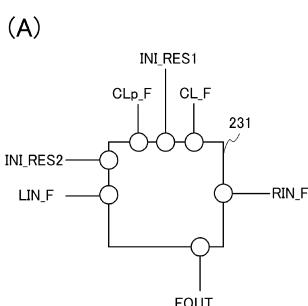

図8(A)に示すように、パルス出力回路231には、セット信号LIN\_F、リセット信号RIN\_F、クロック信号CL\_F、クロック信号CL\_p\_F、及び初期化信号INI\_R\_E\_Sが入力される。また、図8(A)に示すパルス出力回路は、信号FOUTを出力する。信号FOUTがシフトレジスタ230のパルス信号SROUTとなる。なお、初期化信号INI\_R\_E\_Sは、例えばパルス出力回路を初期化する場合などに用いる信号であり、初期化信号INI\_R\_E\_Sのパルスをパルス出力回路に入力することにより、パルス出力回路は初期化される。また、必ずしも初期化信号INI\_R\_E\_Sをパルス出力回路に入力しなくてもよい。

30

#### 【0100】

なお、パルス出力回路231\_X+1の構成は、リセット信号RIN\_Fが入力されないことを除き、他のパルス出力回路と同じ構成である。

40

#### 【0101】

さらに、図8(A)に示すパルス出力回路231は、図8(B)に示すように、電界効果トランジスタ311乃至電界効果トランジスタ319と、容量素子321及び容量素子322と、を備える。

#### 【0102】

電界効果トランジスタ311が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ311が有するゲートには、セット信号LIN\_Fが入力される。

#### 【0103】

電界効果トランジスタ312が有するソース及びドレインの一方には、電位VSSが与え

50

られる。また、電界効果トランジスタ312が有するゲートには、セット信号L I N\_Fが入力される。

【0104】

電界効果トランジスタ313が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ313が有するソース及びドレインの他方は、電界効果トランジスタ312が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ313が有するゲートには、リセット信号R I N\_Fが与えられる。

【0105】

電界効果トランジスタ314が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ314が有するソース及びドレインの他方は、電界効果トランジスタ312のソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ314が有するゲートには、初期化信号I N I\_R E Sが入力される。なお、必ずしも電界効果トランジスタ314を設けなくてもよい。

10

【0106】

電界効果トランジスタ315が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ315が有するソース及びドレインの他方は、電界効果トランジスタ312が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ315が有するゲートには、クロック信号C L p\_Fが入力される。

20

【0107】

電界効果トランジスタ316が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ316が有するソース及びドレインの他方は、電界効果トランジスタ311が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ316が有するゲートは、電界効果トランジスタ312が有するソース及びドレインの他方に電気的に接続される。

【0108】

電界効果トランジスタ317が有するソース及びドレインの一方は、電界効果トランジスタ311が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ317が有するゲートには、電位VDDが与えられる。

30

【0109】

電界効果トランジスタ318が有するソース及びドレインの一方には、クロック信号C L\_Fが入力される。また、電界効果トランジスタ318が有するゲートは、電界効果トランジスタ317が有するソース及びドレインの他方に電気的に接続される。また、図8(B)に示すパルス出力回路では、電界効果トランジスタ318が有するソース及びドレインの他方の電位が信号F O U Tの電位となる。

【0110】

電界効果トランジスタ319が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ319が有するソース及びドレインの他方は、電界効果トランジスタ318が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ319が有するゲートは、電界効果トランジスタ312が有するソース及びドレインの他方に電気的に接続される。

40

【0111】

容量素子321が有する一対の電極の一方には、電位VSSが与えられる。また、容量素子321が有する一対の電極の他方は、電界効果トランジスタ312が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも容量素子321を設けなくてもよい。

【0112】

容量素子322が有する一対の電極の一方は、電界効果トランジスタ318が有するゲートに電気的に接続される。また、容量素子322が有する一対の電極の他方は、電界効果

50

トランジスタ 318 が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも容量素子 322 を設けなくてもよい。

【0113】

図 8 (B) に示すパルス出力回路では、セット信号 L I N\_F に従って電界効果トランジスタ 311 及び電界効果トランジスタ 312 がオン状態になり、電界効果トランジスタ 318 がオン状態になることにより、信号 F O U T の電位がクロック信号 C L\_F の電位と同等の値になる。このとき、電界効果トランジスタ 319 はオフ状態である。また、図 8 (B) に示すパルス出力回路では、リセット信号 R I N\_F に従って電界効果トランジスタ 313 がオン状態になり、電界効果トランジスタ 319 がオン状態になることにより、信号 F O U T の電位が電位 V S S と同等の値になる。このとき、電界効果トランジスタ 313 がオン状態であり、電界効果トランジスタ 316 がオン状態になるため、電界効果トランジスタ 318 はオフ状態である。これにより、パルス出力回路は、パルス信号を出力する。

10

【0114】

また、図 7 (B) に示すシフトレジスタ 230 では、パルス出力回路 231\_1 のセット信号 L I N\_F としてスタートパルス信号 S\_P が入力される。

【0115】

なお、信号線駆動回路 203 にスタートパルス信号 S\_P を入力するための配線に、保護回路を電気的に接続してもよい。

【0116】

また、シフトレジスタ 230 において、パルス出力回路 231\_K (K は 2 以上 X 以下の自然数) のセット信号 L I N\_F としてパルス出力回路 231\_K - 1 の信号 F O U T が入力される。

20

【0117】

また、シフトレジスタ 230 において、パルス出力回路 231\_M のリセット信号 R I N\_F としてパルス出力回路 231\_M + 1 の信号 F O U T が入力される。

【0118】

また、シフトレジスタ 230 において、パルス出力回路 231\_1 のクロック信号 C L\_F としてクロック信号 C L\_K 1 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 2 が入力される。さらに、パルス出力回路 231\_1 を基準として、3つおきのパルス出力回路毎にクロック信号 C L\_F としてクロック信号 C L\_K 1 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 2 が入力される。

30

【0119】

また、シフトレジスタ 230 において、パルス出力回路 231\_2 のクロック信号 C L\_F としてクロック信号 C L\_K 2 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 3 が入力される。さらに、パルス出力回路 231\_2 を基準として、3つおきのパルス出力回路毎にクロック信号 C L\_F としてクロック信号 C L\_K 2 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 3 が入力される。

【0120】

また、シフトレジスタ 230 において、パルス出力回路 231\_3 のクロック信号 C L\_F としてクロック信号 C L\_K 3 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 4 が入力される。さらに、パルス出力回路 231\_3 を基準として、3つおきのパルス出力回路毎にクロック信号 C L\_F としてクロック信号 C L\_K 3 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 4 が入力される。

40

【0121】

また、シフトレジスタ 230 において、パルス出力回路 231\_4 のクロック信号 C L\_F としてクロック信号 C L\_K 4 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 1 が入力される。さらに、パルス出力回路 231\_4 を基準として、3つおきのパルス出力回路毎にクロック信号 C L\_F としてクロック信号 C L\_K 4 が入力され、クロック信号 C L\_p\_F としてクロック信号 C L\_K 1 が入力される。

50

**【 0 1 2 2 】**

なお、クロック信号 C L K 1 を入力するための配線乃至クロック信号 C L K 4 を入力するための配線のそれぞれに保護回路を電気的に接続してもよい。

**【 0 1 2 3 】**

以上がパルス出力回路の説明である。

**【 0 1 2 4 】**

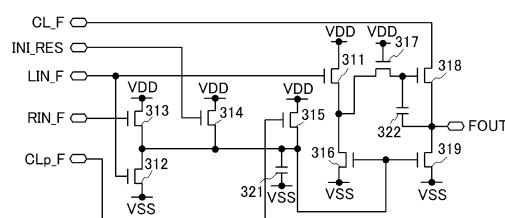

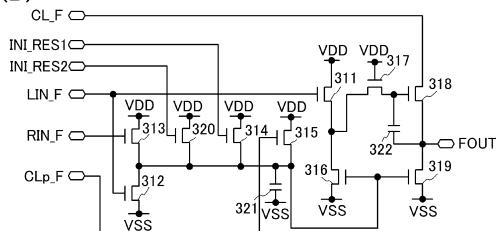

さらに、図 9 は、選択回路の構成例を説明するための図である。

**【 0 1 2 5 】**

図 9 ( A ) に示すように、選択回路 2 3 2 には、パルス信号 S E L I N 、クロック信号 S E C L 、及びクロック信号 R E C L が入力される。また、選択回路 2 3 2 は、パルス信号 S E L O U T 1 及びパルス信号 S E L O U T 2 を出力する。選択回路 2 3 2 は、クロック信号 S E C L 及びクロック信号 R E C L に従ってパルス信号 S E L I N をパルス信号 S E L O U T 1 とみなして出力するかパルス信号 S E L O U T 2 とみなして出力するかを選択する機能を有する。

10

**【 0 1 2 6 】**

また、図 9 ( A ) に示す選択回路 2 3 2 は、図 9 ( B ) に示すように、電界効果トランジスタ 3 3 1 乃至電界効果トランジスタ 3 3 6 と、を備える。

**【 0 1 2 7 】**

電界効果トランジスタ 3 3 1 が有するソース及びドレインの一方には、パルス信号 S E L I N が入力される。また、電界効果トランジスタ 3 3 1 が有するソース及びドレインの他方の電位がパルス信号 S E L O U T 1 の電位となる。

20

**【 0 1 2 8 】**

電界効果トランジスタ 3 3 2 が有するソース及びドレインの一方には、パルス信号 S E L I N が入力される。また、電界効果トランジスタ 3 3 2 が有するソース及びドレインの他方の電位がパルス信号 S E L O U T 2 の電位となる。

**【 0 1 2 9 】**

電界効果トランジスタ 3 3 3 が有するソース及びドレインの一方には、電位 V S S が与えられる。また、電界効果トランジスタ 3 3 3 が有するソース及びドレインの他方は、電界効果トランジスタ 3 3 1 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 3 3 3 が有するゲートには、クロック信号 R E C L が入力される。

30

**【 0 1 3 0 】**

電界効果トランジスタ 3 3 4 が有するソース及びドレインの一方には、電位 V S S が与えられる。また、電界効果トランジスタ 3 3 4 が有するソース及びドレインの他方は、電界効果トランジスタ 3 3 2 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 3 3 4 が有するゲートには、クロック信号 S E C L が入力される。

**【 0 1 3 1 】**

電界効果トランジスタ 3 3 5 が有するソース及びドレインの一方には、クロック信号 S E C L が入力される。また、電界効果トランジスタ 3 3 5 が有するソース及びドレインの他方は、電界効果トランジスタ 3 3 1 が有するゲートに電気的に接続される。また、電界効果トランジスタ 3 3 5 が有するゲートには、電位 V D D が与えられる。なお、必ずしも電界効果トランジスタ 3 3 5 を設けなくてもよい。

40

**【 0 1 3 2 】**

電界効果トランジスタ 3 3 6 が有するソース及びドレインの一方には、クロック信号 R E C L が入力される。また、電界効果トランジスタ 3 3 6 が有するソース及びドレインの他方は、電界効果トランジスタ 3 3 2 が有するゲートに電気的に接続される。また、電界効果トランジスタ 3 3 6 が有するゲートには、電位 V D D が与えられる。なお、必ずしも電界効果トランジスタ 3 3 6 を設けなくてもよい。

**【 0 1 3 3 】**

図9(B)に示す選択回路では、クロック信号SEC Lに従って電界効果トランジスタ331がオン状態になることにより、パルス信号SEL INがパルス信号SEL OUT 1とみなして出力される。このとき、電界効果トランジスタ332はオフ状態であり、電界効果トランジスタ334はオン状態である。また、図9(B)に示す選択回路では、クロック信号REC Lに従って電界効果トランジスタ332がオン状態になることにより、パルス信号SEL INがパルス信号SEL OUT 2とみなして出力される。このとき、電界効果トランジスタ331はオフ状態であり、電界効果トランジスタ333はオン状態である。

#### 【0134】

また、図7(B)に示す選択回路232\_1のパルス信号SEL INとしてスタートパルス信号SPが入力される。

10

#### 【0135】

また、選択回路232\_Kのパルス信号SEL INとしてパルス出力回路231\_K-1の信号FOUTが入力される。

#### 【0136】

また、選択回路232\_Q(Qは1以上X以下の奇数)のクロック信号SEC Lとしてクロック信号FCLK1が入力される。

#### 【0137】

また、選択回路232\_Qのクロック信号REC Lとしてクロック信号FCLK2が入力される。

20

#### 【0138】

また、選択回路232\_R(Rは2以上X以下の偶数)のクロック信号SEC Lとしてクロック信号GCLK1が入力される。

#### 【0139】

また、選択回路232\_Rのクロック信号REC Lとしてクロック信号GCLK2が入力される。

#### 【0140】

なお、クロック信号FCLK1を入力するための配線、クロック信号FCLK2を入力するための配線、クロック信号GCLK1を入力するための配線、及びクロック信号GCLK2を入力するための配線のそれぞれに保護回路を電気的に接続してもよい。

30

#### 【0141】

以上が選択回路の説明である。

#### 【0142】

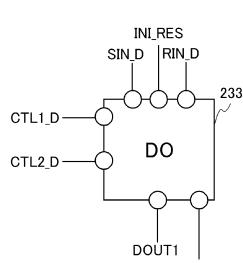

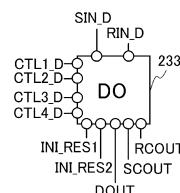

さらに、図10は、駆動信号出力回路の例を説明するための図である。

#### 【0143】

図10(A)に示すように、駆動信号出力回路233には、セット信号SIN\_D、リセット信号RIN\_D、制御信号CTL1\_D、制御信号CTL2\_D、及び初期化信号INI\_RE Sが入力される。なお、初期化信号INI\_RE Sのパルスを駆動信号出力回路に入力することにより、駆動信号出力回路233は初期化される。また、必ずしも初期化信号INI\_RE Sを駆動信号出力回路233に入力しなくてもよい。また、駆動信号出力回路233は、信号DOUT1及び信号DOUT2を出力する。信号DOUT1が駆動信号出力回路233から出力される共通信号となる。なお、信号DOUT1を出力するための配線に保護回路を電気的に接続してもよい。また、図10(A)に示す駆動信号出力回路233は、図3に示す駆動信号出力回路と同様に、ラッチ部と、第1のバッファ部と、第2のバッファ部と、スイッチ部と、を含む。さらに、詳細について以下に説明する。

40

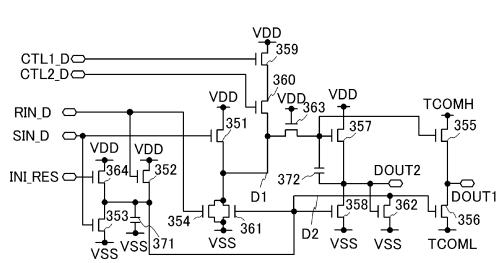

#### 【0144】

図10(A)に示す駆動信号出力回路233は、図10(B)に示すように、電界効果トランジスタ351乃至電界効果トランジスタ364と、容量素子371及び容量素子372と、を備える。なお、電界効果トランジスタ351乃至電界効果トランジスタ364の

50

それぞれは、Nチャネル型トランジスタである。

【0145】

電界効果トランジスタ351は、ラッチ部に設けられる。また、電界効果トランジスタ351が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ351が有するゲートには、セット信号SIN\_Dが入力される。

【0146】

電界効果トランジスタ352は、ラッチ部に設けられる。また、電界効果トランジスタ352が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ352が有するゲートには、リセット信号RIN\_Dが入力される。

【0147】

電界効果トランジスタ353は、ラッチ部に設けられる。また、電界効果トランジスタ353が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ353が有するソース及びドレインの他方は、電界効果トランジスタ352が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ353が有するゲートには、セット信号SIN\_Dが入力される。

【0148】

電界効果トランジスタ354は、ラッチ部に設けられる。また、電界効果トランジスタ354が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ354が有するソース及びドレインの他方は、電界効果トランジスタ351が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ354が有するゲートには、リセット信号RIN\_Dが入力される。

【0149】

電界効果トランジスタ355は、第1のバッファ部に設けられる。また、電界効果トランジスタ355が有するソース及びドレインの一方には、電位TCOMHが与えられる。また、電界効果トランジスタ355が有するソース及びドレインの他方の電位が信号DOUT1の電位となる。

【0150】

電界効果トランジスタ356は、第1のバッファ部に設けられる。また、電界効果トランジスタ356が有するソース及びドレインの一方には、電位TCOMLが与えられる。また、電界効果トランジスタ356が有するソース及びドレインの他方は、電界効果トランジスタ355が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ356が有するゲートは、電界効果トランジスタ352が有するソース及びドレインの他方に電気的に接続される。

【0151】

なお、電位TCOMH及び電位TCOMLは、共通信号の電位を設定するための電位であり、電位TCOMHは、電位TCOMLよりも高い電位である。

【0152】

電界効果トランジスタ357は、第2のバッファ部に設けられる。また、電界効果トランジスタ357が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ357が有するソース及びドレインの他方の電位が信号DOUT2の電位となる。

【0153】

電界効果トランジスタ358は、第2のバッファ部に設けられる。また、電界効果トランジスタ358が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ358が有するソース及びドレインの他方は、電界効果トランジスタ357が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ358が有するゲートは、電界効果トランジスタ352が有するソース及びドレインの他方に電気的に接続される。

【0154】

電界効果トランジスタ359は、スイッチ部に設けられる。また、電界効果トランジスタ

10

20

30

40

50

359が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ359が有するゲートには、制御信号CTL1\_Dが入力される。

**【0155】**

電界効果トランジスタ360は、スイッチ部に設けられる。また、電界効果トランジスタ360が有するソース及びドレインの一方は、電界効果トランジスタ359が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ360が有するソース及びドレインの他方は、電界効果トランジスタ351が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ360が有するゲートには、制御信号CTL2\_Dが入力される。

**【0156】**

電界効果トランジスタ361が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ361が有するソース及びドレインの他方は、電界効果トランジスタ351が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ361が有するゲートは、電界効果トランジスタ352が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも電界効果トランジスタ361を設けなくてもよい。

10

**【0157】**

電界効果トランジスタ362が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ362が有するソース及びドレインの他方は、電界効果トランジスタ352が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ362が有するゲートは、電界効果トランジスタ357が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも電界効果トランジスタ362を設けなくてもよい。

20

**【0158】**

電界効果トランジスタ363が有するソース及びドレインの一方は、電界効果トランジスタ351が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ363が有するソース及びドレインの他方は、電界効果トランジスタ355が有するゲート及び電界効果トランジスタ357が有するゲートに電気的に接続される。また、電界効果トランジスタ363が有するゲートには、電位VDDが与えられる。なお、必ずしも電界効果トランジスタ363を設けなくてもよい。

30

**【0159】**

電界効果トランジスタ364が有するソース及びドレインの一方には、電位VDDが与えられる。また、電界効果トランジスタ364が有するソース及びドレインの他方は、電界効果トランジスタ356が有するゲート及び電界効果トランジスタ358が有するゲートに電気的に接続される。また、電界効果トランジスタ364が有するゲートには、初期化信号INIRESが入力される。なお、必ずしも電界効果トランジスタ364を設けなくてもよい。

**【0160】**

容量素子371が有する一対の電極の一方には、電位VSSが与えられる。また、容量素子371が有する一対の電極の他方は、電界効果トランジスタ356が有するゲート及び電界効果トランジスタ358が有するゲートに電気的に接続される。なお、必ずしも容量素子371を設けなくてもよい。

40

**【0161】**

容量素子372が有する一対の電極の一方は、電界効果トランジスタ355が有するゲート及び電界効果トランジスタ357が有するゲートに電気的に接続され、容量素子372が有する一対の電極の他方は、電界効果トランジスタ357が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも容量素子372を設けなくてもよい。

**【0162】**

図10(B)に示す駆動信号出力回路では、セット信号SIN\_Dに従って電界効果トランジスタ351及び電界効果トランジスタ353がオン状態になり、電界効果トランジス

50

タ355がオン状態になることにより、信号DOUT1の電位が電位T COMHと同等の値になる。このとき、電界効果トランジスタ356はオフ状態である。また、図10(B)に示す駆動信号出力回路では、リセット信号RIN\_Dに従って電界効果トランジスタ352及び電界効果トランジスタ354がオン状態になり、電界効果トランジスタ356がオン状態になることにより、信号DOUT1の電位が電位T COMLと同等の値になる。このとき、電界効果トランジスタ355はオフ状態である。

#### 【0163】

また、図7(B)に示す駆動信号出力回路233\_Mのセット信号SIN\_Dとして選択回路232\_Mのパルス信号SELOUT1が入力される。

#### 【0164】

また、駆動信号出力回路233\_Mのリセット信号RIN\_Dとして選択回路232\_Mのパルス信号SELOUT2が入力される。

#### 【0165】

また、駆動信号出力回路233\_1の制御信号CTL1\_Dとしてクロック信号CLK4が入力される。さらに、駆動信号出力回路233\_1を基準として、3つおきの駆動信号出力回路毎に制御信号CTL1\_Dとしてクロック信号CLK4が入力される。

#### 【0166】

また、駆動信号出力回路233\_2の制御信号CTL1\_Dとしてクロック信号CLK1が入力される。さらに、駆動信号出力回路233\_2を基準として、3つおきの駆動信号出力回路毎に制御信号CTL1\_Dとしてクロック信号CLK1が入力される。

#### 【0167】

また、駆動信号出力回路233\_3の制御信号CTL1\_Dとしてクロック信号CLK2が入力される。さらに、駆動信号出力回路233\_3を基準として、3つおきの駆動信号出力回路毎に制御信号CTL1\_Dとしてクロック信号CLK2が入力される。

#### 【0168】

また、駆動信号出力回路233\_4の制御信号CTL1\_Dとしてクロック信号CLK3が入力される。さらに、駆動信号出力回路233\_4を基準として、3つおきの駆動信号出力回路毎に制御信号CTL1\_Dとしてクロック信号CLK3が入力される。

#### 【0169】

また、駆動信号出力回路233\_1の制御信号CTL2\_Dとしてクロック信号FCLK1が入力される。

#### 【0170】

また、駆動信号出力回路233\_2の制御信号CTL2\_Dとしてクロック信号GCLK1が入力される。

#### 【0171】

また、駆動信号出力回路233\_L(Lは3以上X以下の自然数)の制御信号CTL2\_Dとして駆動信号出力回路233\_L-2の信号DOUT2が入力される。

#### 【0172】

また、駆動信号出力回路233\_Mの信号DOUT1が共通信号CS\_Mとなる。

#### 【0173】

以上が図7(B)に示す信号線駆動回路の説明である。

#### 【0174】

また、本実施形態の液晶表示装置の構成を、図11(A)に示す構成にすることもできる。図11(A)に示す液晶表示装置は、信号線駆動回路203に複数のゲート信号線GL及び複数の共通信号線CLが電気的に接続された構成である。

#### 【0175】

このときの信号線駆動回路203の構成例を図11(B)に示す。図11(B)に示すシフトレジスタ230は、信号線駆動回路202に設けられる。また、複数の選択回路232及び複数の駆動信号出力回路233は、信号線駆動回路203に設けられる。これにより、信号線駆動回路203にシフトレジスタを設けなくても信号線駆動回路202のシフ

10

20

30

40

50

トレジスタ 230 を用いて信号線駆動回路 203 の選択回路 232 にパルス信号 SROUT を出力できる。

**【0176】**

また、本実施形態の液晶表示装置の構成を、図 12 (A) に示す構成にすることもできる。図 12 (A) に示す液晶表示装置は、信号線駆動回路 202 及び信号線駆動回路 203 の代わりに信号線駆動回路 204 を備える構成である。

**【0177】**

信号線駆動回路 204 の構成例を図 12 (B) に示す。図 12 (B) に示す信号線駆動回路 204 は、図 7 (B) に示す信号線駆動回路の構成に加え、ゲート信号 GS\_1 乃至ゲート信号 GS\_X を出力する機能を有する。

10

**【0178】**

図 12 (B) に示す信号線駆動回路では、パルス出力回路 231\_M の信号 FOUT がゲート信号 GS\_M となる。

**【0179】**

また、図 7 (B) に示す信号線駆動回路を他の構成にすることもできる。図 7 (B) に示す信号線駆動回路の他の構成例について図 13 に示す。

**【0180】**

図 13 に示す信号線駆動回路は、図 7 (B) に示す信号線駆動回路と比較してシフトレジスタのパルス出力回路と駆動信号出力回路の構成が異なる。

**【0181】**

図 13 に示すパルス出力回路の構成例について図 14 を用いて説明する。

20

**【0182】**

図 14 (A) に示すパルス出力回路 231 には、初期化信号INI\_RESET の代わりに、初期化信号INI\_RESET\_1 及び初期化信号INI\_RESET\_2 が入力される。なお、初期化信号INI\_RESET\_1 及び初期化信号INI\_RESET\_2 は、例えば回路における複数の接続箇所の電位を独立に初期化する場合などに用いる信号であり、初期化信号INI\_RESET\_1 及び初期化信号INI\_RESET\_2 のパルスをパルス出力回路に入力することにより、パルス出力回路は初期化される。なお、初期化信号INI\_RESET\_1 及び初期化信号INI\_RESET\_2 は、異なる波形の信号である。また、必ずしも初期化信号INI\_RESET\_1 及び初期化信号INI\_RESET\_2 をパルス出力回路に入力しなくてもよい。

30

**【0183】**

さらに、図 14 (A) に示すパルス出力回路は、図 14 (B) に示すように、図 8 (B) に示すパルス出力回路の構成に加え、電界効果トランジスタ 320 を備える。

**【0184】**

電界効果トランジスタ 320 が有するソース及びドレインの一方には、電位 VDD が与えられる。また、電界効果トランジスタ 320 が有するソース及びドレインの他方は、電界効果トランジスタ 319 が有するゲートに電気的に接続される。また、電界効果トランジスタ 320 が有するゲートには、初期化信号INI\_RESET\_2 が入力される。

**【0185】**

また、図 14 (B) に示すパルス出力回路において、電界効果トランジスタ 314 のゲートには、初期化信号INI\_RESET の代わりに初期化信号INI\_RESET\_1 が入力される。

40

**【0186】**

以上が図 13 に示すパルス出力回路の説明である。

**【0187】**

また、図 13 に示す駆動信号出力回路の構成例について図 15 を用いて説明する。

**【0188】**

図 15 (A) に示す駆動信号出力回路 233 には、セット信号SIN\_D、リセット信号RIN\_D、制御信号CTL1\_D 乃至制御信号CTL4\_D、初期化信号INI\_RESET\_1、及び初期化信号INI\_RESET\_2 が入力される。なお、初期化信号INI\_RESET

50

1 及び初期化信号 I N I \_ R E S 2 のパルスを駆動信号出力回路に入力することにより、駆動信号出力回路は初期化される。また、必ずしも初期化信号 I N I \_ R E S 1 及び初期化信号 I N I \_ R E S 2 を駆動信号出力回路に入力しなくてよい。また、図 15 ( A ) に示すように、図 13 に示す複数の駆動信号出力回路 233 のそれぞれは、信号 S C O U T 、信号 R C O U T 、及び信号 D O U T を出力する機能を有する。信号 D O U T が共通信号となる。

#### 【 0 1 8 9 】

さらに、図 15 ( A ) に示す駆動信号出力回路は、データ D 1 1 及びデータ D 2 2 を記憶する第 1 のラッチ部と、データ D 1 3 及びデータ D 2 4 を記憶する第 2 のラッチ部と、第 1 のバッファ部と、第 2 のバッファ部と、第 1 のスイッチ部と、第 2 のスイッチ部と、第 3 のスイッチ部と、第 4 のスイッチ部と、第 3 のバッファ部と、を含む。さらに、詳細について以下に説明する。

10

#### 【 0 1 9 0 】

図 15 ( A ) に示す駆動信号出力回路は、図 15 ( B ) に示すように、電界効果トランジスタ 431 乃至電界効果トランジスタ 444 と、容量素子 451 及び容量素子 452 と、電界効果トランジスタ 461 乃至電界効果トランジスタ 474 と、容量素子 481 及び容量素子 482 と、を備える。

#### 【 0 1 9 1 】

電界効果トランジスタ 431 は、第 1 のラッチ部に設けられ、電界効果トランジスタ 461 は、第 2 のラッチ部に設けられる。また、電界効果トランジスタ 431 及び電界効果トランジスタ 461 が有するソース及びドレインの一方のそれぞれには、電位 V D D が与えられる。また、電界効果トランジスタ 431 及び電界効果トランジスタ 461 が有するゲートのそれぞれには、セット信号 S I N \_ D が入力される。なお、電界効果トランジスタ 431 が有するソース及びドレインの他方の電位がデータ D 1 1 となる。また、電界効果トランジスタ 461 が有するソース及びドレインの他方の電位がデータ D 2 4 となる。

20

#### 【 0 1 9 2 】

電界効果トランジスタ 432 は、第 1 のラッチ部に設けられ、電界効果トランジスタ 462 は、第 2 のラッチ部に設けられる。また、電界効果トランジスタ 432 及び電界効果トランジスタ 462 が有するソース及びドレインの一方のそれぞれには、電位 V D D が与えられる。また、電界効果トランジスタ 432 及び電界効果トランジスタ 462 が有するゲートのそれぞれには、リセット信号 R I N \_ D が入力される。なお、電界効果トランジスタ 432 が有するソース及びドレインの他方の電位がデータ D 2 2 となる。また、電界効果トランジスタ 462 が有するソース及びドレインの他方の電位がデータ D 1 3 となる。

30

#### 【 0 1 9 3 】

電界効果トランジスタ 433 は、第 1 のラッチ部に設けられる。また、電界効果トランジスタ 433 が有するソース及びドレインの一方には、電位 V S S が与えられる。また、電界効果トランジスタ 433 が有するソース及びドレインの他方は、電界効果トランジスタ 432 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 433 が有するゲートには、セット信号 S I N \_ D が入力される。

#### 【 0 1 9 4 】

40

電界効果トランジスタ 463 は、第 2 のラッチ部に設けられる。また、電界効果トランジスタ 463 が有するソース及びドレインの一方には、電位 V S S が与えられる。また、電界効果トランジスタ 463 が有するソース及びドレインの他方は、電界効果トランジスタ 461 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 463 が有するゲートには、リセット信号 R I N \_ D が入力される。

#### 【 0 1 9 5 】

電界効果トランジスタ 434 は、第 1 のバッファ部に設けられ、電界効果トランジスタ 464 は、第 2 のバッファ部に設けられる。また、電界効果トランジスタ 434 及び電界効果トランジスタ 464 が有するソース及びドレインの一方のそれぞれには、電位 V D D が与えられる。また、電界効果トランジスタ 434 が有するソース及びドレインの他方の電

50

位が信号 S C O U T の電位となり、電界効果トランジスタ 4 6 4 が有するソース及びドレインの他方の電位が信号 R C O U T の電位となる。

#### 【 0 1 9 6 】

電界効果トランジスタ 4 3 5 は、第 1 のバッファ部に設けられ、電界効果トランジスタ 4 6 5 は、第 2 のバッファ部に設けられる。また、電界効果トランジスタ 4 3 5 及び電界効果トランジスタ 4 6 5 が有するソース及びドレインの一方のそれぞれには、電位 V S S が与えられる。また、電界効果トランジスタ 4 3 5 が有するソース及びドレインの他方は、電界効果トランジスタ 4 3 4 が有するソース及びドレインの他方に電気的に接続され、電界効果トランジスタ 4 6 5 が有するソース及びドレインの他方は、電界効果トランジスタ 4 6 4 が有するソース及びドレインの他方に電気的に接続される。

10

#### 【 0 1 9 7 】

電界効果トランジスタ 4 3 6 は、第 1 のスイッチ部に設けられ、電界効果トランジスタ 4 6 6 は、第 2 のスイッチ部に設けられる。また、電界効果トランジスタ 4 3 6 及び電界効果トランジスタ 4 6 6 が有するソース及びドレインの一方のそれぞれには、電位 V D D が与えられる。また、電界効果トランジスタ 4 3 6 及び電界効果トランジスタ 4 6 6 が有するゲートのそれぞれには、制御信号 C T L 1 \_ D が入力される。

#### 【 0 1 9 8 】

電界効果トランジスタ 4 3 7 は、第 1 のスイッチ部に設けられ、電界効果トランジスタ 4 6 7 は、第 2 のスイッチ部に設けられる。また、電界効果トランジスタ 4 3 7 及び電界効果トランジスタ 4 6 7 が有するソース及びドレインの一方のそれぞれには、電位 V D D が与えられる。また、電界効果トランジスタ 4 3 7 及び電界効果トランジスタ 4 6 7 が有するゲートのそれぞれには、制御信号 C T L 2 \_ D が入力される。

20

#### 【 0 1 9 9 】

電界効果トランジスタ 4 3 8 は、第 1 のスイッチ部に設けられる。また、電界効果トランジスタ 4 3 8 が有するソース及びドレインの一方は、電界効果トランジスタ 4 3 6 が有するソース及びドレインの他方、並びに電界効果トランジスタ 4 3 7 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 4 3 8 が有するソース及びドレインの他方は、電界効果トランジスタ 4 3 1 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 4 3 8 が有するゲートには、制御信号 C T L 3 \_ D が入力される。

30

#### 【 0 2 0 0 】

電界効果トランジスタ 4 6 8 は、第 2 のスイッチ部に設けられる。また、電界効果トランジスタ 4 6 8 が有するソース及びドレインの一方は、電界効果トランジスタ 4 6 6 が有するソース及びドレインの他方、並びに電界効果トランジスタ 4 6 7 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 4 6 8 が有するソース及びドレインの他方は、電界効果トランジスタ 4 6 2 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 4 6 8 が有するゲートには、制御信号 C T L 4 \_ D が入力される。

#### 【 0 2 0 1 】

電界効果トランジスタ 4 3 9 は、第 3 のスイッチ部に設けられる。また、電界効果トランジスタ 4 3 9 が有するソース及びドレインの一方には、電位 V D D が与えられる。また、電界効果トランジスタ 4 3 9 が有するソース及びドレインの他方は、電界効果トランジスタ 4 3 2 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ 4 3 9 が有するゲートには、制御信号 C T L 5 \_ D として信号 R C O U T が入力される。

40

#### 【 0 2 0 2 】

電界効果トランジスタ 4 6 9 は、第 4 のスイッチ部に設けられる。電界効果トランジスタ 4 6 9 が有するソース及びドレインの一方には、電位 V D D が与えられる。また、電界効果トランジスタ 4 6 9 が有するソース及びドレインの他方は、電界効果トランジスタ 4 6 1 が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジス

50

タ469が有するゲートには、制御信号CTL6\_Dとして信号SCOUTが入力される。

【0203】

電界効果トランジスタ440が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ440が有するソース及びドレインの他方は、電界効果トランジスタ431が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ440が有するゲートは、電界効果トランジスタ432が有するソース及びドレインの他方に電気的に接続される。

【0204】

電界効果トランジスタ470が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ470が有するソース及びドレインの他方は、電界効果トランジスタ462が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ470が有するゲートは、電界効果トランジスタ461が有するソース及びドレインの他方に電気的に接続される。

10

【0205】

電界効果トランジスタ441が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ441が有するソース及びドレインの他方は、電界効果トランジスタ432が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ441が有するゲートは、電界効果トランジスタ434が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも電界効果トランジスタ441を設けなくてもよい。

20

【0206】

電界効果トランジスタ471が有するソース及びドレインの一方には、電位VSSが与えられる。また、電界効果トランジスタ471が有するソース及びドレインの他方は、電界効果トランジスタ463が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ471が有するゲートは、電界効果トランジスタ464が有するソース及びドレインの他方に電気的に接続される。なお、必ずしも電界効果トランジスタ471を設けなくてもよい。

【0207】

電界効果トランジスタ442が有するソース及びドレインの一方は、電界効果トランジスタ431が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ442が有するソース及びドレインの他方は、電界効果トランジスタ434が有するゲートに電気的に接続される。また、電界効果トランジスタ442が有するゲートには、電位VDDが与えられる。なお、必ずしも電界効果トランジスタ442を設けなくてもよい。

30

【0208】

電界効果トランジスタ472が有するソース及びドレインの一方は、電界効果トランジスタ462が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ472が有するソース及びドレインの他方は、電界効果トランジスタ464が有するゲートに電気的に接続される。また、電界効果トランジスタ472が有するゲートには、電位VDDが与えられる。なお、必ずしも電界効果トランジスタ472を設けなくてもよい。

40

【0209】

電界効果トランジスタ443及び電界効果トランジスタ473が有するソース及びドレインの一方のそれぞれには、電位VDDが与えられる。また、電界効果トランジスタ443が有するソース及びドレインの他方は、電界効果トランジスタ435が有するゲートに電気的に接続され、電界効果トランジスタ473が有するソース及びドレインの他方は、電界効果トランジスタ465が有するゲートに電気的に接続される。また、電界効果トランジスタ443が有するゲートには、初期化信号INIRES1が入力され、電界効果トランジスタ473が有するゲートには、初期化信号INIRES2が入力される。なお

50

、必ずしも電界効果トランジスタ443及び電界効果トランジスタ473を設けなくてもよい。

#### 【0210】

電界効果トランジスタ444及び電界効果トランジスタ474が有するソース及びドレインの一方のそれぞれには、電位VDDが与えられる。また、電界効果トランジスタ444が有するソース及びドレインの他方は、電界効果トランジスタ431が有するソース及びドレインの他方に電気的に接続され、電界効果トランジスタ474が有するソース及びドレインの他方は、電界効果トランジスタ462が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ444が有するゲートには、初期化信号INIRES2が入力され、電界効果トランジスタ474が有するゲートには、初期化信号INIRES1が入力される。なお、必ずしも電界効果トランジスタ444及び電界効果トランジスタ474を設けなくてもよい。10

#### 【0211】

容量素子451が有する一対の電極の一方には、電位VSSが与えられる。また、容量素子451が有する一対の電極の他方には、電界効果トランジスタ435が有するゲートに電気的に接続される。

#### 【0212】

容量素子481が有する一対の電極の一方には、電位VSSが与えられる。また、容量素子481が有する一対の電極の他方は、電界効果トランジスタ465が有するゲートに電気的に接続される。20

#### 【0213】

容量素子452が有する一対の電極の一方は、電界効果トランジスタ434が有するゲートに電気的に接続される。また、容量素子452が有する一対の電極の他方は、電界効果トランジスタ434が有するソース及びドレインの他方に電気的に接続される。

#### 【0214】

容量素子482が有する一対の電極の一方は、電界効果トランジスタ464が有するゲートに電気的に接続される。また、容量素子482が有する一対の電極の他方は、電界効果トランジスタ464が有するソース及びドレインの他方に電気的に接続される。

#### 【0215】

なお、必ずしも容量素子451、容量素子452、容量素子481、及び容量素子482を設けなくてもよい。30

#### 【0216】

電界効果トランジスタ491は、第3のバッファ部に設けられる。また、電界効果トランジスタ491が有するソース及びドレインの一方には、電位TCOMHが与えられる。電位TCOMHは、電位VDDよりも大きい値の電位である。また、電界効果トランジスタ491が有するソース及びドレインの他方の電位が信号COUTの電位となる。また、電界効果トランジスタ491が有するゲートには、信号SCOUTが入力される。

#### 【0217】

電界効果トランジスタ492は、第3のバッファ部に設けられる。また、電界効果トランジスタ492が有するソース及びドレインの一方には、電位TCOMLが与えられる。電位TCOMLは、電位VSSよりも小さい値の電位である。また、電界効果トランジスタ492が有するソース及びドレインの他方は、電界効果トランジスタ491が有するソース及びドレインの他方に電気的に接続される。また、電界効果トランジスタ492が有するゲートには、信号RCOUTが入力される。40

#### 【0218】

図15(B)に示す駆動信号出力回路では、セット信号SIN\_Dに従って電界効果トランジスタ431及び電界効果トランジスタ433がオン状態になり、第1のラッチ部のデータD11として電位VDDが書き込まれ、電界効果トランジスタ434がオン状態になり、信号SCOUTの電位が電位VHとなり、信号SCOUTがハイレベルになる。このとき、第1のラッチ部のデータD22として電位VSSが書き込まれ、電界効果トランジ50

スタ435はオフ状態である。また、セット信号SIN\_Dに従って電界効果トランジスタ461がオン状態になり、第2のラッチ部のデータD24として電位VDDが書き込まれ、電界効果トランジスタ465がオン状態になり、信号RCOUTの電位が電位VLとなり、信号RCOUTがローレベルになる。このとき、電界効果トランジスタ464はオフ状態である。

#### 【0219】

また、図15(B)に示す駆動信号出力回路では、リセット信号RIN\_Dに従って電界効果トランジスタ432がオン状態になり、第1のラッチ部のデータD22として電位VDDが書き込まれ、電界効果トランジスタ435がオン状態になり、信号SCOUTの電位が電位VLとなり、信号SCOUTがローレベルになる。このとき、電界効果トランジスタ440がオン状態になり、電界効果トランジスタ431がオフ状態であるため、電界効果トランジスタ434はオフ状態である。また、リセット信号RIN\_Dに従って電界効果トランジスタ462がオン状態になり、電界効果トランジスタ464がオン状態になり、信号RCOUTの電位が電位VHとなり、信号RCOUTがハイレベルになる。このとき、第2のラッチ部のデータD24として電位VSSが書き込まれ、電界効果トランジスタ465はオフ状態である。10

#### 【0220】

また、図15に示す駆動信号出力回路では、初期化信号INI\_RESET1のパルスが入力されることにより、信号SCOUTがローレベルになり、信号RCOUTがハイレベルになる。また、初期化信号INI\_RESET2のパルスが入力されることにより、信号SCOUTがハイレベルになり、信号RCOUTがローレベルになる。20

#### 【0221】

また、図13に示す複数の駆動信号出力回路のそれぞれにおいて、セット信号SIN\_D、リセット信号RIN\_D、制御信号CTL1\_D、制御信号CTL2\_Dとして入力される信号は図7(B)に示す複数の駆動信号出力回路のそれと同一である。

#### 【0222】

さらに、図13に示す駆動信号出力回路233\_1の制御信号CTL3\_Dとしてクロック信号FCLK1が入力される。

#### 【0223】

また、駆動信号出力回路233\_2の制御信号CTL3\_Dとしてクロック信号GCLK1が入力される。30

#### 【0224】

また、駆動信号出力回路233\_Lの制御信号CTL3\_Dとして駆動信号出力回路233\_L-2の信号SCOUTが入力される。

#### 【0225】

また、駆動信号出力回路233\_1の制御信号CTL4\_Dとしてクロック信号FCLK2が入力される。

#### 【0226】

また、駆動信号出力回路233\_2の制御信号CTL4\_Dとしてクロック信号GCLK2が入力される。40

#### 【0227】

また、駆動信号出力回路233\_Lの制御信号CTL4\_Dとして駆動信号出力回路233\_L-2の信号RCOUTが入力される。

#### 【0228】

以上が図13に示す信号線駆動回路の説明である。

#### 【0229】

次に、本実施形態における信号線駆動回路の駆動方法例として、図7(B)に示す信号線駆動回路の駆動方法例について、図16のタイミングチャートを用いて説明する。なお、一例として、クロック信号CLK1乃至クロック信号CLK4のそれぞれを、デューティ比が25%であり、順に1/4周期ずつずれているクロック信号とする。また、クロック50

信号 F C L K 1、クロック信号 F C L K 2、クロック信号 G C L K 1、及びクロック信号 G C L K 2 のそれぞれをデューティ比が 50 % であるクロック信号とし、クロック信号 F C L K 1 は、クロック信号 G C L K 1 の反転信号とし、クロック信号 F C L K 2 はクロック信号 F C L K 1 の反転信号とし、クロック信号 G C L K 2 はクロック信号 G C L K 1 の反転信号とする。

#### 【 0 2 3 0 】

図 16 に示すように、図 7 (B) に示す信号線駆動回路の駆動方法例では、期間 T 2 1 にスタートパルス信号 S P のパルスをシフトレジスタ 2 3 0 及び選択回路 2 3 2 \_ 1 に入力する。

#### 【 0 2 3 1 】

このとき、クロック信号 C L K 1 乃至クロック信号 C L K 4 に従って、期間 T 2 2 にパルス信号 S R O U T \_ 1 のパルスが選択回路 2 3 2 \_ 2 に入力され、期間 T 2 3 にパルス信号 S R O U T \_ 2 のパルスが選択回路 2 3 2 \_ 3 に入力され、期間 T 2 4 にパルス信号 S R O U T \_ 3 のパルスが選択回路 2 3 2 \_ 4 に入力され、期間 T 2 5 にパルス信号 S R O U T \_ 4 のパルスが選択回路 2 3 2 \_ 5 に入力される。なお、期間 T 2 1 乃至期間 T 2 9 において、クロック信号 F C L K 1 がローレベルになり、クロック信号 F C L K 2 がハイレベルになり、クロック信号 G C L K 1 がハイレベルになり、クロック信号 G C L K 2 がローレベルになる。

#### 【 0 2 3 2 】

このとき、選択回路 2 3 2 \_ Q は、入力されるパルス信号 S R O U T のパルスをパルス信号 S E L O U T 2 のパルスとみなして出力する。

#### 【 0 2 3 3 】

また、選択回路 2 3 2 \_ R は、入力されるパルス信号 S R O U T のパルスをパルス信号 S E L O U T 1 のパルスとみなして出力する。

#### 【 0 2 3 4 】

パルス信号 S E L O U T 1 のパルスは、セット信号 S I N \_ D のパルスとして駆動信号出力回路 2 3 3 \_ R に入力される。セット信号 S I N \_ D のパルスが入力された駆動信号出力回路 2 3 3 \_ R では、データ D 1 として電位 V D D が書き込まれ、データ D 2 として電位 V S S が書き込まれる。よって、信号 D O U T 1 の電位は電位 T C O M H となり、信号 D O U T 2 の電位は電位 V H となる。例えば、駆動信号出力回路 2 3 3 \_ 2 の信号 D O U T 1 (共通信号 C S \_ 2 ) は、期間 T 2 2 に電位 T C O M H となり、駆動信号出力回路 2 3 3 \_ 4 の信号 D O U T 1 (共通信号 C S \_ 4 ) は、期間 T 2 4 に電位 T C O M H となる。

#### 【 0 2 3 5 】

また、パルス信号 S E L O U T 2 のパルスは、リセット信号 R I N \_ D のパルスとして駆動信号出力回路 2 3 3 \_ Q に入力される。リセット信号 R I N \_ D のパルスが入力された駆動信号出力回路 2 3 3 \_ Q では、データ D 1 として電位 V S S が書き込まれ、データ D 2 として電位 V D D が書き込まれる。よって、信号 D O U T 1 の電位は電位 T C O M L となり、信号 D O U T 2 の電位は電位 V L となる。例えば、駆動信号出力回路 2 3 3 \_ 1 の信号 D O U T 1 (共通信号 C S \_ 1 ) は、期間 T 2 1 に電位 T C O M L となり、駆動信号出力回路 2 3 3 \_ 3 の信号 D O U T 1 (共通信号 C S \_ 3 ) は、期間 T 2 3 に電位 T C O M L となる。

#### 【 0 2 3 6 】

さらに、期間 T 2 6 乃至期間 T 2 9 では、クロック信号 C L K 1 乃至クロック信号 C L K 4 、クロック信号 F C L K 1 及びクロック信号 F C L K 2 、並びにクロック信号 G C L K 1 及びクロック信号 G C L K 2 に従って、駆動信号出力回路 2 3 3 \_ R に入力される制御信号 C T L 1 及び制御信号 C T L 2 がハイレベルになる。これにより、駆動信号出力回路 2 3 3 \_ R に、データの再書き込みとして電位 V D D の書き込みが行われる。なお、期間 T 2 6 乃至期間 T 2 9 の動作を繰り返し行ってもよい。これにより、再度スタートパルス信号 S P のパルスをシフトレジスタ 2 3 0 に入力するまでの間、データ D 1 の電位の変動

10

20

30

40

50

を少なくできる。

**【0237】**

さらに、期間T30に再度スタートパルス信号S Pのパルスをシフトレジスタ230及び選択回路232\_1に入力する。

**【0238】**

このとき、クロック信号C L K 1乃至クロック信号C L K 4に従って、期間T31にパルス信号S R O U T \_ 1のパルスが選択回路232\_2に入力され、期間T32にパルス信号S R O U T \_ 2のパルスが選択回路232\_3に入力され、期間T33にパルス信号S R O U T \_ 3のパルスが選択回路232\_4に入力される。なお、期間T30乃至期間T34において、クロック信号F C L K 1がハイレベルになり、クロック信号F C L K 2がローレベルになり、クロック信号G C L K 1がローレベルになり、クロック信号G C L K 2がハイレベルになる。10

**【0239】**

このとき、選択回路232\_Qは、入力されるパルス信号S R O U T のパルスをパルス信号S E L O U T 1のパルスとみなして出力する。

**【0240】**

また、選択回路232\_Rは、入力されるパルス信号S R O U T のパルスをパルス信号S E L O U T 2のパルスとみなして出力する。

**【0241】**

さらに、セット信号S I N \_ Dのパルスが入力された駆動信号出回路233\_Qでは、データD1として電位V D Dが書き込まれ、データD2として電位V S Sが書き込まれる。よって、信号D O U T 1の電位は電位T C O M Hとなり、信号D O U T 2の電位は電位V Hとなる。20

**【0242】**

また、リセット信号R I N \_ Dのパルスが入力された駆動信号出回路233\_Rでは、データD1として電位V S Sが書き込まれ、データD2として電位V D Dが書き込まれる。よって、信号D O U T 1の電位は電位T C O M Lとなり、信号D O U T 2の電位は電位V Lとなる。

**【0243】**

以上が図7(A)に示す信号線駆動回路の駆動方法例である。

30

**【0244】**

なお、本実施形態の信号線駆動回路の駆動方法例では、例えば、図17に示すように、クロック信号F C L K 1とクロック信号G C L K 1を同じ信号にし、クロック信号F C L K 2とクロック信号G C L K 2を同じ信号にする駆動方法を用いてもよい。このとき、駆動信号出回路\_Kの信号D O U T 1は、駆動信号出回路\_K - 1の信号D O U T 1がシフトした信号となり、駆動信号出回路\_Kの信号D O U T 2は、駆動信号出回路\_K - 1の信号D O U T 2がシフトした信号となる。

**【0245】**

さらに、図7(A)の液晶表示装置が有する画素回路210の動作例について図18のタイミングチャートを用いて説明する。

40

**【0246】**

図18に示すように、あるフレーム期間F 1において、M行N列目の画素回路210にデータを書き込む場合、画素回路210では、共通信号線C L \_ Mを介して入力される共通信号C S \_ Mにより、液晶素子212が有する一対の電極の他方の電位(V L C 2ともいう)が電位T C O M Lとなる。なお、液晶素子212が有する一対の電極の他方の電位の切り換えは、ゲート信号G S \_ Mのパルスの入力が終わるまでに行えばよく、例えばゲート信号G S \_ Mのパルスが入力されている間に液晶素子212が有する一対の電極の他方の電位を切り換えるよい。

**【0247】**

さらに、ゲート信号線G L \_ Mを介してゲート信号G S \_ Mのパルスが入力され、画素回

50

路 210 では、電界効果トランジスタ 211 がオン状態になる。

**【 0248】**

このとき、画素回路 210 では、液晶素子 212 が有する一対の電極の一方の電位（電位 VLC1 ともいう）がデータ信号線 DL\_N を介して入力されるデータ信号 DS の電位と同等の値になる。ここでは、電位 VLC1 が電位 +V DATA となる。よって、液晶素子 212 の一対の電極の間に印加される電圧は、+V DATA - TCOML となる。これにより、画素回路 210 にデータが書き込まれる。

**【 0249】**

その後、ゲート信号 GS\_M のパルスの入力が終わり、電界効果トランジスタ 211 がオフ状態になり、画素回路 210 では、液晶素子 212 が有する一対の電極の一方に蓄積された電荷が保持される。データが書き込まれた画素回路 210 では、液晶素子 212 において、一対の電極の間に印加される電圧に応じて液晶層に含まれる液晶の配向が制御される。これにより、上記画素回路 210 は、表示状態になる。10

**【 0250】**

さらに、共通信号線 CL\_M を介して入力される共通信号 CS\_M により、画素回路 210 では、液晶素子 212 が有する一対の電極の他方の電位（VLC2 ともいう）が電位 TCOMH になる。

**【 0251】**

さらに、次のフレーム期間 F2 において、同じ M 行 N 列目の画素回路 210 に反転データを書き込む場合、ゲート信号線 GL\_M を介してゲート信号 GS\_M のパルスが入力され、画素回路 210 では、電界効果トランジスタ 211 がオン状態になる。20

**【 0252】**

このとき、画素回路 210 では、液晶素子 212 の電位 VLC1 がデータ信号線 DL\_N を介して入力されるデータ信号 DS の電位と同等の値になる。ここでは、電位 VLC1 が電位 -V DATA となる。よって、液晶素子 212 の一対の電極の間に印加される電圧は、TCOMH - V DATA となる。

**【 0253】**

その後、ゲート信号 GS のパルスの入力が終わり、電界効果トランジスタ 211 がオフ状態になり、画素回路 210 では、液晶素子 212 が有する一対の電極の一方に蓄積された電荷が保持される。データが書き込まれた画素回路 210 では、液晶素子 212 において、一対の電極の間に印加される電圧に応じて液晶層に含まれる液晶の配向が制御される。これにより、上記画素回路 210 は、表示状態になる。30

**【 0254】**

図 18 に示すように、本実施形態の液晶表示装置では、フレーム期間毎にデータ信号及び共通信号の極性を反転させることにより、データ信号の振幅を小さくできるため、ゲート信号の振幅を小さくできる。よって、駆動電圧を低くできるため、消費電力を低減できる。

**【 0255】**

なお、画素回路 210 にデータを書き込む必要が無い場合には、信号線駆動回路 201 乃至信号線駆動回路 203 への電源供給を停止してもよい。これにより、液晶表示装置の消費電力を低減できる。また、画素回路 210 の電界効果トランジスタ 211 としてオフ電流の低い電界効果トランジスタを用いることにより、信号線駆動回路 201 乃至信号線駆動回路 203 への電源供給を停止している間も同じ画像を表示できる。40

**【 0256】**

以上が本実施形態の液晶表示装置の説明である。

**【 0257】**

図 7 乃至図 18 を用いて説明したように、本実施形態の液晶表示装置の一例では、信号線駆動回路を用いて共通信号線の電位を制御することにより、各行の画素回路毎に液晶素子が有する一対の電極の一方の電位と、他方の電位の極性をフレーム期間毎に反転させる駆動方法を用いることができる。50

**【 0 2 5 8 】**

また、本実施形態の液晶表示装置の一例では、上記実施形態1に示す信号線駆動回路を用いて共通信号線の電位を制御する信号線駆動回路を構成する。これにより、シフトレジスタにスタートパルス信号のパルスが入力されない期間であってもラッチ部の第1のデータの再書き込みを行うことができる。よって、例えば駆動信号出力回路を構成する電界効果トランジスタのリーケ電流による、第1のデータとなる電位の変動を抑制できるため、液晶表示装置の動作不良を抑制できる。

**【 0 2 5 9 】**

(実施形態3)

本実施形態では、実施形態2に示す液晶表示装置の構造例について図19を用いて説明する。

10

**【 0 2 6 0 】**

本実施形態における液晶表示装置の例は、横電界方式の液晶表示装置であり、図19に示すように、導電層701a乃至導電層701cと、絶縁層702と、半導体層703a及び半導体層703bと、導電層704a乃至導電層704dと、絶縁層705と、着色層706と、絶縁層707と、構造体708a乃至構造体708dと、導電層709と、導電層710と、絶縁層722と、絶縁層723と、液晶層750と、を含む。

**【 0 2 6 1 】**

導電層701a乃至導電層701cは、基板700の一平面に設けられる。

20

**【 0 2 6 2 】**

導電層701aは、信号線駆動回路部800に設けられる。導電層701aは、信号線駆動回路の電界効果トランジスタが有するゲートとしての機能を有する。

**【 0 2 6 3 】**

導電層701bは、画素回路部801に設けられる。導電層701bは、画素回路の電界効果トランジスタが有するゲートとしての機能を有する。

**【 0 2 6 4 】**

導電層701cは、画素回路部801に設けられる。導電層701cは、画素回路の容量素子が有する一対の電極の他方としての機能を有する。

**【 0 2 6 5 】**

絶縁層702は、導電層701a乃至導電層701cの上に設けられる。絶縁層702は、信号線駆動回路の電界効果トランジスタに含まれるゲート絶縁層、画素回路の電界効果トランジスタに含まれるゲート絶縁層、及び画素回路の容量素子に含まれる誘電体層としての機能を有する。

30

**【 0 2 6 6 】**

半導体層703aは、絶縁層702を挟んで導電層701aに重畳する。半導体層703aは、信号線駆動回路の電界効果トランジスタに含まれるチャネルが形成される層(チャネル形成層ともいう)としての機能を有する。

**【 0 2 6 7 】**

半導体層703bは、絶縁層702を挟んで導電層701bに重畳する。半導体層703bは、画素回路の電界効果トランジスタに含まれるチャネル形成層としての機能を有する。

40

**【 0 2 6 8 】**

導電層704aは、半導体層703aに電気的に接続される。導電層704aは、信号線駆動回路の電界効果トランジスタが有するソース及びドレインの一方としての機能を有する。

**【 0 2 6 9 】**

導電層704bは、半導体層703aに電気的に接続される。導電層704bは、信号線駆動回路の電界効果トランジスタが有するソース及びドレインの他方としての機能を有する。

**【 0 2 7 0 】**

50

導電層 704c は、半導体層 703b に電気的に接続される。導電層 704c は、画素回路の電界効果トランジスタが有するソース及びドレインの一方としての機能を有する。

【0271】

導電層 704d は、半導体層 703b に電気的に接続される。また、導電層 704d は、絶縁層 702 を挟んで導電層 701c に重畳する。導電層 704d は、画素回路の電界効果トランジスタが有するソース及びドレインの他方、並びに画素回路の容量素子が有する一対の電極の一方としての機能を有する。

【0272】

絶縁層 705 は、半導体層 703a 及び半導体層 703b の上、及び導電層 704a 乃至導電層 704d の上に設けられる。絶縁層 705 は、電界効果トランジスタを保護する絶縁層（保護絶縁層ともいう）としての機能を有する。10

【0273】

着色層 706 は、絶縁層 705 の上に設けられる。着色層 706 は、カラーフィルタとしての機能を有する。

【0274】

絶縁層 707 は、着色層 706 を挟んで絶縁層 705 の上に設けられる。絶縁層 707 は、平坦化層としての機能を有する。

【0275】

構造体 708a 乃至構造体 708d は、絶縁層 707 の上に設けられる。構造体 708a 乃至構造体 708d を設けることにより、液晶素子に含まれる液晶の配向を効率よく制御できる。20

【0276】

導電層 709 は、絶縁層 707 の上に設けられ、絶縁層 705 及び絶縁層 707 を貫通して設けられた開口部で導電層 704d に電気的に接続される。また、導電層 709 は、櫛歯部を有する。また、導電層 709 が有する櫛歯部の櫛は、構造体 708b 又は構造体 708d を挟んで絶縁層 707 の上に設けられる。導電層 709 は、画素回路の液晶素子が有する一対の電極の一方としての機能を有する。

【0277】

導電層 710 は、絶縁層 707 の上に設けられる。また、導電層 710 は、櫛歯部を有し、櫛歯部の櫛が導電層 709 の櫛歯部の櫛と交互に並置される。また、導電層 710 が有する櫛歯部の櫛は、構造体 708a 又は構造体 708c を挟んで絶縁層 707 の上に設けられる。導電層 710 は、画素回路の液晶素子が有する一対の電極の他方としての機能を有する。30

【0278】

また、導電層 709 及び導電層 710 は、絶縁層 707 を挟んで着色層 706 に重畳する。

【0279】

絶縁層 722 は、基板 720 の一平面に設けられる。絶縁層 722 は、平坦化層としての機能を有する。

【0280】

絶縁層 723 は、絶縁層 722 の一平面に設けられる。絶縁層 723 は、保護絶縁層としての機能を有する。40

【0281】

液晶層 750 は、導電層 709 及び導電層 710 の上に設けられる。

【0282】

なお、図 19 では、電界効果トランジスタをチャネルエッチ型の電界効果トランジスタとしているが、これに限定されず、例えばチャネルトップ型の電界効果トランジスタとしてもよい。また、トップゲート型の電界効果トランジスタとしてもよい。

【0283】

さらに、図 19 に示す液晶表示装置の各構成要素について説明する。50

## 【0284】

基板700及び基板720としては、例えばガラス基板又はプラスチック基板を用いることができる。

## 【0285】

導電層701a乃至導電層701cとしては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、又はスカンジウムなどの金属材料を含む層を用いることができる。また、導電層701a乃至導電層701cに適用可能な材料の層の積層により、導電層701a乃至導電層701cを構成することもできる。

## 【0286】

絶縁層702としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を用いることができる。また、絶縁層702に適用可能な層の積層により、絶縁層702を構成することもできる。

## 【0287】

半導体層703a及び半導体層703bとしては、例えば酸化物半導体層又は第14族の半導体（例えばシリコンなど）を含む半導体層などを用いることができる。

## 【0288】

例えば、酸化物半導体を含む半導体層は、例えば単結晶、多結晶（ポリクリスタルともいう）又は非晶質である。

## 【0289】

半導体層703a及び半導体層703bに適用可能な酸化物半導体としては、例えばインジウム及びガリウムの一方若しくは両方と、亜鉛と、を含む金属酸化物、又は該金属酸化物に含まれるガリウムの一部若しくは全部の代わりに他の金属元素を含む金属酸化物などが挙げられる。

## 【0290】

上記金属酸化物としては、例えばIn系金属酸化物、Zn系金属酸化物、In-Zn系金属酸化物、又はIn-Ga-Zn系金属酸化物などを用いることができる。また、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部若しくは全部の代わりに他の金属元素を含む金属酸化物を用いてよい。

## 【0291】

上記他の金属元素としては、例えばガリウムよりも多く酸素原子と結合が可能な金属元素を用いることができ、例えばチタン、ジルコニウム、ハフニウム、ゲルマニウム、及び錫の一つ又は複数などを用いることができる。また、上記他の金属元素としては、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムの一つ又は複数などを用いることもできる。上記他の金属元素は、スタビライザーとしての機能を有する。なお、上記他の金属元素の添加量は、該金属酸化物が半導体として機能することが可能な量である。ガリウムよりも多く酸素原子と結合が可能な金属元素を用い、さらに、金属酸化物中に酸素を供給することにより、金属酸化物中の酸素欠陥を少なくできる。

## 【0292】

例えば、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の全部の代わりに錫を用いるとIn-Sn-Zn系金属酸化物となり、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部の代わりにチタンを用いるとIn-Ti-Ga-Zn系金属酸化物となる。

## 【0293】

また、上記酸化物半導体層を、CAAC-O<sub>S</sub> (C Axis Aligned Crys taline Oxide Semiconductor)を含む酸化物半導体層としてもよい。

10

20

30

40

50

## 【0294】

C A A C - O S とは、完全な単結晶ではなく、完全な非晶質でもない、非晶質相に結晶部を有する結晶・非晶質混相構造の酸化物半導体のことをいう。さらに、C A A C - O S に含まれる結晶部は、c 軸が C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれる。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれる。

## 【0295】

10

上記 C A A C - O S を含む酸化物半導体の層をチャネル形成層として用いた電界効果トランジスタは、可視光や紫外光の照射による電気特性の変動が低いため、信頼性が高い。

## 【0296】

また、半導体層 703a 及び半導体層 703b として酸化物半導体層を用いる場合、例えば脱水化・脱水素化を行い、酸化物半導体層中の水素、水、水酸基、又は水素化物（水素化合物ともいう）などの不純物を排除し、且つ酸化物半導体層に酸素を供給することにより、酸化物半導体層を高純度化させることができる。例えば、酸化物半導体層に接する層として酸素を含む層を用い、また、加熱処理を行うことにより、酸化物半導体層を高純度化させることができる。

## 【0297】

20

例えば、350°以上基板の歪み点未満の温度、好ましくは、350°以上450°以下で加熱処理を行う。さらに、その後の工程において加熱処理を行ってもよい。このとき、上記加熱処理を行う加熱処理装置としては、例えば電気炉、又は抵抗発熱体などの発熱体からの熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えば G R T A ( Gas Rapid Thermal Annealing ) 装置又は L R T A ( Lamp Rapid Thermal Annealing ) 装置などの R T A ( Rapid Thermal Annealing ) 装置を用いることができる。

## 【0298】

30

また、上記加熱処理を行った後、その加熱温度を維持しながら又はその加熱温度から降温する過程で該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度の N<sub>2</sub>O ガス、又は超乾燥エア（露点が -40°以下、好ましくは -60°以下の雰囲気）を導入してもよい。このとき、酸素ガス又は N<sub>2</sub>O ガスは、水、水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又は N<sub>2</sub>O ガスの純度を、6N 以上、好ましくは 7N 以上、すなわち、酸素ガス又は N<sub>2</sub>O ガス中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下とすることが好ましい。酸素ガス又は N<sub>2</sub>O ガスの作用により、酸化物半導体層に酸素が供給され、酸化物半導体層中の酸素欠乏に起因する欠陥を低減できる。なお、上記高純度の酸素ガス、高純度の N<sub>2</sub>O ガス、又は超乾燥エアの導入は、上記加熱処理時に行ってもよい。

## 【0299】

40

高純度化させた酸化物半導体層を電界効果トランジスタに用いることにより、酸化物半導体層のキャリア密度を  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満にできる。また、チャネル幅 1 μmあたりの電界効果トランジスタのオフ電流を、10 aA ( $1 \times 10^{-17} \text{ A}$ ) 以下、さらには 1 aA ( $1 \times 10^{-18} \text{ A}$ ) 以下、さらには 10 zA ( $1 \times 10^{-20} \text{ A}$ ) 以下、さらには 1 zA ( $1 \times 10^{-21} \text{ A}$ ) 以下、さらには 100 yA ( $1 \times 10^{-22} \text{ A}$ ) 以下にできる。電界効果トランジスタのオフ電流は、低ければ低いほどよいが、本実施形態における電界効果トランジスタのオフ電流の下限値は、約  $10^{-30} \text{ A} / \mu\text{m}$  であると見積もられる。

## 【0300】

導電層 704a 乃至導電層 704d としては、例えばモリブデン、チタン、クロム、タン

50

タル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム、又はルテニウムなどの金属材料を含む層を用いることができる。また、導電層704a乃至導電層704dに適用可能な材料の層の積層により、導電層704a乃至導電層704dを構成することもできる。

【0301】

絶縁層705としては、例えば酸化シリコン、酸化アルミニウム、酸化ハフニウムなどの酸化絶縁層を用いることができる。

【0302】

着色層706としては、例えば染料又は顔料を含み、赤色を呈する波長の光、緑色を呈する波長の光、又は青色を呈する波長の光を透過する層を用いることができる。また、着色層706として、染料又は顔料を含み、シアン、マゼンタ、又はイエローの色を呈する波長領域の光を透過する層を用いてもよい。10

【0303】

絶縁層707及び絶縁層722としては、例えば有機絶縁材料又は無機絶縁材料の層などを用いることができる。

【0304】

構造体708a乃至構造体708dは、例えば有機絶縁材料又は無機絶縁材料などを用いて構成される。

【0305】

導電層709としては、例えば光を透過する金属酸化物の層などを用いることができる。20

例えば、インジウムを含む金属酸化物などを用いることができる。また、導電層709に適用可能な材料の層の積層により、導電層709を構成することもできる。

【0306】

導電層710としては、例えば光を透過する金属酸化物の層などを用いることができる。

例えば、インジウムを含む金属酸化物などを用いることができる。また、導電層710に適用可能な材料の層の積層により、導電層710を構成することもできる。

【0307】

絶縁層723としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を用いることができる。30

【0308】

また、液晶層750としては、例えばブルー相を示す液晶を含む層を用いることができる。

。

【0309】

ブルー相を示す液晶を含む層は、例えばブルー相を示す液晶、カイラル剤、液晶性モノマー、非液晶性モノマー、及び重合開始剤を含む液晶組成物により構成される。ブルー相を示す液晶は、応答時間が短く、光学的等方性であるため、配向処理が不要であり、視野角依存性が小さい。よって、ブルー相を示す液晶を用いることにより、液晶表示装置の動作速度を高くできる。

【0310】

上記液晶組成物としては、例えば表1に示す組成物を用いることができる。なお、混合比として、各液晶材料の混合比、液晶とカイラル剤との混合比、液晶及びカイラル剤と液晶性モノマーと非液晶性モノマーとの混合比、又は液晶、カイラル剤、液晶性モノマー、及び非液晶性モノマーと重合開始剤との混合比を示す。

【0311】

10

20

30

40

【表1】

| 種別       | 材料                        | 混合比 (wt%) |      |    |      |    |

|----------|---------------------------|-----------|------|----|------|----|

| 液晶       | MDA-00-3506<br>(メルク株式会社製) | 30        | 90.5 | 92 | 99.8 | 10 |

|          | NEDO LC-C                 | 20        |      |    |      |    |

|          | CPP-3FF                   | 20        |      |    |      |    |

|          | PEP-5CNF                  | 15        |      |    |      |    |

|          | PEP-5FCNF                 | 15        |      |    |      |    |

| カイラル剤    | ISO-(6OBA) <sub>2</sub>   |           | 9.5  |    |      |    |

| 液晶性モノマー  | RM257-O6                  |           |      | 4  |      |    |

| 非液晶性モノマー | DMeAc                     |           |      | 4  |      |    |

| 重合開始剤    | DMPAP                     |           |      |    | 0.2  |    |

## 【0312】

なお、 CPP - 3 FF は、 4 - ( trans - 4 - n - プロピルシクロヘキシル ) - 3 ' , 4 ' - ジフルオロ - 1 , 1 ' - ビフェニルの略称である。また、 PEP - 5 CNF は、 4 - n - ペンチル安息香酸 4 - シアノ - 3 - フルオロフェニルの略称である。また、 PEP - 5 FCNF は、 4 - n - ペンチル安息香酸 4 - シアノ - 3 , 5 - ジフルオロフェニルの略称である。また、 ISO - ( 6 OBA )<sub>2</sub> は、 1 , 4 : 3 , 6 - ジアンヒドロ - 2 , 5 - ビス [ 4 - ( n - ヘキシル - 1 - オキシ ) 安息香酸 ] ソルビトールの略称である。また、 RM257 - O6 は、 1 , 4 - ビス - [ 4 - ( 6 - アクリロイルオキシ - n - ヘキシル - 1 - オキシ ) ベンゾイルオキシ ] - 2 - メチルベンゼンの略称である。また、 DMeAc は、 メタクリル酸 n - ドデシルの略称である。また、 DMPAP は、 2 , 2 - ジメトキシ - 2 - フェニルアセトフェノンの略称である。

20

## 【0313】

また、液晶組成物としては、例えば表2に示す組成物を用いることもできる。

## 【0314】

30

【表2】

| 種別       | 材料                        | 混合比 (wt%) |      |    |      |

|----------|---------------------------|-----------|------|----|------|

| 液晶       | MDA-00-3506<br>(メルク株式会社製) | 50        | 92.5 | 92 | 99.7 |

|          | CPEP-3FCNF                | 20        |      |    |      |

|          | PEP-3FCNF                 | 30        |      |    |      |

| カイラル剤    | R-DOL-Pn                  |           | 7.5  |    |      |

| 液晶性モノマー  | RM257-O6                  |           |      | 4  |      |

| 非液晶性モノマー | DMeAc                     |           |      | 4  |      |

| 重合開始剤    | DMPAP                     |           |      |    | 0.3  |

## 【0315】

なお、CPEP-5FCNFは、4-(trans-4-n-ペンチルシクロヘキシリ)安息香酸4-シアノ-3,5-ジフルオロフェニルの略称である。また、PEP-3FCNFは、4-n-プロピル安息香酸4-シアノ-3,5-ジフルオロフェニルの略称である。また、R-DOL-Pnは、(4R,5R)-2,2'-ジメチル-(- - - - -テトラ(9-フェナントリル))-1,3,-ジオキソラン-4,5-ジメタノールの略称である。

## 【0316】

また、上記液晶組成物としては、例えば表3に示す組成物を用いることもできる。

## 【0317】

【表3】

| 種別       | 材料                        | 混合比 (wt%) |      |    |      |

|----------|---------------------------|-----------|------|----|------|

| 液晶       | MDA-00-3506<br>(メルク株式会社製) | 50        | 92.5 | 92 | 99.7 |

|          | PPEP-5FCNF                | 20        |      |    |      |

|          | PEP-3FCNF                 | 30        |      |    |      |

| カイラル剤    | R-DOL-Pn                  |           | 7.5  |    |      |

| 液晶性モノマー  | RM257-O6                  |           |      | 4  |      |

| 非液晶性モノマー | Dac                       |           |      | 4  |      |

| 重合開始剤    | DMPAP                     |           |      |    | 0.3  |

## 【0318】

なお、PPEP-5FCNFは、4-(4-n-ペンチルフェニル)安息香酸4-シアノ

10

20

30

40

50

- 3 , 5 -ジフルオロフェニルの略称である。

**【0319】**

以上が図19に示す液晶表示装置の構造例の説明である。

**【0320】**

図19を用いて説明したように、本実施形態の液晶表示装置の一例では、画素回路と同一基板上に信号線駆動回路を設ける。これにより、画素回路と信号線駆動回路を接続するための配線の数を少なくできる。

**【0321】**

また、本実施形態の液晶表示装置の一例では、ブルー相を示す液晶を用いて液晶素子を構成する。これにより液晶表示装置の動作速度を高くできる。

10

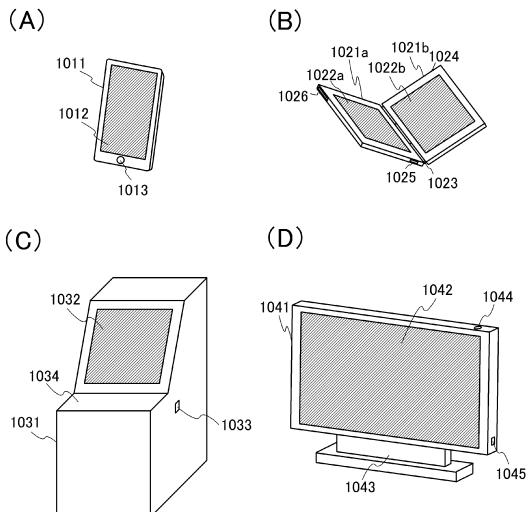

**【0322】**

(実施形態4)

本実施形態では、実施形態2及び実施形態3に示す液晶表示装置を用いたパネルを具備する電子機器の例について、図20を用いて説明する。

**【0323】**

本実施形態における電子機器の構成例を示す模式図を図20に示す。

**【0324】**

図20(A)に示す電子機器は、携帯型情報端末の例である。

**【0325】**

図20(A)に示す情報端末は、筐体1011と、筐体1011に設けられたパネル1012と、ボタン1013とを具備する。

20

**【0326】**

なお、筐体1011に外部機器に図20(A)に示す電子機器を接続するための接続端子、図20(A)に示す電子機器を操作するためのボタンのうち、一つ又は複数を設けてよい。

**【0327】**

パネル1012は、表示パネルとしての機能を有する。

**【0328】**

パネル1012としては、上記実施形態2及び実施形態3の液晶表示装置を用いることができる。

30

**【0329】**

また、パネル1012がタッチパネルとしての機能を有してもよい。このとき、例えばパネル1012にキーボードの画像を表示させ、キーボードの画像を指で触れることにより入力動作を行ってもよい。

**【0330】**

ボタン1013は、筐体1011に設けられる。例えば、電源ボタンであるボタン1013を設けることにより、ボタン1013を押すことで電子機器をオン状態にするか否かを制御できる。

**【0331】**

図20(A)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊戯機の一つ又は複数としての機能を有する。

40

**【0332】**

図20(B)に示す電子機器は、折り畳み式の情報端末の例である。

**【0333】**

図20(B)に示す電子機器は、筐体1021aと、筐体1021bと、筐体1021aに設けられたパネル1022aと、筐体1021bに設けられたパネル1022bと、軸部1023と、ボタン1024と、接続端子1025と、記録媒体挿入部1026と、を備える。

**【0334】**

筐体1021aと筐体1021bは、軸部1023により接続される。

50

**【0335】**

パネル1022a及びパネル1022bは、表示パネルとしての機能を有する。例えば、パネル1022a及びパネル1022bに、互いに異なる画像又は一続きの画像を表示させてもよい。また、図20(B)に示す電子機器を、パネル1022a及びパネル1022bが上下方向又は左右方向に並ぶ向きで操作してもよい。

**【0336】**

パネル1022a及びパネル1022bとしては、上記実施形態2及び実施形態3の液晶表示装置を用いることができる。

**【0337】**

また、パネル1022a及びパネル1022bの一方又は両方がタッチパネルとしての機能を有してもよい。このとき、例えばパネル1022a及びパネル1022bの一方又は両方にキーボードの画像を表示させ、キーボードの画像を指で触れることにより入力動作を行ってもよい。10

**【0338】**

図20(B)に示す電子機器では、軸部1023があるため、例えば筐体1021a又は筐体1021bを動かして筐体1021aを筐体1021bに重畠させ、電子機器を折り置むことができる。

**【0339】**

ボタン1024は、筐体1021bに設けられる。なお、筐体1021aにボタン1024を設けてもよい。例えば、電源ボタンとしての機能を有するボタン1024を設けることにより、ボタン1024を押すことで電子機器内の回路に電力を供給するか否かを制御できる。20

**【0340】**

接続端子1025は、筐体1021aに設けられる。なお、筐体1021bに接続端子1025を設けてもよい。また、複数の接続端子1025を筐体1021a及び筐体1021bの一方又は両方に設けてもよい。接続端子1025は、図20(B)に示す電子機器と他の機器を接続するための端子である。

**【0341】**

記録媒体挿入部1026は、筐体1021aに設けられる。なお、筐体1021bに記録媒体挿入部1026を設けてもよい。また、複数の記録媒体挿入部1026を筐体1021a及び筐体1021bの一方又は両方に設けてもよい。例えば記録媒体挿入部にカード型記録媒体を挿入することにより、カード型記録媒体から電子機器へのデータの読み出し、又は電子機器内データのカード型記録媒体への書き込みを行うことができる。30

**【0342】**

図20(B)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

**【0343】**

図20(C)に示す電子機器は、設置型情報端末の例である。図20(C)に示す設置型情報端末は、筐体1031と、筐体1031に設けられたパネル1032と、ボタン1033と、を具備する。40

**【0344】**

パネル1032は、表示パネル及びタッチパネルとしての機能を有する。

**【0345】**

なお、パネル1032を、筐体1031における甲板部1034に設けることもできる。

**【0346】**

パネル1032としては、上記実施形態2及び実施形態3の液晶表示装置を用いることができる。

**【0347】**

さらに、筐体1031に券などを出力する券出力部、硬貨投入部、及び紙幣挿入部の一つ又は複数を設けてもよい。50

**【0348】**

ボタン1033は、筐体1031に設けられる。例えば、電源ボタンとしての機能を有するボタン1033を設けることにより、ボタン1033を押すことで電子機器内の回路に電力を供給するか否かを制御できる。

**【0349】**

図20(C)に示す電子機器は、例えば現金自動預け払い機、チケットなどの注文をするための情報通信端末(マルチメディアステーションともいう)、又は遊技機としての機能を有する。

**【0350】**

図20(D)は、設置型情報端末の例である。図20(D)に示す電子機器は、筐体1041と、筐体1041に設けられたパネル1042と、筐体1041を支持する支持台1043と、ボタン1044と、接続端子1045と、を備える。

10

**【0351】**

なお、筐体1041に外部機器に接続させるための接続端子、図20(D)に示す電子機器を操作するためのボタンのうち、一つ又は複数を設けてもよい。

**【0352】**

パネル1042は、表示パネルとしての機能を有する。また、パネル1042がタッチパネルとしての機能を有していてもよい。

**【0353】**

パネル1042としては、上記実施形態2及び実施形態3の液晶表示装置を用いることができる。

20

**【0354】**

ボタン1044は、筐体1041に設けられる。例えば、電源ボタンとしての機能を有するボタン1044を設けることにより、ボタン1044を押すことで電子機器内の回路に電力を供給するか否かを制御できる。

**【0355】**

接続端子1045は、筐体1041に設けられる。接続端子1045は、図20(D)に示す電子機器と他の機器を接続するための端子である。例えば、接続端子1045により図20(D)に示す電子機器とパーソナルコンピュータを接続することにより、パーソナルコンピュータから入力されるデータ信号に応じた画像をパネル1042に表示させることができる。例えば、図20(D)に示す電子機器のパネル1042が接続する電子機器のパネルよりも大きければ、他の電子機器の表示画像を拡大でき、複数の人が同時に視認しやすくなる。

30

**【0356】**

図20(D)に示す電子機器は、例えばデジタルフォトフレーム、出力モニタ、パーソナルコンピュータ、又はテレビジョン装置としての機能を有する。

**【0357】**

以上が本実施形態における電子機器の例の説明である。

**【0358】**

図20を用いて説明したように、本実施形態における電子機器の一例では、上記実施形態における液晶表示装置を備えるパネルを設けることにより、パネルの動作速度を高くできるため、例えば動画再生などの動作速度が高い電子機器を提供できる。

40

**【符号の説明】****【0359】**

- 101 シフトレジスタ

- 112 選択回路

- 113 駆動信号出力回路

- 121 ラッピング部

- 122 パッファ部

- 123 パッファ部

|                   |            |    |

|-------------------|------------|----|

| 1 2 4             | スイッチ部      |    |

| 1 3 1 a           | ラッチ部       |    |

| 1 3 1 b           | ラッチ部       |    |

| 1 3 2 a           | バッファ部      |    |

| 1 3 2 b           | バッファ部      |    |

| 1 3 3 a ~ 1 3 3 d | スイッチ部      |    |

| 1 3 4             | バッファ部      |    |

| 2 0 1             | 信号線駆動回路    |    |

| 2 0 2             | 信号線駆動回路    |    |

| 2 0 3             | 信号線駆動回路    | 10 |

| 2 0 4             | 信号線駆動回路    |    |

| 2 1 0             | 画素回路       |    |

| 2 1 1             | 電界効果トランジスタ |    |

| 2 1 2             | 液晶素子       |    |

| 2 1 3             | 容量素子       |    |

| 2 3 0             | シフトレジスタ    |    |

| 2 3 1             | パルス出力回路    |    |

| 2 3 2             | 選択回路       |    |

| 2 3 3             | 駆動信号出力回路   |    |

| 3 1 1 ~ 3 1 9     | 電界効果トランジスタ | 20 |

| 3 2 1             | 容量素子       |    |

| 3 2 2             | 容量素子       |    |

| 3 3 1 ~ 3 3 6     | 電界効果トランジスタ |    |

| 3 5 1 ~ 3 6 4     | 電界効果トランジスタ |    |

| 3 7 1             | 容量素子       |    |

| 3 7 2             | 容量素子       |    |

| 4 3 1 ~ 4 4 4     | 電界効果トランジスタ |    |

| 4 5 1             | 容量素子       |    |

| 4 5 2             | 容量素子       |    |

| 4 6 1 ~ 4 7 4     | 電界効果トランジスタ | 30 |

| 4 8 1             | 容量素子       |    |

| 4 8 2             | 容量素子       |    |

| 4 9 1             | 電界効果トランジスタ |    |

| 4 9 2             | 電界効果トランジスタ |    |

| 7 0 0             | 基板         |    |

| 7 0 1 a           | 導電層        |    |

| 7 0 1 b           | 導電層        |    |

| 7 0 1 c           | 導電層        |    |

| 7 0 2             | 絶縁層        |    |

| 7 0 3 a           | 半導体層       | 40 |

| 7 0 3 b           | 半導体層       |    |

| 7 0 4 a ~ 7 0 4 d | 導電層        |    |

| 7 0 5             | 絶縁層        |    |

| 7 0 6             | 着色層        |    |

| 7 0 7             | 絶縁層        |    |

| 7 0 8 a ~ 7 0 8 d | 構造体        |    |

| 7 0 9             | 導電層        |    |

| 7 1 0             | 導電層        |    |

| 7 2 0             | 基板         |    |

| 7 2 2             | 絶縁層        | 50 |

|           |          |    |

|-----------|----------|----|

| 7 2 3     | 絶縁層      |    |

| 7 5 0     | 液晶層      |    |

| 8 0 0     | 信号線駆動回路部 |    |

| 8 0 1     | 画素回路部    |    |

| 1 0 1 1   | 筐体       |    |

| 1 0 1 2   | パネル      |    |

| 1 0 1 3   | ボタン      |    |

| 1 0 2 1 a | 筐体       |    |

| 1 0 2 1 b | 筐体       |    |

| 1 0 2 2 a | パネル      | 10 |

| 1 0 2 2 b | パネル      |    |

| 1 0 2 3   | 軸部       |    |

| 1 0 2 4   | ボタン      |    |

| 1 0 2 5   | 接続端子     |    |

| 1 0 2 6   | 記録媒体挿入部  |    |

| 1 0 3 1   | 筐体       |    |

| 1 0 3 2   | パネル      |    |

| 1 0 3 3   | ボタン      |    |

| 1 0 3 4   | 甲板部      |    |

| 1 0 4 1   | 筐体       | 20 |

| 1 0 4 2   | パネル      |    |

| 1 0 4 3   | 支持台      |    |

| 1 0 4 4   | ボタン      |    |

| 1 0 4 5   | 接続端子     |    |

【図 1】

【図 2】

【図 3】

【図4】

【図5】

(A)

(B)

【図6】

【図7】

(A)

(B)

【図8】

(B)

【図9】

(B)

【図10】

【 図 1 1 】

(A)

(B)

(A)

(B)

【図 1 2】

(B)

【図13】

【图 1-4】

( 四 15 )

(B)

(A)

(B)

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 4 C |

(56)参考文献 特開2006-276541(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38

G02F 1/133

G02F 1/1368