(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4632279号

(P4632279)

(45) 発行日 平成23年2月16日(2011.2.16)

(24) 登録日 平成22年11月26日(2010.11.26)

(51) Int.Cl.

F 1

|           |           |           |      |

|-----------|-----------|-----------|------|

| GO6F 9/38 | (2006.01) | GO6F 9/38 | 370C |

| GO6F 1/04 | (2006.01) | GO6F 1/04 | 301C |

| GO6F 9/30 | (2006.01) | GO6F 9/30 | 310C |

請求項の数 12 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-618810 (P2000-618810)  |

| (86) (22) 出願日 | 平成12年5月8日 (2000.5.8)          |

| (65) 公表番号     | 特表2002-544618 (P2002-544618A) |

| (43) 公表日      | 平成14年12月24日 (2002.12.24)      |

| (86) 國際出願番号   | PCT/US2000/012467             |

| (87) 國際公開番号   | W02000/070433                 |

| (87) 國際公開日    | 平成12年11月23日 (2000.11.23)      |

| 審査請求日         | 平成19年5月7日 (2007.5.7)          |

| (31) 優先権主張番号  | 09/313,933                    |

| (32) 優先日      | 平成11年5月18日 (1999.5.18)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                       |

|-----------|-----------------------------------------------------------------------|

| (73) 特許権者 | 510000633<br>エスティー・エリクソン、ソシエテ、アノニム                                    |

|           | イスラエル・プラン・レーズアト、シュマン、デュ、シャン・デ・フィーユ、39                                 |

| (74) 代理人  | 100117787<br>弁理士 勝沼 宏仁                                                |

| (72) 発明者  | スウォループ、アダスミリ<br>アメリカ合衆国アリゾナ州、テンプ、ウェスト、ペイスライン、ロード、505アパートメント、ナンバー、2121 |

審査官 三坂 敏夫

最終頁に続く

(54) 【発明の名称】電力消費を低減するシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号を論理的に解析しコプロセッサのクロックをオンまたはオフにする信号を供給するように構成された第1の論理AND構成要素と、

前記第1の論理AND構成要素の入力に結合されたTHUMBビットレジスタと、ここで前記THUMBビットレジスタが、THUMB命令がフェッチされるとオンするTHUMBビット(TBIT)信号の論理値を格納するように構成されており、前記THUMBビット(TBIT)信号は、前記THUMB命令がフェッチされた段階で受信され、

前記第1の論理AND構成要素の入力に結合された実行レジスタとを含んでなり、前記実行レジスタが主ARMプロセッサのバイラインの実行段と関連した命令を格納するように構成されており、

前記THUMB命令がフェッチされ前記THUMBビット(TBIT)信号がオンした場合、前記第1の論理AND構成要素が、前記コプロセッサのクロックをオフにする前記信号を供給するARMコプロセッサ電力低減システム。

## 【請求項 2】

前記コプロセッサのクロックが、前記THUMBビット(TBIT)信号の論理値に基づいてオンまたはオフにされる、請求項1に記載のシステム。

## 【請求項 3】

前記THUMB命令がフェッチされず前記THUMBビット(TBIT)信号がオフである場合、前記第1の論理AND構成要素が、前記コプロセッサのクロックをオンにする

10

20

前記信号を供給する、請求項 1 または 2 に記載の A R M コプロセッサ電力低減システム。

【請求項 4】

前記第 1 の論理 A N D 構成要素は、前記第 1 の論理 A N D 構成要素の入力が論理 1 である場合、論理 1 の値を伝送し、前記第 1 の論理 A N D 構成要素の前記入力のいずれかが論理 0 の値である場合、論理 0 の値を伝送するように構成されている、請求項 1 に記載の A R M コプロセッサ電力低減システム。

【請求項 5】

前記実行レジスタの入力に結合された第 2 の論理 A N D 構成要素と、ここで前記第 2 の論理 A N D 構成要素が前記主 A R M プロセッサのパイプラインを進めるように構成されており、10

前記第 2 の論理 A N D 構成要素の入力に結合された論理 O R 構成要素と、ここで前記論理 O R 構成要素が、前記論理 O R 構成要素の入力が論理 1 である場合、論理 1 の値を伝送し、前記論理 O R 構成要素の前記入力が論理 0 である場合、論理 0 を伝送するように構成されており、10

前記第 2 の論理 A N D 構成要素の入力に結合された待ちレジスタとをさらに含み、この待ちレジスタが、整数の数のメモリクロック入力サイクルの間、A R M コアを機能停止の待ちにるように構成された否定待ち信号の値を取り込むように構成されている、請求項 1 に記載の A R M コプロセッサ電力低減システム。

【請求項 6】

前記論理 O R 構成要素の出力に結合された第 3 の論理 A N D 構成要素と、ここで前記第 3 の論理 A N D 構成要素が、格納されたデータが前記主 A R M プロセッサのパイプラインで転送されるように指示する信号を伝送するように構成されており、20

前記第 3 の論理 A N D 構成要素の出力に結合されたデータ保持レジスタと、ここで前記データ保持レジスタが前記主 A R M プロセッサのパイプラインで処理されるのを待っているデータを格納するように構成され、20

前記第 3 の論理 A N D 構成要素の入力に結合された否定演算コードフェッチレジスタとをさらに含み、前記否定演算コードフェッチレジスタが、A R M コアプロセッサがメモリから命令をフェッチしているかどうかを表示する否定演算コードフェッチ信号の状態を格納するように構成されている、請求項 5 に記載の A R M コプロセッサ電力低減システム。

【請求項 7】

前記第 2 の論理 A N D 構成要素の出力に結合されたデコードレジスタと、ここで前記デコードレジスタが前記主 A R M プロセッサのパイプラインのデコード段と関連した情報を格納するように構成されており、30

前記デコードレジスタの入力に結合されたマルチプレクサとをさらに含み、ここで前記マルチプレクサが前記デコードレジスタに伝送すべき信号を選ぶように構成されている、請求項 5 に記載の A R M コプロセッサ電力低減システム。

【請求項 8】

前記マルチプレクサが、データ保持レジスタからの信号か信号中のデータからの信号かを選ぶ、請求項 7 に記載の A R M コプロセッサ電力低減システム。

【請求項 9】

前記第 1 の論理構成要素が A N D 構成要素であり、ここで前記構成要素が前記入力信号の論理レベルに基づいて前記コプロセッサのクロックをオンまたはオフにし、40

前記実行レジスタの入力に結合された第 2 の論理 A N D 構成要素と、ここで前記第 2 の論理 A N D 構成要素が前記主 A R M プロセッサのパイプラインを進めるように構成され、40

前記第 2 の論理 A N D 構成要素の入力に結合された論理 O R 構成要素とをさらに含み、前記論理 O R 構成要素が、前記論理 O R 構成要素の入力が論理 1 である場合、論理 1 の値を伝送し、前記論理 O R 構成要素の前記入力が論理 0 である場合、論理 0 を伝送するように構成されている、請求項 1 に記載のシステム。

【請求項 10】

前記論理 O R 構成要素が、次のサイクルでメモリアクセスが必要となるかどうかを表示50

するように構成された否定メモリ要求信号と、ARMコアプロセッサ／前記ARMコアプロセッサがメモリから命令をフェッチしているかどうかを表示するように構成された否定演算コードフェッチ信号とに結合されている、請求項5または9に記載のARMコプロセッサ電力低減システム。

#### 【請求項11】

前記論理OR構成要素の出力に結合された第3の論理AND構成要素と、ここで前記第3の論理AND構成要素は、格納されたデータが前記主ARMプロセッサのパイプラインで転送されるように指示する信号を伝送するように構成されており、

前記第3の論理AND構成要素の出力に結合されたデータ保持レジスタと、ここで前記データ保持レジスタは前記主ARMプロセッサのパイプラインで処理されるのを待っているデータを格納するように構成されており、

前記第3の論理AND構成要素の入力に結合された否定演算コードフェッチレジスタと、ここで前記否定演算コードフェッチレジスタは、前記ARMコアプロセッサがメモリから命令をフェッチしているかどうかを表示する否定演算コードフェッチ信号を格納するように構成されており、

前記第2の論理AND構成要素の出力に結合されたデコードレジスタと、ここで前記デコードレジスタは前記主ARMプロセッサのパイプラインの実行段と関連した情報を格納するように構成されており、

前記デコードレジスタの入力に結合されたマルチプレクサとをさらに含み、前記マルチプレクサが、前記デコードレジスタに伝送すべき信号を選ぶように構成されている、請求項10に記載のARMコプロセッサ電力低減システム。

#### 【請求項12】

前記実行レジスタ中の命令と関連したTHUMBビットが論理1であり、かつ前記THUMBビットレジスタの値が論理1である時に、前記第1の論理AND構成要素が前記コプロセッサのクロックをオフにする、請求項11に記載のARMコプロセッサ電力低減システム。

#### 【発明の詳細な説明】

##### 【0001】

本発明はコンピュータ処理システムおよび方法の分野に関する。より詳細には、本発明は高度RISC機械(ARM)をベースにしたシステムで電力消費を改善する、すなわち減少させるシステムおよび方法に関する。これを取り扱う1つの方法は、THUMB状態で動作している時にある機能をオフにすることによる。

##### 【0002】

###### (発明の背景)

コンピュータシステムおよび回路は現代社会の発展に向けて大きく貢献し、いくつかの用途で利用されて有利な結果を達成している。コンピュータシステムは、一般に、1組の命令に従って動作するプロセッサを備えている。デジタルコンピュータ、カルキュレータ、オーディオ装置、ビデオ装置および電話システムのような数多くの電子技術はプロセッサを含み、そのプロセッサは、ビジネス、科学、教育および娯楽の多くの分野でデータ、観念および傾向を分析し通信する際に生産性の向上およびコストの低減を容易にしている。多くの場合に、これらの結果を可能にするように設計されたプロセッサは、命令セットの減少したコンピューターアーキテクチャ(RISC)に従って動作する高度RISC機械(ARM)である。しかし、ARMの機械は、一般に、コプロセッサを利用し、そのコプロセッサは現在ARM動作をサポートしていない時でも大きな電力を消費する。

##### 【0003】

一般に、ARMプロセッサは、非常に強力な命令セットによって比較的高い性能を発揮し、さらに大きな柔軟性を示す。一般的なARMプロセッサは比較的簡単なので、小型でコスト効果のある装置で高い命令スループットおよび効率的な時間割込み応答が容易になる。パイプライン方式が利用されて、処理システムおよびメモリシステムの多数の構成要素が同時に動作することができるようになる。例えば、1つの命令が実行されている間に

10

20

30

40

50

、次の命令がデコードされており、第3の命令がメモリからフェッチされる。

【0004】

通常、ARMプロセッサは2つの状態または命令セットを利用する。一方の状態または命令セットは、32ビットのARMセットを含み、他方の状態または命令セットは16ビットのTHUMBセットを含む。THUMBセットの命令は、ARMセットの命令と同じ32ビットレジスタで動作し、ARMセットの性能の有利さの大部分を維持しながら、ARMセットの密度をほぼ2倍にする。しかし、もっと多くの機能性およびもっと高い性能が要求される場合がある。これらの状況では、通常コプロセッサがシステムに含まれている。

【0005】

ARMコプロセッサは、ARM状態で追加の処理電力を与える。多くの場合に、主ARMプロセッサが他の機能を実行している間に、特定の命令を実行するコプロセッサを持つことが有利である。例えば、コプロセッサは浮動小数点演算、グラフィックス変換、および画像圧縮のような機能を実行することが多い。しかし、コプロセッサを有する一般的なARMシステムでは、たとえコプロセッサが命令または情報を処理するために利用されていなくても、コプロセッサ機能のいくつかは常に維持されている。

【0006】

コプロセッサが主要なシステム動作に寄与していない場合、コプロセッサは、通常、かなりの量のシステム電力を消費する。特に、コプロセッサは16ビットトランザクションを行うために使用されないので、コプロセッサは、16ビットTHUMBトランザクション中は主要なシステム動作に貢献していない。THUMB命令セットはARM命令セットよりも小さく、その上、THUMB状態で動作している間は、ARMシステムのコプロセッサは利用されていない。コプロセッサが命令または情報を処理していない時でも、通常コプロセッサは電力を消費し続ける。例えば、コプロセッサ中のクロックは動作し続け、コプロセッサのレジスタは状態を切り換え続け、それで電力を消費する。

【0007】

ARMシステムの機能性に貢献していない構成要素による電力消費を低減することは、多くの便宜をもたらす。例えば、ARMシステムを利用して処理機能を提供する無線通信システムでは、電力状況はクリティカルになることが多い。無線通信システムは電源としてバッテリーに依拠することが多く、電力消費を低減することでバッテリー寿命が長くなる。また、電力消費を低減することで、バッテリーのサイズを小さくすることができるようになり、それによって、より小型の無線通信装置を製造することができるようになる。小型無線通信装置により、通常実際の応用の有益性はより大きくなる。

【0008】

必要なものは、ARMシステムのコプロセッサによる電力消費を低減するシステムおよび方法である。そのシステムおよび方法はARMシステムの動作機能性を妨害してはならない。THUMB状態で動作中のコプロセッサレジスタの切換わりを少なくしなければならない。また、そのシステムおよび方法は電力供給の要求条件軽減を容易にしなければならない。

【0009】

(発明の概要)

本発明のシステムおよび方法は、ARMシステムのコプロセッサによる電力消費を低減する。本システムおよび方法は、ARMシステムの動作機能性を妨げない。THUMB状態で動作中のコプロセッサレジスタの切換りは本発明によって減少し、また、本発明は電力供給の要求条件軽減を容易にする。

【0010】

本発明の一実施例では、ARMコプロセッサ電力低減システムおよび方法は、ARMシステムがARMコプロセッサを利用しない活動状態にある時を検出し、ARMコプロセッサのクロックをオフにする。本発明のARMコプロセッサ電力低減システムおよび方法は、ARMコアがARM状態で動作しているかまたはTHUMB状態で動作しているかを追跡

10

20

30

40

50

する。例えば、ARMコプロセッサ電力低減システムおよび方法は、ARMコアがARM状態で動作しているかまたはTHUMB状態で動作しているかを表示するTHUMBビット(TBIT)信号を解析する。ARMコアがTHUMB状態で動作している場合、本発明のARMコプロセッサ電力低減システムおよび方法は、コプロセッサのクロックにオフするように命令する。ARMコアがARM状態で動作している場合、本発明のARMコプロセッサ電力低減システムおよび方法は、コプロセッサのクロックにオンするように命令する。

#### 【0011】

##### (発明の詳細な説明)

高度RISC機械(arm)をベースにしたシステムにおける電力消費を低減するシステムおよび方法である、本発明の好ましい実施形態を詳細に参照し、その例を添付の図面で示す。本発明は好ましい実施形態に関連して説明するが、それは本発明をこれらの実施形態に限定する意図でないことは理解されるであろう。それとは逆に、本発明は、添付の特許請求の範囲で定義されるような本発明の精神および範囲内に含まれる可能性のある代替物、修正物および均等物を含む意図である。さらに、本発明の次の詳細な説明で、本発明を完全に理解できるようにするために、数多くの具体的な詳細を示す。しかし、当業者には明らかになるであろうが、本発明はこれらの具体的な詳細なしで実施することができる。他の例では、公知の方法、手順、構成要素、および回路は、本発明の態様を必要に不明瞭にしないために詳細に説明されていない。

#### 【0012】

本発明は、ARMコプロセッサ電力低減システムおよび方法であり、ARMシステムがARMコプロセッサを利用しない活動状態にある時を検出し、ARMコプロセッサのクロックをオフにする。例えば、本発明のARMコプロセッサ電力低減システムおよび方法は、ARMコア周辺からの信号を追跡して、ARMコアがARM状態の動作を容易にしようとしているかまたはTHUMB状態の動作を容易にしようとしているかを決定する。本発明のARMコプロセッサ電力低減システムおよび方法が、ARMコアがTHUMB状態の動作を容易にしようとしていることを検出した場合、ARMコプロセッサ電力低減システムおよび方法は、ARMコプロセッサと関連したクロックにオフするように信号を送る。ARMコプロセッサのクロックがオフになるので、ARMコプロセッサのレジスタは切り換わらないし、電力を消費しない。本発明のARMコプロセッサ電力低減システムおよび方法は、ARMコアがARM状態の動作を容易にしようとしていることを感知した場合、ARMコプロセッサ電力低減システムおよび方法は、ARMコプロセッサと関連したクロックにオンするように信号を送る。

#### 【0013】

ARMコアで命令が処理されるときに、命令はまた、3段を含むARMパイプラインで取り込まれる。ARMパイプラインは、フェッチ段、デコード段および実行段を含む。本発明のARMコプロセッサ電力低減システムは、特定の命令がARMコアのどの段にあるか追跡する(命令がフェッチ段、デコード段、または実行段にあるかどうかを追跡する)。動作状態に変化がある時はいつも(例えば、ARM状態からTHUMB状態に、またはその逆に)、その変化を表示する命令がARMパイプラインを流れる。命令はフェッチされ、デコードされ、それから実行段で、ARMコアは、その命令がARMコアに16ビットTHUMB命令セットに切り換わるように指示しているかまたは32ビットARM命令セットに切り換わるように指示しているかを決定する。状態変化の命令が実行される時に、TBIT(THUMB\_Bit)信号は変化する。例えば、TBITは、命令がTHUMB状態の命令である時には、論理0から論理1に変化し、または、命令がARM状態の命令である時に、論理1から論理0に変化する。

#### 【0014】

状態変化の命令が実行されても、場合によって、パイプラインに保留状態の実行されるべき動作がもう2つある。すなわち、フェッチ段の1つの動作とデコード段の1つの動作である。動作状態がARM状態からTHUMB状態に変化する場合、ARMコプロセッサ

10

20

30

40

50

電力低減システムおよび方法は、デコード段と実行段に残っている2つの動作が完全に実行されるまで、ARMコプロセッサのクロックの電源を遮断しない。このようにして、デコード段と実行段に残っている2つの動作がARM状態の動作を含む場合、コプロセッサは、走っている使用可能なクロックを有し、32ビットのARM状態の動作を処理し続ける。

#### 【0015】

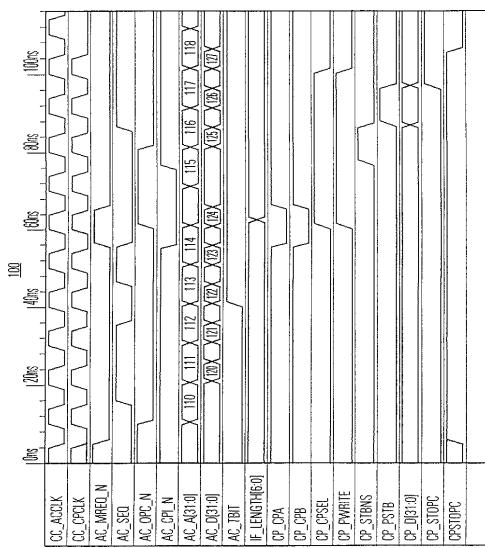

図1は、本発明のARMコプロセッサ電力低減システムおよび方法の一実施形態と関連したコプロセッサクロック停止波形テーブル100の一例である。コプロセッサクロック停止波形テーブル100は、第1のARM命令110、第2のARM命令111、第3のARM命令112、およびそれらの対応する第1のARMデータ転送120、第2のARMデータ転送121、および第3のARMデータ転送123がフェッチされる時に、CPSTOPCレジスタの値がHIGHであり、コプロセッサのクロックが走っていることを図示している。第1のTHUMB命令113がフェッチされる時に、信号AC\_TBTTは論理0(LOW)から論理1(HIGH)に遷移する。しかし、信号CP\_STOPCは論理0(コプロセッサのクロックに走り続けるように命令する)を論理1(コプロセッサのクロックに走るのを停止するように命令する)に切り換えない。信号CP\_STOPCは、第2のTHUMB命令114および第3のTHUMB命令116およびそれらに関連した第2のTHUMBデータ転送124および第3のTHUMBデータ転送126が完了するまで、遷移しない。信号CP\_STOPCは、コプロセッサ不在命令115と、第2のTHUMBデータ転送124と第3のTHUMBデータ転送126の間のコプロセッサ不在命令に関連したコプロセッサ不在データトランザクション125とで示される延長された処理持続時間までも感知する。AC\_TBTT信号は、第4のTHUMB命令117、第5のTHUMB命令118および第4のTHUMBデータ転送127の間ずっと論理1(HIGH)のままである。

#### 【0016】

ARMシステムがTHUMB状態を終了しARM状態になる時に、TBTT信号は、それがARM状態の動作を処理していることを表示する(例えば、LOWになる)。コプロセッサのクロックは、ARMシステムがTHUMB状態を終了しARM状態になる時の同じサイクルの間に始動する。このようにして、実行される次の命令が32ビットARM状態動作である場合、コプロセッサは32ビットARM状態動作を処理し続けるために使用可能である。

#### 【0017】

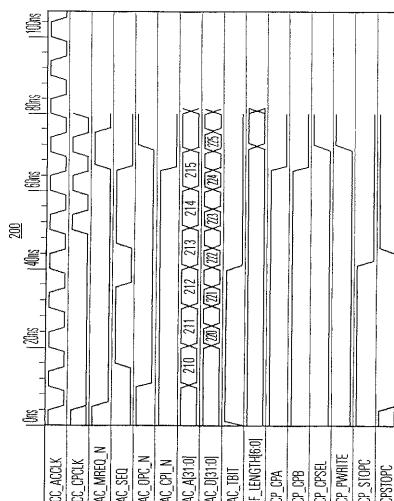

図2は、本発明のARMコプロセッサ電力低減システムおよび方法の一実施形態と関連したコプロセッサクロック始動波形テーブル200の一例である。コプロセッサクロック始動波形テーブル200は、第1のTHUMB命令210、第2のTHUMB命令211および第3のTHUMB命令212、およびそれらの対応する第1のTHUMBデータ転送220、第2のTHUMBデータ転送221および第3のTHUMBデータ転送223がフェッチされる時に、CPSTOPCレジスタの値がLOWでコプロセッサクロックが走っていないことを図示する。第1のARM命令213がフェッチされる時に、信号AC\_TBTTは論理1から論理0に遷移する。信号CP\_STOPCは論理1から論理0に遷移し、コプロセッサクロックに走り始めるように命令する。CPSTOPCレジスタの値は、論理0から論理1に遷移し、クロックが走り始めたことを表示する。CPSTOPCレジスタの値は、第2のARM命令214、第3のARM命令215、第1のARMデータ転送223、第2のARMデータ転送224、および第3のARMデータ転送225の間ずっと論理1のままである。

#### 【0018】

ARMコアはいくつかの信号を利用して、ARMコプロセッサパイプラインの後続の段を介した進度および前送りを表示する。否定メモリ要求信号(MREQ\_NまたはnMREQ)は、次のサイクルでメモリアクセスが要求されているかどうかを表示する。NMR\_EQがLOWである場合、ARMコアプロセッサは次のサイクルでメモリアクセスを要求

10

20

30

40

50

する。否定演算コードフェッチ信号 (O P C \_ N または n O P C ) は、A R Mコアプロセッサがメモリから命令をフェッチしているかどうかを表示する。O P C \_ N がL O Wである場合、A R Mコアプロセッサはメモリから命令をフェッチしており、O P C \_ N がH I G Hである場合、データが転送されている（データがある場合）。A R Mコアに整数の数のメモリクロック入力 (M C L K ) サイクルを待たせるかまたは機能停止にさせるために、否定待ち (W A I T \_ N または n W A I T ) 信号が利用される。M C L K はA R Mコアメモリアクセスと内部動作のタイミングを合せるクロックである。W A I T \_ N がL O Wである時に、A R Mコアは待つか機能停止する。

#### 【0019】

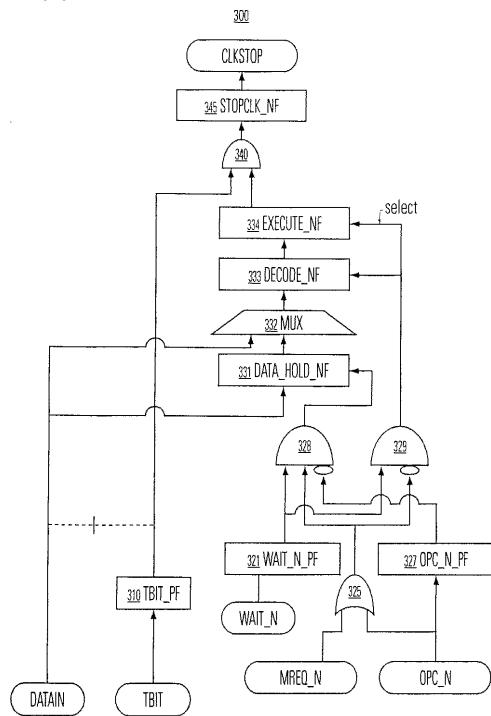

図3は、本発明の一実施形態であるA R Mコプロセッサ電力低減システム300の図である。A R Mコプロセッサ電力低減システム300は、T H U M BビットレジスタT B I T \_ R F 3 1 0、待ちレジスタW A I T \_ N \_ P F 3 2 1、第1の論理O R構成要素3 2 5、否定演算コードフェッチレジスタO P C \_ N \_ P F 3 2 7、第3の論理A N D構成要素3 2 8、第2の論理A N D構成要素3 2 9、データ保持レジスタD A T A \_ H O L D \_ N F 3 3 1、マルチプレクサM U X 3 3 2、デコードレジスタD E C O D E \_ N F 3 3 3、実行レジスタE X E C U T E \_ N F 3 3 4、第1の論理A N D構成要素3 4 0および停止クロックレジスタS T O P C L K \_ N F 3 4 5を備える。識別にP Fを含むレジスタは、信号が正に向かうエッジでトリガされるフリップフロップを含む。識別にN Fを含むレジスタは信号の負に向かうエッジでトリガされるフリップフロップを含む。T B I T \_ P F 3 1 0は、第1の論理A N D構成要素3 4 0に結合されている。第3の論理A N D構成要素3 2 8は、W A I T \_ N \_ P F 3 2 1、第1の論理O R構成要素3 2 5、O P C \_ N \_ P F 3 2 7、およびD A T A \_ H O L D \_ N F 3 3 1に結合されている。第2の論理A N D構成要素3 2 9は、W A I T \_ N \_ P F 3 2 1、第1の論理O R構成要素3 2 5、O P C \_ N \_ P F 3 2 7、D E C O D E \_ N F 3 3 3、およびE X E C U T E \_ N F 3 3 4に結合されている。M U X 3 3 2は、D A T A \_ H O L D \_ N F 3 3 1と、およびE X E C U T E \_ N F 3 3 4に結合されているD E C O D E \_ N F 3 3 3とに結合されている。E X E C U T E \_ N F 3 3 4は、S T O P C L K \_ N F 3 4 5に結合されている第1の論理A N D構成要素3 4 0に結合されている。

#### 【0020】

A R Mコプロセッサ電力低減システム300の構成要素は、協働して動作してA R M命令をA R Mパイプラインを通して転送し、A R MパイプラインがT H U M B状態の命令を処理している場合、コプロセッサのクロックをオフにする信号を起動するように動作する。第1の論理A N D構成要素3 4 0は、論理的に入力信号を解析し、A R Mパイプラインの命令の状態に基づいてコプロセッサのクロックをオンまたはオフにする信号を供給するように構成されている。例えば、第1の論理A N D構成要素3 4 0は、A R Mパイプライン命令がT H U M B状態の命令である場合、コプロセッサのクロックをオフにし、A R Mパイプライン命令がA R M状態の命令である場合、コプロセッサのクロックをオンにする信号を供給する。T H U M BビットレジスタT B I T \_ P F 3 1 0は、T H U M Bビット(T B I T )信号の論理値を格納し、そのT H U M Bビット(T B I T )信号は、A R Mパイプラインの命令がT H U M B状態で動作しているかA R M状態で動作しているかを表示する。実行レジスタE X E C U T E \_ N F 3 3 4は、前記A R Mパイプラインの実行段と関連した情報を格納する。

#### 【0021】

第2のA N D構成要素3 2 9は、A R Mパイプラインにより命令およびデータの前送りを制御する。論理O R構成要素3 2 5は、論理O R構成要素3 2 5の入力（例えば、否定メモリ要求信号 (M R E Q \_ N ) および否定演算コードフェッチ信号 (O P C \_ N ) ）が論理1である場合、論理1の値を伝送し、また、論理O R構成要素3 2 5の前記入力が論理0である場合、論理0を伝送する。待ちレジスタW A I T \_ N \_ P F 3 2 1は否定待ち信号（例えば、W A I T \_ N ）の値を取り込む。

#### 【0022】

10

20

30

40

50

第3の論理AND構成要素328は、格納されたデータをARMパイプラインで転送するように指示する信号を伝送する。データ保持レジスタDATA\_HOLD\_NF331はARMパイプラインで処理されるのを待つデータを格納する。否定演算コードフェッチレジスタOPC\_N\_PF327は、ARMコアプロセッサがメモリから命令をフェッチするかどうかを表示する否定演算フェッチ信号の状態を格納する。デコードレジスタDECODE\_NF333は、ARMパイプラインのデコード段と関連した情報を格納する。マルチプレクサMUX332は、データ保持レジスタまたは信号中のデータからの信号のような前記デコードレジスタに伝送する信号を選択する。

【0023】

ARM命令パイプライン論理は、WAIT\_N\_PF321の情報および信号OPC\_N 10 およびMREQ\_Nの論理状態を調べて、様々なARMコアレジスタによりARMシステムデータからの命令をラッ奇するときを決定する。前の立上がりエッジからTBIT値はサンプリングされ、デコード段および実行段に向けて移動しているデータとともに送り出される。これによって、ARMコプロセッサ電力低減システム300はコプロセッサクロックを適切に始動／停止することができるようになる。

【0024】

図4は、ARMコプロセッサ電力低減真理値表400の図である。ARMコプロセッサ電力低減真理値表400は、ARMコプロセッサ電力低減システム300の真理値表である。本発明の一実施形態では、クロックの立上りエッジでWAIT\_N\_PFの出力が論理1であり、かつOPC\_N信号は論理0であり、かつMREQ\_N信号は論理0である場合、ARMコアは命令をフェッチしている。 20

命令それ自体は、クロックの次の立ち下がりエッジでARMコアデータバス上に置かれる。WAIT\_N\_PFに格納された値が論理0である場合、命令はARMコアのデータバスにとどまつたままであり、DATA\_HOLD\_NF331、マルチプレクサMUX332、デコードレジスタDECODE\_NF333、または実行レジスタEXECUTE\_NF334の間で、命令は移されない。レジスタOPC\_N\_PF327に格納された値が論理1であり、かつ信号OPC\_Nか信号MREQ\_Nが論理1である場合は、DATA\_HOLD\_NF331、マルチプレクサMUX332、デコードレジスタDECODENF333、または実行レジスタEXECUTE\_NF334の間で、命令は移されない。 30

クロックの立ち下がりエッジで、WAIT\_N\_PF321の値が論理1であり、かつOPC\_N信号が論理1であるかMREQ\_N信号が論理1であるかいずれかの場合、ARMコアは現在命令をデコード段および実行段を通して移さない。しかし、データが存在すれば、ARMコアはデータ処理を続ける。OPC\_N\_PFの情報が論理0である場合、ARMデータバス上の命令はDATA\_HOLD\_NF331に入れられ、「オンホールド」状態になる。

【0025】

ARMコプロセッサ電力低減真理値表400の残りの段の間に、命令はパイプラインの段を通って移動する。クロックの立ち下がりエッジで、WAIT\_N\_PF321の情報が論理1であり、かつOPC\_N信号が論理0であり、かつMREQ\_N信号が論理0である場合、ARMコアは現在命令をデコード段に移す。OPC\_N\_PF327の情報の状態によって、どちらの命令がデコード段に移されるかが決まる。OPC\_N\_PF327の情報が論理1である場合、DATA\_HOLD\_NF331の命令はまだデコード段を通過していないので、DATA\_HOLD\_NF331の命令がデコード段に移される。OPC\_N\_PF327の情報が論理1である場合、ARMデータバス上の命令は、デコーディングのために、REGISTER\_DECODE\_NF333に入れられる。クロックの立ち下がりエッジで、WAIT\_N\_PF321の値が論理1であり、かつ信号OPC\_Nが論理0であり、かつ信号MREQ\_Nが論理0である場合、レジスタDECODE\_NF333の内容は、実行のためにレジスタEXECUTE\_NF334に移動する。 40 50

## 【0026】

第1の論理AND構成要素340は、その入力すなわち、TBIT\_PF310に格納された値と、EXECUTE\_NF343に格納された値のTBITとが論理1である場合、論理1の値を伝送する。また、その入力のいずれかが論理0の値である場合、論理0の値を伝送する。第1の論理AND構成要素340で伝送された論理値は一時的にSTOPCLK\_NF345に格納され、それから、信号CLKSTOPとしてコプロセッサのクロックに転送される。CLKSTOPが論理1である場合、コプロセッサのクロックは停止され、CLKSTOPが論理0である場合、コプロセッサは始動される。

## 【0027】

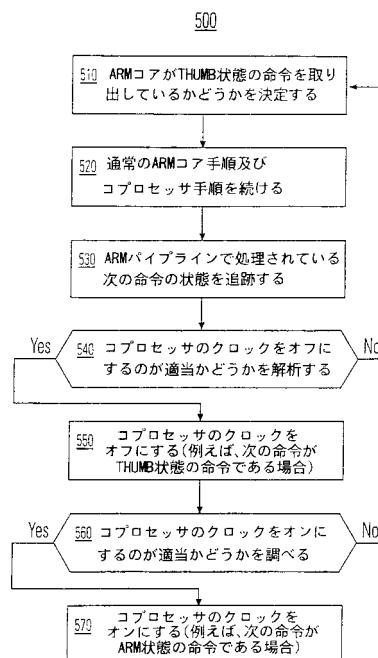

図5は、本発明の一実施形態であるARMコプロセッサ電力低減方法500の流れ図である。ARMコプロセッサ電力低減方法500は、ARMシステムがARMコプロセッサを利用しない活動状態にあるかどうか、さらにARMコプロセッサ分だけ電力消費を低減するかどうかを確定する。一実施形態では、ARMコプロセッサ電力低減方法500はARMコア周辺からの信号を検査して、ARMコアがARM状態の動作を容易にしようとしているかTHUMB状態の動作を容易にしようとしているかを決定する。ARMコプロセッサ電力低減方法500が、ARMコアがTHUMB状態の動作を容易にしようとしているのを検出した場合、ARMコプロセッサ電力低減方法500は、ARMコプロセッサと関連したクロックにオフするように信号を送る。例えば、ARMコプロセッサ電力低減方法500は、ARMバイラインの一連の命令が全てTHUMB状態の動作であると確定した場合、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックがオフになるようになる。ARMコプロセッサのクロックがオフになるので、ARMコプロセッサのレジスタは切り換わらないし、電力を消費しない。

10

## 【0028】

ステップ510で、ARMコプロセッサ電力低減方法500は、ARMコアがTHUMB状態の命令をフェッチしているかどうかを決定する。一実施形態では、ARMコプロセッサ電力低減方法500は、ARMプロセッサが命令をフェッチしているかどうかを検査する。命令がフェッチされている場合、ARMコプロセッサ電力低減方法500は、フェッチされている命令と関連したTBIT信号の論理状態を取り込む。例えば、ARMコプロセッサ電力低減方法500は、否定メモリ要求信号(MREQ\_NまたはnMREQ)、否定演算コードフェッチ信号(OPC\_NまたはnOPC)および否定待ち信号(WAIT\_NまたはnWAIT)を走査して、ARMコアが命令をフェッチしているかどうかを決定する。1つの例では、論理0(LOW)のTBIT信号はARM状態の命令を表示し、論理1(HIGH)のTBIT信号はTHUMB状態の命令を表示する。ARMコプロセッサ電力低減方法500が、ARMコアがTHUMB状態の命令をフェッチしているかどうかを決定した後で、ARMコプロセッサ電力低減方法500はステップ520に進む。

20

## 【0029】

ARMコプロセッサ電力低減方法500は、ステップ520ARMで、通常のARMコア手順およびコプロセッシング手順を継続する。1つの例では、ARMコプロセッサ電力低減方法500は、命令をフェッチ段からのデコード段に移し、さらにその命令を実行段に進めて、通常のARMコア手順およびコプロセッシング手順を継続する。

30

## 【0030】

ステップ530で、ARMコプロセッサ電力低減方法500は、ARMバイラインで処理されている次の命令の状態を追跡する。一実施形態では、ARMコプロセッサ電力低減方法500は、TBITレジスタ(例えば、TBIT\_PF210)のTBIT信号の論理値を格納する。1つの例では、命令がバイラインのフェッチ段からデコード段に移される時に、TBIT値は格納される。

## 【0031】

ステップ540で、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックをオフにするのが適切かどうかを解析する。ARMコプロセッサ電力低減方法500の一

40

50

実施形態では、ARMコプロセッサ電力低減方法500が、ARMパイプラインで処理している命令がTHUMB状態の命令かまたはTHUMB状態の命令と関連したデータであると確定した場合、コプロセッサのクロックをオフにするのが適切である。例えば、THUMB状態の命令またはTHUMB状態の命令と関連したデータがARMパイプラインの段を占めている場合は、コプロセッサのクロックをオフにするのが適切である。コプロセッサのクロックをオフにするのが適切でない場合、ARMコプロセッサ電力低減方法500は、ステップ520に輪を描いて戻る。コプロセッサのクロックをオフにするのが適切な場合、ARMコプロセッサ電力低減方法500は、ステップ550に進む。

#### 【0032】

ステップ550で、ARMコプロセッサ電力低減方法500は、コプロセッサクロックをオフにする。本発明の一実施形態では、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックに停止させる信号を送る。 10

#### 【0033】

ステップ560で、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックをオンにするのが適切かどうかを調べる。ARMコプロセッサ電力低減方法500の一実施形態では、ARMコプロセッサ電力低減方法500が、ARMパイプラインの命令がARM状態の命令かARM状態の命令と関連したデータかであることを確認した場合は、コプロセッサのクロックをオンにするのが適切である。例えば、ARM状態の命令またはARM状態の命令と関連したデータがARMパイプラインレジスタを占めている場合は、コプロセッサのクロックをオンにするのが適切である。一実施形態では、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックがオフになった後で、命令フェッチと関連したTBIT信号を監視し続ける。例えば、ARMコプロセッサ電力低減方法500は、論理0のTBIT値を解釈して、関連した命令フェッチがARM状態の命令フェッチであると表示する。次のフェッチがARM状態の命令である場合は、コプロセッサのクロックをオンにするのが適切である。コプロセッサのクロックをオンにするのが適切でない場合、ARMコプロセッサ電力低減方法500は、ステップ550に輪を描いて戻る。コプロセッサのクロックをオンにするのが適切である場合、ARMコプロセッサ電力低減方法500は、ステップ570に進む。 20

#### 【0034】

ステップ570で、ARMコプロセッサ電力低減方法500は、コプロセッサクロックをオンに切り換え、ステップ510に輪を描いて戻る。 30

#### 【0035】

上で示したように、ARMコプロセッサ電力低減方法500は、ステップ540で、ARMパイプラインで処理している命令がTHUMB状態の命令であるかまたはTHUMB状態の命令と関連したデータであるかを確定する。ARMコプロセッサ電力低減方法500の一実施形態では、格納された待ちの値（例えば、WAIT\_N\_PF221）が論理1であり、かつOPC\_N信号とMREQ\_N信号の両方が論理0である場合、ARMコプロセッサ電力低減方法500は、パイプラインの実行レジスタ（例えば、EXECUTE\_NF234）の命令と関連したTBITとTBITレジスタ（例えば、TBIT\_PF210）の格納されたTBIT値を比較する。パイプラインの実行レジスタ（例えば、EXECUTE\_NF234）の命令と関連したTBITと、TBITレジスタ（例えば、TBIT\_PF210）の格納されたTBIT値との両方が論理1である場合、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックを停止する。パイプラインの実行レジスタ（例えば、EXECUTE\_NF234）の命令と関連したTBITか、またはTBITレジスタ（例えば、TBIT\_PF210）の格納されたTBIT値かいずれかが論理0である場合、ARMコプロセッサ電力低減方法500は、コプロセッサのクロックを停止しない。 40

#### 【0036】

このようにして、本発明のシステムおよび方法によって、ARMシステムのコプロセッサによる電力消費は減少する。本システムおよび方法は、ARMシステムの動作機能性を妨 50

害しない。本発明によって THUMB 状態の動作中に切り換わるコプロセッサのレジスタは減少し、また、本発明により、電力供給の要求条件軽減が容易になる。

【0037】

本発明の特定の実施形態についての上記の記述は、例証と説明のために示した。それらは、網羅的であることを意図しないし、または本発明を開示された明確な形態に限定する意図ではない。上記の教示の観点から、明らかに、多くの修正物および変更物が可能である。実施形態は、本発明の原理およびその実際の応用を最も適切に説明するために選び説明した。これによって、当業者は、特定の意図する使用に適するような様々な修正物で、本発明および様々な実施形態を最適に利用することができるようになる。

【図面の簡単な説明】

10

【図 1】 本発明の ARM コプロセッサ電力低減システムおよび方法の一実施形態と関連したコプロセッサクロック停止波形テーブルの一例である。

【図 2】 本発明の ARM コプロセッサ電力低減システムおよび方法の一実施形態と関連したコプロセッサクロック始動波形テーブルの一例である。

【図 3】 本発明の一実施形態である、ARM コプロセッサ電力低減システムの図である。

【図 4】 本発明の ARM コプロセッサ電力低減システムの ARM コプロセッサ電力低減真理値表の説明図である。

【図 5】 本発明の ARM コプロセッサ電力低減方法の一実施形態の流れ図である。

【図 1】

FIG. 1

【図 2】

FIG. 2

【図3】

FIG.3

【図4】

| WAIT_N_PF | OPC_N_PF | OPC_N | MREQ_N | DHOLD | DECODE | EXECUTE |

|-----------|----------|-------|--------|-------|--------|---------|

| 0         | X        | X     | X      | HOLD  | HOLD   | HOLD    |

| X         | 1        | 1     | X      | HOLD  | HOLD   | HOLD    |

| X         | 1        | X     | 1      | HOLD  | HOLD   | HOLD    |

| 1         | 0        | 0     | 0      | HOLD  | DIN    | DECODE  |

| 1         | 0        | 1     | X      | DIN   | HOLD   | HOLD    |

| 1         | 1        | 0     | 0      | HOLD  | DHOLD  | DECODE  |

FIG.4

【図5】

---

フロントページの続き

(56)参考文献 特開平06-202754(JP,A)

特開平09-212358(JP,A)

特開平03-091028(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 9/38

G06F 1/04

G06F 9/30