(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7263028号

(P7263028)

(45)発行日 令和5年4月24日(2023.4.24)

(24)登録日 令和5年4月14日(2023.4.14)

|                        |                    |

|------------------------|--------------------|

| (51)国際特許分類             | F I                |

| H 04 N 25/60 (2023.01) | H 04 N 25/60       |

| H 04 N 23/54 (2023.01) | H 04 N 23/54       |

| H 04 N 23/60 (2023.01) | H 04 N 23/60 3 0 0 |

請求項の数 10 (全12頁)

|          |                                  |          |                                            |

|----------|----------------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2019-11886(P2019-11886)        | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 平成31年1月28日(2019.1.28)            | (74)代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65)公開番号 | 特開2020-120340(P2020-120340<br>A) | (74)代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (43)公開日  | 令和2年8月6日(2020.8.6)               | (72)発明者  | 村上 直隆<br>東京都大田区下丸子3丁目30番2号キ<br>ヤノン株式会社内    |

| 審査請求日    | 令和4年1月20日(2022.1.20)             | 審査官      | 橋爪 正樹                                      |

最終頁に続く

(54)【発明の名称】 撮像装置およびその制御方法

## (57)【特許請求の範囲】

## 【請求項1】

複数の単位画素が行列状に配列された画素部を有するセンサチップと、画像処理チップとを有する撮像装置であって、

前記センサチップは、

前記画像処理チップから補正データを受信する第1の受信手段と、

前記画素部から読み出した画像データに対して補正処理を行う手段であって、前記画素部からの読み出し処理単位に対応した単位の前記画像データに対して、前記第1の受信手段を介して受信した補正データを用いて前記補正処理を実行して補正画像データを取得する補正手段と、

前記補正画像データを前記画像処理チップに送信する第1の送信手段とを有し、

前記画像処理チップは、

前記センサチップから前記補正画像データを受信する第2の受信手段と、

前記第2の受信手段で受信した前記補正画像データに画像処理する処理手段と、

前記補正手段で用いる補正データを前記センサチップに送信する第2の送信手段とを有する

ことを特徴とする撮像装置。

## 【請求項2】

前記センサチップは、前記第1の受信手段を介して受信した前記補正データを記憶する第1の記憶手段を備え、

前記画像処理チップは、前記第2の送信手段を介して送信する前記補正データを記憶する第2の記憶手段を備えることを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記画像処理チップと接続される不揮発性の記憶手段である第3の記憶手段をさらに有し、

前記撮像装置の起動時に、前記第3の記憶手段に記憶された補正データを前記第3の記憶手段から前記第2の記憶手段へ展開する

ことを特徴とする請求項2に記載の撮像装置。

**【請求項4】**

10

前記画像処理チップは、前記補正データを決定する決定手段をさらに備え、

前記決定手段は、前記補正手段での補正を行わずに得られる画像データに基づいて前記補正データを決定し、決定された前記補正データを前記第3の記憶手段に記憶する

ことを特徴とする請求項3に記載の撮像装置。

**【請求項5】**

前記撮像装置の動作モードを複数の動作モードのいずれかに設定する設定手段を備え、

前記第2の送信手段は、前記複数の動作モードに対応した前記補正データのうち、前記設定手段により設定された動作モードに対応した補正データを前記センサチップに送信し、前記撮像装置の動作モードが変更された場合、前記変更された動作モードに対応した補正データを前記センサチップに送信する

20

ことを特徴とする請求項1から4のいずれか1項に記載の撮像装置。

**【請求項6】**

複数の単位画素が行列状に配列された画素部を有するセンサチップと、画像処理チップとを有する撮像装置の制御方法であって、

前記画像処理チップから前記センサチップが補正データを受信する第1の受信工程と、

前記センサチップが前記画素部から読み出した画像データに対して補正処理を行う工程であって、前記画素部からの読み出し処理単位に対応した単位の前記画像データに対して

前記第1の受信工程で受信した補正データを用いて前記補正処理を実行して補正画像データを取得する補正工程と、

前記センサチップが前記補正画像データを前記画像処理チップに送信する第1の送信工程と、

30

前記画像処理チップが前記センサチップから前記補正画像データを受信する第2の受信工程と、

前記画像処理チップが前記第2の受信工程で受信した前記補正画像データに画像処理する処理工程と、

前記画像処理チップが前記補正工程で用いる補正データを前記センサチップに送信する第2の送信工程と、を有する

ことを特徴とする撮像装置の制御方法。

**【請求項7】**

前記センサチップが、前記第1の受信工程により受信した前記補正データを第1の記憶手段に記憶する第1の記憶工程と、

前記画像処理チップが、前記第2の送信工程により送信する前記補正データを第2の記憶手段に記憶する第2の記憶工程を備える

ことを特徴とする請求項6に記載の撮像装置の制御方法。

**【請求項8】**

前記画像処理チップが、前記撮像装置の起動時に、前記画像処理チップと接続される不揮発性の第3の記憶手段から、前記補正データを前記第2の記憶手段へ展開する展開工程を備える

ことを特徴とする請求項7に記載の撮像装置の制御方法。

**【請求項9】**

40

50

前記画像処理チップが前記補正データを決定する決定工程をさらに備え、前記決定工程は、前記補正工程での補正を行わずに得られる画像データに基づいて前記補正データを決定し、決定された前記補正データを前記第3の記憶手段に記憶することを特徴とする請求項8に記載の撮像装置の制御方法。

#### 【請求項10】

前記撮像装置の動作モードを複数の動作モードのいずれかに設定する設定工程を備え、前記第2の送信工程は、前記複数の動作モードに対応した前記補正データのうち、前記設定工程により設定された動作モードに対応した補正データを前記センサチップに送信し、前記撮像装置の動作モードが変更された場合、前記変更された動作モードに応じた補正データを前記センサチップに送信する

10

ことを特徴とする請求項6から9のいずれか1項に記載の撮像装置の制御方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は撮像装置およびその制御方法に関する。

##### 【背景技術】

##### 【0002】

撮像センサから読み出される画像データに対する補正処理を、撮像センサに設けられた補正回路で実行する撮像装置がある。

##### 【0003】

特許文献1の撮像装置は、撮像センサが備える受光データ処理部で、撮像センサが取得した画像データに対する処理を実行する。

20

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【文献】特開2018-46324号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

撮像センサの特性や撮像装置の動作モードに応じて異なるパラメータを用いて補正処理を実行するために、撮像センサチップに複数のパラメータを格納する大容量のメモリを搭載すると、チップサイズが大きくなるという懸念がある。

30

##### 【0006】

本発明の撮像装置は、撮像センサの特性や撮像装置の動作モードに応じた補正処理を撮像センサチップで実行可能とするとともに、撮像センサチップに設けるメモリサイズの拡大を抑制することを目的とする。

##### 【課題を解決するための手段】

##### 【0007】

本発明は、複数の単位画素が行列状に配列された画素部を有するセンサチップと、画像処理チップとを有する撮像装置であって、前記センサチップは、前記画像処理チップから補正データを受信する第1の受信手段と、前記画素部から読み出した画像データに対して補正処理を行う手段であって、前記画素部からの読み出し処理単位に対応した単位の前記画像データに対して、前記第1の受信手段を介して受信した補正データを用いて前記補正処理を実行して補正画像データを取得する補正手段と、前記補正画像データを前記画像処理チップに送信する第1の送信手段とを有し、前記画像処理チップは、前記センサチップから前記補正画像データを受信する第2の受信手段と、前記第2の受信手段で受信した前記補正画像データに画像処理する処理手段と、前記補正手段で用いる補正データを前記センサチップに送信する第2の送信手段とを有する。

40

##### 【発明の効果】

##### 【0008】

50

本発明の撮像装置によれば、撮像センサの特性や撮像装置の動作モードに応じた補正処理を撮像センサチップで実行可能とともに、撮像センサチップに設けるメモリサイズの拡大を抑制することが可能となる。

【図面の簡単な説明】

【0009】

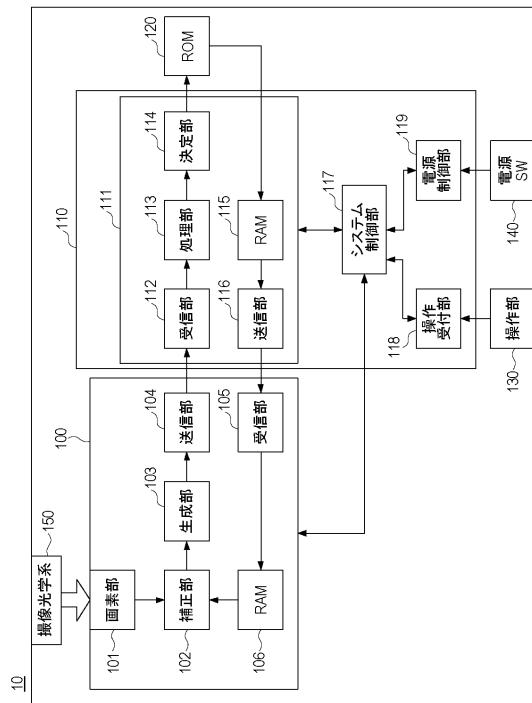

【図1】撮像装置の構成を説明するブロック図である。

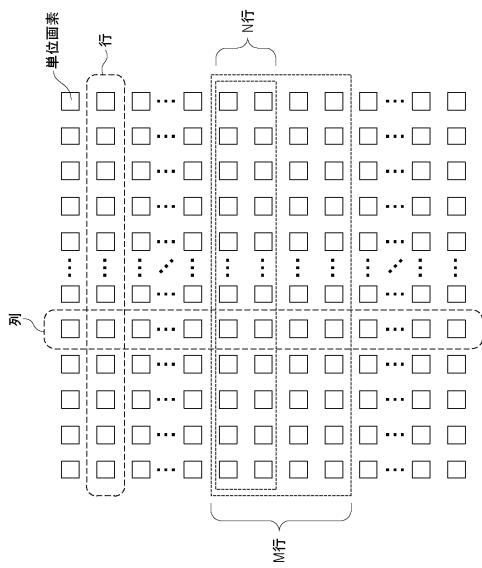

【図2】画素部101における単位画素の配列を示す模式図である。

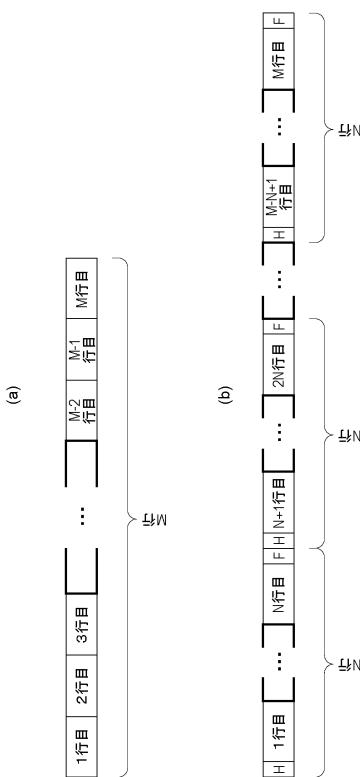

【図3】画像データのパケット化について説明した図である。

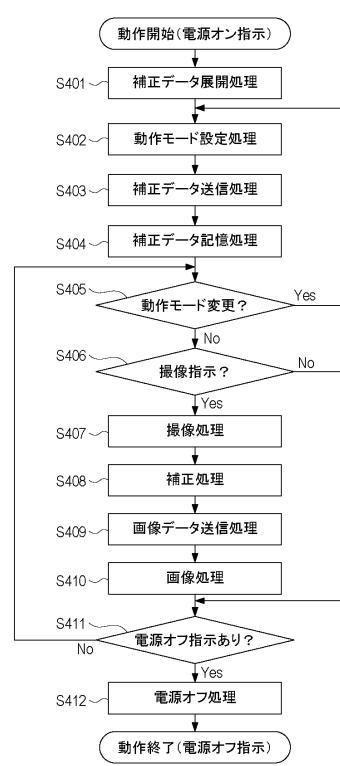

【図4】撮像装置の動作を示したフローチャートである。

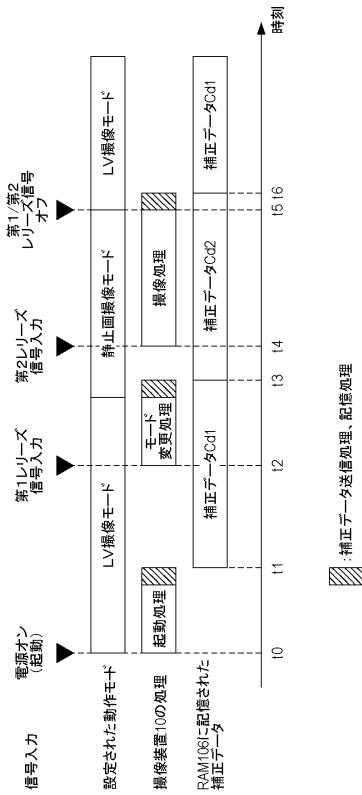

【図5】補正データの送信タイミングを示したタイミングチャートである。

10

【発明を実施するための形態】

【0010】

<実施例1>

以下、本発明の第1の実施形態について詳述する。

【0011】

図1は、本発明における撮像装置の構成を説明するブロック図である。撮像装置10は、撮像センサ100、制御回路110、ROM120、操作部130、電源SW140、および撮像光学系150を備える。

【0012】

撮像センサ100は、光学系を介して受光した光に基づいて画像信号を生成するセンサチップである。撮像センサ100は、画素部101、補正部102、生成部103、送信部104、受信部105、およびRAM106を備える。

20

【0013】

画素部101は受光した光の強度に基づいて各画素の画素データを取得する複数の単位画素を備える。画素部101において、複数の単位画素は、行列状に配列される。画素部101の複数の単位画素から構成される面を「1画面」とし、1画面分の単位画素の画素データから構成される画像データを、1画面分の画像データであるとする。

【0014】

図2は、画素部101における単位画素の配列を示す模式図である。画素部101の複数の単位画素のうち、垂直方向に並んだ複数の単位画素の単位を列と呼ぶ。また、画素部101の複数の単位画素のうち、水平方向に並んだ複数の単位画素の単位を行と呼ぶ。画素部101は、複数の単位画素のうち、複数の行(M行)を同時に選択し、選択された複数の行に含まれる単位画素の画素データを、垂直出力線を介して読み出す構造を備える。ここで、画素部101から出力される複数の行に含まれる単位画素の画素データをブロック画像データと呼ぶ。

30

【0015】

補正部102は、RAM106から取得した補正データを用いて、画素部101から取得したブロック画像データに対して補正処理を行う。

【0016】

例えば、補正部102では、列オフセットノイズ補正を行うとする。ブロック画像データの画素データに重畠したオフセットは、単位画素が所属する列ごとに値が異なる。列ごとに異なるオフセットが重畠することにより、画像データに縞状のノイズが発生することがある。列オフセットノイズ補正は、この列間のオフセット量の差を補正し、縞状のノイズの発生を抑制するための処理である。具体的には、補正部102は、RAM106から取得した列毎の列オフセット補正值を示す補正データを用いて、画素部101から取得した複数の行の単位画素の画素データからオフセット補正值を減算する処理を実行する。

40

【0017】

ここで補正処理した画像信号については、列オフセットノイズ補正以外の処理を引き続き後述する制御回路110の画像処理部111で行う。そのため、単位画素あたりの画像信号の語長は丸めずに、画素部101が読み出した単位画素あたりの画像信号の語長より

50

長いまま送信する。

【0018】

生成部103は、補正部102で補正されたブロック画像データ（補正画像データ）に対してヘッダやフッタといった付加情報を加えて画像信号をパケット化する。

【0019】

図3は、生成部103が実行するブロック画像データのパケット化について示す模式図である。図3において、MとNはどちらも整数でMはNより大きく、MはNの整数倍であるとする。上述したように、画素部101は、M行ごとに画素データを読み出しブロック画像データとして出力する。また、補正部102は、ブロック画像データに対して、補正処理（列オフセットノイズ補正処理）を実行する。図3（a）は、ブロック画像データを示す模式図である。ブロック画像データは、M行分の単位画素の画素データをまとめたデータである。

10

【0020】

生成部103は、補正処理が行われたブロック画像データをN行ごとに分割し、分割された画像データ（送信画像データ）ごとに、ヘッダ（H）およびフッタ（F）を付加する。ヘッダおよびフッタは、画像信号のシンボルアラインの目印にするなどの目的のために付加されるデータである。なお、N行は、画像処理部111の処理部113の処理単位である。図3（b）は、ブロック画像データを分割して得られる送信画像データを示す模式図である。

20

【0021】

撮像センサ100から画像処理部111に送信する画像データのサイズを、予め画像処理部111の処理部113の処理単位に合わせておくことで、処理部113は受信した画像データをそのまま処理することができる。つまり、撮像センサ100の読み出し単位が画像処理部の処理単位を超てしまっている場合でも画像処理部はそれを意識せずに画像信号を処理できる。

【0022】

なお、Nは1より大きい整数であることが望ましい。1行ごとにパケット化してそれにヘッダやフッタを付加するよりも、N行ごとに分割するほうがヘッダやフッタ分のオーバーヘッドを少なくすることができる。

30

【0023】

送信部104は、パケット化された送信画像データを画像処理部111へ出力する。

【0024】

受信部105は、画像処理部111から補正データを受信し、RAM106へ出力する。

【0025】

RAM106は、受信部105からの補正データを記憶し、不図示のタイミング制御回路等からの指示により、画素部101からの画像信号の読み出しに同期して補正データを補正部102へ出力する。

【0026】

制御回路110は、撮像装置10全体の動作を制御する制御回路チップである。また、制御回路110は、撮像センサ100から取得した画像データを処理する画像処理チップでもある。制御回路110は、撮像センサ100から取得した画像データを処理する画像処理部111、システム制御部117、操作受付部118、および電源制御部119を備える。制御回路110は、撮像センサ100と異なるチップである。なお、制御回路110の各機能ブロック、および電子回路は複数のチップにわたって設けられていてもよい。

40

【0027】

画像処理部111は、撮像センサ100から取得した画像データを処理する処理回路である。画像処理部111は、受信部112、処理部113、決定部114、RAM115、および送信部116を備える。

【0028】

受信部112は、撮像センサ100からのパケット化された送信画像データを受信し、

50

処理部 113 へ出力する。

【0029】

処理部 113 は、パケット化された送信画像データのヘッダやフッタといった付加情報を解析して画素部 101 の各単位画素の画素データを取り出し、所定のデータ処理を行う。所定のデータ処理は、N 行分の画素データに対して実行する処理である。また、所定のデータ処理は、補正部 102 で実行する補正処理と異なる処理を含む。例えば、所定のデータ処理は、エンハンス処理、色補正処理、およびノイズ低減処理を含む。また、処理部 113 は、処理された複数の送信画像データを用いて、1 画面分の画像データを生成する。

【0030】

決定部 114 は、補正部 102 が使用する補正データを決定する。決定部 114 は、あらかじめ処理部 113 の処理を実行した後の画像を解析することにより補正データを決定する。

10

【0031】

決定部 114 は、撮像装置 10 の調整用の工程で得られるサンプル画像データを用いて補正データを決定する。サンプル画像データは例えば、白板等の均一な画素データが得られることが期待される被写体を撮像して得られる画像データである。このとき、補正部 102 による補正処理を行わずに、撮像センサ 100 から画像データを取得する。決定部 114 は、得られたサンプル画像データのノイズ成分を解析し、単位画素の列ごとに重畠しているオフセット値を算出する。決定部 114 は、取得したオフセット値から列オフセット補正値を算出する。決定部 114 は、決定したオフセット補正値を、ROM120 に格納する。

20

【0032】

RAM115 は、ROM120 から展開された送信部 116 が撮像センサ 100 に出力するための補正データを、記憶する揮発性の記憶媒体である。

【0033】

送信部 116 は、撮像装置 10 の起動時、および動作モードの変更時に、RAM115 から読み出した補正データを撮像センサ 100 に送信する。

【0034】

システム制御部 117 は、撮像装置 10 の動作を制御するためのプロセッサである。システム制御部 117 は、制御回路 110 の各機能ブロックや、撮像センサ 100 の動作を制御する。システム制御部 117 は、補正データの決定処理、補正データの送信処理、撮像実行指示、動作モード設定処理等を制御する。

30

【0035】

操作受付部 118 は、後述する操作部 130 から入力された操作信号の入力を受け付ける。操作受付部 118 は、入力された操作信号に対応する情報をシステム制御部 117 に出力する。システム制御部 117 は、入力された情報に基づいて、撮像指示、動作モード変更処理等を実行する。

【0036】

電源制御部 119 は、後述する操作部 130 からレリーズ信号の入力を受け付ける。操作受付部 118 は、レリーズ信号が入力されたことをシステム制御部 117 に出力する。

40

【0037】

ROM120 は、撮像センサ 100 の補正部 102 で使用する補正データを記憶する不揮発性の記憶媒体である。

【0038】

操作部 130 は、ユーザが撮像装置 10 の動作を制御するために用いる操作部材である。操作部 130 は、ユーザが撮像を指示する為にユーザが操作可能なレリーズボタンや、撮像パラメータを設定するためのメニューボタン、選択ボタン等を含む。例えば、レリーズボタンをユーザが押下したことに応じて、レリーズ信号が操作受付部 118 に出力される。

【0039】

50

電源 SW140 は、ユーザが撮像装置 10 の電源オンおよびオフの切り替え指示する為に、ユーザが操作可能な切替スイッチである。ユーザが電源 SW140 をオン状態に切り換えると、電源制御部 119 に電源オン信号が出力される。ユーザが電源 SW140 をオフ状態に切り換えると、電源制御部 119 に電源オフ信号が出力される。なお、電源 SW140 がオン状態のとき、電源制御部 119 に接続した信号線の出力が High になり、電源 SW140 がオフ状態のとき、電源制御部 119 に接続した信号線の出力が Low となるスイッチであってもよい。

#### 【0040】

図 4 は、補正データが画像処理部 111 から撮像センサ 100 へ送信され、補正処理が行われる動作を示したフローチャートである。

10

#### 【0041】

電源 SW140 がオン状態に切り換えられたことに応じて、電源制御部 119 がシステム制御部 117 に電源を供給し処理が開始される。

#### 【0042】

S401 で、システム制御部 117 は、ROM120 から RAM115 に補正データを展開する。

#### 【0043】

S402 で、システム制御部 117 は、動作モードを設定する。電源オンの直後は、システム制御部 117 は、前回の電源オフの直前に設定されていた動作モードを設定する。なお、動作モードの変更指示が操作部 130 を介して入力された場合、入力された指示に応じた動作モードを設定する。

20

#### 【0044】

S403 で、システム制御部 117 は、RAM115 に展開された補正データのうち、設定された動作モードに対応する補正データを読み出し、撮像センサ 100 へ送信する。ライブビュー (LV) 撮像モードで使用される補正データを補正データ Cd1 とする。また、静止画撮像モードで使用される補正データを補正データ Cd2 とする。なお、撮像モードの変更は、ISO 感度や露出、絞り等のパラメータが変更した場合を含む。ISO 感度が変わったことに応じて、対応する補正データ Cd を変更してもよい。

#### 【0045】

S404 で、撮像センサ 100 の RAM106 は、受信した補正データを記憶する。

30

#### 【0046】

S405 で、システム制御部 117 は、撮像装置 10 の動作モードの変更があるか否か判断する。動作モードの変更は、操作部 130 を介して入力されるユーザ指示に基づいて実行が指示される。また、LV 撮像モードである場合、取得した画像を解析することで ISO 感度や絞り、露出等の撮像パラメータが異なる動作モードへの変更を、システム制御部 117 が実行することも可能である。

#### 【0047】

また、操作部 130 のリリーズボタンが 2 段階の操作が可能なボタンであり、撮像準備を指示する第 1 リリーズ信号と、撮像実行を指示する第 2 リリーズ信号とを出力可能であるとする。この場合、第 1 リリーズ信号が入力されたことに応じて、LV 撮像モードから静止画撮像モードへの動作モードの変更が指示されたと判定される。

40

#### 【0048】

動作モードの変更がある場合、処理は S402 に戻り、対応する動作モードの設定処理を実行する。動作モードの変更がない場合、処理は S406 へ進む。

#### 【0049】

S406 で、システム制御部 117 は、撮像指示が入力されたか否かを判定する。操作受付部 118 が操作部 130 からリリーズ信号を受け付けた場合、システム制御部 117 は、撮像指示が入力されたと判定する。撮像指示が入力されたと判定された場合、S407 に進む。そうでない場合、処置は S411 に進む。

#### 【0050】

50

S 4 0 7 で、システム制御部 1 1 7 は、撮像センサ 1 0 0 および画像処理部 1 1 1 に、撮像処理を実行させる。

【 0 0 5 1 】

S 4 0 8 で、補正部 1 0 2 は、画素部 1 0 1 から読み出した M 行分の単位画素の画素データから構成されるブロック画像データそれぞれに対して、補正データを用いて補正処理を実行する。処理は、S 4 0 9 へ進む。

【 0 0 5 2 】

S 4 0 9 で、生成部 1 0 3 は、補正部 1 0 2 によって処理されたブロック画像データを N 行ごとに分割した送信画像データを取得し、送信部 1 0 4 を介して制御回路 1 1 0 の画像処理部 1 1 1 に出力する。

10

【 0 0 5 3 】

S 4 1 0 で、画像処理部 1 1 1 の処理部 1 1 3 は、受信した送信画像データに対し画像処理を実行する。また、処理部 1 1 3 は、複数の送信画像データを画像処理し、1 画面の画像データを生成して、不図示の外部記憶媒体に出力する。外部記憶媒体は、撮像装置 1 0 に挿入された SD カード等の記憶媒体であるとする。

【 0 0 5 4 】

S 4 1 1 では、撮像装置 1 0 の電源を落とす指示（電源オフ）があるかどうか判断する。落とす指示が無い場合は S 4 0 5 へ戻る。落とす指示があった場合は動作を終了する。

【 0 0 5 5 】

図 5 は、動作モードに応じて RAM 1 0 6 に格納される補正データの経過を示す模式図である。例えば、時刻 t 0 で起動し、LV 動作モードで撮像装置 1 0 が動作を開始したとする。このとき、時刻 t 1 で、LV 動作モードに対応した補正データ Cd 1 が制御回路 1 1 0 から送信され、RAM 1 0 6 に記憶される。補正データ Cd 1 は、LV 撮像を前提とした補正データである。

20

【 0 0 5 6 】

時刻 t 2 で、操作部 1 3 0 のレリーズボタンから第 1 レリーズ信号が入力されとする。この時、S 4 0 5 で LV 撮像モードから静止画撮像モードへの変更が指示されたと判定し、S 4 0 2 で静止画撮像モードへの設定が実行される。そして、時刻 t 3 で静止画動作モードに対応した補正データ Cd 2 が制御回路 1 1 0 から送信され、RAM 1 0 6 に記憶される。

30

【 0 0 5 7 】

時刻 t 4 で、操作部 1 3 0 のレリーズボタンから第 2 レリーズ信号が入力されたことに応じて、S 4 0 7 ~ S 4 1 0 の処理が実行される。

【 0 0 5 8 】

また、ユーザが操作部 1 3 0 のレリーズボタンへの操作を停止した場合、静止画撮像モードから LV 撮像モードに動作モードが変更されるとする。静止画の撮像処理が完了した時刻 t 5 で、動作モードが LV 動作モードに設定され、時刻 t 6 で補正データ Cd 1 が RAM 1 0 6 に格納される。

【 0 0 5 9 】

上述した撮像装置によれば、撮像センサの読み出し処理単位に応じた補正処理を撮像センサ内で行うことができる。画像処理部が撮像センサの読み出し処理単位に応じた補正処理に対応していない場合でも、画像処理部を交換したり、新しく作り直したりせずに補正処理を行うことができる。

40

【 0 0 6 0 】

なお、撮像センサ 1 0 0 の画素部 1 0 1 が複数の読み出しモードを備え、M 行単位ではなく N 行単位でデータを読み出すモードの場合には、撮像センサ 1 0 0 の補正部 1 0 2 では補正処理を行わずそのまま N 行単位でパケットを送信する。そして、画像処理部 1 1 1 の処理部 1 1 3 で、撮像センサ 1 0 0 の補正部 1 0 2 での補正処理に相当する処理を行ってもよい。

【 0 0 6 1 】

50

以上、本実施形態によれば、撮像センサの特性や撮像装置の動作モードに応じた補正処理を撮像センサチップで実行可能とともに、撮像センサチップに設けるメモリサイズの拡大を抑制することが可能となる。また、撮像センサの読み出し処理単位に応じた補正処理を撮像センサ内で行うことができる。画像処理部が撮像センサの読み出し処理単位に応じた補正処理に対応していない場合でも、画像処理部を交換したり、新しく作り直したりせずに補正処理を行うことができる。

【符号の説明】

【0062】

|       |         |    |

|-------|---------|----|

| 1 0   | 撮像装置    | 10 |

| 1 0 0 | 撮像センサ   |    |

| 1 0 1 | 画素部     |    |

| 1 0 2 | 補正部     |    |

| 1 0 3 | 生成部     |    |

| 1 0 4 | 送信部     |    |

| 1 0 5 | 受信部     |    |

| 1 0 6 | R A M   |    |

| 1 1 0 | 制御回路    |    |

| 1 1 1 | 画像処理部   |    |

| 1 1 2 | 受信部     |    |

| 1 1 3 | 処理部     | 20 |

| 1 1 4 | 決定部     |    |

| 1 1 5 | R A M   |    |

| 1 1 6 | 送信部     |    |

| 1 1 7 | システム制御部 |    |

| 1 2 0 | R O M   |    |

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 特開2008-187438 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 23/54

H04N 23/60 - 23/698

H04N 25/60 - 25/69