(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6290190号

(P6290190)

(45) 発行日 平成30年3月7日(2018.3.7)

(24) 登録日 平成30年2月16日(2018.2.16)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO3F 3/193 (2006.01) | HO3F 3/193 |

| HO3F 3/68 (2006.01)  | HO3F 3/68  |

| HO4B 1/18 (2006.01)  | HO4B 1/18  |

| HO3F 1/22 (2006.01)  | HO3F 1/22  |

請求項の数 15 (全 32 頁)

|               |                               |           |                                                                                                                |

|---------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2015-514234 (P2015-514234)  | (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日 | 平成25年5月24日 (2013.5.24)        | (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (65) 公表番号     | 特表2015-521010 (P2015-521010A) | (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (43) 公表日      | 平成27年7月23日 (2015.7.23)        | (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                         |

| (86) 國際出願番号   | PCT/US2013/042741             | (74) 代理人  | 100194814<br>弁理士 奥村 元宏                                                                                         |

| (87) 國際公開番号   | W02013/177563                 |           |                                                                                                                |

| (87) 國際公開日    | 平成25年11月28日 (2013.11.28)      |           |                                                                                                                |

| 審査請求日         | 平成28年4月25日 (2016.4.25)        |           |                                                                                                                |

| (31) 優先権主張番号  | 61/652,064                    |           |                                                                                                                |

| (32) 優先日      | 平成24年5月25日 (2012.5.25)        |           |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                                                |

| (31) 優先権主張番号  | 13/608,777                    |           |                                                                                                                |

| (32) 優先日      | 平成24年9月10日 (2012.9.10)        |           |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                                                |

最終頁に続く

(54) 【発明の名称】キャリアアグリゲーションのためのカスコード転換スイッチを有する低雑音増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

増幅するための第1の手段がイネーブルにされる場合に、入力無線周波数(RF)信号を増幅するように構成された、前記増幅するための第1の手段と、なお、前記入力RF信号は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む、

増幅するための第2の手段がイネーブルにされる場合に、前記入力RF信号を増幅するように構成された、前記増幅するための第2の手段と、

増幅するための第3の手段がイネーブルにされる場合に、前記入力RF信号を増幅するように構成された、前記増幅するための第3の手段と、なお、前記増幅するための第3の手段は、前記増幅するための第1の手段と並列して結合され、利得トランジスタを前記増幅するための第2の手段と共有する、

前記増幅するための第1の手段に結合された第1の負荷回路と、

前記増幅するための第2の手段に結合された第2の負荷回路と、

を含み、

前記入力RF信号は、シングルエンドの信号を含み、前記第1および第2の負荷回路は、差分出力RF信号を提供する、

装置。

## 【請求項 2】

増幅するための第4の手段がイネーブルにされる場合に、第2の入力RF信号を増幅するように構成された、前記増幅するための第4の手段と、

10

20

増幅するための第 5 の手段がイネーブルにされる場合に、前記第 2 の入力 R F 信号を増幅するように構成された、前記増幅するための第 5 の手段と、

増幅するための第 6 の手段がイネーブルにされる場合に、前記第 2 の入力 R F 信号を増幅するように構成された、前記増幅するための第 6 の手段と、なお、前記増幅するための第 6 の手段は、前記増幅するための第 4 の手段と並列して結合され、増幅手段を前記増幅するための第 5 の手段と共有する、

をさらに含む、請求項 1 に記載の装置。

【請求項 3】

前記増幅するための第 1 の手段は、前記入力 R F 信号を受信するように構成された第 1 の増幅器回路であり、

前記増幅するための第 2 の手段は、前記利得トランジスタを含み、前記入力 R F 信号を受信するように構成された第 2 の増幅器回路であり、

前記増幅するための第 3 の手段は、前記第 1 の増幅器回路の出力と前記第 2 の増幅器回路における前記利得トランジスタとの間に結合されたカスコードトランジスタである、請求項 1 に記載の装置。

【請求項 4】

前記第 2 の増幅器回路の出力と前記第 1 の増幅器回路における利得トランジスタとの間に結合された第 2 のカスコードトランジスタ、

をさらに含む、請求項 3 に記載の装置。

【請求項 5】

前記第 1 の負荷回路に結合され、第 1 の周波数における第 1 の局部発振器 ( L O ) 信号に基づいて前記第 1 の負荷回路からの第 1 の出力 R F 信号のためのダウンコンバージョンを実行するように構成された、第 1 のダウンコンバータ回路と、

前記第 2 の負荷回路に結合され、前記第 1 の周波数とは異なる第 2 の周波数における第 2 の L O 信号に基づいて前記第 2 の負荷回路からの第 2 の出力 R F 信号のためのダウンコンバージョンを実行するように構成された、第 2 のダウンコンバータ回路と、をさらに含む、請求項 1 に記載の装置。

【請求項 6】

前記第 2 の増幅器回路は、前記利得トランジスタのソースと回路接地との間に結合されたインダクタを含む、請求項 3 に記載の装置。

【請求項 7】

前記第 1 および第 2 の増幅器回路のうちの少なくとも 1 つの増幅器回路の出力と入力との間に結合されたフィードバック回路、

をさらに含み、前記フィードバック回路は、抵抗器、キャパシタ、またはトランジスタのうちの少なくとも 1 つを好ましくは含む、請求項 3 に記載の装置。

【請求項 8】

前記第 1 および第 2 の増幅器回路に結合され、前記入力 R F 信号を受信し、減衰された入力 R F 信号を前記第 1 および第 2 の増幅器回路に提供するように構成された、減衰回路、をさらに含む、請求項 3 に記載の装置。

【請求項 9】

前記第 1 の負荷回路は、一次コイルおよび二次コイルを有する変圧器を含み、前記一次コイルは前記第 1 の増幅器回路と電源との間に結合され、前記二次コイルは、前記第 1 の増幅器回路からの増幅された R F 信号が前記一次コイルに適用される場合、差分出力 R F 信号を提供する、請求項 3 に記載の装置。

【請求項 10】

第 1 の動作モードにおいて、前記第 1 の増幅器回路は、前記入力 R F 信号を増幅し、第 1 の増幅された R F 信号を提供するようにイネーブルにされ、前記第 2 の増幅器回路は、前記入力 R F 信号を増幅し、第 2 の増幅された R F 信号を提供するようにイネーブルにされる、請求項 3 に記載の装置。

【請求項 11】

10

20

30

40

50

第2の動作モードにおいて、前記第1の増幅器回路、前記第2の増幅器回路における前記利得トランジスタ、および前記カスコードトランジスタが、前記入力R F信号を増幅し、増幅されたR F信号を提供するようにイネーブルにされる、請求項10に記載の装置。

【請求項12】

第2の入力R F信号を受信するように構成された第3の増幅器回路と、

前記第2の入力R F信号を受信するように構成された第4の増幅器回路と、

前記第3の増幅器回路の出力と前記第4の増幅器回路における利得トランジスタとの間に結合された第2のカスコードトランジスタと、

をさらに含む、請求項3に記載の装置。

【請求項13】

前記第2の増幅器回路の出力と前記第1の増幅器回路における利得トランジスタとの間に結合される第3のカスコードトランジスタと、

前記第4の増幅器回路の出力と前記第3の増幅器回路における利得トランジスタとの間に結合される第4のカスコードトランジスタと、

をさらに含む、請求項12に記載の装置。

【請求項14】

増幅器回路の少なくとも1つの追加のセットと、なお、増幅器回路の各追加のセットは、それぞれの入力R F信号を受信する、

増幅器回路の各追加のセットのための少なくとも1つの追加のカスコードトランジスタと、なお、各追加のカスコードトランジスタは、増幅器回路の前記セットにおける2つの増幅器回路間に結合される、

をさらに含む、請求項3に記載の装置。

【請求項15】

第1の動作モードにおいて、2つの増幅されたR F信号を取得するために、第1および第2の増幅器回路によって入力無線周波数(R F)信号を増幅することと、なお、前記入力R F信号は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む、

第2の動作モードにおいて、単一の増幅されたR F信号を取得するために、前記第1の増幅器回路および第3の増幅器回路によって前記入力R F信号を増幅することと、なお、前記第2および第3の増幅器回路は、利得トランジスタを共有し、ここにおいて、第1の負荷回路は前記第1の増幅器回路に結合され、第2の負荷回路は前記第2の増幅器回路に結合され、前記入力R F信号は、シングルエンドの信号を含み、前記第1および第2の負荷回路は、差分出力R F信号を提供する、

を含む、方法。

【発明の詳細な説明】

【技術分野】

【0001】

[35U.S.C. § 119の下の優先権主張]

[0001] 本特許出願は、2012年5月25日に出願され、この譲受人に譲渡され、引用によりここに明確に組み込まれる、「キャリアアグリゲーションのための低雑音増幅器」(LOW NOISE AMPLIFIERS FOR CARRIER AGGREGATION)と題する、米国仮出願番号第61/652,064号の優先権を主張する。

【0002】

[0002] 本開示は、一般的に電子工学(electronics)に関し、より詳細には、低雑音増幅器(LNA)(low noise amplifiers(LNAs))に関する。

【背景技術】

【0003】

[0003] 無線通信システムにおける無線デバイス(例えば、セルラー電話またはスマートフォン)は、双方向通信のためにデータを送信し、受信することができる。無線デバイスは、データ送信のための送信機およびデータ受信のための受信機を含み得る。データ送

10

20

30

40

50

信の場合には、送信機は、変調された無線周波数（RF）信号を取得するために、データを用いてRFキャリア信号を変調し、適切な出力電力レベルを持つ増幅されたRF信号を取得するために変調されたRF信号を増幅し、アンテナを介して基地局に増幅されたRF信号を送信し得る。データ受信の場合には、受信機はアンテナを介して受信されたRF信号を取得し得、基地局によって送信されたデータを回復するために受信されたRF信号を増幅および処理し得る。

## 【0004】

[0004] 無線デバイスは、複数のキャリア上での同時の動作である、キャリアアグリゲーション（carrier aggregation）をサポートし得る。キャリアは、通信に使用される周波数の範囲を指し得、特定の特徴と関連付けられ得る。例えば、キャリアは、キャリア上の動作を説明するシステム情報と関連付けられ得る。キャリアはまた、コンポーネントキャリア（CC）、周波数チャネル、セル等とも称され得る。キャリアアグリゲーションを無線デバイスによって効率的にサポートすることが望ましい。

## 【図面の簡単な説明】

## 【0005】

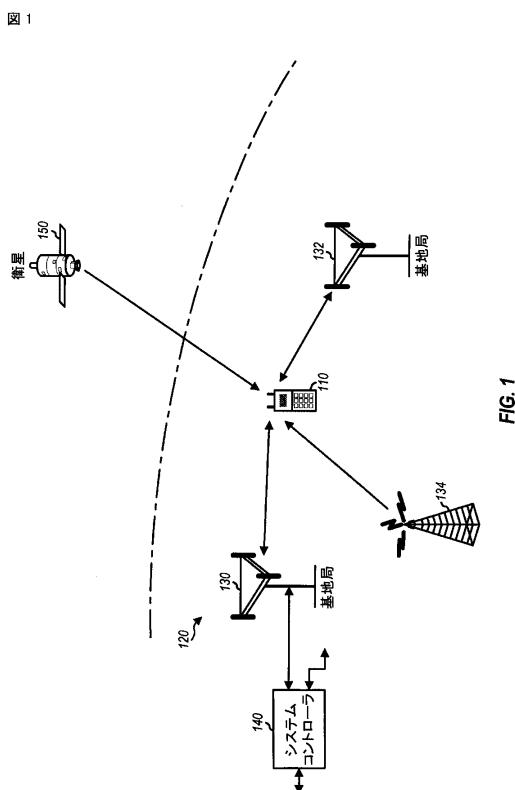

【図1】図1は、無線システムと通信する無線デバイスを示す図である。

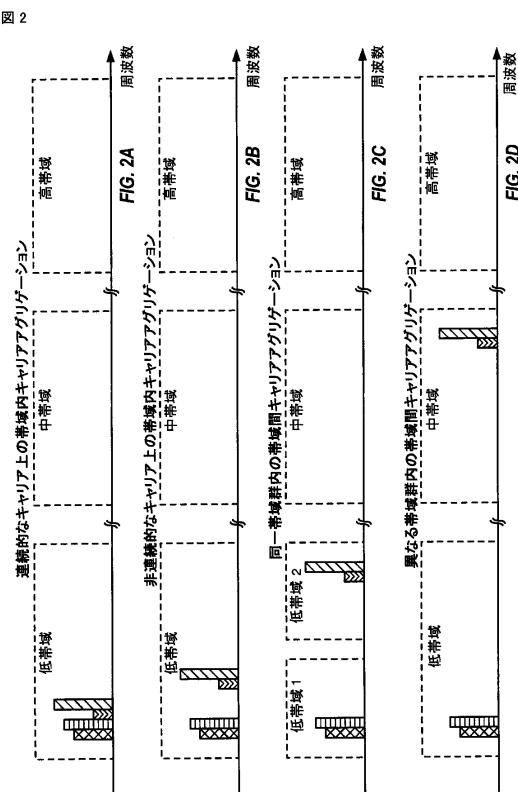

【図2】図2Aは、キャリアアグリゲーション（CA）の1つの例を示す図である。

## 【0006】

図2Bは、キャリアアグリゲーション（CA）の1つの例を示す図である。

## 【0007】

図2Cは、キャリアアグリゲーション（CA）の1つの例を示す図である。

## 【0008】

図2Dは、キャリアアグリゲーション（CA）の1つの例を示す図である。

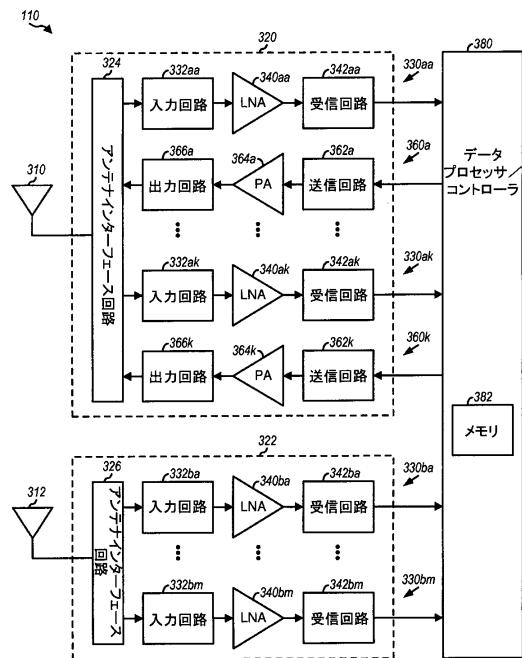

【図3】図3は、図1における無線デバイスのブロック図を示す。

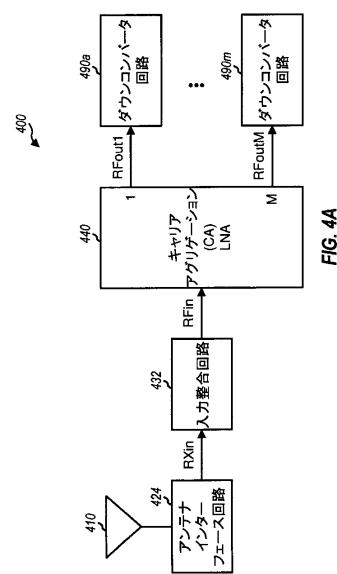

【図4A】図4Aは、帯域内CA（intra-band CA）をサポートする受信機を示す図である。

【図4B】図4Bは、帯域内CAをサポートする受信機を示す図である。

【図5A】図5Aは、帯域内CAおよび帯域間CA（inter-band CA）をサポートする受信機を示す図である。

【図5B】図5Bは、帯域内CAおよび帯域間CAをサポートする受信機を示す図である。

【図6A】図6Aは、インダクティブデジエネレーション（inductive degeneration）およびカスコード転換スイッチ（cascode divert switch）を有するLNAの例示的な設計を示す図である。

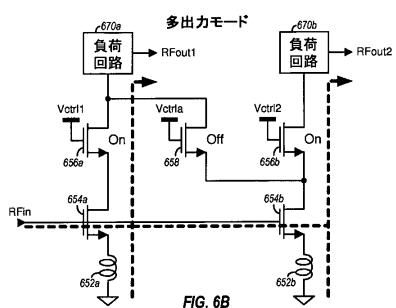

【図6B】図6Bは、インダクティブデジエネレーションおよびカスコード転換スイッチを有するLNAの例示的な設計を示す図である。

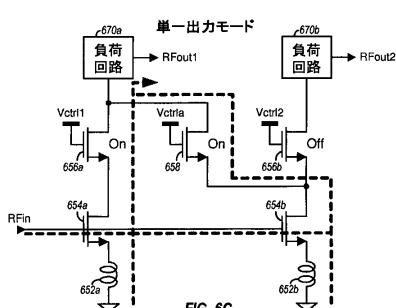

【図6C】図6Cは、インダクティブデジエネレーションおよびカスコード転換スイッチを有するLNAの例示的な設計を示す図である。

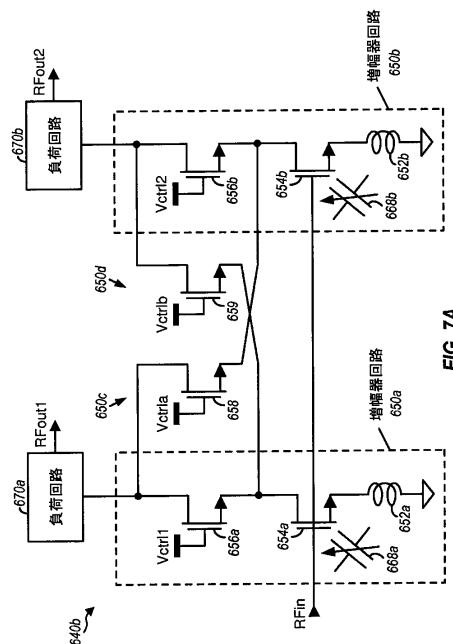

【図7A】図7Aは、カスコード転換スイッチを有するLNAの追加の例示的な設計を示す図である。

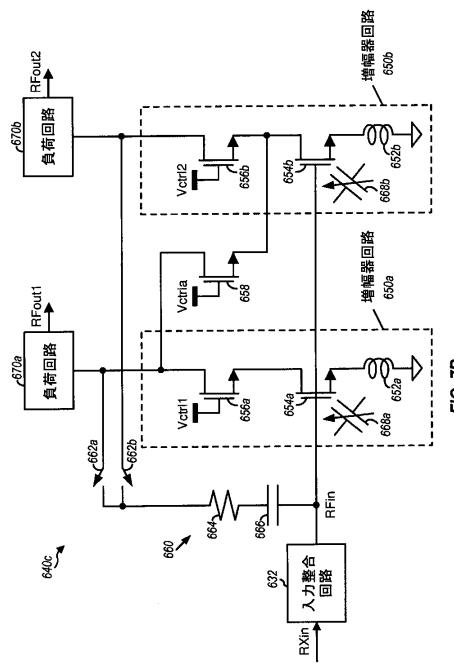

【図7B】図7Bは、カスコード転換スイッチを有するLNAの追加の例示的な設計を示す図である。

【図7C】図7Cは、カスコード転換スイッチを有するLNAの追加の例示的な設計を示す図である。

【図8A】図8Aは、カスコード転換スイッチを有する多入力多出力（MIMO）LNAの例示的な設計を示す図である。

【図8B】図8Bは、カスコード転換スイッチを有する多入力多出力（MIMO）LNAの例示的な設計を示す図である。

【図8C】図8Cは、カスコード転換スイッチを有する多入力多出力（MIMO）LNAの例示的な設計を示す図である。

10

20

30

40

50

【図9】図9は、信号増幅を実行するための処理を示す図である。

【詳細な説明】

【0009】

[0014] 以下に述べられる詳細な説明は、本開示の例示的な設計の説明を意図するものであり、本開示が実現され得る、唯一の設計を表すことを意図したものではない。「例示的」という用語は、本明細書において、「例、事例、または例示として提供する」という意味で使用される。「例示的」なものとしてここに説明される任意の設計は、必ずしも、他の設計よりも好ましい、または利点を有するものと解釈されるべきではない。詳細な説明は、本開示の例示的な設計の完全な理解を提供することを目的とした特定の詳細を含む。ここにおいて説明される例示的な設計が、これらの具体的な詳細なしに実現され得ることを当業者は理解するだろう。いくつかの事例では、周知の構造およびデバイスが、ここに提示される例示的な設計の新規性を曖昧にすることを避けるために、ブロック図形式で示される。

10

【0010】

[0015] キャリアアグリゲーションをサポートするLNAがここに開示される。これらのLNAは、無線通信デバイスのような様々なタイプの電子デバイスのために使用されることができる。

【0011】

[0016] 図1は、無線通信システム120と通信する無線デバイス100を示す。無線システム120は、ロングタームエボリューション(LTE)システム、符号分割多元接続(CDMA)システム、移動通信のための全地球システム(GSM(登録商標))システム、無線ローカルエリアネットワーク(WLAN)システム、またはいくつかの他の無線システムであることができる。CDMAシステムは、広帯域CDMA(WCDMA(登録商標))、時分割同期CDMA(TD-SCDMA)、cdma2000、またはCDMAのいくつかの他のバージョンを実現し得る。簡潔さのために、図1は、2つの基地局130および132、および1つのシステムコントローラ140を含む無線システム120を示す。一般に、無線システムは、任意の数の基地局および任意のネットワークエンティティのセットを含み得る。

20

【0012】

[0017] 無線デバイス110はまた、ユーザ機器(UE)、移動局、端末、アクセス端末、加入者ユニット、局等とも称され得る。無線デバイス110は、セルラー電話、スマートフォン、タブレット、無線モデム、携帯情報端末(PDA)、ハンドヘルドデバイス、ラップトップコンピュータ、スマートブック、ネットブック、コードレス電話、無線ローカルループ局、Bluetooth(登録商標)デバイス等であり得る。無線デバイス110は、無線システム120と通信することが可能であり得る。無線デバイス110はまた、放送局(例えば、放送局134)からの信号、1つ以上のグローバルナビゲーション衛星システム(GNSS)における衛星(例えば、衛星150)からの信号等を受信することができあり得る。無線デバイス110は、LTE、cdma2000、WCDMA、TD-SCDMA、GSM、802.11等のような無線通信のための1つ以上の無線技術をサポートし得る。

30

【0013】

[0018] 無線デバイス110は、複数のキャリア上での動作である、キャリアアグリゲーションをサポートし得る。キャリアアグリゲーションは、マルチキャリア動作とも称され得る。無線デバイス110は、698から960メガヘルツ(MHz)の低帯域(low-band)、1475から2170MHzの中帯域(mid-band)、および/または2300から2690MHz、および3400から3800MHzの高帯域(high-band)において動作することができる。低帯域、中帯域、および高帯域は、3つの帯域の群(または帯域群(band groups))を指し、各帯域群は、多数の周波数帯域(または、単に「帯域」)を含む。各帯域は、200MHzまでカバーすることができ、1つ以上のキャリアを含むことができる。各キャリアは、LTEにおいて20MHzまでカバーすることができる。

40

50

L T E リリース 11 (LTE Release 11) は、35 の帯域をサポートし、それらは L T E / U M T S 帯域と称され、3 G P P T S 36.101 に記載されている。無線デバイス 110 は、L T E リリース 11 において 1 つまたは 2 つの帯域における 5 つまでのキャリアによって構成されることができる。

【 0 0 1 4 】

[0019] 一般的に、キャリアアグリゲーション (C A) は、帯域内 C A および帯域間 C A の 2 種類に分類されることがある。帯域内 C A は、同一の帯域内の複数のキャリア上の動作を指す。帯域間 C A は、異なる帯域における複数のキャリア上の動作を指す。

【 0 0 1 5 】

[0020] 図 2 A は、連続的な (contiguous) 帯域内 C A の例を示す。図 2 A に示される例において、無線デバイス 110 は、低帯域における帯域である、同一帯域における 4 つの連続的なキャリア (contiguous carriers) によって構成される。無線デバイス 110 は、同一帯域内の複数の連続的なキャリア上で伝送を送信するおよび / または受信することができる。

【 0 0 1 6 】

[0021] 図 2 B は、非連続的な (non-contiguous) 帯域内 C A の例を示す。図 2 B に示される例では、無線デバイス 110 は、低帯域における帯域である、同一帯域における 4 つの非連続的なキャリア (non-contiguous carriers) によって構成される。キャリアは、5 M H z、10 M H z、またはいくつかの他の量によって分離される (separated) ことができる。無線デバイス 110 は、同一帯域内の複数の非連続的なキャリア上で伝送を送信および / または受信することができる。

【 0 0 1 7 】

[0022] 図 2 C は、同一帯域群における帯域間 C A の例を示す。図 2 C に示される例では、無線デバイス 110 は、低帯域である、同一帯域群における 2 つの帯域における 4 つのキャリアによって構成される。無線デバイス 110 は、同一の帯域群における異なる帯域 (例えば、図 2 C における低帯域) における複数のキャリア上で伝送を送信および / または受信することができる。

【 0 0 1 8 】

[0023] 図 2 D は、異なる帯域群における帯域間 C A の例を示す。図 2 D に示される例では、無線デバイス 110 は、異なる帯域群における 2 つの帯域における 4 つのキャリアによって構成され、それは低帯域における 1 つの帯域における 2 つのキャリア、および中帯域における別の帯域における 2 つの追加のキャリアを含む。無線デバイス 110 は、異なる帯域群における異なる帯域 (例えば、図 2 D における低帯域および中帯域) における複数のキャリア上で伝送を送信および / または受信することができる。

【 0 0 1 9 】

[0024] 図 2 A から図 2 D は、キャリアアグリゲーションの 4 つの例を示す。キャリアアグリゲーションは、帯域および帯域群の他の組み合わせに対してサポートされることもできる。例えば、キャリアアグリゲーションは、低帯域および高帯域、中帯域および高帯域、高帯域および高帯域等に対してサポートされることがある。

【 0 0 2 0 】

[0025] 図 3 は、図 1 における無線デバイス 110 の例示的な設計のブロック図を示す。例示的な設計において、無線デバイス 110 は、プライマリー・アンテナ (a primary antenna) 310 に結合されたトランシーバ 320、セカンダリー・アンテナ (a secondary antenna) 312 に結合された受信機 322、およびデータプロセッサ / コントローラ 380 を含む。トランシーバ 320 は、複数の帯域、キャリアアグリゲーション、複数の無線技術等をサポートするための、複数の (K 個の) 受信機 330 a a から 330 a k、および複数の (K 個の) 送信機 360 a から 360 k を含む。受信機 322 は、複数の帯域、キャリアアグリゲーション、複数の無線技術、受信ダイバーシチ、複数の送信アンテナから複数の受信アンテナへの M I M O 送信等をサポートするための複数の (M 個の) 受信機 330 b a から 330 b m を含む。

10

20

30

40

50

## 【0021】

[0026] 図3に示される例示的な設計において、各受信機330は、入力回路332、LNA340、および受信回路342を含む。データ受信のために、アンテナ310は基地局および/または他の送信機局から信号を受信し、受信されたRF信号を提供し、それはアンテナインターフェース回路324を通ってルーティングされ、選択された受信機に提供される。アンテナインターフェース回路324は、スイッチ、デュプレクサ、送信フィルタ、受信フィルタ等を含むことができる。以下の説明では、受信機330aaが選択された受信機であると仮定する。受信機330aa内で、受信されたRF信号は、入力回路332aaを通過し、それはLNA340aaに入力RF信号を提供する。入力回路332aaは、整合回路、受信フィルタ等を含むことができる。LNA340aaは、入力RF信号を増幅し、出力RF信号を提供する。受信回路342aaは、出力RF信号を増幅、フィルタリング、およびRFからベースバンドにダウンコンバートし、アナログ入力信号をデータプロセッサ380に提供する。受信回路332aaは、ミキサ、フィルタ、増幅器、整合回路、発振器、局部発振器(LO)発生器、位相ロックループ(PLL)等を含むことができる。トランシーバ320における各残りの受信機330、および、受信機322における各受信機330は、トランシーバ320における受信機330aaと同様の方式で動作することができる。10

## 【0022】

[0027] 図3に示される例示的な設計では、各送信機360は、送信回路362、電力増幅器(PA)364、および出力回路366を含む。データ送信のために、データプロセッサ380は、データが送信されるように処理(例えば、符号化および変調)し、アナログ出力信号を選択された送信機に提供する。以下の説明では、送信機360aが選択された送信機であると仮定する。送信機360a内で、送信回路362aは、アナログ出力信号を増幅、フィルタリング、およびベースバンドからRFにアップコンバートし、変調されたRF信号を提供する。送信回路362aは、増幅器、フィルタ、ミキサ、整合回路、発振器、LO発生器、PLL等を含むことができる。PA364aは、変調されたRF信号を受信し、増幅し、適切な出力電力レベルを有する送信RF信号を提供する。送信RF信号は、出力回路366aを通過し、アンテナインターフェース回路324を通ってルーティングされ、アンテナ310を介して送信される。出力回路366aは、整合回路、送信フィルタ、方向性結合器(a directional coupler)等を含むことができる。20

## 【0023】

[0028] 図3は、受信機330および送信機360の例示的な設計を示す。受信機および送信機は、フィルタ、整合回路等のような、図3に示されない他の回路も含み得る。トランシーバ320および受信機322のすべてまたは一部は、1つ以上のアナログ集積回路(IC)、RFのIC(RFIC)、混合信号IC等の上で実現され得る。例えば、LNA340、受信回路342、および送信回路362は、1つのモジュール上で実現することができ、それはRFIC等であり得る。アンテナインターフェース回路324および326、入力回路332、出力回路366、およびPA364は、別のモジュール上で実現することができ、それはハイブリッドモジュール等であり得る。トランシーバ320および受信機322における回路も、他の方式で実現することができる。30

## 【0024】

[0029] データプロセッサ/コントローラ380は、無線デバイス110のために様々な機能を実行し得る。例えば、データプロセッサ380は、受信機330を介して受信されるデータ、および送信機360を介して送信されるデータの処理を実行することができる。コントローラ380は、アンテナインターフェース回路324および326、入力回路332、LNA340、受信回路342、送信回路362、PA364、出力回路366、またはそれらの組み合わせの動作を制御することができる。メモリ382は、データプロセッサ/コントローラ380のためのプログラムコードおよびデータを記憶し得る。データプロセッサ/コントローラ380は、1つ以上の特定用途向け集積回路(ASIC)および/または他のIC上で実現され得る。40

## 【0025】

[0030] 無線デバイス 110 は、キャリアアグリゲーションのための異なる周波数における複数のキャリア上で 1 つ以上の基地局 / セルから伝送を受信することができる。帯域内 CA では、伝送は同一帯域における異なるキャリア上で送信される。帯域間 CA では、伝送は、異なる帯域における複数のキャリア上で送信される。

## 【0026】

[0031] 図 4 A は、非 CA (no CA)、および帯域内 CA をサポートする、CA 可能な (CA-capable) LNA 440 を有する受信機 400 の例示的な設計のブロック図を示す。CA LNA 440 は、図 3 における 1 つ以上の LNA 340 のために使用されることができる。CA LNA 440 は、単一の入力および複数の (M 個の) 出力を含み、ここで  $M > 1$  である。

10

## 【0027】

[0032] 受信機 400 では、アンテナ 410 は、1 つ以上のキャリア上で送信された 1 つ以上の伝送を含むダウンリンク信号を受信し、受信された RF 信号をアンテナインターフェース回路 424 に提供する。アンテナインターフェース回路 424 は、受信された RF 信号をフィルタリングおよびルーティングし、受信機入力信号、RXin を提供する。入力整合回路 432 は、RXin 信号を受信し、入力 RF 信号、RFin を、CA LNA 440 に提供する。整合回路 432 は、対象の帯域 (a band of interest) のために、CA LNA 440 と、アンテナインターフェース回路 424 またはアンテナ 410 のいずれかとの間で、インピーダンスおよび / または電力整合を実行する。整合回路 432 は、図 3 における入力回路 332 のうちの 1 つの一部であり得る。

20

## 【0028】

[0033] CA LNA 440 は、入力 RF 信号を受信して増幅し、(i) 1 つのセットのキャリア上の非 CA、または CA のいずれかのための 1 つの LNA 出力によって (via) 1 つの出力 RF 信号を、または (ii) M 個までのセットのキャリア上で帯域内 CA のための M 個までの LNA 出力によって、M 個までの出力 RF 信号、RFout1 から RFoutM を、提供する。M 個のダウンコンバータ回路 490a から 490m は、M 個の LNA 出力に結合される。各ダウンコンバータ回路 490 は、イネーブルにされる場合、対象の (of interest) 1 つ以上のキャリア上の 1 つ以上の伝送が RF からベースバンドにダウンコンバートされるように、関連する出力 RF 信号をダウンコンバートする。

30

## 【0029】

[0034] 図 4 A における CA LNA 440 のような CA LNA は、任意の所与の時間 (moment) において単一出力モードまたは多出力モード (a single-output mode or a multi-output mode) で動作することができる。単一出力モードにおいて、CA LNA は、1 入力 1 出力 ( $1 \times 1$ ) 構成で動作し、1 つのセットのキャリア上の 1 つ以上の伝送を含む 1 つの入力 RF 信号を受信し、1 つの出力 RF 信号を 1 つのダウンコンバータ回路に提供する。単一出力モードが、キャリアアグリゲーションなしで単一のキャリア上に送信された伝送を受信するために使用され得る。単一出力モードは、キャリアアグリゲーションによって複数のキャリア (例えば、連続的なキャリア) 上に送信された伝送を受信するためにも使用され得る。このケースでは、全てのキャリア上の伝送が、単一の周波数において単一の LO 信号によってダウンコンバートされ得る。多出力モードにおいて、CA LNA は、 $1 \times M$  構成で動作し、M 個のセットのキャリア上の複数の伝送を含む 1 つの入力 RF 信号を受信し、M 個の出力 RF 信号を M 個のダウンコンバータ回路に提供し、キャリアのセットごとに 1 つの出力 RF 信号を提供し (one output RF signal for each set of carriers)、ここで、 $M > 1$  である。キャリアの各セットは、1 つの帯域における 1 つ以上のキャリアを含むことができる。

40

## 【0030】

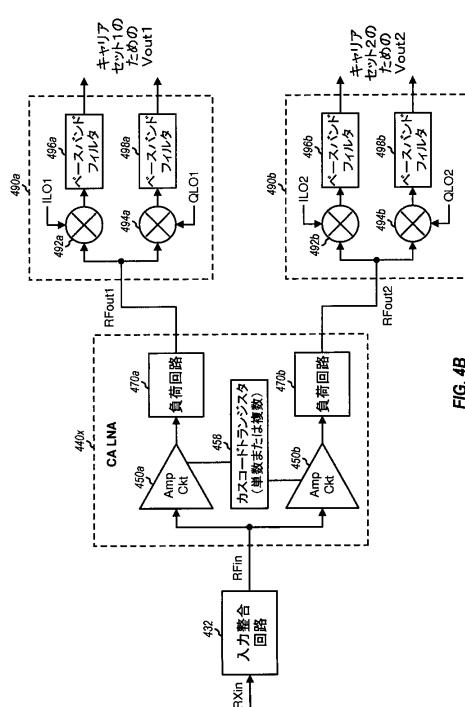

[0035] 図 4 B は、1 つの帯域において 2 つまでのセットのキャリアの上の非 CA、および帯域内 CA をサポートする CA LNA 440x の例示的な設計のブロック図を示す。CA LNA 440x は、図 4 A における CA LNA 440 の 1 つの例示的な設計であ

50

る。

【0031】

[0036] 図4Bに示される例示的な設計では、C A L N A 4 4 0 xは、2つのL N A出力のために、2つの増幅器回路(A m p C k t)4 5 0 aおよび4 5 0 b、1つ以上の転換カスコードトランジスタ(divert cascode transistor)4 5 8、および2つの負荷回路(load circuit)4 7 0 aおよび4 7 0 bを含む。増幅器回路は、増幅段(an amplifier stage)、入力段(an input stage)、利得回路等とも呼ばれ得る。入力R F信号は、増幅器回路4 5 0 aおよび4 5 0 bの両方に提供される。各増幅器回路4 5 0は、その増幅器回路がイネーブルにされる場合、入力R F信号を増幅し、対応する増幅されたR F信号を提供する。以下に説明されるように、転換カスコードトランジスタ(単数または複数)4 5 8のうちの1つは、増幅器回路4 5 0 bから増幅器回路4 5 0 aに、またはその逆に、R F電流を転換する(divert)ようにイネーブルにされ得る。負荷回路4 7 0 aおよび4 7 0 bは、それぞれ増幅器回路4 5 0 aおよび4 5 0 bから、増幅されたR F信号を受信し、出力R F信号をそれぞれダウンコンバータ回路4 9 0 aおよび4 9 0 bに提供する。

【0032】

[0037] 図4Bに示される例示的な設計では、各ダウンコンバータ回路4 9 0は、それぞれ2つのベースバンドフィルタ4 9 6および4 9 8に結合された2つのミキサ4 9 2および4 9 4を含む。ダウンコンバータ回路4 9 0 a内で、ミキサ4 9 2 aは、負荷回路4 7 0 aからの第1の出力R F信号、R F o u t 1を、および、第1のセットのキャリアのための第1の混合周波数で(at a first mixing frequency)、同相(inphase)LO信号、I L O 1を、受信する。ミキサ4 9 2 aは、I L O 1によって第1の出力R F信号をダウンコンバートし、同相(I)のダウンコンバートされた信号(an inphase(I) downconverted signal)を提供し得る。ミキサ4 9 4 aは、第1の混合周波数で、直角位相(quadrature)LO信号、Q L O 1を、および負荷回路4 7 0 aからの第1の出力R F信号を、受信する。ミキサ4 9 4 aは、Q L O 1信号を用いて第1の出力R F信号をダウンコンバートし、直角位相(Q)のダウンコンバートされた信号(a quadrature(Q) downconverted signal)を提供する。フィルタ4 9 6 aおよび4 9 8 aは、それぞれミキサ4 9 2 aおよび4 9 4 aからIおよびQのダウンコンバートされた信号を受信し、フィルタリングし、第1のセットのキャリアのためのIおよびQのベースバンド信号、V o u t 1を提供する。

【0033】

[0038] ダウンコンバータ4 9 0 aおよび4 9 0 bは、2個までのセットのキャリア上で伝送を受信するようにイネーブルにされ得る。各ダウンコンバータ4 9 0は、C A L N A 4 4 0 xからそれぞれの出力R F信号を受信し、その出力R F信号を適切な混合周波数でそれぞれのLO信号を用いてダウンコンバートし、1つのセットのキャリアのためのIおよびQのベースバンド信号を提供する。ダウンコンバータ4 9 0 aおよび4 9 0 bは、2つのセットのキャリアのための異なる混合周波数を用いてダウンコンバージョンを実行し得る。

【0034】

[0039] 図4Bは、ダウンコンバータ回路4 9 0の例示的な設計を示す。ダウンコンバータ回路はまた、異なるおよび/または追加の回路を含み得る。例えば、ダウンコンバータ回路は、ミキサの前に、またはミキサとフィルタとの間に、またはフィルタの後に結合された増幅器を含み得る。

【0035】

[0040] 図4Bは、2つのL N A出力のための2つの増幅器回路4 5 0および2つの負荷回路4 7 0を有する、C A L N A 4 4 0の例示的な設計を示す。C A L N Aはまた、2つより多いL N A出力のための2つより多い増幅器回路および/または2つより多い負荷回路を含み得る。C A L N Aは、任意の数の転換カスコードトランジスタを含み得る。各転換カスコードトランジスタは、2つの増幅器回路の間に結合され得、これらの增

幅器回路の間の R F 電流を転換し得る。

【 0 0 3 6 】

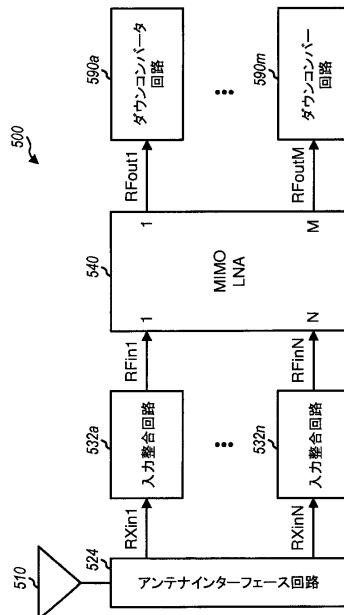

[0041] 図 5 A は、非 C A、帯域内 C A、および帯域間 C A をサポートする M I M O L N A 5 4 0 を有する受信機 5 0 0 の例示的な設計のブロック図を示す。 M I M O L N A 5 4 0 は、図 3 における 1 つ以上の L N A 3 4 0 のために使用されることができる。 M I M O L N A 5 4 0 は、複数の ( N 個の ) 入力および複数の ( M 個の ) 出力を含み、 N × M M I M O L N A と称され得、ここで N > 1 、 M > 1 である。

【 0 0 3 7 】

[0042] 受信機 5 0 0 において、アンテナ 5 1 0 は、同一の帯域または異なる帯域で、 1 つ以上のキャリア上で送信された 1 つ以上の伝送を含むダウンリンク信号を受信する。 アンテナ 5 1 0 は、受信された R F 信号をアンテナインターフェース回路 5 2 4 に提供する。 アンテナインターフェース回路 5 2 4 は、受信された R F 信号をフィルタリングしてルーティングし、 N 個までの受信機入力信号、 R X i n 1 から R X i n N を、それぞれ、 N 個までの入力整合回路 5 3 2 a から 5 3 2 n に提供する。 整合回路 5 3 2 a から 5 3 2 n は、 N 個までの入力 R F 信号、 R F i n 1 から R F i n N を、それぞれ、 M I M O L N A 5 4 0 に提供する。 整合回路 5 3 2 a から 5 3 2 n は、図 3 における 1 つ以上の入力回路 3 3 2 の一部であることができる。 各整合回路 5 3 2 は、 M I M O L N A 5 4 0 と、対象の 1 つ以上の帯域のためのアンテナインターフェース回路 5 2 4 またはアンテナ 5 1 0 のいずれかとの間の、インピーダンスおよび / または電力整合を実行する。 N 個の整合回路 5 3 2 a から 5 4 2 n は、異なる帯域のために設計されることができる。

【 0 0 3 8 】

[0043] M I M O L N A 5 4 0 は、 N 個までの入力 R F 信号を受信し、 ( i ) 非 C A 、または帯域内 C A のための 1 つの入力 R F 信号を、または ( i ) 帯域間 C A のための N 個までの入力 R F 信号を、増幅する。 M I M O L N A 5 4 0 は、 ( i ) 1 つのセットのキャリア上の非 C A 、または C A のいずれかのための、 1 つの L N A 出力による 1 つの出力 R F 信号を、または ( i i ) 帯域内 C A または帯域間 C A のために、 M 個までの L N A 出力によって、 M 個までの出力 R F 信号、 R F o u t 1 から R F o u t M を、提供する。 M 個のダウンコンバータ回路 5 9 0 a から 5 9 0 m は、 M 個の L N A 出力に結合される。 各ダウンコンバータ回路 5 9 0 は、イネーブルにされる場合、対象の 1 つ以上のキャリア上で 1 つ以上の伝送が R F からベースバンドにダウンコンバートされるように、関連する出力 R F 信号をダウンコンバートする。

【 0 0 3 9 】

[0044] 図 5 A における M I M O L N A 5 4 0 のような M I M O L N A は、任意の所与の時間において、単一出力モード、帯域内 C A モード、または帯域間 C A モードで動作することができる。 単一出力モードにおいて、 M I M O L N A は、 1 × 1 構成で動作し、 1 つのセットのキャリア上の 1 つ以上の伝送を含む 1 つの入力 R F 信号を受信し、 1 つの出力 R F 信号を 1 つのダウンコンバータ回路に提供する。 帯域内 C A モードにおいて、 M I M O L N A は、 1 × M 構成で動作し、同一帯域における M 個のセットのキャリア上の伝送を含む 1 つの入力 R F 信号を受信し、 M 個の出力 R F 信号を M 個のダウンコンバータ回路に提供し、キャリアのセットごとに 1 つの出力 R F 信号を提供し、ここで M > 1 である。 帯域間 C A モードにおいて、 M I M O L N A は、 N × M 構成で動作し、 N 個までの異なる帯域における M 個のセットのキャリア上の伝送を含む N 個の入力 R F 信号を受信し、 M 個の出力 R F 信号を M 個の負荷回路に提供し、ここで M > 1 および N > 1 である。 N 個の入力 R F 信号は、 N 個までの異なる帯域に対応し得る。

【 0 0 4 0 】

[0045] 図 5 A における M I M O L N A 5 4 0 のような、 M I M O L N A は、異なる周波数において複数のキャリア上で伝送を受信するために使用され得る。 M I M O L N A は、対象の ( of interest ) 異なるキャリアまたは異なるセットのキャリアのための複数の出力 R F 信号を提供する複数の出力を含み得る。 M I M O L N A は、複数の送信アンテナから複数の受信アンテナに送信される M I M O 伝送を受信するために使用される L

10

20

30

40

50

N A とは異なる。MIMO 伝送のための LNA は、典型的に (i) 1 つの受信アンテナから 1 つの入力 RF 信号を受信する 1 つの入力、および (ii) 1 つの出力 RF 信号を提供する 1 つの出力を有する。MIMO LNA の複数の出力はしたがって、周波数次元 (frequency dimension) をカバーする一方で、MIMO 伝送のために使用される LNA の出力は、空間次元 (spatial dimension) をカバーする。

#### 【0041】

[0046] 図 5 B は、非 CA、帯域内 CA、および帯域間 CA をサポートする MIMO LNA 540x の例示的な設計のブロック図を示す。MIMO LNA 540x は、1 つ以上の帯域における複数のセットのキャリア上の CA をサポートすることができる。キャリアの各セットは、1 つの帯域における 1 つ以上のキャリアを含むことができる。MIMO LNA 540x は、図 5 A における MIMO LNA 540 の 1 つの例示的な設計である。

#### 【0042】

[0047] N 個の入力整合回路 532a から 532n は、N 個の受信機入力信号、RXin1 から RXinN を受信し、N 個の入力 RF 信号、RFin1 から RFinN を提供する。整合回路 532a から 532n は、(i) 1 つのアンテナから同一の受信機入力信号を、または (ii) 1 つ以上のアンテナから異なる受信機入力信号を受信し得る。したがって、RXin1 から RXinN 信号は、同一の信号または異なる信号であり得る。各整合回路 532 は、対象の 1 つ以上の帯域のための入力整合を実行する。例えば、RXin1 から RXinN 信号は、1 つのアンテナからの同一の信号であり得、整合回路 532a から 532n は、異なる帯域のための入力整合を実行し得る。別の例では、RXin1 から RXinN 信号は、異なるアンテナからの異なる信号であり得、整合回路 532a から 532n は、同一の帯域または異なる帯域のための入力整合を実行し得る。

#### 【0043】

[0048] 図 5 B に示される例示的な設計では、MIMO LNA 540x は、N 個の LNA 入力のための N 個の増幅器 (Amp) ブロック 542a から 542n、および 2 つの LNA 出力のための 2 つの負荷回路 570a および 570b を含む。各増幅器ブロック 542 は、2 つの増幅器回路 550 および 560、および 1 つ以上の転換カスコードトランジスタ 558 を含む。N 個の入力 RF 信号、RXin1 から RXinN は、それぞれ、N 個の増幅器ブロック 542a から 542n に提供される。L 個の増幅器ブロック 542 は、K 個のセットのキャリア上の伝送を受信するようにイネーブルにされることができ、ここで、

#### 【数 1】

$$1 \leq L \leq N$$

#### 【0044】

および

#### 【数 2】

$$1 \leq K \leq 2$$

#### 【0045】

である。N - L の残りの増幅器ブロック 542 は、ディスエーブルにされ得る。各イネーブルにされた増幅器ブロック 542 は、その入力 RF 信号を受信して増幅し、1 つまたは 2 つの増幅された RF 信号を提供する。K 個の負荷回路 570 は、全てのイネーブルにされた増幅器ブロック 642 から K 個の増幅された RF 信号を受信し、K 個の出力 RF 信号を、K 個の負荷回路に結合された K 個のダウンコンバータ回路 590 に提供する。

10

20

30

40

50

## 【0046】

[0049] 図5Bに示される例示的な設計において、各ダウンコンバータ回路590は、2つのベースバンドフィルタ596および598にそれぞれ結合された2つのミキサ592および594を含む。ミキサ592および594、およびフィルタ596および598は、図4Bにおけるミキサ492および494、およびフィルタ496および498に関して上述されたように、結合され、動作する。K個までのダウンコンバータ590が、K個までのセットのキャリア上の伝送を受信するために選択されることができる。各ダウンコンバータ590は、LNA540からのその出力RF信号を処理しダウンコンバートし、異なるセットのキャリアのためのIおよびQのベースバンド信号を提供し得る。

## 【0047】

[0050] 図4AにおけるCA LNA 440は、様々な回路アーキテクチャによって実現されることができる。CA LNA 440のいくつかの例示的な設計が、以下に説明される。CA LNA 440はまた、様々なタイプのトランジスタによって実現され得る。N形金属酸化膜半導体(NMOS)トランジスタによって実現されるCA LNA 440のいくつかの例示的な設計が、以下に説明される。

## 【0048】

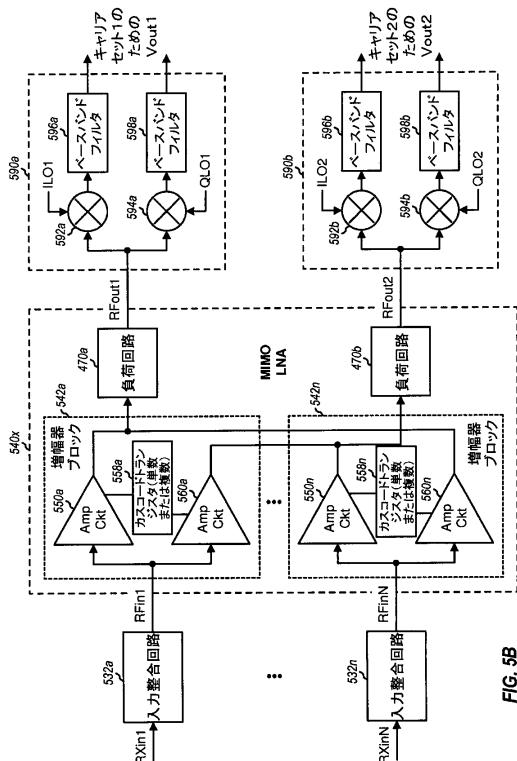

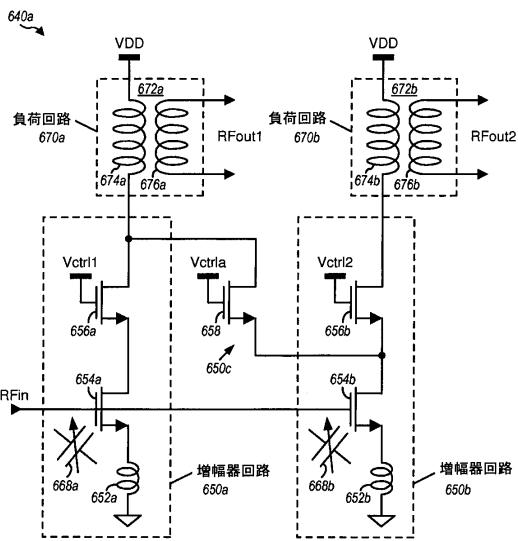

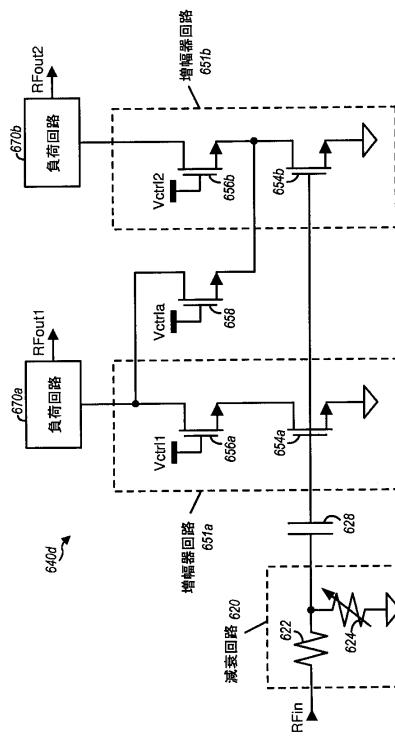

[0051] 図6Aは、インダクティブデジエネレイションおよびカスコード転換スイッチを有するCA LNA 640aの例示的な設計の回路図を示す。CA LNA 640aは、図4AにおけるCA LNA 440の1つの例示的な設計である。CA LNA 640aは、2つの増幅器回路650aおよび650b、転換カスコードトランジスタ658、および2つの負荷回路670aおよび670bを含む。CA LNA 640aは、入力RF信号を受信し、それは1つまたは2つのセットのキャリア上の伝送を含み得、各セットは1つ以上のキャリアを含む。

## 【0049】

[0052] 図6Aに示される例示的な設計において、各増幅器回路650は、ソースデジエネレイションインダクタ(a source degeneration inductor)652、利得トランジスタ(a gain transistor)654、およびカスコードトランジスタ(a cascode transistor)656を含む。増幅器回路650a内で、利得トランジスタ654aは、そのゲートが入力RF信号を受信し、そのソースがインダクタ652aの一端に結合される。インダクタ652aのもう一端は、回路接地に結合される。カスコードトランジスタ656aは、そのソースが利得トランジスタ654aのドレインに結合され、そのゲートが第1の制御信号、Vctr11を受信し、そのドレインが負荷回路670aに結合される。増幅器回路650bは、ソースデジエネレイションインダクタ652b、利得トランジスタ654b、およびカスコードトランジスタ656bを含み、それらは増幅器回路650aにおけるインダクタ652aおよびトランジスタ654aおよび656aと同様の方式で結合される。転換カスコードトランジスタ658は、そのソースが利得トランジスタ654bのドレインに結合され、そのゲートが第3の制御信号、Vctr1aを受信し、そのドレインが負荷回路670aに結合される。利得トランジスタ654b、カスコードトランジスタ658、およびインダクタ652bは、増幅器回路650aと並列に結合された増幅器回路650cの一部であると考えられ得る。利得トランジスタ654、およびカスコードトランジスタ656および658は、図6Aに示されるように、NMOSトランジスタを用いて、または他のタイプのトランジスタを用いて、実現されることができる。

## 【0050】

[0053] 増幅器回路650は、他の方式で実現されることもできる。別の例示的な設計において、増幅器回路は、そのソースが(ソースデジエネレイションインダクタの代わりに)回路接地に直接結合される利得トランジスタを含み得る。さらに別の例示的な設計において、増幅器回路は、並列に結合され、それらのゲートが入力RF信号を受信する、2つの利得トランジスタを含むことができる。第1の利得トランジスタは、図6Aに示されるように、そのソースがソースデジエネレイションインダクタに結合され得る。第2

10

20

30

40

50

の利得トランジスタは、そのソースが回路接地に直接結合され得る。第1または第2の利得トランジスタのいずれかが、選択され得る。

#### 【0051】

[0054] 図6Aに示される例示的な設計では、各負荷回路670は、一次コイル(a primary coil)674および二次コイル(a secondary coil)676を含む変圧器(a transformer)672を含む。負荷回路670a内で、変圧器672aは、(i)カスコードトランジスタ656aおよび658のドレインと、電源(a power supply)、VDDとの間に結合された一次コイル674a、および(ii)第1の差分出力RF信号(a differential first output RF signal)を提供する二次コイル676aを含む。負荷回路670bは、(i)カスコードトランジスタ656bのドレインと、VDD電源との間に結合された一次コイル674b、および(ii)第2の差分出力RF信号(a differential second output RF signal)を提供する二次コイル676bを有する変圧器672bを含む。

10

#### 【0052】

[0055] 負荷回路670は、他の方式で実現されることもできる。別の例示的な設計において、負荷回路は、インダクタ、および場合によりVDD電源とカスコードトランジスタのドレインとの間に結合されたキャパシタ(capacitor)を含み得る。カスコードトランジスタは、そのドレインにおいて出力RF信号を提供し得る。さらに別の例示的な設計において、負荷回路は、そのソースがVDD電源に結合され、そのドレインがカスコードトランジスタのドレインに結合された、P型金属酸化膜半導体(PMOS)トランジスタを含み得る。PMOSトランジスタは、カスコードトランジスタのために能動負荷(an active load)を提供し得る。

20

#### 【0053】

[0056] 簡潔さのために、図6Aは、2つのセットのキャリアのための2つの増幅器回路650aおよび650b、および負荷回路670aおよび670bを含むCA LNA 640aを示す。CA LNA 640aは、2つより多いセットのキャリアのための2つより多い増幅器回路650および2つより多い負荷回路670を含み得る。

#### 【0054】

[0057] CA LNA 640aは、任意の所与の時間において单一出力モードまたは多出力モードで動作することができる。单一出力モードにおいて、CA LNA 640aは、1つのセットのキャリア上の伝送を受信し、1つの出力RF信号を1つのダウンコンバータ回路に提供する。多出力モードでは、CA LNA 640aは、2つのセットのキャリア上の伝送を受信し、2つの出力RF信号を2つのダウンコンバータ回路に提供し、キャリアのセットごとに1つの出力RF信号を提供する。

30

#### 【0055】

[0058] 図6Bは、多出力モードにおけるCA LNA 640aの動作を示す。多出力モードにおいて、増幅器回路650aおよび650bの両方は、それぞれ、カスコードトランジスタ656aおよび656bのゲートにおいて、Vctr11およびVctr12信号に適切なバイアス電圧を提供することによってイネーブルにされる。転換カスコードトランジスタ658は、Vctr1a信号に低電圧を提供することによってディスエーブルにされる。増幅器回路650aは、入力RF信号を増幅し、第1の増幅されたRF信号を負荷回路670aに提供する。増幅器回路650bは、入力RF信号を増幅し、第2の増幅されたRF信号を負荷回路670bに提供する。

40

#### 【0056】

[0059] 図6Cは、单一出力モードにおけるCA LNA 640aの動作を示す。单一出力モードにおいて、利得トランジスタ654aおよび654bの両方は、それぞれ、カスコードトランジスタ656aおよび658のゲートにおいて、Vctr11およびVctr1a信号に適切なバイアス電圧を提供することによってイネーブルにされる。カスコードトランジスタ656bは、Vctr12に低電圧を提供することによってディスエーブルにされる。増幅器回路650aおよび650cは、入力RF信号を増幅し、増幅され

50

た R F 信号を負荷回路 670a に提供する。特に、利得トランジスタ 654a および 654b は、入力 R F 信号を増幅し、増幅された R F 信号をカスコードトランジスタ 656a および 658 を介して負荷回路 670a に提供する。

#### 【0057】

[0060] 図 6 A に示される例示的な設計において、入力 R F 信号は、入力 R F 信号を 2 つの利得トランジスタ 654a および 654b に適用させる (applied) ことによって、「ゲート」レベルで分割される (split)。入力 R F 信号はまた、入力 R F 信号を 2 つのカスコードトランジスタを駆動する単一の利得トランジスタに適用させることによって、「カスコード」レベルで分割されることができる。(図 6 A に示されるように) ゲートレベルで入力 R F 信号を分割することは、カスコードレベルで入力 R F 信号を分割するよりも、より良い性能 (例えば、より良い利得、雑音指數 (noise figure)、線形性 (linearity)、およびアイソレーション (isolation)) を提供し得る。例えば、ゲートレベルで入力 R F 信号を分離することは、約 35 dB の良好な LO-LO アイソレーション (または異なるセットのキャリアのためのダウンコンバータのための LO 信号間のアイソレーション) を提供し得る一方で、カスコードレベルで入力 R F 信号を分離することは、約 15 dB のみの LO-LO アイソレーションを提供し得る。10

#### 【0058】

[0061] CA LNA 640a は、2 つの別個の信号経路を含む。第 1 の信号経路は、増幅器回路 650a および負荷回路 670a を含む。第 2 の信号経路は、増幅器回路 650b および負荷回路 670b を含む。2 つの信号経路は、2 つのセットのキャリアのための 2 つの出力 R F 信号を 2 つのダウンコンバタ回路に提供し得る。20

#### 【0059】

[0062] 多出力モードでは、図 6 B に示されるように、両方の信号経路は同時にオンにされる (turned on)。各信号経路は、入力 R F 信号を増幅し、その負荷回路から出力 R F 信号を提供する。

#### 【0060】

[0063] 図 6 C に示されるように、单一出力モードにおいて、第 1 の信号経路はオンにされ、負荷回路 670a は出力 R F 信号を提供する。さらに、单一出力モードと多出力モードとの間の CA LNA 640a の入力インピーダンスにおける変化を低減させるために、利得トランジスタ 654b がオンにされる。第 2 の信号経路におけるカスコードトランジスタ 656b は、オフにされる (turned off)。しかしながら、転換カスコードトランジスタ 658 はオンにされ、利得トランジスタ 654b からの R F 電流を第 1 の信号経路にステアリングし (steer)、その後单一出力モードにおける LNA 640a の利得 / 相互コンダクタンス (gain/transconductance) をブーストする (boost)。30

#### 【0061】

[0064] 図 6 A に示される例示的な設計において、分離したソースデジエネレイションインダクタ 652a および 652b は、2 つの信号経路間のインタラクション (interaction) を低減させ、雑音指數 (NF) デグラデーション (degradation) を低減させることを助けるために、増幅器回路 650a および 650b に使用される。ソースデジエネレイションインダクタ 652a および 652b はまた、増幅器回路 650a および 650b の線形性を改善し、CA LNA 640a の入力整合を助け得る。インダクタ 652a および 652b は、同一の値または異なる値を有し得る。インダクタ 652a および 652b の値は、单一出力モードおよび多出力モードにおける電圧利得と線形性との間のトレードオフに基づいて、(例えば、独立して) 選択されることがある。40

#### 【0062】

[0065] 図 6 A に示されるように、可変キャパシタ 668a は、利得トランジスタ 654a のゲートおよびソースにわたって存在し得る。キャパシタ 668a は、利得トランジスタ 654a の寄生 (parasitic) を含み得る。キャパシタ 668a はまた、切替可能な (switchable) キャパシタのバンク (a bank of switchable capacitors) を含み得、それは利得トランジスタ 654a の利得およびソースの間に結合され得、CA LNA 640a の利得を調整する。50

0 a の入力インピーダンスを微調整する (fine-tune) ために使用され得る。各切替可能なキャパシタは、スイッチと直列に結合されたキャパシタによって実現され得る。同様に、可変キャパシタ 6 6 8 b は、利得トランジスタ 6 5 4 b のゲートおよびソースにわたって存在し得る。キャパシタ 6 6 8 b は、切替可能なキャパシタのバンクを含み得、それは利得トランジスタ 6 5 4 b の利得およびソースの間に結合され得、C A L N A 6 4 0 a の入力インピーダンスを微調整するために使用され得る。入力整合回路 6 3 2 は、信号経路 6 4 8 a および 6 4 8 b の両方に共通であり、単一出力モードおよび多出力モードの両方で入力整合のために使用される。

#### 【 0 0 6 3 】

[0066] 図 7 A は、インダクティブデジエネレイションおよびカスコード転換スイッチを有する C A L N A 6 4 0 b の例示的な設計の回路図を示す。C A L N A 6 4 0 b は、図 4 A における C A L N A 4 4 0 の別の例示的な設計である。C A L N A 6 4 0 b は、図 6 A における C A L N A 6 4 0 a と同様に、2 つの増幅器回路 6 5 0 a および 6 5 0 b、転換カスコードトランジスタ 6 5 8、および負荷回路 6 7 0 a および 6 7 0 b を含む。C A L N A 6 4 0 b は、さらに、そのソースが利得トランジスタ 6 5 4 a のドレインに結合され、そのゲートが制御信号 V c t r 1 b を受信し、そのドレインがカスコードトランジスタ 6 5 6 b のドレインに結合される、第 2 の転換カスコードトランジスタ 6 5 9 を含む。利得トランジスタ 6 5 4 b、カスコードトランジスタ 6 5 8、およびインダクタ 6 5 2 b は、増幅器回路 6 5 0 a と並列に結合された増幅器回路 6 5 0 c の一部であると考えられ得る。利得トランジスタ 6 5 4 b、カスコードトランジスタ 6 5 9、およびインダクタ 6 5 2 b は、増幅器回路 6 5 0 b と並列に結合された増幅器回路 6 5 0 d の一部であると考えられ得る。C A L N A 6 4 0 b は、増幅された R F 信号を单一出力モードにおける負荷回路 6 7 0 a または 6 7 0 b のいずれかに提供し得る。増幅された R F 信号は、( i ) カスコードトランジスタ 6 5 6 b および 6 5 9 をオンにすること、および( i i ) カスコードトランジスタ 6 5 6 a および 6 5 8 をオフにすることによって、負荷回路 6 7 0 b に提供され得る。

#### 【 0 0 6 4 】

[0067] 図 7 B は、インダクティブデジエネレイション、カスコード転換スイッチ、およびフィードバックを有する C A L N A 6 4 0 c の例示的な設計の回路図を示す。C A L N A 6 4 0 c は、図 4 A における C A L N A 4 4 0 のさらに別の例示的な設計である。C A L N A 6 4 0 c は、図 6 A における C A L N A 6 4 0 a と同様に、2 つの増幅器回路 6 5 0 a および 6 5 0 b、転換カスコードトランジスタ 6 5 8、および負荷回路 6 7 0 a および 6 7 0 b を含む。C A L N A 6 4 0 c は、さらに、カスコードトランジスタ 6 5 6 a および 6 5 6 b のドレインと、利得トランジスタ 6 5 4 a および 6 5 4 b のゲートとの間、すなわち増幅器回路 6 5 0 a および 6 5 0 b の入力および出力の間に、に結合されたフィードバック回路 6 6 0 を含む。

#### 【 0 0 6 5 】

[0068] 図 7 B に示される例示的な設計では、フィードバック回路 6 6 0 は、スイッチ 6 6 2 a および 6 6 2 b、抵抗器 6 6 4、およびキャパシタ 6 6 6 を含む。抵抗器 6 6 4 およびキャパシタ 6 6 6 は直列に結合され、キャパシタ 6 6 6 の基部の端子 (bottom terminal) は利得トランジスタ 6 5 4 a および 6 5 4 b のゲートに結合される。スイッチ 6 6 2 a は、カスコードトランジスタ 6 5 6 a のドレインと、抵抗器 6 6 4 の底部の端子 (top terminal) との間に結合される。スイッチ 6 6 2 b は、カスコードトランジスタ 6 5 6 b のドレインと、抵抗器 6 6 4 の頂部の端子との間に結合される。スイッチ 6 6 2 a および 6 6 2 b は各々、フィードバック回路 6 6 0 をそれの関連するカスコードトランジスタ 6 5 6 と接続するためにクローズにされ得、フィードバック回路 6 6 0 を関連するカスコードトランジスタ 6 5 6 から接続を切るためにオープンにされ得る。フィードバック回路 6 6 0 はまた、トランジスタといった 1 つ以上の能動回路を含み得る。例示的な設計において、フィードバック回路 6 6 0 は、入力電力整合を提供するために、イネーブルにされ、低帯域のために使用されることができる。中帯域および高帯域では、フィードバック

10

20

30

40

50

回路 660 はディスエーブルにされ得、ソースデジエネレイションインダクタ 652a および 652b は、入力電力整合のための整合回路 632 とともに使用され得る。フィードバック回路 660 は、他の方式でも使用され得る。

#### 【0066】

[0069] フィードバック回路 660 は、CA LNA 640c のための入力整合に役立ち得る。入力整合回路 632 は、増幅器回路 650a および 650b の両方に共通しており、単一出力モードおよび多出力モードの両方で使用される。多出力モードにおいて、CA LNA 640c のための入力整合は、フィードバック回路 660、および増幅器回路 650a および 650b のまわりのスイッチ 662a および 662b、およびソースデジエネレイションインダクタ 652a および 652b によって達成され得る。CA LNA 640c のための入力整合は、(i) フィードバック回路 660、スイッチ 662a、および RF out 1 信号のためのソースデジエネレイションインダクタ 652a によって、および (ii) RF out 2 信号のためのソースデジエネレイションインダクタ 652b によって、達成され得る。あるいは、CA LNA 640c のための入力整合は、(i) RF out 1 信号のためのソースデジエネレイションインダクタ 652a によって、および (ii) フィードバック回路 660、スイッチ 662b、および RF out 2 信号のためのソースデジエネレイションインダクタ 652b によって、達成され得る。単一出力モードにおいて、CA LNA 640c のための入力整合は、フィードバック回路 660、スイッチ 662a または 662b、およびソースデジエネレイションインダクタ 652a および 652b によって達成され得る。フィードバック回路 660 は、単一出力モードおよび多出力モードの両方において、LNA 640c 全体のための入力整合に役立ち得る。

10

20

#### 【0067】

[0070] フィードバック回路 660 は、増幅器回路 650a および 650b の線形性を改善し得る。増幅器回路 650a は、(i) スイッチ 662a がクローズである場合に、ソースデジエネレイションインダクタ 652a およびフィードバック回路 660 の両方によって、または (ii) スイッチ 662a がオープンである場合にソースデジエネレイションインダクタ 652a のみによって、線形化され (linearized) 得る。フィードバック回路 660 は、単一出力モードおよび多出力モードの両方において、増幅器回路 650a の線形性を改善し得る。これは、より小さいインダクタ 652a が増幅器回路 650a のための所望の線形性を取得するために使用されることを可能にし得る。同様に、増幅器回路 650b は、(i) スイッチ 662b がクローズである場合に、ソースデジエネレイションインダクタ 652b およびフィードバック回路 660 の両方によって、または (ii) スイッチ 662b がオープンである場合にソースデジエネレイションインダクタ 652b のみによって、線形化され得る。より小さいインダクタは、フィードバック回路 660 がイネーブルにされた状態で (with feedback circuit 660 enabled)、増幅器回路 650b のための所望の線形性を取得するために、インダクタ 652a および / または 652b のために使用されることができる。

30

#### 【0068】

[0071] 図 7B に示される例示的な設計において、1 つのスイッチ 662a または 662b のみが、任意の所与の時間においてイネーブルにされることができる。多出力モードにおいて、フィードバック回路 660 は、1 つの増幅器回路 650a または 650b を線形化するために使用され得るが、両方の増幅器回路のための入力整合を提供し得る。フィードバックなしの他の増幅器回路は、そのデジエネレイションインダクタを介して線形化され得る。単一出力モードにおいて、1 つの増幅器回路 650a または 650b、およびこの増幅器回路のまわりのフィードバックのみが、イネーブルにされ得る。他の増幅器回路およびそれの対応するフィードバックスイッチが、ディスエーブルにされ得る。

40

#### 【0069】

[0072] 図 7C は、カスコード転換スイッチを有し、ソースデジエネレイションインダクタがない、CA LNA 640d の例示的な設計の回路図を示す。CA LNA 640d は、図 4A における CA LNA 440 のさらに別の例示的な設計である。CA LN

50

A 640d は、2つの増幅器回路 651a および 651b、転換カスコードトランジスタ 658、および2つの負荷回路 670a および 670b を含む。

【0070】

[0073] 減衰回路 (attenuation circuit) 620 は、入力 R F 信号を受信し、減衰された (attenuated) 入力 R F 信号を C A L N A 640d に提供する。減衰回路 620 は、(i) 減衰回路 620 の入力と出力の間に結合された抵抗器 622、および(ii) 減衰回路 620 の出力および回路接地の間に結合された可変抵抗器 624 を含む。A C 結合キャパシタ (AC coupling capacitor) 628 は、減衰回路 620 の出力および増幅器回路 651a の入力の間に結合される。

【0071】

[0074] 増幅器回路 651a は、利得トランジスタ 654a およびカスコードトランジスタ 656a を含む。利得トランジスタ 654a は、そのゲートが A C 結合キャパシタ 628 に結合され、そのソースが、(図 7C に示されるように) 回路接地に、または(図 7C に示されていないが) ソースデジエネレイションインダクタに結合される。カスコードトランジスタ 656a は、そのゲートが V c t r 1 1 信号を受信し、そのソースが利得トランジスタ 654a のドレインに結合され、そのドレインが負荷回路 670a に結合される。増幅器回路 651b は、利得トランジスタ 654b、およびカスコードトランジスタ 656b を含み、それらは増幅器回路 651a における利得トランジスタ 654a およびカスコードトランジスタ 656a と同様の方式で結合される。転換カスコードトランジスタ 658 は、そのソースが利得トランジスタ 654b のドレインに結合され、そのゲートが V c t r 1 a 信号を受信し、そのドレインがカスコードトランジスタ 656a のドレインに結合される。

【0072】

[0075] C A L N A 640d は、入力 R F 信号がジャマー (jammer) を含むシナリオにおいて有利に使用され得、ジャマーは所望の信号に周波数が近い、大きな望ましくない信号である。減衰回路 620 は、(例えば、図 7C に示されるように) プログラム可能であり得、または固定され得る(図 7C に示されていない)。減衰回路 620 は、入力 R F 信号におけるジャマーを減衰させること、および C A L N A 640d のための良好な入力整合を提供することの二重目的を果たし (serve) 得る。

【0073】

[0076] 図 6A、7A、7B および 7C は、カスコード転換スイッチを有する C A L N A のいくつかの例示的な設計を示し、それは他の方式で実現され得る。別の例示的な設計において、C A L N A は、それらのソースが単一の共有されたソースデジエネレイションインダクタに結合される、複数の利得トランジスタを含み得る。例えば、図 6A において、利得トランジスタ 654b のソースは、インダクタ 652a に結合され得、インダクタ 652b は省略され得る。図 6A、7A および 7C における入力整合回路 632、および図 7B における減衰回路 620 は、入力整合を変更するために調整され得る、少なくとも 1 つの同調可能な (tunable) 回路コンポーネント (例えば、少なくとも 1 つの調整可能なキャパシタ) を有する、同調可能な整合回路に置き換えられ得る。

【0074】

[0077] 図 5A における M I M O L N A 540 は、様々な回路アーキテクチャによって実現されることができる。M I M O L N A 540 のいくつかの例示的な設計が、以下に説明される。M I M O L N A 540 はまた、様々なタイプのトランジスタによって実現され得る。N M O S トランジスタを用いて実現される M I M O L N A 540 のいくつかの例示的な設計が、以下に説明される。

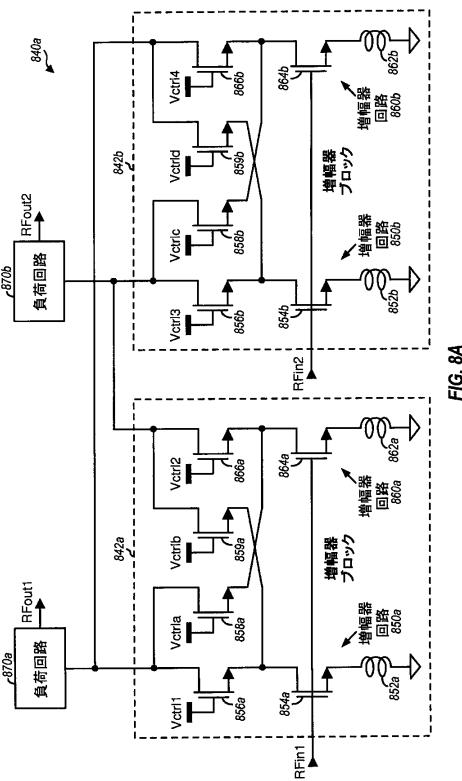

【0075】

[0078] 図 8A は、カスコード転換スイッチを有する 2 × 2 M I M O L N A 840a の例示的な設計の回路図を示す。M I M O L N A 840a は、図 5A における M I M O L N A 540 の 1 つの例示的な設計である。M I M O L N A 840a は、2 つの L N A 入力のための 2 つの増幅器ブロック 842a および 842b、および 2 つの L N A 出

10

20

30

40

50

力のための 2 つの負荷回路 870a および 870b を含む。

【0076】

[0079] 図 8A に示される例示的な設計において、増幅器ブロック 842a は、2 つの増幅器回路 850a および 860a、および転換カスコードトランジスタ 858a および 859a を含む。増幅器ブロック 842b は、2 つの増幅器回路 850b および 860b、および転換カスコードトランジスタ 858b および 859b を含む。各増幅器回路 850 は、利得トランジスタ 854、カスコードトランジスタ 856、およびソースデジエネレイションインダクタ 852 を含み、それらは図 6A における利得トランジスタ 654a、カスコードトランジスタ 656a、およびインダクタ 652a と同様の方式で結合される。各増幅器回路 860 は、利得トランジスタ 864、カスコードトランジスタ 866、およびソースデジエネレイションインダクタ 862 を含み、それらはまた、図 6A における利得トランジスタ 654a、カスコードトランジスタ 656a、およびインダクタ 652a と同様の方式で結合される。増幅器ブロック 842a 内で、転換カスコードトランジスタ 858a は、そのソースが利得トランジスタ 864a のドレインに結合され、そのドレインがカスコードトランジスタ 856a のドレインに結合される。転換カスコードトランジスタ 859a は、そのソースが利得トランジスタ 854a のドレインに結合され、そのドレインがカスコードトランジスタ 866a のドレインに結合される。増幅器ブロック 842b 内で、転換カスコードトランジスタ 858b は、そのソースが利得トランジスタ 864b のドレインに結合され、そのドレインがカスコードトランジスタ 856b のドレインに結合される。転換カスコードトランジスタ 859b は、そのソースが利得トランジスタ 854b のドレインに結合され、そのドレインがカスコードトランジスタ 866b のドレインに結合される。利得トランジスタ 854 および 864、およびカスコードトランジスタ 856、858、859、および 866 は、図 8A に示されるように、NMOS トランジスタを用いて、または他のタイプのトランジスタを用いて、実現されることができる。

【0077】

[0080] 第 1 の入力 RF 信号、RFin1 は、増幅器ブロック 842a における利得トランジスタ 854a および 864b のゲートに提供される。第 2 の入力 RF 信号、RFin2 は、増幅器ブロック 842b における利得トランジスタ 854b および 864b のゲートに提供される。カスコードトランジスタ 856a、866a、856b および 866b は、それらのゲートが、それぞれ、制御信号 Vctrl11、Vctrl12、Vctrl13、および Vctrl14 を受信する。転換カスコードトランジスタ 858a、859a、858b および 859b は、それらのゲートが、それぞれ、制御信号 Vctrl1a、Vctrl1b、Vctrl1c、および Vctrl1d を受信する。カスコードトランジスタ 856a および 866b は、それらのドレインが負荷回路 870a に結合され、カスコードトランジスタ 856b および 866a は、それらのドレインが負荷回路 870b に結合される。

【0078】

[0081] MIMO LNA 840a は、単一出力モード、帯域内 CA モード、および帯域間 CA モードをサポートし得る。単一出力モードが、キャリアアグリゲーションなしで単一のキャリア上に送信された伝送、またはキャリアアグリゲーションを用いて複数のキャリア上に送信された伝送を受信するために使用され得る。単一出力モードにおいて、単一の入力 RF 信号が、単一の増幅器ブロック 842 に適用される。この増幅器ブロック 842 における、利得トランジスタ 854 および 864 の両方、およびカスコードトランジスタ 856 および 858、またはカスコードトランジスタ 859 および 866 のいずれかが、イネーブルにされ、増幅された RF 信号を提供する。1 つのカスコードトランジスタ および 1 つの転換カスコードトランジスタがイネーブルにされ、もう 1 つのカスコードトランジスタ および もう 1 つの転換カスコードトランジスタがディスエーブルにされる。単一の負荷回路 870 は増幅された RF 信号を受信し、1 つのセットのキャリアのための単一の出力 RF 信号を提供する。増幅器回路 850 および 860 は、増幅器ブロック 842 10 20 30 40 50

に対して対称的 (symmetric with) である。R F i n 信号は、2つの出力のうちの1つに転換され (diverted) 得る。選択された出力のための増幅器回路がイネーブルにされ、この増幅器回路と並列に結合された転換カスコードトランジスタもイネーブルにされる。

#### 【 0 0 7 9 】

[0082] 帯域内 C A モードにおいて、単一の入力 R F 信号が単一の増幅器ブロック 8 4 2 に適用される。この増幅器ブロック 8 4 2 における利得トランジスタ 8 5 4 および 8 6 4 の両方、およびカスコードトランジスタ 8 5 6 および 8 6 6 の両方が、イネーブルにされ、2つの増幅された R F 信号を提供する。転換カスコードトランジスタ 8 5 8 および 8 5 9 の両方が、ディスエーブルにされる。2つの負荷回路 8 7 0 は、2つの増幅された R F 信号を受信し、2つのセットのキャリアのための2つの出力 R F 信号を提供する。 10

#### 【 0 0 8 0 】

[0083] 帯域内 C A モードにおいて、2つの入力 R F 信号が、2つの増幅器ブロック 8 4 2 に適用される。各増幅器回路 8 4 2 において、利得トランジスタ 8 5 4 および 8 6 4 の両方、およびカスコードトランジスタ 8 5 6 および 8 5 8 、またはカスコードトランジスタ 8 5 9 および 8 6 6 のいずれかが、増幅された R F 信号を提供するようにイネーブルにされ得る。2つの負荷回路 8 7 0 は、2つの増幅器ブロック 8 4 2 から2つの増幅された R F 信号を受信し、2つのセットのキャリアのための2つの出力 R F 信号を提供する。

#### 【 0 0 8 1 】

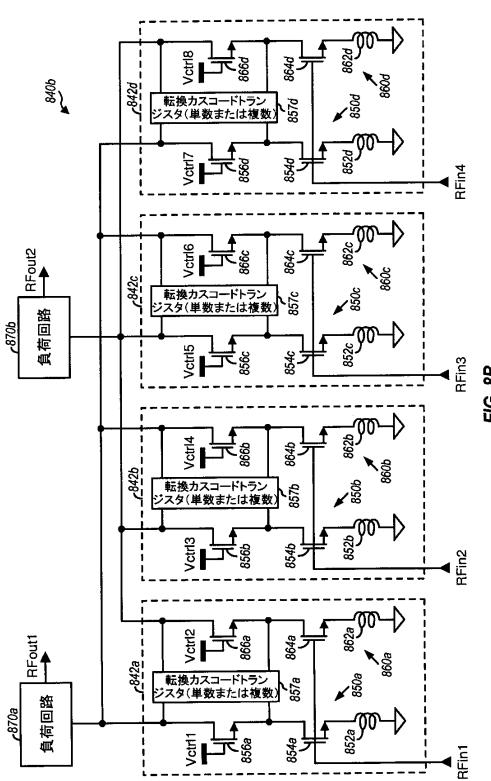

[0084] 図 8 B は、カスコード転換スイッチを有する 4 × 2 M I M O L N A 8 4 0 b の例示的な設計の回路図を示す。M I M O L N A 8 4 0 b は、図 5 A における M I M O L N A 5 4 0 の別の例示的な設計である。M I M O L N A 8 4 0 b は、4つの L N A 入力のための4つの増幅器ブロック 8 4 2 a から 8 4 2 d 、および2つの L N A 出力のための2つの負荷回路 8 7 0 a および 8 7 0 b を含む。 20

#### 【 0 0 8 2 】

[0085] 図 8 B に示される例示的な設計において、各増幅器ブロック 8 4 2 は、2つの増幅器回路 8 5 0 および 8 6 0 、および1つ以上の転換カスコードトランジスタ 8 5 7 を含む。各増幅器回路 8 5 0 は、利得トランジスタ 8 5 4 、カスコードトランジスタ 8 5 6 、およびソースデジエネレイションインダクタ 8 5 2 を含む。各増幅器回路 8 6 0 は、利得トランジスタ 8 6 4 、カスコードトランジスタ 8 6 6 、およびソースデジエネレイションインダクタ 8 6 2 を含む。各増幅器ブロック 8 4 2 内で、転換カスコードトランジスタ ( 単数または複数 ) 8 5 7 は、図 8 A における転換カスコードトランジスタ 8 5 8 および / または 8 5 9 を含み得る。転換カスコードトランジスタ 8 5 8 は ( 存在する場合 ) 、それのソースが利得トランジスタ 8 5 4 のドレインに結合され、そのドレインがカスコードトランジスタ 8 5 6 のドレインに結合される。転換カスコードトランジスタ 8 5 9 は ( 存在する場合 ) 、それのソースが利得トランジスタ 8 5 4 のドレインに結合され、そのドレインがカスコードトランジスタ 8 6 6 のドレインに結合される。 30

#### 【 0 0 8 3 】

[0086] 4つの入力 R F 信号、R F i n 1 から R F i n 4 は、それぞれ、増幅器ブロック 8 4 2 a から 8 4 2 d に提供される。カスコードトランジスタ 8 5 6 a 、 8 5 6 d 、 8 6 6 b および 8 6 6 c は、それらのドレインが負荷回路 8 7 0 a に結合される。カスコードトランジスタ 8 5 6 b 、 8 5 6 c 、 8 6 6 a および 8 6 6 d は、それらのドレインが負荷回路 8 7 0 b に結合される。 40

#### 【 0 0 8 4 】

[0087] M I M O L N A 8 4 0 b は、単一出力モード、帯域内 C A モード、および帯域間 C A モードをサポートし得る。単一出力モードにおいて、単一入力 R F 信号は、4つの L N A 入力のうちの任意の1つを介して受信され、単一の増幅器ブロック 8 4 2 に適用され得る。増幅器回路 8 4 2 は、入力 R F 信号を増幅し、増幅された R F 信号を単一の負荷回路 8 7 0 に提供する。この負荷回路 8 7 0 は、1つのセットのキャリアのための単一の出力 R F 信号を、2つの L N A 出力のうちの1つに提供する。

#### 【 0 0 8 5 】

[0088] 帯域内CAモードにおいて、単一の入力RF信号は、4つのLNA入力のうちの任意の1つを介して受信され得、単一の増幅器ブロック842に適用され得る。この増幅器回路842は、入力RF信号を増幅し、2つの増幅されたRF信号を2つの負荷回路870に提供する。2つの負荷回路870は、2つのセットのキャリアのための2つの出力RF信号を2つのLNA出力に提供する。MIMO LNA 840bは、入力RF信号が任意の増幅器ブロック842に適用され、任意の負荷回路870にルーティングされることを可能にする。

#### 【0086】

[0089] 帯域間CAモードにおいて、2つの入力RF信号は、4つのLNA入力のうちの2つを介して受信され、2つの増幅器ブロック842に適用され得る。これらの2つの増幅器ブロック842は、2つの入力RF信号を増幅し、2つの増幅されたRF信号を2つの負荷回路870に提供する。2つの負荷回路870は、2つのセットのキャリアのための2つの出力RF信号を2つのLNA出力に提供する。図8Bに示される例示的な設計において、MIMO LNA 840bは、帯域間CAモードにおいて入力RF信号の6つの組み合わせをサポートする。特に、入力RF信号の以下の組み合わせ、(RFin1, RFin2)、(RFin1, RFin3)、(RFin1, RFin4)、(RFin2, RFin3)、(RFin2, RFin4)、および(RFin3, RFin4)がサポートされ得る。

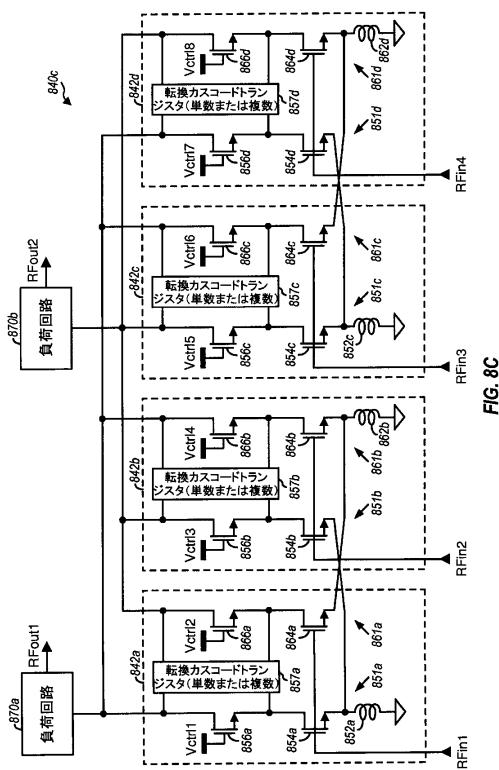

#### 【0087】

[0090] 図8Cは、カスコード転換スイッチを有する4×2 MIMO LNA 840cの例示的な設計の回路図を示す。MIMO LNA 840cは、図5AにおけるMIMO LNA 540のさらに別の例示的な設計である。MIMO LNA 840cは、4つのLNA入力のための4つの増幅器ブロック844aから844d、および2つのLNA出力のための2つの負荷回路870aおよび870bを含む。各増幅器ブロック844は、増幅器回路851および861、および1つ以上の転換カスコードトランジスタ857を含む。転換カスコードトランジスタ(単数または複数)857は、図8Aにおける転換カスコードトランジスタ858および/または859を含み得る。各増幅器回路851は、利得トランジスタ854およびカスコードトランジスタ856を含む。各増幅器回路861は、利得トランジスタ864およびカスコードトランジスタ866を含む。利得トランジスタ854aおよび854bは、同一のソースデジエネレイションインダクタ852aを共有し、それらのソースがインダクタ852aに結合される。利得トランジスタ864aおよび864bは、同一のソースデジエネレイションインダクタ852bを共有し、それらのソースがインダクタ862bに結合される。利得トランジスタ854cおよび854dは、同一のソースデジエネレイションインダクタ852cを共有し、それらのソースがインダクタ852cに結合される。利得トランジスタ864cおよび864dは、同一のソースデジエネレイションインダクタ862dを共有し、それらのソースがインダクタ862dに結合される。図8CにおけるMIMO LNA 840cは、図8BにおけるMIMO LNA 840bのソースデジエネレイションインダクタの半分を含み、それはより小さな回路面積、より低いコスト等といったいくつかの利点を提供し得る。

#### 【0088】

[0091] MIMO LNA 840cは、図8BにおけるMIMO LNA 840bに関して上述されたように単一出力モード、および帯域内CAモードをサポートし得る。MIMO LNA 840cは、帯域間CAモードもサポートし得る。特に、LNA 840cは、帯域間CAモードにおいて、入力RF信号の4つの組み合わせ、(RFin1, RFin3)、(RFin1, RFin4)、(RFin2, RFin3)、および(RFin2, RFin4)をサポートし得る。

#### 【0089】

[0092] ここにおいて説明されるCA LNAおよびMIMO LNAは、以下の望ましい特徴の1つ以上を有し得る：

1. 単一出力モードおよびCAモードの間の入力インピーダンスにおける小さな変化

10

20

30

40

50

2. 転換カスコードトランジスタによる R F 電流ステアリング (RF current steering) を用いた単一出力モードにおけるより高い利得

3. シングルエンドの L N A 入力および差分 L N A 出力 (differential LNA outputs)

4. M I M O L N A のための変圧器 / 誘導負荷 (Transformer/inductive loads) 、および

3. 低利得のためにバイパスされる、および高利得のための L N A 入力におけるインダクティブデジエネレイション。

【 0 0 9 0 】

[0093] 異なる動作モード間の入力インピーダンスにおける小さな変化は、性能を改善し得る。単一出力モードにおけるより高い利得もまた、性能を改善し得る。 10

【 0 0 9 1 】

[0094] シングルエンドの L N A 入力は、入力ポートの数、および M I M O L N A を含むプリント基板 (P C B) 上の入力整合回路のための回路コンポーネントの数を低減し得る。あるいは、M I M O L N A は、シングルエンドの L N A 入力を有する所与の数の入力ポートのための 2 倍の数の増幅器回路をサポートし得る。差分 L N A 出力は、ダウンコンバータ回路において信号をバランスすることによって、L O 漏れおよび二次効果 (L O leakage and second-order effects) を低減し得る。一般に、シングルエンドの回路に対する差分回路 (differential circuits versus single-ended circuits) の全ての利点が、差分 L N A 出力によって取得され得る。 20

【 0 0 9 2 】

[0095] 変圧器 / 誘導負荷は、これらの回路コンポーネントが電圧ヘッドルーム (voltage headroom) を少しも無駄にしないため、L N A が低電力供給電圧 (a low power supply voltage) によって動作することを可能にし得る。他のタイプの負荷 (例えば、能動 / トランジスタ負荷) が、L N A の利得、雑音指数、および線形性を低下させ (degrade) 得る。

【 0 0 9 3 】

[0096] インダクティブデジエネレイションは、高利得 L N A における線形性を改善するために、および目標インピーダンス (例えば、50 オーム) への入力整合を支援するために、使用され得る。デジエネレイションインダクタなしでは、受信機性能 (例えば、入力整合および線形性のための) は、明細書の要件を満たさないことがある。 30

【 0 0 9 4 】

[0097] 例示的な設計において、装置 (例えば、無線デバイス、I C、回路モジュール等) は、第 1 および第 2 の増幅器回路、およびカスコードトランジスタを含み得る。第 1 の増幅器回路 (例えば、図 6 A における増幅器回路 6 5 0 a) は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む入力 R F 信号を受信し得る。第 2 の増幅器回路 (例えば、増幅器回路 6 5 0 b) は、利得トランジスタ (例えば、利得トランジスタ 6 5 4 b) を含み得、また、入力 R F 信号を受信し得る。カスコードトランジスタ (例えば、転換カスコードトランジスタ 6 5 8) は、第 1 の増幅器回路の出力と、第 2 の増幅器回路における利得トランジスタとの間に結合され得る。第 2 の増幅器回路における利得トランジスタおよびカスコードトランジスタは、追加の増幅器回路 (例えば、図 6 A における増幅器回路 6 5 0 c) であると考えられ得、それは (i) 第 1 の増幅器回路と並列して結合され、および (i i) 利得トランジスタを第 2 の増幅器回路と共有する。本装置は、さらに、第 2 の増幅器回路の出力と第 1 の増幅器回路における利得トランジスタとの間に結合された第 2 のカスコードトランジスタ (例えば、図 7 A における転換カスコードトランジスタ 6 5 9) を含み得る。第 1 の増幅器回路における利得トランジスタおよび第 2 のカスコードトランジスタは、(i) 第 2 の増幅器回路と並列に結合され、および (i i) 利得トランジスタを第 1 の増幅器回路と共有する、別の増幅器回路であると考えられ得る。 40

【 0 0 9 5 】

[0098] 本装置は、第1および第2の負荷回路をさらに含み得る。第1の負荷回路(例えば、図6Aにおける負荷回路670a)は、第1の増幅器回路に結合され得る。第2の負荷回路(例えば、負荷回路670b)は、第2の増幅器回路に結合され得る。例示的な設計において、第1の負荷回路は、一次コイルおよび二次コイルを有する変圧器(例えば、変圧器672a)を含み得る。一次コイル(例えば、一次コイル674a)は、第1の増幅器回路と電源との間に結合され得る。二次コイル(例えば、二次コイル676a)は、第1の増幅器回路からの増幅されたRF信号が一次コイルに適用される場合に、差分出力RF信号(a differential output RF signal)を提供し得る。第2の負荷回路は、別の変圧器(例えば、変圧器672b)を含み得る。第1および第2の負荷回路はまた、インダクタ、キャパシタ、トランジスタ等といった他の回路コンポーネントを含み得る。 10

#### 【0096】

[0099] 1つの例示的な設計において、入力RF信号は、シングルエンドの信号を含み得る。第1および第2の負荷回路は、例えば図6Aに示されるように、差分出力RF信号を提供し得る。一般的に、入力および出力RF信号は、各々シングルエンドの信号または差分信号(a differential signal)を含み得る。

#### 【0097】

[00100] 例示的な設計において、第1の増幅器回路は、第1の増幅器回路における利得トランジスタのソースと回路接地との間に結合された、第1のインダクタ(例えば、図6Aにおけるインダクタ652a)を含み得る。第2の増幅器回路は、第2の増幅器回路における利得トランジスタのソースと回路接地との間に結合された、第2のインダクタ(例えば、インダクタ652b)を含み得る。別の例示的な設計において、第1および第2の増幅器回路における利得トランジスタは、例えば図7Cに示されるように、それらのソースが回路接地に直接結合され得る。さらに別の例示的な設計において、第1および第2の増幅器回路における利得トランジスタは、それらのソースが共有されたインダクタに結合され得る。 20

#### 【0098】

[00101] 例示的な設計において、本装置はさらに、第1および第2の増幅器回路のうちの少なくとも1つの出力および入力の間に結合されたフィードバック回路(例えば、図7Bにおけるフィードバック回路660)を含み得る。フィードバック回路は、抵抗器、キャパシタ、トランジスタ、いくつかの他の回路コンポーネント、またはそれらの組み合わせを含み得る。 30

#### 【0099】

[00102] 例示的な設計において、本装置は、第1および第2の増幅器回路に結合された入力整合回路(例えば、図4Bにおける入力整合回路432)を含み得る。別の例示的な設計において、本装置は、第1および第2の増幅器回路に結合され、入力RF信号を受信し、減衰された入力RF信号を第1および第2の増幅器回路に提供するように構成された、減衰回路(例えば、図7Cにおける減衰回路620)を含み得る。

#### 【0100】

[00103] 例示的な設計において、本装置はさらに第1および第2のダウンコンバータ回路を含み得る。第1のダウンコンバータ回路(例えば、図4Bにおけるダウンコンバータ回路490a)は、第1の負荷回路に結合され得、第1の周波数における第1のLO信号に基づいて第1の負荷回路からの第1の出力RF信号のためのダウンコンバージョンを実行し得る。第2のダウンコンバータ回路(例えば、ダウンコンバータ回路490b)は、第2の負荷回路に結合され得、第2の周波数における第2のLO信号に基づいて第2の負荷回路からの第2の出力RF信号のためのダウンコンバージョンを実行し得る。第2の周波数は、第1の周波数とは異なり得る。第1のダウンコンバータ回路は、本装置によって受信される第1のセットのキャリアのためのダウンコンバージョンを実行し得る。第2のダウンコンバータ回路は、本装置によって受信される第2のセットのキャリアのためのダウンコンバージョンを実行し得る。第1および第2の周波数は、それぞれ、受信される第1および第2のセットのキャリアに基づいて選択され得る。 40 50

## 【0101】

[00104] 本装置は、複数の動作モードのうちの1つで動作し得る。第1の動作モード、例えば図6Bに示されるように多出力モードにおいて、第1の増幅器回路は、入力RF信号を増幅し、第1の増幅されたRF信号を提供するようにイネーブルにされ得、第2の増幅器回路は、入力RF信号を増幅し、第2の増幅されたRF信号を提供するようにイネーブルにされ得る。第1および第2の増幅されたRF信号は、本装置によって受信される2つのセットのキャリアのためのものであり得る。第2の動作モード、例えば図6Cに示されるように单一出力モードにおいて、第1の増幅器回路、第2の増幅器回路における利得トランジスタ、およびカスコードトランジスタは、入力RF信号を増幅し、増幅されたRF信号を提供するようにイネーブルにされ得る。増幅されたRF信号は、本装置によって受信される1つのセットのキャリアのためのものであり得る。 10

## 【0102】

[00105] 例示的な設計において、本装置はさらに第3および第4の増幅器回路、および第2のカスコードトランジスタを含み得る。第3の増幅器回路（例えば、図8Aにおける増幅器回路850b）は、第2の入力RF信号を受信し得る。第4の増幅器回路（例えば、増幅器回路860b）もまた、第2の入力RF信号を受信し得る。第2のカスコードトランジスタ（例えば、カスコードトランジスタ858b）は、第3の増幅器回路の出力と、第4の増幅器回路における利得トランジスタとの間に結合され得る。本装置はさらに、第3および第4のカスコードトランジスタを含み得る。第3のカスコードトランジスタ（例えば、図8Aにおける転換カスコードトランジスタ859a）は、第2の増幅器回路の出力と第1の増幅器回路における利得トランジスタとの間に結合され得る。第4のカスコードトランジスタ（例えば、図8Aにおける転換カスコードトランジスタ859b）は、第4の増幅器回路の出力と、第3の増幅器回路における利得トランジスタとの間に結合され得る。一般的に、MIMO LNAは、第1および第2の増幅器回路、および増幅器回路の少なくとも1つの追加のセット（例えば、ペア）を含み得る。増幅器回路の各セットは、それぞれの入力RF信号を受信し得る。増幅器回路の各セットは、1つ以上の転換カスコードトランジスタと関連付けられ得、各転換カスコードトランジスタは、増幅器回路のセットにおける2つの増幅器回路間に結合され得る。 20

## 【0103】

[00106] 例示的な設計において、各増幅器回路における利得トランジスタは、例えば図8Aおよび図8Bに示されるように、分離した（separate）ソースデジエネレイションインダクタに結合され得る。別の例示的な設計において、複数の増幅器回路における複数の利得トランジスタは、ソースデジエネレイションインダクタを共有し得る。例えば、第1のインダクタ（例えば、図8Cにおけるインダクタ852a）は、2つの増幅器回路における2つの利得トランジスタのソースに結合され得、第2のインダクタ（例えば、図8Cにおけるインダクタ862b）は、2つの他の増幅器回路における2つの他の利得トランジスタのソースに結合され得る。 30

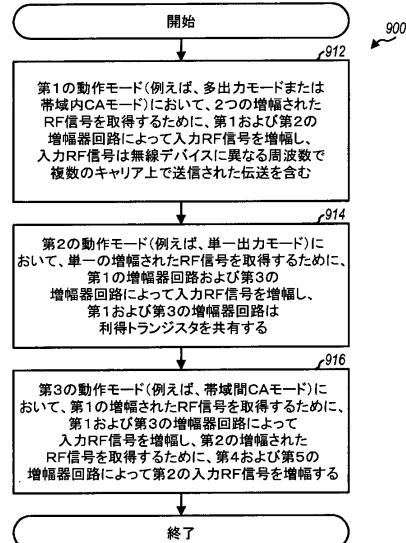

## 【0104】

[00107] 図9は、無線システムにおいて信号増幅を実行するための処理900の例示的な設計を示す。処理900は、無線デバイスによって、またはいくつかの他のエンティティによって実行され得る。入力RF信号は、第1の動作モード（例えば、図6Bにおける多出力モードまたは帯域内CAモード）において2つの増幅されたRF信号を取得するために、第1および第2の増幅器回路（例えば、図7Aにおける増幅器回路650aおよび650b）によって増幅され得る（ブロック912）。入力RF信号は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含み得る。各増幅されたRF信号は、無線デバイスによって受信される異なるセットのキャリアのためのものであり得る。入力RF信号は、第2の動作モード（例えば、図6Cにおける单一出力モード）において单一の増幅されたRF信号を取得するために、第1の増幅器回路および第3の増幅器回路（例えば、図7Aにおける増幅器回路650cまたは650d）によって増幅され得る（ブロック914）。第1および第3の増幅器回路は、並列に結合され得、それらの 40

入力をともに結合し、それらの出力をともに結合し得る。第2および第3の増幅器回路は、利得トランジスタ（例えば、図7Aにおける利得トランジスタ654aまたは654b）を共有し得る。

#### 【0105】

[0108] 第3の動作モード（例えば、帯域間CAモード）において、入力RF信号は、第1の増幅されたRF信号を取得するために第1および第3の増幅器回路によって増幅され得、第2の入力RF信号は、第2の増幅されたRF信号を取得するために第4および第5の増幅器回路によって増幅され得る（ブロック916）。第4の増幅器回路は、図8Aにおける増幅器回路850bに対応し得る。第5の増幅器回路は、図8Aにおける利得トランジスタ864bおよびカスコードトランジスタ858bを含み得る。 10

#### 【0106】

[00109] ここで説明されるLNAは、IC、アナログIC、RFIC、混合信号IC、ASIC、PCB、電子デバイス等上で実現され得る。LNAはまた、相補型金属酸化膜半導体（CMOS）、NMOS、PMOS、バイポーラ接合トランジスタ（BJT）、バイポーラCMOS（BiCMOS）、シリコンゲルマニウム（SiGe）、ガリウムヒ素（GaAs）、ヘテロ接合バイポーラトランジスタ（HBT）、高電子移動度トランジスタ（HEMT）、シリコンオンインシュレータ（SOI）等といった、様々なIC処理技術を用いて製造され得る。

#### 【0107】

[00110] ここに説明されるLNAを実現する装置は、スタンドアロンのデバイスであり得、またはより大きなデバイスの一部であり得る。デバイスは、（i）スタンドアロンのIC、（ii）データおよび/または命令を記憶するためのメモリICを含み得る1つ以上のICのセット、（iii）RF受信機（RFR）またはRF送信機/受信機（RTT）のようなRFIC、（iv）移動局モデム（MSM）のようなASIC、（v）他のデバイス内に埋め込まれ得るモジュール、（vi）受信機、セルラー電話、無線デバイス、ハンドセット、またはモバイル・ユニット、（vii）など、であり得る。 20

#### 【0108】

[00111] 1つ以上の例示的な設計において、説明された機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせで実現されることができる。ソフトウェアで実現される場合、機能は、コンピュータ読み取り可能な媒体上で、1つ以上の命令またはコードとして、記憶または伝送されることができる。コンピュータ読み取り可能な媒体は、ある場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体とコンピュータ記憶媒体との両方を含む。記憶媒体は、コンピュータによってアクセスできる何らかの利用可能な媒体であってもよい。限定ではなく例として、そのようなコンピュータ読み取り可能な媒体は、RAM、ROM、EEPROM、CD-ROM、または他の光ディスク記憶装置、磁気ディスク記憶装置、または他の磁気記憶デバイス、または、命令またはデータ構造の形態で所望のプログラムコードを搬送または記憶するために使用されることができ、かつ、コンピュータによってアクセスされることができる任意の他の媒体を含むことができる。また、任意の接続は、コンピュータ読み取り可能な媒体と適切に称される。例えば、ソフトウェアが、ウェブサイト、サーバ、または他のリモートソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線（DSL）、または赤外線（IR）、無線、およびマイクロ波のような無線技術を使用して伝送される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波のような無線技術は、媒体の定義に含まれる。ここで使用したようなディスク（disk）およびディスク（disc）は、コンパクトディスク（CD）、レザーディスク（登録商標）、光ディスク、デジタル汎用ディスク（DVD）、フロッピー（登録商標）ディスク、およびブルーレイ（登録商標）ディスクを含むが、一般的に、ディスク（disk）は、データを磁気的に再生する一方で、ディスク（disc）はデータをレーザによって光学的に再生する。上記の組み合わせは、また、コンピュータ読み取り可能な媒体の範囲内に含まれるべきである。 30 40 50

## 【0109】

[00112] 本開示の先の説明は、いずれの当業者にも本開示を製造または使用することを可能にするために提供されている。本開示に対するさまざまな変更は、当業者に容易に理解され、本明細書において定義された一般的な原理は、本開示の範囲から逸脱することなく、他の変形例に適用されることができる。したがって、本開示は、本明細書において説明された例および設計に限定されることは意図せず、本明細書に開示された原理および新規な特徴と一致する最も広い範囲が付与されるべきである。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

## [C 1]

無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む、入力無線周波数（RF）信号を受信するように構成された第1の増幅器回路と、

利得トランジスタを含み、前記入力RF信号を受信するように構成された第2の増幅器回路と、

前記第1の増幅器回路の出力と前記第2の増幅器回路における前記利得トランジスタとの間に結合されたカスコードトランジスタと、

を含む、装置。

## [C 2]

前記第2の増幅器回路の出力と前記第1の増幅器回路における利得トランジスタとの間に結合された第2のカスコードトランジスタ、

をさらに含む、C 1に記載の装置。

10

## [C 3]

前記第1の増幅器回路に結合された第1の負荷回路と、

前記第2の増幅器回路に結合された第2の負荷回路と、

をさらに含む、C 1に記載の装置。

## [C 4]

前記第1の負荷回路に結合され、第1の周波数における第1の局部発振器（LO）信号に基づいて前記第1の負荷回路からの第1の出力RF信号のためのダウンコンバージョンを実行するように構成された、第1のダウンコンバータ回路と、

前記第2の負荷回路に結合され、前記第1の周波数とは異なる第2の周波数における第2のLO信号に基づいて前記第2の負荷回路からの第2の出力RF信号のためのダウンコンバージョンを実行するように構成された、第2のダウンコンバータ回路と、をさらに含む、C 3に記載の装置。

20

## [C 5]

前記第2の増幅器回路は、前記利得トランジスタのソースと回路接地との間に結合されたインダクタを含む、C 1に記載の装置。

## [C 6]

前記第1および第2の増幅器回路のうちの少なくとも1つの増幅器回路の出力と入力との間に結合されたフィードバック回路、

をさらに含む、C 1に記載の装置。

30

## [C 7]

前記フィードバック回路は、抵抗器、キャパシタ、またはトランジスタのうちの少なくとも1つを含む、C 6に記載の装置。

40

## [C 8]

前記第1および第2の増幅器回路に結合され、前記入力RF信号を受信し、減衰された入力RF信号を前記第1および第2の増幅器回路に提供するように構成された、減衰回路、

をさらに含む、C 1に記載の装置。

## [C 9]

前記第1の負荷回路は、一次コイルおよび二次コイルを有する変圧器を含み、前記一次コイルは前記第1の増幅器回路と電源との間に結合され、前記二次コイルは、前記第1の

50

増幅器回路からの増幅された R F 信号が前記一次コイルに適用される場合、差分出力 R F 信号を提供する、C 3 に記載の装置。

[C 1 0]

前記入力 R F 信号は、シングルエンドの信号を含み、前記第 1 および第 2 の負荷回路は、差分出力 R F 信号を提供する、C 3 に記載の装置。

[C 1 1]

第 1 の動作モードにおいて、前記第 1 の増幅器回路は、前記入力 R F 信号を増幅し、第 1 の増幅された R F 信号を提供するようにイネーブルにされ、前記第 2 の増幅器回路は、前記入力 R F 信号を増幅し、第 2 の増幅された R F 信号を提供するようにイネーブルにされる、C 1 に記載の装置。

10

[C 1 2]

第 2 の動作モードにおいて、前記第 1 の増幅器回路、前記第 2 の増幅器回路における前記利得トランジスタ、および前記カスコードトランジスタが、前記入力 R F 信号を増幅し、増幅された R F 信号を提供するようにイネーブルにされる、C 1 1 に記載の装置。

[C 1 3]

第 2 の入力 R F 信号を受信するように構成された第 3 の増幅器回路と、

前記第 2 の入力 R F 信号を受信するように構成された第 4 の増幅器回路と、

前記第 3 の増幅器回路の出力と前記第 4 の増幅器回路における利得トランジスタとの間に結合された第 2 のカスコードトランジスタと、

をさらに含む、C 1 に記載の装置。

20

[C 1 4]

前記第 2 の増幅器回路の出力と前記第 1 の増幅器回路における利得トランジスタとの間に結合される第 3 のカスコードトランジスタと、

前記第 4 の増幅器回路の出力と前記第 3 の増幅器回路における利得トランジスタとの間に結合される第 4 のカスコードトランジスタと、

をさらに含む、C 1 3 に記載の装置。

30

[C 1 5]

前記第 1 から第 4 の増幅器回路のうちの 2 つにおける利得トランジスタのソースに結合される第 1 のインダクタと、

前記第 1 から第 4 の増幅器回路のうちの残りの 2 つにおける利得トランジスタのソースに結合される第 2 のインダクタと、

をさらに含む、C 1 3 に記載の装置。

[C 1 6]

増幅器回路の少なくとも 1 つの追加のセットと、なお、増幅器回路の各追加のセットは、それぞれの入力 R F 信号を受信する、

増幅器回路の各追加のセットのための少なくとも 1 つの追加のカスコードトランジスタと、なお、各追加のカスコードトランジスタは、増幅器回路の前記セットにおける 2 つの増幅器回路間に結合される、

をさらに含む、C 1 に記載の装置。

40

[C 1 7]

第 1 の動作モードにおいて、2 つの増幅された R F 信号を取得するために、第 1 および第 2 の増幅器回路によって入力無線周波数 ( R F ) 信号を増幅することと、なお、前記入力 R F 信号は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む、

第 2 の動作モードにおいて、単一の増幅された R F 信号を取得するために、前記第 1 の増幅器回路および第 3 の増幅器回路によって前記入力 R F 信号を増幅することと、なお、前記第 2 および第 3 の増幅器回路は、利得トランジスタを共有する、

を含む、方法。

[C 1 8]

第 3 の動作モードにおいて、第 1 の増幅された R F 信号を取得するために、前記第 1 お

50

および第3の増幅器回路によって前記入力R F信号を増幅することと、第2の増幅されたR F信号を取得するために、第4および第5の増幅器回路によって第2の入力R F信号を増幅することと、

をさらに含む、C 17に記載の方法。

[C 19]

増幅するための第1の手段がイネーブルにされる場合に、入力無線周波数(R F)信号を増幅するように構成された、前記増幅するための第1の手段と、なお、前記入力R F信号は、無線デバイスに異なる周波数において複数のキャリア上で送信された伝送を含む、

増幅するための第2の手段がイネーブルにされる場合に、前記入力R F信号を増幅するように構成された、前記増幅するための第2の手段と、

10

増幅するための第3の手段がイネーブルにされる場合に、前記入力R F信号を増幅するように構成された、前記増幅するための第3の手段と、なお、前記増幅するための第3の手段は、前記増幅するための第1の手段と並列して結合され、増幅手段を前記増幅するための第2の手段と共有する、

装置。

[C 20]

増幅するための第4の手段がイネーブルにされる場合に、第2の入力R F信号を増幅するように構成された、前記増幅するための第4の手段と、

増幅するための第5の手段がイネーブルにされる場合に、前記第2の入力R F信号を増幅するように構成された、前記増幅するための第5の手段と、

20

増幅するための第6の手段がイネーブルにされる場合に、前記第2の入力R F信号を増幅するように構成された、前記増幅するための第6の手段と、なお、前記増幅するための第6の手段は、前記増幅するための第4の手段と並列して結合され、増幅手段を前記増幅するための第5の手段と共有する、

C 19に記載の装置。

【図1】

【図2】

【図3】

図3

FIG. 3

【図4A】

図4A

FIG. 4A

【図4B】

図4B

FIG. 4B

【図5A】

図5A

FIG. 5A

【図5B】

## 【図 6 A】

図 5B

FIG. 5B

图 6A

FIG. 6A

【図 6 B】

【図7A】

6B

FIG. 6B

【図6C】

図 6C

FIG. 6C

図 7A

FIG. 7A

【図 7 B】

図 7B

FIG. 7B

【図 7 C】

図 7C

FIG. 7C

【図 8 A】

図 8A

FIG. 8A

【図 8 B】

図 8B

FIG. 8B

FIG. 8C

FIG. 8D

### 【図 8 C】

图 8C

【図9】

图 9

FIG. 9

---

フロントページの続き

(72)発明者 デビルワラ、アノッシュ・ボミ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 タシック、アレクサンダー・ミオドラッグ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 高 橋 義昭

(56)参考文献 特開2008-016927(JP, A)

国際公開第2011/134504(WO, A1)

特開平07-038404(JP, A)

米国特許出願公開第2008/0139154(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03F 3/193

H03F 1/22

H03F 3/68

H04B 1/18