(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-524250

(P2004-524250A)

(43) 公表日 平成16年8月12日(2004.8.12)

| (51) Int.C1. <sup>7</sup> |               | F 1           | テーマコード (参考) |         |

|---------------------------|---------------|---------------|-------------|---------|

| <b>C30B</b>               | <b>29/38</b>  | C 30 B 29/38  | D           | 4 G 077 |

| <b>C23C</b>               | <b>16/34</b>  | C 23 C 16/34  |             | 4 K 030 |

| <b>H01L</b>               | <b>21/205</b> | H 01 L 21/205 |             | 5 F 041 |

| <b>H01L</b>               | <b>33/00</b>  | H 01 L 33/00  | C           | 5 F 045 |

| <b>H01S</b>               | <b>5/323</b>  | H 01 S 5/323  | 6 1 O       | 5 F 073 |

審査請求 未請求 予備審査請求 有 (全 60 頁)

|               |                              |          |                                                                                                |

|---------------|------------------------------|----------|------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2002-550144 (P2002-550144) | (71) 出願人 | 503215457<br>ニトロネックス・コーポレーション<br>アメリカ合衆国ノース・カロライナ州27<br>606, ローリー, ハットン・ストリート<br>628, スイート 106 |

| (86) (22) 出願日 | 平成13年12月14日 (2001.12.14)     | (74) 代理人 | 100089705<br>弁理士 社本 一夫                                                                         |

| (85) 翻訳文提出日   | 平成15年6月13日 (2003.6.13)       | (74) 代理人 | 100076691<br>弁理士 増井 忠式                                                                         |

| (86) 國際出願番号   | PCT/US2001/048426            | (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                          |

| (87) 國際公開番号   | W02002/048434                | (74) 代理人 | 100080137<br>弁理士 千葉 昭男                                                                         |

| (87) 國際公開日    | 平成14年6月20日 (2002.6.20)       | (74) 代理人 | 100096013<br>弁理士 富田 博行                                                                         |

| (31) 優先権主張番号  | 09/736,972                   |          |                                                                                                |

| (32) 優先日      | 平成12年12月14日 (2000.12.14)     |          |                                                                                                |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                |

最終頁に続く

(54) 【発明の名称】窒化ガリウム材料および方法

## (57) 【要約】

本発明は、シリコン基板上に形成されている窒化ガリウム材料層を含む半導体材料及びその半導体材料を形成するための方法を提供する。この半導体材料は、シリコン基板と窒化ガリウム材料層との間に形成された転移層を含む。この転移層は、窒化ガリウム材料と基板との間の熱膨張率の差から生じる可能性のある窒化ガリウム材料層中の応力を低減するために組成的な勾配が付けられる。窒化ガリウム材料層中の応力を低減すると、亀裂が生成する傾向が減る。従って、本発明は、亀裂が殆どないか、または全くない窒化ガリウム材料層を含む半導体材料の製造を可能にする。この半導体材料は、多くのマイクロエレクトロニクス用途および光学的用途に用いられてもよい。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

シリコン層を含む基板；

その基板の上をおおって形成されている組成的に勾配を付けた転移層；および

その転移層の上をおおって形成されている窒化ガリウム材料層；

を含む半導体材料。

## 【請求項 2】

その転移層の組成が、その層の厚さ方向に連続的に勾配付けされている請求項 1 に記載の半導体材料。

## 【請求項 3】

その転移層の組成が、その層の厚さ方向に不連続的に勾配付けされている請求項 1 に記載の半導体材料。

## 【請求項 4】

その転移層が、 $Al_x In_y Ga_{(1-x-y)} N$ 、 $In_y Ga_{(1-y)} N$ 、および $Al_x Ga_{(1-x)} N$ からなる群から選ばれる窒化ガリウムの合金を含んでいる請求項 1 に記載の半導体材料。

## 【請求項 5】

その転移層のガリウムの濃度が段々変化している請求項 4 に記載の半導体材料。

## 【請求項 6】

$x$  および  $y$  または  $y$  が、その転移層の背面における第 1 の値から、その転移層の前面における第 2 の値へ変化し、その背面が、その前面より基板のより近くにある、請求項 4 に記載の半導体材料。

## 【請求項 7】

その背面における  $x$  の値と  $y$  の値の和が 0.4 より大きい請求項 6 に記載の半導体材料。

## 【請求項 8】

その背面における  $x$  の値と  $y$  の値の和が 0.8 より大きい請求項 6 に記載の半導体材料。

## 【請求項 9】

その転移層が、基板と接しているその転移層の背面に、 $Al_x In_{(1-x)} N$  を含んでいる請求項 6 に記載の半導体材料。

## 【請求項 10】

その前面における  $x$  の値と  $y$  の値の和が 0.3 未満である請求項 6 に記載の半導体材料。

## 【請求項 11】

その転移層が、窒化ガリウム材料層と接している転移層の前面に、 $GaN$  を含んでおり、そして基板と接している転移層の背面にはガリウムを含んでいない請求項 6 に記載の半導体材料。

## 【請求項 12】

その転移層が  $Al_x Ga_{(1-x)} N$  を含んでいる請求項 4 に記載の半導体材料。

## 【請求項 13】

$x$  の値が、基板から離れる方向に減少している請求項 4 に記載の半導体材料。

## 【請求項 14】

$x$  の値が、基板から離れる方向に増加している請求項 4 に記載の半導体材料。

## 【請求項 15】

$y$  の値が、転移層を横断して一定に保たれている請求項 4 に記載の半導体材料。

## 【請求項 16】

その転移層が超格子を含んでいる請求項 1 に記載の半導体材料。

## 【請求項 17】

その超格子がプラッグ反射体である請求項 16 に記載の半導体材料。

## 【請求項 18】

その超格子が、 $Al_x In_y Ga_{(1-x-y)} N$  と  $Al_a In_b Ga_{(1-a-b)} N$  が交互に並んだ一連の層を含んでいる、請求項 16 に記載の半導体材料。

10

20

30

40

50

## 【請求項 19】

$x$ 、 $y$ 、 $a$  および  $b$  の値は、個々の層を横断して一定であり、そして個々の層の厚さは、転移層を横断して変化している、請求項 18 に記載の半導体材料。

## 【請求項 20】

その転移層が、約 0.03 ミクロンと約 20 ミクロンの間の厚さを有する請求項 1 に記載の半導体材料。

## 【請求項 21】

その窒化ガリウム材料層が  $GaN$  を含んでいる請求項 1 に記載の半導体材料。

## 【請求項 22】

その窒化ガリウム材料層が  $Al_xIn_yGaN_{(1-x-y)}$  を含んでいる請求項 1 に記載の半導体材料。 10

## 【請求項 23】

その窒化ガリウム材料層が 0.75 ミクロンより厚い厚さを有する請求項 1 に記載の半導体材料。

## 【請求項 24】

その半導体材料が半導体デバイスを構成している請求項 1 に記載の半導体材料。

## 【請求項 25】

その半導体材料が LED を構成している請求項 24 に記載の半導体材料。

## 【請求項 26】

その半導体材料がレーザ・ダイオードを構成している請求項 24 に記載の半導体材料。 20

## 【請求項 27】

その半導体材料が FET を構成している請求項 24 に記載の半導体材料。

## 【請求項 28】

その窒化ガリウム材料層が  $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 1 に記載の半導体材料。

## 【請求項 29】

その窒化ガリウム材料層が、 $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 1 に記載の半導体材料。

## 【請求項 30】

その窒化ガリウム材料層が、実質的に亀裂を含んでいない請求項 1 に記載の半導体材料。 30

## 【請求項 31】

その窒化ガリウム材料層が単結晶性である請求項 1 に記載の半導体材料。

## 【請求項 32】

その基板が 250 ミクロンより大きい厚さを有する請求項 1 に記載の半導体材料。

## 【請求項 33】

その基板が組織構造加工されている請求項 1 に記載の半導体材料。

## 【請求項 34】

その基板の上をおおって、そして転移層の下に形成された中間層をさらに含んでいる、請求項 1 に記載の半導体材料。

## 【請求項 35】

その中間層が、一定の組成を有する、請求項 1 に記載の半導体材料。

## 【請求項 36】

その中間層が、 $Al_xIn_yGaN_{(1-x-y)}$ 、 $In_yGaN_{(1-y)}$ 、および  $Al_xGaN_{(1-x)}$  からなる群から選ばれる窒化ガリウムの合金を含んでいる、請求項 1 に記載の半導体材料。

## 【請求項 37】

その基板がシリコン・ウエハを含んでいる請求項 1 に記載の半導体材料。

## 【請求項 38】

シリコン層を含む基板；

その基板の上をおおって形成されている、 $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する 50

窒化ガリウム材料層；を含んでいる半導体材料。

【請求項 3 9】

その窒化ガリウム材料層が GaN を含んでいる請求項 3 8 に記載の半導体材料。

【請求項 4 0】

その窒化ガリウム材料層が  $Al_x In_y Ga_{(1-x-y)} N$ 、 $In_y Ga_{(1-y)} N$ 、および  $Al_x Ga_{(1-x)} N$  からなる群から選ばれる窒化ガリウムの合金を含んでいる請求項 3 8 に記載の半導体材料。

【請求項 4 1】

その窒化ガリウム材料層が  $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 3 6 に記載の半導体材料。

10

【請求項 4 2】

その窒化ガリウム材料層が実質的に亀裂を含んでいない請求項 3 6 に記載の半導体材料。

【請求項 4 3】

その窒化ガリウム材料層が単結晶性である請求項 3 6 に記載の半導体材料。

【請求項 4 4】

その基板がシリコン・ウエハを含んでいる請求項 3 6 に記載の半導体材料。

【請求項 4 5】

シリコン層を含む基板；および

その基板の上をおおって形成されており、その厚さが 0.5ミクロンより厚い窒化ガリウム材料層；

20

を含む半導体構造物であって、その半導体構造物が半導体デバイスを構成している、半導体構造物。

【請求項 4 6】

その窒化ガリウム材料層が 1.0ミクロンより厚い厚さを有する、請求項 4 5 に記載の半導体構造物。

【請求項 4 7】

その基板が、シリコン・ウエハを含んでいる請求項 4 5 に記載の半導体構造物。

【請求項 4 8】

その半導体構造物が LED を構成している請求項 4 5 に記載の半導体構造物。

30

【請求項 4 9】

その半導体構造物がレーザ・ダイオードを構成している請求項 4 5 に記載の半導体構造物。

【請求項 5 0】

その半導体構造物が FET を構成している請求項 4 5 に記載の半導体構造物。

【請求項 5 1】

その窒化ガリウム材料層が  $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 4 5 に記載の半導体構造物。

40

【請求項 5 2】

その窒化ガリウム材料層が  $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 4 5 に記載の半導体構造物。

【請求項 5 3】

その窒化ガリウム材料層が実質的に亀裂を含んでいない請求項 4 5 に記載の半導体構造物。

【請求項 5 4】

シリコン層を含む基板の上をおおって組成的に勾配を付けた転移層を形成させる工程；および、その転移層の上をおおって窒化ガリウム材料層を形成させる工程；を含む半導体材料を製造する方法。

【請求項 5 5】

その転移層の組成が、その層の厚さ方向に連続的に勾配付けされている請求項 5 4 に記載の方法。

50

**【請求項 5 6】**

その転移層の組成が、その層の厚さ方向に不連続的に勾配付けされている請求項 5 4 に記載の方法。

**【請求項 5 7】**

その転移層が、 $Al_x In_y Ga_{(1-x-y)} N$ 、 $In_y Ga_{(1-y)} N$ 、および $Al_x Ga_{(1-x)} N$ からなる群から選ばれる窒化ガリウムの合金を含んでいる、請求項 5 4 に記載の方法。

**【請求項 5 8】**

その転移層中のガリウムの濃度が、段々変化している請求項 5 4 に記載の方法。

**【請求項 5 9】**

$x$  の値が、基板から離れる方向に減少している請求項 5 6 に記載の方法。

**【請求項 6 0】**

その転移層が $Al_x Ga_{(1-x)} N$ を含んでいる請求項 5 6 に記載の方法。

**【請求項 6 1】**

その転移層が、一連の交互 $Al_x In_y Ga_{(1-x-y)} N / Al_a In_b Ga_{(1-a-b)} N$ 層を含んでいる超格子を含む請求項 5 4 に記載の方法。

**【請求項 6 2】**

窒化ガリウム材料層が $GaN$ を含んでいる請求項 5 4 に記載の方法。

**【請求項 6 3】**

窒化ガリウム材料層が $Al_x In_y Ga_{(1-x-y)} N$ を含んでいる請求項 5 4 に記載の方法 20

。

**【請求項 6 4】**

その半導体材料を、少なくとも一つの半導体デバイスを調製するために加工することをさらに含んでいる、請求項 5 4 に記載の方法。

**【請求項 6 5】**

その窒化ガリウム材料層が $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する、請求項 5 4 に記載の方法。

**【請求項 6 6】**

その窒化ガリウム材料層が $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する、請求項 5 4 に記載の方法 30

**【請求項 6 7】**

その窒化ガリウム材料層が実質的に亀裂を含んでいない請求項 5 4 に記載の方法。

**【請求項 6 8】**

その窒化ガリウム材料層が単結晶性である請求項 5 4 に記載の方法。

**【請求項 6 9】**

その基板の上をおおって、そして転移層の下に、中間層をさらに形成させることを含んでいる請求項 5 4 に記載の方法。

**【請求項 7 0】**

シリコン層を含む基板の上をおおって形成された $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する窒化ガリウム材料層を形成させることを含んでいる半導体材料を製造する方法。 40

**【請求項 7 1】**

その窒化ガリウム材料層が、 $GaN$ を含んでいる請求項 7 0 に記載の方法。

**【請求項 7 2】**

その窒化ガリウム材料層が 1.0ミクロンより厚い厚さを有する請求項 7 0 に記載の方法。

**【請求項 7 3】**

その窒化ガリウム材料層が $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 7 0 に記載の方法。

**【請求項 7 4】**

その窒化ガリウム材料層が実質的に亀裂を含んでいない請求項 7 0 に記載の方法。

**【請求項 7 5】**

その窒化ガリウム材料層が単結晶性である請求項 7 0 に記載の方法。

【請求項 7 6】

シリコン層を含む基板と、そのシリコン基板の上をおおって形成されている 0.5ミクロンより厚い厚さを有する窒化ガリウム材料層とを含む半導体構造物を形成させることを含む半導体構造物を調製する方法。

【請求項 7 7】

その窒化ガリウム材料層が 1.0ミクロンより厚い厚さを有する請求項 7 6 に記載の方法。

【請求項 7 8】

その半導体構造物が L E D を構成している請求項 7 6 に記載の方法。

【請求項 7 9】

その半導体構造物がレーザ・ダイオードを構成している請求項 7 6 に記載の方法。

【請求項 8 0】

その半導体構造物が F E T を構成している請求項 7 6 に記載の方法。

【請求項 8 1】

その窒化ガリウム材料層が  $0.005 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 7 6 に記載の方法。

【請求項 8 2】

その窒化ガリウム材料層が  $0.001 \mu m / \mu m^2$  未満の亀裂レベルを有する請求項 7 6 に記載の方法。

【請求項 8 3】

その窒化ガリウム材料層が、実質的に亀裂を含んでいない請求項 7 6 に記載の方法。

【請求項 8 4】

シリコン(100) 基板；およびそのシリコン基板の上をおおって形成されているウルツ鉱構造を有する窒化ガリウム材料層；を含んでいる半導体材料。

【請求項 8 5】

シリコン(100) 基板と窒化ガリウム材料層の間に形成された組成的に勾配を付けた転移層を、さらに含んでいる請求項 8 4 に記載の半導体材料。

【発明の詳細な説明】

【0 0 0 1】

発明の分野

本発明は、一般的には半導体材料に関するものであり、そしてより特定すれば、窒化ガリウム材料および窒化ガリウム材料を製造する方法に関するものである。

【0 0 0 2】

発明の背景

窒化ガリウム材料は、窒化ガリウム( G a N )と、窒化アルミニウム・ガリウム( A l G a N )、窒化インジウム・ガリウム( I n G a N )および窒化アルミニウム・インジウム・ガリウム( A l I n G a N )などの窒化ガリウムの合金を含む。これらの材料は、高エネルギー電子遷移の生起を可能にする比較的広い直接帯間隙( direct bandgap )を有する半導体化合物である。このような電子遷移の結果、窒化ガリウム材料は、青光を効率的に発光する能力、高周波数での信号を遷移する能力およびその他の能力を含む多くの魅力的な性質を有することになる。従って、窒化ガリウム材料は、トランジスター、電界エミッターやオプト・エレクトロニックデバイスのような多くのマイクロエレクトロニクス用途で、広く研究されている。

【0 0 0 3】

多くの適用例で、窒化ガリウム材料は基板上に成長させられる。しかし、窒化ガリウム材料と基板の間の性質の差が、多くの用途に適した層を成長させることを困難にすることがある。例えば、窒化ガリウム( G a N )は、サファイヤ、炭化ケイ素およびシリコンを含む多くの基板材料とは異なる熱膨張係数( 即ち、熱膨張率 )を有する。熱膨張におけるこの差は、例えば、加工中にその構造物が冷却される時、そのような基板上に成長した窒化ガリウム層を亀裂させことがある。この亀裂現象は、窒化ガリウム材料を、多くの用途

10

20

30

40

50

での使用に適合させるのを妨げることになり得る。亀裂は、比較的厚い（例えば、> 0.5 ミクロン）窒化ガリウム層で特に問題になる。

#### 【0004】

窒化ガリウム（GaN）はまた、大半の基板材料とは異なる格子定数を有する。格子定数における差は、基板上に成長された窒化ガリウム層中に欠陥を生じさせる可能性がある。このような欠陥は、その窒化ガリウム材料層を用いて作られたデバイスの実用性能を悪化させる。

#### 【0005】

従来技術で、サファイア基板および炭化ケイ素基板上に成長された窒化ガリウム材料中の亀裂の生成と欠陥の生成に対応する方法が開発されてきた。このような方法は、例えば、その基板上に一つまたはそれ以上の緩衝層を成長させ、次いでその緩衝層（単層または複数層）の上に窒化ガリウム材料を成長させることを含んでいる。

#### 【0006】

##### 本発明の概要

本発明は、シリコン基板上に形成された窒化ガリウム材料層を含む半導体材料およびその半導体材料を調製する方法を提供する。この半導体材料は、そのシリコン基板と窒化ガリウム材料層の間に形成された転移層を含んでいる。この転移層は、窒化ガリウム材料と基板との間の熱膨張率の差から生じる可能性のある窒化ガリウム材料層中の応力を低減するために組成的な勾配が付けられる。窒化ガリウム材料層中の応力を低減すると、亀裂が生成する傾向が減り、亀裂が殆どないか、または全くない窒化ガリウム材料層を含む半導体材料の製造が可能になる。この半導体材料は、多くのマイクロエレクトロニクス用途および光学的用途に用いられてもよい。

#### 【0007】

本発明は、窒化ガリウム材料（例えば、GaN）とシリコンの間の熱膨張率および格子定数の両方における大きい差に起因する亀裂が、殆どまたは全く無い窒化ガリウム材料をシリコン基板上に成長させるという、他のタイプの基板（例えば、SiCおよびサファイア）上での場合より、かなり挑戦的で大きい課題を克服した。

#### 【0008】

一つの態様では、本発明は半導体材料を提供する。この材料は、シリコン層を含む基板とその基板の上をおおって形成された組成的に勾配を付けた転移層とを含む。この材料は、その転移層の上をおおって形成された窒化ガリウム材料層をさらに含んでいる。

#### 【0009】

もう一つの態様で、本発明は半導体材料を提供する。この半導体材料は、シリコン層を含む基板とその基板上をおおって形成された窒化ガリウム材料層とを含む。この窒化ガリウム材料層の亀裂レベルは  $0.005 \mu\text{m} / \mu\text{m}^2$  未満である。

#### 【0010】

もう一つの態様で、本発明は半導体構造物を提供する。この半導体構造物は、シリコン層を含む基板とその基板上をおおって形成された窒化ガリウム材料層を含む。この窒化ガリウム材料層の厚さは 0.5ミクロンより大きい。この半導体構造物は半導体デバイスを構成する。

#### 【0011】

もう一つの態様では、本発明は半導体材料を製造する方法を提供する。この方法は、シリコン層を含む基板上をおおって、組成的に勾配を付けた転移層を形成させる工程および、この転移層上をおおって窒化ガリウム材料層を形成させる工程を含んでいる。

#### 【0012】

もう一つの態様で、本発明は半導体材料を製造する方法を提供する。この方法は、シリコン層を含む基板上をおおって形成される窒化ガリウム材料層を形成させる工程を含む。この窒化ガリウム材料層の亀裂レベルは  $0.005 \mu\text{m} / \mu\text{m}^2$  未満である。

#### 【0013】

もう一つの態様では、本発明は半導体構造物を調製する方法を提供する。この方法はシリ

10

20

30

40

50

コン層を含む基板およびこの基板上に形成された窒化ガリウム材料層を含んでいる半導体構造物を調製することを含む。この窒化ガリウム材料層の厚さは  $0.5 \mu m$  より厚い。

【0014】

もう一つの態様では、本発明は半導体材料を提供する。この半導体材料は、シリコン(100)基板と、そのシリコン基板上に形成されたウルツ鉱構造(Wurtzite structure)を有する窒化ガリウム材料層を含んでいる。

【0015】

以下の本発明の詳細な説明を、添付した図面と組み合わせて考察すれば、本発明の他の利点、態様および特徴が明らかになるであろう。

本発明の詳細な説明

本発明は、窒化ガリウム材料層を含む半導体材料および、その半導体材料を製造する方法を提供する。本明細書で用いられている、“窒化ガリウム材料”という用語は、窒化ガリウム(GaN)および、窒化アルミニウム・ガリウム( $Al_x Ga_{(1-x)} N$ )、窒化インジウム・ガリウム( $In_y Ga_{(1-y)} N$ )、窒化アルミニウム・インジウム・ガリウム( $Al_x In_y Ga_{(1-x-y)} N$ )、ヒ化・リン化・窒化ガリウム(gallium arsenide phosphide nitride)( $GaAs_a Pb_{(1-a-b)} N$ )、ヒ化・リン化・窒化・アルミニウム・インジウム・ガリウム(aluminum indium gallium arsenide phosphide nitride)( $Al_x In_y Ga_{(1-x-y)} As_a Pb_{(1-a-b)} N$ )、その他のような窒化ガリウムの合金の中の任意の物である。普通、ヒ素および/またはリンは存在するとしても、低濃度(即ち、5重量%未満)である。

【0016】

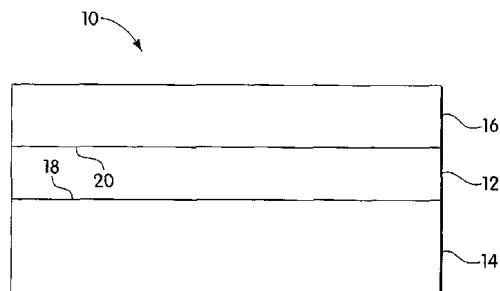

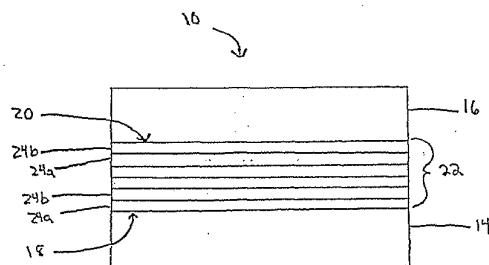

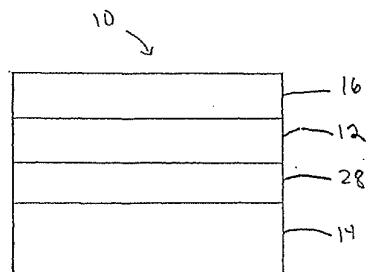

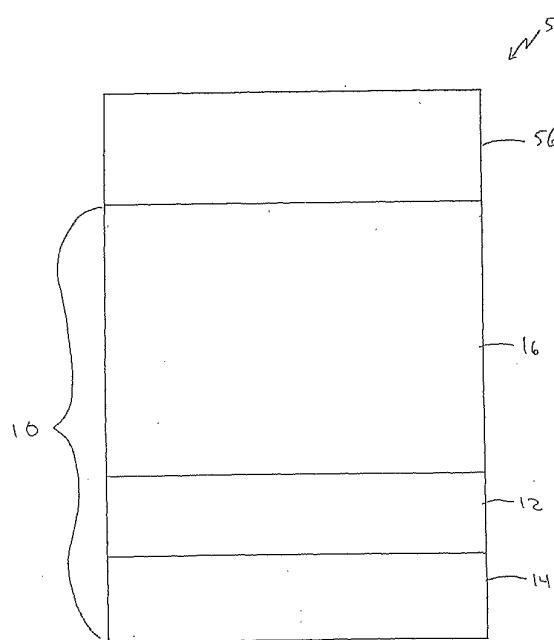

図1を参照すると、本発明の一つの態様に従う、半導体材料10が示されている。半導体材料10は、シリコン基板14上をおおって形成された転移層12とその転移層の上をおおって形成された窒化ガリウム材料層16を含んでいる。下でさらに説明されるように、基板14と窒化ガリウム材料層の熱膨張率の差から生じる可能性のある窒化ガリウム材料層16中の内部応力を低減するために、転移層12には、組成的に勾配が付けられている。この内部応力は、例えば、その半導体材料10が、窒化ガリウム材料層16の沈着後に冷却され、そして基板14が窒化ガリウム材料層より急速に収縮する時に上昇する可能性がある。この内部応力が低下する結果、FETs、LEDs、レーザ・ダイオードおよび類似用途を含む多くの用途で使用するのに適した半導体材料10を作るための亀裂レベルの低い窒化ガリウム材料層16を調製することができる。

【0017】

一つの層が、もう一つの層の“上に”(“on”)または“上をおおって”(“over”)存在するとして引用される場合、その層または基板上に直接存在していてもよく、または間に挟まった層が存在していてもよい。また一つの層が、もう一つの層の“上に”(“on”)または、“上をおおって”(“over”)存在するとして引用される場合、その層または基板の全部、またはその層または基板の一部をカバーすると理解すべきである。

【0018】

本明細書で用いられる“組成的に勾配を付けた層”(compositionally-graded layer)という用語は、その層の少なくとも一部の厚さ方向に変化する組成を有する層のことである。かくして、転移層12は、その層内の異なる深さに、少なくとも二つの異なる組成物を含んでいる。下でさらに説明されるように、転移層12の組成は、多くの方法で変えられる。普通、窒化ガリウム材料層16中での亀裂の生成を限定または防止するのに十分な応力の低減を提供するように転移層12の組成を変化させるのが有利である。

【0019】

一組の実施態様では、転移層12は、 $Al_x In_y Ga_{(1-x-y)} N$ 、 $Al_x Ga_{(1-x)} N$ および $In_y Ga_{(1-y)} N$ 、のような窒化ガリウムの合金から構成される。しかし他の組成を有する転移層も用いられる得ると理解すべきである。窒化ガリウムの合金を利用する態様では、その合金の元素(例えば、Ga、Al、In)の少なくとも一つの濃度を、普通、その転移層の厚さの少なくとも一部を横断して変化させる。転移層12が $Al_x In_n$

10

20

30

40

50

$y \text{ Ga}_{(1-x-y)} \text{ N}$  の組成を有する場合には、 $x$  および  $/$  または  $y$  が変えられる。転移層 1 2 が  $\text{Al}_x \text{ Ga}_{(1-x)} \text{ N}$  の組成を有する場合には、 $x$  が変えられる。転移層 1 2 が  $\text{In}_y \text{ Ga}_{(1-y)} \text{ N}$  の組成を有する場合には、 $y$  が変えられる。

【0020】

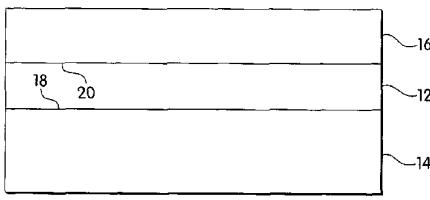

一定の推奨される実施態様では、転移層 1 2 は、背面 1 8 でガリウム濃度が低く、そして前面 2 0 でガリウム濃度が高いのが望ましい。このような転移層は、窒化ガリウム材料層 1 6 内の内部応力を低減させるのに特に有効である。窒化ガリウム合金の転移層のガリウム濃度を下げるにその合金の熱膨張率をシリコンの熱膨張率に、より近づけることができる。下でさらに説明するように、普通、窒化ガリウム材料層 1 6 は、高い濃度のガリウムを含んでいる。かくして、これらの実施態様で、転移層 1 2 中のガリウムの濃度を高くすると、その合金の熱膨張率を窒化ガリウム材料層 1 6 の熱膨張率に、より近づけることができる。これらの推奨される実施態様での効果的な応力の低減は、背面 1 8 が基板 1 4 に比較的近い熱膨張率を有しており、一方、前面 2 0 は窒化ガリウム材料層 1 6 の熱膨張率に比較的近い熱膨張率を有しているので、達成されるものと信じられる。

【0021】

幾つかの場合、背面 1 8 における  $(x + y)$  の和は、0.4 より大きく、0.6 より大きく、0.8 より大きく、あるいはさらに大きいこともある。幾つかの推奨される態様では、背面 1 8 で  $(x + y) = 1$  であり、即ち転移層 1 2 は、背面にガリウムを含んでいない。幾つかの場合、前面 2 0 における  $(x + y)$  の和は、0.3 より小さく、0.2 より小さく、あるいはさらに小さいことさえある。幾つかの推奨される態様では、前面 2 0 で  $(x + y)$  の和 = 0 であり、即ち転移層 1 2 の前面における組成は  $\text{GaN}$  である。窒化ガリウム材料層 1 6 の組成が  $\text{GaN}$  である場合には、転移層 1 2 にとって、前面 2 0 の組成が  $\text{GaN}$  であることが特に推奨されるであろう。窒化ガリウム材料層 1 6 が  $\text{GaN}$  の合金で構成される他のケースでは、前面 2 0 での転移層 1 2 の組成は、窒化ガリウム材料層 1 6 の組成と同じであるのが望ましいであろう。幾つかのケースでは、転移層 1 2 は、背面 1 8 にガリウムを含まず、そして前面 2 0 の組成は  $\text{GaN}$  である。

【0022】

また、 $x$  の値（即ち、ガリウム濃度）は、その基板から離れる方向に増加して行くと理解すべきである。

特定の実施態様では、転移層 1 2 は、 $\text{Al}_x \text{ Ga}_{(1-x)} \text{ N}$  の組成であることが推奨される。これらのケースでは、その転移層はインジウムを含まない。他のケースでは、転移層 1 2 は、少量の、例えば 10 重量 % 未満のインジウムを含んでもよい。転移層 1 2 中にインジウムが存在する場合（即ち、 $\text{Al}_x \text{ In}_y \text{ Ga}_{(1-x-y)} \text{ N}$ ）、インジウムの濃度（即ち、 $y$ ）は、転移層の中全体で一定のまでもよいが、一方ガリウムとアルミニウムの濃度は勾配付けされる。

【0023】

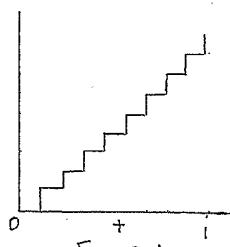

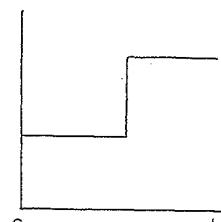

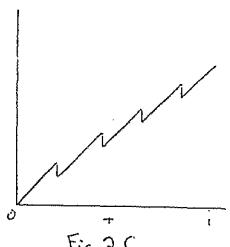

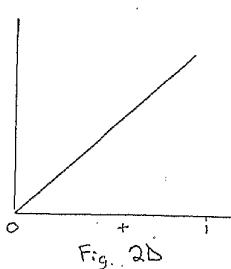

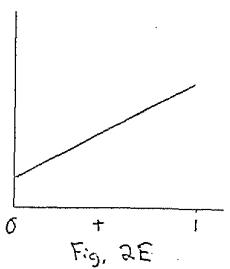

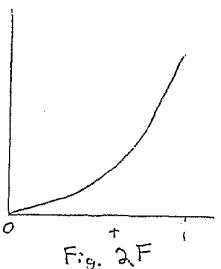

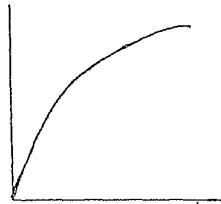

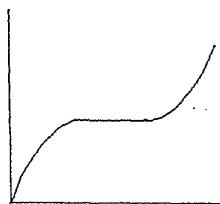

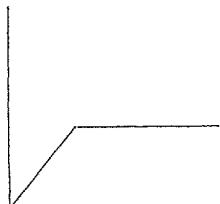

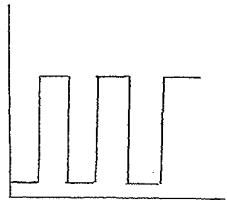

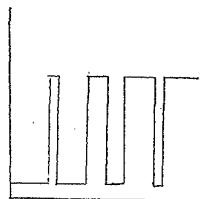

転移層 1 2 の組成は、複数の異なる方式で、その厚さ方向に勾配付されてもよい。例えばその組成は、その全厚さを横断して、またはその厚さの一部だけを横断して、連続的にまたは不連続的に勾配付けされてもよい。上に説明したように、その組成は、元素（即ち  $\text{Ga}$ 、 $\text{Al}$ 、 $\text{In}$ ）の一つもしくはそれ以上の濃度を変えることにより勾配付けされてもよい。図 2 A ~ 2 I は、転移層 1 2 を横断する厚さの関数として元素の一つの濃度を変えることによりその組成に勾配を付けてもよい代表的な様式を例示している。特定の推奨される態様で、図中の線(profiles)は、転移層 1 2 の厚さを横断するガリウムの濃度を表しているが、他の実施態様では、これらの線は、他の元素（即ち、 $\text{Al}$  または  $\text{In}$ ）の濃度を表す場合もあると理解すべきである。図 2 A ~ 2 I では、転移層 1 2 の厚さは基板から離れる方向に増加する（即ち、背面 1 8 で  $t = 0$ 、前面 2 0 で  $t = 1$ ）と約束される。

【0024】

図 2 A は、複数段を含む、厚さの関数としての濃度の段階的变化を示している。図 2 B は、二つの段を含む、厚さの関数としての濃度の段階的变化を示している。図 2 C は、厚さの関数としての濃度の鋸歯状の変化を示している。図 2 D は、厚さの関数としての定率で

10

20

30

40

50

の濃度の連続的变化を示している。図2Eは、0でない濃度から始まる定率での濃度の連続的变化を示している。図2Fと2Gは、指数関数的割合での厚さの関数としての濃度の連続的变化を示している。図2Hは、厚さの関数としての濃度の不連續的变化を示している。図2Iは、転移層の厚さの一部を横断しての濃度の变化を示している。

【0025】

図2A～2Iに例示された線は、例示を目的としたものであり、そして転移層12の組成は、本発明の範囲内にある他の様式で勾配付けされてもよいことを理解すべきである。

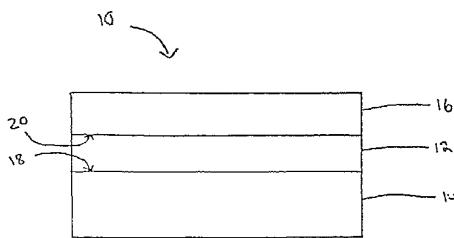

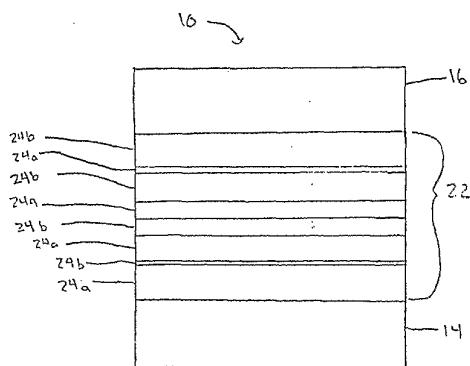

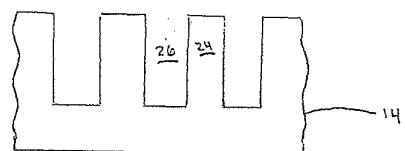

図3Aおよび3Bを参照して説明すると、転移層12は、本発明のもう一つの態様に従う組成的に勾配付けされたひずみ層超格子(strained layer superlattice)22でもよい。

超格子22は、異なる組成を有する半導体化合物の交互層24a、24bを含んでいる。

10

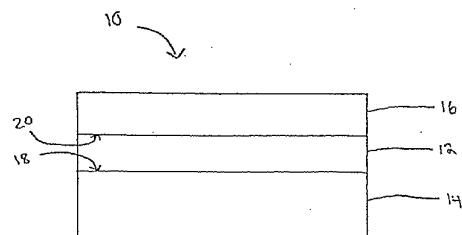

幾つかの場合では、個々の層24a、24bの各々を横断する組成は、上に説明した様式の任意の様式で変えられる。他の場合では、個々の層24a、24bの組成は、図4Aおよび4Bの濃度線に示されているように、個々の層の厚さを横断して一定である。図3B(および4B)中に示されているように、個々の層24a、24bの厚さは、組成的に勾配を付けるために転移層12を横断して変えられる。

【0026】

超格子22は、本発明の幾つかの態様において、ブレッジ(Bragg)反射体として機能してもよいと理解すべきである。

推奨される一組の態様で、超格子22は、組成の異なる窒化ガリウム合金の交互層を含んでいる。例えば、層24aは、 $Al_xIn_yGa_{(1-x-y)}N$ の組成を有し、そして層24bは $Al_aIn_bGa_{(1-a-b)}N$ (式中、 $x=a$ そして $y=b$ )の組成を有している。個々の層を横断して組成が段階的に変化している場合、この合金の元素(即ちAl、In、Ga)の少なくとも一つの濃度が、上述した方法の任意の方法に従って変えられる。個々の層24a、24bの組成が一定であるケース(図3B)では、そのガリウム濃度は、層24a、24b中で異なるのが普通である。

20

【0027】

上に説明したように、背面18ではガリウム濃度が低く、前面20ではガリウム濃度が高いことが望ましい場合がある。転移層12として超格子22が用いられる態様では、背面18から離れる方向へのガリウム濃度の増加は、個々の層の厚さを変えることにより達成することができる。図3Aおよび3Bに示されているように、層24aはガリウム濃度が低く、そして層24bのガリウム濃度は高い。示されているように、層24aは相対的に厚く、層24bは、背面18のすぐ近くで相対的に薄い。背面18から離れる方向に向かって、層24aの厚さは減少し、そして層24bの厚さは増加する。かくして前面20のすぐ近くで層24aは相対的に薄く、層24bは相対的に厚い。この構造が、背面18で低いガリウム濃度を、そして前面20で高いガリウム濃度を提供する。

30

【0028】

転移層12は、勾配の付いた組成を有する単一層と超格子の組合せで形成されてもよいと理解すべきである。幾つかの場合には、この超格子が、組成的に勾配が付けられている単一層の上をおおつて形成される。他の場合には、組成的に勾配の付いた単一層が超格子上をおおつて形成される。

40

【0029】

転移層12は、その用途に依存して多様な厚さを有することが可能である。常にではないが、一般に、転移層12の厚さは、約500ミクロンより薄い。幾つかの場合には、例えば、約2.0ミクロンと約20ミクロンの間のような比較的厚い転移層が推奨される。厚い窒化ガリウム材料層(即ち、5ミクロンより厚い)が造られる場合、厚い転移層が推奨される。幾つかの場合には、例えば、約0.03ミクロンと約2.0ミクロンの間のような比較的薄い転移層が推奨される場合がある。転移層として超格子が用いられる場合には、個々の層24a、24bの厚さは、特定の用途に依存する。普通、個々の層24a、24bの厚さは、約0.001～0.020ミクロンでもよい。上述のように、個々の層の厚さは、転移層12を横断して変えてよい(図3B)。

50

## 【0030】

窒化ガリウム材料層16は、窒化ガリウム(GaN)または、窒化アルミニウム・ガリウム(Al<sub>x</sub>Ga<sub>(1-x)</sub>N)、窒化インジウム・ガリウム(In<sub>y</sub>Ga<sub>(1-y)</sub>N)および窒化アルミニウム・インジウム・ガリウム(Al<sub>x</sub>In<sub>y</sub>Ga<sub>(1-x-y)</sub>N)を含む窒化ガリウムの任意の合金で形成される。窒化ガリウム材料層16の組成は、転移層12を別にして、一般に、その厚さ方向で一定である。かくして、窒化ガリウム材料が上述の混合合金の任意の物で構成されている場合には、一般にxおよびyまたはyは固定される。例えば、成長中の僅かな不均一性および不均質性の結果として、その窒化ガリウム材料層16の組成の小さな変動が起り得ることを理解すべきである。

## 【0031】

特定の推奨される態様では、窒化ガリウム材料層16は、高い濃度のガリウムを含み、そしてアルミニウムおよび/またはインジウムを殆ど、または全く含んでいない。ガリウム濃度の高い態様では、(x+y)の和は、0.4より小さく、0.2より小さく、0.1より小さくてもよく、あるいはより小さいことさえあってもよい。幾つかの場合、窒化ガリウム材料層16の組成は、GaN(即ち、x+y=0)であるのが望ましい。

## 【0032】

上に説明したように、窒化ガリウム材料層16は、シリコン基板と窒化ガリウム材料層との間の熱膨張率の差から生じ得る応力を低減させる転移層12の能力の結果、低い亀裂レベルを有している。本明細書で用いられる“亀裂”(“Crack”)とは、その窒化ガリウム材料の表面に延びている、長さ/幅比が5:1より大きい線状の割れ目または開裂である。亀裂は、その窒化ガリウム材料の全厚さを通して延びてもよく、全厚さにわたってなくともよいと理解されるべきである。“亀裂レベル”(crack level)とは、単位表面積当たりの窒化ガリウム材料中の全ての亀裂の長さの総測定値として定義される。亀裂レベルは $\mu\text{m}/\mu\text{m}^2$ の単位で表される。窒化ガリウム材料の亀裂レベルは、例えば光学顕微鏡法を用いて測定できる。亀裂レベルを求めるためには、所定の面積(即ち、1mm×1mm)中の全ての亀裂の長さを加算し、そしてその総表面積で割る。必要なら、その窒化ガリウム材料全部を代表する測定値を得るために、この操作が、その表面を横断する多数の個所で繰返し行われてもよい。各個所における亀裂レベルを平均すると、その材料の亀裂レベルが得られる。この個所の数は、その窒化ガリウム材料の表面積の量に依存する。窒化ガリウム材料の亀裂レベルを測定する場合、端除外(edge exclusion)として知られているが、材料の端に近い領域では測定しない。名目的な端除外は端から5mmである。かかる領域での端の影響(edge effect)は、亀裂レベルを大きくする可能性があり、普通、デバイス作製においては用いられない。

## 【0033】

窒化ガリウム材料は、低亀裂レベルであるのが好都合である。幾つかの場合には、窒化ガリウム材料層16の亀裂レベルは $0.005\mu\text{m}/\mu\text{m}^2$ 未満である。幾つかの場合には、窒化ガリウム材料は $0.001\mu\text{m}/\mu\text{m}^2$ 未満の非常に低い亀裂レベルを有する。特定の場合には、窒化ガリウム材料層16は、 $0.0001\mu\text{m}/\mu\text{m}^2$ 未満の亀裂レベルで規定されるような実質的に亀裂を含んでいないことが望ましい。

## 【0034】

窒化ガリウム材料層16は、単結晶構造であるのが望ましい。推奨されるケースで、窒化ガリウム材料層16は、ウルツ鉱(六方晶系)構造(Wurtzite structure)をしている。窒化ガリウム材料層全体が、ウルツ鉱構造であるのが望ましい。この窒化ガリウム材料層16は、一般に、それらの中でデバイスの調製が可能なほど十分高品質である。幾つかの態様では、窒化ガリウム材料層16は、例えば、窒化ガリウムとシリコンの間での格子不適合に由来する欠陥の量が比較的少ない(例えば、 $10^9/\text{cm}^2$ 未満)。

## 【0035】

特定の用途での要求により、窒化ガリウム材料層16の厚さが部分的に読み取られる。窒化ガリウム材料がデバイスの層として用いられる用途では、その厚さは、そのデバイスの作製を可能にするのに十分な厚さである。窒化ガリウム材料層16は一般に、0.1ミクロン

10

20

30

40

50

より大きい厚さを有するが、常にではない。他の場合には、0.5ミクロンより厚い、0.75ミクロンより厚い、1.0ミクロンより厚い、2.0ミクロンより厚い、あるいは5.0ミクロンより厚くさえあるようなより厚い窒化ガリウム材料層が希望される。転移層12の存在により、厚い窒化ガリウム材料層16も、低い亀裂密度で得られる。欠陥は、その層を垂直に通り抜けて伝播する時にお互いに潰し合う傾向があるので、比較的厚い窒化ガリウム材料層中では、その層の最上層領域に含まれる欠陥の量が少ない場合がある。かくしてこれらのケースでは、厚い窒化ガリウム材料層を利用して、デバイスの実用性能を向上させることができる。

#### 【0036】

シリコン基板14は、普通、この技術分野で容易に入手できる高品質の単結晶シリコンから調製される。異なる結晶配向を有する複数のシリコン基板14が使用可能である。幾つかの場合にはシリコン(111)基板が推奨される。他の場合にはシリコン(100)基板が推奨される。転移層12を用いて、シリコン(111)基板およびシリコン(100)基板の上にウルツ鉱構造を有する窒化ガリウム材料層16が成長させられてもよい。常用されている方法では、シリコン(100)基板上に成長させると、一般に、亜鉛ブレンド(立方晶系)とウルツ鉱構造の混合物を有する窒化ガリウム材料が得られるので、ウルツ鉱構造を有する窒化ガリウム材料層16が、シリコン(100)基板上に成長し得ることは驚くべきことである。

#### 【0037】

シリコン基板は、この技術分野で用いられているように、任意の寸法を持ち得る。適切な直径は、2インチ、4インチ、6インチおよび8インチであるが、それらに限定されない。幾つかの態様では、シリコン基板14は比較的厚く、例えば250ミクロンより厚い。より厚い基板は、一般に、より薄い基板の場合に起り得る屈曲に抵抗できる。

#### 【0038】

本明細書で用いられる、シリコン基板14とは、シリコン層を含んでいる任意の基板のことである。適したシリコン基板の例に含まれるのは、全体がシリコンで構成されている基板(例えば、バルクシリコン・ウエハ)、絶縁体上シリコン(SOI:silicon-on-insulator)基板、サファイア上シリコン(SOI:silicon-on-saphirer)基板(SOS)およびSIMOX基板、などである。適したシリコン基板には、ダイヤモンド、AINまたは他の多結晶性材料などの別の材料に結合されたシリコン・ウエハを有する基板も含まれる。

#### 【0039】

図5を参照して説明すると、シリコン基板14は、本発明の幾つかの態様に従って、組織加工される(textured)。例示されているように、加工された基板14は、多数のポスト(posts)24を含んでおり、それらの間でトレンチ(trenches)を規定している。このような組織加工(texturing)は、選択的エッティングおよび/または、選択的エピタキシャル成長法を用いて行われる。エッティングは、後で除去することのできるマスクを用いるような、標準的な乾式または湿式エッティング法を用いて行うことができる。幾つかのケースでは、組織加工された基材は、欠陥密度が非常に小さい(例えば $10^7 / \text{cm}^2$ 未満の)窒化ガリウム材料層を成長させるために、本明細書で説明した転移層と組合せて用いられる。シリコン基板14はまた、その基板の領域を選択的に露出させ、一方他の領域を被覆するマスク領域を含ませるために前もってパターン化することができる。このようなプレ・パターン化された基板は、選ばれた領域でエピタキシャル成長させることができ、欠陥密度を最小にするのに好都合である。

#### 【0040】

図6を参照して説明すると、半導体材料10は、本発明のもう一つの態様に従って、シリコン基板14と転移層12の間に中間層28を含んでいる。中間層28は、転移層12と窒化ガリウム材料層16の間に位置している場合もあることを理解すべきである。中間層28は、準備されるなら、窒化ガリウム材料層16中の応力をさらに低減し得る。中間層の厚さは、一般に、約500ミクロン未満であり、幾つかの場合には、約0.01ミクロンと約2.0ミクロンの間である。中間層28が存在すると、転移層12の厚さを低減させることができるのである。この中間層28の組成は、普通、その厚さを通して一定である。

10

20

30

40

50

## 【0041】

中間層28は、例えば、窒化アルミニウム・ガリウム( $Al_x Ga_{(1-x)} N$ )、窒化インジウム・ガリウム( $In_y Ga_{(1-y)} N$ )および窒化アルミニウム・インジウム・ガリウム( $Al_x In_y Ga_{(1-x-y)} N$ )のような $GaN$ の合金から構成されている。これらの場合、中間層での( $x+y$ )の和は、0.4より大きくても、0.6より大きくても、0.8より大きくても、0.9より大きくても、あるいはそれより大きくさえあってもよい。幾つかの推奨されるケースでは、この中間層はガリウムを含まず、そして $Al_x In_y N$ または $Al N$ から構成される。 $GaN$ 濃度の低い $GaN$ 合金中間層は、それらの熱膨張率がシリコン基板14の熱膨張率に比較的近いので、応力を低減するのに有効であり得る。

## 【0042】

この中間層28は、転移層として超格子を用いる態様を含めて本明細書で説明される任意の態様で用い得ることを理解すべきである。転移層12が組成的に勾配を付けた単一層と超格子を含んでいる態様では、その中間層は、その組成的に勾配を付けた層と超格子の間に位置していてもよい。本発明の幾つかの態様では、組成の異なる一つより多い中間層28が準備される場合もある。

## 【0043】

推奨される一つの方法に従って、転移層12と窒化ガリウム材料層16は、金属有機化学蒸着(MOCVD)法を用いて成長させられる。転移層12と窒化ガリウム材料層16を蒸着させるためには、分子ビーム・エピタキシー(MBE)、水素化物気相エピタキシー(HVPE)、および類似の方法を含む、この技術分野で知られている他の適した方法も用い得ることを理解すべきである。

## 【0044】

一般にMOCVD法は、異なる複数の源気体(source gases)を基板の周囲の環境(例えば、工程装置)に導入し、そしてその基板表面上に層を形成させるために、この複数の気体の間の反応を促進する条件を提供することを含む。この反応は、希望の厚さの層が得られるまで進められる。この層の組成は、下でさらに説明されるように、気体の組成、気体の濃度および反応条件(例えば、温度と圧力)を含む数種の因子により制御することができる。この転移層のMOCVD法による成長に適した源気体の例に含まれるのは、アルミニウム源としてのトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)；インジウム源としてのトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)；ガリウム源としてのトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)；および窒素源としてのアンモニア( $NH_3$ )である。用いられる特定の源ガスは、転移層の希望の組成に依存する。例えば、 $Al_x Ga_{(1-x)} N$ の組成を有するフィルムを成長させるためには、アルミニウム源(例えばTMAまたはTEA)、ガリウム源(例えばTMGまたはTEG)および窒素源が用いられる。

## 【0045】

希望の組成を有する転移層を提供するために、複数の源気体の流速、複数の源気体の比および複数の源気体の絶対濃度を制御することができる。 $Al_x Ga_{(1-x)} N$ 層の成長では、TMAの標準的な流速は、約 $5\mu mol/min$ ～約 $50\mu mol/min$ であり、幾つかのケースでは約 $20\mu mol/min$ の流速が推奨され；TMGの標準的な流速は、約 $5\mu mol/min$ ～約 $250\mu mol/min$ であり、幾つかのケースでは約 $115\mu mol/min$ の流速が推奨され；そしてアンモニアの流速は、普通、約 $3s1pm$ ～約 $10s1pm$ である。反応温度は一般に、約 $900$ ～約 $1200$ であり、そして工程圧は、約 $1Torr$ ～約 $760Torr$ の間である。この工程条件、特にその流速は、反応装置の構造に強く依存する。普通、処理能力のより小さい装置は、処理能力のより大きい装置より、必要な流量がより少ない。

## 【0046】

転移層の組成的勾配付けを制御するために、工程パラメータが適切に調整される。この組成は、特別の組成の成長に好都合なように工程条件を変える事により勾配付けされてもよい。例えば、転移層内へのガリウムの取込みを増やし、それによりガリウム濃度を増大させるために、ガリウム源(例えばTMGまたはTEG)の流速および/または濃度を大きくして

10

20

30

40

50

もよい。同様に、転移層内へのアルミニウムの取込みを増やし、それによりアルミニウム濃度を増大させるために、アルミニウム源（例えばTMAまたはTEA）の流速および／または濃度を大きくしてもよい。この源気体の流速および／または濃度を増加（または減少）させる方が組成に勾配を付ける様式を左右する。他の態様では、特別の化合物の成長に好都合なように温度および／または圧力が調整される。転移層内へのガリウムの取込みに好都合な成長温度および圧力は、転移層内へのアルミニウムの取込みに好都合な成長温度および圧力とは異なる。かくしてその組成は、温度と圧力を適切に調整することにより勾配付けをされてもよい。

#### 【0047】

転移層の標準的成长速度は、約 $0.01 \mu\text{m/hr}$ ～約 $3.0 \mu\text{m/hr}$ である。この成長速度は、工程パラメータそしてまたその層の組成に依存する。10

窒化ガリウム材料層（そして存在するなら、中間層）もMOCVD法により成長させられてもよい。このプロセスは、転移層の蒸着のために上に説明したのに類似した源気体とプロセスパラメータを利用できる。希望の組成をベースにして、特定の源気体とプロセスパラメータが選ばれる。しかし、窒化ガリウム材料層（そして存在するなら、中間層）を蒸着させる場合、一定の組成を有するフィルムを提供できるように、プロセスパラメータは、一定に維持される。

#### 【0048】

本発明の半導体材料は、多様な用途に用いることができる。幾つかの場合、半導体材料10は、半導体デバイスを調製するために、既存の方法を用いて加工される。希望する半導体構造物を製造するために、窒化ガリウム材料層16内にドープされた領域を形成させ、そしてその窒化ガリウム材料層の上に追加の層を成長させてもよい。幾つかの態様で、窒化ガリウム材料層16は、希望の導電率を達成するために既知の方法を用いてドーピングされる。20

#### 【0049】

電子デバイスと光学デバイスを含めて、この技術分野で知られている任意の適切な半導体デバイスが、半導体材料10を用いて製造できる。代表的デバイスに含まれるのは、LEDs、レーザ・ダイオード類、FETs（例えばHFETs）などである。

#### 【0050】

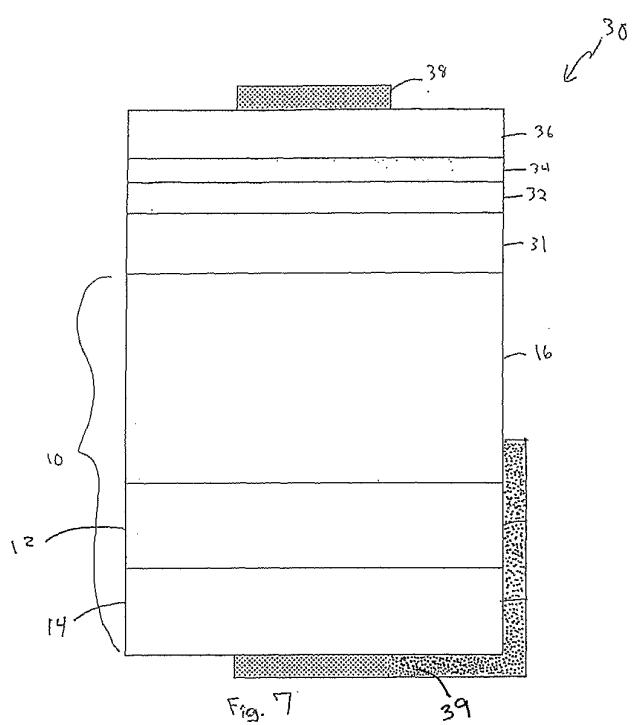

図7は半導体材料10から作られた代表的LED30を模式的に例示している。LED30は、シリコン基板14上の転移層12の上に形成されたシリコンでドープした窒化ガリウム材料層16を含んでいる。この例示実施態様では、以下の複数の層が、順次、窒化ガリウム材料層16の上に形成される：シリコン・ドープ $A_{1-x}Ga_{(1-x)}$  N層31（0-20重量%のA1を含む）、GaN/InGaN单一または多重量子井戸（quantum well）32、マグネシウム・ドープ $A_{1-x}Ga_{(1-x)}$  N層34（10-20重量%のA1を含む）およびマグネシウム・ドープGaN層36。LED30は、マグネシウム・ドープGaN層36の上にp-タイプ金属接点38を、そしてシリコン・ドープ窒化ガリウム材料層16の上にn-タイプ金属接点パッド（metal contact pad）39を含んでいる。LED30は、二重ヘテロ構造（例えば、層31中で $A_1 > 0\%$ ）、单一ヘテロ構造（例えば、層31中で $A_1 = 0\%$ ）、対称構造または非対称構造を含む多様な異なる構造体として提供することができる。3040

#### 【0051】

LEDは、この技術分野での普通の習熟者に知られているような多様な異なる構造を有してもよいことが理解されるべきである。

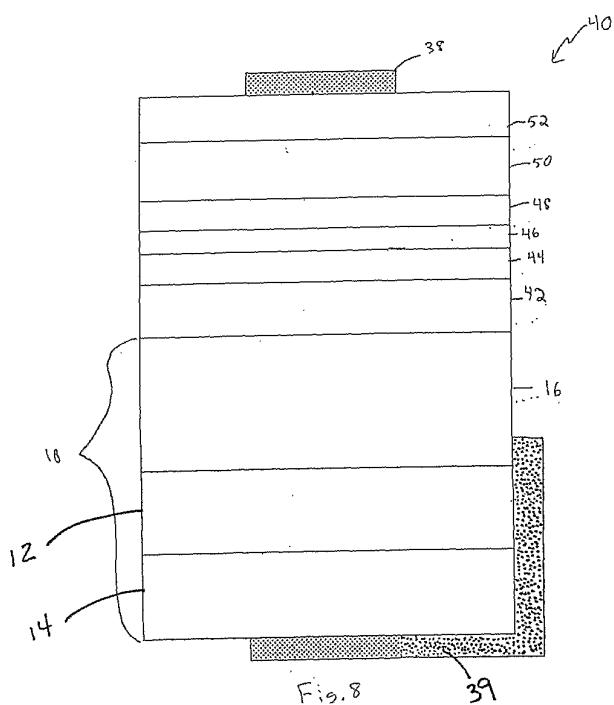

図8は半導体材料10から作られた代表的レーザ・ダイオード40を模式的に例示している。レーザ・ダイオード40は、シリコン基板14上の転移層12の上に形成されたシリコンでドープした窒化ガリウム材料層16を含んでいる。この例示実施態様では、以下の複数の層が、順次窒化ガリウム材料層16の上に形成される：シリコン・ドープ $A_{1-x}Ga_{(1-x)}$  N層42（5-30重量%のA1を含む）、シリコン・ドープ $A_{1-x}Ga_{(1-x)}$  N層44（0-20重量%のA1を含む）、GaN/InGaN单一または多重量子井戸（quantum well）46、マグネシウム・ドープ $A_{1-x}Ga_{(1-x)}$  N層48（5-20重量%のA1を含む50

)、マグネシウム・ドープ  $\text{Al}_x\text{Ga}_{(1-x)}\text{N}$  層 50 (5-30重量%の  $\text{Al}$  を含む) およびマグネシウム・ドープ  $\text{GaN}$  層 52。レーザ・ダイオード 40 は、マグネシウム・ドープ  $\text{GaN}$  層 52 の上に  $p$ -タイプ金属接点 38 を、そしてシリコン・ドープ窒化ガリウム材料層 16 の上に  $n$ -タイプ金属接点パッド 39 を含んでいる。レーザ・ダイオード 40 は、この技術分野での普通の習熟者に知られているような多様な異なる構造を持ち得ると理解されるべきである。

#### 【0052】

図9は、半導体材料10から作られたFET54(例えば、HFET)を模式的に例示している。FET54は、シリコン基板14上の転移層12の上に形成された固有の窒化ガリウム材料層16を含んでいる。FET54は、 $\text{Al}_x\text{Ga}_{(1-x)}\text{N}$ 層56(10-40重量%の  $\text{Al}$  を含む)を含んでいる。FET54は、この技術分野での普通の習熟者に知られているような多様な異なる構造を持ち得ると理解されるべきである。

10

#### 【0053】

本発明のこれらの態様および他の態様の機能と利点は、以下の実施例から、より十分に理解されるであろう。以下の実施例は、本発明の利点を例示することを意図しているが、本発明の全ての範囲を例示するものではない。

#### 【0054】

##### 実施例1：組成的に勾配付けした転移層を利用する窒化ガリウム層の調製

この実施例は、シリコン基板上に成長させた窒化ガリウム材料中の亀裂の数を制限することにおける組成的に勾配付けした転移層の有効性を例示している。

20

#### 【0055】

MOCVD法を用いて、シリコン基板上に、 $\text{AlN}$ 中間層、組成的に勾配付けした $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 転移層および $\text{GaN}$ 層を、順次成長させた。

直径2-インチ、厚さ250ミクロンのシリコン基板をMOCVD装置中に設置した。 $\text{AlN}$ 中間層を成長させるために、トリメチルアルミニウムガス(TMA)をこのMOCVD装置中に、約50 $\mu\text{mol}/\text{min}$ の流速で、そしてアンモニアガス( $\text{NH}_3$ )を約3~約10s1pmの流速で、この装置に導入した。この装置中で、成長温度を約1000-1100 $^{\circ}\text{C}$ の間にそして、成長圧力を30-200Torrの間に保持した。約60分後、このシリコン基板上に、約0.3ミクロンの厚さの $\text{AlN}$ 中間層が形成された。

30

#### 【0056】

中間層の成長後、この装置中にトリメチルガリウム(TM)を約5 $\mu\text{mol}/\text{min}$ の流速で、導入し、TMA:TMの比を約10:1にした。組成的に勾配付けした転移層を成長させるために、TMAの流速を約5 $\mu\text{mol}/\text{min}$ に減らし、一方TMの流速を約115 $\mu\text{mol}/\text{min}$ に増やした。この時間の間に、TMA:TMの比は約10:1から約1:23に低下した。約30分後、約0.4ミクロンの厚さを有する組成的に勾配付けされた転移層が中間層上に成長した。

#### 【0057】

転移層の上に窒化ガリウム層を成長させるために、装置中へのTMAの導入を停止し、そしてTMの流速を約115 $\mu\text{mol}/\text{min}$ に調節した。アンモニアの流速は、約3と約10s1pmの間に維持された。成長温度を約1000-約1050 $^{\circ}\text{C}$ の間に、そして成長圧力を約30-約200Torrの間に維持した。約45分後、組成的に勾配付けされた転移層上に、約1.5ミクロンの厚さの $\text{GaN}$ 層が成長した。この半導体材料は、炉中で室温まで冷却され、そしてMOCVD装置から分析のために取出された。

40

#### 【0058】

得られた半導体材料は、シリコン基板上に形成された0.3ミクロンの $\text{AlN}$ 中間層、この中間層上に形成された0.4ミクロンの厚さの連続的に勾配付けされた $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 転移層、およびこの転移層上に形成された1.5ミクロンの $\text{GaN}$ 層を含んでいた。この $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 転移層の組成は、中間層との接合点での $x=0.8$ から、 $\text{GaN}$ 層との接合点での $x=0$ まで勾配が付いていた。この $\text{GaN}$ 層は単結晶構造であった。

#### 【0059】

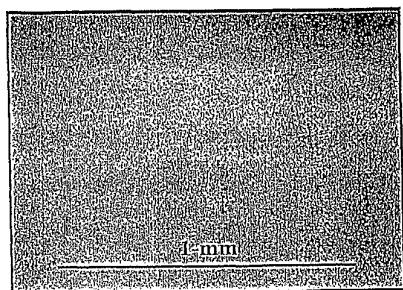

この半導体材料の亀裂レベルを光学顕微鏡法を用いて測定した。この光学顕微鏡は、 $\text{GaN}$

50

N層の表面の顕微鏡写真を撮ることができるカメラを備えていた。図10は、GaN層の表面上の1mm<sup>2</sup>より僅かに大きい代表的領域を示す顕微鏡写真である。この代表的領域中には亀裂は視られない。このGaN層の表面上の他の数個所の部分で測定を繰返し、類似の結果が得られた。この窒化ガリウム材料は、0.0001μm / μm<sup>2</sup>未満の亀裂レベルで定義されるところの、実質的な無亀裂、であることが見出された。

#### 【0060】

この実施例は、組成的に勾配を付けた転移層を用いれば、シリコン基板上に低亀裂レベルの窒化ガリウム層を成長させることができることを例示している。

#### 比較例2：組成的に勾配付けした転移層を利用しない窒化ガリウム層の調製

この例は、組成的に勾配付けした転移層を利用しないシリコン基板上に成長された窒化ガリウム材料中の亀裂の発生を例示している。

#### 【0061】

MOCVD法を用いて、シリコン基板上に、AlN中間層とGaN層を順次成長させた。

直径2インチ、厚さ250ミクロンのシリコン(111)基板を、実施例1で用いられたようなMOCVD装置中に設置した。実施例1での中間層の成長の場合と基本的に同じ加工条件を用いてAlN中間層を成長させた。この中間層上に、実施例1でのGaN層の成長の場合と基本的に同じ加工条件を用いてGaN層を成長させた。組成的に勾配の付いた転移層は成長させなかつた。この半導体材料は、炉内で室温まで冷却され、そしてMOCVD装置から分析のために取出された。

#### 【0062】

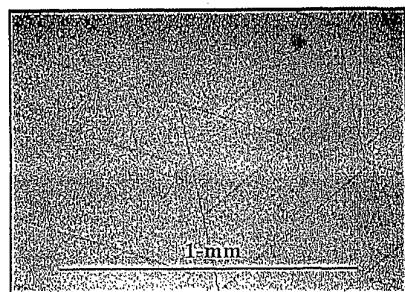

得られた半導体材料は、シリコン基板上に形成された0.3ミクロンのAlN中間層と、この中間層上に形成された1.5ミクロンのGaN層を含んでいた。このGaN層は単結晶構造を有していた。

#### 【0063】

このGaN層の亀裂レベルを、実施例1で説明したのと同じ方法を用いて測定した。図11は、GaN層の表面上の1mm<sup>2</sup>より僅かに大きい代表的領域を示す顕微鏡写真である。この領域中の各亀裂の長さを測定し、そして加算して総亀裂長を求めた。この総亀裂長をその表面積で割って亀裂レベルを求めた。この表面上の数個所の他の位置で測定を繰返し、平均して、このGaN層の亀裂レベル：約0.007μm / μm<sup>2</sup>を得た。

#### 【0064】

この比較例は、組成的に勾配付けした転移層を利用しないシリコン基板上に成長させた窒化ガリウム層中には亀裂が存在することを例示している。

この技術分野の習熟者達は容易に認識するであろうが、本明細書中に列挙した全てのパラメータは、例示であることを意味しており、そして現実のパラメータは、本発明の半導体材料および方法がそのために用いられる特定の用途に依存するであろう。それ故、前述の実施態様は、実施例という方法によってのみ提示されており、そして添付された請求の範囲およびその均等物の範囲内で、本発明は、特定して説明した以外の方法でも実施され得ることが理解されるべきである。

#### 【図面の簡単な説明】

#### 【0065】

【図1】図1は、本発明の一つの態様に従う、組成的に勾配を付けた転移層を含む半導体材料を例示した図である。

【図2】図2A～2Iは、組成的に勾配を付けた転移層を横断する厚さの関数として元素の濃度を示した代表的な分布図である。

【図3】図3Aおよび3Bは、本発明のもう一つの態様に従う、超格子転移層を含む半導体材料を例示した図である。

【図4】図4Aおよび4Bは、それぞれ図3Aおよび3Bの半導体材料中の転移層の厚さの関数として元素の濃度を示した代表的な分布図である。

【図5】本発明の一つの態様に従って半導体材料を調製するために用いられた組織加工した基板(textured substrate)を例示した図である。

10

20

30

40

50

【図6】本発明のもう一つの態様に従う、基板と転移層の間に中間層を含んでいる半導体材料を例示した図である。

【図7】本発明のもう一つの態様に従って、半導体材料から作製されたLEDを例示した図である。

【図8】本発明のもう一つの態様に従って、半導体材料から作製されたレーザ・ダイオードを例示した図である。

【図9】本発明のもう一つの態様に従って、半導体材料から作製されたFETを例示した図である。

【図10】実施例1で説明したような、転移層を有するシリコン基板上に形成された窒化ガリウム層の表面の顕微鏡写真である。

【図11】比較例2で説明したような、転移層を有しないシリコン基板上に形成された窒化ガリウム層の表面の顕微鏡写真である。

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

20 June 2002 (20.06.2002)

PCT

(10) International Publication Number

WO 02/48434 A2

(51) International Patent Classification: C30B 29/40. (81) Designated States (national): AE, AG, AL, AM, AT, AU, 25/18, H01L 21/00 AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

(21) International Application Number: PCT/US01/48426

(22) International Filing Date:

14 December 2001 (14.12.2001)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

09/736,972 14 December 2000 (14.12.2000) US(71) Applicant: NITRONEX CORPORATION [US/US];

628 Hutton Street, Suite 103, Raleigh, NC 27606 (US).

(72) Inventors: WEEKS, T., Warren, Jr., 5716 Lakehaven Drive, Raleigh, NC 27612 (US), PINER, Edwin, L., 112 Franklin Chase Court, Cary, NC 27511 (US), GEHRKE, Thomas, 113 Milky Way Drive, Apex, NC 27502 (US), LINTHICUM, Kevin, J., 474 Cross Link Drive, Angier, NC 27501 (US).

(74) Agent: WALAT, Robert, H. Wolf, Greenfield &amp; Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210 (US).

(54) Title: GALLIUM NITRIDE MATERIALS AND METHODS

WO 02/48434 A2

(57) Abstract: The invention provides semiconductor materials including a gallium nitride material layer formed on a silicon substrate and methods to form the semiconductor materials. The semiconductor materials include a transition layer formed between the silicon substrate and the gallium nitride material layer. The transition layer is compositionally graded to lower stress in the gallium nitride material layer which can result from differences in thermal expansion rates between the gallium nitride material and the substrate. The lowering of stresses in the gallium nitride material layer reduces the tendency of cracks to form. Thus, the invention enables the production of semiconductor materials including gallium nitride material layers having few or no cracks. The semiconductor materials may be used in a number of microelectronic and optical applications.

**GALLIUM NITRIDE MATERIALS AND METHODS****Field of Invention**

The invention relates generally to semiconductor materials and, more particularly, to gallium nitride materials and methods of producing gallium nitride materials.

**Background of Invention**

Gallium nitride materials include gallium nitride (GaN) and its alloys such as aluminum gallium nitride (AlGaN), indium gallium nitride (InGaN), and aluminum indium gallium nitride (AlInGaN). These materials are semiconductor compounds that have a relatively wide, direct bandgap which permits highly energetic electronic transitions to occur. Such electronic transitions can result in gallium nitride materials having a number of attractive properties including the ability to efficiently emit blue light, the ability to transmit signals at high frequency, and others. Accordingly, gallium nitride materials are being widely investigated in many microelectronic applications such as transistors, field emitters, and optoelectronic devices.

In many applications, gallium nitride materials are grown on a substrate. However, differences in the properties between gallium nitride materials and substrates can lead to difficulties in growing layers suitable for many applications. For example, gallium nitride (GaN) has a different thermal expansion coefficient (i.e., thermal expansion rate) than many substrate materials including sapphire, silicon carbide, and silicon. This difference in thermal expansion can lead to cracking of a gallium nitride layer deposited on such substrates when the structure is cooled, for example, during processing. The cracking phenomena can prevent gallium nitride materials from being suitable for use in many applications. Cracking can be particularly problematic for relatively thick (e.g., > 0.5 micron) gallium nitride layers.

Gallium nitride (GaN) also has a different lattice constant than most substrate materials. The difference in lattice constant may lead to the formation of defects in gallium nitride material layers deposited on substrates. Such defects can impair the performance of devices formed using the gallium nitride material layers.

Prior art techniques have been developed to address crack formation and defect formation in gallium nitride materials deposited on sapphire substrates and silicon

carbide substrates. Such techniques, for example, may involve depositing one or more buffer layers on the substrate and, then, depositing the gallium nitride material on the buffer layer(s).

Summary of Invention

5 The invention provides semiconductor materials including a gallium nitride material layer formed on a silicon substrate and methods to form the semiconductor materials. The semiconductor materials include a transition layer formed between the silicon substrate and the gallium nitride material layer. The transition layer is compositionally-graded to lower stresses in the gallium nitride material layer which can

10 result from differences in thermal expansion rates between the gallium nitride material and the substrate. The lowering of stresses in the gallium nitride material layer reduces the tendency of cracks to form which enables the production of semiconductor materials including gallium nitride material layers having few or no cracks. The semiconductor materials may be used in a number of microelectronic and optical

15 applications.

The invention has overcome the problem of growing gallium nitride materials having few or no cracks on silicon substrates which, due to the large differences in both thermal expansion rate and lattice constant between gallium nitride materials (e.g., GaN) and silicon, is considerably more challenging than on other types of substrates

20 (e.g., SiC and sapphire).

In one aspect, the invention provides a semiconductor material. The material includes a substrate including a silicon layer and a compositionally-graded transition layer formed over the substrate. The material further includes a gallium nitride material layer formed over the transition layer.

25 In another aspect, the invention provides a semiconductor material. The semiconductor material includes a substrate including a silicon layer and a gallium nitride material layer formed over the substrate. The gallium nitride material layer has a crack level of less than  $0.005 \mu\text{m}/\mu\text{m}^2$ .

In another aspect, the invention provides a semiconductor structure. The

30 semiconductor structure includes a substrate including a silicon layer, and a gallium nitride material layer formed over the substrate. The gallium nitride material layer has

a thickness of greater than 0.5 micron. The semiconductor structure forms a semiconductor device.

In another aspect, the invention provides a method of producing a semiconductor material. The method includes the steps of forming a compositionally-5 graded transition layer over a substrate including a silicon layer, and forming a gallium nitride material layer over the transition layer.

In another aspect, the invention provides a method of producing a semiconductor material. The method includes forming a gallium nitride material layer formed over a substrate including a silicon layer. The gallium nitride material layer has10 a crack level of less than  $0.005 \mu\text{m}/\mu\text{m}^2$

In another aspect, the invention provides a method of forming a semiconductor structure. The method includes forming a semiconductor structure comprising a substrate including a silicon layer, and a gallium nitride material layer formed over the substrate. The gallium nitride material layer has a thickness of greater than 0.5 micron.

15 In another aspect, the invention provides a semiconductor material. The semiconductor material comprises a silicon (100) substrate and a gallium nitride material layer having a Wurtzite structure formed over the silicon substrate.

Other advantages, aspects, and features of the invention will become apparent from the following detailed description of the invention when considered in20 conjunction with the accompanying drawings.

#### Brief Description of the Drawings

Fig. 1 illustrates a semiconductor material including a compositionally-graded transition layer according to one embodiment of the present invention.

25 Figs. 2A to 2I are exemplary profiles of the concentration of an element as a function of the thickness across the compositionally-graded transition layer.

Figs. 3A and 3B illustrate a semiconductor material that includes a superlattice transition layer according to another embodiment of the present invention.

30 Figs. 4A and 4B are exemplary profiles of the concentration of an element as a function of the thickness of the transition layers in the semiconductor materials of Figs. 3A and 3B, respectively.

Fig. 5 illustrates a textured substrate used to form the semiconductor material according to one embodiment of the present invention.

Fig. 6 illustrates a semiconductor material including an intermediate layer between the substrate and the transition layer according to another embodiment of the 5 present invention.

Fig. 7 illustrates an LED formed from the semiconductor material according to another embodiment of the present invention.

Fig. 8 illustrates a laser diode formed from the semiconductor material according to another embodiment of the present invention.

10 Fig. 9 illustrates a FET formed from the semiconductor material according to another embodiment of the present invention.

Fig. 10 is a micrograph of the surface of a gallium nitride layer formed on a silicon substrate with a transition layer as described in Example 1.

15 Fig. 11 is a micrograph of the surface of a gallium nitride layer formed on a silicon substrate without a transition layer as described in comparative Example 2.

#### Detailed Description of the Invention

The invention provides semiconductor materials including a gallium nitride material layer and a process to produce the semiconductor materials. As used herein, 20 the phrase "gallium nitride material" refers to gallium nitride and any of its alloys, such as aluminum gallium nitride ( $Al_xGa_{(1-x)}N$ ), indium gallium nitride ( $In_yGa_{(1-y)}N$ ), aluminum indium gallium nitride ( $Al_xIn_yGa_{(1-x-y)}N$ ), gallium arsenide phosphide nitride ( $GaAs_xP_bN_{(1-a-b)}$ ), aluminum indium gallium arsenide phosphide nitride ( $Al_xIn_yGa_{(1-x-y)}As_xP_bN_{(1-a-b)}$ ), amongst others. Typically, when present, arsenic and/or phosphorous 25 are at low concentrations (i.e., less than 5 weight percent).

Referring to Fig. 1, a semiconductor material 10 according to one embodiment of the invention is shown. Semiconductor material 10 includes a transition layer 12 formed over a silicon substrate 14 and a gallium nitride material layer 16 formed over the transition layer. As described further below, transition layer 12 is compositionally- 30 graded to reduce internal stresses within gallium nitride material layer 16 that can result from differences between the thermal expansion rates of substrate 14 and the gallium nitride material layer. The internal stresses may arise, for example, when

semiconductor material 10 is cooled after the deposition of gallium nitride material layer 16 and substrate 14 contracts more rapidly than the gallium nitride material layer. As a result of the reduced internal stresses, gallium nitride material layer 16 can be formed with a low crack level making semiconductor material 10 suitable for use in a number of applications including FETs, LEDs, laser diodes, and the like.

It should be understood that when a layer is referred to as being "on" or "over" another layer or substrate, it can be directly on the layer or substrate, or an intervening layer may also be present. It should also be understood that when a layer is referred to as being "on" or "over" another layer or substrate, it may cover the entire layer or 5 substrate, or a portion of the layer or substrate.

As used herein, the term "compositionally-graded layer" refers to a layer having a composition that varies across at least a portion of the thickness of the layer. Thus, transition layer 12 includes at least two different compositions at different depths within the layer. As described further below, the composition of transition layer 12 can 10 be varied in a number of ways. It is generally advantageous to vary the composition of transition layer 12 in a manner that provides sufficient strain relief to limit or prevent the formation of cracks in gallium nitride material layer 16.

According to one set of embodiments, transition layer 12 is composed of an 15 alloy of gallium nitride such as  $Al_xIn_xGa_{(1-x-y)}N$ ,  $Al_xGa_{(1-x)}N$ , and  $In_yGa_{(1-y)}N$ . It should be understood, however, that transition layers having other compositions may also be used. In embodiments which utilize alloys of gallium nitride, the concentration of at 20 least one of the elements (e.g., Ga, Al, In) of the alloy is typically varied across at least a portion of the thickness of the transition layer. When transition layer 12 has an  $Al_xIn_yGa_{(1-x-y)}N$  composition, x and/or y is varied. When transition layer 12 has a 25  $Al_xGa_{(1-x)}N$  composition, x is varied. When transition layer 12 has a  $In_yGa_{(1-y)}N$  composition, y is varied.

In certain preferred embodiments, it is desirable for transition layer 12 to have a 30 low gallium concentration at back surface 18 and a high gallium concentration at front surface 20. It has been found that such transition layers are particularly effective in relieving internal stresses within gallium nitride material layer 16. Decreasing the gallium concentration of a gallium nitride alloy transition layer can make the thermal expansion rate of the alloy more similar to the thermal expansion rate of silicon. As

described further below, gallium nitride material layer 16 typically includes a high gallium concentration. Thus, in these embodiments, increasing the concentration of gallium in transition layer 12 can make the thermal expansion rate of the alloy more similar to the thermal expansion rate of gallium nitride material layer 16. It is believed 5 that in these preferred embodiments effective strain relief is achievable because back surface 18 has a relatively similar thermal expansion rate as substrate 14, while front surface 20 has a relatively similar thermal expansion rate as gallium nitride material layer 16.

In some cases, the sum of (x + y) at back surface 18 is greater than 0.4, greater 10 than 0.6, greater than 0.8 or even higher. In some preferred embodiments, (x + y) = 1 at back surface 18, so that transition layer 12 is free of gallium at the back surface. In some cases, the sum of (x + y) is less than 0.3, less than 0.2, or even less at front 15 surface 20. In some preferred embodiments, the sum of (x + y) = 0 at front surface 20, so that transition layer 12 has a composition of GaN at the front surface. It may be particularly preferred for transition layer 12 to have a composition of GaN at front 20 surface 20, when gallium nitride material layer 16 has a composition of GaN. In other cases when gallium nitride material layer is composed of an alloy of GaN, it may be preferable for the composition of transition layer 12 at front surface 20 to be the same as the composition of gallium nitride material layer 16. In some cases, transition layer 12 is free of gallium at back surface 18 and has a composition of GaN at front surface 20.

It should also be understood that the value of x (i.e., the gallium concentration) may be increased in a direction away from the substrate.

In certain embodiments, it may be preferable for transition layer 12 to comprise 25  $\text{Al}_x\text{Ga}_{(1-x)}\text{N}$ . In these cases, the transition layer is free of indium. In other cases, transition layer 12 may include a small amount of indium, for example, less than 10 percent by weight. When indium is present in transition layer 12 (i.e.,  $\text{Al}_x\text{In}_y\text{Ga}_{(1-x-y)}\text{N}$ ), the concentration of indium (i.e., y) may remain constant throughout the transition layer, while the concentration of gallium and aluminum are graded.

30 The composition in transition layer 12 may be graded across its thickness in a number of different manners. For example, the composition may be graded continuously, discontinuously, across the entire thickness, or across only a portion of

the thickness. As described above, the composition may be graded by varying the concentration of one or more of the elements (i.e., Ga, Al, In). Figs. 2A to 2I illustrate exemplary manners in which the composition may be graded by varying the concentration of one of the elements as a function of thickness across transition layer 12. In certain preferred embodiments, the profiles represent the concentration of gallium across the thickness of transition layer 12, though it should be understood that in other embodiments the profiles may represent the concentration of other elements (i.e., Al or In). The convention in Figs. 2A to 2I is that the thickness of transition layer 12 increases in the direction away from substrate 14 (i.e.,  $t = 0$  at back surface 18 and  $t = 1$  at front surface 20).

Fig. 2A shows a step-wise variation of concentration as a function of thickness which includes multiple steps. Fig. 2B shows a step-wise variation of concentration as a function of thickness which includes two steps. Fig. 2C shows a saw tooth variation of concentration as a function of thickness. Figs. 2D shows continuous variations of concentration at a constant rate as a function of thickness. Fig. 2E shows a continuous variation of concentration at a constant rate starting from a non-zero concentration. Figs. 2F and 2G show continuous variations of concentration as a function of thickness at exponential rates. Fig. 2H shows a discontinuous variation of concentration as a function of thickness. Fig. 2I shows a variation of the concentration across a portion of the thickness of the transition layer.

It should be understood that the profiles illustrated in Figs. 2A to 2I are intended to be exemplary and that the composition of transition layer 12 may be graded in other manners that are within the scope of the present invention.

Referring to Figs. 3A and 3B, transition layer 12 may be a compositionally-graded strained layer superlattice 22 according to another embodiment of the present invention. Superlattice 22 includes alternating layers 24a, 24b of semiconductor compounds having different compositions. In some cases, the composition across each individual layer 24a, 24b is varied according to any of the manners described above. In other cases, the composition of individual layers 24a, 24b is constant across the thickness of the individual layer as shown in the concentration profile of Figs. 4A and 4B. As shown in Fig. 3B (and 4B), the thicknesses of individual layers 24a, 24b is varied across transition layer 12 to provide compositional grading.

It should be understood that superlattice 22 may function as a Bragg reflector in some embodiments of the invention.

In one preferred set of embodiments, superlattice 22 comprises alternating layers of gallium nitride alloys having different compositions. For example, layer 24a 5 has a composition of  $Al_xIn_yGa_{(1-x-y)}N$  and layer 24b has a composition of  $Al_aIn_bGa_{(1-a-b)}N$ , wherein  $x \neq a$  and  $y \neq b$ . In cases when the composition is graded across each individual layer, the concentration of at least one of the elements (i.e., Al, In, Ga) of the alloy can be varied according to any of the manners described above. In cases when the composition of individual layers 24a, 24b is constant (Fig. 3B), the gallium 10 concentration is typically different in individual layers 24a, 24b.

As described above, it may be desirable to have a low gallium concentration at back surface 18 and a high gallium concentration at front surface 20. In embodiments that utilize superlattice 22 as transition layer 12, increasing the gallium concentration in a direction away from back surface 18 can be accomplished by varying the thickness of 15 individual layers. As shown in Figs. 3B and 4B, layer 24a has a low gallium concentration and layer 24b has a high gallium concentration. As shown, layers 24a are relatively thick and layers 24b are relatively thin proximate back surface 18. The thickness of layers 24a is decreased and the thickness of layers 24b is increased in a direction away from back surface 18. Thus, layers 24a are relatively thin and layers 20 24b are relatively thick proximate front surface 20. This structure provides a low gallium concentration at back surface 18 and a high gallium concentration at front surface 20.

It should be understood that transition layer 12 may be formed of a combination of a single layer having a graded composition and a superlattice. In some cases, the 25 superlattice is formed over the single compositionally-graded layer. In other cases, the single compositionally-graded layer is formed over the superlattice.

Transition layer 12 can have a variety of thicknesses depending on the application. Generally, though not always, transition layer 12 has a thickness of less than about 500 microns. In some cases, relatively thick transition layers are preferable, 30 for example between about 2.0 microns and about 20 microns. Thick transition layers may be preferred when thick gallium nitride material layers (i.e., greater than 5 microns) are produced. In some cases, relatively thin transition layers are preferable,

for example between about 0.03 micron and about 2.0 microns. When superlattice structures are used as transition layers, the thickness of individual layers 24a, 24b depends upon the particular application. Typically the thickness of individual layers 24a, 24b may be between about 0.001 microns and about 0.020 microns. As described above, the thicknesses of individual layers may vary across transition layer 12 (Fig. 3B).

Gallium nitride material layer 16 is formed of gallium nitride (GaN) or any of its alloys including aluminum gallium nitride ( $Al_xGa_{(1-x)}N$ ), indium gallium nitride ( $In_yGa_{(1-y)}N$ ), and aluminum indium gallium nitride ( $Al_xIn_yGa_{(1-x-y)}N$ ). The composition of gallium nitride material layer 16 is generally constant across its thickness as distinguished with transition layer 12. Thus, x and/or y are generally fixed when gallium nitride material is formed of any of the aforementioned compound alloys. It should be understood that small variations in the composition of gallium nitride material layer 16 may occur, for example, as a result of slight non-uniformities and inhomogeneities during growth.

In certain preferred embodiments, gallium nitride material layer 16 has a high concentration of gallium and includes little or no amounts of aluminum and/or indium. In high gallium concentration embodiments, the sum of (x + y) may be less than 0.4, less than 0.2, less than 0.1, or even less. In some cases, it is preferable for gallium nitride material layer 16 to have a composition of GaN (i.e., x + y = 0).

As described above, gallium nitride material layer 16 has a low crack level as a result of the ability of transition layer 12 to relieve stress arising from differences in thermal expansion rates between the silicon substrate and the gallium nitride material. A "crack," as used herein, is a linear fracture or a cleavage having a length to width ratio of greater than 5:1 that extends to the surface of the gallium nitride material. It should be understood that a crack may or may not extend through the entire thickness of the gallium nitride material. "Crack level" is defined as a total measure of all crack lengths in a gallium nitride material per unit surface area. Crack level can be expressed in units of  $\mu m/\mu m^2$ . The crack level of a gallium nitride material can be measured, for example, using optical microscopy techniques. To determine the crack level, the length of all of the cracks in a given area (i.e., 1 mm x 1 mm) are added together and divided by the total surface area. If necessary, this process may be repeated at a number of

-10-

locations across the surface to provide a measurement representative of the entire gallium nitride material. The crack level at each location may be averaged to provide a crack level for the material. The number of locations depends upon the amount of surface area of the gallium nitride material. When measuring the crack level of a gallium nitride material, measurements are not made within a region proximate to edges of the material known as an edge exclusion. The nominal edge exclusion is 5 mm from the edge. Edge effects in such regions may lead to increased crack levels and are typically not used to in device formation.

Gallium nitride material layer 16 advantageously has a low crack level. In some cases, gallium nitride material layer 16 has a crack level of less than  $0.005 \mu\text{m}/\mu\text{m}^2$ . In some cases, gallium nitride material has a very low crack level of less than  $0.001 \mu\text{m}/\mu\text{m}^2$ . In certain cases, it may be preferable for gallium nitride material layer 16 to be substantially crack-free as defined by a crack level of less than  $0.0001 \mu\text{m}/\mu\text{m}^2$ .

Gallium nitride material layer 16 preferably has a monocrystalline structure. In preferred cases, gallium nitride material layer 16 has a Wurtzite (hexagonal) structure. Preferably, the entire gallium nitride material layer has a Wurtzite structure. The gallium nitride material layer 16 is generally of high enough quality so as to permit the formation of devices therein. In some embodiments, gallium nitride material layer 16 has a relatively low amount of defects (e.g., less than  $10^9 \text{ cm}^{-2}$ ) which, for example, result from the lattice mismatch between gallium nitride and silicon.

The thickness of gallium nitride material layer 16 is dictated, in part, by the requirements of the specific application. In applications when gallium nitride material is used as a device layer, the thickness is sufficient to permit formation of the device. Gallium nitride material layer 16 generally has a thickness of greater than 0.1 micron, though not always. In other cases, thicker gallium nitride material layers are desired such as thicknesses greater than 0.5 micron, greater than 0.75 micron, greater than 1.0 microns, greater than 2.0 microns, or even greater than 5.0 microns. Even thick gallium nitride material layers 16 are achievable at low crack densities because of the presence of transition layer 12. In relatively thick gallium nitride layers, upper regions of the layer may include low amounts of defects due to the tendency of defects to annihilate one another as they propagate vertically through the layer. Thus, in these cases, the use of thick gallium nitride layers may improve device performance.

Silicon substrate 14 typically is formed of high-quality single-crystal silicon as readily available in the art. Silicon substrates 14 having different crystallographic orientations may be used. In some cases, silicon (111) substrates are preferred. In other cases, silicon (100) substrates are preferred. Gallium nitride material layer 16 having a Wurtzite structure may be grown on silicon (111) substrates and silicon (100) substrates using transition layer 12. It is particularly surprising that gallium nitride material layer 16 having a Wurtzite structure may grow on silicon (100) substrates because conventional techniques generally result in gallium nitride materials having a mixture of zinc blend (cubic) and Wurtzite structures when grown on silicon (100) substrates.

10 Silicon substrate may have any dimensions as used in the art. Suitable diameters include, but are not limited to, 2 inches, 4 inches, 6 inches, and 8 inches. In some embodiments, silicon substrate 14 is relatively thick, for example, greater than 250 microns. Thicker substrates are generally able to resist bending which can occur, 15 in some cases, in thinner substrates.

As used herein, silicon substrate 14 refers to any substrate that includes a silicon layer. Examples of suitable silicon substrates include substrates that are composed entirely of silicon (e.g., bulk silicon wafers), silicon-on-insulator (SOI) substrates, silicon-on-sapphire substrate (SOS), and SIMOX substrates, amongst others. Suitable 20 silicon substrates also include substrates that have a silicon wafer bonded to another material such as diamond, AlN, or other polycrystalline materials.

Referring to Fig. 5, silicon substrate 14 is textured according to some 25 embodiments of the present invention. As illustrated, textured substrate 14 includes a plurality of posts 24 which define trenches 26 therebetween. Such texturing can be provided using selective etching and/or selective epitaxial growth. Etching may be 30 performed using standard dry or wet etching techniques, such as with a mask which later may be removed. In some cases, textured substrates are used in conjunction with the transition layers described herein to grow gallium nitride material layers with very low defect densities (e.g., less than  $10^7 \text{ cm}^{-2}$ ). Silicon substrate 14 may also be pre-patterned to include mask areas which selectively expose regions of the substrate, while covering other regions. Such pre-patterned substrates enable selective area epitaxial growth which may be advantageous in minimizing defect densities.

-12-

Referring to Fig. 6, semiconductor material 10 includes an intermediate layer 28 between silicon substrate 14 and transition layer 12 according to another embodiment of the present invention. It should be understood that intermediate layer 28 may also be positioned between transition layer 12 and gallium nitride material layer 16.

5 Intermediate layer 28, when provided, may further relieve stress in gallium nitride material layer 16. Intermediate layer generally has a thickness of less than about 500 microns and, in some cases, between about 0.01 micron and about 2.0 microns. The presence of intermediate layer 28 may permit reduction of the thickness of transition layer 12. The composition of the intermediate layer is generally constant throughout its

10 thickness.

Intermediate layer 28, for example, can be composed of a GaN alloy such as aluminum gallium nitride ( $Al_xGa_{(1-x)}N$ ), indium gallium nitride ( $In_yGa_{(1-y)}N$ ), and aluminum indium gallium nitride ( $Al_xIn_yGa_{(1-x-y)}N$ ). In these cases, the sum of ( $x + y$ ) in the intermediate layer may be greater than 0.4, greater than 0.6, greater than 0.8, greater than 0.9, or even more. In some preferred cases, the intermediate layer is free of gallium and is composed of  $Al_xIn_yN$  or AlN. GaN alloy intermediate layers with low Ga concentrations may be effective at relieving stresses because they have a thermal expansion rate relatively close to the thermal expansion rate of silicon substrate 14.

It should be understood that intermediate layer 28 may be utilized in accordance with any of the embodiments described herein including embodiments that use a superlattice as a transition layer. In embodiments in which transition layer 12 includes a single compositionally-graded layer and a superlattice, the intermediate layer may be positioned between the compositionally-graded layer and the superlattice. In some embodiments of the invention, more than one intermediate layer 28 having different compositions may be provided.

According to one preferred method, transition layer 12 and gallium nitride material layer 16 are grown using a metalorganic chemical vapor deposition (MOCVD) process. It should be understood that other suitable techniques known in the art may also be utilized to deposit transition layer 12 and gallium nitride material layer 16

30 including molecular beam epitaxy (MBE), hydride vapor phase epitaxy (HVPE), and the like.

Generally, the MOCVD process involves introducing different source gases into an environment (e.g., a process system) around a substrate and providing conditions which promote a reaction between the gases to form a layer on the substrate surface. The reaction proceeds until a layer of desired thickness is achieved. The composition 5 of the layer may be controlled, as described further below, by several factors including gas composition, gas concentration, and the reaction conditions (e.g. temperature and pressure).

Examples of suitable source gases for MOCVD growth of the transition layer include trimethylaluminum (TMA) or triethylaluminum (TEA) as sources of aluminum; 10 trimethylindium (TMI) or triethylindium (TEI) as sources of indium; trimethylgallium (TMG) or trimethylgallium (TEG) as sources of gallium; and ammonia (NH<sub>3</sub>) as a source of nitrogen. The particular source gas used depends upon the desired composition of the transition layer. For example, an aluminum source (e.g., TMA or TEA), a gallium source (TMG or TEG), and a nitrogen source are used to deposit films 15 having an Al<sub>x</sub>Ga<sub>1-x</sub>N composition.

The flow rates of the source gases, the ratios of the source gases, and the absolute concentrations of the source gases may be controlled to provide transition layers having the desired composition. For the growth of Al<sub>x</sub>Ga<sub>1-x</sub>N layers, typical 20 TMA flow rates are between about 5  $\mu\text{mol}/\text{min}$  and about 50  $\mu\text{mol}/\text{min}$  with a flow rate of about 20  $\mu\text{mol}/\text{min}$  being preferred in some cases; typical TMG flow rates are between about 5  $\mu\text{mol}/\text{min}$  and 250  $\mu\text{mol}/\text{min}$ , with a flow rate of 115  $\mu\text{mol}/\text{min}$  being preferred in some cases; and the flow rate of ammonia is typically between about 3 slpm to about 10 slpm. The reaction temperatures are generally between about 900°C and about 1200°C and the process pressures are between about 1 Torr and about 760 25 Torr. It is to be understood that the process conditions, and in particular the flow rate, are highly dependent on the process system configuration. Typically, smaller throughput systems require less flow than larger throughput systems.

Process parameters are suitably adjusted to control the compositional grading of the transition layer. The composition may be graded by changing the process 30 conditions to favor the growth of particular compositions. For example, to increase incorporation of gallium in the transition layer thereby increasing the gallium concentration, the flow rate and/or the concentration of the gallium source (e.g., TMG

WO 02/48434

PCT/US01/48426

-14-

or TEG) may be increased. Similarly, to increase incorporation of aluminum into the transition layer thereby increasing the aluminum concentration, the flow rate and/or the concentration of the aluminum source (e.g., TMA or TEA) may be increased. The manner in which the flow rate and/or the concentration of the source is increased (or 5 decreased) controls the manner in which the composition is graded. In other embodiments, the temperature and/or pressure is adjusted to favor the growth of a particular compound. Growth temperatures and pressures favoring the incorporation of gallium into the transition layer differ from the growth temperatures and pressures favoring the incorporation of aluminum into the transition layer. Thus, the composition 10 may be graded by suitably adjusting temperature and pressure.

Typical growth rates of the transition layer are between about 0.01 $\mu$ m/hr and about 3.0  $\mu$ m/hr. The growth rate depends upon the process parameters as well as the composition of the layer.

The gallium nitride material layer (and intermediate layers, if present) may also 15 be grown using an MOCVD process. The process may utilize source gases and process parameters similar to those described above for the deposition of the transition layer. The particular source gases and process parameters are selected based upon the desired composition. When depositing the gallium nitride material layer (or the intermediate 20 layer), however, the process parameters are maintained constant so as to provide a film having a constant composition.

The semiconductor materials of the invention may be used in a variety of 25 applications. In some cases, semiconductor material 10 is processed using known techniques to form a semiconductor device. Doped regions may be formed within gallium nitride material layer 16 and additional layers may be deposited upon the gallium nitride material layer to produce the desired semiconductor structure. In some 30 embodiments, gallium nitride material layer 16 is doped using known techniques to achieve a desired conductivity.

Any suitable semiconductor device known in the art including electronic and 35 optical devices can be produced using semiconductor material 10. Exemplary devices include LEDs, laser diodes, FETs (e.g., HFETs) amongst others.

Fig. 7 schematically illustrates an exemplary LED 30 formed from 30 semiconductor material 10. LED 30 includes silicon-doped gallium nitride material

layer 16 formed on transition layer 12 on silicon substrate 14. In the illustrative embodiment, the following layers are formed on gallium nitride material layer 16 in succession: a silicon-doped  $Al_xGa_{(1-x)}N$  layer 31 (containing 0-20% by weight Al), a GaN/InGaN single or multiple quantum well 32, a magnesium-doped  $Al_xGa_{(1-x)}N$  layer 34 (containing 10-20% by weight Al), and a magnesium-doped GaN layer 36. LED 30 includes a p-type metal contact 38 on magnesium-doped GaN layer 36 and an n-type metal contact pad 39 on silicon-doped gallium nitride material layer 16. LED 30 may be provided as a variety of different structure including: a double heterostructure (e.g., Al > 0% in layer 31), a single heterostructure (e.g., Al = 0% in layer 31), a symmetric structure, or an asymmetric structure. It should be understood that LED may have a variety of different structures as known to those of ordinary skill in the art.

Fig. 8 schematically illustrates an exemplary laser diode 40 formed from semiconductor material 10. Laser diode 40 includes silicon-doped gallium nitride material layer 16 formed on transition layer 12 on silicon substrate 14. In the illustrative embodiment, the following layers are formed on gallium nitride material layer 16 in succession: a silicon-doped  $Al_xGa_{(1-x)}N$  layer 42 (containing 5-30% by weight Al), a silicon-doped  $Al_xGa_{(1-x)}N$  layer 44 (containing 0-20% by weight Al), a GaN/InGaN single or multiple quantum well 46, a magnesium-doped  $Al_xGa_{(1-x)}N$  layer 48 (containing 5-20% by weight Al), a magnesium-doped  $Al_xGa_{(1-x)}N$  layer 50 (containing 5-30% by weight Al), and a magnesium-doped GaN layer 52. Laser diode 40 includes a p-type metal contact 38 on magnesium-doped GaN layer 52 and an n-type metal contact pad 39 on silicon-doped gallium nitride material layer 16. It should be understood that laser diode 40 may have a variety of different structures as known to those of ordinary skill in the art.

Fig. 9 schematically illustrates a FET 54 (e.g., HFET) formed from semiconductor material 10. FET 54 includes intrinsic gallium nitride material layer 16 formed on transition layer 12 on silicon substrate 14. FET 54 includes an  $Al_xGa_{(1-x)}N$  layer 56 (containing 10-40% by weight Al). It should be understood that FET 54 may have a variety of different structures as known to those of ordinary skill in the art.

The function and advantage of these and other embodiments of the present invention will be more fully understood from the examples below. The following

examples are intended to illustrate the benefits of the present invention, but do not exemplify the full scope of the invention.

Example 1: Production of Gallium Nitride Layer Using A Compositinally Graded

5 Transition Layer

This example illustrates the effectiveness of a compositionally-graded transition layer in limiting the number of cracks in a gallium nitride material grown on a silicon substrate.

An MOCVD process was used to grow an AlN intermediate layer, an  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  10 compositionally-graded transition layer, and a GaN layer in succession on a silicon substrate.

A silicon substrate having a 2-inch diameter and a thickness of 250 microns was positioned in an MOCVD system. To grow the AlN intermediate layer, trimethylaluminum gas (TMA) was introduced into the MOCVD system at a flow rate 15 of about 50  $\mu\text{mol}/\text{min}$  and ammonia gas ( $\text{NH}_3$ ) was introduced into the system at a flow rate of between about 3 and about 10 slpm. A growth temperature of between about 1000-1100°C and a growth pressure 30-200 Torr were maintained in the system. After about 60 minutes, an AlN intermediate layer was formed having a thickness of about 0.3 micron on the silicon substrate.

20 After the growth of the intermediate layer, trimethylgallium (TMG) was introduced into the system at a flow rate of about 5  $\mu\text{mol}/\text{min}$  to provide a ratio of TMA:TMG of about 10:1. To form the compositionally-graded transition layer, the flow rate of the TMA was decreased to about 5  $\mu\text{mol}/\text{min}$ , while the flow rate of TMG was increased to about 115  $\mu\text{mol}/\text{min}$ . Over this time, the ratio of TMA:TMG was 25 decreased from about 10:1 to about 1:23. After about 30 minutes, a compositionally-graded transition layer having a thickness of about 0.4 micron was grown on the intermediate layer.

To grow the gallium nitride layer on the transition layer, the introduction of TMA into the system was stopped and the TMG flow rate was adjusted to about 115 30  $\mu\text{mol}/\text{min}$ . The flow rate of ammonia was maintained between about 3 and about 10 slpm. The growth temperature was maintained between about 1000 and about 1050°C and the growth pressure between about 30 and about 200 Torr. After about 45 minutes,

-17-

a GaN layer having a thickness of about 1.5 micron was grown on the compositionally-graded transition layer. The semiconductor material was furnace-cooled to room temperature and removed from the MOCVD system for analysis.

The resulting semiconductor material included a 0.3 micron AlN intermediate layer formed on the silicon substrate; a 0.4 micron thick continuously graded  $Al_xGa_{1-x}N$  transition layer formed on the intermediate layer; and a 1.5 micron GaN layer grown on the transition layer. The composition of the  $Al_xGa_{1-x}N$  transition layer was graded from  $x = 0.8$  at the juncture with the intermediate layer to  $x = 0$  at the juncture with the GaN layer. The GaN layer had a monocrystalline structure.

10 The crack level of the semiconductor material was measured using an optical microscopic technique. The microscope was equipped with the camera capable of taking micrographs of the surface of the GaN layer. Fig. 10 is a micrograph showing a representative area of slightly greater than 1 mm<sup>2</sup> on the surface of the GaN layer. No cracks are visible in the representative area. Measurements were repeated at several 15 other locations on the surface of the GaN layer and similar results were achieved. The gallium nitride material was found to be substantially crack-free as defined by a crack level of less than 0.0001  $\mu m/\mu m^2$ .

This example illustrates the ability to grow gallium nitride layers having a low crack level on a silicon substrate using a compositionally-graded transition layer.

20 Comparative Example 2: Production of Gallium Nitride Layer Without Using A Compositonally Graded Transition Layer

This example illustrates the generation of cracks in a gallium nitride material grown on a silicon substrate without using a compositionally-graded transition layer.

25 An MOCVD process was used to grow an AlN intermediate layer and a GaN layer in succession on a silicon substrate.

A silicon (111) substrate having a 2-inch diameter and a thickness of 250 microns was positioned in the same MOCVD system as used in Example 1. An AlN intermediate layer was formed using essentially the same processing conditions as the 30 growth of the intermediate layer in Example 1. A GaN layer was grown on the intermediate layer using essentially the same processing conditions as the growth of the GaN layer in Example 1. A compositionally-graded transition layer was not grown.

WO 02/48434

PCT/US01/48426

-18-

The semiconductor material was furnace-cooled to room temperature and removed from the MOCVD system for analysis.

The resulting semiconductor material included a 0.3 micron AlN intermediate layer formed on the silicon substrate, and a 1.5 micron GaN layer grown on the 5 intermediate layer. The GaN layer had a monocrystalline structure.

The crack level of the GaN layer was measured using the same technique as described in Example 1. Fig. 11 is a micrograph showing a representative area of slightly greater than 1 mm<sup>2</sup> on the surface of the GaN layer. The length of each crack in the area was measured and added together to determine the total crack length. The 10 total crack length was divided by the surface area to determine the crack level.

Measurements were repeated at several other locations on the surface which were averaged to provide a crack level of the GaN layer of about 0.007  $\mu\text{m}/\mu\text{m}^2$ .

This comparative example illustrates the presence of cracks in gallium nitride layers grown on a silicon substrate without using a compositionally-graded transition 15 layer.

Those skilled in the art would readily appreciate that all parameters listed herein are meant to be exemplary and that the actual parameters would depend upon the specific application for which the semiconductor materials and methods of the 20 invention are used. It is, therefore, to be understood that the foregoing embodiments are presented by way of example only and that, within the scope of the appended claims and equivalents thereto the invention may be practiced otherwise than as specifically described.

What is claimed is:

CLAIMS

1. A semiconductor material comprising:

a substrate including a silicon layer;

5 a compositionally-graded transition layer formed over the substrate; and

a gallium nitride material layer formed over the transition layer.

2. The semiconductor material of claim 1, wherein the composition of the transition layer is graded continuously across the thickness of the layer.

- 10 3. The semiconductor material of claim 1, wherein the composition of the transition layer is graded discontinuously across the thickness of the layer.

4. The semiconductor material of claim 1, wherein the transition layer comprises

15 an alloy of gallium nitride selected from the group consisting of  $Al_xIn_yGa_{(1-x-y)}N$ ,

$In_yGa_{(1-y)}N$ , and  $Al_xGa_{(1-x)}N$ .