## (12) 发明专利

(10) 授权公告号 CN 109716601 B

(45) 授权公告日 2022.12.13

(21) 申请号 201780055997.2

(74) 专利代理机构 北京集佳知识产权代理有限公司 11227

(22) 申请日 2017.08.08

专利代理人 康建峰 杨华

(65) 同一申请的已公布的文献号

申请公布号 CN 109716601 A

(51) Int.CI.

H01S 5/183 (2006.01)

(43) 申请公布日 2019.05.03

H01S 5/20 (2006.01)

(30) 优先权数据

H01S 5/42 (2006.01)

62/372,126 2016.08.08 US

(85) PCT国际申请进入国家阶段日

2019.03.12

(56) 对比文件

US 2015222094 A1, 2015.08.06

(86) PCT国际申请的申请数据

US 2004264541 A1, 2004.12.30

PCT/US2017/045965 2017.08.08

CN 104412148 A, 2015.03.11

(87) PCT国际申请的公布数据

CN 103548220 A, 2014.01.29

W02018/031582 EN 2018.02.15

CN 1917312 A, 2007.02.21

(73) 专利权人 菲尼萨公司

CN 1917312 A, 2007.02.21

地址 美国加利福尼亚州

US 5373520 A, 1994.12.13

(72) 发明人 卢克·格拉哈姆 安迪·麦金尼斯

US 8774246 B1, 2014.07.08

CN 103548220 A, 2014.01.29

US 2003185267 A1, 2003.10.02

审查员 周冠锐

权利要求书2页 说明书12页 附图8页

(54) 发明名称

形成阻挡芯。这种提供用于VCSEL的当前孔避免了通过VCSEL的台面中的层的横向氧化而提供的当前孔的可靠性问题。

经蚀刻的平坦化的竖直腔表面发射激光器

CN 109716601 B

一种经蚀刻的平坦化的VCSEL包括：包括MQW (138,140) 的有源区 (122)；在有源区上方的阻挡区 (127,160)，其可以由InGaP制成，并且在其中限定孔；孔中的导电沟道芯 (129,162)，其可以由AlGaAs制成，其中，导电沟道芯和阻挡区形成隔离区 (128)。VCSEL可以包括间隔层 (148,150)。一种制造VCSEL的方法包括：形成有源区；在有源区上方形成阻挡区；在阻挡区中蚀刻孔；以及在阻挡区的孔中形成导电沟道芯。另一种经蚀刻的平坦化的VCSEL包括：有源区；在有源区上方的导电区，且在其中限定孔；以及在孔中的阻挡芯，其中，阻挡芯和导电区形成隔离区。一种制造VCSEL的方法包括：形成有源区；在有源区上方形成导电区；在导电区中蚀刻孔；以及在导电区的孔中

1. 一种经蚀刻的平坦化的竖直腔表面发射激光器VCSEL阵列，包括：

有源区；

隔离区，包括：

在所述有源区上方的阻挡区，所述阻挡区在其中限定多个孔，其中，所述多个孔横向布置在所述阻挡区中，其中，所述阻挡区包括具有第一折射率并且没有氧化的第一材料；

在所述阻挡区的所述多个孔中的多个导电沟道芯，其中，每个导电沟道芯包括具有第二折射率并且没有氧化的第二材料，其中，所述第一折射率小于所述第二折射率；

设置在所述阻挡区和所述多个导电沟道芯上方的整体导电翼层，其中，所述整体导电翼层与所述多个导电沟道芯的顶部接触并且包括具有高于所述第二折射率的折射率的材料；

在所述有源区和所述多个导电沟道芯下方的底部反射镜区；

在所述隔离区和所述多个导电沟道芯上方的顶部反射镜区；以及

用于所述多个导电沟道芯的顶部发光表面，

其中，所述多个导电沟道芯、所述顶部反射镜区的反射镜层以及所述顶部发光表面是平坦化的，并且

其中，所述VCSEL阵列没有台面。

2. 根据权利要求1所述的VCSEL阵列，其中，所述阻挡区具有1nm到500nm的厚度，并且每个导电沟道芯具有1微米到10微米的直径。

3. 根据权利要求1所述的VCSEL阵列，其中，所述VCSEL阵列没有：氧化物孔；以及氧化。

4. 根据权利要求1所述的VCSEL阵列，其中，所述多个导电沟道芯彼此分隔开1微米到10微米。

5. 根据权利要求1所述的VCSEL阵列，其中，所述阻挡区是InGaP，并且所述多个导电沟道芯是AlGaAs。

6. 根据权利要求1所述的VCSEL阵列，其中，每个导电沟道芯具有中心点，并且每个中心点之间的距离为2微米到6微米。

7. 一种制造根据权利要求1所述的VCSEL阵列的方法，包括：

在衬底上方形成所述有源区；

在所述有源区上方形成所述阻挡区，其中，所述阻挡区包括具有第一折射率并且没有氧化的第一材料；

在所述阻挡区中蚀刻所述多个孔；

在所述阻挡区的所述多个孔中形成所述多个导电沟道芯，其中，每个导电沟道芯包括具有第二折射率并且没有氧化的第二材料，其中，所述第一折射率小于所述第二折射率；

在所述阻挡区和所述多个导电沟道芯上方形成所述整体导电翼层以与所述多个导电沟道芯的顶部接触，所述整体导电翼层在所述多个导电沟道芯之间延伸并且连接所述多个导电沟道芯；

在所述整体导电翼层和所述多个导电沟道芯上方形成所述顶部反射镜区；以及

使所述多个导电沟道芯、所述顶部反射镜区以及发光表面平坦化。

8. 根据权利要求7所述的方法，还包括：

使用抑制蚀刻的化学试剂涂覆所述阻挡区的顶部，同时留下没有所述化学试剂的多个

区；以及

在所述阻挡区中在没有所述化学试剂的所述多个区中蚀刻所述多个孔。

9. 根据权利要求8所述的方法,还包括:通过MOCVD、使用所述多个导电沟道芯填充所述阻挡区中的所述多个孔。

10. 根据权利要求8所述的方法,还包括:

在蚀刻以形成所述多个孔之后并且在使用所述多个导电沟道芯填充所述多个孔之前,去除抑制蚀刻的所述化学试剂。

11. 根据权利要求7所述的方法,还包括:形成所述导电沟道芯以贯穿所述阻挡区并且与所述有源区接触或者与在所述有源区上方的顶部间隔区接触。

12. 根据权利要求7所述的方法,还包括:在公共阻挡区中形成多个所述导电沟道芯。

13. 根据权利要求9所述的方法,还包括:使所述多个导电沟道芯的顶表面平坦化。

## 经蚀刻的平坦化的竖直腔表面发射激光器

[0001] 对相关申请的交叉引用

[0002] 本专利申请要求于2016年8月8日提交的美国临时申请第62/372,126号的优先权，该临时申请的全部内容通过特定引用并入本文。

### 背景技术

[0003] 激光器通常用在许多用于数据传输的现代通信组件中。一种已经变得更普遍的用途是激光器在数据网络中的使用。激光器用于许多光纤通信系统以在网络上传输数字数据。在一个示例性配置中，可以通过数字数据对激光器进行调制以产生包括表示二进制数据流的亮输出和暗输出的时段的光信号。在实际实践中，激光器输出表示二进制高的高的光输出和表示二进制低的低功率光输出。为了获得快速的反应时间，激光器始终开启，只从高的光输出到低的光输出变化。

[0004] 与诸如基于铜线的网络的其他类型的网络相比，光网络具有各种优点。例如，许多现有的铜线网络以针对铜线技术的近最大可行数据传输速率和近最大可行距离操作。另一方面，许多现有的光网络在数据传输速率和距离方面都超过了针对铜线网络可行的最大值。也就是说，光网络能够在比铜线网络可行的更远距离以更高速率可靠地传输数据。

[0005] 在光学数据传输中使用的一种类型的激光器是竖直腔面发射激光器(VCSEL)。VCSEL具有夹在两个反射镜叠层之间并由两个反射镜叠层限定的激光腔。VCSEL通常构造在诸如砷化镓(GaAs)的半导体晶片上。VCSEL包括构造在半导体晶片上的底部反射镜。通常，底部反射镜包括多个交替的高折射率层和低折射率层。当光从具有一个折射率的层穿过至具有另一折射率的层时，光的一部分被反射。通过使用足够数量的交替层，可以通过反射镜反射高百分比的光。

[0006] 底部反射镜上形成有包括多个量子阱的有源区。有源区形成夹在底部反射镜与顶部反射镜之间的PN结，底部反射镜和顶部反射镜具有相反的导电类型(例如，一个p型反射镜和一个n型反射镜)。值得注意的是，顶部反射镜和底部反射镜的概念在一定程度上可以是任意的。在一些结构中，可以从VCSEL的晶片侧提取光，其中，“顶部”反射镜是完全反射的——并且因此顶部反射镜是不透明的。然而，出于本发明的目的，“顶部”反射镜指的是从其提取光的反射镜，而不管其在物理结构中如何设置。当PN结通过电流正向偏置时，空穴和电子形式的载流子被注入到量子阱中。在足够高的偏置电流下，被注入的少数载流子在量子阱中形成产生光增益的粒子数反转。当有源区中的光子激发电子与导带中的空穴重新结合到价带——产生额外光子——时，发生光增益。当光增益超过两个反射镜中的总损耗时，发生激光振荡。

[0007] 有源区还可以包括使用在靠近有源区的顶部反射镜和/或底部反射镜中形成的一个或更多个氧化物层形成的氧化物孔。氧化物孔既用于形成光学腔又用于引导偏置电流通过所形成的腔的中心区。可替选地，可以使用诸如离子注入、图案化后的外延再生长或其他光刻图案化的其他手段来执行这些功能。

[0008] 有源区上形成有顶部反射镜。顶部反射镜与底部反射镜类似，因为它通常包括在

高折射率与较低折射率之间交替的多个层。通常，顶部反射镜具有较少的高折射率层和低折射率层交替的反射镜周期，以增强来自VCSEL顶部的光发射。

[0009] 说明性地，当电流流过PN结将载流子注入到有源区中时，激光器起作用。注入的载流子在量子阱中从导带重新组合到价带导致光子开始在由反射镜限定的激光腔中行进。反射镜将光子来回反射。当偏置电流足以在由腔支持的波长下产生量子阱状态之间的粒子数反转时，在量子阱中产生光增益。当光增益等于腔损耗时，发生激光振荡并且称激光器处于阈值偏置，并且VCSEL如从VCSEL的顶部发射光学相干光子那样开始“激光”。

[0010] 美国专利8,774,246描述了具有使用耗尽型半导体异质结界面形成的电流阻挡区的发光器件。使用这种类型的用于阻挡的异质结界面允许通过向阻挡区或者中心导电区本身施加位置选择性特定掺杂变化来形成导电沟道。在这种方法中，掺杂通过扩散机制传递。

[0011] Zou等人(D.Zhou和L.J.Mawst, “High-Power Single-Mode Antiresonant Reflecting Optical Waveguide-Type Vertical-Cavity-Surface-Emitting Lasers”, IEEE量子电子学期刊, 第58期, 第12卷, 第1599至1606页(2002年))描述了使用异质结电流阻挡区和中心蚀刻的导电沟道的发光器件，但是在该设计中使用的后续再生长不是平坦化的，并且在器件的中心沟道中不形成折射率传导光学模式。代替地，形成具有可以泄漏到相邻区域的较大光学模式的反谐振器件。虽然这对于非常大的发射器或紧密放置的阵列可能是有用的，但是该设计方法对于单个高的光输出效率和高调制带宽的VCSEL来说是不可取的。

[0012] Chriovsky等人(L.M.F.Chriovsky, W.S.Hobson, R.E.Leibenguth, S.P.Hui, J.Lopata, G.J.Zydzik, G.Giaretta, K.W.Goossen, J.D.Wynn, A.V.Krishnamoorthy, B.J.Tseng, J.M.Vandenberg, L.A.D’Asaro, “Implant-Apertured and Index-Guided Vertical-Cavity-Surface-Emitting Lasers (I2-VCSELs)”, IEEE光子技术快报, 第11期, 第5卷, 第500至502页(1999年))电流阻挡区是通过离子注入损伤而不是通过低掺杂异质结的使用形成。如美国专利8,774,246中那样通过经蚀刻的台面(mesa)形成折射率传导光学模式。

[0013] 本文要求保护的主题不限于解决任何缺点的实施方式或仅在例如上面描述的环境下操作的实施方式。确切的说，该背景技术仅被提供用以说明可以实践本文所描述的一些实施方式的一种示例技术。

## 发明内容

[0014] 在一个实施方式中，经蚀刻的平坦化竖直腔表面发射激光器(VCSEL)可以包括：有源区；在有源区上方的阻挡区，阻挡区在其中限定一个或更多个孔；在阻挡区的一个或更多个孔中的一个或更多个导电沟道芯，其中，一个或更多个导电沟道芯和阻挡区形成隔离区。在一个方面，VCSEL可以包括在有源区下方的底部反射镜区，以及在隔离区上方的顶部反射镜区。在一个方面，阻挡区具有1nm到500nm的厚度。在一个方面，导电沟道芯具有约1微米到约10微米的直径。在一个方面，VCSEL包括在阻挡区中的多个导电沟道芯。在一个方面，导电沟道芯具有比阻挡区高的折射率。在一个方面，VCSEL没有以下中的一个或更多个：氧化物孔；氧化；台面。在一个方面，VCSEL可以包括与一个或者更多个导电沟道芯的顶部整合或接触的导电翼层。在一个方面，一个或更多个导电通道芯是平坦化的。在一个方面，一个或更

多个导电沟道芯和顶部反射镜的反射镜层是平坦化的。

[0015] 在一个实施方式中,提供了一种制造具有含阻挡区中的一个或更多个导电沟道芯的阻挡区的VCSEL的方法。这种制造VCSEL的实施方式的方法可以包括:在衬底上方形成有源区;在有源区上方形成阻挡区;在阻挡区中蚀刻一个或更多个孔;在阻挡区的一个或更多个孔中形成一个或更多个导电沟道芯。在一个方面,该方法可以包括:使用抑制蚀刻的化学试剂涂覆阻挡区的顶部,同时留下没有化学试剂的一个或更多个区;以及在阻挡区中在没有化学试剂的一个或更多个区中蚀刻一个或更多个孔。在一个方面,该方法可以包括:通过MOCVD、使用一个或更多个导电沟道芯填充阻挡区中的一个或者更多个孔。在一个方面,该方法可以包括在蚀刻以形成一个或更多个孔之后并且在使用一个或更多个导电沟道芯填充一个或更多个孔之前去除抑制蚀刻的化学试剂。在一个方面,该方法还可以包括形成导电沟道芯以贯穿阻挡区并且与有源区接触或者与在有源区上方的顶部间隔区接触。在一个方面,该方法可以包括在公共阻挡区中形成多个导电沟道芯。在一个方面,该方法可以包括形成导电翼层以与一个或更多个导电沟道芯的顶部整合或接触。在一个方面,该方法可以包括使一个或更多个导电沟道芯的顶表面平坦化。

[0016] 在一个方面,一种经蚀刻的平坦化竖直腔表面发射激光器(VCSEL)可以包括:有源区;在有源区上方的导电区,导电区在其中限定一个或更多个孔;以及在导电区的一个或更多个孔中的一个或更多个阻挡芯,其中,一个或更多个阻挡芯和导电区形成隔离区。因此,具有其中含导电沟道芯的阻挡区的VCSEL的所有教导和实施方式可以被颠倒,使得在导电区中具有阻挡芯。这样,可以交换本文所描述的特征,以提供具有其中含阻挡芯的导电区的VCSEL的实施方式|。

[0017] 在一个实施方式中,提供了一种制造具有其中含阻挡芯的导电区的VCSEL的方法。这种方法可以包括:在衬底上方形成有源区;在有源区上方形成导电区;在导电区中蚀刻一个或更多个孔;在导电区的一个或更多个孔中形成一个或更多个阻挡芯。因此,制造具有其中含导电沟道芯的阻挡区的VCSEL的所有教导和实施方式可以被颠倒,使得该方法产生其中含阻挡芯的导电区。这样,可以交换在本文所描述的特征,以制造具有其中含阻挡芯的导电区的VCSEL的实施方式。

## 附图说明

[0018] 根据以下描述和所附权利要求书,结合附图,本公开内容的前述和以下信息以及其他特征将变得更加明显。应理解的是,这些附图描绘了根据本公开内容的仅若干实施方式,并且因此这些附图不应认为是对本公开内容范围的限制,将通过附图的使用利用附加特征和细节来描述本公开内容。

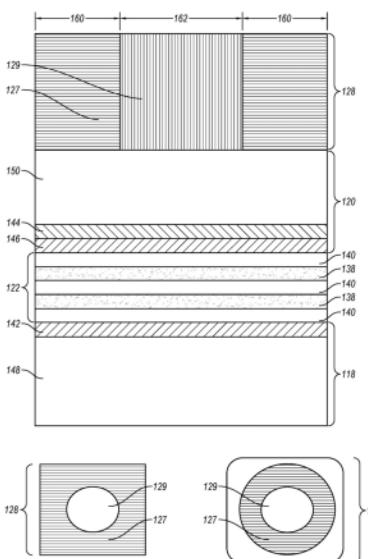

[0019] 图1是VCSEL操作环境的实施方式的示意图。

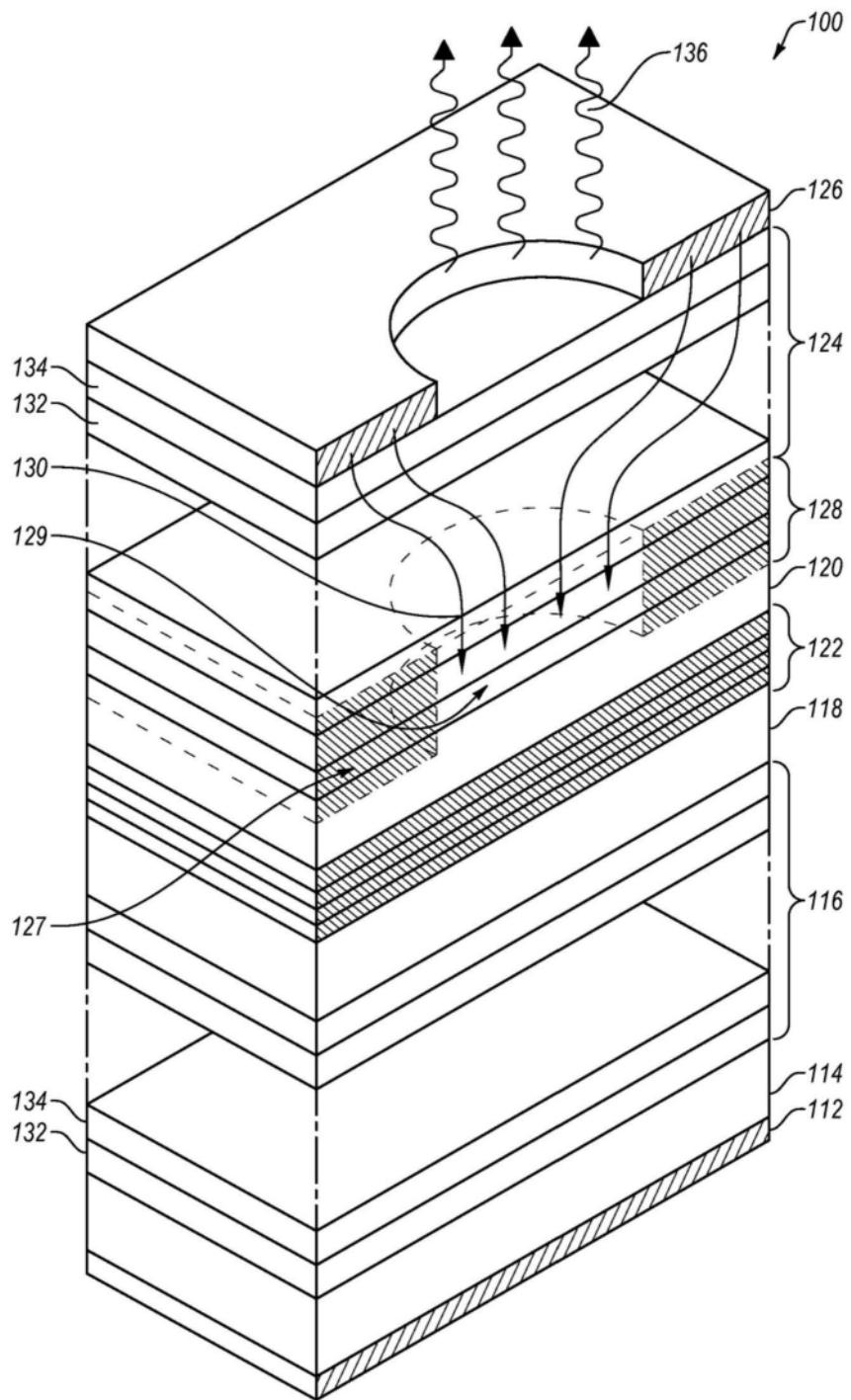

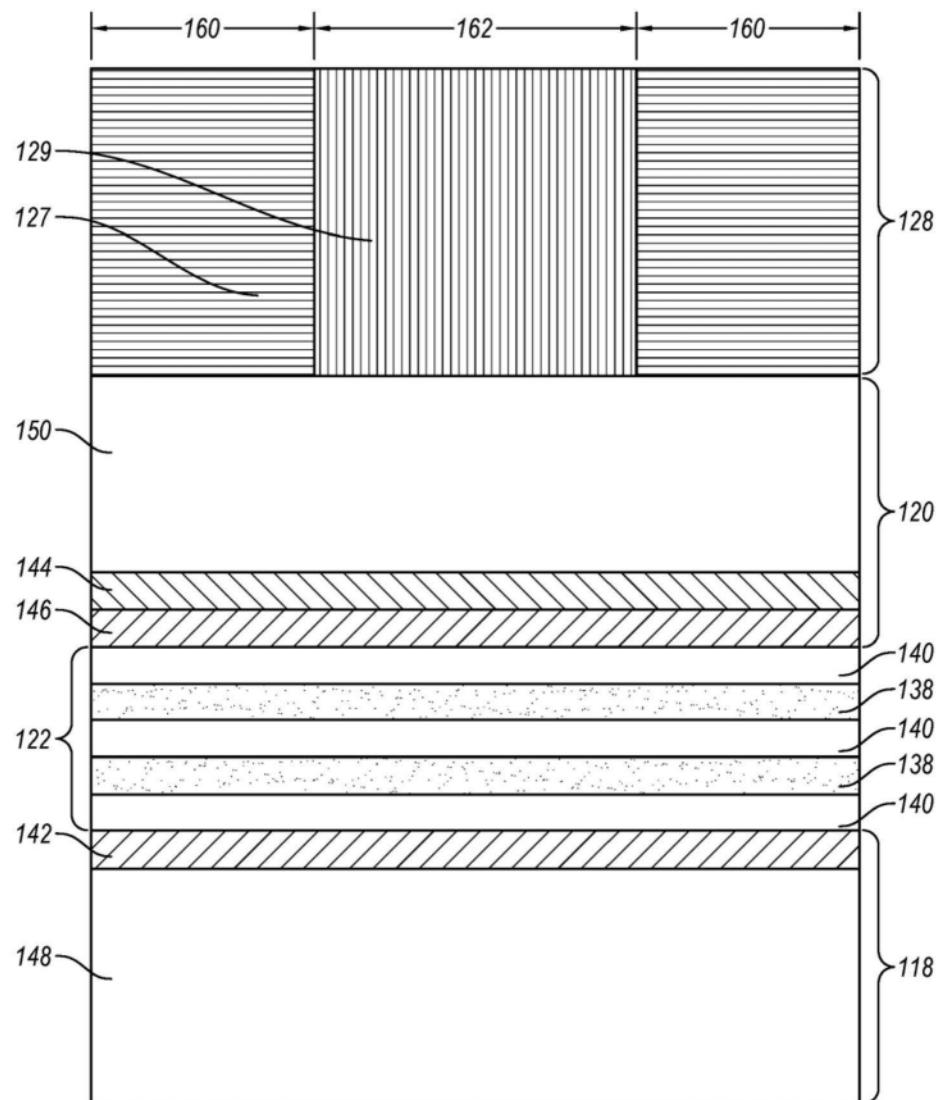

[0020] 图2是VCSEL层状半导体操作环境的实施方式的示意图。

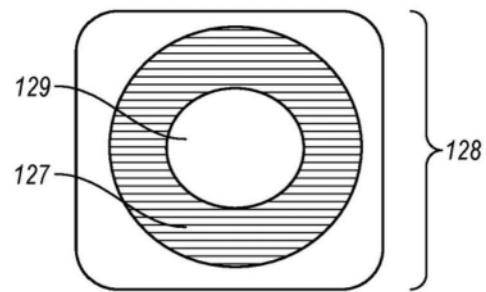

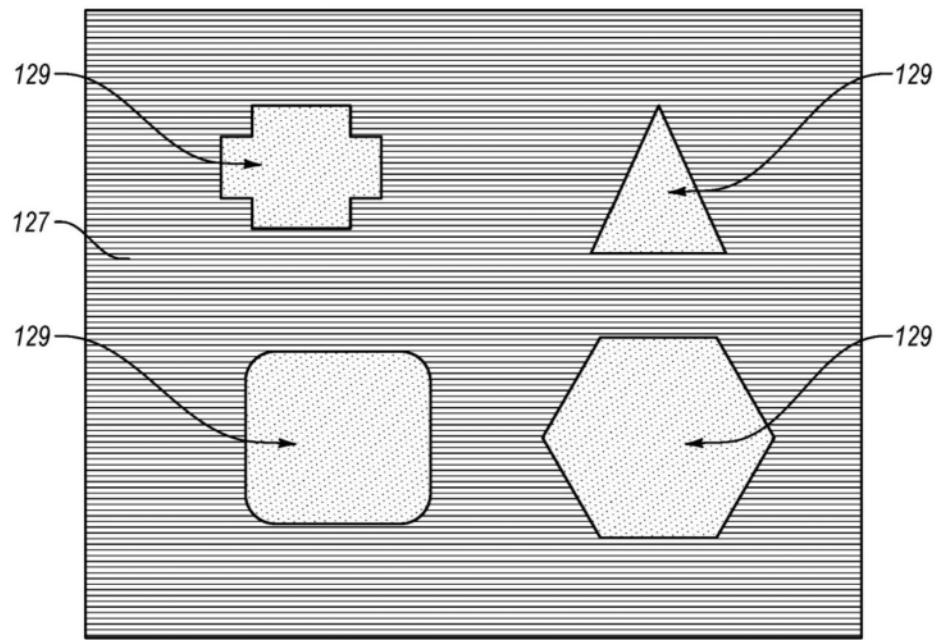

[0021] 图2A示出了隔离区的方形的横截面的俯视图。

[0022] 图2B示出了利用蚀刻以形成台面的隔离区的圆形横截面的俯视图。

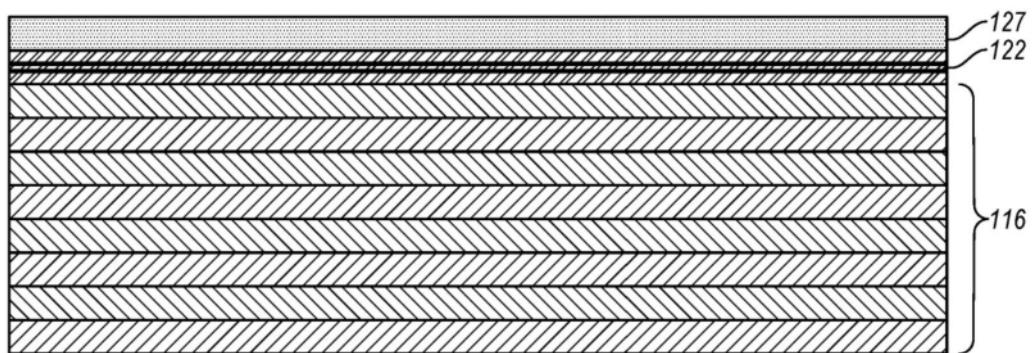

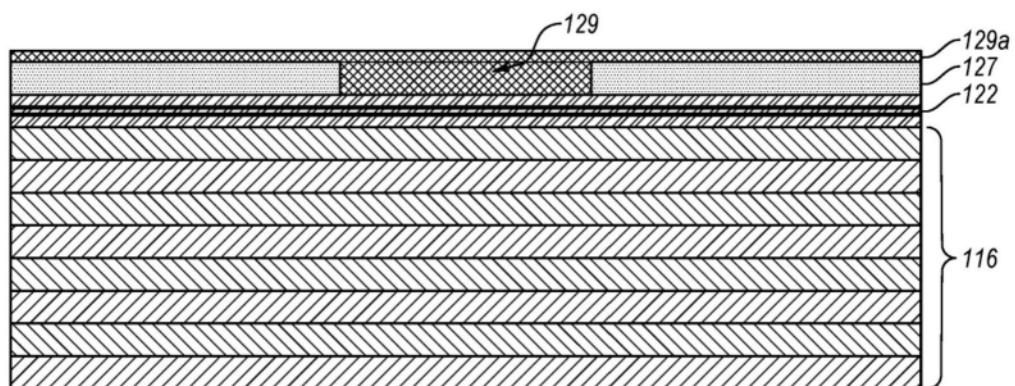

[0023] 图3是示出了N型DBR反射镜、阻挡区覆盖的具有QW的有源区的第一生长的图。

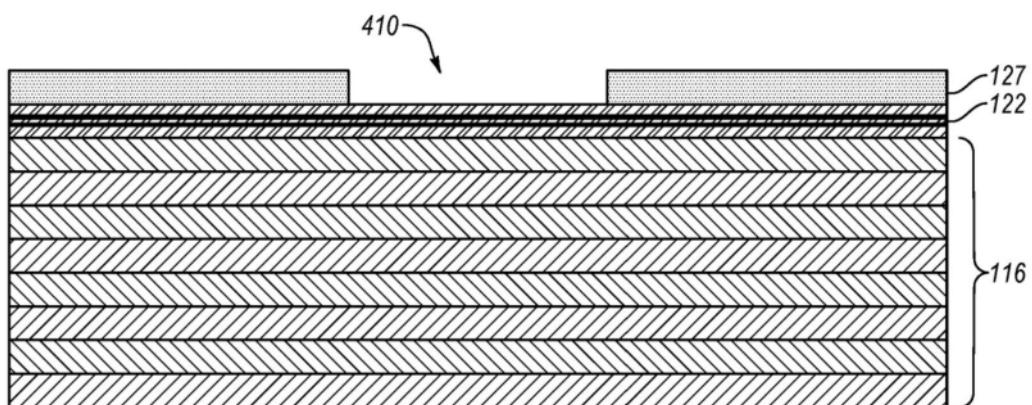

[0024] 图4是示出阻挡区中的经蚀刻的开口的图。

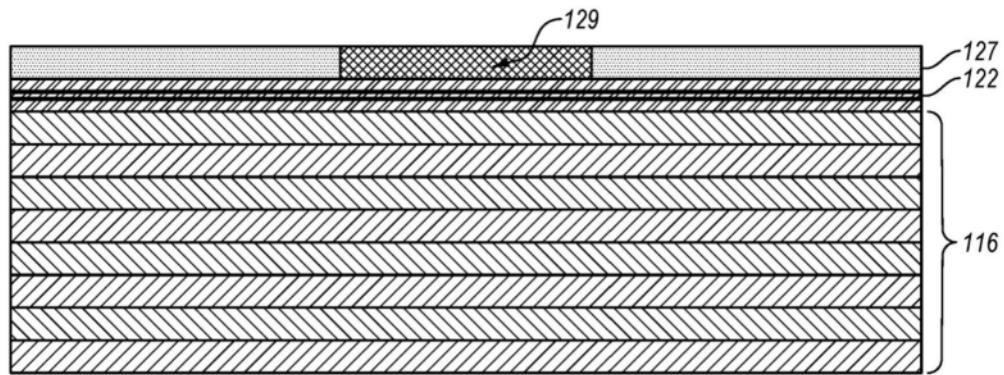

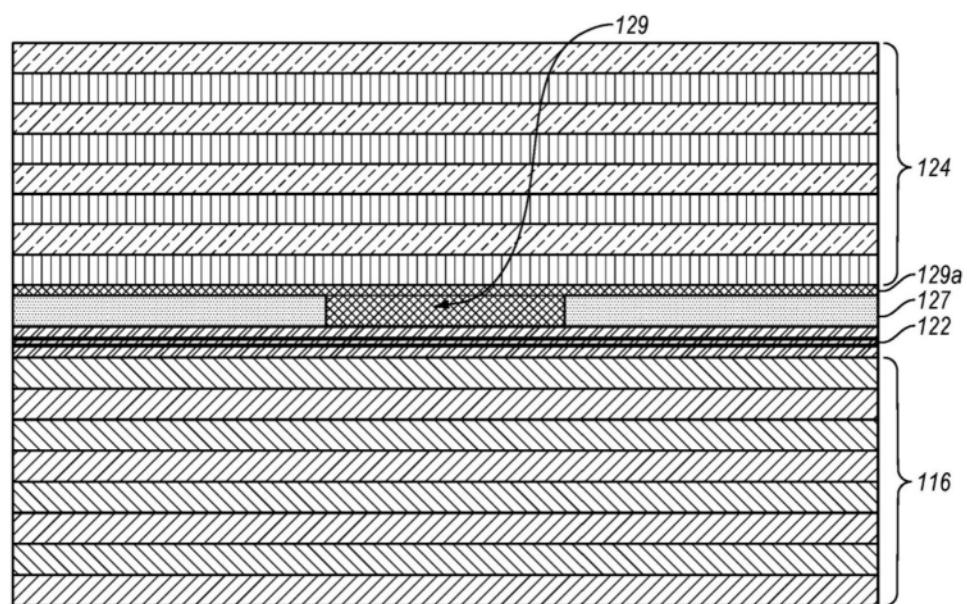

[0025] 图5是示出形成折射率传导、导电沟道的平坦化再生长的图。

[0026] 图5A是示出形成覆盖有覆盖阻挡区的平面翼层的折射率传导导电沟道的平坦化再生长的图。

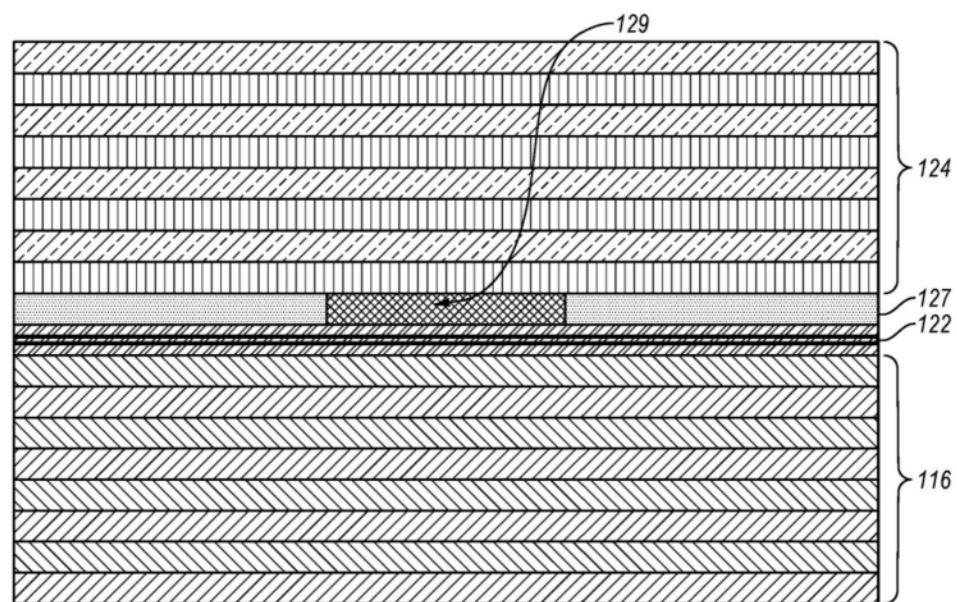

[0027] 图6是示出形成用覆盖阻挡区的平面翼层和平面翼层上方的P型DBR反射镜覆盖的导电沟道、折射率传导的平坦化再生长的图。

[0028] 图6A是示出形成折射率传导、导电沟道(不具有平面翼层)和在平面翼层上方的P型DBR反射镜、的平坦化再生长的图。

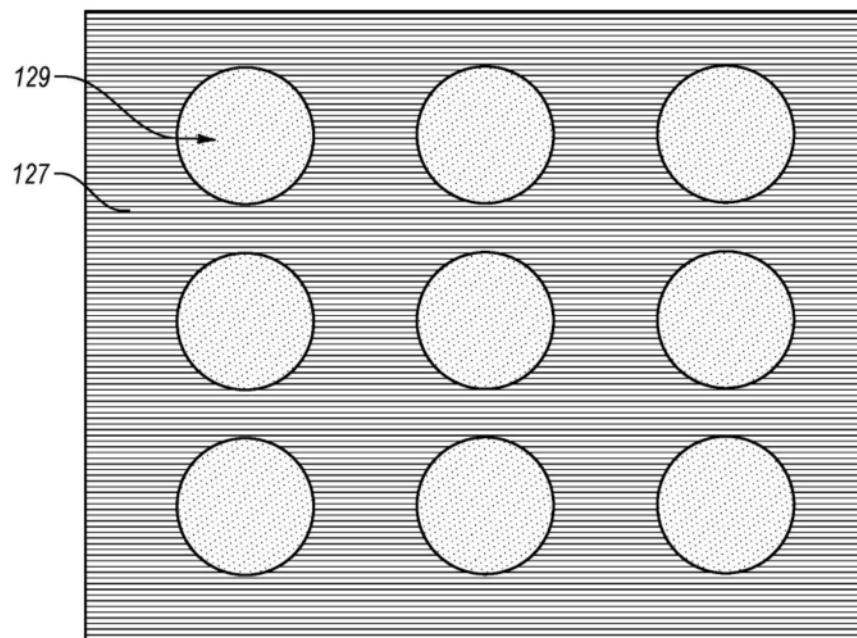

[0029] 图7是示出公共阻挡层中的多个导电沟道芯的图。

[0030] 图7A是示出公共阻挡层中的具有复杂形状的多个导电沟道芯的图。

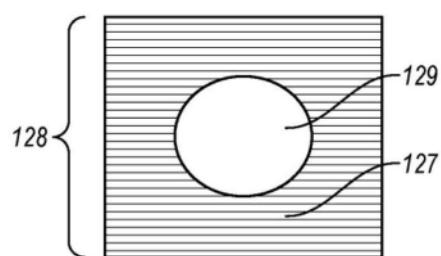

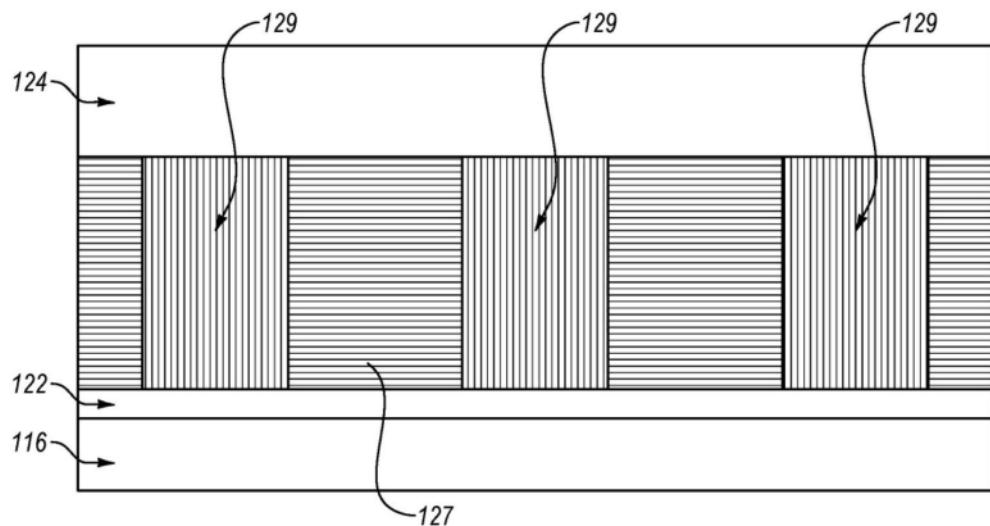

[0031] 图8是具有其中含多个导电沟道芯的阻挡区的隔离区的横截面侧视图。

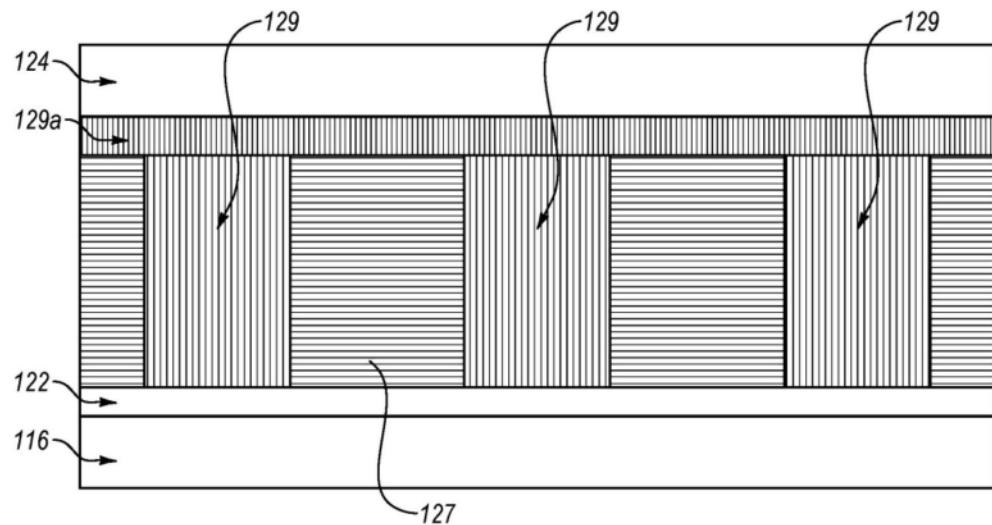

[0032] 图8A是具有其中含多个导电沟道芯和在多个导电沟道芯和阻挡区上方的平坦化翼层的阻挡区的隔离区的横截面侧视图。

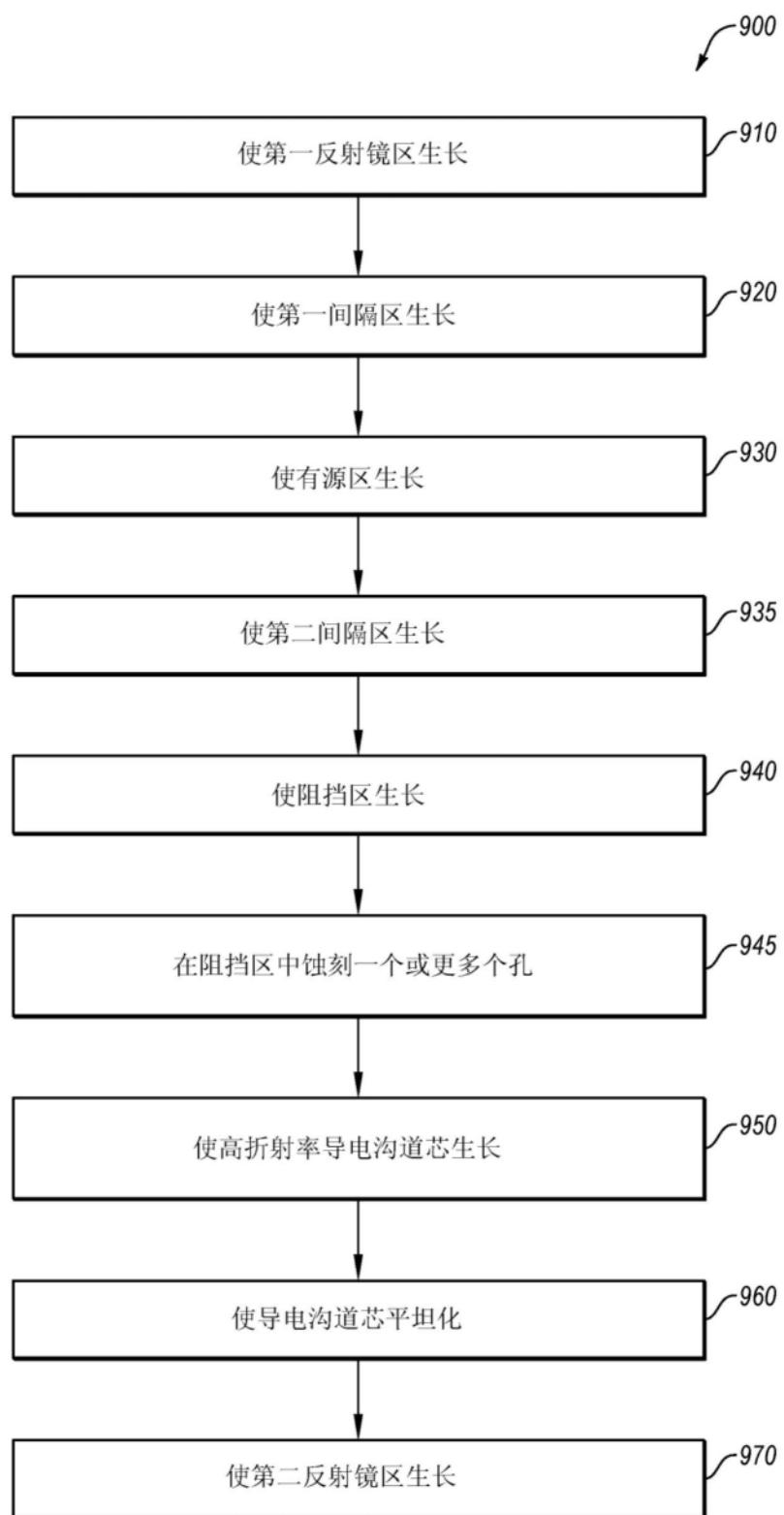

[0033] 图9是制造VCSEL的方法的实施方式的流程图。

## 具体实施方式

[0034] 在下面的详细描述中,将参考构成本发明的一部分的附图。在附图中,除非上下文另有规定,否则相似的附图标记通常标识相似的部件。在具体实施方式、附图和权利要求书中描述的说明性实施方式不意在是限制性的。在不背离本文所提出的主题的精神或范围的情况下可以使用其他实施方式并且可以作出其他改变。将容易理解的是,可以以多种不同的配置对本公开内容的如本文总体描述的并如图中所示出的各方面进行布置、替代、组合、分离和设计,所有的这些均是本文所明确构思的。

[0035] 通常,当前VCSEL技术的进步涉及通过蚀刻阻挡区的中心区并在其中沉积导电区而形成的导电区和阻挡区。在VCSEL的操作和有源区中的光发射期间,导电区可以包括比阻挡区的材料更导电的材料。因此,阻挡区和导电区可以形成用于选择性电流传导的异质结。导电区可以通过阻挡区形成导电通道。可以通过在阻挡区上方形成导电区的一部分来使导电区平坦化。可以在导电区上方形成平面化层例如反射镜层。否则,可以按照工业标准或者按照所并入的参考文献或本文中所描述的制备VCSEL。

[0036] 本发明的半导体器件可以由任何类型的半导体制造。合适材料的示例包括III-V半导体材料(例如,由一种或更多种III族材料(硼(B)、铝(Al)、镓(Ga)、铟(In)、铊(Tl)和Ununtrium(Uut))和一种或更多种V族材料(氮(N)、磷(P)、砷(As)、锑(Sb)、铋(Bi)和ununpentium(Uup)(未经证实))制备)并且可选地包括一些IV型材料。

[0037] 半导体器件可以包括具有一个或更多个量子阱和一个或更多个量子阱势垒的有源区。量子阱和量子阱势垒可以由其间的一个或更多个过渡层分隔开。因为过渡层位于量子阱与量子阱势垒之间的界面处,所以过渡层也可以称为界面层。然而,有源区可以按照VCSEL领域中任何已知的或已开发的方式进行配置。

[0038] 可选地,电限制层可以夹持有源区并通过将载流子限制到有源区来提供光增益效率。限制层可以具有高能带隙区,其在许多III-V化合物中转化为高铝含量(例如,对于III型材料,70%至100%的铝)。与有源区的量子阱势垒中的带隙相比,可以选择铝含量以使材料具有相对宽的带隙。宽带隙材料可以使限制层具有良好的载流子限制并且可以提高有源区的效率。在示例性实施方式中,高铝区还可以包括增加掺杂。取决于限制势垒是在有源区

的n侧还是p侧,限制层可以掺杂有p型掺杂剂或n型掺杂剂。

[0039] 通过使得能够实现小孔径(例如,2μm至6μm)VCSEL器件,异质结导电沟道结构可以提供改进的光纤收发器可靠性、电光带宽和链路距离。在高功率VCSEL中,异质结导电沟道结构允许每个VCSEL具有更高的最大功率,并且在密集阵列中每单位面积具有更多的发射器。

[0040] 通过允许在制造时使用一个或更多个MOCVD(金属-有机化学气相沉积)晶体生长步骤,异质结导电沟道结构使得能够更有效地大规模生产导模VCSEL。因此,该方法可以省略横向蒸汽氧化或任何氧化物孔的形成。

[0041] 图1示出了具有顶部(124)反射镜和底部(116)反射镜的周期性层对的平面电流传导的VCSEL 100。衬底114形成在底部接触部112上并且掺杂有第一类型的杂质(即,p型掺杂剂或n型掺杂剂)。在衬底114上形成有底部反射镜叠层116,并且在底部反射镜叠层116上形成有可选的底部限制层118。在底部反射镜叠层116上方或者在底部限制层118上方(当存在时)形成有源区122。在有源区122上方形成有可选的顶部限制层120。在一个可选的方面,底部限制层118和顶部限制层120夹持有源区122。在有源区122上方或者可选的顶部限制层120上方形成有隔离区128。隔离区包括横向区阻挡区127和中心导电沟道芯129。底部限制层118和/或顶部限制层120可以是有源区与隔离区之间的间隔区。可替选地,底部限制层118和/或顶部限制层120可以是导电区。因此,限制有源区的任何间隔区可以是限制区、导电区或不限制或不导电的半导体间隔件。

[0042] 在隔离区128的上方形成有上反射镜叠层124。金属层126在叠层124的一部分上形成接触。然而,也可以利用其他VCSEL结构,并且可以使用各种其他VCSEL层或层的类型。

[0043] 隔离区128限制电流130通过有源区122的面积。可以通过包括通过沉积其中形成随后由中心导电沟道芯129填充的孔的阻挡区127而得到的横向区阻挡区127和中心导电沟道芯129来形成隔离区128。隔离区128可以包括单层阻挡区127或多层阻挡层,和/或单层中心导电沟道芯129或多层中心导电沟道芯层。

[0044] 反射镜叠层116(底部)和反射镜叠层124(顶部)可以是分布式布拉格反射器(DBR)叠层,并且包括周期性层(例如,132和134,但是可以从所示出的进行交换)。周期性层132和134通常分别是AlGaAs和AlAs,但也可以由其他III-V半导体材料制成。反射镜叠层116和反射镜叠层124可以是掺杂的或不掺杂的,并且取决于特定的VCSEL设计,掺杂可以是n型或p型。然而,可以使用其他类型的VCSEL反射镜。

[0045] 金属接触层112和金属接触层126可以是允许VCSEL 100的适当电偏置的欧姆接触。当VCSEL 100正向偏置时,接触126上的电压不同于接触112上的电压,有源区122发射光136,光136穿过顶部反射镜叠层124。本领域技术人员将认识到,可以使用其他的接触结构生成跨有源区122的电压并产生光136。

[0046] 图2示出了在具有阻挡区127和中心导电沟道芯129的隔离区128下方的有源区122和限制层118和限制层120。阻挡区127形成外部电流阻挡区160并且中心导电沟道芯129形成中心模式限制区162。有源区122由通过量子阱势垒140分隔开的一个或更多个量子阱138形成,其中,过渡层可以是在量子阱138与势垒140之间的线。限制层118和限制层120可以分别可选地包括高铝含量区142和144。高铝含量区在有源区122中提供良好的载流子限制。

[0047] 限制区120可以包括位于有源区122与高铝含量区144之间的斜坡区146。如下所

述,高铝含量区144和斜坡区146的组合为注入结构提供良好载流子限制和良好的电子注入。

[0048] 取决于VCSEL器件的设计和高铝含量区142和144的厚度,限制区118和限制区120可以分别可选地包括间隔层148和间隔层150。间隔层148和间隔层150的厚度可以取决于所制造的VCSEL器件的类型。在诸如VCSEL或VCSEL的竖直腔谐振器件中,间隔层提供反射镜之间的共振间隔,并且在需要时使得有源区的量子阱以光场的峰为中心。

[0049] 限制层118和限制层120以及有源区122可以由一种或更多种类型的半导体材料例如GaAs、AlAs、InP、AlGaAs、InGaAs、InAlAs、InGaP、AlGaAsP、AlGaInP、InGaAsP、InAlGaAs、SiGe等形成。

[0050] 在一个示例中,下电限制层为AlInP。在另一示例中,上电限制层可以为AlInGaP。

[0051] 图2A示出了隔离区128的方形横截面的俯视图。图2B示出了利用蚀刻以形成台面的隔离区128的圆形横截面的俯视图。单个芯片可以具有如图2A中那样是平面的多个隔离区128,或者在单个芯片上被蚀刻成具有如图2B中那样的多个台面。

[0052] VCSEL异质结导电沟道结构可以形成为包括异质结电流阻挡区,其中,通过在阻挡区中蚀刻孔来形成导电沟道,并且在蚀刻的孔中沉积较高折射率的导电沟道芯。阻挡区可以是较低折射率的周界。阻挡区的较低的折射率可以是与导电沟道芯的较高折射率相比较而言的。这使得能够形成传导光学模式。现在利用异质结导电沟道结构,可以使用标准MOCVD技术和目前在大批量VCSEL制造中采用的其他标准制造技术更容易地制造VCSEL或VCSEL阵列。

[0053] 在一个实施方式中,制造如图3所示具有异质结导电沟道结构的VCSEL的方法可以包括:形成反射镜区116;在反射镜区116上方形成有源区122;以及在有源区122上方形成阻挡区127。可以通过MOCVD来形成。在一个示例中,如图3中所示,该结构可以包括未掺杂的阻挡层127(例如,InGaP,诸如 $In_{0.48}Ga_{0.52}P$ ),其为与GaAs和AlGaAs匹配的晶格。阻挡层127不受空气中会干扰基于MOCVD的再生长的侵蚀性氧化。因此,MOCVD的使用可以有利于形成异质结导电沟道结构。

[0054] 阻挡层127使得通过湿式化学蚀刻选择性地去除的中心区从图3的结构转变为图4的结构。如图5所示,在阻挡区中蚀刻孔410之后(孔410为有源区122或顶部限制区120作为其基部、阻挡区127作为从基部延伸的侧壁的凹部),例如通过使用较高折射率材料(与阻挡区相比)例如 $Al_{0.15}Ga_{0.85}As$ 通过使再生长平面化在蚀刻的孔410中形成导电沟道芯129。执行平坦化再生长以使用导电沟道芯129填充经蚀刻的孔410,然后如图5A所示形成任何可选区(例如,具有翼129a的导电平面),并且如图6中所示在经蚀刻的区上形成反射镜区124。通过对MOCVD生长参数的选择来实现平坦化再生长,以在孔410内获得更高的可达到的生长速率。跟随顶部P掺杂反射镜(例如,分布式布拉格反射器-DBR)生长的选择性区域再生长也可用于实现平坦化。当底部反射镜是P掺杂时,顶部反射镜可以是N掺杂的并且VCSEL的其他层也相应地制定。

[0055] 因此,图3示出了DBR反射镜116、有源区122和阻挡区127的第一生长。图4示出了阻挡区127中的经蚀刻的孔410。图5示出了形成折射率传导、导电沟道芯129的平坦化再生长。图5A示出了形成具有在导电沟道芯129上方的翼129a的导电平面的折射率传导导电沟道的平坦化再生长。图6示出了顶部反射镜124的平坦化层。图6A示出了在导电沟道芯129上方不

存在具有翼129a的导电平面，并且代替地顶部反射镜124直接在导电沟道芯129和横向阻挡区127上方的选项。

[0056] 在一个实施方式中，本VCSEL可以被配置成包括通过蚀刻阻挡区形成的中心导电沟道，并且具有填充有导电区的经蚀刻的区，然后具有沉积在阻挡区和导电区的顶部上的随后一系列的平坦化层以形成折射率传导光学模式。

[0057] 在一个实施方式中，可以颠倒实施方式和处理，使得对导电层施加而不对阻挡层施加，然后蚀刻导电层以形成腔，然后使用阻挡层填充腔以形成阻挡芯。然而，在该实施方式中，阻挡芯不具有带翼的阻挡平面。

[0058] 在一个实施方式中，单个衬底可以包括可以形成为阵列的多个VCSEL发射器。可以在多个位置选择性地蚀刻具有宏阻挡区的宏基板并使用导电沟道芯重新填充具有宏阻挡区的宏基板以形成VCSEL阵列。每个导电沟道芯可以是使用异质结电流阻挡区和中心蚀刻的导电沟道的单独的发光器件，并且整个导电沟道和阻挡区可以利用平坦化层接纳其随后的再生长。图7示出了在单个衬底上的这种VCSEL发射器的激光器阵列。每个VCSEL发射器可以包括导电沟道芯129，其中所有VCSEL发射器均被公共阻挡层127围绕。图7B示出了可以进行蚀刻以产生具有复杂形状的导电沟道芯129，这可以通过以下方式实现：选择性地沉积保护剂，留下未受保护的复杂形状，然后将其蚀刻成复杂的蚀刻形状。

[0059] 因为该处理不使用可能损坏半导体层的横向氧化，所以本结构可以导致VCSEL没有氧化物孔。具有导电沟道芯的阻挡层的使用使用了具有更好热连接性的半导体材料。由于顶部反射镜中的砷化铝层并且处理不会使砷化铝层氧化，因此热连接性变得更好。底部反射镜可以使用二元材料。因为制造方法不包括在有源区附近切割出沟槽并氧化成半导体，所以还可以提高VCSEL的可靠性。

[0060] 当器件在较低温度下操作时，可以提高VCSEL的可靠性。在现有技术中，由于氧化物层的低热连接性，因此氧化物限制的VCSEL变热更多。在器件中切割出沟槽以允许形成氧化物层。因此，本文提供的VCSEL可以没有这种氧化物层和/或允许形成氧化物层的沟槽。

[0061] 激光器装置可靠性的大多数问题与在使该氧化物层的尖端处发生的某种化学过程有关。由于由氧化物层引起的应力，所以在氧化物尖端处出现一些可靠性问题。大多数可靠性问题在高温下会加剧。由于与氧化层的物理相互作用，所以氧化物限制的激光器具有可靠性问题，且氧化物层处的应力驱使缺陷形成在半导体层中。鉴于此，由于没有氧化物层，预期本文所述的激光器应具有较少的缺陷，并且即使在较高温度下也具有较少的缺陷形成。本发明的植入VCSELS可以由于不具有氧化物层而具有改善的可靠性。

[0062] 现在利用本技术，可以在阻挡层中形成非常小的孔以形成具有改善的可靠性的一个或更多个激光器器件。非常小的孔的激光器件现在可以彼此非常接近。例如，各个导电沟道芯可以具有1微米到10微米、1.5微米到5微米、2微米到4微米、或约2.5微米到3微米的直径(或其他截面尺寸)。各个导电沟道芯可以分隔开1微米到10微米、1.5微米到5微米、2微米到4微米、或约2.5微米到3微米的距离(例如，相距最小距离)。这可以在公共芯片上包括1、2、3、4、5、6、7、8、9、10或更多个激光器，其中一个或更多个(例如，4或5)激光器可以耦合到共同的光纤中。

[0063] 化学蚀刻的共同点是，可以使用掩模限定蚀刻部分和非蚀刻部分。可以将掩模或其他化学阻挡材料放置在具有限定化学蚀刻将在何处发生的孔的阻挡层上。在一个示例

中, MOCVD沉积被用于形成导电沟道芯。在一个示例中, 通过将 $\text{SiO}_2$ 层放置在阻挡层上的除了留下作为孔的一个或更多个孔(圆形或其他形状)以外的各处来限定非蚀刻区。然后去除 $\text{SiO}_2$ 。在去除 $\text{SiO}_2$ 之后, 然后MOCVD使用较高折射率材料填充孔以形成导电沟道芯。通过添加更高折射率的材料使导电沟道芯变平以形成具有翼的层。然后可以在隔离区上形成反射镜。

[0064] 在一个实施方式中, 在再生长期间填充孔时可以调节MOCVD处理的温度可以导致更多的材料在孔中生长然后随后使其平坦化。再生长处理的温度可以确定平坦化发生的程度。

[0065] 在一个方面, 制造过程省略了蚀刻或以其他方式形成台面。因此, 在激光器件不包括在激光器将要处于的地方的中心的凸起区域。

[0066] 在一个实施方式中, 阻挡区是InGaP。并且这种材料其中48%的碘、52%的镓以及磷。这种InGaP材料是与GaAs匹配的晶格。

[0067] 如图7A所示, 选择性蚀刻使得可以形成各种形状的孔, 然后可以在各种形状的孔中填充成形的导电沟道芯129。

[0068] 图8示出了具有填充有导电沟道芯129的多个孔的阻挡区127的半导体的横截面侧视图。

[0069] 图8A示出了具有填充有导电通道芯129的多个孔的阻挡区127以及与多个或所有导电沟道芯129的顶部整合或位于多个或所有导电沟道芯129的顶部并且与多个或所有导电沟道芯129接触的整体导电翼层129a的半导体的横截面侧视图。

[0070] 图9是制造如本文所述的VCSEL的方法的实施方式的另一处理900的流程图。该处理可以包括使具有多个第一反射镜层的第一反射镜区生长, 所述多个第一反射镜层具有一个或多个折射率(框910), 然后(可选地)在第一反射镜区上方使第一间隔区生长(框920)。然后, 在第一间隔区上方(或当第一间隔区未生长时在第一反射镜上方)使有源区生长(框930)。然后在有源区上使可选的第二间隔区生长(框935)。然后在第二间隔区上方(或当第二间隔区未生长时在有源区上)使阻挡区生长(框940)。然后在阻挡区中蚀刻一个或更多个孔(仅蚀刻阻挡区, 不蚀刻有源区, 可选地可以蚀刻第二阻挡区中的一些或全部)(框945)。然后使用高折射率材料(例如, 比阻挡层更高的RI)填充一个或更多个孔(框950)以形成导电沟道芯。处理900还可以包括例如通过形成翼(框960)然后生长具有多个第二反射镜层的第二反射镜区(框970)来使导电通道芯平坦化, 所述多个第二反射镜层具有一个或更多个折射率。

[0071] 此外, 可以使用分子束外延(MBE)来产生VCSEL的有源区或整个半导体层。MBE期间的较低生长温度可以用于制备VCSEL半导体层。通过MBE进行的这些结构的生长可以在<(小于)500°C下进行。相比之下, 用于MOCVD的温度可以>(大于)600°C。另外, VCSEL可以通过可以产生所描述的区的类似于MBE的方法例如GSMBE(气体源MBE)和MOMBE(金属有机MBE)等制备。

[0072] 化学蚀刻可以是本领域中有用且已知的任何化学蚀刻。

[0073] 在一个实施方式中, 可以交换阻挡区和导电区的定向, 使得阻挡区是由导电区所围绕的芯。这里, 导电区包括具有阻挡芯的孔。

[0074] 在一个实施方式中, 沟槽和氧化的缺少可以导致导电芯(或中心阻挡区)比现有器

件更靠近在一起。在一个示例中,由于沟槽和氧化,现有器件可以具有相距约21微米到25微米的(导电或阻挡)芯。然而,因为当前器件省略了沟槽和氧化,所以(导电或阻挡)芯可能必须更靠近在一起,例如相距1微米到8微米、或2微米到6微米、或4微米(中心到中心)

[0075] 现在,例如,在芯中心到芯中心约4微米的情况下,可以实现高密度阵列。高密度可以允许具有相同相位的芯的相干阵列。此外,可以存在对相控阵中的相干的光束的一些控制,其可以向下聚焦到小光点以在扫描中使用。另外,对高密度阵列的更精确控制使得激光武器能够使用利用本技术所实现的高密度阵列。

[0076] 该技术可以实现相干阵列,这意味着所有芯具有相同的相位或者你可以控制芯之间的相位,这可以提供可以指向期望位置的激光束而无需物理地转动激光器。在一个示例中,在机头中存在相控阵列的战斗机照射另一个战斗机,从而相控阵列可以指向任何地方。对相控阵列的光束的相干性的控制可以实现光束的向下聚焦到小点。这种控制使得本发明能够被用在扫描应用上。该控制在激光武器中也可以是有用的,因为这种布置可以在大面积上分布许多芯,这可以控制散热,并且所有芯的相位的控制可以使得它们能够例如通过聚焦被组合,使得在聚焦时所有芯协同工作以对其功率进行组合来获得每单位面积上非常大的功率。

[0077] 在一个实施方式中,经蚀刻的平坦化竖直腔表面发射激光器(VCSEL)可以包括:有源区;在有源区上方的阻挡区,阻挡区在其中限定一个或更多个孔;在阻挡区的一个或更多个孔中的一个或更多个导电沟道芯,其中,一个或更多个导电沟道芯和阻挡区形成隔离区。在一个方面,VCSEL可以包括在有源区下方的底部反射镜区,以及在隔离区上方的顶部反射镜区。在一个方面,VCSEL可以包括在底部反射镜区与有源区之间的底部间隔区,以及在有源区与阻挡区之间的顶部间隔区。在一个方面,导电沟道芯贯穿阻挡区并与有源区接触。在一个方面,导电沟道芯贯穿阻挡区并与顶部间隔区接触。在一个方面,阻挡区具有1nm至500nm、1nm至30nm、1nm至10nm、或1nm至3nm的厚度。在一个方面,导电沟道芯具有与阻挡区相同的厚度。在一个方面,导电通道芯具有约1微米到约10微米的直径。在一个方面,导电通道芯具有约2微米到约6微米的直径。在一个方面,阻挡区或阻挡层为InGaP。在一个方面,导电沟道芯为AlGaAs。在一个方面,一个或更多个导电通道芯是平坦化的。在一个方面,一个或更多个导电沟道芯和顶部反射镜是平坦化的。

[0078] 在一个实施方式中,VCSEL可以包括在公共阻挡区中的多个导电沟道芯。在一个方面,VCSEL可以包括在公共阻挡区中的多达五个导电沟道芯,或者多于五个导电沟道芯。

[0079] 在一个实施方式中,导电沟道芯具有比阻挡区高的折射率。在一个方面,阻挡区具有比导电沟道芯低的折射率。在一个方面,导电通道芯具有约3.7至3的折射率。在一个方面,阻挡区具有约3.7至3的折射率。

[0080] 在一个实施方式中,VCSEL的阵列可以包括本文中根据任何实施方式描述的多个单独VCSEL。

[0081] 在一个实施方式中,VCSEL可以不含有在VCSELS中常见的某些特征。在一个方面,VCSEL没有氧化物孔。在一个方面,VCSEL没有氧化。在一个方面,VCSEL没有台面。

[0082] 在一个实施方式中,VCSEL可以包括导电翼层。在一个方面,导电翼层与一个或更多个导电沟道芯的顶部整合。在一个方面,导电翼层是分开的并且与一个或更多个导电沟道芯的顶部接触。

[0083] 在一个实施方式中,制造VCSEL的方法可以包括:形成具有以下部分的VCSEL:有源区;在有源区上方的阻挡区,阻挡区在其中限定一个或更多个孔;以及在阻挡区的一个或更多个孔中的一个或更多个导电通道芯。在一个方面,该方法可以包括形成阻挡区。在一个方面,该方法可以包括形成阻挡区,以及在阻挡区中蚀刻一个或更多个孔。在一个方面,该方法可以包括:形成阻挡区;使用抑制蚀刻的化学试剂涂覆阻挡区的顶部,同时留下没有化学试剂的一个或更多个区;以及在阻挡区中在没有化学试剂的一个或更多个区中蚀刻一个或更多个孔。在一个方面,该方法可以包括:形成阻挡区;使用抑制蚀刻的化学试剂涂覆阻挡区的顶部,同时留下没有化学试剂的一个或更多个区;在阻挡区中在没有化学试剂的一个或者更多个区中蚀刻一个或更多个孔;并且使用一个或多个导电沟道芯填充阻挡区中的一个或更多个孔。

[0084] 在一个方面,该方法可以包括在蚀刻以形成孔之后并且在使用一个或更多个导电沟道芯填充孔之前去除抑制蚀刻的化学试剂。在一个方面,该方法可以包括在使用一个或更多个导电沟道芯填充孔之后去除抑制蚀刻的化学试剂。

[0085] 在一个实施方式中,该方法可以包括在有源区下方形成底部反射镜区,以及在有源区、阻挡区和导电沟道芯上方形成顶部反射镜区。在一个方面,该方法可以包括在底部反射镜区与有源区之间形成底部间隔区,以及在有源区与隔离区之间形成顶部间隔区。

[0086] 在一个实施方式中,该方法可以包括形成导电沟道芯以贯穿阻挡区并与有源区接触。在一个方面,该方法可以包括形成导电沟道芯以贯穿阻挡区并与顶部隔离区接触。在一个方面,该方法可以包括在公共阻挡区中形成多个导电沟道芯。在一个方面,该方法可以包括形成导电沟道芯以具有比阻挡区更高的折射率。在一个方面,该方法可以包括形成具有比导电沟道芯低的折射率的阻挡区。

[0087] 在一个实施方式中,该方法可以包括使用MOCVD形成一个或更多个导电沟道芯。在一个方面,该方法可以包括使用MOCVD形成一个或更多个导电沟道芯,以及在一个或更多个导电沟道芯上方形成具有翼层的导电平面。在一个实施方式中,该方法可以包括使用MOCVD形成一个或更多个导电沟道芯,以及在一个或更多个导电沟道芯上方形成具有翼层的导电平面,并且在具有翼层的一个或更多个导电平面上方形成顶部反射镜。

[0088] 在一个实施方式中,可以使各种层平坦化。在一个方面,该方法可以包括使顶部反射镜平坦化。在一个方面,该方法可以包括形成一个或更多个导电沟道芯以使其平坦化。在一个方面,该方法可以包括形成一个或更多个导电沟道芯和顶部反射镜以使其平坦化。

[0089] 在一个实施方式中,该方法可以包括形成VCSEL的阵列。

[0090] 在一个实施方式中,该方法可以包括形成与一个或更多个导电沟道芯的顶部整合的导电翼层。在一个方面,该方法可以包括单独地形成导电翼层并与一个或更多个导电沟道芯的顶部接触。

[0091] 在一个实施方式中,经蚀刻的平坦化竖直腔表面发射激光器(VCSEL)可以包括:有源区;在有源区上方的导电沟道区,导电沟道区在其中限定一个或更多个孔;在导电沟道区的一个或更多个孔中的一个或更多个阻挡芯,其中,一个或更多个阻挡芯和导电沟道区形成隔离区。因此,本文所述的元件可以应用于这样的VCSEL,该VCSEL具有阻挡构件作为阻挡芯而不是导电构件作为导电芯。根据该实施方式的修改包括在本文中。还可以调整制造方法,使得阻挡构件作为阻挡芯而不是导电构件作为导电芯。

[0092] 本领域技术人员将理解的是,对于本文公开的这些和其他处理和方法,可以以不同的顺序来实现在处理和方法中执行的功能。此外,概述的步骤和操作仅作为示例提供,并且在不偏离所公开的实施方式的本质的情况下,一些步骤和操作可以是可选的、可以被组合成较少的步骤和操作或者可以被扩展成另外的步骤和操作。

[0093] 本公开内容不限于该申请中所描述的特定实施方式的各方面,其意在作为对各个方面的说明。对于本领域技术人员将明显的是,在不偏离其精神和范围的情况下,可以进行许多修改和变化。根据前述描述,除了本文列举的那些方法和装置之外,本公开内容的范围内的在功能上等同的方法和装置对本领域技术人员将是明显的。这些修改和变化旨在落在所附权利要求书的范围内。本公开内容仅受所附权利要求书的条款以及这些权利要求书所赋予的等同物的全部范围的限制。可以理解的是在本文中使用的术语仅为了描述特定实施方式的目的,而不旨在限制。

[0094] 本领域技术人员可以理解的是,在本文中使用的术语以及尤其是在所附权利要求书(例如,所附权利要求书的主体)中使用的术语通常意为“开放式”术语(例如,术语“包括”应当被解释为“包括并且不限于”,术语“具有”应当被解释为“至少具有”,术语“包含”应当被解释为“包含并且不限于”等)。本领域技术人员还将理解的是,如果意指特定数目的引入的权利要求的记载,则在权利要求中将明确地陈述这种意图,并且在没有这样的叙述的情况下,不存在这样的意图。例如,为了帮助理解,所附权利要求书可以包括使用引导性短语“至少一个”和“一个或更多个”来引导权利要求叙述。然而,即使在相同的权利要求包括引导性短语“一个或更多个”或“至少一个”以及不定冠词例如“一(a)”或“一个(an)”(例如,“一”和/或“一个”应当被解释为意为“至少一个”或“一个或更多个”),这样的短语的使用也不应当被解释为暗示由不定冠词“一(a)”或“一个(an)”对权利要求列举的引导将包含这样引导的权利要求列举的任何特定权利要求限制为包含仅一个这样的列举的实施方式;对于使用用于引入权利要求的记载的定冠词也是如此。此外,即使明确地列举了引导的权利要求列举的特定数目,本领域技术人员也要认识到,这样的列举应当被解释为意为至少所列举的数量(例如,仅有的“两个列举”的列举,在没有其他修饰语的情况下,意为至少两个列举、或两个或更多个列举)。此外,在使用类似于“A、B和C等中的至少一个”的约定的那些情况下,通常这样的结构旨在使用本领域技术人员应当理解的约定的含义(例如,“具有A、B和C中的至少一种的系统”包括但不限于单独具有A、单独具有B、单独具有C、具有A和C、具有A和C、具有B和C或者具有A、B和C的系统)。在使用类似于“A、B或C等中的至少一个”的约定的那些情况下,通常这样的结构意在本领域技术人员将理解该约定的意义(例如,“具有A、B或C中的至少一种的系统”包括但不限于单独具有A、单独具有B、单独具有C、具有A和B、具有A和C、具有B和C和/或具有A、B和C的系统)。本领域技术人员还可以理解的是,呈现两个或更多个可替选术语的任何分隔的词和/或短语,不论在说明书、权利要求书还是附图中,都应当被理解为构思了包括所述术语中的一个、所述术语中的任何一个或所述术语两者的可能性。例如,短语“A或B”将被理解为包括“A”或“B”或“A和B”的可能性。

[0095] 另外,在按照马库什(Markush)组描述本公开内容的特征或各方面的情况下,本领域技术人员将认识到,本公开内容由此还按照马库什组的任何单独成员或子组成员进行描述。

[0096] 如本领域技术人员将理解的,出于任何和所有目的,例如在提供书面描述方面,本

文中公开的所有范围还涵盖任何和所有可能的子范围以及其子范围的组合。任何列出的范围可以容易地被识别为充分地描述并且使得相同的范围被分解为至少相等的一半、三分之一、四分之一、五分之一、十分之一等。作为非限制性示例,这里讨论的每个范围可以容易地被分解为下三分之一、中间的三分之一和上三分之一等。如本领域技术人员还将理解的,诸如“至多”,“至少”等的所有语言包括所述的数字并且指代可以随后分解成如上所述的子范围的范围。最后,如本领域技术人员将理解的,范围包括每个单独的成员。因此,例如,具有1至3个单元格的组是指具有1、2或3个单元格的组。类似地,具有1至5个单元格的组是指具有1、2、3、4或5个单元格的组等。

[0097] 根据前述内容可以理解,出于说明的目的,在本文中已经描述了本公开内容的各种实施方式,并且在不偏离本公开内容的范围和精神的情况下可以进行各种修改。因此,本文中所公开的各种实施方式并不意在限制,真正的范围和精神由所附权利要求书来指示。

[0098] 本文引用的所有参考文献的全部内容通过特定引用并入本文。

图1

图2

图2A

图2B

图3

图4

图5

图5A

图6

图6A

图7

图7A

图8

图8A

图9