(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6316836号

(P6316836)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

H01P 5/19 (2006.01)

F 1

H01P 5/19

A

請求項の数 7 (全 13 頁)

(21) 出願番号 特願2015-542731 (P2015-542731)

(86) (22) 出願日 平成25年11月12日 (2013.11.12)

(65) 公表番号 特表2015-535162 (P2015-535162A)

(43) 公表日 平成27年12月7日 (2015.12.7)

(86) 國際出願番号 PCT/US2013/069753

(87) 國際公開番号 WO2014/078334

(87) 國際公開日 平成26年5月22日 (2014.5.22)

審査請求日 平成28年10月18日 (2016.10.18)

(31) 優先権主張番号 13/678,277

(32) 優先日 平成24年11月15日 (2012.11.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】フレキシブルに出力間隔をあけるコンパクトなパワー分配器/結合器

## (57) 【特許請求の範囲】

## 【請求項 1】

装置であって、

第2のおよび第3のポートに連結された第1のポートを持つ3つのポート回路を提供するための手段と、

接地に前記第2のおよび第3のポートを連結するように構成された整合するための手段とを備え、

整合するための前記手段は、

第1のノードと前記第2のポートとの間に連結された整合するための第1の手段と、

前記第1のノードと前記第3のポートとの間に連結された整合するための第2の手段と、 10

前記第1のノードと接地との間に連結された整合するための第3の手段とを備え、

前記装置はさらに、

前記第1のおよび第2のポートとの間を連結するための手段としての第1の送信ラインと、

第1のおよび第3のポートとの間を連結するための手段としての第2の送信ラインとを備え、

前記第1の送信ライン、前記第2の送信ライン、整合するための前記第1の手段、整合するための前記第2の手段、および、整合するための前記第3の手段のインピダンスは、第1の選択された特性インピダンス値に整合するように結合され、および、前記第1のボ

ー<sup>ト</sup>において、第1の結合されたインピダンス値が得られるように結合され、

前記第1のポートにおいて、前記第1の結合されたインピダンス値を得るために、整合

するための前記第1の手段、整合するための前記第2の手段、および、整合するための前

記第3の手段のインピダンスが調整される、装置。

【請求項2】

前記第1の結合されたインピダンス値は、50オームに設定された、請求項1に記載の

装置。

【請求項3】

整合するための前記第1の手段および整合するための前記第2の手段は、整合するため

の前記第1の手段、整合するための前記第2の手段、および整合するための前記第3の手

段の代わりに、前記第2のポートと前記第3のポートとの間に抵抗器が連結される場合に

比べて、前記第2のおよび第3のポートとの間の間隔を増加させるように構成された請求

項1に記載の装置。

10

【請求項4】

前記第1の送信ライン、前記第2の送信ライン、整合するための前記第1の手段、整合

するための前記第2の手段、および、整合するための前記第3の手段のインピダンスは、

第2の選択された特性インピダンス値に整合するように結合され、および、前記第2のポ

ートにおいて、第2の結合されたインピダンス値が得られるように結合された、請求項1

に記載の装置。

【請求項5】

20

前記第2の結合されたインピダンス値は、50オームに設定された、請求項4に記載の

装置。

【請求項6】

前記装置は、双方向の受動的なパワー結合器／分配器を形成する請求項1に記載の装置

。

【請求項7】

前記双方向の受動的なパワー結合器／分配器は、トランシーバにおける使用のために構

成される請求項6に記載の装置。

【発明の詳細な説明】

【技術分野】

30

【0001】

[米国特許法第119条に基づく優先権の主張]

[0001] 本出願は、概してアナログ・フロント・エンドの動作および設計に、より具体的

的には、アナログ・フロント・エンドにおける使用のためのパワー分配器／結合器の動作

および設計に、関連する。

【背景技術】

【0002】

[0002] 多数のアンテナをもつビームフォーミングトランシーバは、ミリメートル波長

で動作するワイヤレスリンク上の信号を送信および受信するために、例えば、60GHz

における信号を送信および受信するために、概して利用される。ほとんど全てのビームフ

ォーミングトランシーバは、パワー分配器／結合器ネットワークを利用する。信号送信(

$T_x$ )中に、分配器／結合器ネットワークは複数のアンテナ間に送信信号のパワーを分配

するために使用される。信号受理( $R_x$ )中に、分配器／結合器ネットワークは複数のアン

テナから受信された信号のパワーを結合するために使用される。

40

【0003】

[0003] 1つの従来のパワー分配器／結合器は、ウィルキンソン・パワー分配器／結合

器と呼ばれる。ウィルキンソン・パワー分配器／結合器は、 $T_x$ と $R_x$ の機能間で共有さ

れることができる受動的なネットワークで、電力消費はなく、よい線形性および、よい雑

音性能を有している。不運にも、ウィルキンソン・パワー分配器／結合器に関連した1つ

の問題は、それが大きな回路領域を利用することである。ウィルキンソン・パワー分配器

50

/ 結合器に関連した他の問題は、その回路実装が概して、接近した間隔をあけられたポート・ピンをもたらすことで、それはさらなるレイアウトの複雑さに導く。

【0004】

[0004] 従って、ウィルキンソン・パワー分配器 / 結合器に匹敵する性能を持つが、より小さな回路領域を利用し、レイアウトの複雑さを減少させるため、より大きなフレキシビリティを提供する単純でローコストなパワー分配器 / 結合器を持つことが、望ましいだろう。

【発明の概要】

【0005】

[0005] 本明細書に説明される前述の態様は、添付図面と合わせられた場合、下記の説明を参照することにより、より容易に明確になるであろう。

10

【図面の簡単な説明】

【0006】

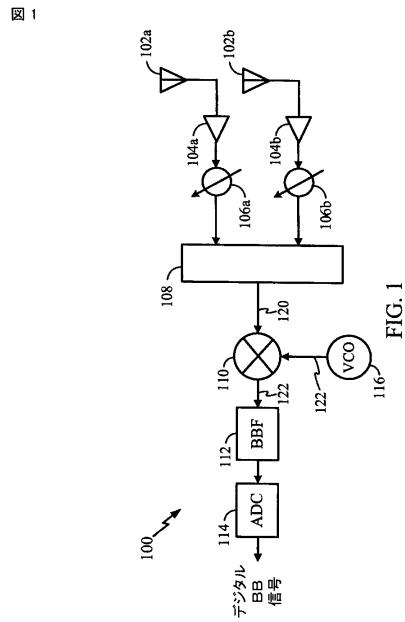

【図1】[0006] パワー分配器 / 結合器の典型的な実施態様を備える広帯域の直接変換レシーバを示す図

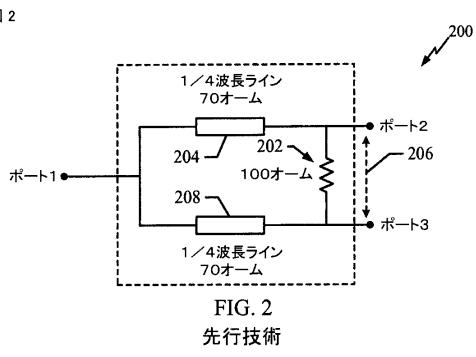

【図2】[0007] 従来のウィルキンソン・パワー分配器 / 結合器の詳細な図

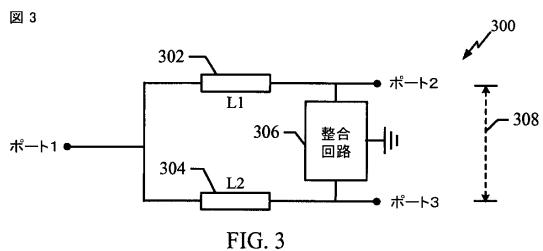

【図3】[0008] 分配器 / 結合器の典型的な実施態様を示す図

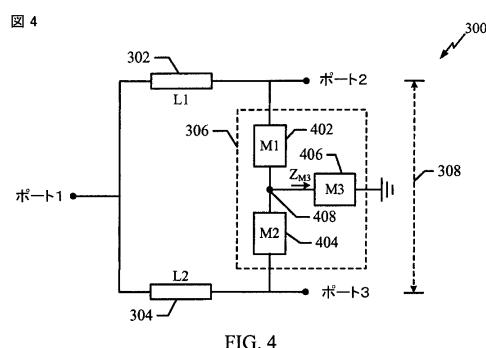

【図4】[0009] 図3に示された分配器 / 結合器の詳細な典型的な実施態様を示す図

【図5】[0010] 図4に示された分配器 / 結合器の、典型的な偶数のモードの説明を示す図

20

【図6】[0011] 図4に示された分配器 / 結合器の、典型的な偶数のモードの説明を示す図

【図7】[0012] 図4に示された分配器 / 結合器の、典型的な奇数のモードの説明を示す図

【図8】[0013] 分配器 / 結合器の構造の典型的な実施態様を示す図

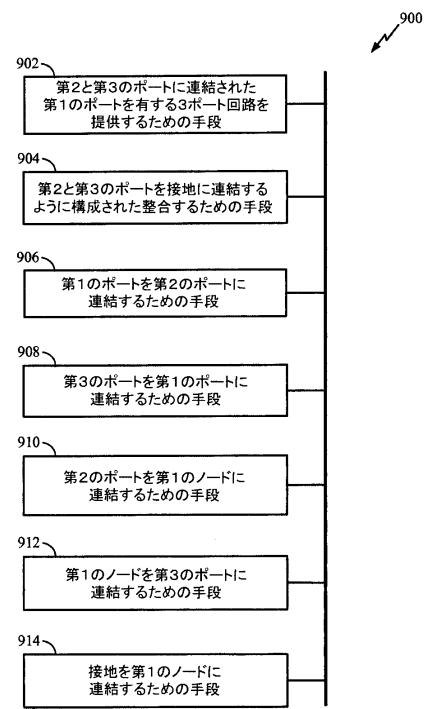

【図9】[0014] 分配器 / 結合器の装置の典型的な実施態様を示す図

【発明の詳細な説明】

【0007】

[0015] 添付図面に関連して以下に記載される詳細な説明は、本発明の典型的な実施形態の説明として意図され、本発明が実現されうる唯一の実施形態を表すようには意図されない。本明細書の全体にわたって用いられる「典型的 (exemplary)」という用語は、「例、実例、または例示を提供する」を意味し、他の典型的な実施形態に対して、必ずしも好ましいまたは有利であるようには解釈されるべきではない。詳細な説明は、本発明の典型的な実施形態の完全な理解を提供することを目的として特定の詳細を含む。本発明の典型的な実施形態は、これらの特定の詳細なしで実現されうることが当業者に明らかになるであろう。いくつかの事例では、周知の構造およびデバイスが、本明細書に示される典型的な実施形態の新規性を曖昧にすることを避けるために、ブロック図の形式で示される。

30

【0008】

[0016] 図1は、ワイヤレスデバイスにおける使用のためにRFビームフォーミングを使用する広帯域の直接変換レシーバ100を示す。多重アンテナ102(a-b)は各々、低雑音増幅器104(a-b)へ入力される広帯域のRF信号を受信する。LNA104の出力は、所望のビームパターン / 方向に関連した選択された位相シフトの量で、これらの受信されたRF信号の位相をシフトする移相器106(a-b)へ入力される。適切な位相シフトを提供することにより、移相器106は、複数の可能なビームパターン / 方向から選ばれた、選択されたビームパターン / 方向を生成することができる。

40

【0009】

[0017] 移相器106から出力された位相シフトされた信号は、RF広帯域ビームフォーミングされた信号120を生成するために新規の分配器 / 結合器108によって結合される。ビームフォーミングされた信号120は、電圧制御発振器(VCO)116によって生成されたローカル発振器(local oscillator)(LO)信号122を使用して、ダウ

50

ンコンバージョン (down-conversion) を行なうミキサー 110 へ入力される。ミキサー 110 は、ワイヤレスデバイスによってさらに処理され得るデジタル B B 信号を生成するために、ベースバンドフィルタ (B B F) 112 によってフィルタされ、アナログ - ディジタルフィルタ (A D C) 114 によってデジタル化された、ベースバンドビームフォーミングされた信号 122 を生成する。

#### 【0010】

[0018] 様々な典型的な実施態様では、新規な分配器 / 結合器 108 は、より小さな回路領域を利用するように構成され、従来の分配器 / 結合器と比較された時、レイアウトの複雑さの減少のために、より大きなフレキシビリティを提供する。分配器 / 結合器 108 が、信号送信中のような逆方向に流れる信号を処理するために、さらに動作することは、また注目されるべきである。したがって、送信中に、分配器 / 結合器 108 は、入力として送信信号を受信し、多重の移相器に接続された多重の出力への送信信号のパワーを分配する。その後、移相器は、所望の送信ビームパターンを形成するために、選択された量の位相シフトを提供する。

10

#### 【0011】

[0019] 図 2 は、従来のウィルキンソン・パワー分配器 / 結合器 200 を示している。例えば、パワー分配器 / 結合器 200 は、図 1 に示されるレシーバ 100 において使用され得る。パワー分配器 / 結合器 200 は、100 オームの抵抗器 202 と一緒に接続されている 2 つのノード (ポート 2、ポート 3) を備えている。抵抗器 202 は、典型的に非常に小さく、それは 2 つのノード (ポート 2、ポート 3) 間の間隔 206 が、通常、非常に小さいことを意味する。多くの実装において、相互に非常に接近しているノード (ポート 2、ポート 3) を持っていることは実現可能ではあり得ず、したがって、分配器 / 結合器 200 の実装は、増加したレイアウトの複雑さをもたらす、より少ないフレキシビリティを提供する。

20

#### 【0012】

[0020] 分配器 / 結合器 200 は、さらに 70 オームの特性インピダンスを提供する送信ライン 204 および 208 を備えている。送信ライン 204 および 208 のインピダンスとサイズの間に関係がある。例えば、送信ライン 204 のインピダンスがより大きくなるので、送信ライン 204 に必要とされる回路領域は、増加し得る。したがって、70 オームの送信ラインおよびより小さな抵抗器 202 を利用することによって、分配器 / 結合器 200 は、大きな回路領域および増加したレイアウトの複雑さの不利益を有する。従って、様々な典型的な実施態様では、新規なパワー分配器 / 結合器 108 は、より小さな回路領域を有し、ウィルキンソン・パワー分配器 / 結合器 200 と比較された時、より減少したレイアウトの複雑さに、より大きなフレキシビリティを提供する。

30

#### 【0013】

[0021] 図 3 は、分配器 / 結合器 300 の典型的な実施態様を示している。分配器 / 結合器 300 は、より小さな回路領域を利用し、および図 2 に示される従来のウィルキンソン・分配器 / 結合器 200 と比較された時、減少したレイアウトの複雑さに、増加したフレキシビリティを提供するように構成される。分配器 / 結合器 300 は、第 1 のポート (ポート 1) と第 2 のポート (ポート 2) の間に接続された第 1 の送信ライン 302 を備えている。分配器 / 結合器 300 は、さらに、ポート 1 と第 3 のポート (ポート 3) の間に接続された第 2 の送信ライン 304 を備えている。分配器 / 結合器 300 は、さらに、ポート 2 とポート 3 の間に連結された、の間に連結された整合回路 306 を備えている。整合回路 306 も、接地に連結されます。したがって、分配器 / 結合器 300 は、第 1、第 2 および第 3 のポートを有する 3 つのポート回路を備えており、接地に第 2 および第 3 のポートを連結するように構成された、整合回路を含んでいる。

40

#### 【0014】

[0022] 典型的な実施態様では、整合回路 306 は、ポート 2 とポート 3 の間の増加された間隔 308 を可能にし、それによって、増加されたレイアウトフレキシビリティを提供する。更に、送信ライン 302、304 のサイズが減らされることを可能にするよう

50

に、送信ライン 302、304 および整合回路 306 のインピダンスは、調整可能であり、それによって、図 2 に示された分配器 / 結合器 200 と比較された時に、全体としてより小さな回路をもたらす。

#### 【0015】

[0023] 図 4 は、分配器 / 結合器 300 の詳細な典型的な実施態様を示している。分配器 / 結合器 300 は、より小さな回路領域を利用し、および図 2 に示される従来のウィルキンソン分配器 / 結合器 200 と比較された時、減少されたレイアウトの複雑さのために増加されたフレキシビリティを提供するように設定可能である。送信ライン 302 は、長さ ( $L_1$ ) および特性インピダンス ( $Z_{L_1}$ ) を有している。ライン 304 は、長さ ( $L_2$ ) および特性インピダンス ( $Z_{L_2}$ ) を有している。整合回路 306 は、ポート 2 とポート 3 の間に直列に接続された第 1 の整合回路 ( $M_1$ ) 402、および第 2 の整合回路 ( $M_2$ ) 404 を備えている。第 3 の整合回路 ( $M_3$ ) 406 は、第 1 のノード 408 と接地の間に接続されている。第 3 の整合回路 ( $M_3$ ) 406 は、( $Z_{M_3}$ ) として定義された入力インピダンス値を有する。

#### 【0016】

[0024] 典型的な実施態様において、第 1 の 402 および第 2 の整合回路 404 の実装は、ポート 2 とポート 3 の間の増加された間隔 314 を提供し、それによって、増加されたレイアウトフレキシビリティを提供する。送信ライン 302、304 および整合回路 402、404 および 406 のインピダンスも、送信ライン 302、304 のサイズが減らされるように調整され得、それによって、図 2 に示された分配器 / 結合器 200 と比較された時に、全体としてより小さな回路をもたらす。減少された回路サイズを得るための分配器 / 結合器 300 のインピダンスへの調整は、下に提供される偶数および奇数モード分析の結果に基づいて実行され得る。

#### 【0017】

##### [偶数モード解析]

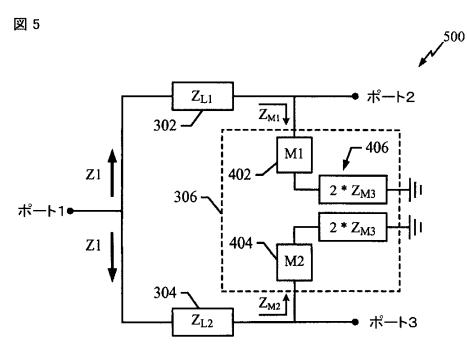

[0025] 図 5 は、ポート 1 に関して分配器 / 結合器 300 の典型的な偶数モードの説明 500 を示している。この説明において、送信ライン 302、304 および整合回路 402、404 および 406 のインピダンスは、それらが、ポート 1 において見られるインピダンス ( $Z_1$ ) と整合し、結合されるように構成される。図 5 において説明されたように、整合回路  $M_3$  406 は、入力インピダンス  $Z_{M_3}$  を形成するために結合された、2 つの別個のインピダンス提供するために分割される。

#### 【0018】

[0026] 典型的な実施態様において、インピダンス  $Z_1$  が 100 オームと等価になるように、上記のインピダンスは、設定され、したがって、ポート 1 で見られる結合されたインピダンスは、50 オームになるだろう。50 オームとは異なるポート 1 において見られる結合されたインピダンスを得るために、インピダンス値のレンジが使用され得ることが、注目されるべきである。整合回路  $M_1$  402、 $M_2$  404 および  $M_3$  406 のインピダンスの調節によって、所望のポート 1 のインピダンスを達成する上に、送信ライン 302 および 304 のサイズを調整することが可能である。例えば、送信ライン 302 および 304 のサイズは、ポート 1 において、所望の結合されたインピダンスを達成するために整合回路 402、404 および 406 のインピダンスを調整することにより、減少され得る。その結果、送信ライン 302 および 304 は、より小さなインピダンスを提供し、および対応するより小さなサイズを有するために、設定され得る。

#### 【0019】

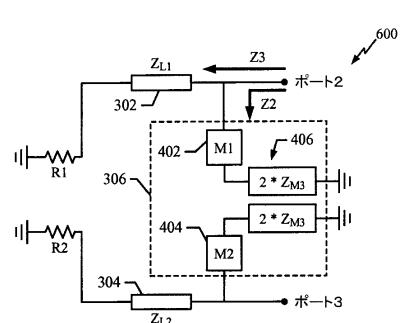

[0027] 図 6 は、ポート 2 および 3 に関して、新規の分配器 / 結合器 300 の典型的な偶数モードの説明 600 を示している。ポート 2 に関して、送信ライン 302、304 および整合回路 402、404 および 406 のインピダンスは、所望のインピダンス値を得るために、ポート 2 において見られるインピダンス ( $Z_2$  および  $Z_3$ ) が、並列結合を形成するように構成される。例えば、ポート 2 における所望のインピダンスが、50 オームである場合、インピダンス  $Z_2$  および  $Z_3$  の並列結合は、下記のように 50 オームに設定さ

10

20

30

40

50

れる。

【0020】

$$50 = Z2 \parallel Z3 \quad (Z2 \text{ と } Z3 \text{ の並列結合})$$

[0028] したがって、送信ライン302および304のサイズは、ポート2において、所望の結合されたインピダンスを達成するために整合回路402、404および406のインピダンスを調整することにより、減少され得る。その結果、送信ライン302および304は、より小さなインピダンスを提供し、および対応するより小さなサイズを有するために、設定され得る。

【0021】

[奇数モード解析]

10

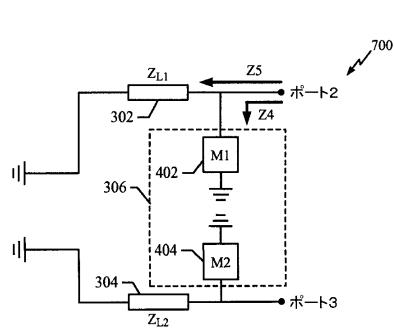

[0029] 図7は、ポート2および3に関して、新規の分配器/結合器300の典型的な奇数モードの説明700を示している。ポート2に関して、整合回路406は、0インピダンスを持つように設定され、および、したがって、接地への短絡と置き換えられる。伝送路302、304および整合回路402、404のインピダンスは、所望のインピダンス値を得るために、ポート2において見られるインピダンス( $Z4$ および $Z5$ )が、並列結合を形成するように構成される。例えば、ポート2における所望のインピダンスが、50オームである場合、インピダンス $Z4$ および $Z5$ の並列結合は、下記のように50オームに設定される。

【0022】

$$50 = Z4 \parallel Z5 \quad (Z4 \text{ と } Z5 \text{ の並列結合})$$

20

[0030] したがって、新規の分配器/結合器300は、送信ライン302、304のインピダンスを減少し、およびそれによって送信ライン302および304の必要なチップ領域を減少するために整合回路402、404および406のインピダンスを調整することにより構成され得る。分配器/結合器300は、また、図2に示される分配器/結合器200と比較して、より大きなレイアウトフレキシビリティを提供するためにポート2と3の間のポート間隔を増加させるように構成される。

【0023】

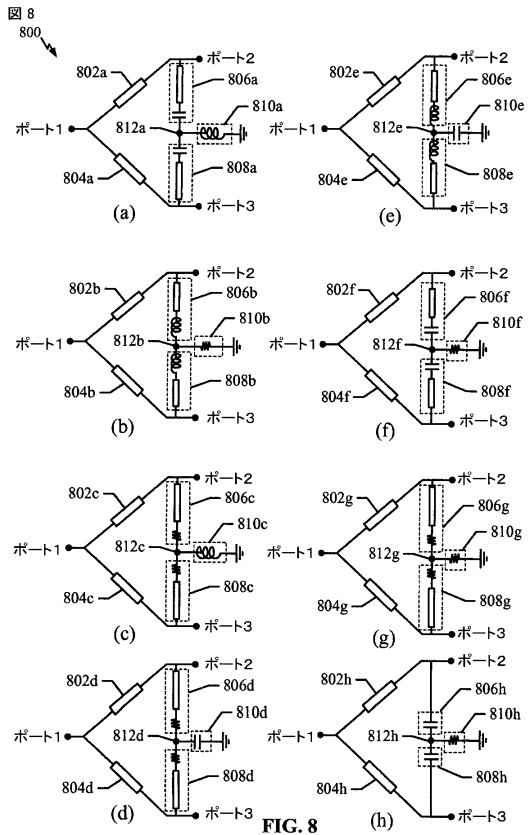

[0031] 図8は、分配器/結合器配置800の典型的な実施態様を示している。各配置において、ポート1は、送信ライン802によりポート2に連結されており、また、ポート1は、送信ライン804によりポート3に連結されている。第1の整合回路806は、ポート2とノード812の間に連結されており、また、第2の整合回路812は、ポート3とノード812の間に連結されている。第3の整合回路810は、ノード812と接地の間に連結されている。

30

【0024】

[0032] 様々な配置において、整合回路806、808、および810は、送信ライン、インダクタ、キャパシタおよび/または抵抗器を備える。例えば、整合回路806aは、送信ラインとキャパシタを備え、整合回路806bは、送信ラインとインダクタを傷つけ、および、整合回路806cは、送信ラインと抵抗器を備える。整合回路806および808は、送信ラインを備える必要がないことは注目されるべきである。例えば、整合回路806hおよび808hは、キャパシタのみを備える。

40

【0025】

[0033] 図8に示される全ての新規の分配器/結合器配置は、送信ライン802および804の必要なチップ領域を減少し、および、図2に示される分配器/結合器200と比較して、より大きなレイアウトフレキシビリティを提供するためにポート2と3の間のポート間隔を増加させるために整合回路806、808および810のインピダンスを調整することにより構成され得る。

【0026】

[0034] 図9は、分配器/結合器装置900の典型的な実施態様を示している。例えば、装置900は、図4に示される分配器/結合器300、または図1に示される分配器/結合器108としての使用に適している。態様において、装置900は、本明細書に記述

50

されたように、機能を提供するように構成された 1 つまたは複数のモジュールによって実装される。例えば、一態様において、各モジュールは、ハードウェアおよび / またはハードウェア実行ソフトウェアを備える。

【 0 0 2 7 】

[0035] 装置 900 は、第 2 と第 3 のポートに連結された第 1 のポートを有する 3 ポート回路を提供するための手段 (902) を備える第 1 のモジュールを備え、それは、態様においてパワー分配器 / 結合器 300 を備える。

【 0 0 2 8 】

[0036] 装置 900 は、第 2 と第 3 のポートを接地に連結するように構成された整合するための手段 (904) を備える第 2 のモジュールを備え、それは、態様において整合回路 306 を備える。

10

【 0 0 2 9 】

[0037] 装置 900、整合するための手段 904 は、第 1 のポートを第 2 のポートに連結するための手段 (906) を備える第 3 のモジュールを備え、それは、態様において送信ライン 302 を備える。

【 0 0 3 0 】

[0038] 装置 900、整合するための手段 904 は、第 3 のポートを第 1 のポートに連結するための手段 (908) を備える第 4 のモジュールも備え、それは、態様において送信ライン 304 を備える。

20

【 0 0 3 1 】

[0039] 装置 900、整合するための手段 904 は、第 2 のポートを第 1 のノードに連結するための手段 (910) を備える第 5 のモジュールも備え、それは、態様において整合回路 402 を備える。

【 0 0 3 2 】

[0040] 装置 900、整合するための手段 904 は、第 1 のノードを第 3 のポートに連結するための手段 (912) を備える第 6 のモジュールも備え、それは、態様において整合回路 404 を備える。

【 0 0 3 3 】

[0041] 装置 900、整合するための手段 904 は、接地を第 1 のノードに連結するための手段 (914) を備える第 7 のモジュールも備え、それは、態様において整合回路 406 を備える。

30

【 0 0 3 4 】

[0042] 当業者は、情報および信号は、異なる技術および技法のうちの任意の種類を使用して表され、または処理され得ることを、理解するであろう。例えば、上記の説明を通して参照され得るデータ、命令群、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界あるいは磁気粒子、光学界または光学粒子、またはそれら任意の組み合わせによって表わされ得る。トランジスタタイプおよび技術は、同じ結果を獲得するために置き換えられ、再配列され、またはそうでなければ修正され得ることはさらに注目される。例えば、PMOSトランジスタを利用して示された回路は、NMOSトランジスタを使用するために修正され得、その逆もまた同様である。従って、本明細書で開示された增幅器は、様々なトランジスタタイプおよび技術を使用して実現され得、図面で説明されるそれらのトランジスタタイプおよび技術に限定されない。例えば、BJT、GaAs、MOSFET、または任意の他のトランジスタ技術のようなトランジスタタイプが使用され得る。

40

【 0 0 3 5 】

[0043] 当業者はさらに、本明細書において開示された実施態様に関連して表現された様々な実例となる論理ブロック、モジュール、回路、アルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、または両方の組み合わせとして実装されうることを認識するだろう。ハードウェアおよびソフトウェアのこの互換性を明確に説明するために、多様な実例となるコンポーネント、ブロック、モジュール、回路、およびステップが、

50

概してそれらの機能の観点から上記で説明されている。このような機能が、ハードウェアとして実装されるか、あるいはソフトウェアとして実装されるかは、特定のアプリケーションおよびシステム全体に課せられる設計制約に依存する。当業者は、各特定のアプリケーションに関して様々な方法で、説明された機能性を実装し得るが、そのような実装の決定は、本発明の典型的な実施態様の範囲から逸脱を引き起こすとして解釈されるべきでない。

### 【 0 0 3 6 】

[0044] 本明細書において開示された実施態様に関連して表現された様々な実例となる論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ (D S P)、特定用途向け集積回路 (A S I C)、フィールドプログラマブルゲートアレイ (F P G A) または他のプログラマブル論理デバイス、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、あるいは本明細書に説明された機能を実行するようにデザインされたそれらの任意の組み合わせで実装または実行され得る。汎用プロセッサはマイクロプロセッサでありうるが、代替としてプロセッサは任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンでありうる。プロセッサはまた、例えば、D S Pとマイクロプロセッサ、複数のマイクロプロセッサ、D S Pコアと連結した1つまたは複数のマイクロプロセッサ、あるいはその他任意のこののような構成の組み合わせである、コンピューティングデバイスの組み合わせとして実装され得る。

### 【 0 0 3 7 】

[0045] 本明細書において開示された実施態様に関連して表現されたアルゴリズムまたは方法のステップは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこれら2つの組み合わせにおいて、具体化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ (R A M)、フラッシュメモリ、読み出し専用メモリ (R O M)、電気的プログラマブルR O M (E P R O M)、電気的消去可能プログラマブルR O M (E E P R O M (登録商標))、レジスタ、ハードディスク、リムーバルディスク、C D - R O M、または当該技術分野において周知である任意の他の形態の記憶媒体において存在し得る。典型的な記憶媒体は、プロセッサがこの記憶媒体から情報を読み取り、またこの記憶媒体に情報を書き込むことができるよう、プロセッサに連結される。代替においては、記憶媒体はプロセッサに統合され得る。プロセッサおよび記憶媒体はA S I Cに存在し得る。A S I Cは、ユーザ端末内に存在し得る。代替として、プロセッサおよび記憶媒体は、ユーザ端末内にディスクリートコンポーネントとして存在し得る。

### 【 0 0 3 8 】

[0046] 1つまたは複数の典型的な実施態様において、記述された機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせに実装され得る。ソフトウェアで実装される場合、これら機能は、コンピュータ可読媒体上で、1つまたは複数の命令またはコードとして送信または記憶され得る。コンピュータ可読媒体は、1つの場所から別の場所へのコンピュータプログラムの転送を促進する任意の媒体を含む非一時的なコンピュータ記憶媒体および通信媒体の双方を含む。非一時的な記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、このようなコンピュータ可読媒体は、R A M、R O M、E E P R O M (登録商標)、C D - R O Mまたは他の光ディスク記憶装置、磁気ディスク記憶装置またはその他の磁気記憶デバイス、または、データ構造または命令の形式で所望のプログラムコードを記憶または伝送するために使用され得、およびコンピュータによってアクセスされ得る他の任意の媒体を備え得る。また、任意の接続は、コンピュータ可読媒体と厳密には称され得る。例えば、ソフトウェアがウェブサイト、サーバ、または他の遠隔ソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線 (D S L)、あるいは赤外線、無線、およびマイクロ波のようなワイヤレス技法を使用して送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、D S L、あるいは赤外線、無線、お

10

20

30

40

50

およびマイクロ波のようなワイヤレス技法は、媒体の定義に含まれる。ここで使用される場合、ディスク (disk) およびディスク (disc) は、コンパクトディスク (CD)、レーザーディスク (登録商標)、光ディスク、デジタル多目的ディスク (DVD)、フロッピー (登録商標) ディスクおよびブルーレイ (登録商標) ディスクを含み、ここでディスク (disks) は、通常磁気的にデータを再生し、一方、ディスク (discs) は、レーザーを用いて光学的にデータを再生する。上記の組み合わせもまた、コンピュータ可読媒体の範囲内に含まれるべきである。

**【 0 0 3 9 】**

[0047] 開示された典型的な実施態様の説明は、任意の当業者に、本発明の製造または使用を可能にするように提供される。これらの典型的な実施態様への様々な修正は、当業者にとって容易に明らかであり、ここに定義された一般的な原理は、本発明の精神または範囲から逸脱することなく、他の実施態様にも適用されうる。したがって、本発明は、本明細書に示された典型的な実施態様に限定されるようには意図されず、本明細書に開示された原理および新規な特徴と一致する最も広い範囲を与えられることとなる。

以下に、出願当初の特許請求の範囲に記載された発明を付記する。

**[ C 1 ]**

第 2 のおよび第 3 のポートに連結された第 1 のポートを持つ 3 つのポート回路と、接地上に前記第 2 のおよび第 3 のポートを連結するように構成された整合回路とを備えた装置。

**[ C 2 ]**

前記整合回路は、第 1 のノードと前記第 2 のポートとの間に連結された第 1 の整合回路と、前記第 1 のノードと前記第 3 のポートとの間に連結された第 2 の整合回路、および、前記第 1 のノードと接地上に接続された第 3 の整合回路を備える C 1 に記載の装置。

**[ C 3 ]**

前記第 1 のポートと前記第 2 のポートとの間に連結された第 1 の送信ラインおよび、前記第 1 のポートと前記第 3 のポートとの間に連結された第 2 の送信ラインをさらに備える、C 2 に記載の装置。

**[ C 4 ]**

前記第 1 のおよび第 2 の送信ライン、および前記第 1 の、第 2 のおよび第 3 の整合回路は、選択された特性インピダンス値に整合された前記第 1 のポートにおいて見られる結合されたインピダンス値を提供するように構成された、C 3 に記載の装置。

**[ C 5 ]**

前記選択された特性インピダンス値は、50 オームに設定された C 4 に記載の装置。

**[ C 6 ]**

前記第 1 の、第 2 のおよび第 3 の整合回路は、前記第 1 のおよび第 2 の送信ラインのサインズを調整するように構成された C 3 に記載の装置。

**[ C 7 ]**

前記第 1 のおよび第 2 の整合回路は、前記第 2 のおよび第 3 のポートとの間の間隔を増加させるように構成された C 2 に記載の装置。

**[ C 8 ]**

前記第 1 のおよび第 2 の送信ライン、および前記第 1 の、第 2 のおよび第 3 の整合回路は、選択された特性インピダンス値に整合された前記第 2 のポートにおいて見られる結合されたインピダンス値を提供するように構成された、C 3 に記載の装置。

**[ C 9 ]**

前記選択された特性インピダンス値は、50 オームに設定された C 8 に記載の装置。

**[ C 1 0 ]**

前記装置は、双方向の受動的なパワー結合器 / 分配器を形成する C 1 に記載の装置。

**[ C 1 1 ]**

前記双方向の受動的なパワー結合器 / 分配器は、トランシーバにおける使用のために構成される C 1 0 に記載の装置。

**[ C 1 2 ]**

10

20

30

40

50

第2のおよび第3のポートに連結された第1のポートを持つ3つのポート回路を提供するための手段と、接地に前記第2のおよび第3のポートを連結するように構成された整合するための手段とを備えた装置。

[ C 1 3 ]

整合するための前記手段は、第1のノードと前記第2のポートとを連結するための手段と、前記第1のノードと前記第3のポートとを連結するための手段と、前記第1のノードに接地を連結するための手段とを備えるC 1 2に記載の装置。

[ C 1 4 ]

前記第1のおよび第2のポートとの間に第1の送信ラインを連結するための手段および、第1のおよび第3のポートとの間に第2の送信ラインを連結するための手段をさらに備える、C 1 3に記載の装置。

10

[ C 1 5 ]

前記第1の送信ライン、前記第2の送信ライン、前記第2のポートを連結するための前記手段、前記第1のノードを連結するための前記手段、および、前記接地を連結するための前記手段は、選択された特性インピダンス値に整合された前記第1のポートにおいて見られる結合されたインピダンス値を提供するように構成された、C 1 4に記載の装置。

[ C 1 6 ]

前記第2のポートを連結するための前記手段、前記第1のノードを連結するための前記手段、および、前記接地を連結するための前記手段は、前記第1のおよび第2の送信ラインのサイズを調整するように構成されたC 1 4に記載の装置。

20

[ C 1 7 ]

前記第2のポートを連結するための前記手段、前記第1のノードを連結するための前記手段は、前記第2のおよび第3のポートとの間の間隔を増加させるように構成されたC 1 4に記載の装置。

[ C 1 8 ]

前記第1の送信ライン、前記第2の送信ライン、前記第2のポートを連結するための前記手段、前記第1のノードを連結するための前記手段、および、前記接地を連結するための前記手段は、選択された特性インピダンス値に整合された前記第2のポートにおいて見られる結合されたインピダンス値を提供するように構成された、C 1 4に記載の装置。

30

[ C 1 9 ]

前記装置は、双方向の受動的なパワー結合器／分配器を形成するC 1 2に記載の装置。

[ C 2 0 ]

前記双方向の受動的なパワー結合器／分配器は、トランシーバにおける使用のために構成されるC 1 9に記載の装置。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 エーヤイー、ダニエル

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 岸田 伸太郎

(56)参考文献 実開昭58-003602(JP, U)

特開2000-307314(JP, A)

特開昭59-176903(JP, A)

特開2007-019827(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01P 1/00 - 11/00