(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4865197号

(P4865197)

(45) 発行日 平成24年2月1日(2012.2.1)

(24) 登録日 平成23年11月18日(2011.11.18)

|                |              |

|----------------|--------------|

| (51) Int.Cl.   | F 1          |

| HO 1 L 27/00   | (2006.01)    |

| HO 1 L 23/52   | (2006.01)    |

| HO 1 L 21/3205 | (2006.01)    |

| HO 1 L 25/065  | (2006.01)    |

| HO 1 L 25/07   | (2006.01)    |

| HO 1 L 27/00   | HO 1 L 21/88 |

|                | HO 1 L 25/08 |

|                | J            |

|                | B            |

請求項の数 29 (全 34 頁) 最終頁に続く

|           |                               |           |                                                        |

|-----------|-------------------------------|-----------|--------------------------------------------------------|

| (21) 出願番号 | 特願2004-194690 (P2004-194690)  | (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (22) 出願日  | 平成16年6月30日 (2004.6.30)        | (74) 代理人  | 100110928<br>弁理士 速水 進治                                 |

| (65) 公開番号 | 特開2006-19433 (P2006-19433A)   | (74) 代理人  | 100118544<br>弁理士 野本 可奈                                 |

| (43) 公開日  | 平成18年1月19日 (2006.1.19)        | (74) 代理人  | 100127236<br>弁理士 天城 聰                                  |

| 審査請求日     | 平成19年5月17日 (2007.5.17)        | (72) 発明者  | 栗田 洋一郎<br>神奈川県川崎市中原区下沼部 1753 番地<br>NECエレクトロニクス株式会社内    |

| 審判番号      | 不服2010-17543 (P2010-17543/J1) |           |                                                        |

| 審判請求日     | 平成22年8月5日 (2010.8.5)          |           |                                                        |

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

平板状の配線体と、

前記配線体の一方の面に設けられた第一の半導体素子と、

前記一方の面の全面および前記第一の半導体素子の側面を被覆する封止樹脂と、

前記封止樹脂により被覆された後の前記配線体に接続され、前記配線体の他方の面上に前記第一の半導体素子に対して少なくとも一部が対向する位置に設けられた第二の半導体素子と、を有し、

前記配線体は、

前記一方の面側に設けられ、前記第一の半導体素子と接続しており、前記配線体から露出した全面が前記封止樹脂によって被覆されている配線層と、

前記配線層の前記第一の半導体素子が接続されていない側に積層され、前記配線層を支持する支持層と、

前記支持層を貫通し、前記配線層と接続している貫通電極と、を備え、

前記配線体を介して前記第一の半導体素子と前記第二の半導体素子とが電気的に接続されており、

前記第二の半導体素子は前記他方の面上に電極を介して接続されており、

前記貫通電極と前記電極とが前記配線体の面に対し、略垂直に一直線に接続され、

前記支持層がシリコン、セラミック、および珪ホウ酸ガラスからなる群から選択される一種以上の材料からなることを特徴とする半導体装置。

10

20

**【請求項 2】**

請求項 1 に記載の半導体装置において、

前記支持層はシリコンからなり、

前記配線体は前記他方の面側に絶縁膜をさらに備え、

前記貫通電極は前記支持層および前記絶縁膜を貫通して設けられていることを特徴とする半導体装置。

**【請求項 3】**

請求項 1 に記載の半導体装置において、

前記支持層はセラミックまたは珪ホウ酸ガラスからなることを特徴とする半導体装置。

**【請求項 4】**

請求項 1 乃至 3 いずれか 1 項に記載の半導体装置において、

前記貫通電極は、前記配線層を貫通することを特徴とする半導体装置。

**【請求項 5】**

請求項 1 乃至 4 いずれか 1 項に記載の半導体装置において、

平面視で前記第一の半導体素子と前記第二の半導体素子とが重なる部分において、前記第一の半導体素子と前記第二の半導体素子とが前記貫通電極を介して電気的に接続されていることを特徴とする半導体装置。

**【請求項 6】**

請求項 1 乃至 5 いずれか 1 項に記載の半導体装置において、

前記第一の半導体素子は、前記配線体の前記一方の面に第一の電極を介して接続され、

前記第二の半導体素子は、前記配線体の前記他方の面に第二の電極を介して接続されており、

前記第一の電極と前記貫通電極と前記第二の電極とが、前記配線層の面に対して略垂直に一直線に接続していることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 乃至 6 いずれか 1 項に記載の半導体装置において、

前記第一の半導体素子は、前記配線体の前記一方の面に第一の電極を介して接続され、

前記第二の半導体素子は、前記配線体の前記他方の面に第二の電極を介して接続されており、

前記第一の電極及び前記第二の電極のすべてが、平面視で前記第一の半導体素子の内側の領域に配置されていることを特徴とする半導体装置。

**【請求項 8】**

請求項 1 乃至 7 いずれか 1 項に記載の半導体装置において、

前記貫通電極は、格子状に平面配置されていることを特徴とする半導体装置。

**【請求項 9】**

請求項 8 に記載の半導体装置において、

前記貫通電極は、正方格子状に平面配置されていることを特徴とする半導体装置。

**【請求項 10】**

請求項 8 に記載の半導体装置において、

前記貫通電極は、斜格子状に平面配置されていることを特徴とする半導体装置。

**【請求項 11】**

請求項 1 乃至 10 いずれか 1 項に記載の半導体装置において、

前記支持層は、能動素子が形成されたシリコン層であることを特徴とする半導体装置。

**【請求項 12】**

請求項 1 乃至 11 いずれか 1 項に記載の半導体装置において、

前記配線体は、絶縁膜と、前記支持層と、前記配線層とがこの順に積層された構成を有し、前記第一の半導体素子が前記配線層に接続され、前記第二の半導体素子が前記絶縁膜側に接続されていることを特徴とする半導体装置。

**【請求項 13】**

請求項 1 乃至 12 いずれか 1 項に記載の半導体装置において、

10

20

30

40

50

前記封止樹脂を貫通する貫通プラグを備えることを特徴とする半導体装置。

**【請求項 14】**

請求項 1 乃至 13 いずれか 1 項に記載の半導体装置において、

前記配線層が多層配線層であることを特徴とする半導体装置。

**【請求項 15】**

請求項 1 乃至 14 いずれか 1 項に記載の半導体装置において、

前記第一の半導体素子が前記封止樹脂に埋設されていることを特徴とする半導体装置。

**【請求項 16】**

請求項 1 乃至 15 いずれか 1 項に記載の半導体装置において、前記貫通電極は、前記配線体の前記他方の面に対し凸状に張り出していることを特徴とする半導体装置。 10

**【請求項 17】**

請求項 1 乃至 16 いずれか 1 項に記載の半導体装置において、前記貫通電極は、複数の導電体を積層して形成されていることを特徴とする半導体装置。

**【請求項 18】**

基板上に形成された支持層を貫通する導体ヴィアを形成する工程と、

前記基板上に前記導体ヴィアと接続し、前記支持層により支持される配線層を形成する工程と、

前記配線層と第一の半導体素子とを接続させる工程と、

前記配線層の前記配線体から露出した全面および前記第一の半導体素子の側面を封止樹脂により被覆する工程と、 20

前記基板の前記配線層の形成面の裏面から前記基板を薄化する工程と、

前記基板を薄化する前記工程の後に前記配線層を介して第二の半導体素子の少なくとも一部を前記第一の半導体素子に対向させ、前記導体ヴィアを介して前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する工程と、

を含み、

前記配線層の表面および前記第一の半導体素子の側面を封止樹脂により被覆する前記工程は、前記基板上に形成された前記配線層の表面の全面を前記封止樹脂により覆う工程を含み、

前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する前記工程において、前記支持層側の表面に露出させた前記導体ヴィアに電極を介して前記第二の半導体素子を接続し、前記導体ヴィアと前記電極とを前記配線層の面に対し、略垂直に一直線に接続させ、 30

前記支持層がシリコン、セラミック、および珪ホウ酸ガラスからなる群から選択される一種以上の材料からなることを特徴とする半導体装置の製造方法。

**【請求項 19】**

請求項 18 に記載の半導体装置の製造方法において、

導体ヴィアを形成する前記工程は、シリコンからなる前記支持層との間に絶縁層が形成された前記基板の前記絶縁層及び前記支持層に前記導体ヴィアを貫通させることを特徴とする半導体装置の製造方法。

**【請求項 20】**

請求項 18 に記載の半導体装置の製造方法において、

導体ヴィアを形成する前記工程は、セラミックまたは珪ホウ酸ガラスからなる前記支持層に前記導体ヴィアを貫通させることを特徴とする半導体装置の製造方法。 40

**【請求項 21】**

請求項 18 乃至 20 いずれか 1 項に記載の半導体装置の製造方法において、

前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する前記工程は、平面視で前記第一の半導体素子と前記第二の半導体素子とが重なる部分において、前記導体ヴィアを介して前記第一の半導体素子と前記第二の半導体素子とを電気的に接続させる工程を含むことを特徴とする半導体装置の製造方法。

**【請求項 22】**

50

請求項 1 8 乃至 2 1 いずれか 1 項に記載の半導体装置の製造方法において、前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する前記工程は、前記第一の半導体素子を前記配線層の一方の面に第一の電極を介して接続し、前記第二の半導体素子を前記配線層の他方の面に第二の電極を介して接続し、前記第一の電極と前記導体ヴィアと前記第二の電極とを前記配線層の面に対して略垂直に一直線に接続させる工程を含むことを特徴とする半導体装置の製造方法。

**【請求項 2 3】**

請求項 1 8 乃至 2 2 いずれか 1 項に記載の半導体装置の製造方法において、基板を薄化する前記工程は、前記基板を除去し、前記導体ヴィアの表面を露出させる工程を含むことを特徴とする半導体装置の製造方法。 10

**【請求項 2 4】**

請求項 1 8 乃至 2 3 いずれか 1 項に記載の半導体装置の製造方法において、配線層を形成する前記工程は、表面に絶縁膜と前記配線層を支持する支持層とがこの順に積層された前記基板を準備する工程と、前記支持層上に前記配線層を設ける工程と、を含むことを特徴とする半導体装置の製造方法。

**【請求項 2 5】**

請求項 1 8 乃至 2 4 いずれか 1 項に記載の半導体装置の製造方法において、前記導体ヴィアは、格子状に平面配置されていることを特徴とする半導体装置の製造方法。 20

**【請求項 2 6】**

請求項 2 5 に記載の半導体装置の製造方法において、前記導体ヴィアは、正方格子状に平面配置されていることを特徴とする半導体装置の製造方法。

**【請求項 2 7】**

請求項 2 5 に記載の半導体装置の製造方法において、前記導体ヴィアは、斜格子状に平面配置されていることを特徴とする半導体装置の製造方法。

**【請求項 2 8】**

請求項 1 8 乃至 2 7 いずれか 1 項に記載の半導体装置の製造方法において、前記基板がシリコン基板であることを特徴とする半導体装置の製造方法。 30

**【請求項 2 9】**

請求項 1 8 乃至 2 8 いずれか 1 項に記載の半導体装置の製造方法において、前記配線層の表面および前記第一の半導体素子の側面を封止樹脂により被覆する前記工程は、

前記配線層の表面の全面を前記封止樹脂により封止することにより前記第一の半導体素子を埋設する工程と、

前記第一の半導体素子を埋設する前記工程の後に、前記封止樹脂を薄化して前記第一の半導体素子の表面を露出させる工程と、 40

を含むことを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、半導体装置およびその製造方法に関する。

**【背景技術】**

**【0 0 0 2】**

従来の半導体装置としては、特許文献 1 に記載されたものがある。同文献には、回路基板の両面に半導体装置がフリップチップ実装により設けられている両面実装構造体が開示されている。特許文献 1 によれば、実装後の半導体装置を封止する封止樹脂のガラス転移 50

温度を調節することにより、生産歩留まりおよび信頼性の向上が可能であるとされている。

【0003】

【特許文献1】特開2001-345418号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところが、上記文献記載の従来技術では、基板と半導体素子の基材との間の熱膨張係数の差により接合精度や品質が劣化する懸念があった。このため、半導体素子への微細な配線の接続が困難であった。また、接続信頼性においても改善の余地があった。このため、配線密度の高い大規模なチップ間接続を実現することが困難であった。10

【0005】

本発明は、上記事情に鑑みてなされたものであり、その目体は、複数の半導体素子間を高密度で接続する技術を提供することにある。また、本発明の別の目的は、複数の半導体素子の接続信頼性を向上させることにある。

【課題を解決するための手段】

【0006】

本発明によれば、平板状の配線体と、前記配線体の一方の面に設けられた第一の半導体素子と、前記一方の面の全面および前記第一の半導体素子の側面を被覆する封止樹脂と、20

前記封止樹脂により被覆された後の前記配線体に接続され、前記配線体の他方の面上に前記第一の半導体素子に対して少なくとも一部が対向する位置に設けられた第二の半導体素子と、を有し、前記配線体は、前記一方の面側に設けられ、前記第一の半導体素子と接続してあり、前記配線体から露出した全面が前記封止樹脂によって被覆されている配線層と、前記配線層の前記第一の半導体素子が接続されていない側に積層され、前記配線層を支持する支持層と、前記支持層を貫通し、前記配線層と接続している貫通電極と、を備え、前記配線体を介して前記第一の半導体素子と前記第二の半導体素子とが電気的に接続されており、前記第二の半導体素子は前記他方の面上に電極を介して接続されており、前記貫通電極と前記電極とが前記配線体の面に対し、略垂直に一直線に接続され、前記支持層がシリコン、セラミック、および珪ホウ酸ガラスからなる群から選択される一種以上の材料からなることを特徴とする半導体装置が提供される。30

【0007】

本発明の半導体装置は、配線層と、前記配線層を支持する支持層と、前記配線層および前記支持層を貫通する貫通電極と、を備えるため、貫通電極を高密度で配設することが可能とのある。また、支持層を有するため、貫通電極を高密度で設けた際にも、半導体素子と貫通電極との接続信頼性の向上が可能である。よって、複数のチップや大規模なチップ間接続が可能となる。

【0008】

本発明において、前記配線層および前記支持層がこの順に積層された構成とすることができる。また、貫通電極が複数の導電部材から構成されていてもよい。

【0009】

本発明の半導体装置において、前記支持層の材料は、線膨張係数が0.5 ppm / 以上5 ppm / 以下であってもよい。こうすることにより、第一の半導体装置と第二の半導体装置との接続信頼性をさらに向上させることができる。40

【0010】

本発明の半導体装置において、前記支持層がシリコン層であってもよい。剛性の高いシリコン層上に微細な配線体を形成し、支持層と熱膨張係数が等しいシリコン半導体素子を接続することで、高精度かつ信頼性の高い接続が可能となる。

【0011】

本発明の半導体装置において、前記支持層にトランジスタ等の能動素子が形成されていてもよい。50

**【 0 0 1 2 】**

本発明の半導体装置において、前記配線体は、絶縁膜と、前記支持層と、前記配線層とがこの順に積層された構成を有し、前記第一の半導体素子が前記配線層に接続され、前記第二の半導体素子が前記絶縁膜側に接続されていてもよい。こうすることにより、半導体の表面を確実に絶縁するとともに、半導体素子同士の接続信頼性を充分に確保することができる。本発明において、半導体素子同士が、シリコン層および絶縁膜を貫通する貫通電極と、配線層と、を介して電気的に接続されている構成とすることができる。

**【 0 0 1 4 】**

本発明の半導体装置においては、導電体が平板状の絶縁体を貫通している。このため、導電体の狭ピッチ化が可能である。よって、第一の半導体素子と第二の半導体素子とを接続する導電体を高密度で配置することが可能である。10

**【 0 0 1 5 】**

本発明において、絶縁体を貫通する導電体は連続する一部材から構成されていてもよいし、複数の導電部材が接合されて電気的接続が確保されている構成としてもよい。たとえば一つの導電体が一つの導電プラグからなる構成であってもよい。また、配線層が多層配線であって、導電体が配線層中の配線およびプラグが接合されている構成であってもよい。。

**【 0 0 1 6 】**

本発明の半導体装置において、前記導電体は、前記絶縁体のいずれかの面に設けられた接続電極を含み、前記接続電極の側面が前記絶縁体中に埋設されるとともに、前記接続電極の少なくとも一つの面の全体が前記絶縁体から露出している構成とすることができます。この構成では、接続電極の少なくとも一つの面の全体が前記絶縁体から露出しているため、外部引き出し電極が絶縁体に接していない。こうすることにより、接続電極を高密度で精密に設けることが可能となる。20

**【 0 0 1 7 】**

なお、本発明において、接続電極の側面が絶縁体に接している構成とすることができます。また、接続電極の側面外周全体が絶縁体に接していてもよい。また、本発明において、接続電極が設けられている側の配線体の面を平坦面とすることができます。

**【 0 0 1 8 】**

また、本発明において、接続電極は、半導体素子に電気的に接続する素子接続電極および素子の外部の導電部材に接続する外部接続電極を含む。本発明では、これらのいずれについても上述した構成とすることができます。30

**【 0 0 1 9 】**

本発明の半導体装置において、前記導電体は、前記絶縁体のいずれかの面に接して設けられた配線を含み、前記配線の側面の少なくとも一部および前記配線の一つの面が前記絶縁体から露出している構成とすることができます。こうすることにより、微細な配線を高密度で設けることが可能な構成とすることができます。

**【 0 0 2 0 】**

なお、本発明の半導体装置において、前記配線が前記引き出し電極に電気的に接続している構成とすることができます。また、本発明において、前記配線の側面全体が前記絶縁体から露出していてもよい。40

**【 0 0 2 1 】**

本発明の半導体装置において、前記配線の少なくとも一部が前記封止樹脂に埋設されていてもよい。こうすることにより、半導体装置の強度を向上させることができる。

**【 0 0 2 2 】**

本発明の半導体装置において、前記導電体の最小間隔が $50\mu m$ 以下であってもよい。こうすることにより、半導体素子間のデータ転送能を向上させることができる。

**【 0 0 2 3 】**

本発明の半導体装置において、前記導電体は、種々の平面配置とすることができます。たとえば、正方格子状、千鳥格子等の斜格子状等の配置をとることができます。50

## 【0024】

本発明の半導体装置において、前記第一の半導体素子の前記配線体の側に設けられた第一導電パッドと、前記第二の半導体素子の前記配線体の側の面に設けられた第二導電パッドとが、平面視において一致している構成とすることができる。これにより、半導体素子間のデータ転送能をより一層向上させることができる。

## 【0025】

本発明の半導体装置において、前記封止樹脂を貫通する貫通プラグを有する構成とすることができる。こうすることにより、熱応力緩和機能により優れた二次実装信頼性が得られる。また、複合素子である半導体装置全体がフリップチップ接続される構成とすることができます。なお、本発明の半導体装置において、前記貫通プラグは前記配線層中の配線に接続された構成とすることができます。10

## 【0026】

本発明の半導体装置において、前記配線層が多層配線層であってもよい。これにより、配線体の設計の自由度を高めることができる。

## 【0027】

本発明の半導体装置において、前記第一の半導体素子が前記封止樹脂に埋設されていてもよい。これにより、第一の半導体素子の表面を確実に絶縁するとともに、第一の半導体素子を保護することができます。

## 【0028】

本発明によれば、基板上に形成された支持層を貫通する導体ヴィアを形成する工程と、前記基板上に前記導体ヴィアと接続し、前記支持層により支持される配線層を形成する工程と、前記配線層と第一の半導体素子とを接続させる工程と、前記配線層の前記配線体から露出した全面および前記第一の半導体素子の側面を封止樹脂により被覆する工程と、前記基板の前記配線層の形成面の裏面から前記基板を薄化する工程と、前記基板を薄化する前記工程の後に前記配線層を介して第二の半導体素子の少なくとも一部を前記第一の半導体素子に対向させ、前記導体ヴィアを介して前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する工程と、を含み、前記配線層の表面および前記第一の半導体素子の側面を封止樹脂により被覆する前記工程は、前記基板上に形成された前記配線層の表面の全面を前記封止樹脂により覆う工程を含み、前記第一の半導体素子と前記第二の半導体素子とを電気的に接続する前記工程において、前記支持層側の表面に露出させた前記導体ヴィアに電極を介して前記第二の半導体素子を接続し、前記導体ヴィアと前記電極とを前記配線層の面に対し、略垂直に一直線に接続させ、前記支持層がシリコン、セラミック、および珪ホウ酸ガラスからなる群から選択される一種以上の材料からなることを特徴とする半導体装置の製造方法が提供される。2030

## 【0029】

また、本発明の半導体装置において、基板上に前記配線体が形成され、前記配線体上に前記第一の半導体素子が接続され、前記第一の半導体素子の側面および前記配線体の露出面が前記封止樹脂により被覆された後に、前記基板を除去することにより得られる構成とすることができます。

## 【0030】

本発明においては、配線体が基板上に設けられた状態で第一の半導体素子が接続され、この後、基板が薄化または除去される。このため、第一の基板と配線体との接合を安定的に行なうことが可能である。なお、本発明において、「半導体基板上」は、半導体基板上に接して設けられた構成であっても他の層を介して設けられた構成であってもよい。40

## 【0031】

本発明の半導体装置において、前記基板の線膨張係数が $0.5\text{ ppm}$ 以上 $5\text{ ppm}$ /以下であってもよい。こうすれば、製造安定性にさらに優れた構成とすることができます。

## 【0032】

本発明の半導体装置において、前記基板がシリコン基板であってもよい。このようにす50

れば、より一層製造安定性に優れた構成とすることができます。

**【0033】**

また、本発明の製造方法において、配線層を準備する工程に用いられる基板と、前記第一の半導体素子を構成する半導体基板と、前記第二の半導体素子を構成する半導体基板とが、同じ材料であってもよい。こうすれば、基板と素子の接続時における反りを確実に抑制することができる。このため、接続信頼性を向上させることができる。

**【0034】**

また、本発明の半導体装置の製造方法において、基板を薄化する前記工程は、前記基板を除去し、前記配線層の表面を露出させる工程を含んでもよい。こうすることにより、装置構成を簡素化しつつ、安定的な半導体装置の製造が可能となる。

10

**【0035】**

本発明の半導体装置の製造方法において、配線層を準備する前記工程は、表面に絶縁膜と前記配線層を支持する支持層とがこの順に積層された前記基板を準備する工程と、前記支持層上に前記配線層を設ける工程と、を含んでもよい。こうすることにより、配線層と半導体素子の接続信頼性をより一層向上させることができます。

**【発明の効果】**

**【0036】**

本発明によれば、複数の半導体素子間を高密度で接続する技術が実現される。また、本発明によれば、複数の半導体素子の接続信頼性を向上させる技術が実現される。

**【発明を実施するための最良の形態】**

20

**【0037】**

以下、本発明の実施の形態について、図面を用いて説明する。なお、すべての図面において、同じ構成要素には共通の符号を付し、適宜説明を省略する。

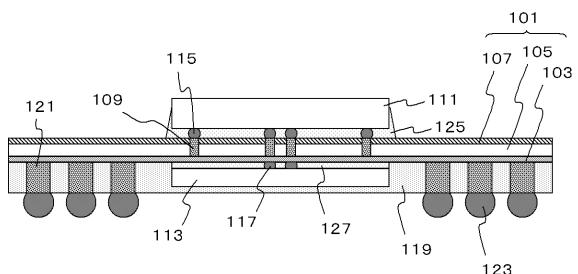

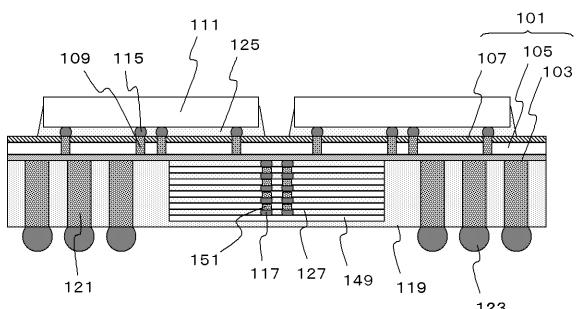

**【0038】**

(第一の実施形態)

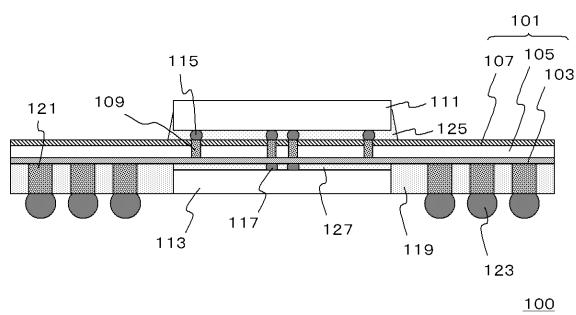

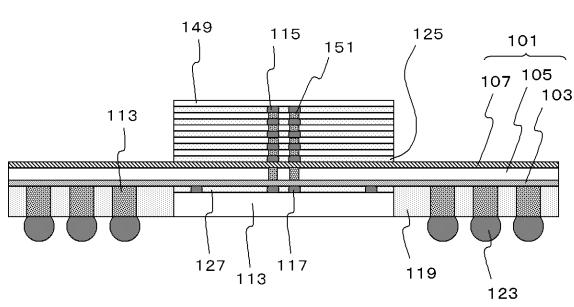

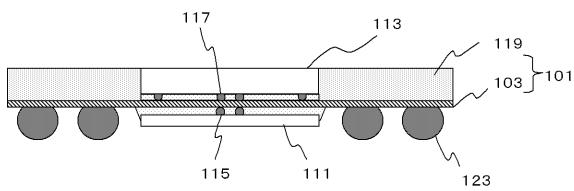

図1は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図1に示した半導体装置100は、平板状の配線体101と、配線体101の一方の面に設けられた第一の半導体素子113と、配線体101の第一の半導体素子113の設けられた側の面および第一の半導体素子113の側面を被覆する絶縁樹脂119と、配線体101の他方の面に、第二の半導体素子111に対向配置させて設けられた第二の半導体素子111と、を有する。

30

**【0039】**

配線体101は、配線層103、シリコン層105および絶縁膜107がこの順に積層された構成である。第一の半導体素子113は配線層103に接して設けられ、第二の半導体素子111は絶縁膜107に接して設けられている。

**【0040】**

配線層103は、平板状の絶縁体と、絶縁体を貫通する導電体と、を有する。導電体を介して第二の半導体素子111と第一の半導体素子113とが電気的に接続される。また、配線層103は、所定の形状および配置を有する配線を備える。配線層103は、単層であってもよいし、多層であってもよい。なお、配線層103の具体的な構成は、第三の実施形態および第七の実施形態において後述する構成とすることができる。

40

**【0041】**

シリコン層105は、配線層103を支持する支持層である。シリコン層105の配線層103と反対側の面に設けられた絶縁膜107は、たとえばSiO<sub>2</sub>等の酸化膜、SiNやSiON等の窒化膜とする。

**【0042】**

なお、配線層103の支持層として、本実施形態および以降の実施形態においてはシリコン層105を例示しているが、第一の半導体素子113および第二の半導体素子111の基板として通常用いられているSiと同程度の熱膨張率を有する他の材料とすることもできる。

50

## 【0043】

支持層として、たとえば、線膨張係数が .0.5 ppm / 以上 5 ppm / 以下の材料を用いることができる。線膨張係数を 0.5 ppm / 以上とすることにより、半導体装置 100 の製造歩留まりを向上させることができる。また、5 ppm / 以下 線膨張係数をとすることにより、第一の半導体素子 113 および第二の半導体素子 111 との電気的な接続信頼性を充分に確保することができる。また、支持層は、熱伝導性に優れた材料により構成するとよい。シリコン以外の支持層の材料として、具体的には、AlN 等のセラミック材料や、バイレックス（登録商標）ガラス等の珪ホウ酸ガラス等が挙げられる。

## 【0044】

また、配線層 103 は、シリコン層 105 および絶縁膜 107 を貫通して設けられた導体ヴィア 109 を有する。これにより、配線層 103 の両面の電気的導通が確保される。導体ヴィア 109 の平面配置に特に制限はなく、半導体装置 100 の設計に応じて適宜選択することができる。たとえば、導体ヴィア 109 を正方格子状に配置したり、千鳥配置等の斜格子状に配置したりすることができる。

10

## 【0045】

第一の半導体素子 113 は、配線体 101 の配線層 103 の側にアンダーフィル樹脂 127 を介して接合されている。第一の半導体素子 113 中の導電部材（不図示）はアンダーフィル樹脂 127 中に埋設された電極 117 を介して導体ヴィア 109 にフリップチップ接続されている。また、配線体 101 において、第一の半導体素子 113 が設けられている側の面には、第一の半導体素子 113 の側壁を覆う絶縁樹脂 119 が設けられている。

20

## 【0046】

第一の半導体素子 113 および第二の半導体素子 111 の構成は、半導体装置 100 の設計に応じて適宜選択することができるが、たとえば、第一の半導体素子 113 をメモリLSIチップとし、第二の半導体素子 111 をロジックLSIチップとすることができる。

## 【0047】

封止樹脂である絶縁樹脂 119 の材料に特に制限はなく、半導体封止用の樹脂を適宜選択して用いることができる。たとえば、シリカやアルミナ等の無機充填剤を含むエポキシ樹脂とすることができます。

30

## 【0048】

導体スルーホール 121 は、絶縁樹脂 119 を貫通し、配線体 101 中の導電体に電気的に接続されている。導体スルーホール 121 の配線体 101 と反対側の面は絶縁樹脂 119 から露出しており、露出面に電極端子 123 が設けられている。導体スルーホール 121 は電極端子 123 を介して外部に電気的に接続されている。

## 【0049】

第二の半導体素子 111 は、配線体 101 の絶縁膜 107 の側にアンダーフィル樹脂 127 を介して接合されている。第二の半導体素子 111 中の導電部材（不図示）は、アンダーフィル樹脂 125 中に埋設された電極 115 を介して導体ヴィア 109 にフリップチップ接続されている。

40

## 【0050】

半導体装置 100 において、第一の半導体素子 113 と第二の半導体素子 111 とは、電極 117、配線層 103 中の導電体、導体ヴィア 109 および電極 115 を介して電気的に接続された構成となっている。なお、本実施形態および以降の他の実施形態において、電極 115 および電極 117 は、たとえばバンプとすることができます。

## 【0051】

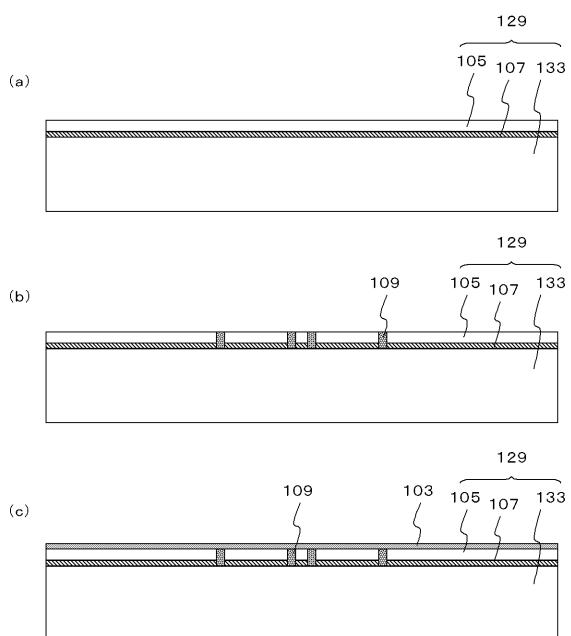

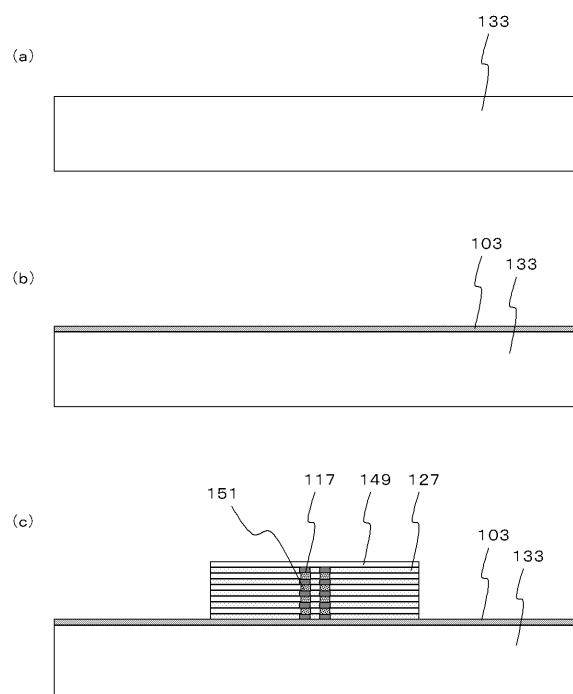

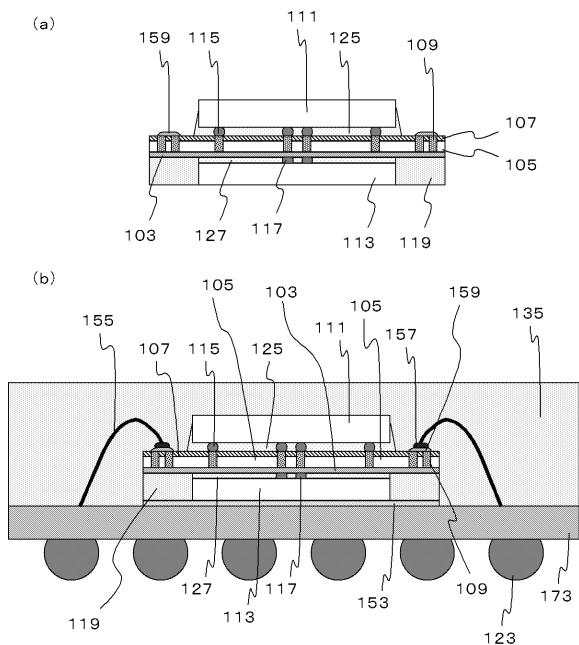

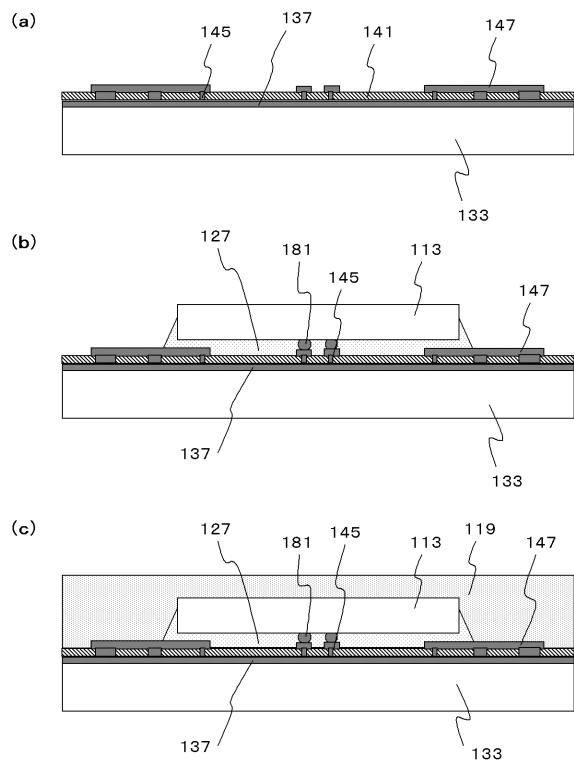

次に、図 1 に示した半導体装置 100 の製造方法を説明する。半導体装置 100 は、シリコン基板上で配線層 103 が形成され、配線層 103 上に前記第一の半導体素子 113 が接続され、第一の半導体素子 113 の側面および第一の半導体素子 113 の露出面が樹脂封止された後に、シリコン基板を除去することにより得られる。図 2 (a) ~ 図 2 (c)

50

)、図3(a)～図3(c)、および図4(a)～図4(c)は、半導体装置100の製造工程を示す断面図である。

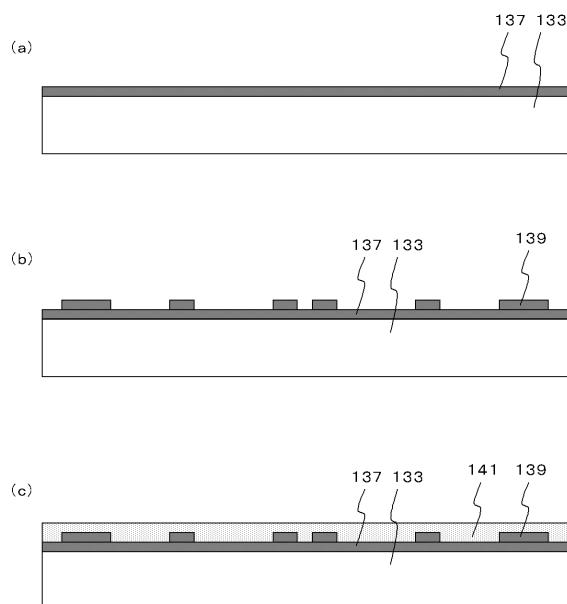

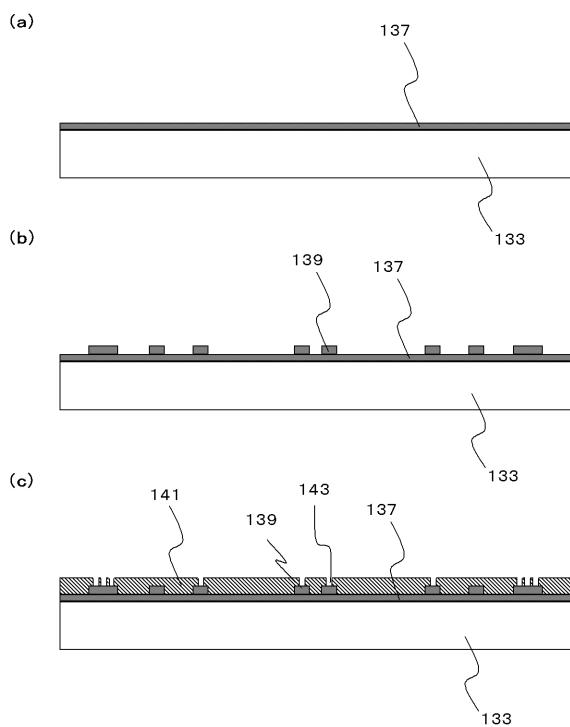

#### 【0052】

まず、図2(a)に示すように、ウェハ状態のシリコン基板133の上部に絶縁膜107を介してシリコン層105が形成された、SOI(シリコンオンインシュレータ)基板129を準備する。絶縁膜107は単層であってもよいし、多層であってもよい。

#### 【0053】

次に、SOI基板129の導体ヴィア109を設ける位置に、シリコン層105および絶縁膜107を貫通する開口部を形成する。そして、開口部が設けられたSOI基板129の表面に拡散防止膜を形成する。これにより、導体ヴィア109を構成する材料のSOI基板中への拡散を抑制することができる。そして、開口部を導電材料により埋め込むことにより、導体ヴィア109を形成する(図2(b))。導体ヴィア109は、SOI基板129において第二の半導体素子111および第一の半導体素子113が接合される領域に設けることができる。

#### 【0054】

導体ヴィア109の材料としては、たとえば、銅、アルミニウム、タンゲステン等の金属や多結晶シリコンなどを用いることができる。なお、導体ヴィア109が絶縁膜107を貫通せずに、シリコン層105から絶縁膜107中の所定の位置にわたって設けられた構成としてもよい。また、導体ヴィア109がシリコン層105を貫通し絶縁膜107の上部に接する構成であってもよい。

#### 【0055】

次に、SOI基板129の上部に配線層103を形成する(図2(c))。配線層103の作製方法は、第三または第七の実施形態で後述する方法とすることができる。また、シリコン層105上に絶縁膜を形成し、たとえばダマシン法により所定の形状の配線を所定の位置に配置してもよい。配線は、導体ヴィア109に電気的に接続される。配線の材料は、導体ヴィア109の材料と同じ材料としてもよいし、異なる導電材料としてもよい。配線層103は単層構造であっても多層構造であっても構わない。また、配線層103を形成する前に、シリコン層105上にトランジスタ等の能動素子やメモリ素子等の受動素子など、所定の素子を形成してもよい。

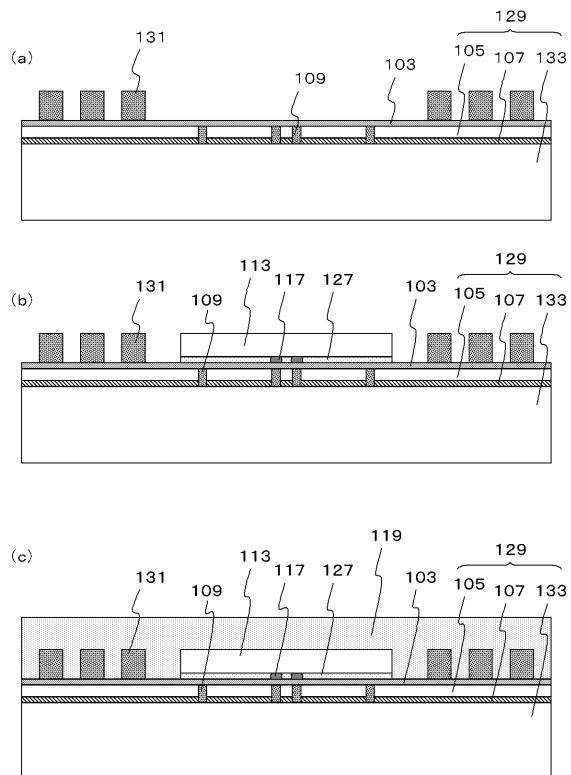

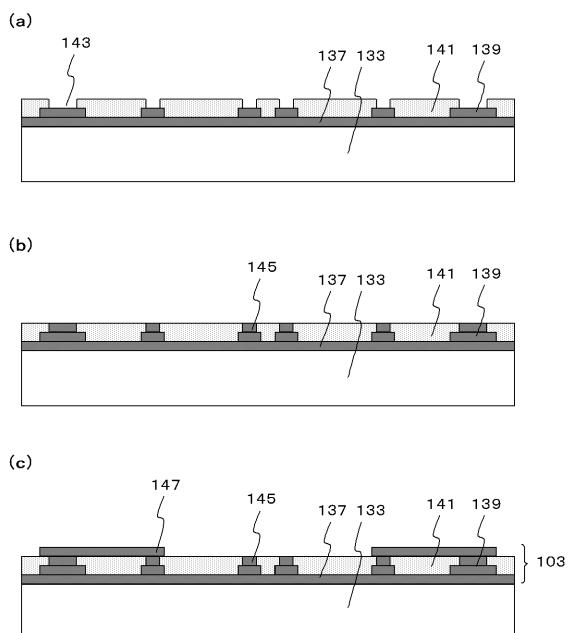

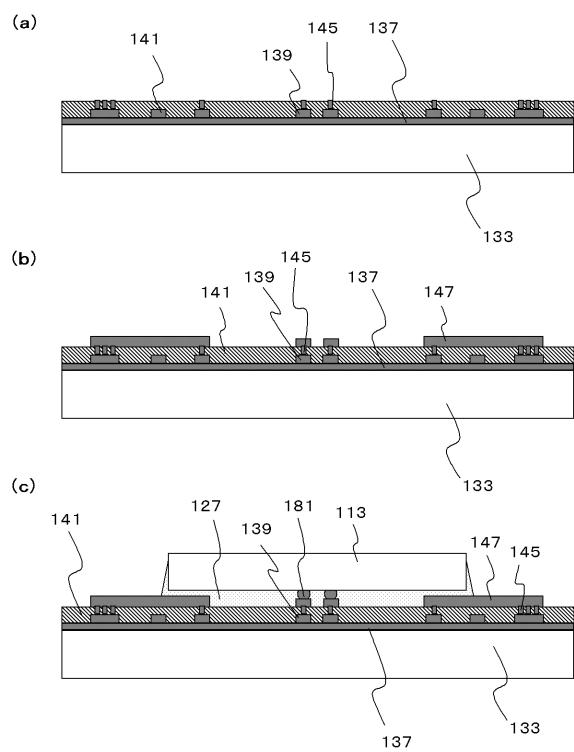

#### 【0056】

次に、配線層103上に、図1における導体スルーホール121となる導体ポスト131を形成する(図3(a))。導体ポスト131の材料は、たとえば銅または金などの金属とすることができます。また、導体ポスト131は、配線層103上に、導体ポスト131を設ける領域を開口部とするレジストパターンを設け、たとえばセミアディティブ法の無電解めっき法により、開口部中に金属膜を成長させることにより作製することができる。

#### 【0057】

次に、配線層103上に第一の半導体素子113を電気的に接続する。接続方法としては各種の方法を用いることが可能であるが、たとえば、第一の半導体素子113上にあらかじめ形成した電極117としてバンプ電極を形成しておき、電極117と配線層103中の配線とをバンプ接合することにより接続することができる。このとき、フリップチップ接合法を用いることができる。フリップチップ接合法を用いることにより、配線層103と第一の半導体素子113とを簡単な方法で確実に接続することができる。また、他の接続方法としては、たとえば、配線層103の表面と第一の半導体素子113の表面をプラズマ照射などの方法で活性化した状態で押圧接合する、活性化接合法などが挙げられる。接合後、第一の半導体素子113とSOI基板129との間にアンダーフィル樹脂127を充填する(図3(b))。

#### 【0058】

そして、トランスファーモールドなどの方法を用いて、配線層103の上面全面を絶縁性の絶縁樹脂119で封止する(図3(c))。これにより、第一の半導体素子113お

10

20

30

40

50

および導体ポスト 131 は絶縁樹脂 119 中に埋設される。封止方法としてはこの他にも絶縁樹脂シートを圧着する方法や、液状樹脂を塗布後、硬化させる方法など各種の方法から選択することができる。

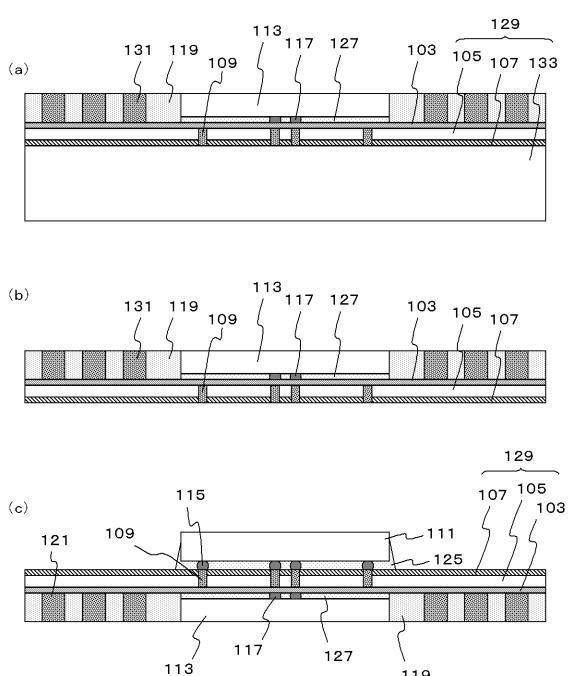

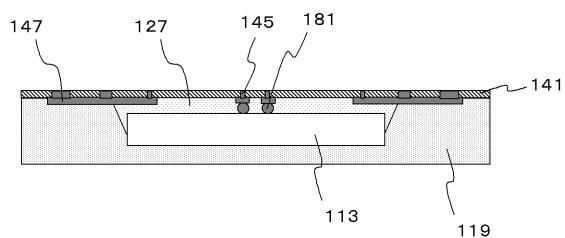

#### 【0059】

次に、絶縁樹脂 119 の形成面側の研削等により絶縁樹脂 119 を薄化して、第一の半導体素子 113 の上面および導体ポスト 131 の端部を露出させる(図4(a))。なお、この工程は、後述するシリコン基板 133 の除去工程(図4(b))の後に行うことができる。また、図3(c)を用いて前述した絶縁樹脂 119 の形成工程において絶縁樹脂 119 の膜厚をあらかじめ所定の厚さにコントロールすることも可能であり、その場合、導体ポスト 131 の露出工程の省略が可能となる。

10

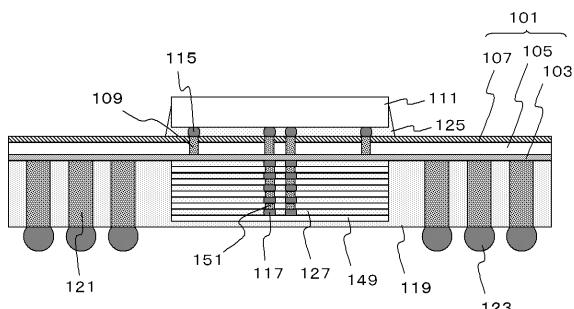

#### 【0060】

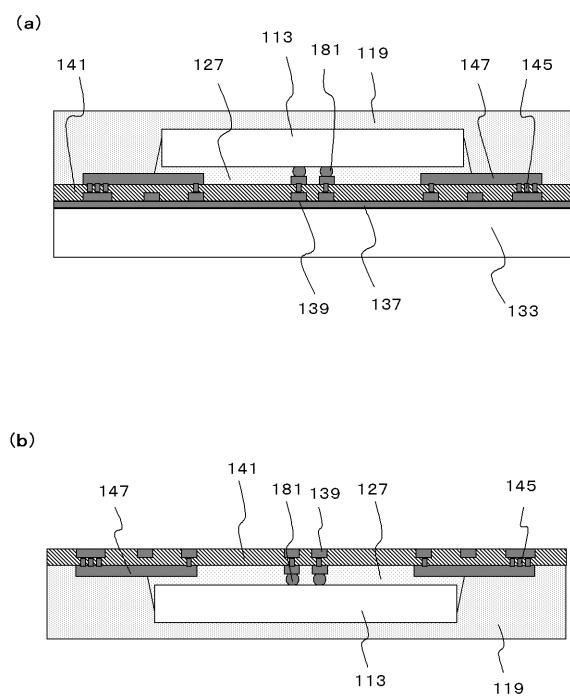

そして、第一の半導体素子 113 の接合面の裏面の側からシリコン基板 133 を除去する。このとき除去方法としては、機械研削、CMP、ケミカルエッティングなどを採用することができる。また、別の除去方法として、シリコン基板 133 と配線層 103 との界面に密着力の低い層をあらかじめ形成しておき、この介在層の部分から剥離させるなどの方法が挙げられる。さらに、絶縁膜 107 の一部や拡散防止膜(不図示)を除去し、導体ヴィア 109 の端面を露出させる(図4(b))。導体ヴィア 109 を露出させるプロセスに特に限定はなく、各種の方法が選択可能である。

#### 【0061】

次に、露出した導体ヴィア 109 に第二の半導体素子 111 を接続する。接続方法として、第一の半導体素子 113 の接続(図3(b))の方法を用いることができる。たとえば、第二の半導体素子 111 の表面に電極 115 を形成し、シリコン層 105 と導体ヴィア 109 とを接合することにより接続できる。接続後、第二の半導体素子 111 と SOI 基板 129 との間にアンダーフィル樹脂 127 を充填してもよい(図4(c))。

20

#### 【0062】

そして、導体ポスト 131 の露出面にはんだバンプなどの電極端子 123 を形成する。以上の工程により、図1に示した半導体装置 100 が製造可能される。以上のプロセスは初期的にはウェハすなわちシリコン基板 133 上に第二の半導体素子 111 および第一の半導体素子 113 がそれぞれ複数設けられた半導体装置の状態で実施されるが、絶縁樹脂 119 による封止工程以降、任意の位置で複数のチップに半導体装置間を分離することができる。また、前述したように、工程の順序としても、シリコン基板 133 除去と絶縁樹脂 119 の研削順序を逆にすることなどの変更が可能である。

30

#### 【0063】

次に、図1に示した半導体装置 100 の効果を説明する。

図1に示した半導体装置 100 において、配線体 101 は、絶縁膜 107、シリコン層 105 および配線層 103 がこの順に積層された構造になっている。そして、配線層 103 中の導電体およびこれに接続して設けられた導体ヴィア 109 により構成される貫通電極が配線体 101 を貫通した構成となっている。また、配線体 101 の両面に第一の半導体素子 113 および第二の半導体素子 111 が対向して接合されている。

#### 【0064】

40

支持層となるシリコン層 105 を設けることにより、熱膨張係数の相違による反りの発生、接合精度の低下や残留熱応力による接続信頼性の低下を抑制することができる。このため、高精度で信頼性の高い接続が可能となる。また、高密度で導体ヴィア 109 を配置した場合にも、確実に配線体 101 と第一の半導体素子 113 および第二の半導体素子 111 とを接続することができる。このため、配線体 101 を貫通する貫通電極構造の高密度配置が可能となる。なお、配線体 101 を貫通する貫通電極構造は、複数の導電体からなる構成とすることができます。

#### 【0065】

また、支持層としてシリコン層 105 を有する配線体 101 の両面に、熱膨張係数の等しいシリコンデバイスすなわち第二の半導体素子 111 および第一の半導体素子 113 が

50

接続される。このため、半導体装置 100 は構造の対称性に優れる。よって、半導体装置 100 は製造安定性に優れ、第一の半導体素子 113 と第二の半導体素子 111 とを確実に接続する構成となっている。

#### 【0066】

このように、半導体装置 100 では、配線体 101 の両面に設けられた第一の半導体素子 113 および第二の半導体素子 111 の間を高密度かつ優れた信頼性で接続することができる。半導体素子との接続信頼性の向上が可能なシリコン層 105 を有する配線体 101 を用いることで、高い配線密度で複数のチップや大規模なチップ間を接続することが可能となる。

#### 【0067】

たとえば、半導体装置 100 は、たとえば 50 μm 以下の電極ピッチ間隔すなわち導体ヴィア 109 の最小間隔がたとえば 50 μm 以下である構成にも対応可能な構成となっている。また、高密度な配線体 101 を介した接続構造が実現されるため、チップサイズや電極位置、外部端子への配線接続に関する設計に対して高い自由度を提供し、発熱の大きいロジック LSI チップを第二の半導体素子 111 とすれば、ロジック LSI チップに対してヒートスプレッダなどの放熱機構を附加することも可能になる。

10

#### 【0068】

また、半導体装置 100において、平板状の配線体 101 の両面に接続された複数の半導体素子が配線体 101 を貫通する導体ヴィア 109 および導体ヴィア 109 に接続している配線層 103 中の配線を介して電気的に接続される。第一の半導体素子 113 および第二の半導体素子 111 が、シリコン層 105 と絶縁膜 107 とを貫通する導体スルーホールである導体ヴィア 109 および配線層 103 中の配線を介して電気的に接続されているため、第一の半導体素子 113 と第二の半導体素子 111 との接続距離を短くすることができる。このため、第一の半導体素子 113 と第二の半導体素子 111 との間の通信処理速度を増加させることができる。

20

#### 【0069】

また、複数の LSI 間を微細な配線で高密度に接続することにより、電気特性に優れた構成となっている。また、従来のチップオンチップ (COG) 構造の半導体装置などのマルチチップパッケージに比較して高い設計自由度を有する。これに伴い、放熱性に優れた構造も容易に実現可能である。さらには、2次実装信頼性も高い BGA 型半導体装置とすることができる。さらにこのようにして高精度で接合された第一の半導体素子 113 を含む配線体 101 の片面を樹脂封止した後にシリコン基板 133 を取り除き、反対面に第二の半導体素子 111 を接続することにより、半導体素子間を高密度に電気的に接続することができる。

30

#### 【0070】

また、半導体装置 100 では、半導体素子間を高密度に電気的に接続することができるため、バス幅の拡大に相当する効果が得られる。このため、高速化と低消費電力化の両立が可能となる。たとえば、同一の処理速度でのクロック周波数の低減が可能となる。また、同一のクロック周波数における処理速度を増加させることができる。

40

#### 【0071】

したがって、たとえば、半導体装置 100 は、大容量メモリとシステム LSI とのチップオンチップ接続に適用することができる。このとき、バンプ接続等の電極接続の多ピン化および狭ピッチ化が可能となる。また、配線体 101 は、ロジック回路が形成された半導体チップと DRAM 等のメモリ素子が設けられたメモリチップとの間に設けられ、これらを接続する接続部材として好適に用いることができる。

#### 【0072】

また、半導体装置 100において、配線体 101 の少なくとも片面に絶縁樹脂 119 からなる層が形成されている。具体的には、配線体 101 の配線層 103 の側の面には絶縁樹脂 119 の層が形成されている。また、絶縁樹脂 119 を貫通し、配線層 103 中の配線に接続された導体スルーホール 121 の絶縁樹脂 119 からの露出面に電極端子 123

50

が形成されている。樹脂貫通スルーホールである導体スルーホール 121 を用いた構造とすることにより、熱応力緩和機能により優れた二次実装信頼性が得られる。

#### 【0073】

また、半導体装置 100において、平板状の配線体 101は、シリコン基板 133 上で形成される。半導体素子間を電気的に接続するための配線体 101を剛性の高いシリコン基板 133 上で形成するため、配線パターンの微細化が可能となる。

#### 【0074】

また、半導体装置 100は、シリコン基板 133 上に配線体 101が設けられ、配線体 101上に第一の半導体素子 113を接合した後シリコン基板 133を除去することにより得られる。シリコン基板 133を用いることにより、第一の半導体素子 113と配線体 101中の導電部材との接続プロセスにおける熱膨張係数の不一致による接続安定性の低下を抑制することができる。このため、非常に高精度で信頼性の高い接合が実現される。

#### 【0075】

また、半導体装置 100は、シリコン基板 133を取り除いた後、反対面にも LSI すなわち第二の半導体素子 111を接続することにより作製される。このように、半導体装置 100は、複数の LSI 間を微細な配線で高密度にかつ安定に接続された構成となっているため、従来のシステムインパッケージ (SiP) で実現できなかった良好な動作特性を発揮することができる。

#### 【0076】

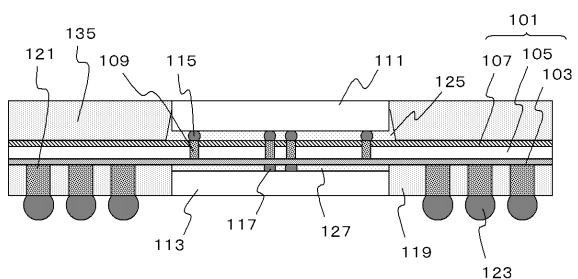

なお、図 1 に示した半導体装置 100および以降の実施形態に記載の半導体装置において、第一の半導体素子 113が絶縁樹脂 119に埋設されている構成とすることもできる。図 5 は、第一の半導体素子 113が絶縁樹脂 119中に埋設された構成の半導体装置を模式的に示す断面図である。

#### 【0077】

また、図 1 に示した半導体装置 100および以降の実施形態に記載のシリコン層 105を有する半導体装置において、支持層であるシリコン層 105にトランジスタ等の能動素子が形成されていてもよい。こうすれば、配線体 101をさらに高機能化することができる。

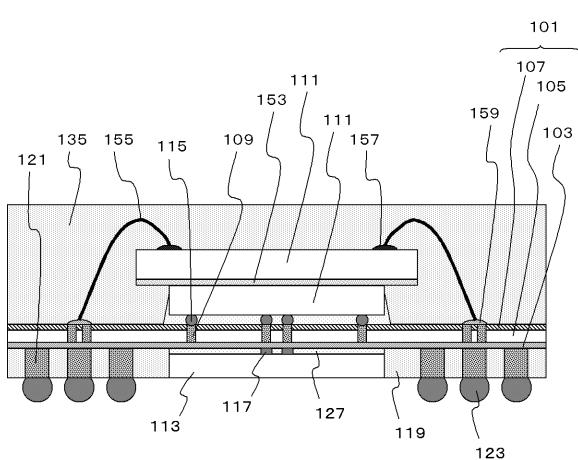

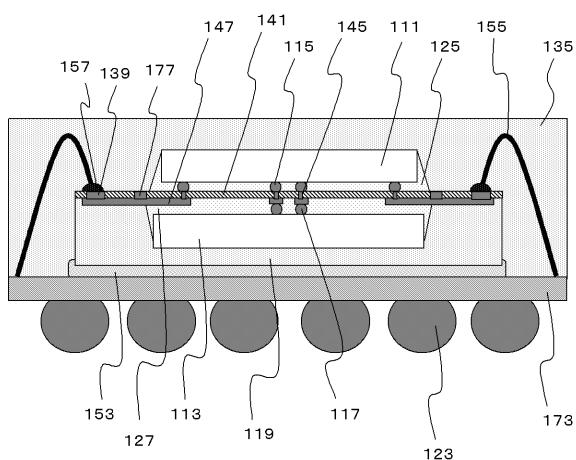

#### 【0078】

また、半導体装置 100および以降の実施形態に記載の半導体装置において、配線体 101の第二の半導体素子 111の接合された側の面にも絶縁樹脂が設けられていてもよい。図 6 は、第二の半導体素子 111の側壁および絶縁膜 107の表面を覆う絶縁樹脂 135が設けられているフリップチップ型の半導体装置の構成を模式的に示す断面図である。配線体 101の両面が絶縁樹脂 119および絶縁樹脂 135により封止された構成とすることにより、半導体装置の強度を向上させることができる。また、配線体 101の両面の構成の対称性を高めることができるため、製造安定性を向上させることができる。

#### 【0079】

以下の実施形態においては、第一の実施形態と異なる部分を中心に説明する。

#### 【0080】

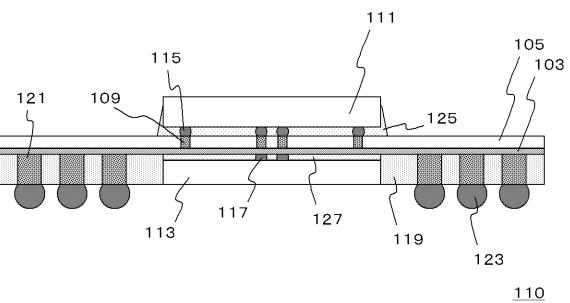

##### (第二の実施形態)

第一の実施形態に記載の半導体装置 100(図 1)は、配線層 103、シリコン層 105、絶縁膜 107がこの順に積層された構成の配線体 101を備えていたが、配線体 101は、配線層 103およびシリコン層 105の積層体からなる構成としてもよい。図 7 は、本実施形態に係る半導体装置 110の構成を模式的に示す断面図である。

#### 【0081】

図 7 に示した半導体装置 110の基本構成は第一の実施形態に記載の半導体装置 100(図 1)と同様であるが、絶縁膜 107が設けられておらず、第二の半導体素子 111は配線体 101のシリコン層 105の表面に電極 115およびアンダーフィル樹脂 127を介して接続されている点が異なる。また、半導体装置 110において、導体ヴィア 109は、シリコン層 105を貫通し配線層 103中の配線に電気的に接続されている。

10

20

30

40

50

**【0082】**

半導体装置110は、図2(b)、図2(c)、図3(a)～図3(c)、および図4(a)～図4(c)を用いて前述した工程を用いて製造することができる。まず、シリコン基板133に導体ヴィア109を形成し、導体ヴィア109の形成面に配線層103を形成する。そして、第一の実施形態の場合と同様にして第一の半導体素子113および第二の半導体素子111を配線体101に接合する。なお、半導体装置110の製造においては、シリコン基板133を裏面から薄化し、除去せずに所定の厚さのシリコン基板133をシリコン層105として残存させる。

**【0083】**

図7に示した半導体装置110においても、配線層103および支持層であるシリコン層105がこの順に積層された構成の配線体101を備えているため、第一の半導体素子113および第二の半導体素子111の接合時の熱膨張率差が小さい構成となっている。このため、これらの接続信頼性を充分に確保するとともに、接続する導体ヴィア109の間隔を充分に小さくすることができる。

**【0084】**

また、半導体装置110においては、バルクのシリコン基板133が利用可能であり、シリコン基板133の研削厚をコントロールすることにより所定の厚さのシリコン層105を有する配線体101を設けることができる。このため、SOI基板129を用いる必要がなく、装置構成を簡素化することができる。

**【0085】**

なお、半導体装置110においては、導体ヴィア109の周囲におけるシリコン層105の表面が絶縁される。これにより、第二の半導体素子111の電極間の絶縁性が確保される。図7では、絶縁性のアンダーフィル樹脂125をシリコン層105と第二の半導体素子111との間に埋設することにより、導体ヴィア109の周囲が絶縁された構造となっている。

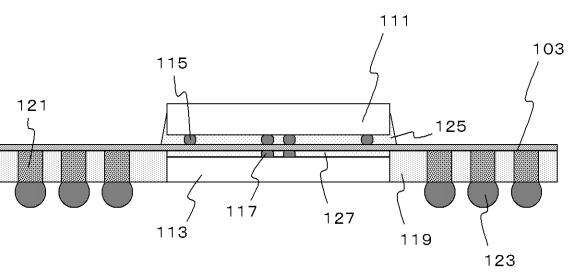

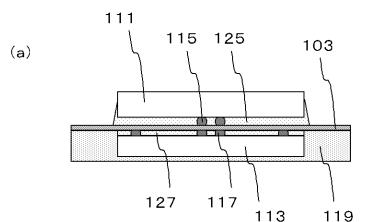

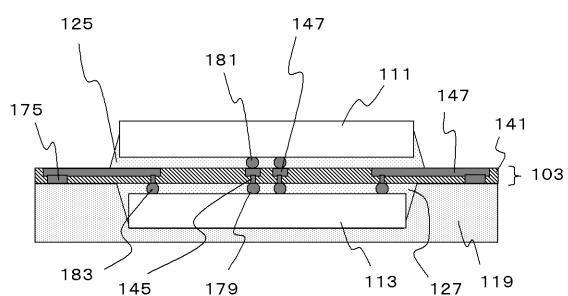

**【0086】****(第三の実施形態)**

以上の実施形態に記載の半導体装置において、配線体101が配線層103のみから構成されていてもよい。図8は、本実施形態に係る半導体装置120の構成を模式的に示す断面図である。

**【0087】**

図8に示した半導体装置120の基本構成は第一の実施形態に記載の半導体装置100(図1)と同様であるが、配線体101が配線層103のみからなり、第一の半導体素子113および第二の半導体素子111が配線層103の異なる面に対向して設けられている点が異なる。また、第二の半導体素子111が配線層103の表面に電極115およびアンダーフィル樹脂127を介して接続されている点が異なる。

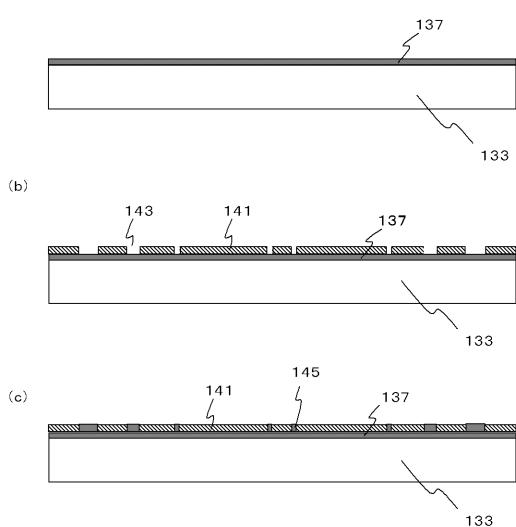

**【0088】**

半導体装置120において、配線層103からなる配線体101は、たとえば以下の方法により製造することができる。図9(a)～図9(c)および図10(a)～図10(c)は、配線層103の作製工程を模式的に示す断面図である。

**【0089】**

まず、シリコン基板133の表面に、スパッタ法などを用いて金属のシード層137を形成する(図9(a))。シード層137は、たとえばNiとすることができます。次に、シード層137上に配線形成位置を露出させるレジストパターンを形成し、シード層137の露出部を起点として所定のパターンの接続電極139を形成する(図9(b))。接続電極139は、後述する絶縁樹脂膜141の下面側の電極である。接続電極139は、外部引き出し電極として用いることができる。接続電極139は、たとえば電解めっき法により形成することができる。

**【0090】**

接続電極139の材料は、Cu、Al、Au、Ni、W等の金属や合金、メタルシリサ

10

20

30

40

50

イド、またはポリシリコンなどの各種導電性材料で形成することができ、単層構造の他、半田の拡散防止層や電極強度の補強層を含む積層構造とすることもできる。積層構造の電極としては、下端側から Au、Ni、Cu がこの順で積層された電極 (Au / Ni / Cu 電極)、下端側から Ni、Au、Ni、Cu がこの順で積層された電極 (Ni / Au / Ni / Cu 電極)、この Ni / Au / Ni / Cu 電極から最下端層の Ni 層が除去された Au / Ni / Cu 電極、下端側から Cu、Ag、Cu がこの順で積層された電極 (Cu / Ag / Cu 電極) を挙げることができる。上記電極において、中間の Ni 層は半田の拡散防止層として機能する。また、Cu / Ag / Cu 電極において、Ag 層は電極の強度向上する補強層として機能する。

## 【0091】

10

次に、接続電極 139 の形成面の全面に絶縁樹脂膜 141 を設け、接続電極 139 を絶縁樹脂で埋め込む (図 9 (c))。絶縁樹脂膜 141 は、たとえばラミネートフィルム状の絶縁樹脂シートを接合する方法や、スピンドルコート法等により形成することができる。そして、絶縁樹脂膜 141 の所定の位置にレーザー光を照射し、レーザーヴィアすなわち開口部 143 を設ける (図 10 (a))。また、絶縁樹脂膜 141 に感光性樹脂を用い、フォトリソグラフィー法により開口部 143 を形成してもよい。

## 【0092】

その後、開口部 143 を Cu 等の所定の金属膜で埋めこみ、ヴィアプラグ 145 とする (図 10 (b))。そして、ヴィアプラグ 145 に接続し、所定のパターンを有する配線 147 を絶縁樹脂膜 141 上に形成する (図 10 (c))。配線 147 の材料は、たとえば Cu 等の金属とする。そして、配線 147 の表面に、上層から Au / Ni からなるめっき層 (不図示) を形成する。以上の工程により、シリコン基板 133 上に多層の配線層 103 が形成される。

20

## 【0093】

なお、ヴィアプラグ 145 の平面配置に特に制限はなく、半導体装置 120 の設計に応じて適宜選択することができる。たとえば、ヴィアプラグ 145 を正方格子状に配置したり、千鳥配置等の斜格子状に配置したりすることができる。

## 【0094】

30

図 8 に示した半導体装置 120 は、以上的方法でシリコン基板 133 上に配線層 103 を作製した後、第二の実施形態に記載の半導体装置 110 (図 7) の製造工程を用いて製造することができる。ここで、第二の実施形態においては配線体 101 がシリコン層 105 を有する構成であったため、シリコン基板 133 を薄化したが、本実施形態に係る半導体装置 120 はシリコン層 105 を有しない構成であるため、第一の半導体素子 113 を接合した後、第一の実施形態の場合と同様にシリコン基板 133 を除去する。そして、配線体 101 に第二の半導体素子 111 を接合する

## 【0095】

こうして得られる半導体装置 120 (図 8、図 10 (c))において、接続電極 139 は、絶縁樹脂膜 141 の第二の半導体素子 111 の側に設けられる。接続電極 139 は、第二の半導体素子 111 を第一の半導体素子 113 に接続するための素子接続電極と、第二の半導体素子 111 を外部に接続するための外部接続電極とを含む。接続電極 139 がこれらのいずれである場合においても、接続電極 139 の側面全面が絶縁樹脂膜 141 中に埋設されるとともに、接続電極 139 の絶縁樹脂 119 と反対側の面の全体が絶縁樹脂膜 141 から露出し、この面では接続電極 139 が絶縁樹脂膜 141 に接していない構成となっている。

40

## 【0096】

これにより、接続電極 139 の高密度配置が可能となる。また、接続電極 139 の側面外周を確実に絶縁することができる。また、配線層 103 の第二の半導体素子 111 の側の面を平坦面としつつ、電極端子 123 を所定の領域に確実に設け、電極端子 123 の周囲を確実に絶縁することが可能となる。

## 【0097】

50

また、接続電極 139 を外部接続電極とする場合、従来のワイヤボンディング形式の接続に対し、高密度かつ短い接続距離での接続が可能となる。

#### 【0098】

なお、半導体装置 120において、接続電極 139 は、複数の導電部材が接合されて構成されていてもよい。また、接続電極 139 の絶縁樹脂膜 141 からの露出面は平坦面でなくともよい。たとえば、接続電極 139 の露出面が絶縁樹脂膜 141 の表面から凸状にはりだした曲面であってもよい。また、接続電極 139 は、絶縁樹脂膜 141 からの露出面にバンプ電極が接合されていてもよい。

#### 【0099】

接続電極 139 の絶縁樹脂膜 141 からの露出面を曲面とすることにより、接続電極 139 を他の接続部材に接合するのに充分な高さが確保される。こうした構成は、たとえば接続電極 139 の露出面に、無電解めっき法などにより曲面状の電極を形成することにより得られる。

#### 【0100】

また、図 8 に示した半導体装置 120 は、バルクのシリコン基板 133 を利用して製造することが可能である。このため、低成本で高密度な配線構造により第一の半導体素子 113 と第二の半導体素子 111 とを接続することができる。また、配線体 101 が配線層 103 からなるため、簡素な構成である。このため、製造工程を簡素化し、製造コストの低減が可能である。

#### 【0101】

第一の半導体素子 113 および第二の半導体素子 111 は、線膨張係数が 0.5 ppm / 以上 5 ppm / 以下の基板を有する構成とした場合、シリコン基板 133 との熱膨張係数の差を小さくすることができるため、配線体 101 と第一の半導体素子 113 および第二の半導体素子 111 との接続信頼性を向上させることができる。また、第一の半導体素子 113 および第二の半導体素子 111 の基板の種類に応じて、バルクのシリコン基板 133 に代えて、これらの半導体素子の基板との線膨張係数差の小さい材料を用いて半導体装置 120 を製造してもよい。

#### 【0102】

また、第一の半導体素子 113 および第二の半導体素子 111 が、シリコン基板を有する素子であってもよく、この場合、バルクのシリコン基板 133 を用いることによる効果が顕著に発揮される。このため、第一の半導体素子 113 と第二の半導体素子 111 とを接続する導体ヴィア 109 を高密度で設け、これらの半導体素子間を高密度で接続することが可能となる。

#### 【0103】

また、配線層 103 中の接続電極 139 およびヴィアプラグ 145 の側面は絶縁樹脂膜 141 に覆われているため、接続電極 139 の端面に電極 115 または電極 117 として半田バンプを接続する場合、半田の流動による接続不良を抑制することができる。

#### 【0104】

また、半導体装置 120 は、配線体 101 の両面に半導体素子が接合されるため、対称性が高い構成である。このため、第二の半導体素子 111 と第一の半導体素子 113 との接続信頼性を充分に確保することができる。

#### 【0105】

また、第一の半導体素子 113 の配線層 103 の側の面と、第二の半導体素子 111 の配線層 103 の側の面とが、配線層 103 の面に略垂直に一直線に接続されている。このため、接続距離を短縮し、安定的な接続が確保された構成となっている。なお、配線体 101 の内部で水平方向に延在する配線を介さずに接続されれば、半導体素子間の接続が完全に垂直でなくてもよい。また、本実施形態において、配線体 101 の面に垂直方向に設けられた導電部材すなわちヴィアプラグ 145 の最小間隔をたとえば 50 μm 以下と高密度化することができる。

#### 【0106】

10

20

30

40

50

本実施形態において、配線層 103 からなる配線体 101 を有する半導体装置は、以下の構成としてもよい。図 31 は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図 31 に示した半導体装置 150 の基本構成は図 8 に示した半導体装置 120 と同様であるが、絶縁樹脂 119 中を貫通する導体スルーホール 121 を有さず、配線体 101 の第二の半導体素子 111 の側の面に接して設けられ、配線体 101 中の配線に接続した電極端子 123 を有する点が異なる。

#### 【0107】

半導体装置 150 は、図 8 に示した半導体装置 120 と同様に、平板状の絶縁樹脂膜 141 およびこれを貫通する導電体を有するため、第一の半導体素子 113 と第二の半導体素子 111 とを高密度で確実に接続することができる。また、絶縁樹脂 119 中に導体スルーホール 121 を設ける工程を設けることなく製造可能であるため、製造プロセスを簡素化可能な構成となっている。

#### 【0108】

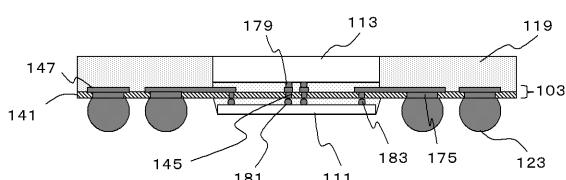

図 32 および図 33 は、図 31 に示した半導体装置 150 の配線層 103 の構成を詳細に示した断面図である。

#### 【0109】

図 32 に示した半導体装置では、配線層 103 が、ヴィアプラグ 145 およびパッド 175 が設けられた層と配線 147 が設けられた層との二層構造となっている場合を例示している。なお、ヴィアプラグ 145 およびパッド 175 が設けられた層には、ヴィアプラグ 145 およびパッド 175 以外の所定の配線が形成されていてもよい。

#### 【0110】

図 32 において、電極端子 123 は、配線 147 に接合されている。また、配線 147 は、所定のヴィアプラグ 145 またはパッド 175 に接合されている

#### 【0111】

ヴィアプラグ 145 およびパッド 175 は、絶縁樹脂膜 141 の第二の半導体素子 111 に設けられた接続電極である。これらは、前述した図 10 (c) における接続電極 139 に相当する。これらの接続電極の側面全面が絶縁樹脂膜 141 中に埋設されるとともに、接続電極の絶縁樹脂 119 と反対側の面が全面絶縁樹脂膜 141 から露出し、この面では接続電極が絶縁樹脂膜 141 に接していない構成となっている。これにより、配線層 103 を平坦面としつつ、電極端子 123 を所定の領域に選択的に設けることが可能となる。

#### 【0112】

なお、図 32 において、ヴィアプラグ 145 は第二の半導体素子 111 との素子接続電極であり、パッド 175 は電極端子 123 に接続する外部引き出しパッド、すなわち外部接続電極である。

#### 【0113】

配線 147 は、絶縁樹脂膜 141 第一の半導体素子 113 の接続面上に設けられている。配線 147 の側面および絶縁樹脂 119 の側の面は、絶縁樹脂膜 141 に埋設されておらず、絶縁樹脂膜 141 から露出している。また、露出部分は絶縁樹脂 119 中に埋設されている。これにより、配線層 103 の強度が充分に確保されている。

#### 【0114】

なお、図 32 において、第一の半導体素子 113 をメモリチップとし、第二の半導体素子 111 をロジックチップとしてもよい。このとき、図 31 における電極 115 として、第二の半導体素子 111 を第一の半導体素子 113 に接続させるメモリ通信用電極 179 および第二の半導体素子 111 を電極端子 123 に接続させる外部入出力用電極 183 を設けることができる。また、図 31 における電極 117 として、第一の半導体素子 113 を第二の半導体素子 111 に接続させるメモリ電極 181 を設けることができる。

#### 【0115】

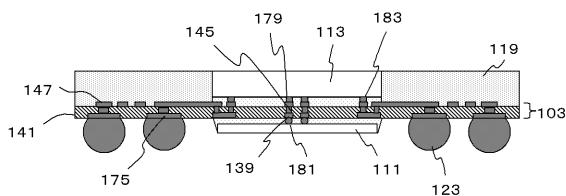

また、図 33 に示した半導体装置の基本構成は図 32 と同様であるが、図 32 と異なり、ヴィアプラグ 145 とパッド 175 とが異なる層に設けられている。このため、パッド

10

20

30

40

50

175の層すなわち接続電極139の層、ヴィアプラグ145の層、および配線147の層がこの順に積層された配線層103は、図32よりも一層多い三層構造となっている。この構成では、接続電極139を有する層が一つの面が絶縁樹脂膜141から露出した接続電極の層となっている。接続電極139の一部は第二の半導体素子111に接続する素子接続電極であり、他の一部は電極端子123に接続するパッド175である。

#### 【0116】

また、図33において、第二の半導体素子111をメモリチップとし、第一の半導体素子113をロジックチップとしてもよい。このとき、図32の場合とは逆に、図31の電極115としてメモリ電極181を設け、図31の電極117としてメモリ通信用電極179および外部入出力用電極183を設けることができる。

10

#### 【0117】

なお、図31に示した半導体装置150において、配線層103の構成および積層数は図32および図33に示した態様に限られず、装置構成に応じて適宜設定することができる。また、図32および図33に示した半導体装置における配線層103は、たとえば第七の実施形態にて後述する方法により製造することができる。

#### 【0118】

さらに、本実施形態に係る半導体装置は、他の半導体装置と積層接続して用いることもできる。図34および図35は、こうした半導体装置の構成を模式的に示す断面図である。

#### 【0119】

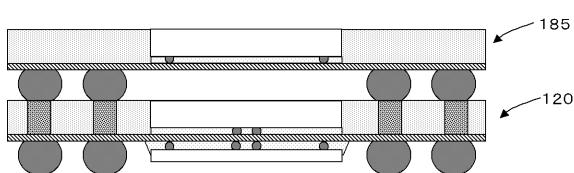

図34は、図8に示した半導体装置120を他の半導体装置185と接続した構成を示す図である。半導体装置120と半導体装置185とは、半導体装置185に設けられた電極端子および半導体装置120に設けられた導体スルーホール121を介して接続されている。

20

#### 【0120】

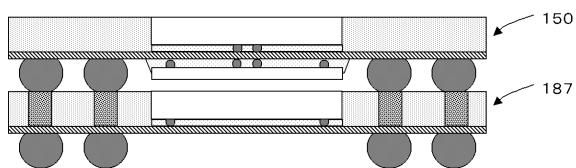

また、図35は、図31に示した半導体装置150を他の半導体装置187と接続した構成を示す図である。半導体装置150と半導体装置187とは、半導体装置150に設けられた電極端子123および半導体装置187に設けられた導体スルーホールを介して接続されている。

#### 【0121】

30

なお、本実施形態において、配線層103からなる配線体101の構成を第七の実施形態において後述する構成としてもよい。また、第七の実施形態に記載の半導体装置に本実施形態の構成を適用することもできる。

#### 【0122】

##### (第四の実施形態)

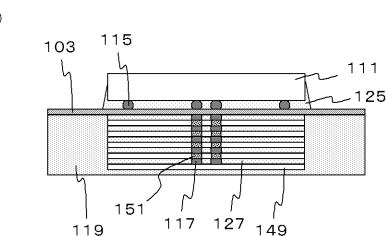

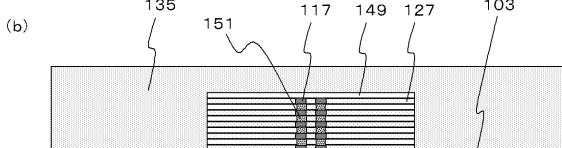

第一の実施形態に記載の半導体装置100において、配線体101の配線層103の側に接合された第一の半導体素子113が、複数の半導体素子の積層体であってもよい。図11は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図11に示した半導体装置の基本構成は第一の実施形態に記載の半導体装置100(図1)と同様であるが、第一の半導体素子113に代えて複数の半導体素子149が面の法線に沿って積層された構成である点が異なる。

40

#### 【0123】

図11に示した半導体装置において、配線体101の配線層103の面に、アンダーフィル樹脂127、半導体素子149、アンダーフィル樹脂127、半導体素子149、・・・、アンダーフィル樹脂127、半導体素子149が繰り返し設けられた構成によって複数の半導体素子149が積層されている。それぞれの半導体素子149には、当該半導体素子149を貫通する導体スルーホール151が設けられている。また、それぞれのアンダーフィル樹脂127には隣接する二つの半導体素子149間を接続する電極117が設けられている。

#### 【0124】

50

図11に示した半導体装置は、絶縁樹脂119の形成面側に複数の積層された半導体素子149が接続され、積層された半導体素子149間が、半導体素子149を貫通する導体スルーホール151を介して電気的に接続されている構成になっている。具体的には、複数の半導体素子149は、配線層103に接続する電極117、導体スルーホール151、電極117、導体スルーホール151、・・・、電極117という電極117と導体スルーホール151の繰り返し構造により配線体101に電気的に接続される。電極117と導体スルーホール151との繰り返し構造は、配線体101の表面に対する法線方向に略一直線上に形成されている。このため、図11に示した半導体装置は、半導体素子149間の接続距離が短く、接続信頼性に優れた構成となっている。

## 【0125】

10

また、図11では、配線層103の側に半導体素子149の積層体が配置されたが、配線体101の絶縁膜107の側の面に接続される第二の半導体素子111が複数の半導体素子の積層構造を有していてもよい。図12は、こうした半導体素子の構成を模式的に示す断面図である。図12に示した半導体装置の基本構成は第一の実施形態に記載の半導体装置100(図1)と同様であるが、第二の半導体素子111に代えて複数の半導体素子149が面の法線に沿って積層された構成である点が異なる。

## 【0126】

図12に示した半導体装置において、配線体101の絶縁膜107の面に、アンダーフィル樹脂125、半導体素子149、アンダーフィル樹脂125、半導体素子149、・・・、アンダーフィル樹脂125、半導体素子149が繰り返し設けられた構成によって複数の半導体素子149が積層されている。それぞれの半導体素子149には、当該半導体素子149を貫通する導体スルーホール151が設けられている。また、それぞれのアンダーフィル樹脂125には隣接する二つの半導体素子149を接続する電極115が設けられている。

20

## 【0127】

また、複数の半導体素子149は、絶縁膜107に接続する電極115、導体スルーホール151、電極115、導体スルーホール151、・・・、電極115という電極115と導体スルーホール151の繰り返し構造により配線体101に電気的に接続される。電極115と導体スルーホール151との繰り返し構造は、配線体101の表面に対する法線方向に略一直線上に形成されている。このため、図12に示した半導体装置も、図11に示した半導体素子の場合と同様に、半導体素子149間の接続距離が短く、接続信頼性に優れた構成となっている。

30

## 【0128】

なお、第一の半導体素子113または第二の半導体素子111が複数の半導体素子149の積層体からなる構成は、第二および第三の実施形態に記載の配線体101の構成に適用することもできる。

## 【0129】

40

また、本実施形態および積層された半導体素子149を有する他の実施形態の半導体装置において、積層された半導体素子149は、積層メモリモジュールとすることができます。これにより、メモリ容量を増加させつつ、ロジック部等を有する第二の半導体素子111との良好な電気的接続を得ることができる。

## 【0130】

## (第五の実施形態)

以上の実施形態に記載の半導体装置において、配線体101の一つの面に複数の半導体素子が平面配置されていてもよい。以下、第四の実施形態に記載の半導体装置(図11)の場合を例に説明する。図13は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。

## 【0131】

図13に示した半導体装置の基本構成は図11に示した半導体装置の構成と同様に、配線体101の絶縁樹脂119形成面側、すなわち配線層103側の面に、複数の積層され

50

た半導体素子 149 が接続され、積層された半導体素子 149 間が、半導体素子 149 を貫通する導体スルーホール 151 および電極 117 を介して電気的に接続されている。また、図 13 に示した半導体装置では、図 11 に示した半導体装置と異なり、配線体 101 の絶縁樹脂 119 形成面に対向する面、すなわち絶縁膜 107 側の面に、複数の第二の半導体素子 111 が配設されている点が異なる。

#### 【0132】

図 13 に示した半導体装置においては、複数の第二の半導体素子 111 が同一平面に配置されて、これらが電極 117 および導体ヴィア 109 を介して配線層 103 に接続する構成となっている。このため、複数の第二の半導体素子 111 と配線層 103 との接続距離をそろえ、これらを短縮することができる。よって、複数の第二の半導体素子 111 と半導体素子 149 との接続信頼性に優れた構成となっている。また、シリコン層 105 に形成する導体ヴィア 109 を高密度化することが可能であるため、第二の半導体素子 111 を高密度で確実に配線層 103 に接続することができる。10

#### 【0133】

##### (第六の実施形態)

以上の実施形態に記載の半導体装置において、配線体 101 中に設けられている導体ヴィア 109 を導体ワイヤとの接続部材として利用することもできる。また、配線体 101 の絶縁樹脂 119 形成面と対向する面に接着材により積層された複数の半導体素子が接続され、そのうち少なくとも 1 つの半導体素子が、ワイヤを介して、配線体 101 に電気的に接続された構成とすることができる。図 14 は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。20

#### 【0134】

図 14 に示した半導体装置の基本構成は第一の実施形態に記載の半導体装置（図 6）と同様であるが、第一の半導体素子 113 および第二の半導体素子 111 が設けられていない領域においても配線体 101 のシリコン層 105 および絶縁膜 107 を貫通する導体ヴィア 109 が設けられている点が異なる。

#### 【0135】

また、図 14 に示した半導体装置においては、配線体 101 の絶縁樹脂 119 形成面と対向する面すなわち絶縁膜 107 の側の面に、接着剤 153 により積層された複数の第二の半導体素子 111 が接続されている。そして、少なくとも 1 つの第二の半導体素子 111 が、配線体 101 のシリコン層 105 と絶縁膜 107 を貫通する導体ヴィア 109 に接続して形成された導体パッド 159 に、導体パッド 157 および導体からなるワイヤ 155 を介して接続された構成となっている。導体パッド 157 は、たとえば無電解めっき法により形成することができる。30

#### 【0136】

本実施形態では、導体ヴィア 109 を第一の半導体素子 113 および第二の半導体素子 111 の接合領域以外の絶縁樹脂 119 および絶縁樹脂 135 に封止された領域にも設けることにより、第二の半導体素子 111 とのワイヤボンディングに好適に利用することができる。このため、第二の半導体素子 111 と配線体 101 との電気的接続の設計の自由度の大きい構成となっている。40

#### 【0137】

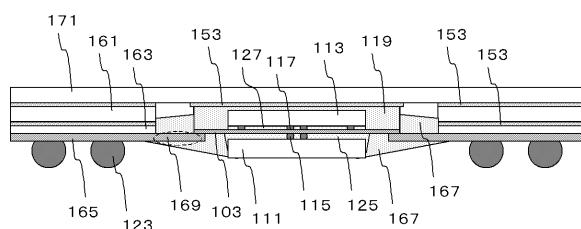

##### (第七の実施形態)

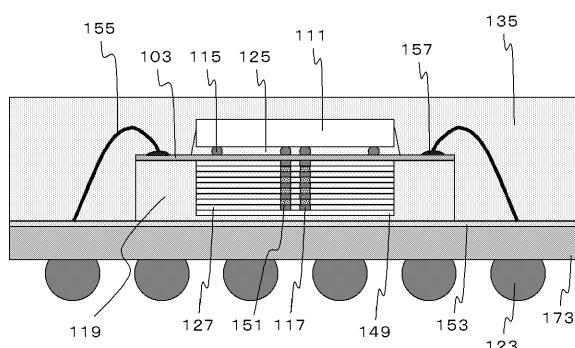

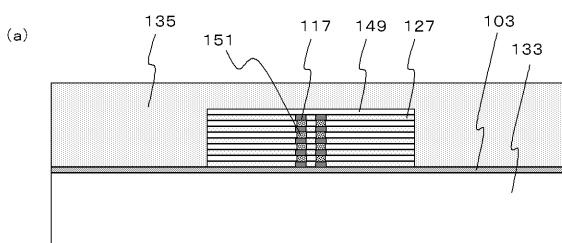

図 15 (a) および図 15 (b) は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図 15 (a) は、図 15 (b) に示した半導体装置のボンディング前の状態を示す図である。図 15 (a) に示した半導体装置は、第三の実施形態に記載の配線層 103 からなる配線体 101 の一方の面に第一の半導体素子 113 が接合され、他方の面に第二の半導体素子 111 が配設された構成を有する。第一の半導体素子 113 は、配線体 101 上を覆う絶縁樹脂 119 中に埋設されている。なお、絶縁樹脂 119 を貫通する導体スルーホール 121 および導体スルーホール 121 に接続する電極端子 123 は、図 15 (a) においては設けられていない。50

## 【0138】

図15(a)に示した半導体装置は、チップ間が電気的に接続された半導体モジュールである。図15(b)に示したように、図15(a)に示した半導体装置は、接着剤153によりヒートプレッダ171の表面に接着される。半導体装置の側方においてヒートプレッダ171の表面にサポートリング161およびTABテープ基板163がこの順に接着剤153により接着されている。TABテープ基板163の表面には配線層165が設けられている。配線層165は、端部が配線層103に向かって引き出されたインナーリード169を有し、インナーリード169はインナーリード封止樹脂167により封止されている。そして、図15(a)に示した半導体装置の外部に引き出された配線層103からなる配線体101は、TAB(Tape Automated Bonding)技術によりインナーリード169を介してTABテープ基板163上の配線層165に接続されている。10

## 【0139】

このように、配線層103を有する半導体装置は、TAB接続型の装置に適用することもできる。TAB技術を用いてインナーリードを接続することにより、半導体装置の設計の自由度をさらに増すことができる。

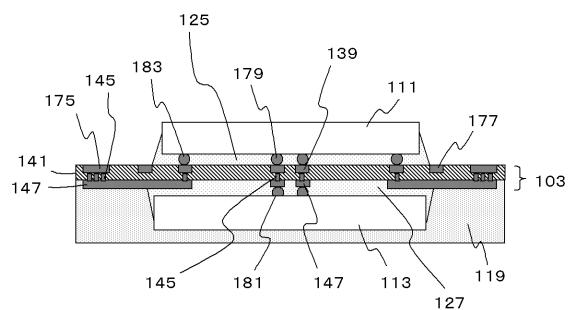

## 【0140】

なお、本実施形態および配線層103からなる配線体101を有する他の実施形態に係る半導体装置において、配線体101の両面に第一の半導体素子113および第二の半導体素子111が接合された半導体モジュールの構成は、たとえば以下のようにすることができる。図16は、本実施形態に係る半導体モジュールの構成を模式的に示す断面図である。20

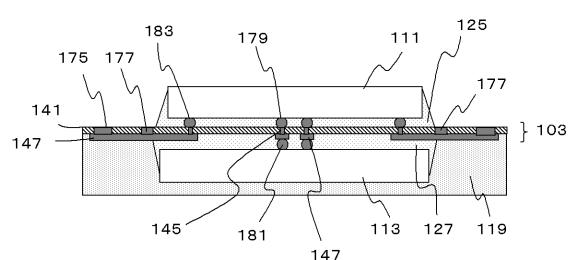

## 【0141】

図16に示した半導体モジュールは、図32に示した配線層103と同様の基本構成を有する配線体101を備える。接続電極であるヴィアプラグ145と外部引き出し用のパッド175とが同層に設けられている。また、これらと同層に樹脂止めパターン177が設けられている。樹脂止めパターン177は、ヴィアプラグ145やパッド175と同じ材料で同一工程により形成することができる。

## 【0142】

パッド175は、第一の半導体素子113および第二の半導体素子111の形成領域の側方における配線層103に設けられている。また、樹脂止めパターン177は、アンダーフィル樹脂125およびアンダーフィル樹脂127の形成領域の近傍において、これらのアンダーフィル樹脂の形成領域の側方に設けられている。30

## 【0143】

また、絶縁樹脂119の形成面と反対側の面に接続された第二の半導体素子111(ロジックLSIチップ)は、外部入出力用電極183、ヴィアプラグ145および配線147を介して配線147に接続されている。また、第二の半導体素子111は、メモリ通信用電極179が、ヴィアプラグ145、配線147およびメモリ電極181を介して配線層103の反対面に接続された第一の半導体素子113(メモリLSIチップ)と接続されている。40

## 【0144】

図16に示した半導体モジュールは、たとえば第三の実施形態に記載の方法(図9(a)～図9(c)、図10(a)～図10(c))を用いて作製することができる。また、以下の方法により作製してもよい。図21(a)～図21(c)、図22(a)～図22(c)、および図23は、図16に示した半導体モジュールの別の製造工程を模式的に示す断面図である。

## 【0145】

まず、シリコン基板133の表面に、スパッタ法などを用いて金属のシード層137を形成する(図21(a))。シード層137は、たとえばCuやNi等とすることができる。次に、シリコン基板133におけるシード層137の形成面の全面に絶縁樹脂膜14

1を設け、絶縁樹脂膜141の所定の位置にレーザー光を照射し、レーザーヴィアすなわち開口部143を設ける(図21(b))。

#### 【0146】

その後、開口部143をCu等の所定の金属膜で埋めこみ、ヴィアプラグ145等の接続電極とする(図21(c))。接続電極の材料は、Cu、Ni、Au、W等の金属または合金等の導電材料とすることができます。さらに具体的には、接続電極を、上からCu/Ni/Au/Niの4層構造とすることができます。また、上からCu/Ni/Auの3層構造とすることもできる。

#### 【0147】

そして、接続電極に接続し、所定のパターンを有する配線147を絶縁樹脂膜141上に形成する(図22(a))。配線147の材料は、たとえばCu等の金属とする。そして、配線147の表面に、上層からAu/Niからなるめっき層(不図示)を形成する。以上の工程により、シリコン基板133上に配線層103が形成される。

#### 【0148】

次に、第二の実施形態に記載の半導体装置110(図7)の製造工程を用いて第一の半導体素子113を配線体101の表面に接続する。第一の半導体素子113のメモリ電極181と配線層103の配線147とを接合させて、第一の半導体素子113と配線層103との間にアンダーフィル樹脂127を充填する(図22(b))。そして、配線層103の表面全面に絶縁樹脂119を成形し、第一の半導体素子113をモールド封入する(図22(c))。

10

20

#### 【0149】

そして、裏面研削等により、シリコン基板133を除去し、シード層137およびNi層をエッティング除去する。さらに、絶縁樹脂119の一部を研削し、ヴィアプラグ145の表面を露出させる(図23)。そして、配線体101の面に第一の半導体素子113に対向させて第二の半導体素子111を接続する。こうして、図16に示した半導体モジュールが得られる。

#### 【0150】

また、図24は、図16に示した半導体モジュールの変形例である。図24に示した半導体モジュールの基本構成は図16と同様であるが、配線体101への第二の半導体素子111および第一の半導体素子113の接合面が反転している。この構成では、たとえば、第一の半導体素子113をロジックLSIチップとし、第二の半導体素子111をメモリチップとすることができます。

30

#### 【0151】

また、本実施形態において、配線層103からなる配線体101を有する半導体モジュールの構成は、図25または図29に示す構成としてもよい。図25および図29は、本実施形態に係る半導体モジュールの構成を模式的に示す断面図である。図25および図29に示した半導体モジュールは、それぞれ基本構成を図16および図24に示した半導体モジュールと同様としているが、配線層103が、接続電極139の形成層、ヴィアプラグ145の形成層、および配線147の形成層の三層の積層構造となっている点が異なる。接続電極139の一部は素子接続電極であり、他の一部は外部接続電極であるパッド175となっている。

40

#### 【0152】

また、図25に示した構成では、たとえば、第一の半導体素子113をメモリチップとし、第二の半導体素子111をロジックLSIチップとすることができます。また、図29に示した半導体モジュールの基本構成は図25と同様であるが、配線体101への第二の半導体素子111および第一の半導体素子113の接合面が反転している。この構成では、たとえば、第一の半導体素子113をロジックLSIチップとし、第二の半導体素子111をメモリチップとすることができます。

#### 【0153】

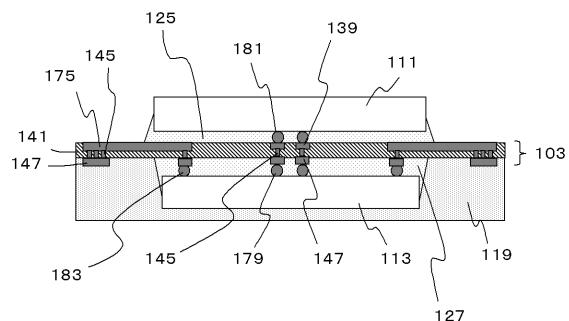

図25に示した半導体モジュールは、たとえば次のようにして作製される。図26(a)

50

) ~ 図 26 ( c )、図 27 ( a ) ~ 図 27 ( c ) および図 28 ( a ) ~ 図 28 ( b ) は、図 25 に示した半導体モジュールの製造工程を模式的に示す断面図である。

#### 【 0154 】

まず、シリコン基板 133 の表面に、スパッタ法などを用いて金属のシード層 137 を形成する(図 26 ( a ) )。次に、シード層 137 上に配線形成位置を露出させるレジストパターンを形成し、シード層 137 の露出部を起点として所定のパターンの接続電極 139 を形成する(図 26 ( b ) )。

#### 【 0155 】

次に、接続電極 139 の形成面の全面に絶縁樹脂膜 141 を設け、接続電極 139 を絶縁樹脂で埋め込む(図 26 ( c ) )。絶縁樹脂膜 141 は、たとえばラミネートフィルム状の絶縁樹脂シートを接合する方法や、スピンドルコート法等により形成することができる。シリコン基板 133 におけるシード層 137 の形成面の全面に絶縁樹脂膜 141 を設け、絶縁樹脂膜 141 の所定の位置にレーザー光を照射し、レーザーヴィアすなわち開口部 143 を設ける(図 26 ( c ) )。

10

#### 【 0156 】

その後、開口部 143 を Cu 等の所定の金属膜で埋めこみ、ヴィアプラグ 145 とする(図 27 ( a ) )。ヴィアプラグ 145 の材料は、たとえば Cu 等の金属とすることができる。また、ヴィアプラグ 145 は、たとえばめっき法により形成することができる。

#### 【 0157 】

そして、ヴィアプラグ 145 に接続し、所定のパターンを有する配線 147 を絶縁樹脂膜 141 上に形成する(図 27 ( b ) )。配線 147 の材料は、たとえば Cu 等の金属とする。そして、配線 147 の表面に、上層から Au / Ni からなるめっき層(不図示)を形成する。以上の工程により、シリコン基板 133 上に配線層 103 が形成される。

20

#### 【 0158 】

次に、第二の実施形態に記載の半導体装置 110 (図 7) の製造工程を用いて第一の半導体素子 113 を配線体 101 の表面に接続する。第一の半導体素子 113 のメモリ電極 181 と配線層 103 の配線 147 とを接合させて、第一の半導体素子 113 と配線層 103 との間にアンダーフィル樹脂 127 を充填する(図 27 ( c ) )。そして、配線層 103 の表面全面に絶縁樹脂 119 を成形し、第一の半導体素子 113 をモールド封入する(図 28 ( a ) )。そして、裏面研削等により、シリコン基板 133 を除去し、シード層 137 および Ni 層をエッチング除去し、ヴィアプラグ 145 の表面を露出させる(図 28 ( b ) )。そして、配線体 101 の面に第一の半導体素子 113 に対向させて第二の半導体素子 111 を接続する。こうして、図 25 に示した半導体モジュールが得られる。

30

#### 【 0159 】

なお、こうした半導体モジュールは、配線層 103 からなる配線体 101 を有する半導体装置だけでなく、たとえば第六の実施形態に記載の半導体装置(図 14)等に適用することも可能である。

#### 【 0160 】

##### ( 第八の実施形態 )

図 17 ( a ) および図 17 ( b ) は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図 17 ( a ) に示した半導体装置は、配線層 103 からなる平板状の配線体と、配線層 103 の一方の面に設けられた第一の半導体素子と、一方の面および第一の半導体素子の側面を被覆する絶縁樹脂 119 と、絶縁樹脂 119 を貫通する導体スルーホール 121 と、配線層 103 の他方の面に設けられた第二の半導体素子 111 と、を有する。

40

#### 【 0161 】

そして、第一の半導体素子は、複数の半導体素子 149 が面に垂直な方向に沿って積層された積層体であり、配線 147 において最も配線体 101 から遠い側に設けられた電極 117 と、第一の半導体素子 113 の配線層 103 の側の面に設けられた電極 115 とが、平面視において一致している構成なっている。

50

**【 0 1 6 2 】**

なお、本実施形態においても、配線層 103 は、平板状の絶縁樹脂膜 141（図 17(a) では不図示）と、絶縁体を貫通する導電体と、を有し、導電体を介して複数の半導体素子 149 と第二の半導体素子 111 とを電気的に接続する。

**【 0 1 6 3 】**

図 17(a) に示した半導体モジュールは、図 17(b) に示したように、配線層 103 中に配線に接続する導体パッド 157 および導体パッド 157 に接続しているワイヤ 155 により配線基板 173 に接続され、半導体モジュールとワイヤ 155 とが絶縁樹脂 135 により封止されている。

**【 0 1 6 4 】**

次に、図 17(a) に示した半導体モジュールの製造方法を説明する。図 18(a) ~ 図 18(c) および図 19(a)、図 19(b) は、図 17 に示した半導体装置の製造工程を説明する断面図である。

**【 0 1 6 5 】**

まず、図 18(a) に示したシリコン基板 133 上に配線層 103 を形成する（図 18(b)）。配線層 103 の形成方法は、たとえば第三の実施形態または第七の実施形態に記載の方法とすることができます。次に、あらかじめ一方の面に電極 117 を形成した半導体素子 149 を配線層 103 上の配線に接合する。そして、半導体素子 149 と電極 117 との間にアンダーフィル樹脂 127 を充填する。これを繰り返すことにより、所定の数の半導体素子 149 が配線層 103 上に積層される（図 18(c)）。

**【 0 1 6 6 】**

次に、配線層 103 の半導体素子 149 が積層された側の面を絶縁樹脂 135 で被覆する。このとき、半導体素子 149 を絶縁樹脂 135 中に埋設させる（図 19(a)）。そして、裏面研削等の方法により、シリコン基板 133 を裏面側から除去する（図 19(b)）。そして、シリコン基板 133 の除去により露出した配線層 103 の表面に第二の半導体素子 111 を接合する。これにより、図 17(a) に示した半導体モジュールが得られる。

**【 0 1 6 7 】**

図 17(b) に示した半導体装置は、以上の工程で得られた半導体モジュールを、配線基板 173 の表面に接着し、ワイヤ 155 によるボンディングおよび絶縁樹脂 135 による封止を行う。そして、電極端子 123 の形成を行うことにより得ることができる。

**【 0 1 6 8 】**

図 17(a) および図 17(b) に示した半導体装置は、第二の半導体素子 111 と半導体素子 149 とが配線体 101 の主面の法線方向に一直線に導電部材が設けられて第二の半導体素子 111 と半導体素子 149 とが接続された構成となっている。このため、第二の半導体素子 111 と半導体素子 149 との接続距離を短くしつつ、導電部材を高密度に配置することができる。このため、第二の半導体素子 111 と半導体素子 149 との間の信号処理速度を向上することができる。

**【 0 1 6 9 】**

また、図 20(a) および図 20(b) は、それぞれ図 17(a) および図 17(b) に示した半導体装置において、配線体 101 が絶縁膜 107、シリコン層 105 および配線層 103 の積層体であるとともに、半導体素子 149 の積層体にかえて一つの第一の半導体素子 113 を配線層 103 の一方の面に接合した構成の半導体装置を模式的に示す断面図である。

**【 0 1 7 0 】**

図 20(b) に示したように、この半導体装置は、シリコン層 105 および絶縁膜 107 を貫通する導体ヴィア 109 に接続して形成された導体パッド 157 を有する半導体モジュール（図 20(a)）を、配線基板 173 に接着剤 153 を介して搭載している。そして、導体パッド 157 と配線基板 173 とをワイヤ 155 により電気的に接続するとともに、半導体モジュールとワイヤ 155 を絶縁樹脂 135 により封止した構成になつて

10

20

30

40

50

る。

【0171】

また、図30は、図20(b)に示した半導体装置に配線層103からなる配線体101を有する半導体モジュールを適用した例を示す断面図である。なお、図30では、第一の半導体素子113が絶縁樹脂119から露出せずに埋設された構成となっている。

【0172】

図30においては、接続電極139に導体パッド157を接合し、導体パッド157と配線基板173との間をワイヤ155で接続することにより、配線層103を介して配線基板173と第一の半導体素子113および第二の半導体素子111とが電気的に接続されている。この構成において、絶縁樹脂119と配線基板173とを接続する接着剤153は、たとえばAgペーストとすることができる。なお、図30において、接続電極139の一部はヴィアプラグ145となっている。

【0173】

図30に示した半導体装置では、配線体101と配線基板173とを確実に接続しつつ、第二の半導体素子111と第一の半導体素子113とを短距離で高密度に接続されるため、動作特性に優れた構成となっている。

【0174】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0175】

たとえば、以上の実施形態に記載の半導体装置において、配線体101の構成は第一の実施形態～第三の実施形態のいずれかに記載された構成を選択して用いることができる。

【図面の簡単な説明】

【0176】

【図1】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図2】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図3】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図4】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図5】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図6】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図7】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図8】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図9】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図10】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図11】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図12】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図13】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図14】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図15】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図16】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図17】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図18】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図19】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図20】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図21】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図22】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図23】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図24】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図25】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

10

20

30

40

50

【図26】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図27】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図28】実施の形態に係る半導体装置の製造工程を模式的に示した断面図である。

【図29】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図30】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図31】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図32】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図33】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図34】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

【図35】実施の形態に係る半導体装置の構成を模式的に示した断面図である。

10

## 【符号の説明】

## 【0177】

|     |             |    |

|-----|-------------|----|

| 100 | 半導体装置       |    |

| 101 | 配線体         |    |

| 103 | 配線層         |    |

| 105 | シリコン層       |    |

| 107 | 絶縁膜         |    |

| 109 | 導体ヴィア       |    |

| 110 | 半導体装置       | 20 |

| 111 | 半導体素子       |    |

| 113 | 半導体素子       |    |

| 115 | 電極          |    |

| 117 | 電極          |    |

| 119 | 絶縁樹脂        |    |

| 120 | 半導体装置       |    |

| 121 | 導体スルーホール    |    |

| 123 | 電極端子        |    |

| 125 | アンダーフィル樹脂   |    |

| 127 | アンダーフィル樹脂   |    |

| 129 | 基板          | 30 |

| 131 | 導体ポスト       |    |

| 133 | シリコン基板      |    |

| 135 | 絶縁樹脂        |    |

| 137 | シード層        |    |

| 139 | 接続電極        |    |

| 141 | 絶縁樹脂膜       |    |

| 143 | 開口部         |    |

| 145 | ヴィアプラグ      |    |

| 147 | 配線          |    |

| 149 | 半導体素子       | 40 |

| 150 | 半導体装置       |    |

| 151 | 導体スルーホール    |    |

| 153 | 接着剤         |    |

| 155 | ワイヤ         |    |

| 157 | 導体パッド       |    |

| 159 | 導体パッド       |    |

| 161 | サポートリング     |    |

| 163 | テープ基板       |    |

| 165 | 配線層         |    |

| 167 | インナーリード封止樹脂 | 50 |

- 1 6 9 インナーリード

1 7 1 ヒートスプレッダ

1 7 3 配線基板

1 7 5 パッド

1 7 7 樹脂止めパターン

1 7 9 メモリ通信用電極

1 8 1 メモリ電極

1 8 3 外部入出力用電極

1 8 5 半導体装置

1 8 7 半導体装置

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

120

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

(a)

【図16】

【図17】

(a)

(b)

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図31】

【図30】

【図32】

【図33】

【図34】

【図35】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 25/18 (2006.01)

合議体

審判長 丸山 英行

審判官 田口 傑

審判官 川向 和実

(56)参考文献 特開2001-177049 (JP, A)

特開平4-370958 (JP, A)

特開2003-46026 (JP, A)

特開2002-343904 (JP, A)

特開平3-120749 (JP, A)

特開平5-48001 (JP, A)

国際公開第02/069399 (WO, A1)

特開2003-7910 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/00-25/18

H01L 23/12