【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成22年10月28日(2010.10.28)

【公表番号】特表2010-503929(P2010-503929A)

【公表日】平成22年2月4日(2010.2.4)

【年通号数】公開・登録公報2010-005

【出願番号】特願2009-528456(P2009-528456)

【国際特許分類】

G 06 F 12/02 (2006.01)

G 06 F 12/00 (2006.01)

【F I】

G 06 F 12/02 510 A

G 06 F 12/02 530 E

G 06 F 12/00 597 U

【手続補正書】

【提出日】平成22年9月9日(2010.9.9)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

共に消去可能なデータの論理ユニットを記憶するためのブロックから各々なる、複数のブロックに組織化された不揮発性メモリにおける、データを前記メモリに記憶する方法であって、

データの論理ユニットの更新を記憶するために同時に開放中の更新ブロックとして、第1の所定ブロック数まで割り当てるステップと、

データの論理ユニットの更新を記憶するために同時に開放中の更新ブロックの第1の所定最大数までのプールを提供するステップと、

更新ブロックを属性のセットに基づいて分類するための予め定められたクラスのセットを提供するステップであって、各クラスは、関連する所定最大数の更新ブロックまでのサブプールをサポートするステップと、

対応する置換規則のセットを前記予め定められたクラスのセットに提供して、それぞれのサブプール内の置換されるべき前記更新ブロックを特定するステップと、

前記プール内の前記更新ブロックを対応するサブプールにグループ化するステップと、

同一のクラスの他の更新ブロックが導入されつつある場合にはいつでも、前記関連する所定最大数の更新ブロックを含むサブプール内にある最もアクティブでない更新ブロックを閉鎖および削除するステップであって、前記削除される更新ブロックは、同一のクラス用の前記対応する置換規則に従って選択されるステップと、

を含む方法。

【請求項2】

請求項1記載の方法において、

前記属性のセットは、論理的に連続した順序でデータを記憶するブロックを含む方法。

【請求項3】

請求項1記載の方法において、

前記属性のセットは、論理的に不連続な順序でデータを記憶するブロックを含む方法。

【請求項4】

請求項1記載の方法において、

前記属性のセットは、前記メモリを動作させることに関連したシステムデータを記憶するブロックを含む方法。

【請求項5】

請求項1記載の方法において、

前記メモリは、フラッシュEEPROMである方法。

【請求項6】

請求項1記載の方法であって、

前記メモリは、NAND構造を有する方法。

【請求項7】

請求項1記載の方法において、

前記メモリは、着脱可能なメモリカード上にある方法。

【請求項8】

請求項1記載の方法において、

前記不揮発性メモリは、フローティングゲート構造のメモリセルを有する方法。

【請求項9】

請求項1記載の方法において、

前記不揮発性メモリは、誘電体層構造のメモリセルを有する方法。

【請求項10】

請求項1～9記載の方法において、

前記メモリは、1ビットのデータをそれぞれ記憶するメモリセルを有する方法。

【請求項11】

請求項1～9記載の方法において、

前記メモリは、1ビット以上のデータをそれぞれ記憶するメモリセルを有する方法。

【請求項12】

不揮発性メモリであって、

ブロックに組織化されたメモリであって、各ブロックは、共に消去可能なメモリユニットに分割され、各メモリユニットは、データの論理ユニットを記憶するためのものであるメモリと、

データの論理ユニットの更新を記憶するために同時に開放中の更新ブロックの第1の所定最大数までのプールと、

更新ブロックを属性のセットに基づいて分類するための予め定められたクラスのセットであって、各クラスは、関連する所定最大数の更新ブロックまでのサブプールをサポートするセットと、

それぞれのサブプール内の置換されるべき前記更新ブロックを特定するための、前記予め定められたクラスのセットに対応する置換規則のセットと、

クラス毎に更新ブロックを含むサブプールのセットと、

前記ブロックの動作を制御するためのコントローラであって、前記動作は、

同一のクラスの他の更新ブロックが導入されつつある場合にはいつでも、前記関連する所定最大数の更新ブロックを含むサブプール内にある更新ブロックを閉鎖および削除し、前記削除される更新ブロックは、同一のクラス用の前記対応する置換規則に従って選択されることを含むコントローラと、

を備える不揮発性メモリ。

【請求項13】

請求項1記載のメモリにおいて、

前記属性のセットは、論理的に連続した順序でデータを記憶するブロックを含むメモリ。

【請求項14】

請求項1記載のメモリにおいて、

前記属性のセットは、論理的に不連続な順序でデータを記憶するブロックを含むメモリ

。

【請求項 1 5】

請求項1 2記載のメモリにおいて、

前記属性のセットは、前記メモリを動作させることに関連したシステムデータを記憶するブロックを含むメモリ。

【請求項 1 6】

請求項1 2記載のメモリであって、

前記メモリは、フラッシュEEPROMであるメモリ。

【請求項 1 7】

請求項1 2記載のメモリにおいて、

前記メモリは、NAND構造を有するメモリ。

【請求項 1 8】

請求項1 2記載のメモリにおいて、

前記メモリは、着脱可能なメモリカード上にあるメモリ。

【請求項 1 9】

請求項1 2記載のメモリにおいて、

前記不揮発性メモリは、フローティングゲート構造のメモリセルを有するメモリ。

【請求項 2 0】

請求項1 2記載のメモリにおいて、

前記不揮発性メモリは、誘電体層構造のメモリセルを有するメモリ。

【請求項 2 1】

不揮発性メモリであって、

ブロックに組織化されたメモリであって、各ブロックは、共に消去可能なメモリユニットに分割され、各メモリユニットは、データの論理ユニットを記憶するためのものであるメモリと、

データの論理ユニットの更新を記憶するために同時に開放中の更新ブロックの第1の所定最大数までのプールと、

更新ブロックを属性のセットに基づいて分類するための予め定められたクラスのセットであって、各クラスは、関連する所定最大数の更新ブロックまでのサブプールをサポートするセットと、

それぞれのサブプール内の置換されるべき前記更新ブロックを特定するため、前記予め定められたクラスのセットに対応する置換規則のセットと、

クラス毎に更新ブロックを含むサブプールのセットと、

同一のクラスの他の更新ブロックが導入されつつある場合にはいつでも、前記関連する所定最大数の更新ブロックを含むサブプール内にある更新ブロックを閉鎖するおよび削除する手段であって、前記削除される更新ブロックは、同一のクラス用の前記対応する置換規則に従って選択される手段と、

を備える不揮発性メモリ。

【請求項 2 2】

請求項1 2 ~ 2 1記載のメモリにおいて、

前記メモリは、1ビットのデータをそれぞれ記憶するメモリセルを有するメモリ。

【請求項 2 3】

請求項1 2 ~ 2 1記載のメモリにおいて、

前記メモリは、1ビット以上のデータをそれぞれ記憶するメモリセルを有するメモリ。

【手続補正 2】

【補正対象書類名】図面

【補正対象項目名】図 2 6 C

【補正方法】変更

【補正の内容】

【図 26C】

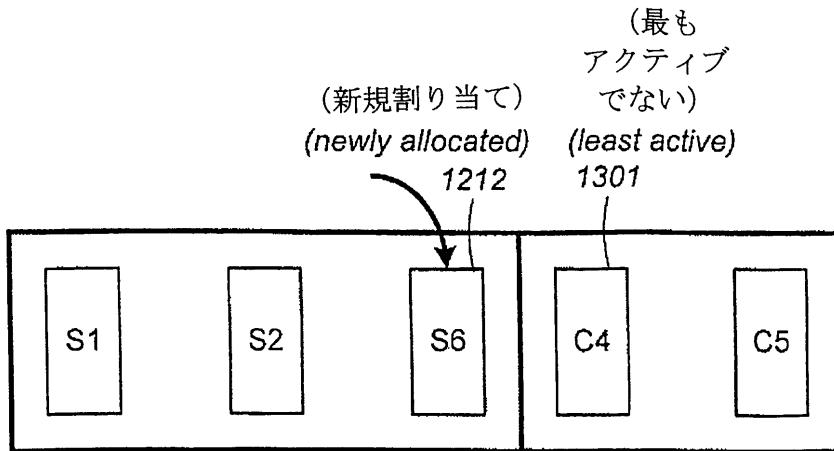

(A newly allocated update block S6 is introduced to the update pool for the new logical group)

(新規に割り当てられた更新ブロック S6 が、新規の論理グループ用の更新プールに導入される)

FIG. 26C

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図 27 B

【補正方法】変更

【補正の内容】

【図 27 B】

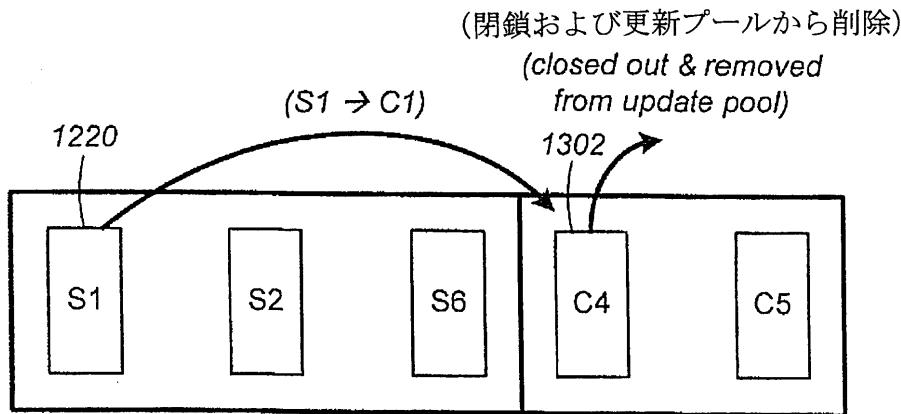

(In order  $U_{cmax}$  not be exceeded, the least active chaotic update block is closed out to make room)

( $U_{cmax}$ を超えないようにするために、

空きを作るために最もアクティブでない

カオス的更新ブロックが閉鎖される)

FIG. 27B

【手続補正4】

【補正対象書類名】図面

【補正対象項目名】図 27 C

【補正方法】変更

【補正の内容】

【図 27C】

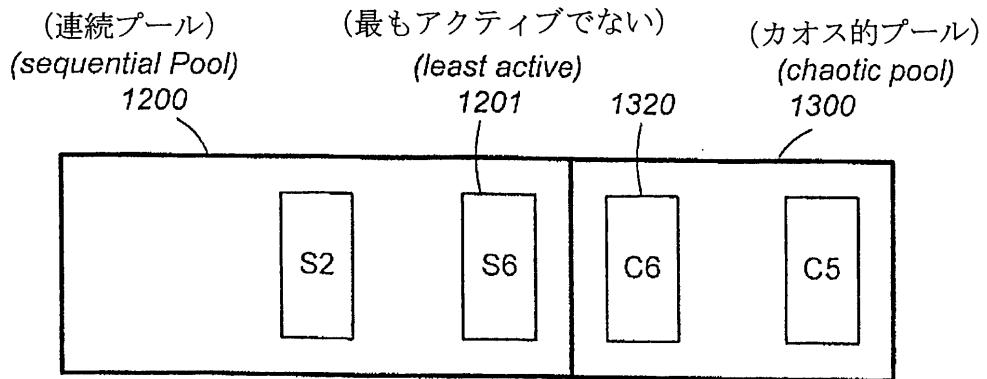

*(The chaotic update block S1 is introduced as C6 to the chaotic update pool)*

(カオス的更新ブロック S1 が、

C6 としてカオス的更新プールに導入される)

**FIG. 27C**