(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-113568

(P2006-113568A)

(43) 公開日 平成18年4月27日(2006.4.27)

| (51) Int.Cl.                | F 1         | テーマコード (参考) |

|-----------------------------|-------------|-------------|

| <b>G09F</b> 9/30 (2006.01)  | G09 F 9/30  | 338 3K007   |

| <b>G09F</b> 9/00 (2006.01)  | G09 F 9/00  | 338 5C094   |

| <b>H05B</b> 33/22 (2006.01) | HO5 B 33/22 | Z 5G435     |

| <b>H01L</b> 51/50 (2006.01) | HO5 B 33/14 | A           |

| <b>H05B</b> 33/10 (2006.01) | HO5 B 33/10 |             |

審査請求 未請求 請求項の数 17 OJ (全 44 頁) 最終頁に続く

|              |                              |            |                                                  |

|--------------|------------------------------|------------|--------------------------------------------------|

| (21) 出願番号    | 特願2005-267826 (P2005-267826) | (71) 出願人   | 000153878                                        |

| (22) 出願日     | 平成17年9月15日 (2005. 9. 15)     |            | 株式会社半導体エネルギー研究所                                  |

| (31) 優先権主張番号 | 特願2004-272628 (P2004-272628) |            | 神奈川県厚木市長谷398番地                                   |

| (32) 優先日     | 平成16年9月17日 (2004. 9. 17)     | (72) 発明者   | 村上 智史                                            |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内              |

|              |                              | (72) 発明者   | 大谷 久<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内      |

|              |                              | (72) 発明者   | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内     |

|              |                              | F ターム (参考) | 3K007 AB12 AB18 BA06 BB01 DB03<br>EA02 FA01 FA02 |

(54) [発明の名称] 表示装置、及び表示装置の作製方法

(57) 【要約】

**【課題】** 本発明では、信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

**【解決手段】** 本発明は、画素電極層上にスペーサを形成し、電界発光層形成時のマスクから画素電極層を保護する。また、透水性を有する有機材料を含む層を表示装置の中にシール材で封止し、かつシール材と有機材料を含む層が接しないため、発光素子の水等の汚染物質による劣化を防ぐ事ができる。シール材は表示装置の駆動回路領域の一部に形成されるため表示装置の狭額縁化も達成できる。

【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

画素領域、接続領域を有し、

前記画素領域に不純物領域を含む半導体層を有し、

前記半導体層上にはゲート絶縁層を有し、

前記ゲート絶縁層上にはゲート電極層を有し、

前記ゲート電極層上には第1の層間絶縁層を有し、

前記ゲート絶縁層及び前記第1の層間絶縁層は前記不純物領域に達する第1の開口を有し、

前記開口にソース電極層又はドレイン電極層を有し、

前記ソース電極層又は前記ドレイン電極層は、前記第1の層間絶縁層を介して前記ゲート電極層の一部を覆っており、

前記ソース電極層又は前記ドレイン電極層及び前記第1の層間絶縁層上に第2の層間絶縁層を有し、

前記第2の層間絶縁層は前記ソース電極層又は前記ドレイン電極層に達する第2の開口を有し、

前記第2の開口は、前記第1の層間絶縁層を介して前記ゲート電極層の一部を覆っている前記ソース電極層又は前記ドレイン電極層に設けられ、

前記第2の開口にスペーサを有する第1の電極層を有し、

前記接続領域に前記第1の層間絶縁層上に設けられた配線層を有し、

前記配線層上に、前記配線層に達する第3の開口が設けられた前記第2の層間絶縁層を有し、

前記第3の開口の上端部は、絶縁層に覆われており、

前記第3の開口に、前記絶縁層に接して第2の電極層を有することを特徴とする表示装置。

**【請求項 2】**

画素領域、接続領域を有し、

前記画素領域に不純物領域を含む半導体層を有し、

前記半導体層上にはゲート絶縁層を有し、

前記ゲート絶縁層上にはゲート電極層を有し、

前記ゲート電極層上には第1の層間絶縁層を有し、

前記ゲート絶縁層及び前記第1の層間絶縁層は前記不純物領域に達する第1の開口を有し、

前記開口にソース電極層又はドレイン電極層を有し、

前記ソース電極層又は前記ドレイン電極層は、前記第1の層間絶縁層を介して前記ゲート電極層の一部を覆っており、

前記ソース電極層又は前記ドレイン電極層及び前記第1の層間絶縁層上に第2の層間絶縁層を有し、

前記第2の層間絶縁層は前記ソース電極層又は前記ドレイン電極層に達する第2の開口を有し、

前記第2の開口は、前記第1の層間絶縁層を介して前記ゲート電極層の一部を覆っている前記ソース電極層又は前記ドレイン電極層に設けられ、

前記第2の開口にスペーサを有する第1の電極層を有し、

前記接続領域に前記第1の層間絶縁層上に設けられた配線層を有し、

前記配線層上に、前記配線層に達する第3の開口が設けられた前記第2の層間絶縁層を有し、

前記第3の開口の上端部は、絶縁層に覆われており、

前記第3の開口に、前記絶縁層に接して第2の電極層を有し、

前記第1の層間絶縁層上にシール材を有し、

前記シール材は前記絶縁層と接しないことを特徴とする表示装置。

10

20

30

40

50

**【請求項 3】**

請求項 1 または請求項 2 において、前記スペーサは柱状であることを特徴とする表示装置。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれか一項において、前記スペーサと前記絶縁層とは分離していることを特徴とする表示装置。

**【請求項 5】**

請求項 1 乃至請求項 3 のいずれか一項において、前記スペーサと前記絶縁層とはつながっていることを特徴とする表示装置。

**【請求項 6】**

画素領域、接続領域を有し、

前記画素領域に不純物領域を含む半導体層を有し、

前記半導体層上にはゲート絶縁層を有し、

前記ゲート絶縁層上にはゲート電極層を有し、

前記ゲート電極層上には第 1 の層間絶縁層を有し、

前記ゲート絶縁層及び前記第 1 の層間絶縁層は前記不純物領域に達する第 1 の開口を有し、

前記開口にソース電極層又はドレイン電極層を有し、

前記ソース電極層又は前記ドレイン電極層は、前記第 1 の層間絶縁層を介して前記ゲート電極層の一部を覆っており、

前記ソース電極層又は前記ドレイン電極層及び前記第 1 の層間絶縁層上に第 2 の層間絶縁層を有し、

前記第 2 の層間絶縁層は前記ソース電極層又は前記ドレイン電極層に達する第 2 の開口を有し、

前記第 2 の開口は、前記第 1 の層間絶縁層を介して前記ゲート電極層の一部を覆っている前記ソース電極層又は前記ドレイン電極層に設けられ、

前記第 2 の開口に第 1 の電極層を有し、

前記接続領域に前記第 1 の層間絶縁層上に設けられた配線層を有し、

前記配線層上に、前記配線層に達する第 3 の開口が設けられた前記第 2 の層間絶縁層を有し、

前記第 3 の開口の上端部は、絶縁層に覆われており、

前記第 3 の開口に、前記絶縁層に接して第 2 の電極層を有し、

前記第 1 の層間絶縁層上にシール材を有し、

前記シール材は前記絶縁層と接しないことを特徴とする表示装置。

**【請求項 7】**

請求項 1 乃至 6 のいずれか一項において、前記第 1 の層間絶縁層は無機絶縁性材料であり、前記第 2 の層間絶縁層は有機絶縁性材料であることを特徴とする表示装置。

**【請求項 8】**

請求項 1 乃至 6 のいずれか一項において、前記第 2 の層間絶縁層は 2 層の積層構造であることを特徴とする表示装置。

**【請求項 9】**

請求項 8 において、前記第 2 の層間絶縁層は無機絶縁性材料と有機絶縁性材料の 2 層の積層構造であることを特徴とする表示装置。

**【請求項 10】**

画素領域に不純物領域を有する半導体層を形成し、

接続領域及び前記半導体層上にゲート絶縁層を形成し、

前記ゲート絶縁層上にゲート電極層及び導電層を形成し、

前記ゲート電極層上及び前記導電層上に第 1 の層間絶縁層を形成し、

前記ゲート絶縁層及び前記第 1 の層間絶縁層は前記不純物領域に達する第 1 の開口を有し、

10

20

30

40

50

前記第1の開口、及び前記ゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、

前記第1の層間絶縁層上に前記導電層を覆って配線層を形成し、

前記第1の層間絶縁層、前記配線層、前記ソース電極層及び前記ドレイン電極層上に第2の層間絶縁層を形成し、

前記第2の層間絶縁層に前記ソース電極層又は前記ドレイン電極層に達する第2の開口、及び前記配線層に達する第3の開口を形成し、

前記第2の開口に第1の電極層を形成し、

前記第2の層間絶縁層の前記第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、

前記第1の電極層上にスペーサを形成し、

前記第3の開口に、前記絶縁層に接して第2の電極層を形成することを特徴とする表示装置の作製方法。

#### 【請求項1-1】

画素領域に不純物領域を有する半導体層を形成し、

接続領域及び前記半導体層上にゲート絶縁層を形成し、

前記ゲート絶縁層上にゲート電極層及び導電層を形成し、

前記ゲート電極層上及び前記導電層上に第1の層間絶縁層を形成し、

前記ゲート絶縁層及び前記第1の層間絶縁層は前記不純物領域に達する第1の開口を有し、

前記第1の開口、及び前記ゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、

前記第1の層間絶縁層上に前記導電層を覆って配線層を形成し、

前記第1の層間絶縁層、前記配線層、前記ソース電極層及び前記ドレイン電極層上に第2の層間絶縁層を形成し、

前記第2の層間絶縁層に前記ソース電極層又は前記ドレイン電極層に達する第2の開口、及び前記配線層に達する第3の開口を形成し、

前記第2の開口に第1の電極層を形成し、

前記第2の層間絶縁層の前記第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、

前記第1の電極層上にスペーサを形成し、

前記第3の開口に、前記絶縁層に接して第2の電極層を形成し、

前記第1の層間絶縁層上に、前記絶縁層に接せずにシール材を形成することを特徴とする表示装置の作製方法。

#### 【請求項1-2】

請求項1-0または請求項1-1において、前記スペーサと前記絶縁層とは同材料を用いて同工程で形成することを特徴とする表示装置の作製方法。

#### 【請求項1-3】

画素領域に不純物領域を有する半導体層を形成し、

接続領域及び前記半導体層上にゲート絶縁層を形成し、

前記ゲート絶縁層上にゲート電極層及び導電層を形成し、

前記ゲート電極層上及び前記導電層上に第1の層間絶縁層を形成し、

前記ゲート絶縁層及び前記第1の層間絶縁層は前記不純物領域に達する第1の開口を有し、

前記第1の開口、及び前記ゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、

前記第1の層間絶縁層上に前記導電層を覆って配線層を形成し、

前記第1の層間絶縁層、前記配線層、前記ソース電極層及び前記ドレイン電極層上に第2の層間絶縁層を形成し、

前記第2の層間絶縁層に前記ソース電極層又は前記ドレイン電極層に達する第2の開

10

20

30

40

50

口、及び前記配線層に達する第3の開口を形成し、

前記第2の開口に第1の電極層を形成し、

前記第2の層間絶縁層の前記第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、

前記第3の開口に、前記絶縁層に接して第2の電極層を形成し、

前記第1の層間絶縁層上に、前記絶縁層に接せずにシール材を形成することを特徴とする表示装置の作製方法。

【請求項14】

請求項10乃至13いずれか一項において、前記第1の層間絶縁層を形成した後、加熱処理を行うことを特徴とする表示装置の作製方法。 10

【請求項15】

請求項10乃至14いずれか一項において、前記第1の層間絶縁層は無機絶縁材料を用いて形成し、前記第2の層間絶縁層は有機絶縁性材料を塗布法を用いて形成することを特徴とする表示装置の作製方法。

【請求項16】

請求項10乃至14いずれか一項において、前記第2の層間絶縁層は2層の積層構造であり、酸化窒化膜を形成した後、アルキル基を有する酸化珪素膜を塗布法により形成することを特徴とする表示装置の作製方法。

【請求項17】

請求項10乃至14いずれか一項において、前記第1の層間絶縁層は2層の積層構造であり、窒化酸化珪素膜を形成し、連続的に酸化窒化珪素膜を形成することを特徴とする表示装置の作製方法。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置、及び表示装置の作製方法に関する。

【背景技術】

【0002】

EL素子は、一定期間駆動すると、発光輝度、発光の均一性等の発光特性が初期に比べて著しく劣化するという問題がある。この信頼性の低さは実用化の用途が限られている要因である。 30

【0003】

信頼性を悪化させる要因の一つに、外部からEL素子に侵入する水分や酸素などがあげられる。

【0004】

EL素子の劣化を防ぐ構造を有する表示装置の開発がなされている。また、EL素子の形成された絶縁体の上にシール材を形成し、シール材を用いてカバー材およびシール材で囲まれた密閉空間を樹脂などから成る充填材で充填し、外部から遮断する方法もある（例えば、特許文献1参照。）。 40

【特許文献1】特開2001-203076号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明では、工程、装置を複雑化することなく、高い信頼性や優れた電気特性を有する表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、コンタクトにおける開口の段差を絶縁層によって被覆し、段差を軽減し、 50

なだらかな形状に加工する。その絶縁層に接して配線等は形成されるため、配線の被覆性が向上する。また、透水性を有する（水分を透過し得る）有機材料を含む層を表示装置の中にシール材で封止し、かつシール材と有機材料を含む層が接しないため、発光素子の水等の汚染物質による劣化を防ぐ事ができる。シール材は表示装置の駆動回路領域の一部に形成されるため表示装置の狭額縫化も達成できる。

#### 【 0 0 0 7 】

本発明を用いることのできる表示装置には、エレクトロルミネセンス（以下「EL」ともいう。）と呼ばれる発光を発現する有機物、若しくは有機物と無機物の混合物を含む層を、電極間に介在させた発光素子とTFTとが接続された発光表示装置がある。

#### 【 0 0 0 8 】

本発明の表示装置の一は、画素領域、接続領域を有し、画素領域に不純物領域を含む半導体層を有し、半導体層上にはゲート絶縁層を有し、ゲート絶縁層上にはゲート電極層を有し、ゲート電極層上には第1の層間絶縁層を有し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、開口にソース電極層又はドレイン電極層を有し、ソース電極層又はドレイン電極層は、第1の層間絶縁層を介してゲート電極層の一部を覆っており、ソース電極層又はドレイン電極層及び第1の層間絶縁層上に第2の層間絶縁層を有し、第2の層間絶縁層はソース電極層又はドレイン電極層に達する第2の開口を有し、第2の開口は、第1の層間絶縁層を介してゲート電極層の一部を覆っているソース電極層又はドレイン電極層に設けられ、第2の開口にスペーサを有する第1の電極層を有し、接続領域に第1の層間絶縁層上に設けられた配線層を有し、配線層上に、配線層に達する第3の開口が設けられた第2の層間絶縁層を有し、第3の開口の上端部は、絶縁層に覆われており、第3の開口に、絶縁層に接して第2の電極層を有する。

#### 【 0 0 0 9 】

本発明の表示装置の一は、画素領域、接続領域を有し、画素領域に不純物領域を含む半導体層を有し、半導体層上にはゲート絶縁層を有し、ゲート絶縁層上にはゲート電極層を有し、ゲート電極層上には第1の層間絶縁層を有し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、開口にソース電極層又はドレイン電極層を有し、ソース電極層又はドレイン電極層は、第1の層間絶縁層を介してゲート電極層の一部を覆っており、ソース電極層又はドレイン電極層及び第1の層間絶縁層上に第2の層間絶縁層を有し、第2の層間絶縁層はソース電極層又はドレイン電極層に達する第2の開口を有し、第2の開口は、第1の層間絶縁層を介してゲート電極層の一部を覆っているソース電極層又はドレイン電極層に設けられ、第2の開口にスペーサを有する第1の電極層を有し、接続領域に第1の層間絶縁層上に設けられた配線層を有し、配線層上に、配線層に達する第3の開口が設けられた第2の層間絶縁層を有し、第3の開口の上端部は、絶縁層に覆われており、第3の開口に、絶縁層に接して第2の電極層を有し、第1の層間絶縁層上にシール材を有し、シール材は絶縁層と接しない。

#### 【 0 0 1 0 】

上記構成において、スペーサと絶縁層とは図18のように分離していてもよいし、図22のように、連続的につながっていてもよい。スペーサは、画素電極層として機能する第1の電極層上に電界発光層を形成する際、使用するマスクに対するスペーサとなるだけでなく、電界発光層を形成し、封止基板により封止し表示装置として完成した後も、表示装置が外部からの圧力や衝撃により、損傷、変形するのを防ぐスペーサとして機能する。

#### 【 0 0 1 1 】

本発明の表示装置の一は、画素領域、接続領域を有し、画素領域に不純物領域を含む半導体層を有し、半導体層上にはゲート絶縁層を有し、ゲート絶縁層上にはゲート電極層を有し、ゲート電極層上には第1の層間絶縁層を有し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、開口にソース電極層又はドレイン電極層を有し、ソース電極層又はドレイン電極層は、第1の層間絶縁層を介してゲート電極層の一部を覆っており、ソース電極層又はドレイン電極層及び第1の層間絶縁層上に第2の層間絶縁層を有し、第2の層間絶縁層はソース電極層又はドレイン電極層に達する第2の開口を

10

20

30

40

50

有し、第2の開口は、第1の層間絶縁層を介してゲート電極層の一部を覆っているソース電極層又はドレイン電極層に設けられ、第2の開口に第1の電極層を有し、接続領域に第1の層間絶縁層上に設けられた配線層を有し、配線層上に、配線層に達する第3の開口が設けられた第2の層間絶縁層を有し、第3の開口の上端部は、絶縁層に覆われており、第3の開口に、絶縁層に接して第2の電極層を有し、第1の層間絶縁層上にシール材を有し、シール材は絶縁層と接しない。

#### 【0012】

本発明の表示装置の作製方法の一は、画素領域に不純物領域を有する半導体層を形成し、接続領域及び半導体層上にゲート絶縁層を形成し、ゲート絶縁層上にゲート電極層及び導電層を形成し、ゲート電極層上及び導電層上に第1の層間絶縁層を形成し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、第1の開口、及びゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、第1の層間絶縁層上に導電層を覆って配線層を形成し、第1の層間絶縁層、配線層、ソース電極層及びドレイン電極層上に第2の層間絶縁層を形成し、第2の層間絶縁層にソース電極層又はドレイン電極層に達する第2の開口、及び配線層に達する第3の開口を形成し、第2の開口に第1の電極層を形成し、第2の層間絶縁層の第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、第1の電極層上にスペーサを形成し、第3の開口に、絶縁層に接して第2の電極層を形成する。

#### 【0013】

本発明の表示装置の作製方法の一は、画素領域に不純物領域を有する半導体層を形成し、接続領域及び半導体層上にゲート絶縁層を形成し、ゲート絶縁層上にゲート電極層及び導電層を形成し、ゲート電極層上及び導電層上に第1の層間絶縁層を形成し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、第1の開口、及びゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、第1の層間絶縁層上に導電層を覆って配線層を形成し、第1の層間絶縁層、配線層、ソース電極層及びドレイン電極層上に第2の層間絶縁層を形成し、第2の層間絶縁層にソース電極層又はドレイン電極層に達する第2の開口、及び配線層に達する第3の開口を形成し、第2の開口に第1の電極層を形成し、第2の層間絶縁層の第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、第1の電極層上にスペーサを形成し、第3の開口に、絶縁層に接して第2の電極層を形成し、第1の層間絶縁層上に、絶縁層に接せずにシール材を形成する。

#### 【0014】

本発明の表示装置の作製方法の一は、画素領域に不純物領域を有する半導体層を形成し、接続領域及び半導体層上にゲート絶縁層を形成し、ゲート絶縁層上にゲート電極層及び導電層を形成し、ゲート電極層上及び導電層上に第1の層間絶縁層を形成し、ゲート絶縁層及び第1の層間絶縁層は不純物領域に達する第1の開口を有し、第1の開口、及びゲート電極層の一部を覆ってソース電極層又はドレイン電極層を形成し、第1の層間絶縁層上に導電層を覆って配線層を形成し、第1の層間絶縁層、配線層、ソース電極層及びドレイン電極層上に第2の層間絶縁層を形成し、第2の層間絶縁層にソース電極層又はドレイン電極層に達する第2の開口、及び配線層に達する第3の開口を形成し、第2の開口に第1の電極層を形成し、第2の層間絶縁層の第3の開口の上端部及び第1の電極層の一部を覆って絶縁層を形成し、第3の開口に、絶縁層に接して第2の電極層を形成し、第1の層間絶縁層上に、絶縁層に接せずにシール材を形成する。

#### 【0015】

上記構成において、スペーサと絶縁層とは、別工程で形成してもよいし、同材料を用いて、同工程で形成してもよい。

#### 【発明の効果】

#### 【0016】

本発明を用いると、信頼性の高い表示装置を簡略化した工程で作製することができる。よって、高精細、高画質な表示装置を低いコストで歩留まり良く製造することができる

10

20

30

40

50

## 【発明を実施するための最良の形態】

## 【0017】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

## 【0018】

## (実施の形態1)

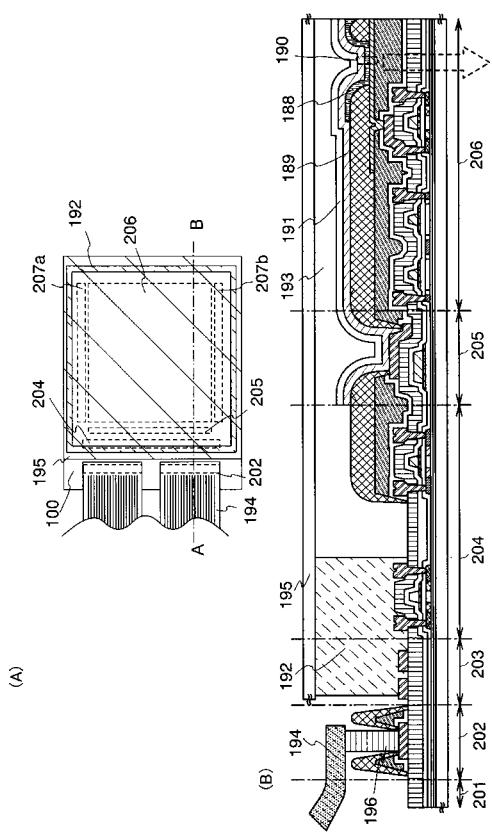

本実施の形態における薄膜トランジスタの作製方法を、図1乃至図3を用いて詳細に説明する。

## 【0019】

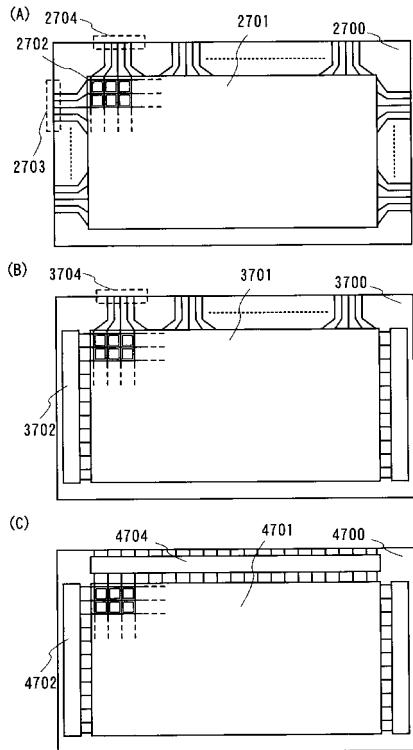

図16(A)は本発明に係る表示パネルの構成を示す上面図であり、絶縁表面を有する基板2700上に画素2702をマトリクス上に配列させた画素部2701、走査線側入力端子2703、信号線側入力端子2704が形成されている。画素数は種々の規格に従って設ければ良く、XGAであれば $1024 \times 768 \times 3$ (RGB)、UXGAであれば $1600 \times 1200 \times 3$ (RGB)、フルスペックハイビジョンに対応させるのであれば $1920 \times 1080 \times 3$ (RGB)とすれば良い。

## 【0020】

画素2702は、走査線側入力端子2703から延在する走査線と、信号線側入力端子2704から延在する信号線とが交差することで、マトリクス状に配設される。画素2702のそれぞれには、スイッチング素子とそれに接続する画素電極層が備えられている。スイッチング素子の代表的な一例はTFTであり、TFTのゲート電極層側が走査線と、ソース若しくはドレイン側が信号線と接続されることにより、個々の画素を外部から入力する信号によって独立して制御可能としている。

## 【0021】

TFTは、その主要な構成要素として、半導体層、ゲート絶縁層及びゲート電極層が挙げられ、半導体層に形成されるソース及びドレイン領域に接続する配線層がそれに付随する。構造的には基板側から半導体層、ゲート絶縁層及びゲート電極層を配設したトップゲート型と、基板側からゲート電極層、ゲート絶縁層及び半導体層を配設したボトムゲート型などが代表的に知られているが、本発明においてはそれらの構造のどのようなもの用いても良い。

## 【0022】

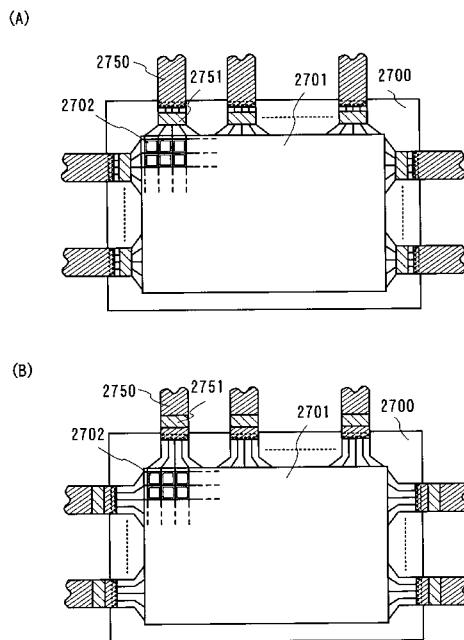

図16(A)は、走査線及び信号線へ入力する信号を、外付けの駆動回路により制御する表示パネルの構成を示しているが、図17(A)に示すように、COG(Chip on Glass)方式によりドライバIC2751を基板2700上に実装しても良い。また他の実装形態として、図17(B)に示すようなTAB(Tape Automated Bonding)方式を用いてもよい。ドライバICは単結晶半導体基板に形成されたものでも良いし、ガラス基板上にTFTで回路を形成したものであっても良い。図17において、ドライバIC2751は、FPC(Flexible printed circuit)2750と接続している。

## 【0023】

また、画素に設けるTFTを結晶性を有する半導体で形成する場合には、図16(B)に示すように走査線側駆動回路3702を基板3700上に形成することもできる。図16(B)において、画素部3701は、信号線側入力端子3704と接続した図16(A)と同様に外付けの駆動回路により制御する。画素に設けるTFTを移動度の高い、多結晶(微結晶)半導体、単結晶半導体などで形成する場合は、図16(C)は、画素部4701、走査線駆動回路4702と、信号線駆動回路4704を基板4700上に一体形

成することもできる。

#### 【0024】

図2に示すように、絶縁表面を有する基板100の上に下地膜として、スパッタリング法、PVD法(Physical Vapor Deposition)、減圧CVD法(LPCVD法)、またはプラズマCVD法等のCVD法(Chemical Vapor Deposition)などにより窒化酸化珪素膜(SiNO)を用いて下地膜101aを10~200nm(好ましくは50~100nm)形成し、酸化窒化珪素膜(SiON)を用いて下地膜101bを50~200nm(好ましくは100~150nm)積層する。本実施の形態では、プラズマCVD法を用いて下地膜101a、下地膜101bを形成する。基板100としてはガラス基板、石英基板やシリコン基板、金属基板、またはステンレス基板の表面に絶縁膜を形成したもの用いて良い。また、本実施の形態の処理温度に耐えうる耐熱性を有するプラスチック基板を用いててもよいし、フィルムのような可撓性基板を用いても良い。プラスチック基板としてはPET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)からなる基板、可撓性基板としてはアクリル等の合成樹脂を用いることができる。

#### 【0025】

下地膜としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを用いることができ、単層でも2層、3層といった積層構造でもよい。なお本明細書中において酸化窒化珪素とは酸素の組成比が窒素の組成比より大きい物質であり、窒素を含む酸化珪素とも言える。同様に、窒化酸化珪素とは、窒素の組成比が酸素の組成比より大きい物質であり、酸素を含む窒化珪素とも言える。本実施の形態では、基板上にSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O、N<sub>2</sub>及びH<sub>2</sub>を反応ガスとして窒化酸化珪素膜を膜厚50nm形成し、SiH<sub>4</sub>及びN<sub>2</sub>Oを反応ガスとして酸化窒化珪素膜を膜厚100nmで形成する。また窒化酸化珪素膜の膜厚を140nm、積層する酸化窒化珪素膜の膜厚を100nmとしてもよい。

#### 【0026】

次いで、下地膜上に半導体膜を形成する。半導体膜は25~200nm(好ましくは30~150nm)の厚さで公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜すればよい。本実施の形態では、非晶質半導体膜を、レーザ結晶化し、結晶性半導体膜とするものを用いるのが好ましい。

#### 【0027】

半導体膜を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体:AS」ともいう。)、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう。)半導体などを用いることができる。

#### 【0028】

SASは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5~20nmの結晶領域を観測することが出来、珪素を主成分とする場合にはラマンスペクトルが520cm<sup>-1</sup>よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。未結合手(ダンギリングボンド)を終端化させるため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。SASは、珪化物気体をグロー放電分解(プラズマCVD)して形成する。珪化物気体としては、SiH<sub>4</sub>、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることが可能である。またF<sub>2</sub>、GeF<sub>4</sub>を混合させても良い。この珪化物気体をH<sub>2</sub>、又は、H<sub>2</sub>とHe、Ar、Kr、Neから選ばれた一種または複数種の希ガス元素で希釈しても良い。希釈率は2~1000倍の範囲、圧力は概略0.1Pa~133Paの範囲、電源周波数は1MHz~120MHz、好ましくは13MHz~60MHzである。基板加熱温度は300以下が好ましく、100~200の基板加熱温度

10

20

30

40

50

でも形成可能である。ここで、主に成膜時に取り込まれる不純物元素として、酸素、窒素、炭素などの大気成分に由来する不純物は  $1 \times 10^{20} \text{ cm}^{-3}$  以下とすることが望ましく、特に、酸素濃度は  $5 \times 10^{19} \text{ cm}^{-3}$  以下、好ましくは  $1 \times 10^{19} \text{ cm}^{-3}$  以下となるようになることが好ましい。また、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好な S A S が得られる。また半導体膜としてフッ素を含む珪化物気体より形成される S A S 層に水素を含む珪化物気体より形成される S A S 層を積層してもよい。

## 【0029】

非晶質半導体としては、代表的には水素化アモルファスシリコン、結晶性半導体としては代表的にはポリシリコンなどがあげられる。ポリシリコン（多結晶シリコン）には、800 以上的プロセス温度を経て形成されるポリシリコンを主材料として用いた所謂高温ポリシリコンや、600 以下のプロセス温度で形成されるポリシリコンを主材料として用いた所謂低温ポリシリコン、また結晶化を促進する元素などを添加し結晶化させたポリシリコンなどを含んでいる。もちろん、前述したように、セミアモルファス半導体又は半導体膜の一部に結晶相を含む半導体を用いることもできる。

## 【0030】

30 インチ、40 インチのような大型の基板を用いる場合は、アモルファスシリコンのような非晶質半導体を用いると、工程が複雑化せず生産性がよい。

## 【0031】

半導体膜に、結晶性半導体膜を用いる場合、その結晶性半導体膜の作製方法は、公知の方法（レーザ結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等）を用いれば良い。また、S A S である微結晶半導体をレーザ照射して結晶化し、結晶性を高めることもできる。結晶化を助長する元素を導入しない場合は、非晶質半導体膜にレーザ光を照射する前に、窒素雰囲気下 500 で 1 時間加熱することによって非晶質半導体膜の含有水素濃度を  $1 \times 10^{20} \text{ atoms / cm}^3$  以下にまで放出させる。これは水素を多く含んだ非晶質半導体膜にレーザ光を照射すると非晶質半導体膜が破壊されてしまうからである。結晶化のための加熱処理は、加熱炉、レーザ照射、若しくはランプから発する光の照射（ランプアニールともいう）などを用いることができる。加熱方法として加熱した気体を用いる G R T A (Gas Rapid Thermal Anneal) 法、ランプによる光を用いる L R T A (Lamp Rapid Thermal Anneal) 法等の R T A 法がある。

## 【0032】

非晶質半導体膜への金属元素の導入の仕方としては、当該金属元素を非晶質半導体膜の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタ法、C V D 法、プラズマ処理法（プラズマ C V D 法も含む）、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体膜の表面のぬれ性を改善し、非晶質半導体膜の表面全体に水溶液を行き渡らせるため、酸素雰囲気中の U V 光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

## 【0033】

連続発振が可能な固体レーザを用い、基本波の第 2 高調波～第 4 高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。例えば、代表的には、N d : Y V O<sub>4</sub> レーザ（基本波 1064 nm）の第 2 高調波（532 nm）や第 3 高調波（355 nm）を用いるのが望ましい。具体的には、連続発振の Y V O<sub>4</sub> レーザから射出されたレーザ光を非線形光学素子により高調波に変換し、出力数 W 以上のレーザ光を得る。そして、好ましくは光学系により照射面にて矩形状または橍円形状のレーザ光に成形して、半導体膜に照射する。このときのエネルギー密度は 0.001 ~ 100 MW / cm<sup>2</sup> 程度（好ましくは 0.1 ~ 10 MW / cm<sup>2</sup>）が必要である。そして、走査速度を 0.5 ~ 2000 cm / sec 程度（好ましくは 10 ~ 200 cm / sec）とし、照射する。

## 【0034】

10

20

30

40

50

レーザのビーム形状は、線状とすると好ましい。その結果、スループットを向上させることができる。またさらにレーザは、半導体膜に対して入射角（ $0 < \theta < 90$  度）を持たせて照射させるとよい。レーザの干渉を防止することができるからである。

#### 【0035】

このようなレーザと、半導体膜とを相対的に走査することにより、レーザ照射を行うことができる。またレーザ照射において、ビームを精度よく重ね合わせたり、レーザ照射開始位置やレーザ照射終了位置を制御するため、マーカーを形成することもできる。マーカーは非晶質半導体膜と一緒に、基板上へ形成すればよい。

#### 【0036】

なおレーザは、連続発振またはパルス発振の気体レーザ、固体レーザ、銅蒸気レーザまたは金蒸気レーザなどを用いることができる。気体レーザとして、エキシマレーザ、Arレーザ、Krレーザ、He-Cdレーザなどがあり、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザなどが挙げられる。

#### 【0037】

また、パルス発振のレーザ光の発振周波数を0.5MHz以上とし、通常用いられている数十Hz～数百Hzの周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行っても良い。パルス発振でレーザ光を半導体膜に照射してから半導体膜が完全に固化するまでの時間は数十nsec～数百nsecと言われている。よって上記周波数帯を用いることで、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できる。したがって、半導体膜中において固液界面を連続的に移動させることができるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜が形成される。具体的には、含まれる結晶粒の走査方向における幅が10～30μm、走査方向に対して垂直な方向における幅が1～5μm程度の結晶粒の集合を形成することができる。該走査方向に沿って長く伸びた単結晶の結晶粒を形成することで、少なくとも薄膜トランジスタのチャネル方向には結晶粒界のほとんど存在しない半導体膜の形成が可能となる。

#### 【0038】

また、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。これにより、レーザ光の照射により半導体表面の荒れを抑えることができ、界面準位密度のばらつきによって生じるしきい値のばらつきを抑えることができる。

#### 【0039】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

#### 【0040】

本実施の形態では、下地膜101b上に、非晶質半導体膜を形成し、非晶質半導体膜を結晶化させることによって結晶性半導体膜を形成する。非晶質半導体膜としては、SiH<sub>4</sub>、H<sub>2</sub>の反応ガスにより形成する非晶質珪素を用いる。本実施の形態において、下地膜101a、下地膜101b、非晶質半導体膜は、同チャンバー内で真空を破らずに（真空状態を保ったまま）330の同一温度下で、反応ガスを切り替えながら連続的に形成する。

#### 【0041】

非晶質半導体膜上に形成された酸化膜を除去した後、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を1～5nm形成する。本実施の形態では、結晶化を助長する元素としてNiを用いる。Ni酢酸塩10ppmを含有した水溶液をスピノコーティング法により塗布する。

#### 【0042】

本実施の形態では、熱処理をRTA法により650で6分間行った後、半導体膜上に形成される酸化膜を除去し、レーザ光を照射する。非晶質半導体膜は以上の結晶化処理により結晶化し、結晶性半導体膜として形成される。

#### 【0043】

10

20

30

40

50

金属元素を用いた結晶化を行った場合、金属元素を低減、又は除去するためにゲッタリング工程を施す。本実施の形態では、非晶質半導体膜をゲッタリングシンクとして金属元素を捕獲する。まず、結晶性半導体膜上に酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を形成する。酸化膜は加熱処理によって厚膜化することが望ましい。本実施の形態では、酸化膜形成後に、RTA法により650で6分間熱処理を行うことによって、酸化膜の厚膜化を行う。次いでプラズマCVD法（本実施の形態における条件350W、35Pa）を用いて、非晶質半導体膜を30nmの膜厚で形成する。

#### 【0044】

その後、RTA法により650で6分間熱処理を行い、金属元素を低減、又は除去する。熱処理は窒素雰囲気下で行ってもよい。そして、ゲッタリングシンクとなっていた非晶質半導体膜、及び非晶質半導体膜上に形成された酸化膜をフッ酸等により除去し、金属元素が低減、又は除去された結晶性半導体膜102を得ることができる（図2（A）参照。）。本実施の形態では、ゲッタリングシンクとなった非晶質半導体膜の除去をTMAH（Tetramethyl ammonium hydroxide）を用いて行う。

#### 【0045】

このようにして得られた半導体膜に対して、薄膜トランジスタのしきい値電圧を制御するために微量な不純物元素（ボロンまたはリン）のドーピングを行ってもよい。この不純物元素のドーピングは、結晶化工程の前の非晶質半導体膜に行ってもよい。非晶質半導体膜の状態で不純物元素をドーピングすると、その後の結晶化のための加熱処理によって、不純物の活性化も行うことができる。また、ドーピングの際に生じる欠陥等も改善することができる。

#### 【0046】

次に結晶性半導体膜102をマスクを用いて所望の形状に加工する。本実施の形態では結晶性半導体膜102上に形成された酸化膜を除去した後、新たに酸化膜を形成する。そして、フォトマスクを作製し、フォトリソグラフィ法を用いた加工処理により、半導体層103、半導体層104、半導体層105、及び半導体層106を形成する。

#### 【0047】

エッチング加工は、プラズマエッチング（ドライエッチング）又はウエットエッチングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッチングが適している。エッチングガスとしては、CF<sub>4</sub>、NF<sub>3</sub>などのフッ素を含むガス、Cl<sub>2</sub>、BCl<sub>3</sub>などの塩素を含むガスを用い、HeやArなどの不活性ガスを適宜加えても良い。また、大気圧放電のエッチング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

#### 【0048】

本発明において、配線層若しくは電極層を形成する導電層や、所定のパターンを形成するためのマスク層などを、液滴吐出法のような選択的にパターンを形成できる方法により形成してもよい。液滴吐出（噴出）法（その方式によっては、インクジェット法とも呼ばれる。）は、特定の目的に調合された組成物の液滴を選択的に吐出（噴出）して所定のパターン（導電層や絶縁層など）を形成することができる。この際、被形成領域にぬれ性や密着性を制御する処理を行ってもよい。また、パターンが転写、または描写できる方法、例えば印刷法（スクリーン印刷やオフセット印刷などパターンが形成される方法）なども用いることができる。

#### 【0049】

本実施の形態において、用いるマスクは、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサンポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いることもできる。或いは、感光剤を含む市販のレジスト材料を用いてもよく、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナ

10

20

30

40

50

フトキノンジアジド化合物を含むレジスト、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを含むレジスト用いてもよい。液滴吐出法を用いる場合、いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

#### 【0050】

半導体層上の酸化膜を除去し、半導体層103、半導体層104、半導体層105、及び半導体層106を覆うゲート絶縁層107を形成する。ゲート絶縁層107はプラズマCVD法またはスパッタ法などを用い、厚さを10～150nmとして珪素を含む絶縁膜で形成する。ゲート絶縁層107としては、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の公知の材料で形成すればよく、積層でも単層でもよい。本実施の形態では、ゲート絶縁層は窒化珪素膜、酸化珪素膜、窒化珪素膜の3層の積層を用いる。またそれらや、酸化窒化珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を用いるとよい。さらに半導体層とゲート絶縁層の間に、膜厚1～100nm、好ましくは1～10nm、さらに好ましくは2～5nmである膜厚の薄い酸化珪素膜を形成してもよい。薄い酸化珪素膜の形成方法としては、GRTA法、LRTA法等を用いて半導体領域表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することができる。なお、低い成膜温度でゲートリーク電流が少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

#### 【0051】

次いで、ゲート絶縁層107上にゲート電極層として用いる膜厚20～100nmの第1の導電膜108と、膜厚100～400nmの第2の導電膜109とを積層して形成する(図2(B)参照。)。第1の導電膜108及び第2の導電膜109は、スパッタリング法、蒸着法、CVD法等の公知の手法により形成することができる。第1の導電膜108及び第2の導電膜109はタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジウム(Nd)から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第1の導電膜108及び第2の導電膜109としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、第1の導電膜として膜厚50nmのタングステン膜、第2の導電膜として膜厚500nmのアルミニウムとシリコンの合金(Al-Si)膜、第3の導電膜として膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al-Si)膜に代えてアルミニウムとチタンの合金膜(Al-Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。本実施の形態では、第1の導電膜106として窒化タンタル(TaN)を膜厚30nm形成し、第2の導電膜107としてタングステン(W)を膜厚370nm形成する。

#### 【0052】

次に、フォトリソグラフィ法を用いてレジストからなるマスク110a、マスク110b、マスク110c、マスク110d、及びマスク110fを形成し、第1の導電膜108及び第2の導電膜109を所望の形状に加工し、第1のゲート電極層121、第1のゲート電極層122、導電層123、第1のゲート電極層124、第1のゲート電極層125、及び第1のゲート電極層126、並びに導電層111、導電層112、導電層113、導電層114、導電層115、及び導電層116を形成する(図2(C)参照。)。ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を用い、エッチング条件(コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等)を適宜調節することにより、第1のゲート電極層121、第1のゲート電極層122、導電層123、第1のゲート電極層124、第1のゲート電極層125、及び第1のゲート電極層126、並びに導電層111、導電層112、導電層111

10

20

30

40

50

3、導電層114、導電層115、及び導電層116を所望のテーパー形状を有するようにエッティングすることができる。また、テーパー形状は、マスク110a、マスク110b、マスク110c、マスク110d、及びマスク110fの形状によっても角度等を制御することができる。なお、エッティング用ガスとしては、C<sub>l</sub><sub>2</sub>、B<sub>C</sub>l<sub>3</sub>、S*i*C<sub>l</sub><sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。本実施の形態では、CF<sub>4</sub>、Cl<sub>2</sub>、O<sub>2</sub>からなるエッティング用ガスを用いて第2の導電膜109のエッティングを行い、連続してCF<sub>4</sub>、Cl<sub>2</sub>からなるエッティング用ガスを用いて第1の導電膜108をエッティングする。

#### 【0053】

次に、マスク110a、マスク110b、マスク110c、マスク110d、及びマスク110fを用いて、導電層111、導電層112、導電層113、導電層114、導電層115、及び導電層116を所望の形状に加工する。このとき、導電層を形成する第2の導電膜109と、第1のゲート電極層を形成する第1の導電膜108との選択比の高いエッティング条件で、導電層をエッティングする。このエッティングによって、導電層111、導電層112、導電層113、導電層114、導電層115、及び導電層116をエッティングし、第2のゲート電極層131、第2のゲート電極層132、導電層133、第2のゲート電極層134、第2のゲート電極層135、及び第2のゲート電極層136を形成する。本実施の形態では、第3導電層もテーパー形状を有しているが、そのテーパー角度は、第1のゲート電極層121、第1のゲート電極層122、導電層123、第1のゲート電極層124、第1のゲート電極層125、及び第1のゲート電極層126の有するテーパー角度より大きい。なおテーパー角度とは第1のゲート電極層、第2のゲート電極層、導電層表面に対する側面の角度である。よって、テーパー角度を大きくし、90度の場合導電層は垂直な側面を有しており、テーパー形状を有さなくなる。本実施の形態では、第2のゲート電極層を形成するためのエッティング用ガスとしてCl<sub>2</sub>、SF<sub>6</sub>、O<sub>2</sub>を用いる。

#### 【0054】

本実施の形態では第1のゲート電極層、導電層、及び第2のゲート電極層を、テーパー形状を有する様に形成するため、2層のゲート電極層両方がテーパー形状を有している。しかし、本発明はそれに限定されず、ゲート電極層の一層のみがテーパー形状を有し、他方は異方性エッティングによって垂直な側面を有していてもよい。本実施の形態のように、テーパー角度も積層するゲート電極層間で異なっていても良いし、同一でもよい。テーパー形状を有することによって、その上に積層する膜の被覆性が向上し、欠陥が軽減されるので信頼性が向上する。

#### 【0055】

以上の工程によって、周辺駆動回路領域204に第1のゲート電極層121及び第2のゲート電極層131からなるゲート電極層117、第1のゲート電極層122及び第2のゲート電極層132からなるゲート電極層118、画素領域206に第1のゲート電極層124及び第2のゲート電極層134からなるゲート電極層127、第1のゲート電極層125及び第2のゲート電極層135からなるゲート電極層128、第1のゲート電極層126及び第2のゲート電極層136からなるゲート電極層129、接続領域205に導電層123及び導電層133からなる導電層130を形成することができる（図2（D）参照。）。本実施の形態では、ゲート電極層の形成をドライエッティングで行うがウェットエッティングでもよい。

#### 【0056】

ゲート電極層を形成する際のエッティング工程によって、ゲート絶縁層107は多少エッティングされ、膜厚が減る（膜厚が薄くなる、いわゆる膜減り）ことがある。

#### 【0057】

ゲート電極層を形成する際、ゲート電極層の幅を細くすることによって、高速動作が可能な薄膜トランジスタを形成することができる。ゲート電極層をチャネル方向の幅を細

10

20

30

40

50

く形成する2つの方法を以下に示す。

#### 【0058】

第1の方法はゲート電極層のマスクを形成した後、マスクを幅方向にエッチング、アッティング等により細くして、さらに幅の細いマスクを形成する。あらかじめ幅細い形状に形成されたマスクを用いることによって、ゲート電極層も幅細い形状に形成することができる。

#### 【0059】

次に、第2の方法はマスクを形成し、そのマスクを用いてゲート電極層を形成する。次に得られたゲート電極層を幅方向にさらにサイドエッチングして細らせる。よって最終的に幅の細いゲート電極層を形成することができる。以上の工程を経ることによって、後にチャネル長の短い薄膜トランジスタを形成することが可能であり、高速度動作が可能な薄膜トランジスタを作製することが可能である。

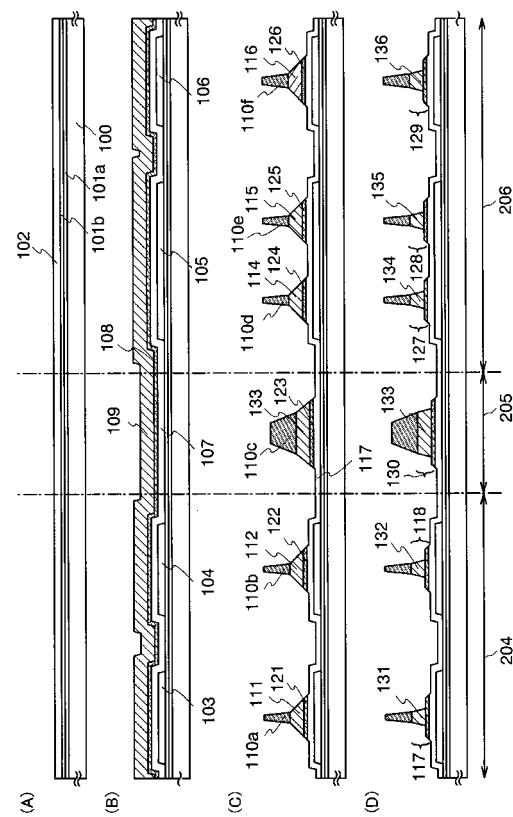

#### 【0060】

次に、ゲート電極層117、ゲート電極層118、ゲート電極層127、ゲート電極層128、ゲート電極層129、導電層130をマスクとして、n型を付与する不純物元素151を添加し、第1のn型不純物領域140a、第1のn型不純物領域140b、第1のn型不純物領域141a、第1のn型不純物領域141b、第1のn型不純物領域142a、第1のn型不純物領域142b、第1のn型不純物領域142c、第1のn型不純物領域143a、第1のn型不純物領域143bを形成する(図3(A)参照。)。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン(PH<sub>3</sub>)(ドーピングガスはPH<sub>3</sub>を水素(H<sub>2</sub>)で希釈しており、ガス中のPH<sub>3</sub>の比率は5%)を用い、ガス流量80sccm、ビーム電流54μA/cm、加速電圧50kV、添加するドーズ量7.0×10<sup>13</sup>ions/cm<sup>2</sup>条件下でドーピングを行う。ここでは、第1のn型不純物領域140a、第1のn型不純物領域140b、第1のn型不純物領域141a、第1のn型不純物領域141b、第1のn型不純物領域142a、第1のn型不純物領域142b、第1のn型不純物領域142c、第1のn型不純物領域143a、第1のn型不純物領域143bに、n型を付与する不純物元素が1×10<sup>17</sup>~5×10<sup>18</sup>/cm<sup>3</sup>程度の濃度で含まれるように添加する。本実施の形態では、n型を付与する不純物元素としてリン(P)を用いる。

#### 【0061】

本実施の形態では、不純物領域がゲート絶縁層を介してゲート電極層と重なる領域をlov領域と示し、不純物領域がゲート絶縁層を介してゲート電極層と重ならない領域をloff領域と示す。図3では、不純物領域においてハッチングと白地で示されているが、これは、白地部分に不純物元素が添加されていないということを示すのではなく、この領域の不純物元素の濃度分布がマスクやドーピング条件を反映していることを直感的に理解できるようにしたためである。なお、このことは本明細書の他の図面においても同様である。

#### 【0062】

次に半導体層103、半導体層105の一部、半導体層106を覆うマスク153a、マスク153b、マスク153c、及びマスク153dを形成する。マスク153a、マスク153b、マスク153c、マスク153d、第2のゲート電極層132をマスクとしてn型を付与する不純物元素152を添加し、第2のn型不純物領域144a、第2のn型不純物領域144b、第3のn型不純物領域145a、第3のn型不純物領域145b、第2のn型不純物領域147a、第2のn型不純物領域147b、第2のn型不純物領域147c、第3のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dが形成される。本実施の形態では、不純物元素を含むドーピングガスとしてPH<sub>3</sub>(ドーピングガスはPH<sub>3</sub>を水素(H<sub>2</sub>)で希釈しており、ガス中のPH<sub>3</sub>の比率は5%)を用い、ガス流量80sccm、ビーム電流540μA/cm、加速電圧70kV、添加するドーズ量5.0×10<sup>15</sup>ions/cm<sup>2</sup>の条件下でドーピングを行う。ここでは、第2のn型不純物領域144a、第2

10

20

30

40

50

の n 型不純物領域 144b に n 型を付与する不純物元素が  $5 \times 10^{19} \sim 5 \times 10^{20} / \text{cm}^3$  程度の濃度で含まれるように添加する。第 3 の不純物領域 145a、第 3 の不純物領域 145b は、第 3 の n 型不純物領域 148a、第 3 の n 型不純物領域 148b、第 3 の n 型不純物領域 148c、第 3 の n 型不純物領域 148d と同程度、もしくは少し高めの濃度で n 型を付与する不純物元素を含むように形成される。また、半導体層 104 にチャネル形成領域 146、半導体層 105 にチャネル形成領域 149a 及びチャネル形成領域 149b が形成される。

#### 【 0 0 6 3 】

第 2 の n 型不純物領域 144a、第 2 の n 型不純物領域 144b、第 2 の n 型不純物領域 147a、第 2 の n 型不純物領域 147b、第 2 の n 型不純物領域 147c は高濃度 n 型不純物領域であり、ソース、ドレインとして機能する。一方、第 3 の n 型不純物領域 145a、第 3 の n 型不純物領域 145b、第 3 の n 型不純物領域 148a、第 3 の n 型不純物領域 148b、第 3 の n 型不純物領域 148c、第 3 の n 型不純物領域 148d は低濃度不純物領域であり、LDD (Lightly Doped Drain) 領域となる。n 型不純物領域 145a、n 型不純物領域 145b は、ゲート絶縁層 107 を介して、第 1 のゲート電極層 122 に覆われているので Lov 領域であり、ドレイン近傍の電界を緩和し、ホットキャリアによるオン電流の劣化を抑制することが可能である。この結果、高速動作が可能な薄膜トランジスタを形成することができる。一方、第 3 の n 型不純物領域 148a、第 3 の n 型不純物領域 148b、第 3 の n 型不純物領域 148c、第 3 の n 型不純物領域 148d はゲート電極層 127、ゲート電極層 128 に覆われていない Loff 領域に形成されるため、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐとともに、オフ電流を低減する効果がある。この結果、信頼性の高く、低消費電力の半導体装置を作製することが可能である。

#### 【 0 0 6 4 】

次に、マスク 153a、マスク 153b、マスク 153c 及びマスク 153d を除去し、半導体層 103、半導体層 105 を覆うマスク 155a、マスク 155b を形成する。マスク 155a、マスク 155b、ゲート電極層 117 及びゲート電極層 129 をマスクとして p 型を付与する不純物元素 154 を添加し、第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b、第 1 の p 型不純物領域 163a、第 1 の p 型不純物領域 163b、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b、第 2 の p 型不純物領域 164a、第 2 の p 型不純物領域 164b が形成される。本実施の形態では、不純物元素としてボロン (B) を用いるため、不純物元素を含むドーピングガスとしてジボラン ( $\text{B}_2\text{H}_6$ ) (ドーピングガスは  $\text{B}_2\text{H}_6$  を水素 ( $\text{H}_2$ ) で希釈しており、ガス中の  $\text{B}_2\text{H}_6$  の比率は 15 %) を用い、ガス流量 70 sccm、ビーム電流  $180 \mu\text{A}/\text{cm}$ 、加速電圧 80 kV、添加するドーズ量  $2.0 \times 10^{15} \text{ ions/cm}^2$  でドーピングを行う。ここでは、第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b、第 1 の p 型不純物領域 163a、第 1 の p 型不純物領域 163b、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b、第 2 の p 型不純物領域 164a、第 2 の p 型不純物領域 164b に p 型を付与する不純物元素が  $1 \times 10^{20} \sim 5 \times 10^{21} / \text{cm}^3$  程度の濃度で含まれるように添加する。本実施の形態では、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b、第 2 の p 型不純物領域 164a、第 2 の p 型不純物領域 164b は、ゲート電極層 117 及びゲート電極層 129 の形状を反映し、自己整合的に第 1 の p 型不純物領域 160a、第 1 の p 型不純物領域 160b、第 1 の p 型不純物領域 163a、第 1 の p 型不純物領域 163b より低濃度となるように形成する。また、半導体層 103 にチャネル形成領域 162、半導体層 106 にチャネル形成領域 165 が形成される。

#### 【 0 0 6 5 】

第 2 の n 型不純物領域 144a、第 2 の n 型不純物領域 144b、第 2 の n 型不純物領域 147a、第 2 の n 型不純物領域 147b、第 2 の n 型不純物領域 147c は高濃度 n 型不純物領域であり、ソース、ドレインとして機能する。一方、第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b、第 2 の p 型不純物領域 164a、第 2 の p 型不純物領域 164b は、

10

20

30

40

50

不純物領域 164b は低濃度不純物領域であり、 LDD (Lightly Doped Drain) 領域となる。第 2 の p 型不純物領域 161a、第 2 の p 型不純物領域 161b、第 2 の p 型不純物領域 164a、第 2 の p 型不純物領域 164b は、ゲート絶縁層 107 を介して、第 1 のゲート電極層 121、第 1 のゲート電極層 126 に覆われているので Lov 領域であり、ドレイン近傍の電界を緩和し、ホットキャリアによるオン電流の劣化を抑制することが可能である。

#### 【0066】

マスク 155a、マスク 155b を O<sub>2</sub> アッシングやレジスト剥離液により除去し、酸化膜も除去する。その後、ゲート電極層の側面を覆うように、絶縁膜、いわゆるサイドウォールを形成してもよい。サイドウォールは、プラズマ CVD 法や減圧 CVD (LPCVD) 法を用いて、珪素を有する絶縁膜により形成することができる。10

#### 【0067】

不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と半導体層との界面へのプラズマダメージを回復することができる。

#### 【0068】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、絶縁膜 167 と絶縁膜 168 との積層構造とする（図 4 (A) 参照。）。絶縁膜 167 として窒化酸化珪素膜を膜厚 200 nm 形成し、絶縁膜 168 として酸化窒化絶縁膜を膜厚 800 nm 形成し、積層構造とする。また、ゲート電極層、ゲート絶縁層を覆って、酸化窒化珪素膜を膜厚 30 nm 形成し、窒化酸化珪素膜を膜厚 140 nm 形成し、酸化窒化珪素膜を膜厚 800 nm 形成し、3 層の積層構造としてもよい。本実施の形態では、絶縁膜 167 及び絶縁膜 168 を下地膜と同様にプラズマ CVD 法を用いて連続的に形成する。絶縁膜 108 は窒化珪素膜に限定されるものでなく、スパッタ法、またはプラズマ CVD を用いた窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または 3 層以上の積層構造として用いても良い。20

#### 【0069】

さらに、窒素雰囲気中で、300 ~ 550 で 1 ~ 12 時間の熱処理を行い、半導体層を水素化する工程を行う。好ましくは、400 ~ 500 で行う。この工程は層間絶縁層である絶縁膜 167 に含まれる水素により半導体層のダングリングボンドを終端する工程である。本実施の形態では、410 度（）で加熱処理を行う。30

#### 【0070】

絶縁膜 167、絶縁膜 168 としては他に窒化アルミニウム (AlN)、酸化窒化アルミニウム (AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム (AlNO) または酸化アルミニウム、ダイアモンドライカーボン (DLC)、窒素含有炭素膜 (CN)、ポリシラザン、その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si 結合を含む樹脂に相当する。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテンを用いることができる。平坦性のよい塗布法によって形成される塗布膜を用いてもよい。40

#### 【0071】

次いで、レジストからなるマスクを用いて絶縁膜 167、絶縁膜 168、ゲート絶縁層 107 に半導体層に達するコンタクトホール（開口）を形成する。エッチングは、用いる材料の選択比によって、一回で行っても複数回行っても良い。本実施の形態では、酸化窒化珪素膜である絶縁膜 168 と、窒化酸化珪素膜である絶縁膜 167 及びゲート絶縁層 107 と選択比が取れる条件で、第 1 のエッチングを行い、絶縁膜 168 を除去する。次50

に第2のエッチングによって、絶縁膜167及びゲート絶縁層107を除去し、ソース領域又はドレイン領域である第1のp型不純物領域160a、第1のp型不純物領域160b、第1のp型不純物領域163a、第1のp型不純物領域163b、第2のn型不純物領域144a、第2のn型不純物領域144b、第2のn型不純物領域147a、第2のn型不純物領域147bに達する開口(開口部ともいう)を形成する。本実施の形態では、第1のエッチングをウェットエッチングによって行い、第2のエッチングをドライエッティングによって行う。ウェットエッチングのエッチャントは、フッ素水素アンモニウム及びフッ化アンモニウムを含む混合溶液のようなフッ酸系の溶液を用いるとよい。エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素を含むガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素を含むガス又はO<sub>2</sub>を適宜用いることができる。また用いるエッチング用ガスに不活性気体を添加してもよい。添加する不活性元素としては、He、Ne、Ar、Kr、Xeから選ばれた一種または複数種の元素を用いることができる。

#### 【0072】

開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層169a、ソース電極層又はドレイン電極層169b、ソース電極層又はドレイン電極層170a、ソース電極層又はドレイン電極層170b、ソース電極層又はドレイン電極層171a、ソース電極層又はドレイン電極層171b、ソース電極層又はドレイン電極層172a、ソース電極層又はドレイン電極層172b、配線156を形成する。ソース電極層又はドレイン電極層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電界メッキ法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属又はその合金、若しくはその金属窒化物を用いて形成する。また、これらから選ばれた材料の積層構造としても良い。本実施の形態では、チタン(Ti)を膜厚100nm形成し、アルミニウムとシリコンの合金(Al-Si)を膜厚700nm形成し、チタン(Ti)を膜厚200nm形成し、所望な形状に加工する。

#### 【0073】

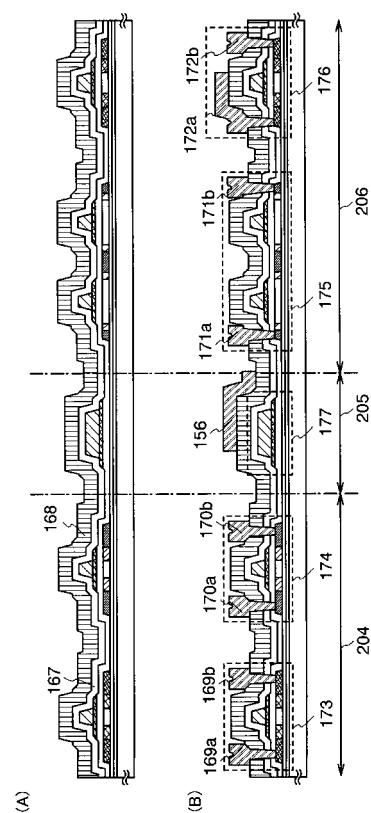

以上の工程で周辺駆動回路領域204にLoV領域にp型不純物領域を有するpチャネル型薄膜トランジスタ173、LoV領域にnチャネル型不純物領域を有するnチャネル型薄膜トランジスタ174を、接続領域に、導電層177を、画素領域206にLoff領域にn型不純物領域を有するマルチチャネル型のnチャネル型薄膜トランジスタ175、LoV領域にp型不純物領域を有するpチャネル型薄膜トランジスタ176を有するアクティブマトリクス基板を作製することができる(図4(B)参照。)。

#### 【0074】

そして、アクティブマトリクス基板は、自発光素子を有する発光装置、液晶素子を有する液晶表示装置、その他の表示装置に用いることができる。またCPU(中央演算処理装置)に代表される各種プロセッサやIDチップを搭載したカード等の半導体装置に用いることができる。

#### 【0075】

本実施の形態に限定されず、薄膜トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、周辺駆動回路領域の薄膜トランジスタも、シングルゲート構造、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

#### 【0076】

なお、本実施の形態で示した薄膜トランジスタの作製方法に限らず、トップゲート型(プレーナー型)、ボトムゲート型(逆スタガ型)、あるいはチャネル領域の上下にゲート絶縁膜を介して配置された2つのゲート電極層を有する、デュアルゲート型やその他の

10

20

30

40

50

構造においても適用できる。

#### 【0077】

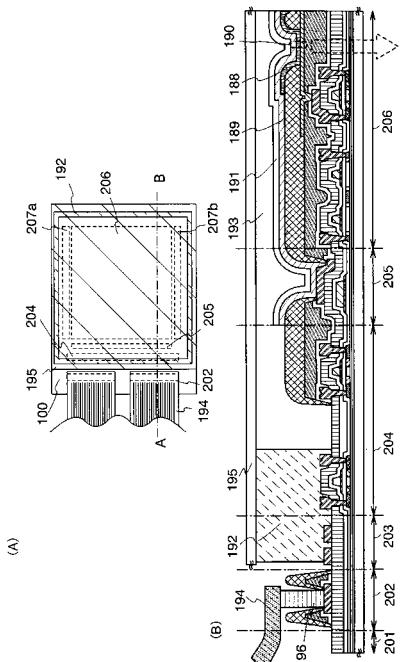

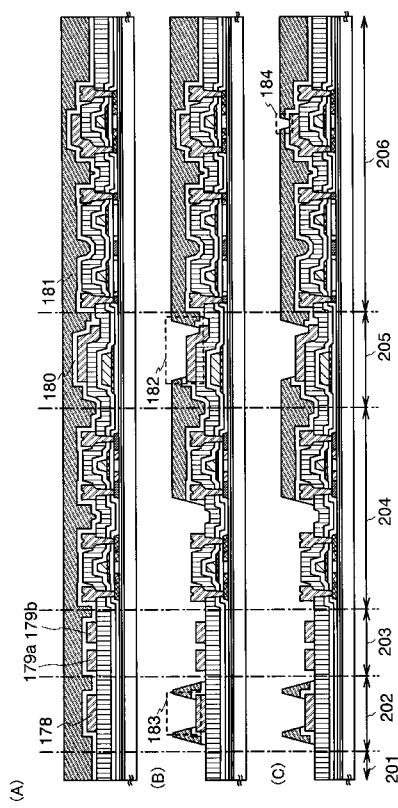

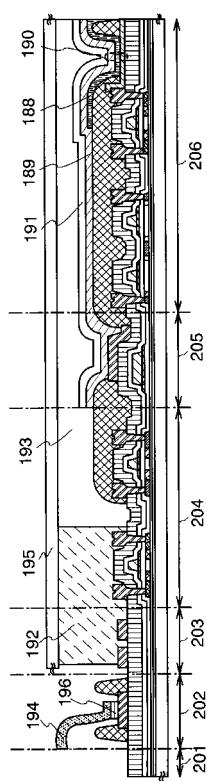

次に第2の層間絶縁層として絶縁膜180及び絶縁膜181を形成する(図5(A)参照。)。図5は、表示装置の作製工程を示しており、スクライブによる切り離しのための切り離し領域201、FPCの貼り付け部である外部端子接続領域202、周辺部の引き回し配線領域である配線領域203、周辺駆動回路領域204、接続領域205、画素領域206である。配線領域203には配線179a、配線179bが設けられ、外部端子接続領域202には、外部端子と接続する端子電極層178が設けられている。

#### 【0078】

絶縁膜180、絶縁膜181としては酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイアモンドライカーボン(DLC)、窒素含有炭素膜(CN)、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜、ポリシリコン、その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シリコサン樹脂を用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料としては、感光性、非感光性どちらでも良く、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、低誘電率であるLow-k材料を用いることができる。

#### 【0079】

本実施の形態では、絶縁膜180としてCVD法を用いて酸化窒化珪素膜を膜厚200nm形成する。平坦化のために設ける層間絶縁層としては、耐熱性および絶縁性が高く、且つ、平坦化率の高いものが要求されるので、絶縁膜181の形成方法としては、スピノコート法で代表される塗布法を用いると好ましい。

#### 【0080】

本実施の形態では、絶縁膜181の材料としては、シリコサン樹脂材料を用いた塗布膜を用いる。焼成した後の膜は、アルキル基を含む酸化珪素膜(SiO<sub>x</sub>)(x,y=1,2,...)と呼べる。このアルキル基を含む酸化珪素膜は、300以上の加熱処理にも耐えうるものである。

#### 【0081】

絶縁膜180、絶縁膜181は、ディップ、スプレー塗布、ドクターナイフ、ロールコーダー、カーテンコーダー、ナイフコーダー、CVD法、蒸着法等を採用して形成することができる。液滴吐出法により絶縁膜180、絶縁膜181を形成してもよい。液滴吐出法を用いた場合には材料液を節約することができる。また、液滴吐出法のようにパターンが転写、または描写できる方法、例えば印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)なども用いることができる。

#### 【0082】

次に、図5(B)に示すように、第2の層間絶縁層である絶縁膜180及び絶縁膜181に開口部を形成する。絶縁膜180及び絶縁膜181は、接続領域205、配線領域203、外部端子接続領域202、切り離し領域201等では広面積にエッチングする必要がある。しかし、画素領域206においては開口面積が、接続領域205等の開口面積と比較して非常に小さく、微細なものとなる。従って、画素領域の開口部形成用のフォトリソグラフィ工程と、接続領域の開口部形成用のフォトリソグラフィ工程とを設けることにより、エッチング条件のマージンをより広げることができる。その結果、歩留まりを向上させることができる。またエッチング条件のマージンが広がることにより、画素領域に形成されるコンタクトホールを高精度に形成することができる。

#### 【0083】

具体的には、接続領域205、配線領域203、外部端子接続領域202、切り離し領域201、周辺駆動回路領域204の一部に設けられた絶縁膜180及び絶縁膜181に広面積な開口部を形成する。そのため、画素領域206、接続領域205の一部、及び周辺駆動回路領域204の一部の絶縁膜180及び絶縁膜181を覆うようにマスクを形

10

20

30

40

50

成する。エッティングは平行平板R I E装置やI C Pエッティング装置を用いることができる。なおエッティング時間は、配線層や第1の層間絶縁層がオーバーエッティングされる程度に設定するとよい。このようにオーバーエッティングされる程度に設定すると、基板内の膜厚バラツキと、エッティングレートのバラツキを低減することができる。このようにして接続領域205には開口部182が、外部端子接続領域202には開口部183がそれぞれ形成される。

#### 【0084】

その後図5(B)に示すように、画素領域206の絶縁膜180及び絶縁膜181に微細な開口部、つまりコンタクトホールを形成する(図5(C)参照。)。このとき、画素領域206、接続領域205の一部、及び周辺駆動回路領域204、画素領域206を覆うようにマスクを形成する。マスクは、画素領域206の開口部形成用のマスクであり、所定な箇所に微細な開口部が設けられている。このようなマスクとしては、例えばレジストマスクを用いることができる。

#### 【0085】

そして、並行平板R I E装置を用いて、絶縁膜180及び絶縁膜181をエッティングする。なおエッティング時間は、配線層や第1の層間絶縁層がオーバーエッティングされる程度とするとよい。このようにオーバーエッティングされる程度とすると、基板内の膜厚バラツキと、エッティングレートのバラツキを低減することができる。

#### 【0086】

またエッティング装置にI C P装置を用いてもよい。以上の工程で、画素領域206にソース電極又はドレイン電極172aに達する開口部184を形成する。本発明において、ソース電極又はドレイン電極172aは、薄膜トランジスタ176において薄膜が多く積層しており総膜厚が大きい場所であるゲート電極層126を、絶縁膜167及び絶縁膜168を介して覆うように形成されている。よって開口部184を膜厚深く開口する必要がないため、開口工程が短縮でき、制御性も向上する。また、開口部に形成される電極層も、角度の大きい開口部を広く被覆する必要がないため、被覆性良く形成することができ、信頼性も向上する。

#### 【0087】

本実施の形態では、接続領域205、配線領域203、外部端子接続領域202、切り離し領域201、周辺駆動回路領域204の一部を覆い、画素領域206に所定の開口部が設けられたマスクで、絶縁膜180及び絶縁膜181をエッティングする場合を説明したが、本発明はこれに限定されない。例えば、接続領域204の開口部は広面積であるため、エッティングする量が多い。このような広面積な開口部は、複数回エッティングしてもよい。また、その他の開口部と比較して、深い開口部を形成する場合、同様に複数回エッティングしてもよい。そのため、配線領域203、外部端子接続領域202、切り離し領域201、周辺駆動回路領域204の一部の絶縁膜180及び絶縁膜181のみ覆い、接続領域205及び画素領域206には所定の開口部が設けられたマスクを用いて、絶縁膜180及び絶縁膜181をエッティングしてもよい。このようなマスクを用いて、エッティングする場合、接続領域205における、絶縁膜180及び絶縁膜181は、深さが増すようにエッティングされ、絶縁膜168が露出するまでエッティングする。

#### 【0088】

また、本実施の形態では、絶縁膜180及び絶縁膜181への開口部の形成を図5(B)、(C)で示すように複数回に分けて行うが、一回のエッティング工程によって形成しても良い。この場合、I C P装置を用いて、I C Pパワー7000W、バイアスパワー1000W、圧力0.8パスカル(Pa)、エッティングガスとしてCF<sub>4</sub>を240sccm、O<sub>2</sub>を160sccmとしてエッティングする。バイアスパワーは1000~4000Wが好ましい。一回のエッティング工程で開口部が形成できるので工程が簡略化する利点がある。

#### 【0089】

次に、ソース電極層又はドレイン電極層172aと接するように、第1の電極層18

10

20

30

40

50

5(画素電極層ともいう。)を形成する。第1の電極層は陽極、または陰極として機能し、Ti、Ni、W、Cr、Pt、Zn、Sn、In、またはMoから選ばれた元素、TiN、 $TiSi_xNy$ 、 $WSi_x$ 、 $WN_x$ 、 $WSi_xNy$ 、NbN、または前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそれらの積層膜を総膜厚100nm～800nmの範囲で用いればよい。

#### 【0090】

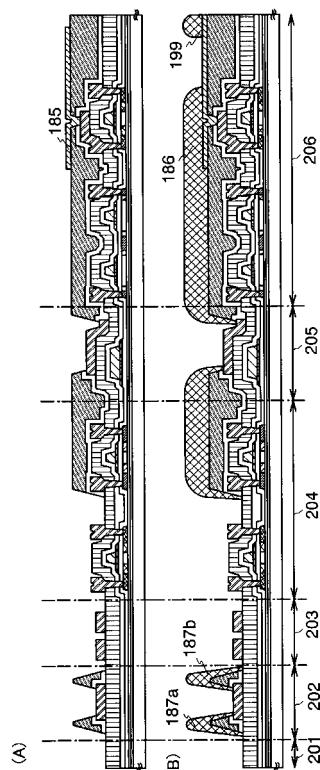

本実施の形態では、表示素子として発光素子を用い、発光素子からの光を第1の電極層185側から取り出す構造のため、第1の電極層185が透光性を有する。第1の電極層185として、透明導電膜を形成し、所望の形状にエッチングすることで第1の電極層185を形成する。本発明で用いる第1の電極層185として、酸化珪素を含む酸化インジウムスズ(酸化珪素を含むインジウム錫酸化物ともいう、以下、「ITO」という。)、酸化亜鉛、酸化スズ、酸化インジウムなどを用いてもよい。この他、酸化インジウムに2～20atomic%の酸化亜鉛(ZnO)を混合した酸化インジウム酸化亜鉛合金などの透明導電膜を用いることができる。第1の電極層185として上記透明導電膜の他に、窒化チタン膜またはチタン膜を用いても良い。この場合、透明導電膜を成膜した後に、窒化チタン膜またはチタン膜を、光が透過する程度の膜厚(好ましくは、5nm～30nm程度)で成膜する。本実施の形態では、第1の電極層185として、酸化インジウムスズと酸化珪素を用いたITOを用いる。本実施の形態では、ITO膜を、インジウム錫酸化物に1～10[w t %]の酸化珪素(SiO<sub>2</sub>)を混合したターゲットを用い、Arガス流量を120sccm、O<sub>2</sub>ガス流量を5sccm、圧力を0.25Pa、電力3.2kWの条件下でスパッタ法により膜厚185nmで成膜する。第1の電極層185は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体で拭出し、研磨しても良い。またCMP法を用いた研磨後に、第1の電極層185の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

#### 【0091】

第1の電極層185を形成後、加熱処理を行ってもよい。この加熱処理により、第1の電極層185中に含まれる水分は放出される。よって、第1の電極層185は脱ガスなどを生じないため、第1の電極層上に水分によって劣化しやすい発光材料を形成しても、発光材料は劣化せず、信頼性の高い表示装置を作製することができる。本実施の形態では、第1の電極層185にITOを用いているので、ベークを行ってもITO(酸化インジウム酸化スズ合金)のように結晶化せず、アモルファス状態のままである。従って、ITOは、ITOよりも平坦性が高く、有機化合物を含む層が薄くとも陰極とのショートが生じにくい。

#### 【0092】

次に、第1の電極層185の端部、ソース電極層又はドレイン電極層を覆う絶縁物(絶縁層)186(隔壁、障壁などと呼ばれる)を形成する(図6(B)参照。)。また同工程で外部端子接続領域202に絶縁物187a、絶縁物187bを形成する。

#### 【0093】

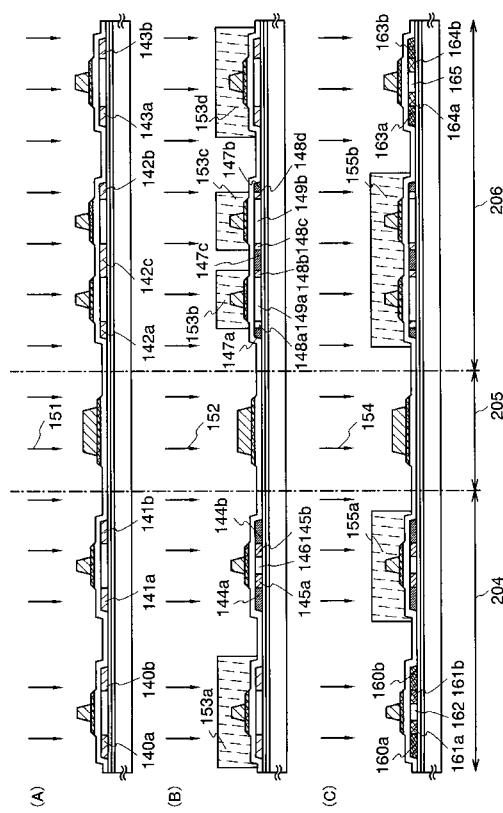

フルカラー表示を行うためには、第1の電極層上に電界発光層を形成する際、RGBの発光を行う電界発光層をそれぞれ作り分けなければならない。よって、他色の電界発光層を形成する時は、その画素電極層(第1の電極層)はマスクによって覆われている。マスクは金属材料などからなる膜状の形態を用いることができる。このとき、マスクは隔壁となる絶縁物186上に設けられ、支持されるが、たわみやよじれなどによって、画素電極層に接する可能性があり、画素電極層に傷を付けてしまう。画素電極層に傷などにより形状不良が生じると、発光不良や、表示不良などを引き起こし、画質の低下を招く。よって信頼性も性能も低下してしまう。

#### 【0094】

本発明においては画素電極層である第1の電極層185上に絶縁物186と同等の膜厚でスペーサ199を形成する。このスペーサ199によりマスクは支持されるので、第1の電極層に接触しなくなる。よって、マスクによる第1の電極層への形状不良は防止さ

10

20

30

40

50

れ、第1の電極層は発光不良、表示不良を引き起こすことなく、信頼性の高い高画質な表示装置とすることができる。スペーサは、画素電極層として機能する第1の電極層上に電界発光層を形成する際、使用するマスクに対するスペーザとなるだけでなく、電界発光層を形成し、封止基板により封止し表示装置として完成した後も、表示装置が外部からの圧力や衝撃により、損傷、変形するのを防ぐスペーザとして機能する。

#### 【0095】

本実施の形態ではスペーサ199は、隔壁である絶縁物186と同材料、同工程で形成されるが、別工程で形成されても良い。スペーサの形状や大きさは限定されず、画素領域の大きさや、開口率などを考慮して設定すればよい。本実施の形態では、図6(B)で示すような柱状で上部が半球のように丸みを帯びた形状としており、大きさは1μm~2μm(好ましくは1.5μm以上2μm以下)である。10

#### 【0096】

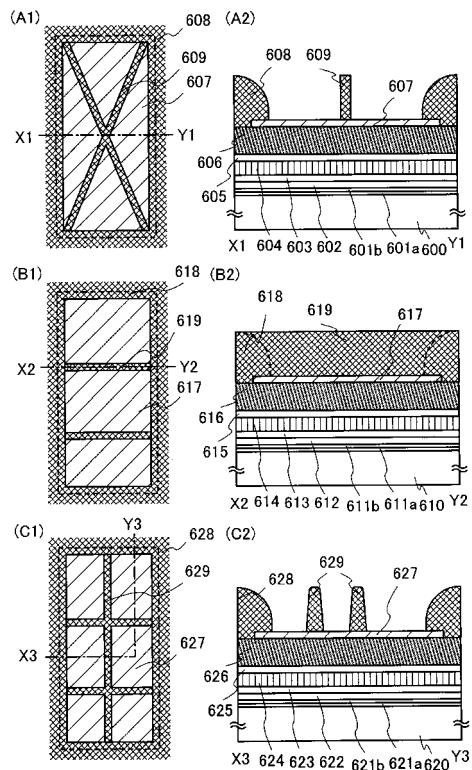

スペーサの形状の例を図22を用いて説明する。図22(A1)、(B1)、(C1)は画素領域の上面図であり、図22(A2)、(B2)、(C2)は図22(A1)、(B1)、(C1)における線X1-Y1、X2-Y2、X3-Y3の断面図である。図22(A1)及び(A2)において、基板600、下地膜601a、下地膜601b、ゲート絶縁層602、絶縁膜603、絶縁膜604、絶縁膜605、絶縁膜606上に画素電極層である第1の電極層607が形成されている。第1の電極層607の端部を覆うようにして隔壁である絶縁物608が形成され、絶縁物608と同材料、同工程でスペーサ609が形成されている。スペーサは図22のように、隔壁となる絶縁層とつながって形成されていてもよい。20

#### 【0097】

図22(A1)及び(A2)において、スペーサ609は、絶縁物608と接するように形成され、第1の電極層上を、第1の電極層609を対角線上に横切るように連続して形成されている。このように連続的にスペーサ609を形成すると、マスクは移動中もいつもスペーサ609に支持されるので、第1の電極層607に接すし、第1の電極層607の形状不良を引き起こすことを防止することができる。

#### 【0098】

図22(B1)及び(B2)において、基板610、下地膜611a、下地膜611b、ゲート絶縁層612、絶縁膜613、絶縁膜614、絶縁膜615、絶縁膜616上に画素電極層である第1の電極層617が形成されている。第1の電極層617の端部を覆うようにして隔壁である絶縁物618が形成され、絶縁物608と同材料、同工程でスペーサ619が形成されている。30

#### 【0099】

図22(B1)及び(B2)において、スペーサ619は、絶縁物618と接するように形成され、第1の電極層上を、第1の電極層619の短辺方向に横切るように連続して、2個所において形成されている。このように複数個所に連続的にスペーサ619を形成すると、マスクは移動中もいつもスペーサ619に支持されるので、第1の電極層617に接すし、第1の電極層617の形状不良を引き起こすことを防止することができる。

#### 【0100】

図22(C1)及び(C2)において、基板620、下地膜621a、下地膜621b、ゲート絶縁層622、絶縁膜623、絶縁膜624、絶縁膜625、絶縁膜626上に画素電極層である第1の電極層627が形成されている。第1の電極層627の端部を覆うようにして隔壁である絶縁物628が形成され、絶縁物628と同材料、同工程でスペーサ629が形成されている。40

#### 【0101】

図22(C1)及び(C2)において、スペーサ629は、絶縁物628と接するように形成され、第1の電極層上を、第1の電極層629の長辺方向及び短辺方向に横切るように連続して、格子状に形成されている。このようにスペーサ629を格子状に連続的に形成すると、マスクは移動中もいつもスペーサ629に支持されるので、第1の電極層50

627に接し、第1の電極層627の形状不良を引き起こすことを防止することができる。図22(C2)に示すように、スペーサ629は、テーパーを有する形状をしている。このようにスペーサは、図22(A2)のように概略直方体でもよく、円柱、角柱、テーパー形状を有しているものなど様々な形状のものを用いることができる。

#### 【0102】

図22において、スペーサは、隔壁となる絶縁物と接して形成されているが、接さず、離れて形成されていてもよい。

#### 【0103】

スペーサは、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン樹脂を用いて形成することができる。本実施の形態ではスペーサ199にアクリルを用いる。

#### 【0104】

本実施の形態では、絶縁物186にアクリルを用いる。また絶縁物186に絶縁膜181と同材料を用い、同工程で形成すると、製造コストを削減することができる。また、塗布成膜装置やエッチング装置などの装置の共通化によるコストダウンが図れる。

#### 【0105】

絶縁物186は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン樹脂を用いて形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。絶縁物186は曲率半径が連続的に変化する形状が好ましく、上に形成される電界発光層188、第2の電極層189の被覆性が向上する。

#### 【0106】

接続領域205において、絶縁物186は、開口部182の側面の絶縁膜180及び絶縁膜181の端部を覆うように形成されている。エッチング工程によって段差を有するように加工された絶縁膜180及び絶縁膜181の端部は、その急激な段差のため、その上に積層する第2の電極層189の被覆性が悪い。よって本発明のように、開口部周辺の段差を絶縁物186によって覆い、段差をなだらかにすることで、積層する第2の電極層189の被覆性を向上させることができる。接続領域205において、第2の電極層と同工程、同材料で形成される配線層は配線層156と電気的に接続する。本実施の形態では、第2の電極層189は配線層156と直接接して電気的に接続されているが、他の配線を介して電気的に接続されてもよい。

#### 【0107】

また、さらに信頼性を向上させるため、電界発光層(有機化合物を含む層)188の形成前に真空加熱を行って脱気を行うことが好ましい。例えば、有機化合物材料の蒸着を行う前に、基板に含まれるガスを除去するために減圧雰囲気や不活性雰囲気で200~400、好ましくは250~350の加熱処理を行うことが望ましい。またそのまま大気に晒さずに電界発光層188を真空蒸着法や、減圧下の液滴吐出法で形成することが好ましい。この熱処理で、第1の電極層となる導電膜や絶縁層(隔壁)に含有、付着している水分を放出することができる。この加熱処理は、真空を破らず、真空のチャンバー内を基板が輸送できるのであれば、先の加熱工程と兼ねることもでき、先の加熱工程を絶縁層(隔壁)形成後に、一度行えばよい。ここでは、層間絶縁膜と絶縁物(隔壁)とを高耐熱性を有する物質で形成すれば信頼性向上のための加熱処理工程を十分行うことができる。

#### 【0108】

第1の電極層185の上には電界発光層188が形成される。なお、図1では一画素しか図示していないが、本実施の形態ではR(赤)、G(緑)、B(青)の各色に対応した電界電極層を作り分けている。本実施の形態では電界発光層188として、赤色(R)

10

20

30

40

50

、緑色（G）、青色（B）の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法等によって選択的に形成する様子を図23に示す。

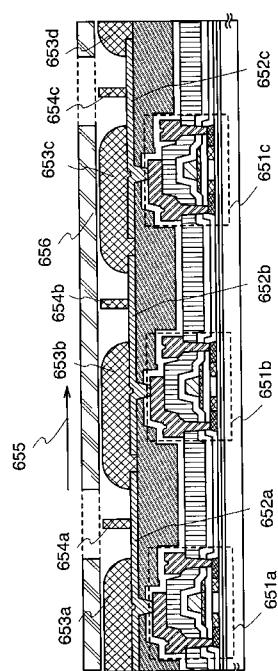

#### 【0109】

図23において、薄膜トランジスタ651a、薄膜トランジスタ651b、薄膜トランジスタ651cは画素電極層である第1の電極層652a、第1の電極層652b、第1の電極層652cと接続している。第1の電極層の端部はそれぞれ、隔壁として機能する絶縁物653a、絶縁物653b、絶縁物654c、絶縁物653dに覆われてあり、第1の電極層上には、スペーサ654a、スペーサ654b、スペーサ654cが形成されている。マスク656は、第1の電極層652a、第1の電極層652b、第1の電極層652cに電界発光層を形成したのち、矢印655の方向へ移動しながら各第1の電極層上に電界発光層を形成する。マスク656は、第1の電極層652a、第1の電極層652b、第1の電極層652c上ではスペーサ654a、スペーサ654b、スペーサ654cに支持されるため、たわみやよじれなどによって、第1の電極層に接し、第1の電極層に形状不良を引き起こす問題がない。よって、第1の電極層は発光不良、表示不良を引き起こすことなく、信頼性の高い高画質な表示装置を作製することができる。

10

#### 【0110】

赤色（R）、緑色（G）、青色（B）の発光を示す材料は、液滴吐出法により形成することもでき（低分子または高分子材料など）る。

#### 【0111】

次に、電界発光層188の上に導電膜からなる第2の電極層189が設けられる。第2の電極層189としては、仕事関数の小さい材料（Al、Ag、Li、Ca、またはこれらの合金や化合物、MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム）を用いればよい。こうして第1の電極層185、電界発光層188及び第2の電極層189からなる発光素子190が形成される。

20

#### 【0112】

図1に示した本実施の形態の表示装置において、発光素子190から発した光は、第1の電極層185側から、図1中の矢印の方向に透過して射出される。

#### 【0113】

第2の電極層189を覆うようにしてパッシベーション膜191を設けることは有効である。パッシベーション膜191としては、窒化珪素、酸化珪素、酸化窒化珪素（SiON）、窒化酸化珪素（SiNO）、窒化アルミニウム（AlN）、酸化窒化アルミニウム（AlON）、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム（AlNO）または酸化アルミニウム、ダイアモンドライクカーボン（DLC）、窒素含有炭素膜（CN）を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層を用いることができる。また、シリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

30

#### 【0114】

この際、カバレッジの良い膜をパッシベーション膜として用いることが好ましく、炭素膜、特にDLC膜を用いることは有効である。DLC膜は室温から100以下の温度範囲で成膜可能であるため、耐熱性の低い電界発光層188の上方にも容易に成膜することができる。DLC膜は、プラズマCVD法（代表的には、RFプラズマCVD法、マイクロ波CVD法、電子サイクロトロン共鳴（ECR）CVD法、熱フィラメントCVD法など）、燃焼炎法、スパッタ法、イオンビーム蒸着法、レーザ蒸着法などで形成することができる。成膜に用いる反応ガスは、水素ガスと、炭化水素系のガス（例えばCH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub>など）とを用い、グロー放電によりイオン化し、負の自己バイアスがかかったカソードにイオンを加速衝突させて成膜する。また、CN膜は反応ガスとしてC<sub>2</sub>H<sub>4</sub>ガスとN<sub>2</sub>ガスとを用いて形成すればよい。DLC膜は酸素に対するプロッキング効果が高く、電界発光層188の酸化を抑制することが可能である。そのため、この後に続く封止工程を行う間に電界発光層188が酸化するといった問題を防止できる。

40

50

## 【0115】

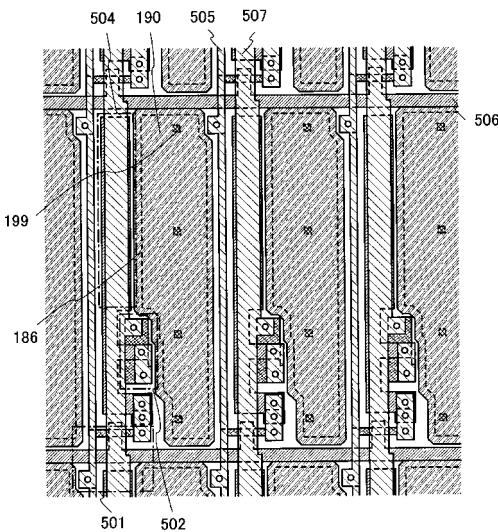

本実施の形態で作製した表示装置の画素領域の上面図を図18に示す。図18において、画素2702は、薄膜トランジスタ501、薄膜トランジスタ502、容量504、発光素子190、ゲート配線層506、ソース及びドレイン配線層505、電源線507から構成されている。図18において、第1の電極層上にスペーサ199が複数設けられている。スペーサは、単数でも複数でもよく、複数である場合、同一の形状である必要もない。また、スペーサ199のように絶縁層186(図18では点線で図示している)と接さず、分離して形成されてもよい。

## 【0116】

このように発光素子190が形成された基板100と、封止基板195とをシール材192によって固着し、発光素子を封止する(図1参照。)。本発明の表示装置においては、シール材192と絶縁物186とを接しないように離して形成する。このようにシール材と、絶縁物186とを離して形成すると、絶縁物186に吸湿性の高い有機材料を用いた絶縁材料を用いても、水分が侵入しにくく、発光素子の劣化が防止でき、表示装置の信頼性が向上する。シール材192としては、代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。例えば、ビスフェノールA型液状樹脂、ビスフェノールA型固体樹脂、含ブロムエポキシ樹脂、ビスフェノールF型樹脂、ビスフェノールAD型樹脂、フェノール型樹脂、クレゾール型樹脂、ノボラック型樹脂、環状脂肪族エポキシ樹脂、エピビス型エポキシ樹脂、グリシジルエステル樹脂、グリジシルアミン系樹脂、複素環式エポキシ樹脂、変性エポキシ樹脂等のエポキシ樹脂を用いることができる。なお、シール材で囲まれた領域には充填材193を充填してもよく、窒素雰囲気下で封止することによって、窒素等を封入してもよい。本実施の形態は、下方射出型のため、充填材193は透光性を有する必要はないが、充填材193を透過して光を取り出す構造の場合は、透光性を有する必要がある。代表的には可視光硬化、紫外線硬化または熱硬化のエポキシ樹脂を用いればよい。以上の工程において、本実施の形態における、発光素子を用いた表示機能を有する表示装置が完成する。また充填材は、液状の状態で滴下し、表示装置内に充填することもできる。

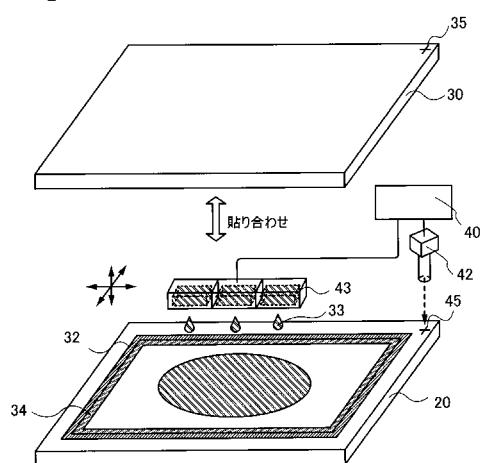

## 【0117】

ディスペンサ方式を採用した滴下注入法を図19を用いて説明する。図19の滴下注入法は、制御装置40、撮像手段42、ヘッド43、充填材33、マーカー35、マーカー45は、バリア層34、シール材32、TFT基板30、対向基板20からなる。シール材32で閉ループを形成し、その中にヘッド43より充填材33を1回若しくは複数回滴下する。充填材材料の粘性が高い場合は、連続的に吐出され、繋がったまま被形成領域に付着する。一方、充填材材料の粘性が低い場合には、図19のように間欠的に吐出され充填材が滴下される。そのとき、シール材32と充填材33とが反応することを防ぐため、バリア層34を設けてもよい。続いて、真空中で基板を貼り合わせ、その後紫外線硬化を行って、充填材が充填された状態とする。この充填剤として、乾燥剤などの吸湿性を含む物質を用いると、さらなる吸水効果が得られ、素子の劣化を防ぐことができる。

## 【0118】

EL表示パネル内には素子の水分による劣化を防ぐため、乾燥剤を設置される。本実施の形態では、乾燥剤は、画素領域を取り囲むように封止基板に形成された凹部に設置され、薄型化を妨げない構成とする。また、ゲート配線層に対応する領域にも乾燥剤を形成し、吸水面積を広く取っているので、吸水効果が高い。また、直接発光しないゲート配線層上に乾燥剤を形成しているので、光取り出し効率を低下させることもない。

## 【0119】

なお、本実施の形態では、ガラス基板で発光素子を封止した場合を示すが、封止の処理とは、発光素子を水分から保護するための処理であり、カバー材で機械的に封入する方法、熱硬化性樹脂又は紫外線硬化性樹脂で封入する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法のいずれかを用いる。カバー材としては、ガラス、セラミックス、プラスチックもしくは金属を用いることができるが、カバー材側に光を放射

10

20

30

40

50

させる場合は透光性でなければならない。また、カバー材と上記発光素子が形成された基板とは熱硬化性樹脂又は紫外光硬化性樹脂等のシール材を用いて貼り合わせられ、熱処理又は紫外光照射処理によって樹脂を硬化させて密閉空間を形成する。この密閉空間の中に酸化バリウムに代表される吸湿材を設けることも有効である。この吸湿材は、シール材の上に接して設けても良いし、発光素子よりの光を妨げないような、隔壁の上や周辺部に設けても良い。さらに、カバー材と発光素子の形成された基板との空間を熱硬化性樹脂若しくは紫外光硬化性樹脂で充填することも可能である。この場合、熱硬化性樹脂若しくは紫外光硬化性樹脂の中に酸化バリウムに代表される吸湿材を添加しておくことは有効である。

## 【0120】

10

本実施の形態では、外部端子接続領域202において、端子電極層178に異方性導電層196によってFPC194を接続し、外部と電気的に接続する構造とする。また表示装置の上面図である図1(A)で示すように、本実施の形態において作製される表示装置は信号線駆動回路を有する周辺駆動回路領域204のほかに、走査線駆動回路を有する周辺駆動回路領域207a、周辺駆動回路領域207bが設けられている。

## 【0121】

本実施の形態では、上記のような回路で形成するが、本発明はこれに限定されず、周辺駆動回路としてICチップを前述したCOG方式やTAB方式によって実装したものでもよい。また、ゲート線駆動回路、ソース線駆動回路は複数であっても単数であっても良い。

20

## 【0122】

また、本発明の表示装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、表示装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

## 【0123】

30

さらに、ビデオ信号がデジタルの表示装置において、画素に入力されるビデオ信号が定電圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV)には、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加される電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの(CC)には、発光素子に印加される電圧が一定のもの(CCVC)と、発光素子に印加される電流が一定のもの(CCCC)とがある。

## 【0124】

本発明を用いると、信頼性の高い表示装置を簡略化した工程で作製することができる。よって、高精細、高画質な表示装置を低いコストで歩留まり良く製造することができる。

## 【0125】

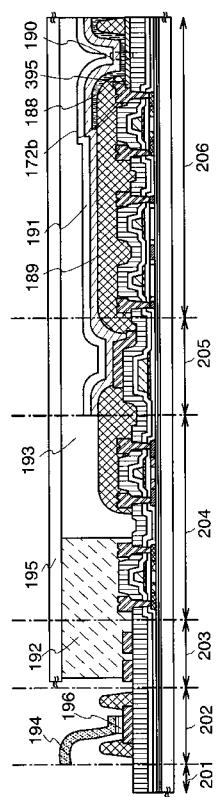

(実施の形態2)

本発明の実施の形態を、図7乃至図9を用いて説明する。本実施の形態は、実施の形態1で作製した表示装置において、第2の層間絶縁層を形成しない例を示す。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

40

## 【0126】

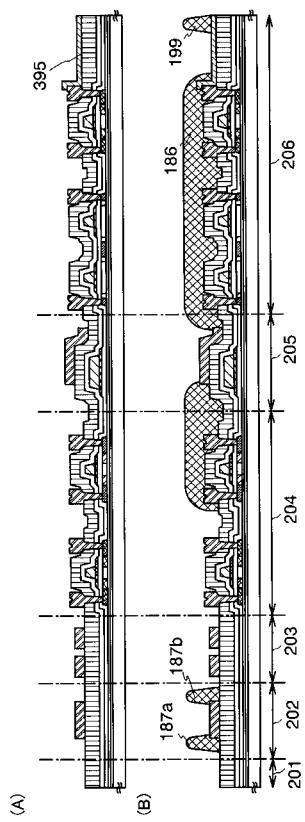

実施の形態1で示したように、基板100上に薄膜トランジスタ173、薄膜トランジスタ174、薄膜トランジスタ175、薄膜トランジスタ176、導電層177を形成し、絶縁膜168、絶縁膜168を形成する。各薄膜トランジスタには半導体層のソース領域又はドレイン領域に接続するソース電極層又はドレイン電極層が形成されている。画素領域206に設けられた薄膜トランジスタ176におけるソース電極層又はドレイン電極層172bに接して第1の電極層395を形成する(図7(A)参照。)。

## 【0127】

50

第1の電極層395は画素電極として機能し、実施の形態1における第1の電極層185と同様な材料と工程で形成すればよい。本実施の形態でも実施の形態1と同様に第1の電極層中を光を通過させて取り出すために、透明導電膜であるITOを第1の電極層395に用いて所望の形状に加工し形成する。

#### 【0128】

第1の電極層395の端部及び薄膜トランジスタを覆うように絶縁物186を形成する(図7(B)参照。)。絶縁物186には本実施の形態ではアクリルを用いる。第1の電極層上に電界発光層188を形成し、第2の電極層189を積層することによって発光素子190を形成する。第2の電極層189は接続領域205において配線層156と電気的に接続し、外部端子接続領域202においては端子電極層178に異方性導電層196を介してFPC194が接着される。第2の電極層189を覆うようにパッシベーション膜191を形成する。基板100はシール材192によって封止基板195と張り合わされ、表示装置内には充填材193が充填されている(図8参照。)。本発明の表示装置においては、シール材192と絶縁物186とを接しないように離して形成する。このようにシール材と、絶縁物186とを離して形成すると、絶縁物186に吸湿性の高い有機材料を用いた絶縁材料を用いても、水分が侵入しにくく、発光素子の劣化が防止でき、表示装置の信頼性が向上する。

#### 【0129】

また図9における表示装置は、第1の電極層395を、薄膜トランジスタ176と接続するソース電極層又はドレイン電極層172bの形成前に、絶縁膜168上に選択的に形成することもできる。この場合、本実施の形態とはソース電極層又はドレイン電極層172bと、第1の電極層395の接続構造が、第1の電極層395の上にソース電極層又はドレイン電極層172bが積層する構造となる。第1の電極層395をソース電極層又はドレイン電極層172bより先に形成すると、平坦な形成領域に形成できるので、被覆性がよく、CMPなどの研磨処理も十分に行えるので平坦性よく形成できる利点がある。

#### 【0130】

本発明を用いると、信頼性の高い表示装置を簡略化した工程で作製することができる。よって、高精細、高画質な表示装置を低いコストで歩留まり良く製造することができる。

#### 【0131】

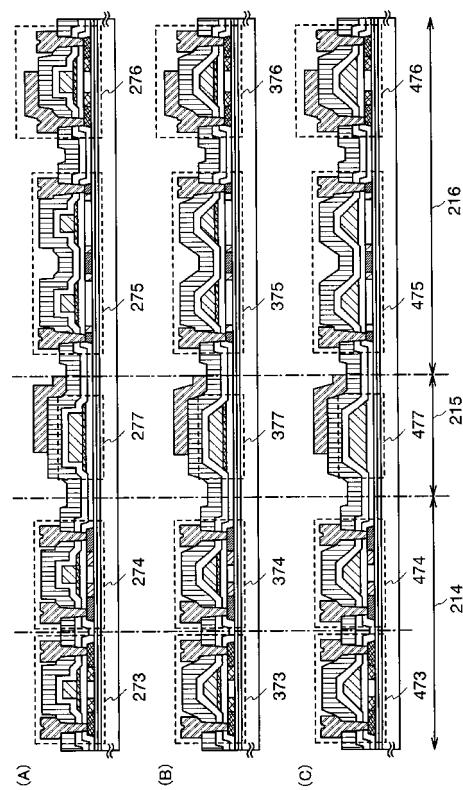

(実施の形態3)

本発明の実施の形態を、図10を用いて説明する。本実施の形態は、実施の形態1で作製した表示装置において、薄膜トランジスタのゲート電極層の構造が異なる例を示す。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

#### 【0132】

図10(A)乃至(C)は、作製工程にある表示装置であり、実施の形態1で示した図4(B)の表示装置と対応している。

#### 【0133】

図10(A)において、周辺駆動回路領域214に薄膜トランジスタ273及び薄膜トランジスタ274が、接続領域215に導電層277が、画素領域216に薄膜トランジスタ275及び薄膜トランジスタ276が設けられている。図10(A)における薄膜トランジスタのゲート電極層は2層の導電膜の積層で構成され、上層のゲート電極層が下層のゲート電極層より幅が細く加工されている。下層のゲート電極層はテーパー形状を有しているが、上層のゲート電極層はテーパー形状を有していない。このように、ゲート電極層はテーパー形状を有していても良いし、側面の角度が垂直に近い形状、いわゆるテーパー形状を有さない形状でもよい。

#### 【0134】

図10(B)において、周辺駆動回路領域214に薄膜トランジスタ373及び薄膜トランジスタ374が、接続領域215に導電層377が、画素領域216に薄膜トランジスタ375及び薄膜トランジスタ376が設けられている。図10(B)における薄膜

10

20

30

40

50

トランジスタのゲート電極層も2層の導電膜の積層で構成されているが、上層のゲート電極層と下層のゲート電極層は連続的なテーバー形状を有している。

#### 【0135】

図10(C)において、周辺駆動回路領域214に薄膜トランジスタ473及び薄膜トランジスタ474が、接続領域215に導電層477が、画素領域216に薄膜トランジスタ475及び薄膜トランジスタ476が設けられている。図10(C)における薄膜トランジスタのゲート電極層は、単層構造でありテーバー形状を有している。このようにゲート電極層は単層構造でもよい。

#### 【0136】

以上のように、ゲート電極層はその構成と形状によって様々な構造をとりうる。よって作製される表示装置も様々な構造を示す。半導体層中の不純物領域は、ゲート電極層をマスクとして自己整合的に形成される場合、ゲート電極層の構造によってその不純物領域の構造や濃度分布が変化する。以上のことも考慮して設計を行うと所望の機能を有する薄膜トランジスタを作製することができる。

#### 【0137】

本実施の形態は、実施の形態1及び2とそれぞれと組み合わせて用いることが可能である。

#### 【0138】

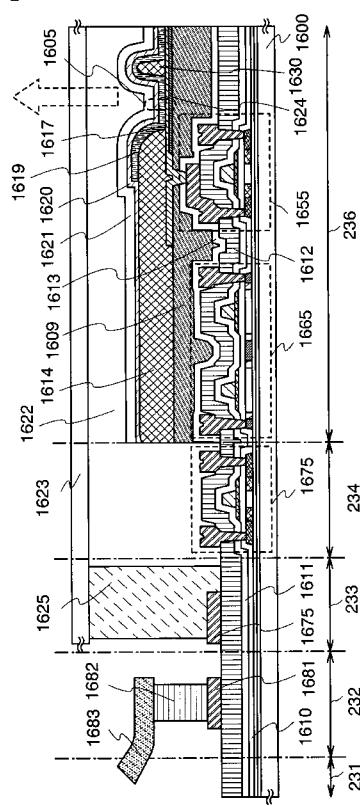

##### (実施の形態4)

本発明を適用して発光素子を有する表示装置を形成することができるが、該発光素子から発せられる光は、下方放射、上方放射、両方放射のいずれかを行う。本実施の形態では、両方射出型、上方射出型の例を、図11及び図12を用いて説明する。

#### 【0139】

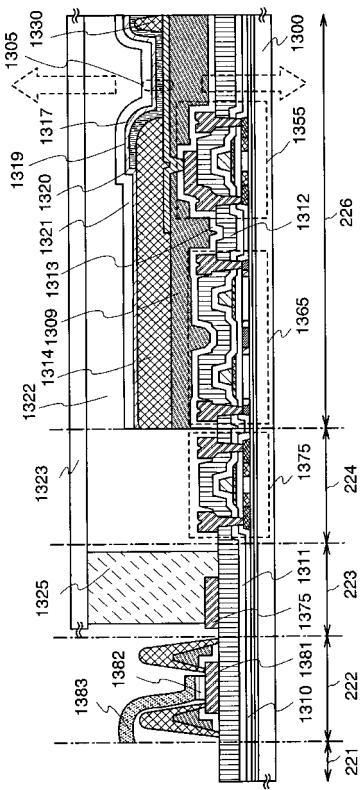

図12に示す表示装置は、素子基板1300、薄膜トランジスタ1355、薄膜トランジスタ1365、薄膜トランジスタ1375、第1の電極層1317、電界発光層1319、第2の電極層1320、透明導電膜1321、充填材1322、シール材1325、ゲート絶縁層1310、絶縁膜1311、絶縁膜1312、絶縁膜1313、絶縁膜1309、絶縁物1314、封止基板1323、配線層1308、端子電極層1381、異方性導電層1382、FPC1383、スペーサ1330、発光素子1305によって構成されている。表示装置は、切り離し領域221、外部端子接続領域222、配線領域223、周辺駆動回路領域224、画素領域226を有している。充填剤1322は、図19の滴下法のように、液状の組成物にして、滴下法によって形成することができる。滴下法によって充填剤が形成された素子基板1300と封止基板1323を張り合わせて発光表示装置を封止する。

#### 【0140】

図12の表示装置は、両面射出型であり、矢印の方向に素子基板1300側からも、封止基板1323側からも光を射出する構造である。なお本実施の形態では、透明導電膜を成膜し、所望の形状にエッチングすることで第1の電極層1317を形成する。第1の電極層1317として透明導電膜を用いることができる。第1の電極層1317として上記透明導電膜の他に、窒化チタン膜またはチタン膜を用いても良い。この場合、透明導電膜を成膜した後に、窒化チタン膜またはチタン膜を、光が透過する程度の膜厚(好ましくは、5nm～30nm程度)で成膜する。本実施の形態では、第1の電極層1317としてITOを用いている。

#### 【0141】

次に、電界発光層1319の上には導電膜からなる第2の電極層1320が設けられる。第2の電極層1320としては、仕事関数の小さい材料(A1、Ag、Li、Ca、またはこれらの合金や化合物、MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム)を用いればよい。図6の表示装置では、発光が透過するように、第2の電極層1320として膜厚を薄くした金属薄膜(MgAg:膜厚10nm)と、透明導電膜1321として、膜厚100nmのITOとの積層を用いる。透明導電膜1321として上

10

20

30

40

50

述の第1の電極層1317と同様なものを用いることができる。

#### 【0142】

図11の表示装置は、片面射出型であり、矢印の方向に上方射出する構造である。図11に示す表示装置は、素子基板1600、薄膜トランジスタ1655、薄膜トランジスタ1665、薄膜トランジスタ1675、反射性を有する金属層1624、第1の電極層1617、電界発光層1619、第2の電極層1620、透明導電膜1621、充填材1622、シール材1625、ゲート絶縁層1610、絶縁膜1611、絶縁膜1612、絶縁膜1613、絶縁膜1609、絶縁物1614、封止基板1623、配線層1608、端子電極層1681、異方性導電層1682、FPC1683、スペーサ1630、発光素子1605によって構成されている。図11における表示装置において、端子電極層1681に積層していた絶縁層はエッティングによって除去されている。このように端子電極層の周囲に透水性を有する（水分を透過し得る）絶縁層を設けないと信頼性がより向上する。また、表示装置は、切り離し領域231、外部端子接続領域232、配線領域233、周辺駆動回路領域234、画素領域236を有している。この場合、前述の図12で示した両方射出型の表示装置において、第1の電極層1317の下に、反射性を有する金属層1624を形成する。反射性を有する金属層1624の上に陽極として機能する透明導電膜である第1の電極層1617を形成する。金属層1624としては、反射性を有すればよいので、Ta、W、Ti、Mo、Al、Cuなどを用いればよい。好ましくは、可視光の領域で反射性が高い物質を用いることがよく、本実施の形態では、TiN膜を用いる。

10

20

30

40

50

#### 【0143】

電界発光層1619の上には導電膜からなる第2の電極層1620が設けられる。第2の電極層1620としては、陰極として機能させるので仕事関数の小さい材料（Al、Ag、Li、Ca、またはこれらの合金や化合物、MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム）を用いればよい。本実施の形態では、発光が透過するよう、第2の電極層1620として膜厚を薄くした金属薄膜（MgAg：膜厚10nm）と、透明導電膜1621として、膜厚110nmのITOとの積層を用いる。

#### 【0144】

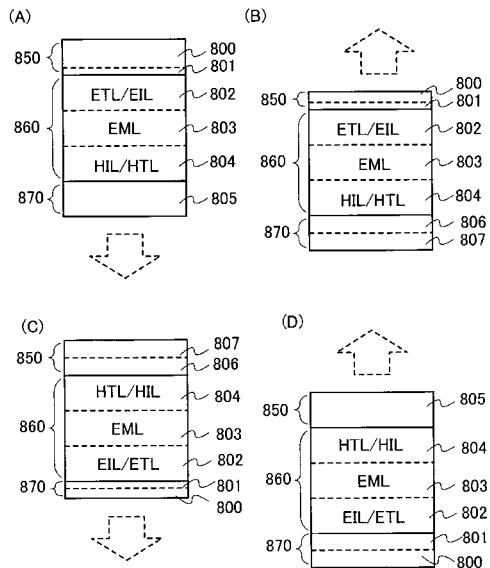

本実施の形態において適用できる発光素子の形態を図13に示す。発光素子は、電界発光層860を第1の電極層870と第2の電極層850で挟んだ構成になっている。第1の電極層及び第2の電極層は仕事関数を考慮して材料を選択する必要があり、そして第1の電極層及び第2の電極層は、画素構成によりいずれも陽極、又は陰極となりうる。本実施の形態では、駆動用TFTの極性がpチャネル型である場合、第1の電極層を陽極、第2の電極層を陰極とするとよい。また、駆動用TFTの極性がNチャネル型であるため、第1の電極層を陰極、第2の電極層を陽極とすると好ましい。

#### 【0145】

図13(A)及び(B)は、第1の電極層870が陽極であり、第2の電極層850が陰極である場合であり、電界発光層860は、第1の電極層870側から、HIL(ホール注入層)HTL(ホール輸送層)804、EML(発光層)803、ETL(電子輸送層)EIL(電子注入層)802、第2の電極層850の順に積層するのが好ましい。図13(A)は第1の電極層870から光を放射する構成であり、第1の電極層870は透光性を有する酸化物導電性材料からなる電極層805で構成し、第2の電極層は電界発光層860側から、LiFやMgAgなどアルカリ金属又はアルカリ土類金属を含む電極層801とアルミニウムなどの金属材料で形成する電極層800より構成されている。図13(B)は第2の電極層850から光を放射する構成であり、第1の電極層は、アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する電極層807と、酸化珪素を1~15原子%の濃度で含む酸化物導電性材料で形成する第2の電極層806より構成されている。第2の電極層は、第2の電極層は電界発光層860側から、LiFやMgAgなどアルカリ金属又はアルカリ土類金属を含む電極層801とアルミニウムなどの金属材料で形成する電極層800より構成されてい

るがいずれの層も 100 nm 以下の厚さとして光を透過可能な状態としておくことで、第 2 の電極層 850 から光を放射することが可能となる。

#### 【0146】

図 13 (C) 及び (D) は、第 1 の電極層 870 が陰極であり、第 2 の電極層 850 が陽極である場合であり、電界発光層 860 は、陰極側から EIL (電子注入層) ETL (電子輸送層) 802、EML (発光層) 803、HTL (ホール輸送層) HIL (ホール注入層) 804、陽極である第 2 の電極層 850 の順に積層するのが好ましい。図 13 (C) は第 1 の電極層 870 から光を放射する構成であり、第 1 の電極層 870 は電界発光層 860 側から、LiF や MgAg などアルカリ金属又はアルカリ土類金属を含む電極層 801 とアルミニウムなどの金属材料で形成する電極層 800 より構成されているがいずれの層も 100 nm 以下の厚さとして光を透過可能な状態としておくことで、第 1 の電極層 870 から光を放射することが可能となる。第 2 の電極層は、電界発光層 860 側から、酸化珪素を 1~15 原子% の濃度で含む酸化物導電性材料で形成する第 2 の電極層 806、アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する電極層 807 より構成されている。図 13 (D) は第 2 の電極層 850 から光を放射する構成であり、第 1 の電極層 870 は電界発光層 860 側から、LiF や MgAg などアルカリ金属又はアルカリ土類金属を含む電極層 801 とアルミニウムなどの金属材料で形成する電極層 800 より構成されており、膜厚は電界発光層 860 で発光した光を反射可能な程度に厚く形成している。第 2 の電極層 850 は、透光性を有する酸化物導電性材料からなる電極層 805 で構成されている。なお電界発光層は、積層構造以外に単層構造、又は混合構造をとることができる。10

20

#### 【0147】

また、電界発光層として、赤色 (R)、緑色 (G)、青色 (B) の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法等によって選択的に形成する。赤色 (R)、緑色 (G)、青色 (B) の発光を示す材料はカラーフィルタ同様、液滴吐出法により形成することもでき（低分子または高分子材料など）、この場合マスクを用いずとも、RGB の塗り分けを行うことができるため好ましい。

#### 【0148】

また上面放射型の場合で、第 2 の電極層に透光性を有するITOやITSOを用いる場合、ベンゾオキサゾール誘導体 (BzOs) に Li を添加した BzOs-Li などを用いることができる。また例えば EML は、R、G、B のそれぞれの発光色に対応したドーパント (R の場合 DCM 等、G の場合 DMQD 等) をドープした Alq<sub>3</sub> を用いればよい。30

#### 【0149】

なお、電界発光層は上記材料に限定されない。例えば、CuPc や PEDOT の代わりに酸化モリブデン (MoO<sub>x</sub> : x = 2~3) 等の酸化物と -NPD やルブレンを共蒸着して形成し、ホール注入性を向上させることもできる。また電界発光層の材料は、有機材料（低分子又は高分子を含む）、又は有機材料と無機材料の複合材料として用いることができる。以下発光素子を形成する材料について詳細に述べる。

#### 【0150】

電荷注入輸送物質のうち、特に電子輸送性の高い物質としては、例えばトリス (8-キノリノラト) アルミニウム（略称：Alq<sub>3</sub>）、トリス (5-メチル-8-キノリノラト) アルミニウム（略称：Almq<sub>3</sub>）、ビス (10-ヒドロキシベンゾ [h] - キノリナト) ベリリウム（略称：BeBq<sub>2</sub>）、ビス (2-メチル-8-キノリノラト) - 4-フェニルフェノラト - アルミニウム（略称：BA1q）など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等が挙げられる。また正孔輸送性の高い物質としては、例えば 4,4'-ビス [N-(1-ナフチル)-N-フェニル-アミノ] - ビフェニル（略称：-NPD）や 4,4'-ビス [N-(3-メチルフェニル)-N-フェニル-アミノ] - ビフェニル（略称：TPD）や 4,4',4'''-トリス (N,N-ジフェニル-アミノ) - トリフェニルアミン（略称：TDATA）、4,4',4'''-トリス [N-(3-

10

20

30

40

50

メチルフェニル) - N - フェニル - アミノ] - トリフェニルアミン(略称: M T D A T A )などの芳香族アミン系(即ち、ベンゼン環 - 窒素の結合を有する)の化合物が挙げられる。

### 【0151】

また、電荷注入輸送物質のうち、特に電子注入性の高い物質としては、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaF<sub>2</sub>)等のようなアルカリ金属又はアルカリ土類金属の化合物が挙げられる。また、この他、Alq<sub>3</sub>のような電子輸送性の高い物質とマグネシウム(Mg)のようなアルカリ土類金属との混合物であってもよい。

### 【0152】

電荷注入輸送物質のうち、正孔注入性の高い物質としては、例えば、モリブデン酸化物(MoO<sub>x</sub>)やバナジウム酸化物(VO<sub>x</sub>)、ルテニウム酸化物(RuO<sub>x</sub>)、タンゲステン酸化物(WO<sub>x</sub>)、マンガン酸化物(MnO<sub>x</sub>)等の金属酸化物が挙げられる。また、この他、フタロシアニン(略称:H<sub>2</sub>Pc)や銅フタロシアニン(CuPc)等のフタロシアニン系の化合物が挙げられる。

### 【0153】

発光層は、発光波長帯の異なる発光層を画素毎に形成して、カラー表示を行う構成としても良い。典型的には、R(赤)、G(緑)、B(青)の各色に対応した発光層を形成する。この場合にも、画素の光放射側にその発光波長帯の光を透過するフィルターを設けた構成とすることで、色純度の向上や、画素部の鏡面化(映り込み)の防止を図ることができる。フィルターを設けることで、従来必要であるとされていた円偏光板などを省略することが可能となり、発光層から放射される光の損失を無くすことができる。さらに、斜方から画素部(表示画面)を見た場合に起こる色調の変化を低減することができる。

### 【0154】

発光材料には様々な材料がある。低分子有機発光材料では、4 - ジシアノメチレン - 2 - メチル - 6 - [2 - (1,1,7,7 - テトラメチル - 9 - ジュロリジル)エテニル] - 4H - ピラン(略称: DCJT)、4 - ジシアノメチレン - 2 - t - ブチル - 6 - [2 - (1,1,7,7 - テトラメチルジュロリジン - 9 - イル)エテニル] - 4H - ピラン(略称: DCJTB)、ペリフランテン、2,5 - ジシアノ - 1,4 - ビス[2 - (10 - メトキシ - 1,1,7,7 - テトラメチルジュロリジン - 9 - イル)エテニル]ベンゼン、N,N' - デジメチルキナクリドン(略称: DMQd)、クマリン6、クマリン545T、トリス(8 - キノリノラト)アルミニウム(略称: Alq<sub>3</sub>)、9,9' - ビアントリル、9,10 - ジフェニルアントラセン(略称: DPAA)や9,10 - ビス(2 - ナフチル)アントラセン(略称: DNA)等を用いることができる。また、この他の物質でもよい。

### 【0155】

一方、高分子系有機発光材料は低分子系に比べて物理的強度が高く、素子の耐久性が高い。また塗布により成膜することができるるので、素子の作製が比較的容易である。高分子系有機発光材料を用いた発光素子の構造は、低分子系有機発光材料を用いたときと基本的には同じであり、順に陰極、有機発光層、陽極となる。しかし、高分子系有機発光材料を用いた発光層を形成する際には、低分子系有機発光材料を用いたときのような積層構造を形成させることは難しく、多くの場合2層構造となる。具体的には、順に陰極、発光層、正孔輸送層、陽極という積層構造である。

### 【0156】

発光色は、発光層を形成する材料で決まるため、これらを選択することで所望の発光を示す発光素子を形成することができる。発光層の形成に用いることができる高分子系の電界発光材料は、ポリパラフェニレンビニレン系、ポリパラフェニレン系、ポリチオフェン系、ポリフルオレン系が挙げられる。

### 【0157】

ポリパラフェニレンビニレン系には、ポリ(パラフェニレンビニレン)[PPV]の誘導体、ポリ(2,5 - ジアルコキシ - 1,4 - フェニレンビニレン)[RO-PPV]

10

20

30

40

50

、ポリ(2-(2'-エチル-ヘキソキシ)-5-メトキシ-1,4-フェニレンビニレン)[M E H - P P V]、ポリ(2-(ジアルコキシフェニル)-1,4-フェニレンビニレン)[R O P h - P P V]等が挙げられる。ポリパラフェニレン系には、ポリパラフェニレン[P P P]の誘導体、ポリ(2,5-ジアルコキシ-1,4-フェニレン)[R O - P P P]、ポリ(2,5-ジヘキソキシ-1,4-フェニレン)等が挙げられる。ポリチオフェン系には、ポリチオフェン[P T]の誘導体、ポリ(3-アルキルチオフェン)[P A T]、ポリ(3-ヘキシルチオフェン)[P H T]、ポリ(3-シクロヘキシルチオフェン)[P C H T]、ポリ(3-シクロヘキシル-4-メチルチオフェン)[P C H M T]、ポリ(3,4-ジシクロヘキシルチオフェン)[P D C H T]、ポリ[3-(4-オクチルフェニル)-チオフェン][P O P T]、ポリ[3-(4-オクチルフェニル)-2,2ビチオフェン][P T O P T]等が挙げられる。ポリフルオレン系には、ポリフルオレン[P F]の誘導体、ポリ(9,9-ジアルキルフルオレン)[P D A F]、ポリ(9,9-ジオクチルフルオレン)[P D O F]等が挙げられる。

10

## 【0158】

なお、正孔輸送性の高分子系有機発光材料を、陽極と発光性の高分子系有機発光材料の間に挟んで形成すると、陽極からの正孔注入性を向上させることができる。一般にアクセプター材料と共に水に溶解させたものをスピンコート法などで塗布する。また、有機溶媒には不溶であるため、上述した発光性の有機発光材料との積層が可能である。正孔輸送性の高分子系有機発光材料としては、P E D O Tとアクセプター材料としてのショウノウスルホン酸(C S A)の混合物、ポリアニリン[P A N I]とアクセプター材料としてのポリスチレンスルホン酸[P S S]の混合物等が挙げられる。

20

## 【0159】

また、発光層は単色又は白色の発光を呈する構成とすることができる。白色発光材料を用いる場合には、画素の光放射側に特定の波長の光を透過するフィルター(着色層)を設けた構成としてカラー表示を可能にすることができる。

## 【0160】

白色に発光する発光層を形成するには、例えば、A l q<sub>3</sub>、部分的に赤色発光色素であるナイルレッドをドープしたA l q<sub>3</sub>、A l q<sub>3</sub>、p-E t T A Z、T P D(芳香族ジアミン)を蒸着法により順次積層することで白色を得ることができる。また、スピンコートを用いた塗布法によりE Lを形成する場合には、塗布した後、真空加熱で焼成することが好ましい。例えば、正孔注入層として作用するポリ(エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)水溶液(P E D O T/P S S)を全面に塗布、焼成し、その後、発光層として作用する発光中心色素(1,1,4,4-テトラフェニル-1,3-ブタジエン(T P B)、4-ジシアノメチレン-2-メチル-6-(p-ジメチルアミノ-スチリル)-4H-ピラン(D C M 1)、ナイルレッド、クマリン6など)ドープしたポリビニルカルバゾール(P V K)溶液を全面に塗布、焼成すればよい。

30

## 【0161】

発光層は単層で形成することもでき、ホール輸送性のポリビニルカルバゾール(P V K)に電子輸送性の1,3,4-オキサジアゾール誘導体(P B D)を分散させてよい。また、30 wt%のP B Dを電子輸送剤として分散し、4種類の色素(T P B、クマリン6、D C M 1、ナイルレッド)を適定量分散することで白色発光が得られる。ここで示した白色発光が得られる発光素子の他にも、発光層の材料を適宜選択することによって、赤色発光、緑色発光、または青色発光が得られる発光素子を作製することができる。

40

## 【0162】

さらに、発光層は、一重項励起発光材料の他、金属錯体などを含む三重項励起材料を用いても良い。例えば、赤色の発光性の画素、緑色の発光性の画素及び青色の発光性の画素のうち、輝度半減時間が比較的短い赤色の発光性の画素を三重項励起発光材料で形成し、他を一重項励起発光材料で形成する。三重項励起発光材料は発光効率が良いので、同じ輝度を得るのに消費電力が少なくて済むという特徴がある。すなわち、赤色画素に適用した場合、発光素子に流す電流量が少なくて済むので、信頼性を向上させることができる。

50

低消費電力化として、赤色の発光性の画素と緑色の発光性の画素とを三重項励起発光材料で形成し、青色の発光性の画素を一重項励起発光材料で形成しても良い。人間の視感度が高い緑色の発光素子も三重項励起発光材料で形成することで、より低消費電力化を図ることができる。

#### 【0163】

三重項励起発光材料の一例としては、金属錯体をドーパントとして用いたものがあり、第三遷移系列元素である白金を中心金属とする金属錯体、イリジウムを中心金属とする金属錯体などが知られている。三重項励起発光材料としては、これらの化合物に限られることはなく、上記構造を有し、且つ中心金属に周期表の8～10属に属する元素を有する化合物を用いることも可能である。

10

#### 【0164】

以上に掲げる発光層を形成する物質は一例であり、正孔注入輸送層、正孔輸送層、電子注入輸送層、電子輸送層、発光層、電子プロック層、正孔プロック層などの機能性の各層を適宜積層することで発光素子を形成することができる。また、これらの各層を合わせた混合層又は混合接合を形成しても良い。発光層の層構造は変化しうるものであり、特定の電子注入領域や発光領域を備えていない代わりに、もっぱらこの目的用の電極層を備えたり、発光性の材料を分散させて備えたりする変形は、本発明の趣旨を逸脱しない範囲において許容されうるものである。

#### 【0165】

上記のような材料で形成した発光素子は、順方向にバイアスすることで発光する。発光素子を用いて形成する表示装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。いずれにしても、個々の画素は、ある特定のタイミングで順方向バイアスを印加して発光させることとなるが、ある一定期間は非発光状態となっている。この非発光時間に逆方向のバイアスを印加することで発光素子の信頼性を向上させることができる。発光素子では、一定駆動条件下で発光強度が低下する劣化や、画素内で非発光領域が拡大して見かけ上輝度が低下する劣化モードがあるが、順方向及び逆方向にバイアスを印加する交流的な駆動を行うことで、劣化の進行を遅くすることができ、発光装置の信頼性を向上させることができる。また、デジタル駆動、アナログ駆動どちらでも適用可能である。

20

#### 【0166】

よって、封止基板にカラーフィルタ（着色層）を形成してもよい。カラーフィルタ（着色層）は、蒸着法や液滴吐出法によって形成することができ、カラーフィルタ（着色層）を用いると、高精細な表示を行うこともできる。カラーフィルタ（着色層）により、各RGBの発光スペクトルにおいてプロードなピークを鋭いピークになるように補正できるからである。

30

#### 【0167】

以上、各RGBの発光を示す材料を形成する場合を説明したが、単色の発光を示す材料を形成し、カラーフィルタや色変換層を組み合わせることによりフルカラー表示を行うことができる。カラーフィルタ（着色層）や色変換層は、例えば第2の基板（封止基板）に形成し、基板へ張り合わせればよい。

40

#### 【0168】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの表示装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

#### 【0169】

上記構成において、陰極としては、仕事関数が小さい材料を用いることが可能で、例えば、Ca、Al、CaF、MgAg、AlLi等が望ましい。電界発光層は、単層型、積層型、また層の界面がない混合型のいずれでもよい。またシングレット材料、トリプレット材料、又はそれらを組み合わせた材料や、有機化合物又は無機化合物を含む電荷注入輸送物質及び発光材料で形成し、その分子数から低分子系有機化合物、中分子系有機化合

50

物（昇華性を有さず、且つ分子数が 20 以下、又は連鎖する分子の長さが 10 μm 以下の有機化合物を指している）、高分子系有機化合物から選ばれた一種又は複数種の層を含み、電子注入輸送性又は正孔注入輸送性の無機化合物と組み合わせてもよい。第 1 の電極層は光を透過する透明導電膜を用いて形成し、例えば ITO、ITSO の他、酸化インジウムに 2 ~ 20 atom % の酸化亜鉛 (ZnO) を混合した透明導電膜を用いる。なお、第 1 の電極層を形成する前に、酸素雰囲気中のプラズマ処理や真空雰囲気下での加熱処理を行うとよい。隔壁（土手ともいう）は、珪素を含む材料、有機材料及び化合物材料を用いて形成する。また、多孔質膜を用いても良い。但し、アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに（破れることなく）形成されるため好ましい。本実施の形態は、上記の実施の形態と自由に組み合わせることが可能である。

10

#### 【0170】

本発明を用いると、信頼性の高い表示装置を簡略化した工程で作製することができる。よって、高精細、高画質な表示装置を低いコストで歩留まり良く製造することができる。

#### 【0171】

本実施の形態は、実施の形態 1 乃至 3 とそれぞれと組み合わせて用いることが可能である。

#### 【0172】

##### (実施の形態 5)

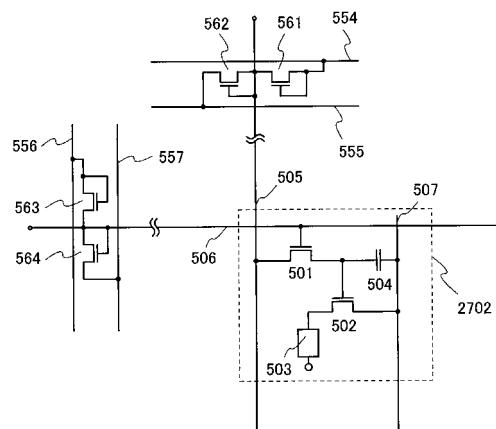

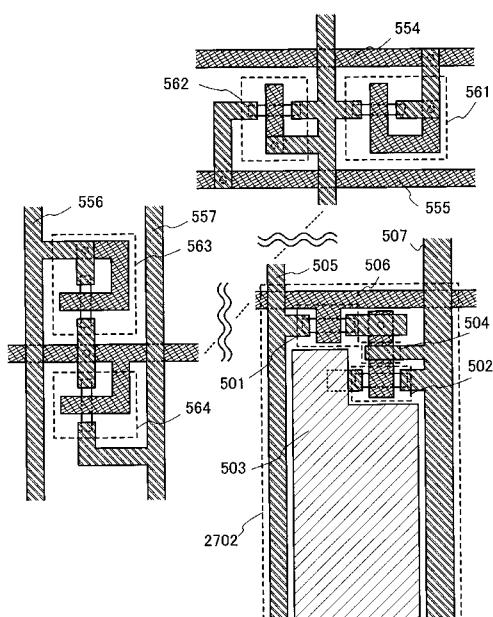

走査線側入力端子部と信号線側入力端子部とに保護ダイオードを設けた一態様について図 15 を参照して説明する。図 15において画素 2702 には TFT501、TFT502、容量素子 504、発光素子 503 が設けられている。この TFT は実施の形態 1 と同様な構成を有している。

20

#### 【0173】

信号線側入力端子部には、保護ダイオード 561 と保護ダイオード 562 が設けられている。この保護ダイオードは、TFT501 若しくは TFT502 と同様な工程で作製され、ゲートとドレイン若しくはソースの一方とを接続することによりダイオードとして動作させている。図 15 で示す上面図の等価回路図を図 14 に示している。

30

#### 【0174】

保護ダイオード 561 は、ゲート電極層、半導体層、配線層から成っている。保護ダイオード 562 も同様な構造である。この保護ダイオードと接続する共通電位線 554、共通電位線 555 はゲート電極層と同じ層で形成している。従って、配線層と電気的に接続するには、絶縁層にコンタクトホールを形成する必要がある。

#### 【0175】

絶縁層へのコンタクトホールは、マスク層を形成し、エッチング加工すれば良い。この場合、大気圧放電のエッチング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

#### 【0176】

信号配線層は TFT501 におけるソース及びドレイン配線層 505 と同じ層で形成され、それに接続している信号配線層とソース又はドレイン側が接続する構造となっている。

40

#### 【0177】

走査信号線側の入力端子部も同様な構成である。保護ダイオード 563 は、ゲート電極層、半導体層、配線層から成っている。保護ダイオード 564 も同様な構造である。この保護ダイオードと接続する共通電位線 556、共通電位線 557 はソース及びドレイン配線層と同じ層で形成している。入力段に設けられる保護ダイオードを同時に形成することができる。なお、保護ダイオードを挿入する位置は、本実施の形態のみに限定されず、駆動回路と画素との間に設けることもできる。

#### 【0178】

50

## (実施の形態 6 )

本発明によって形成される表示装置によって、テレビジョン装置を完成させることができる。表示パネルには、図16(A)で示すような構成として画素部のみが形成されて走査線側駆動回路と信号線側駆動回路とが、図17(B)のようなTAB方式により実装される場合と、図17(A)のようなCOG方式により実装される場合と、図16(B)に示すようにSASでTFTを形成し、画素部と走査線側駆動回路を基板上に一体形成し信号線側駆動回路を別途ドライバICとして実装する場合、また図16(C)のように画素部と信号線側駆動回路と走査線側駆動回路を基板上に一体形成する場合などがあるが、どのような形態としても良い。

## 【0179】

10 その他の外部回路の構成として、映像信号の入力側では、チューナで受信した信号のうち、映像信号を増幅する映像信号增幅回路と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路などからなっている。コントロール回路は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

## 【0180】

チューナで受信した信号のうち、音声信号は、音声信号增幅回路に送られ、その出力は音声信号処理回路を経てスピーカに供給される。制御回路は受信局(受信周波数)や音量の制御情報を入力部から受け、チューナや音声信号処理回路に信号を送出する。

## 【0181】

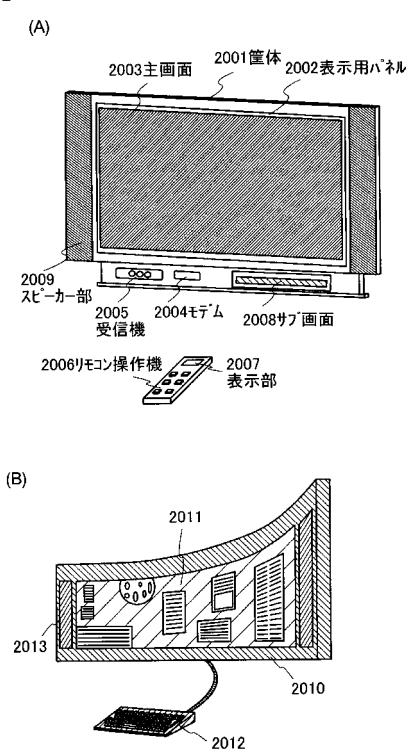

表示モジュールを、図20(A)、(B)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた図1のような表示パネルのことを一般的にはEL表示モジュールともいう。よって図1のようなEL表示モジュールを用いると、ELテレビジョン装置を完成することができる。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えられている。このように、本発明によりテレビジョン装置を完成させることができる。

## 【0182】

また、位相差板や偏光板を用いて、外部から入射する光の反射光を遮断するようにしてもよい。また上面放射型の表示装置ならば、隔壁となる絶縁層を着色しブラックマトリクスとして用いてもよい。この隔壁は液滴吐出法などによっても形成することができ、顔料系の黒色樹脂や、ポリイミドなどの樹脂材料に、カーボンブラック等を混合させてよく、その積層でもよい。液滴吐出法によって、異なった材料を同領域に複数回吐出し、隔壁を形成してもよい。位相差板、位相差板としては /4板、/2板を用い、光を制御できるように設計すればよい。構成としては、順にTFT素子基板、発光素子、封止基板(封止材)、位相差板、位相差板(/4板、/2板)、偏光板となり、発光素子から放射された光は、これらを通過し偏光板側より外部に放射される。この位相差板や偏光板は光が放射される側に設置すればよく、両面放射される両面放射型の表示装置であれば両方に設置することもできる。また、偏光板の外側に反射防止膜を有していても良い。これにより、より高繊細で精密な画像を表示することができる。

## 【0183】

40 図20(A)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モ뎀2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。

## 【0184】

10

20

30

40

50

また、テレビジョン装置にも、主画面 2003 の他にサブ画面 2008 を第 2 の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面 2003 を視野角の優れた E L 表示用パネルで形成し、サブ画面を低消費電力で表示可能な液晶表示用パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面 2003 を液晶表示用パネルで形成し、サブ画面を E L 表示用パネルで形成し、サブ画面は点滅可能とする構成としても良い。本発明を用いると、このような大型基板を用いて、多くの T F T や電子部品を用いても、信頼性の高い表示装置とすることができる。

#### 【 0 1 8 5 】

図 20 ( B ) は例えば 20 ~ 80 インチの大型の表示部を有するテレビジョン装置であり、筐体 2010 、操作部であるキー ボード部 2012 、表示部 2011 、スピーカー部 2013 等を含む。本発明は、表示部 2011 の作製に適用される。図 20 ( B ) の表示部は、わん曲可能な物質を用いているので、表示部がわん曲したテレビジョン装置となっている。このように表示部の形状を自由に設計することができるので、所望な形状のテレビジョン装置を作製することができる。

#### 【 0 1 8 6 】

本発明により、簡略な工程で表示装置を形成できるため、コストダウンも達成できる。よって本発明を用いたテレビジョン装置では、大画面の表示部を有しても低いコストで形成できる。よって高性能、高信頼性のテレビジョン装置を歩留まりよく作製することができる。

#### 【 0 1 8 7 】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

#### 【 0 1 8 8 】

##### ( 実施の形態 7 )

本発明を適用して、様々な表示装置を作製することができる。即ち、それら表示装置を表示部に組み込んだ様々な電子機器に本発明を適用できる。

#### 【 0 1 8 9 】

その様な電子機器としては、ビデオカメラ、デジタルカメラ等のカメラ、プロジェクター、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、カーステレオ、パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc ( D V D ) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それらの例を図 21 に示す。

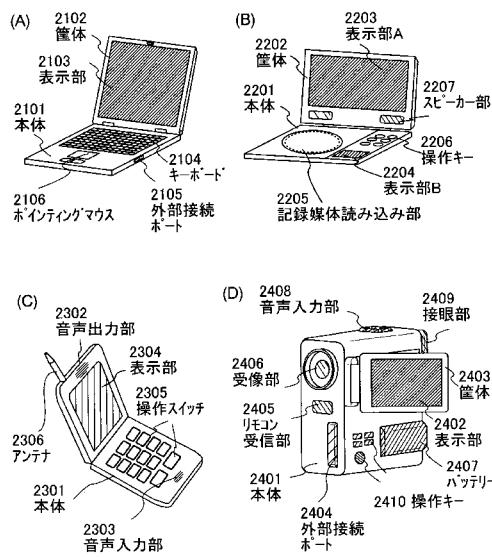

#### 【 0 1 9 0 】

図 21 ( A ) は、コンピュータであり、本体 2101 、筐体 2102 、表示部 2103 、キー ボード 2104 、外部接続ポート 2105 、ポインティングマウス 2106 等を含む。本発明を用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示するコンピュータを完成させることができる。

#### 【 0 1 9 1 】

図 21 ( B ) は記録媒体を備えた画像再生装置（具体的には D V D 再生装置）であり、本体 2201 、筐体 2202 、表示部 A 2203 、表示部 B 2204 、記録媒体（ D V D 等）読み込み部 2205 、操作キー 2206 、スピーカー部 2207 等を含む。表示部 A 2203 は主として画像情報を表示し、表示部 B 2204 は主として文字情報を表示する。本発明を用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示する画像再生装置を完成させることができる。

#### 【 0 1 9 2 】

図 21 ( C ) は携帯電話であり、本体 2301 、音声出力部 2302 、音声入力部 2303 、表示部 2304 、操作スイッチ 2305 、アンテナ 2306 等を含む。本発明を用いると、

10

20

30

40

50

用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示する携帯電話を完成することができる。

【0193】

図21(D)はビデオカメラであり、本体2401、表示部2402、筐体2403、外部接続ポート2404、リモコン受信部2405、受像部2406、バッテリー2407、音声入力部2408、接眼部2409、操作キー2410等を含む。本発明を用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示できるビデオカメラを完成することができる。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

【図面の簡単な説明】

10

【0194】

【図1】本発明の表示装置を説明する図。

【図2】本発明の表示装置の作製方法を説明する図。

【図3】本発明の表示装置の作製方法を説明する図。

【図4】本発明の表示装置の作製方法を説明する図。

【図5】本発明の表示装置の作製方法を説明する図。

【図6】本発明の表示装置の作製方法を説明する図。

【図7】本発明の表示装置の作製方法を説明する図。

【図8】本発明の表示装置を説明する図。

【図9】本発明の表示装置を説明する図。

20

【図10】本発明の表示装置を説明する図。

【図11】本発明の表示装置を説明する図。

【図12】本発明の表示装置を説明する図。

【図13】本発明に適用できる発光素子の構成を説明する図。

【図14】図15で説明するEL表示装置の等価回路図。

【図15】本発明の表示装置を説明する上面図。

【図16】本発明の表示装置の上面図。

【図17】本発明の表示装置の上面図。

【図18】本発明の表示装置の上面図。

【図19】本発明に適用することのできる滴下注入法を説明する図。

30

【図20】本発明が適用される電子機器を示す図。

【図21】本発明が適用される電子機器を示す図。

【図22】本発明の表示装置を説明する図。

【図23】本発明の表示装置を説明する図。

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(51)Int.Cl. F I テーマコード(参考)

H 05B 33/04 (2006.01) H 05B 33/04

F ターム(参考) 5C094 AA21 AA31 AA42 AA43 AA44 BA03 BA29 DA07 DA13 EC03

HA08 HA10

5G435 AA13 AA16 AA17 BB05 CC09 KK05 LL04 LL08