(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

**(19) World Intellectual Property Organization**

International Bureau

A standard linear barcode is located at the bottom of the page, spanning most of the width. It is used for document tracking and identification.

**(43) International Publication Date

28 July 2011 (28.07.2011)**

(10) International Publication Number

**WO 2011/091323 A1**

(51) International Patent Classification:

*G06F 15/00 (2006.01) G06F 15/76 (2006.01)*

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

**(21) International Application Number:** PCT/US2011/022152

**(22) International Filing Date:** 21 January 2011 (21.01.2011)

**(25) Filing Language:** English

**(26) Publication Language:** English

**(30) Priority Data:** 61/297,139 21 January 2010 (21.01.2010) US

(71) **Applicant** (for all designated States except US): QST

**HOLDINGS, LLC** [US/US]; 1800 Embarcadero Road, Palo Alto, CA 94303 (US).

(72) Inventors; and

(75) Inventors/Applicants (*for US only*): **MASTER, Paul, L.** [US/US]; 796 Dartshire Way, Sunnyvale, CA 94087 (US). **FURTEK, Frederick** [US/US]; 2470 Sharon Oaks Drive, Menlo Park, CA 94025 (US).

(74) **Agent: TANG, Wayne, L.**; Nixon Peabody LLP, 300 S. Riverside Plaza, 16th Floor, Chicago, IL 60606 (US).

(84) **Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— with international search report (Art. 21(3))

**(54) Title: A METHOD AND APPARATUS FOR A GENERAL-PURPOSE, MULTIPLE-CORE SYSTEM FOR IMPLEMENTING STREAM-BASED COMPUTATIONS**

FIG. 1

**(57) Abstract:** A method and system of efficient use and programming of a multi-processing core device. The system includes a programming construct that is based on stream-domain code. A programmable core based computing device is disclosed. The computing device includes a plurality of processing cores coupled to each other. A memory stores stream-domain code including a stream defining a stream destination module and a stream source module. The stream source module places data values in the stream and the stream conveys data values from the stream source module to the stream destination module. A runtime system detects when the data values are available to the stream destination module and schedules the stream destination module for execution on one of the plurality of processing cores.

## A METHOD AND APPARATUS FOR A GENERAL-PURPOSE, MULTIPLE-CORE SYSTEM FOR IMPLEMENTING STREAM-BASED COMPUTATIONS

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application claims priority to Provisional Application Serial No. 61/297,139 filed January 21, 2010. This application is related to U.S. patent application Ser. No. 09/815,122, filed on Mar. 22, 2001, now U.S. Patent No. 6,836,839 entitled “ADAPTIVE INTEGRATED CIRCUITRY WITH HETEROGENEOUS AND RECONFIGURABLE MATRICES OF DIVERSE AND ADAPTIVE COMPUTATIONAL UNITS HAVING FIXED, APPLICATION SPECIFIC COMPUTATIONAL ELEMENTS”; U.S. patent application Ser. No. 10/384,486, now U.S. Patent No. 7,325,123 entitled HIERARCHICAL INTERCONNECT FOR CONFIGURING SEPARATE INTERCONNECTS FOR EACH GROUP OF FIXED AND DIVERSE COMPUTATIONAL ELEMENTS”; and U.S. patent application Ser. No. 10/443,501, now U.S. Patent No. 7,609,297 entitled “HARDWARE TASK MANAGER.” All of these applications are hereby incorporated by reference.

### TECHNICAL FIELD

**[0002]** This invention relates in general to programming multiple processor systems and more specifically to a hardware task manager that efficiently utilizes parallel programming constructs incorporating both streams and threads.

### BACKGROUND

**[0003]** A common limitation to processing performance in a digital system is the efficiency and speed of transferring instruction, data and other information among different components and subsystems within the digital system. For example, the bus speed in a general-purpose Von Neumann architecture dictates how fast data can be transferred between the processor and memory and, as a result, places a limit on the computing performance (e.g., million instructions per second (MIPS), floating-point operations per second (FLOPS), etc.).

**[0004]** Other types of computer architecture design, such as multi-processor or parallel processor designs require complex communication, or interconnection, capabilities so that each of the different processors can communicate with other processors, with multiple memory devices, input/output (I/O) ports, etc. With today's complex processor system designs, the importance of an efficient and fast interconnection facility rises dramatically.

**[0005]** However, such facilities are difficult to design to optimize goals of speed, flexibility and simplicity of design.

**[0006]** Currently, parallel programming is based on threads as the central, organizing principle of computing. However, threads are seriously flawed as a computation model because they are wildly nondeterministic and rely on programming style to constrain that non-determinism to achieve deterministic aims. Test and verification become difficult in the presence of this wild non-determinism. One solution has been suggested by GPU (Graphics Processing Unit) vendors is to narrow the forms of parallelism expressible in the programming model. Their focus on data parallelism, however, ties the hands of programmers and prevents exploiting the full potential of multi-core processors.

**[0007]** Further, threads do not just run on a bank of identical cores. A modern computer (supercomputer, workstation, desktop and laptops) contains a bewildering array of different heterogeneous cores all requiring separate programming models to program. For example, a motherboard may have one to four main CPUs (central processing units e.g., Pentium Processor) each having on-die 1 to 6 CPU cores with an on-die or on-package GPU (Graphics Processing Unit – e.g. NVIDIA GPU) which itself contains 16 to 256 GPU cores along with several discrete video & audio encode & decode cores (for the encoding and decoding of a multiplicity of video standards – e.g. MPEG2, MPEG4, VC-1, H.264 etc.). Also on the motherboard are from 1 to 4 discrete high end GPUs each containing 16 to 1024 GPU cores along with several discrete high-end configurable (meaning the core can be selected to encode/deocode a variety of pre-existing standards) video/audio encode & decode cores (for the encoding and decoding of a multiplicity of video standards – e.g. MPEG2, MPEG4, VC-1, H.264 etc., at very high resolutions and with multiple channels of sound). Additional subsystems composed of processing cores are added to the motherboard in the form of communications cores (e.g. TCP/IP offload cores which themselves are typical built from one or more CPU cores and one or more packet processing cores. WiFi cores, Blue Tooth cores, WiMax cores, 3G cores, 4G cores which are from one or more CPU cores and one or more broadband/baseband processing cores).

**[0008]** Current high end of the spectrum devices such as supercomputers add an additional processor in the form of one to four FPGAs (field programmable gate array) per motherboard. Each FPGA is itself composed of hundreds of thousand to tens of millions of very simplistic CLB processing cores along with multiple hard IP or Soft IP CPU core and multiple DSP cores). Then these motherboards themselves are then replicated and

interconnected in the hundreds to thousands to produce a modern supercomputer. These systems (either the desktops/workstations/laptops and/or the supercomputers) and then interconnected via the Internet to provide national and global computing capabilities.

**[0009]** The complexity of “managing” and “programming” such a diverse series of cores is a severe problem. Most programmers do not even attempt this and just settle for programming just one CPU core ignoring the rest of the cores. There are a certain number of algorithms known in the industry as “embarrassingly parallel problems” (e.g. the Google Search algorithm for example is simple to spread across multiple CPUs due to the fact that there is very little to no interactivity across the parallel threads). Unfortunately the vast majority of problems do not have these characteristics, they require a high degree of interactivity and synchronization across the multiple threads.

**[0010]** It would therefore be desirable to incorporate multithreading, unrestricted parallelism and deterministic behavior such as in modern programming language streams. Streams date at least to the introduction of the C programming language in 1978, and have been incorporated into such languages as C++, Java, Visual Basic and F#. However, in these languages, streams are relegated to a rather narrow role of providing a framework for I/O and file access. It is therefore desirable to expand the role of streams in parallel programming to first-class objects, a status roughly comparable to that of variables.

## SUMMARY

**[0011]** According to one example, a programmable core based computing device is disclosed. The computing device includes a plurality of processing cores coupled to each other. A memory stores stream-domain code including a stream defining a stream destination module and a stream source module. The stream source module places data values in the stream and the stream conveys data values from the stream source module to the stream destination module. A runtime system detects when the data values are available to the stream destination module and schedules the stream destination module for execution on one of the plurality of processing cores.

**[0012]** Additional aspects of the invention will be apparent to those of ordinary skill in the art in view of the detailed description of various embodiments, which is made with reference to the drawings, a brief description of which is provided below.

**BRIEF DESCRIPTION OF THE DRAWINGS**

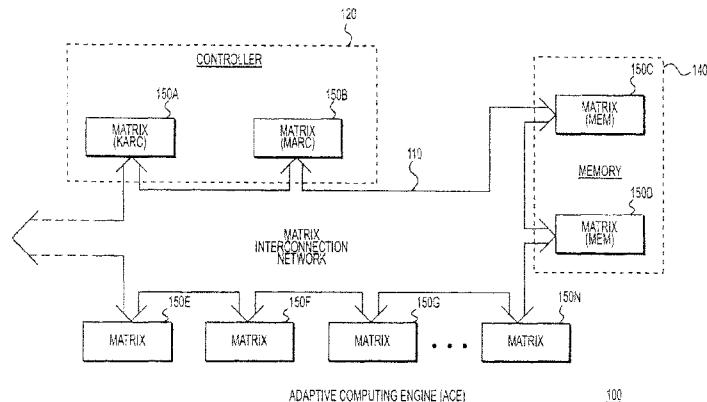

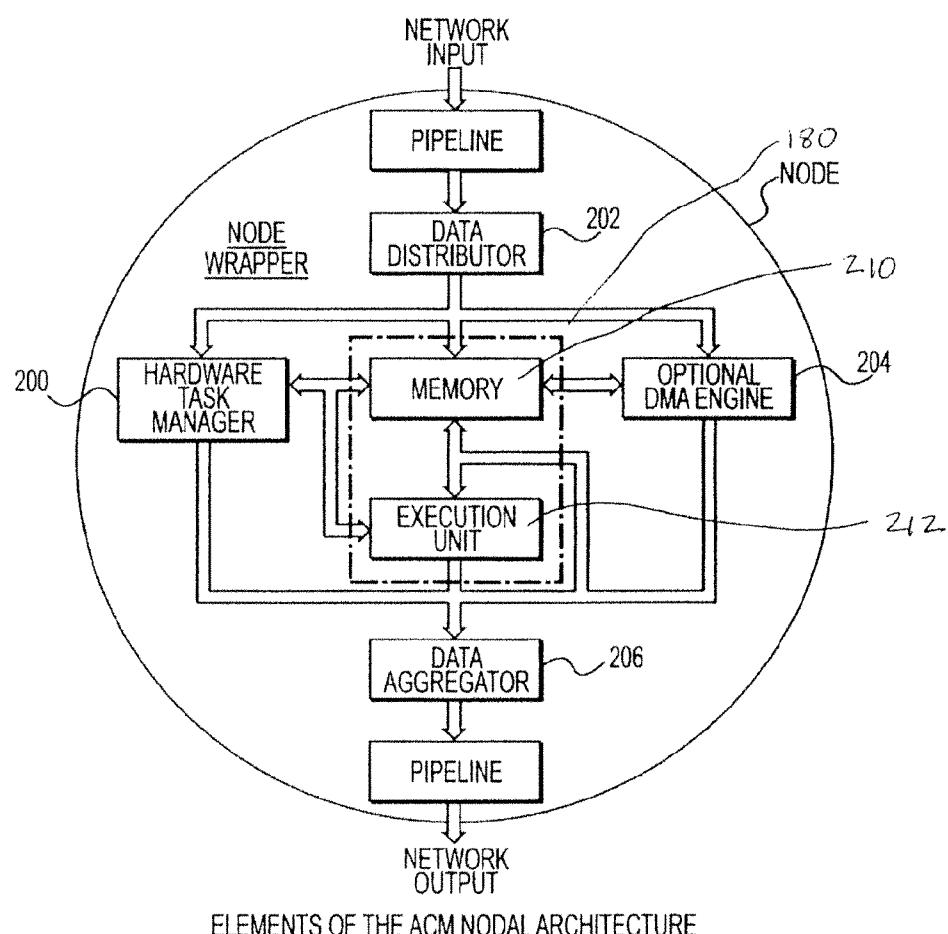

[0013] FIG. 1 shows an overview of an adaptable computing engine compatible with a disclosed stream based programming model;

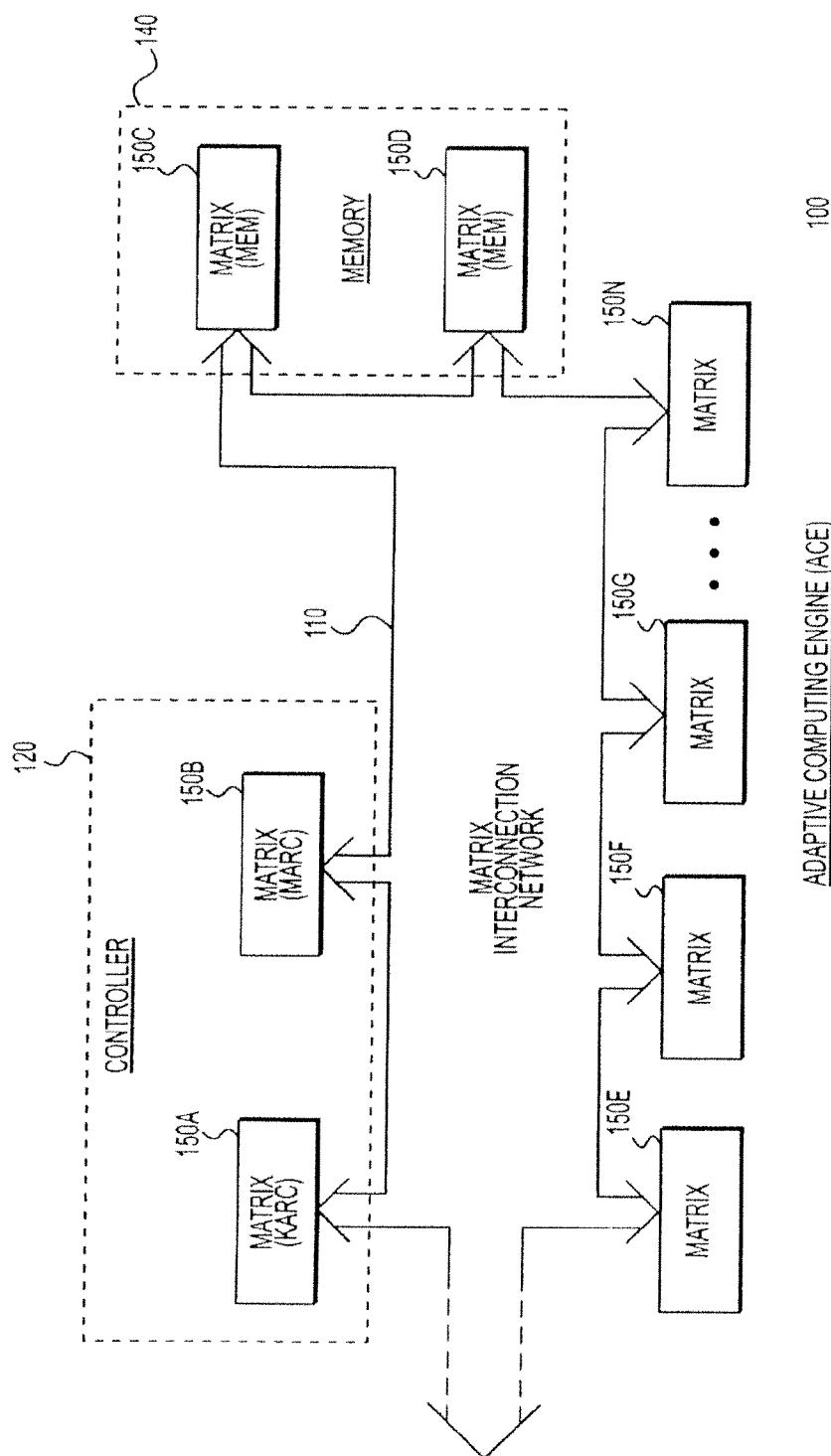

[0014] FIG. 2 illustrates a block diagram of an adaptive computing machine compatible with the programming model;

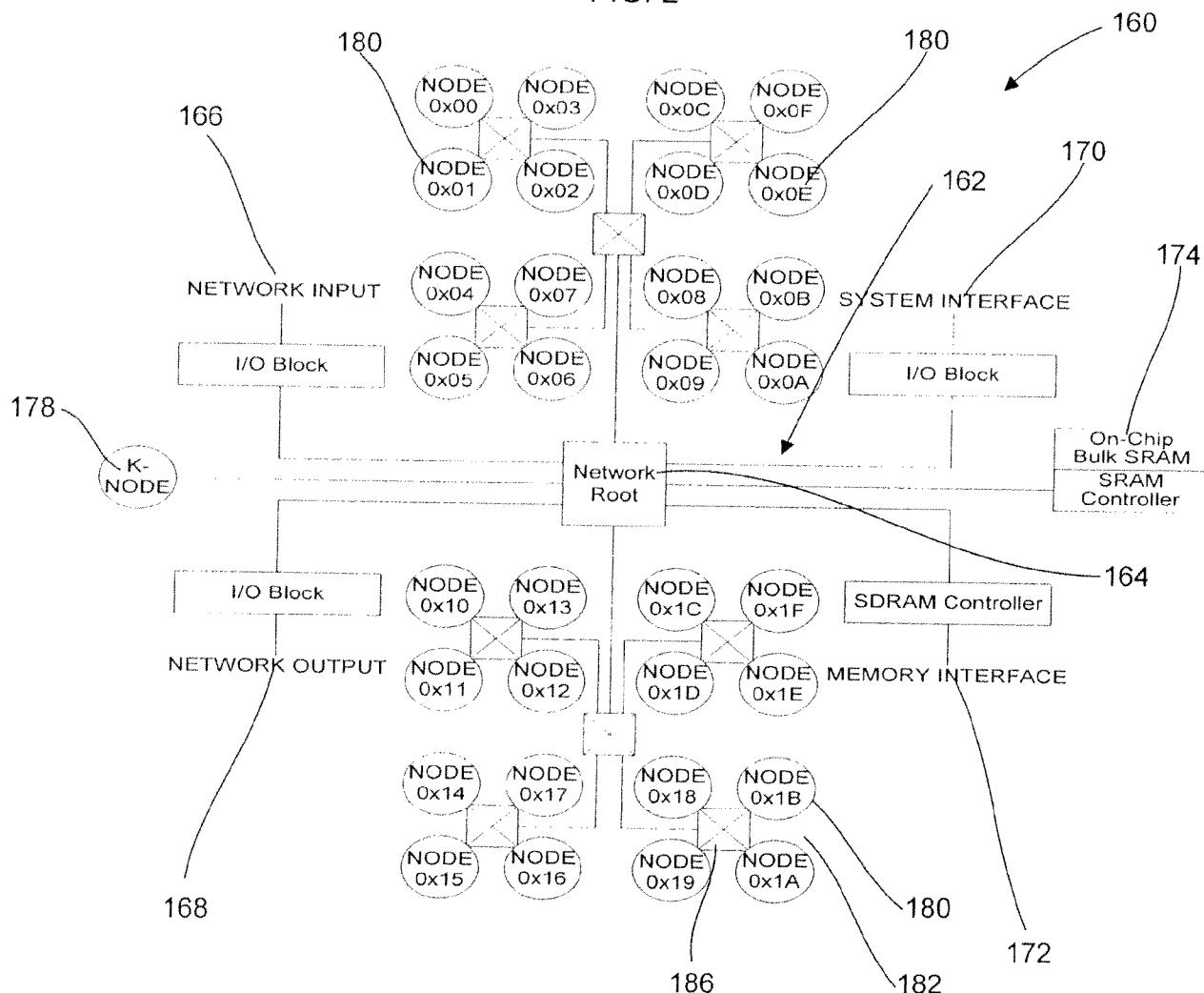

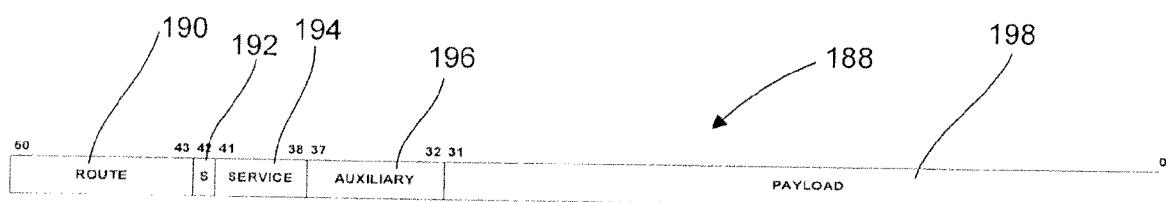

[0015] FIG. 3 is a diagram of a network word in the network of the adaptive computing machine in FIG. 2;

[0016] FIG. 4 illustrates the node wrapper interface between heterogeneous nodes and the homogenous network in the ACE architecture in FIG. 1 or ACM architecture in FIG. 2;

[0017] FIG. 5 shows basic components of a hardware task manager used for the node wrapper in FIG. 4;

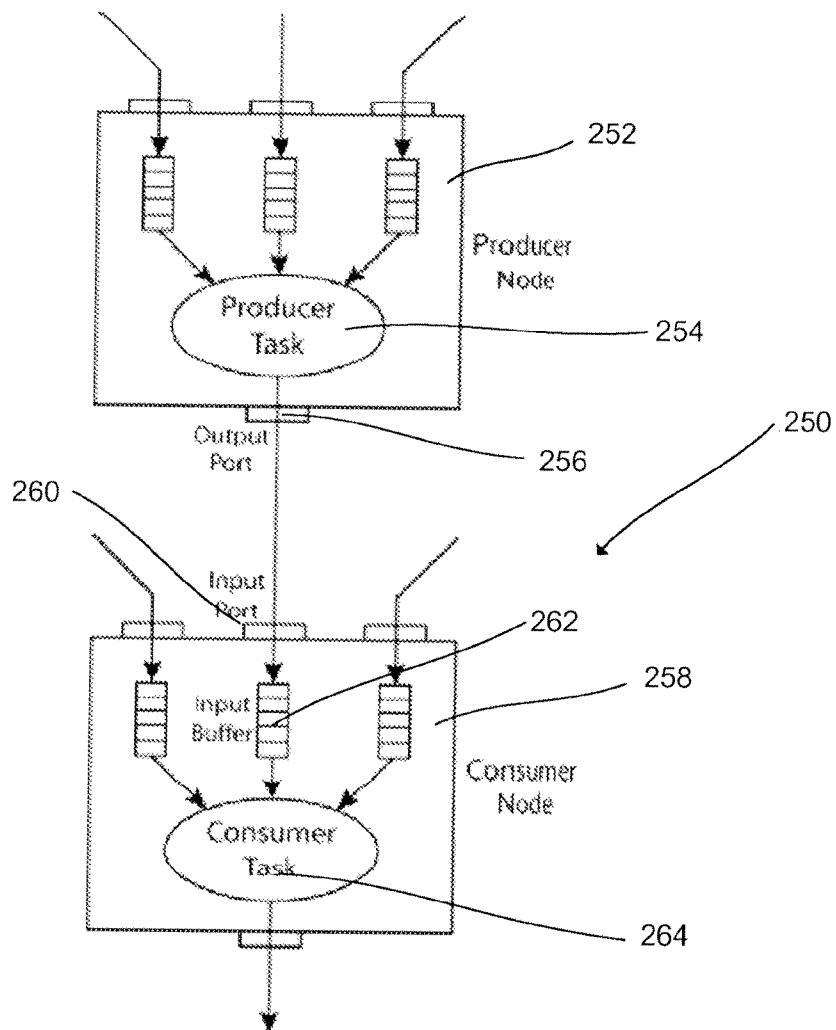

[0018] FIG. 6 shows a point-to-point channel used for streaming data in the ACM architecture in FIG. 2;

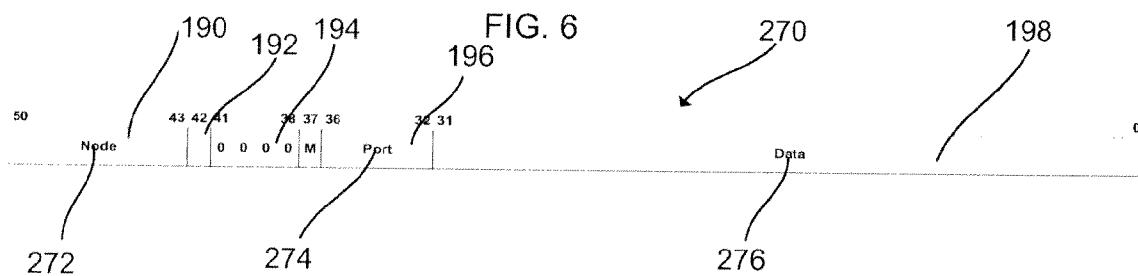

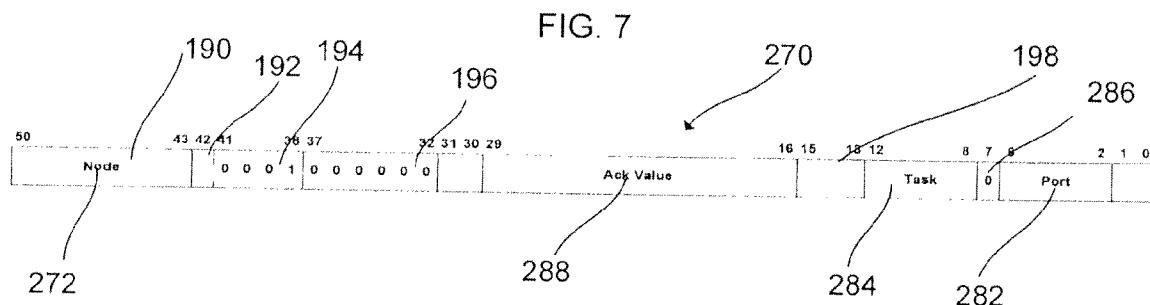

[0019] FIG. 7 shows a point-to-point network word used by the point-to-point channel in FIG. 6;

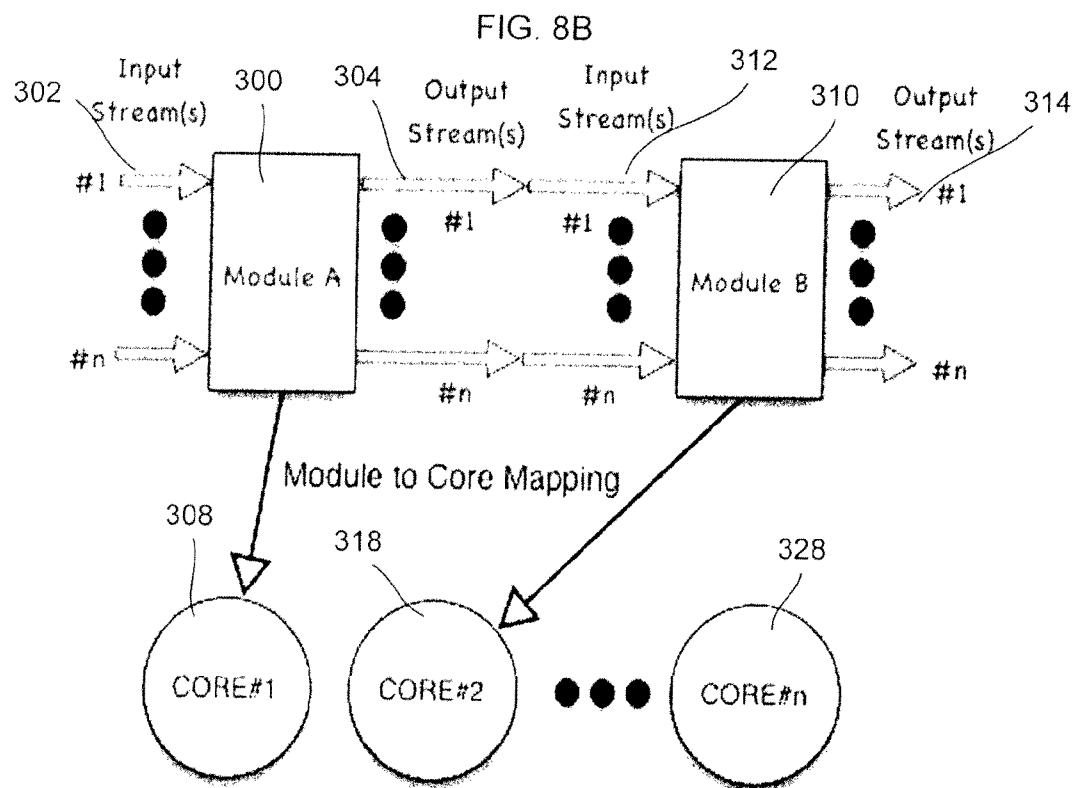

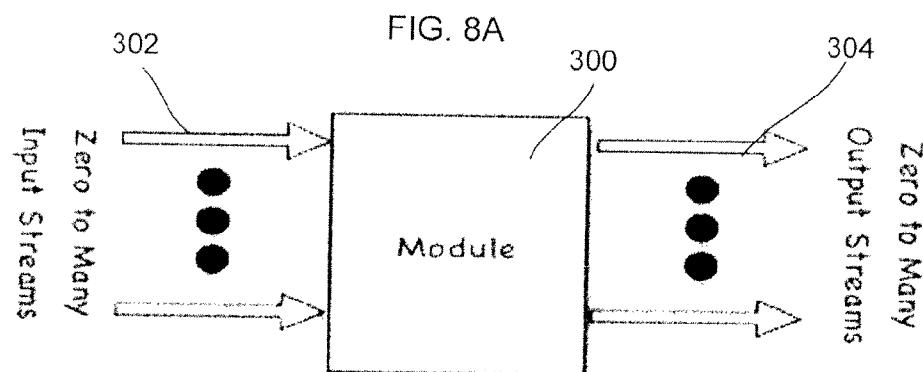

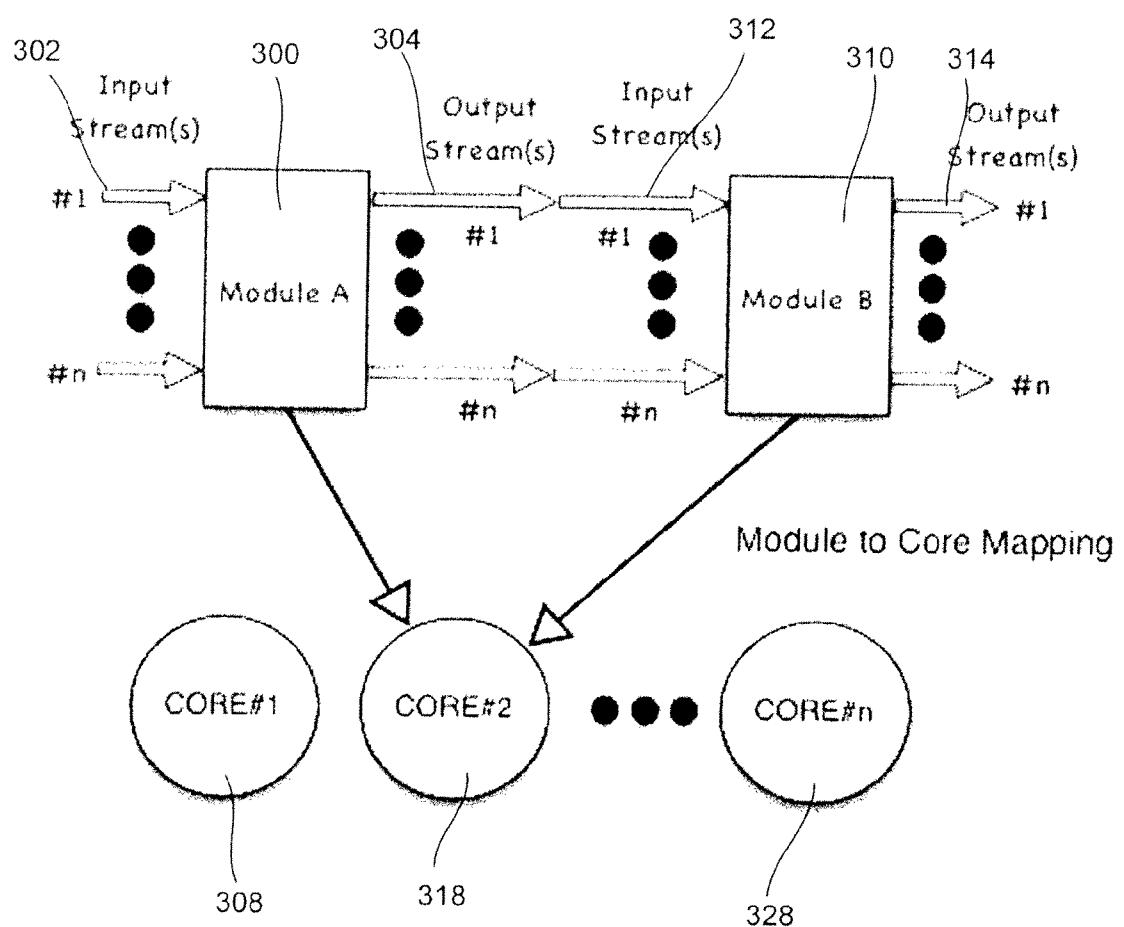

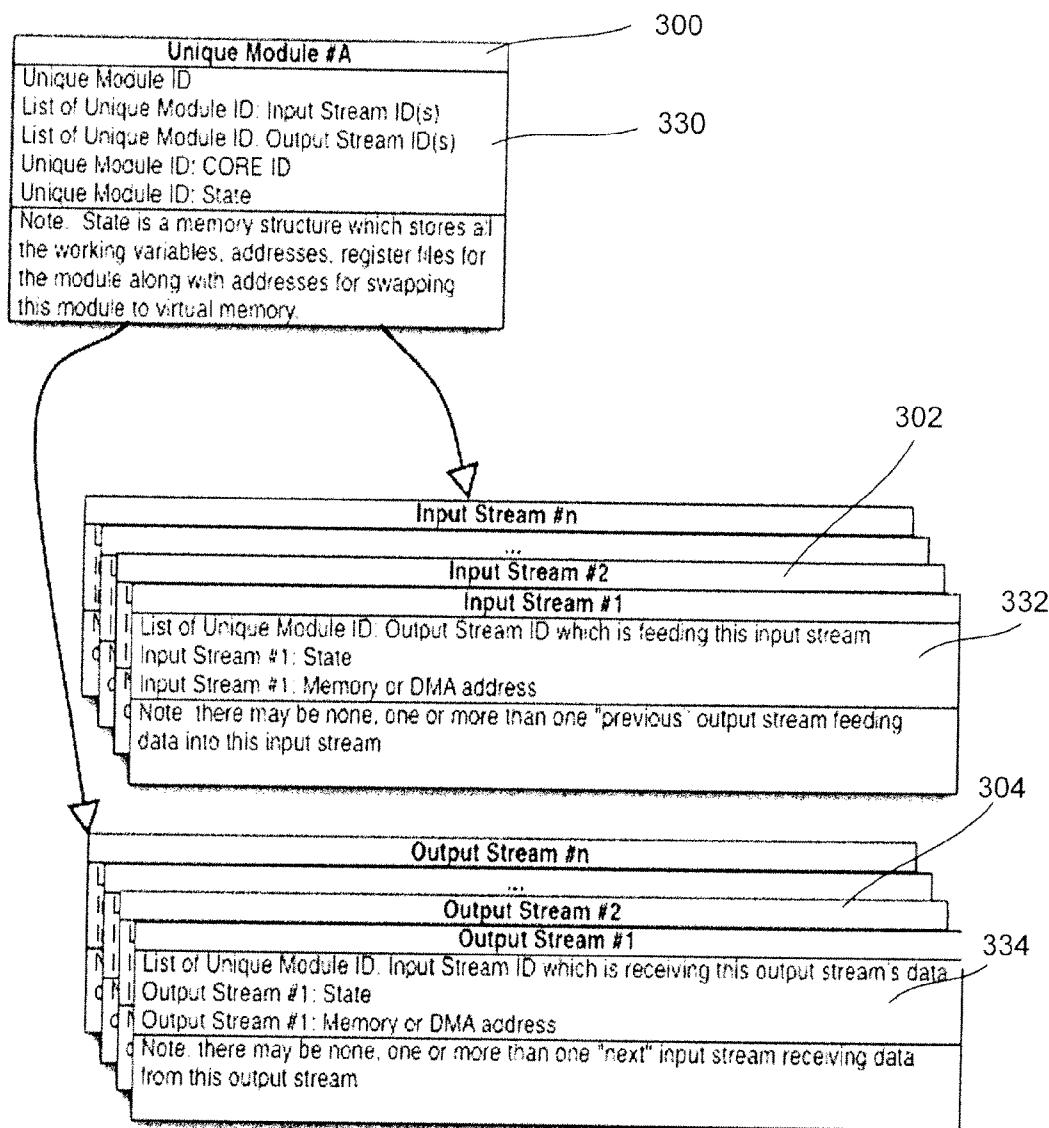

[0020] FIGs. 8A-8D are diagrams of modules in relation to nodes for different stream flows;

[0021] FIGs. 9A and 9B are graphical representations of the assignments of values to streams;

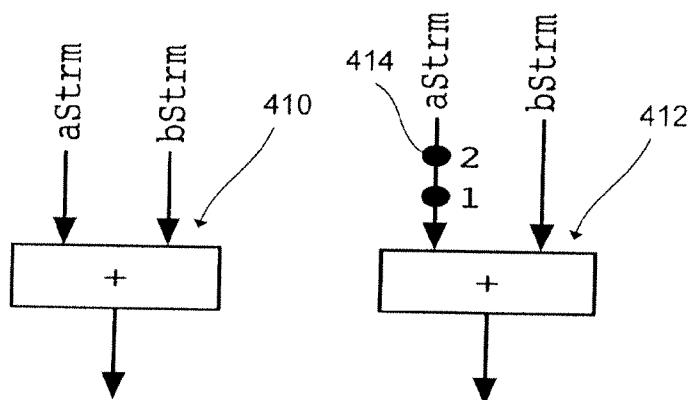

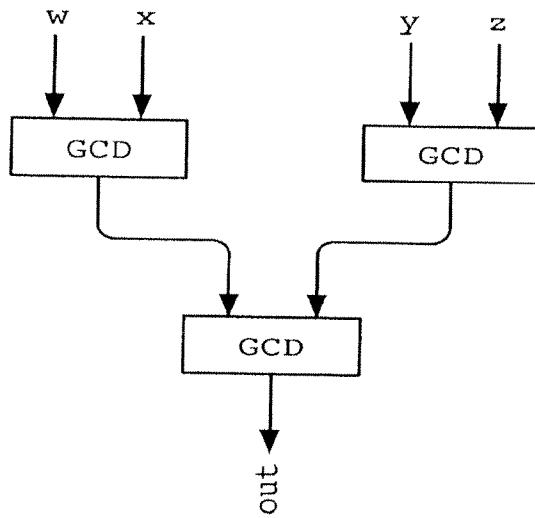

[0022] FIG. 10 is a graphical depiction of a five-tap FIR filter that may be modeled using modules and stream concepts;

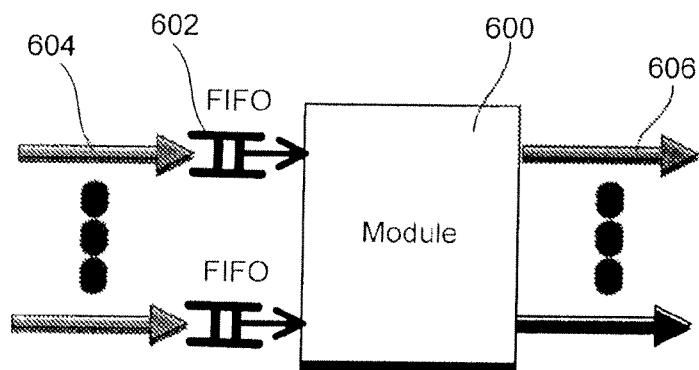

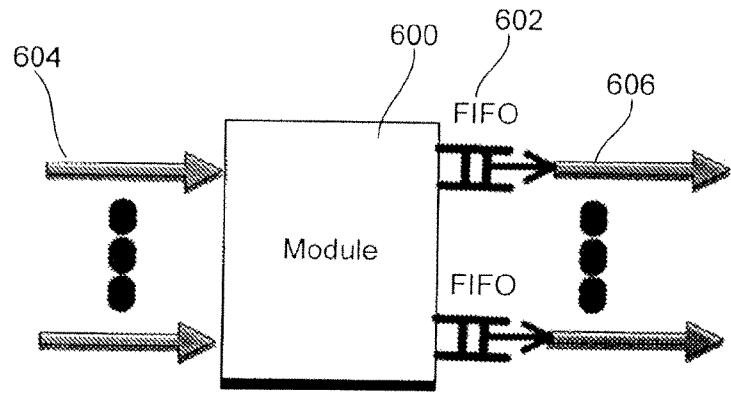

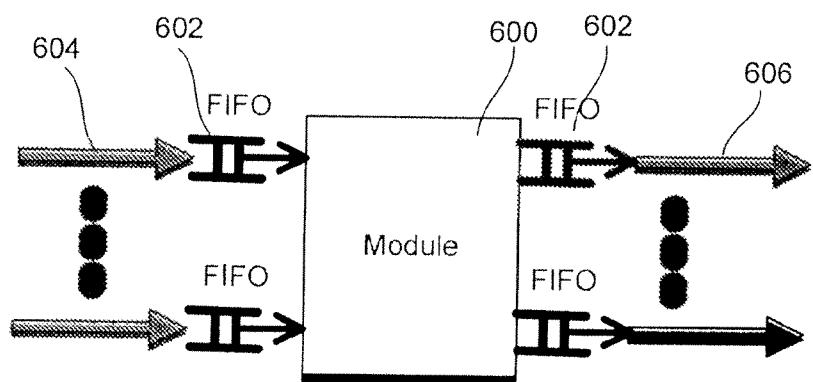

[0023] FIGs. 11A-C are modules with various configurations of FIFO;

[0024] FIG. 12 is a flow diagram of threads used in the example programming language; and

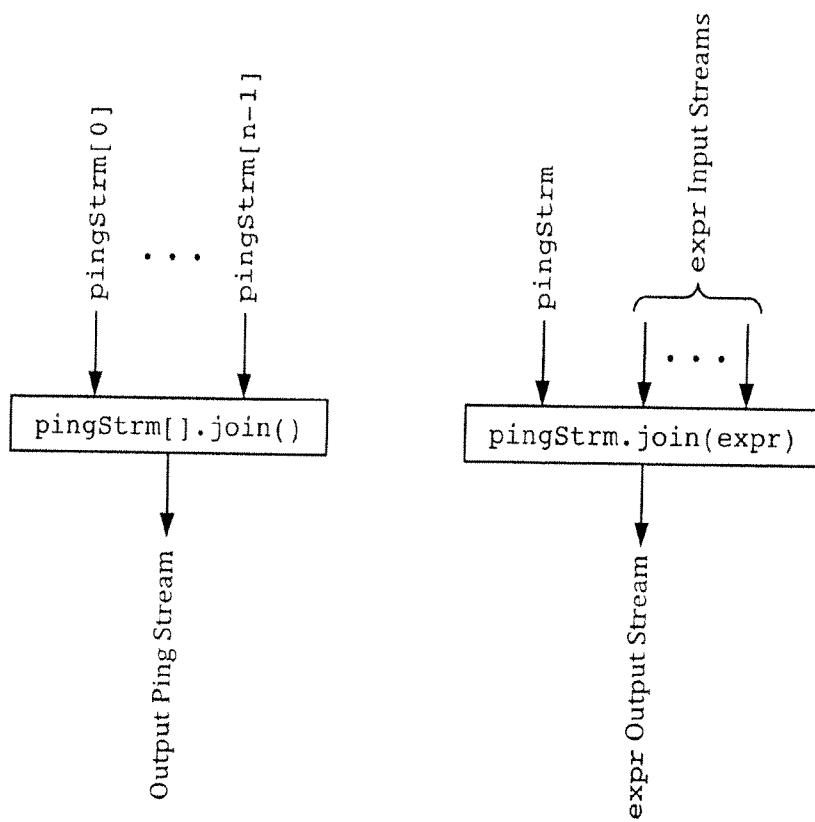

[0025] FIG. 13A-B are diagrams of forms of the join operation of the example programming language.

**DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT****ADAPTIVE COMPUTING ENGINE AND ADAPTIVE COMPUTING MACHINE**

[0026] FIG. 1 is a block diagram illustrating an example of a multi-processor system using an example computational model. Apparatus 100, referred to herein as an adaptive computing engine (ACE) 100, is preferably embodied as an integrated circuit, or as a portion

of an integrated circuit having other, additional components. In the exemplary embodiment, and as discussed in greater detail below, the ACE 100 includes one or more reconfigurable matrices (or nodes) 150, such as matrices 150A through 150N as illustrated, and a matrix interconnection network 110. Also in the exemplary embodiment, and as discussed in detail below, one or more of the matrices 150, such as matrices 150A and 150B, are configured for functionality as a controller 120, while other matrices, such as matrices 150C and 150D, are configured for functionality as a memory 140. The various matrices 150 and matrix interconnection network 110 may also be implemented together as fractal subunits, which may be scaled from a few nodes to thousands of nodes.

**[0027]** In a preferred embodiment, the ACE 100 does not utilize traditional (and typically separate) data, DMA, random access, configuration and instruction busses for signaling and other transmission between and among the reconfigurable matrices 150, the controller 120, and the memory 140, or for other input/output ("I/O") functionality. Rather, data, control and configuration information are transmitted between and among these matrix 150 elements, utilizing the matrix interconnection network 110, which may be configured and reconfigured, in real-time, to provide any given connection between and among the reconfigurable matrices 150, including those matrices 150 configured as the controller 120 and the memory 140.

**[0028]** The matrices 150 configured to function as memory 140 may be implemented in any desired or exemplary way, utilizing computational elements (discussed below) of fixed memory elements, and may be included within the ACE 100 or incorporated within another IC or portion of an IC. In the exemplary embodiment, the memory 140 is included within the ACE 100, and preferably is comprised of computational elements which are low power consumption random access memory (RAM), but also may be comprised of computational elements of any other form of memory, such as flash, DRAM, SRAM, MRAM, ROM, EPROM or E2PROM. In the exemplary embodiment, the memory 140 preferably includes direct memory access (DMA) engines, not separately illustrated.

**[0029]** The controller 120 is preferably implemented, using matrices 150A and 150B configured as adaptive finite state machines (FSMs), as a reduced instruction set ("RISC") processor, controller or other device or IC capable of performing the two types of functionality discussed below. Alternatively, these functions may be implemented utilizing a conventional RISC or other processor. The first control functionality, referred to as "kernel" control, is illustrated as kernel controller ("KARC") of matrix 150A, and the second control

functionality, referred to as "matrix" control, is illustrated as matrix controller ("MARC") of matrix 150B. The kernel and matrix control functions of the controller 120 are explained in greater detail below, with reference to the configurability and reconfigurability of the various matrices 150, and with reference to the exemplary form of combined data, configuration and control information referred to herein as a "silverware" module.

**[0030]** The matrix interconnection network 110 of FIG. 1, includes subset interconnection networks (not shown). These can include a boolean interconnection network, data interconnection network, and other networks or interconnection schemes collectively and generally referred to herein as "interconnect," "interconnection(s)" or "interconnection network(s)," or "networks," and may be implemented generally as known in the art, such as utilizing FPGA interconnection networks or switching fabrics, albeit in a considerably more varied fashion. In the exemplary embodiment, the various interconnection networks are implemented as described, for example, in U.S. Pat. No. 5,218,240, U.S. Pat. No. 5,336,950, U.S. Pat. No. 5,245,227, and U.S. Pat. No. 5,144,166. These various interconnection networks provide selectable (or switchable) connections between and among the controller 120, the memory 140, the various matrices 150, and the computational units (or "nodes") and computational elements, providing the physical basis for the configuration and reconfiguration referred to herein, in response to and under the control of configuration signaling generally referred to herein as "configuration information." In addition, the various interconnection networks (110, 210, 240 and 220) provide selectable or switchable data, input, output, control and configuration paths, between and among the controller 120, the memory 140, the various matrices 150, and the computational units, components and elements, in lieu of any form of traditional or separate input/output busses, data busses, DMA, RAM, configuration and instruction busses.

**[0031]** It should be pointed out, however, that while any given switching or selecting operation of, or within, the various interconnection networks may be implemented as known in the art, the design and layout of the various interconnection networks, in accordance with the present invention, are new and novel, as discussed in greater detail below. For example, varying levels of interconnection are provided to correspond to the varying levels of the matrices, computational units, and elements. At the matrix 150 level, in comparison with the prior art FPGA interconnect, the matrix interconnection network 110 is considerably more limited and less "rich," with lesser connection capability in a given area, to reduce capacitance and increase speed of operation. Within a particular matrix or computational unit,

however, the interconnection network may be considerably more dense and rich, to provide greater adaptation and reconfiguration capability within a narrow or close locality of reference.

**[0032]** The various matrices or nodes 150 are reconfigurable and heterogeneous, namely, in general, and depending upon the desired configuration: reconfigurable matrix 150A is generally different from reconfigurable matrices 150B through 150N; reconfigurable matrix 150B is generally different from reconfigurable matrices 150A and 150C through 150N; reconfigurable matrix 150C is generally different from reconfigurable matrices 150A, 150B and 150D through 150N, and so on. The various reconfigurable matrices 150 each generally contain a different or varied mix of adaptive and reconfigurable nodes, or computational units; the nodes, in turn, generally contain a different or varied mix of fixed, application specific computational components and elements that may be adaptively connected, configured and reconfigured in various ways to perform varied functions, through the various interconnection networks. In addition to varied internal configurations and reconfigurations, the various matrices 150 may be connected, configured and reconfigured at a higher level, with respect to each of the other matrices 150, through the matrix interconnection network 110. Details of the ACE architecture can be found in the related patent applications, referenced above.

**[0033]** Another example of an adaptive computing machine 160 that may use the parallel computational model is shown in FIG. 2. The adaptive computing machine 160 in this example has thirty-two heterogeneous leaf nodes 180 that are coupled together via a network 162. The network 162 has a single root 164 that is coupled to a group of network input ports 166, a group of network output ports 168, an optional system interface port 170, an external memory interface 172 and an internal memory interface 174. A supervisor node or K-node 178 is also coupled to the root 164.

**[0034]** The nodes 180 are each grouped in a quadtrees such as the quadtree 182. The quadtrees such as the quadtree 182 are implemented using 5-ported switch elements 184, each connected to a single parent and up to four children nodes 180. The switch elements implement a fair, round-robin arbitration scheme and provide pipelining with multi-level look-ahead for enhanced performance. In this example, the width of all paths is constant (51 bits), but the option is available to widen pathways as a tree is ascended, in the style of Leiserson's fat trees, in order to increase network bandwidth.

**[0035]** In this example all traffic on the network 162 is in the form of 51-bit network words as shown in the network word 188 shown in FIG. 3. The network word 188 has a route field 190, a security bit 192, a service field 194, an auxiliary field 196 and a payload field 198. The route field 190 is the destination address of the network word 188. The two high-order bits in the route field 190 are the chip ID. The security bit 192 allows peeks (reads) and pokes (writes) to configuration memory. The security bit 192 is set only for words sent by the K-Node 178. The service field 194 defines the type of service and the auxiliary field 196 is dependent on the service type. The service field 194 defines one of sixteen service types including Point-to-Point (PTP) which relates to streaming data and PTP acknowledgement which supports flow control for PTP data and causes a Consumer or Producer Count at the destination node to be incremented or decremented.

#### NODE WRAPPER

**[0036]** FIG. 4 illustrates the interface between heterogeneous nodes and the homogenous network in the ACE architecture in FIG. 1 or the ACM architecture in FIG. 2. This interface is referred to as a "node wrapper" since it is used to provide a common input and output mechanism for each node. A node's execution units and memory are interfaced with the network and with control software via the node wrapper to provide a uniform, consistent system-level programming model. In this example, the node 180 includes a memory 210 and an execution unit 212. Details of the node wrapper can be found in the related patent applications referenced, above.

**[0037]** In a preferred embodiment, each node wrapper includes a hardware task manager (HTM) 200. Node wrappers also include data distributor 202, optional direct memory access (DMA) engine 204 and data aggregator 206. The HTM coordinates execution, or use, of node processors and resources, respectively. The HTM does this by processing a task list and producing a ready-to-run queue. The HTM is configured and controlled by a specialized node referred to as a K-node 178 in FIG. 2 or control node (not shown). However, other HTM control approaches may be used.

**[0038]** The node wrapper in FIG. 4 makes the node 180 identical in outward appearance to all other nodes in the adaptive computing machine 160 in FIG. 2 or the adaptive computing engine 100 in FIG. 1 regardless of its internal structure or functionality. The node wrapper also relieves the execution unit 212 from having to deal with myriad activities associated with task management and network interactions. Among other things, the node wrapper is

responsible for disposing of each incoming network word such as the network word 188 in FIG. 2 in an appropriate fashion in one clock cycle.

**[0039]** The execution unit 212 in FIG. 4 is responsible for executing tasks (a task is equivalent to a module instance). The execution unit 212 may include a digital signal processor (DSP), a reduced-instruction-set (RISC) processor, a domain-specific processor, an application-specific integrated circuit (ASIC) or a reconfigurable (FPGA) fabric. Regardless of its form, the execution unit 212 interacts with the node wrapper through a standard interface.

**[0040]** The nodal memory 210 is accessible to both the node wrapper and the execution unit 212. The nodal memory 210 is where the node wrapper deposits incoming streaming data and where the execution unit 212 accesses that data. A node's own memory 210, however, is typically not where the execution unit 212 sends output data. To minimize memory accesses, output data is usually sent directly to the node(s) requiring that data: the consumer node(s). Nodal memory 210 is also used to store task parameters and is available to tasks for temporary (scratchpad) storage.

**[0041]** In a multi-node system such as the ACM 160 in FIG. 2 where the nodes 180 are both consumers and producers of streaming data, matching production and consumption rates is desirable. A producer task on one node may produce data at a rate that is either greater than or less than the rate at which a consuming task on another node can handle. If the producer is sending data at a greater rate than the consumer can handle, then data is eventually lost. If the producer is sending data at a lesser rate than the consumer can handle, then the consumer may be starved for data, thereby potentially causing the consumer to sit idle waiting for additional data.

**[0042]** The ACM 160 provides, via the Point-to-Point protocol, and the node wrapper in FIG. 4 a single, uniform and consistent mechanism for task management, flow control and load balancing. Task management ensures that a task is placed in execution only when it has sufficient input data and when there is sufficient space in the consumer node(s) to accommodate the data produced by the task. Flow control guarantees that a producer task will never overwhelm a consumer task with too much data in too short a time. Load balancing permits a producer task to distribute data among several alternate consumer nodes, thus allowing the producer task to operate at a potentially higher rate.

**[0043]** Streaming data is transferred between two nodes 180 (points) via a point-to-point channel (point-to-point stream) 250 as shown in FIG. 5. Each PTP channel such as the

point-to-point channel includes a producer node 252, a producer task 254, an output port 256, a consumer node 258, an input port 260, an input buffer 262 and a consumer task 264. The producer task 254 runs on the execution unit of the producer node 252 and produces a finite-sized block of PTP data per task activation. The block of data is sent over the PTP channel 250 as a sequence of PTP words. The sending of blocks is shown as task 1 in FIG. 5. The output port 256 on the producer node 252 is associated with the producer task 254.

**[0044]** The consumer task 264 receives PTP data from the PTP channel 252 via the input port on the consumer node 258. The circular input buffer 262 in the nodal memory of the consumer node 258 stores the incoming PTP data. A consumer task such as the consumer task 264 runs on the execution unit of the consumer node 258 and consumes a finite amount of the PTP data residing in the circular input buffer 262 per task activation (Task 2 in FIG. 5).

**[0045]** Data is conveyed over the PTP channel 252 when the producer task 254 transfers a 50-bit point-to-point word 270 as shown in FIG. 6 to the node wrapper in the producer node 252. The point-to-point word 270 has the same fields as the network word 188 in FIG. 3 and like elements/fields are labeled with the same element numbers in FIG. 5. The point-to-point word 270 includes a node word 272 in the route field 190, a port word 274 in the auxiliary field 196 and a data word 276 in the payload field 198. In this example, a 51<sup>st</sup> bit, the security bit 192, is added later by the network 162 in FIG. 2. The node wrapper such as the node wrapper in FIG. 4, in turn, hands the PTP word over to the packet-switched network for transfer to the consumer node 258 in FIG. 5. The 8-bit route field 190 of the PTP word 270 provides the address in the form of the node word 272 of the consumer node such as the node 258 in FIG. 5. The port word 274 includes the low-order 5 bits of the auxiliary field 196 that indicate to which of the input ports of the consumer node the data is directed. When the PTP word arrives at the consumer node, the node wrapper deposits the 32-bit data word 176 in the payload field 198 into the circular input buffer associated with the indicated input port. The transfer is then complete.

**[0046]** The ACM 160 includes mechanisms for task management, flow control and load balancing. There is an input buffer associated with each input port. There is also a two's-complement signed count associated with each port, both input and output.

**[0047]** For an input port, the count is referred to as a consumer count since it reflects the amount of data in that port's input buffer that is available to be consumed by the associated task. A consumer count is enabled when its value is non-negative – that is, when its sign bit is 0. An enabled consumer count indicates that the associated input buffer has the minimum

amount of data required by an activation of the associated task. At system initialization, or upon reconfiguration, a consumer count is typically reset to  $-C$ , where  $C$  is the minimum number of 32-bit words required per task activation.

**[0048]** For an output port, the count is referred to as a producer count since it reflects the amount of available space in the downstream input buffer to accept the data that is produced by the associated task. A producer count is enabled when its value is negative – that is, when its sign bit is 1. An enabled producer count indicates that the downstream input buffer has space available to accommodate the maximum amount of data produced per activation of the associated task. At system initialization, or upon reconfiguration, a producer count is typically reset to  $P - S - 1$ , where  $P$  is the maximum number of 32-bit words produced per task activation and  $S$  is the size of the downstream input buffer in 32-bit words.

**[0049]** Both consumer counts and producer counts are typically initialized to negative values, causing the consumer counts start out disabled while producer counts start out enabled. This initial state reflects the fact that input buffers are usually empty at system initialization/reconfiguration.

**[0050]** Consumer and producer counts are updated by a system of credits and debits in the form of forward acknowledgements and backward acknowledgements. Both types of acknowledgements are network words such as the acknowledgment network word 280 shown in FIG. 7. The acknowledgment network word 280 has the same fields as the network word 188 in FIG. 3 and like elements/fields are labeled with the same element numbers. The acknowledgment network 280 word is sent by a task as the last steps in a task activation. In both cases, the payload field 198 contains four subfields: a type of acknowledgement subfield 282 (one bit), a port subfield 284, (3) a task subfield 286 and an Ack Value subfield 288.

**[0051]** The sequence of acknowledgements that a task performs at the end of each activation is described below. For each output port of the task, a forward acknowledgement is sent to the consumer node specifying the consumer input port and the consumer task. The Ack Value is the number of PTP words the task just sent to the consumer input port. A backward acknowledgement (a self ack) is sent to the node on which the task resides specifying the output port and the task. The Ack Value is the number of PTP words the task just sent via the output port.

**[0052]** For each input port of the task, a backward acknowledgement is sent to the producer node specifying the producer output port and producer task. The Ack Value is minus the number of 32-bit words the task just consumed from the input port's buffer. A

forward acknowledgement (a self ack) is sent to the node on which the task resides indicating the input port and the task. The Ack Value is minus the number of 32-bit words the task just consumed from the input port's buffer.

### **HARDWARE TASK MANAGER**

**[0053]** The hardware task manager 200 shown in FIG. 4 is the part of the node wrapper responsible for updating consumer and producer counts in response to incoming acknowledgements. It also monitors the sign bits of those counts and launches a task when an appropriate set of counts is enabled. This last responsibility is met using two signed counts that are associated not with a port but with a task: a task input count and a task output count. A task's input (output) count reflects the number of task consumer (producer) counts that are enabled. A task count is enabled when its value is non-negative. A task is enabled, and available for execution, when both its input count and its output count are enabled.

**[0054]** Incoming acknowledgements update various counts and cause tasks to be launched as follows. If a forward acknowledgement is received, the specified port is interpreted as an input port, and Ack Value is added to the corresponding consumer count. If the consumer count makes a transition from disabled to enabled (enabled to disabled), then the input count of the specified task is incremented (decremented) by 1. If a backward acknowledgement is received, the specified port is interpreted as an output port, and the Ack Value is added to the corresponding producer count. If the producer count makes a transition from disabled to enabled (enabled to disabled), then the output count of the specified task is incremented (decremented) by 1. If after a forward or backward acknowledgement is received, the specified task's input and output counts are both enabled, then the task is placed on the ready-to-run queue if it is not already on the queue. The task is launched when it reaches the head of the queue.

**[0055]** These actions embody the firing rule for tasks. They cause a task to be placed on the ready-to-run queue and ultimately executed when a sufficient number of consumer counts and a sufficient number of producer counts are enabled. What those sufficient numbers are is determined by the initial values of a task's input count and output count. If  $I$  ( $O$ ) is the number of input (output) ports associated with a task and  $IC_{Initial}$  ( $OC_{Initial}$ ) is the initial value of the task's input (output) count, and if it is assumed all consumer counts are initially disabled and all producer counts are initially enabled as discussed above, then a task fires when

$-IC_{Initial}$  out of I consumer counts are enabled

AND

$(O - OC_{Initial})$  out of O producer counts are enabled

For example, for I = 4,

If  $IC_{Initial} = -1$ , then 1 out of 4 consumer counts must be enabled

If  $IC_{Initial} = -2$ , then 2 out of 4 consumer counts must be enabled

If  $IC_{Initial} = -3$ , then 3 out of 4 consumer counts must be enabled

If  $IC_{Initial} = -4$ , then 4 out of 4 consumer counts must be enabled

For O = 4,

If  $OC_{Initial} = 3$ , then 1 out of 4 producer counts must be enabled

If  $OC_{Initial} = 2$ , then 2 out of 4 producer counts must be enabled

If  $OC_{Initial} = 1$ , then 3 out of 4 producer counts must be enabled

If  $OC_{Initial} = 0$ , then 4 out of 4 producer counts must be enabled

**[0056]** The programming of the multi-processor system such as the ACE 100 in FIG. 1 and the ACM 200 in FIG. 2 may be accomplished using what may be termed as the Stream C programming language.

### STREAM C MODULES

**[0057]** In a Stream C program, there is only one mechanism for expressing concurrency: through the concurrent operation of the program's modules (and module-like stream expressions). Syntactically, modules are very similar to C functions, but semantically, they are different. A C function (subroutine) initiates activity only when it is called. In a call, control is passed to the C function, usually together with some input arguments. The C function then performs a task/computation, and when finished, returns control together with any output result. Unlike C functions, modules are not called nor is control passed to or returned from modules. Instead, modules carry on ongoing interactions with other modules and the outside world through their input and output ports. Through these ports, a module receives streams of input values and emits streams of output values.

**[0058]** The syntax of a module prototype is identical to that of a C function prototype, with three exceptions. First, the keyword, `stream`, precedes a module prototype. This tells the compiler/linker that each module input and module output is associated with a stream of values of the specified type, not an individual value. Second, to permit a module to have multiple output streams, the module return type may be replaced by a parentheses-delimited

list that is identical in syntax to the input parameter list. Third, to extend the notion of an array to modules, a square-bracket-delimited list of array indices may be inserted immediately after the module name and before the input argument list. The module arrays are discussed below.

**[0059]** The following are two examples of module declarations:

```

stream int moduleA(int, int);

stream (int, int) moduleB(int, int);

```

Parameter names have been omitted here since they are not required in a module declaration (in contrast to a module definition or module instantiation), but Parameter names may be included at the programmer's discretion, usually as a mnemonic aid, for inputs and, when there are multiple outputs, for the outputs as well. The two declarations, for example, might then be expressed as:

```

stream int moduleA(int a, int b);

stream (int x, int y) moduleB(int a, int b);

```

**[0060]** The first declaration indicates that moduleA has two input streams, both of integer type, and a single output stream, also of integer type. The second declaration indicates that moduleB has two input streams, both of integer type, and two output streams, also both of integer type.

**[0061]** Like the definition of a C function, the definition of a module has a body delimited by curly braces ({ and }). Also as in the definition of a C function, each module input (and output in the case of multiple outputs) is assigned an identifier. The following are two examples of module definitions:

```

stream int moduleA(int a, int b)

{

// Module Body

}

stream (int x, int y) moduleB(int a, int b)

{

// Module Body

```

}

**[0062]** A module instantiation is the module counterpart to a C function call. Like a function call, a module instantiation is where a module gets used. While the syntax of these two types of expressions are similar, the semantics are different. A fragment of C code may be expressed as:

```

int x, y;

int F(int, int);

.

.

.

int z = F(4, x + 5*y);

```

**[0063]** The first statement declares that  $x$  and  $y$  are integers, while the second declares that  $F$  is a function with two integer parameters and an integer result. The last statement is an assignment containing the function call  $F(4, x + 5*y)$ , which has two arguments, the expressions  $4$  and  $x + 5*y$ , corresponding to the two parameters of  $F$ .

**[0064]** The stream version of this code fragment is as follows:

```

stream int x, y;

stream int F(int, int);

.

.

.

stream int z = F(4, x + 5*y);

```

**[0065]** In the stream version, each of the statements above is prefaced with the keyword `stream`. The change in syntax produces a dramatic change in semantics. Instead of individual values, streams of values are used. Thus the first statement declares that  $x$  and  $y$  are integer streams, while the second declares that  $F$  is a module with two integer-stream inputs and an integer-stream output. The last statement is now an assignment containing the module instantiation  $F(4, x + 5*y)$ , which has two arguments, the stream expressions  $4$  and  $x + 5*y$ , corresponding to the two parameters of  $F$ .

**[0066]** In the case of the function call, each execution of the assignment  $z = F(4, x + 5*y)$  causes expressions  $4$  and  $x + 5*y$  to be evaluated and the two resulting values to be supplied as parameters in a call to function  $F$ . After some period of time,  $F$  returns a value. In the case of the module instantiation, there is no execution of the assignment  $z = F(4, x +$

$5*y$ ) and no call to module F. Instead, an instance of module F is created (instantiated) at system initialization, just before the Stream C program begins execution, thereby making the instance ready to receive streams of integers on its two input ports and produce a stream of integers on its output port. And once program execution commences, the instance of F remains operative until program termination i.e., the instance of F is persistent.

**[0067]** This simple example illustrates the general mechanism used in Stream C to create a community of interacting modules. Each module instantiation causes a separate module instance to be created at system initialization. Once created (instantiated), a module instance is ready to receive streams of values on its input ports and produce streams of values on its output ports. Furthermore, once program execution commences, the module instance remains operative until program termination.

**[0068]** The general form of the instantiation of a module with multiple output ports is:

(<identifier-list>) <module-identifier> (<expression-list>)

While the input arguments are expressions, the output arguments are identifiers. These identifiers serve to name the otherwise nameless output streams. The stream assignment statement above plays the same role by assigning the name z to the otherwise nameless output stream of F (4, x + 5\*y). For example:

```

stream int w, x, y, z;

stream (int, int) F(int, int);

.

.

.

(w, z) = F(4, x + 5*y);

```

**[0069]** As before, F has two integer-stream inputs, but in contrast to the earlier example, F now has two integer-stream outputs. Those two output streams appear in the instantiation of F as the list of identifiers (w, z), which serves to give the two output streams the names w and z.

**[0070]** Statements within a module body fall into two categories (or domains), stream statements that involve only streams and thread statements that include the entire range of C statements as well as statements that allow a thread to read from and write to streams. Because each module instantiation causes a separate module instance to be created at system initialization, Stream C does not allow a module to have within its body, or within the body of a submodule, an instantiation of itself. In other words, circularity in module references is

not allowed. This prohibition helps avoid the difficult task of instantiating an infinite number of module instances.

**[0071]** In a Steam C module, there is no notion of returning control, and so the `return` statement is inappropriate. In a module, output values are simply inserted into a module output stream. But in order to do that, the output stream must have a name. For modules with a parentheses-delimited list of named output streams, that's not a problem. It is a problem, however, when the module prototype provides only the type of the module's sole output stream. In that case, code in the module's body, either in the stream domain or thread domain, can use the keyword `out` as the name of the default module output stream. This usage is illustrated in the following code fragment.

```

stream int moduleA(int a, int b)

{

.

.

.

out = a + b;

.

.

.

}

```

**[0072]** Modules and the streams they are partnered with provide the framework for the web of interactions and concurrent activity typical of a Stream C program, while functions provide the computational building blocks of a program. Although modules deal with streams of values, that does not prevent modules from accessing individual values within a stream and supplying those values to a function. Likewise, a module can access the output value of a function and insert that value into a stream. A function, on the other hand, cannot reference a module because there is no mechanism within a function for such interaction. Because of this asymmetry in capabilities, modules are found at the higher levels of a program hierarchy, while functions are found at the lower levels.

**[0073]** While the differences between modules and functions are substantial, there is one area in which they are similar. They both support side effects, that is, they both may manipulate external data structures independently of their input and output ports. This stems from the fact that modules may contain threads that may have side effects.

**[0074]** FIG. 8A shows a generic module which includes a module 300 and a number of input streams 302 (from zero to N) which provide data/control to the module 300 and a number of output streams 304 (from zero to N) which provide data/control to the next

module/function. A module with no output streams is a “sink” and a module with no input streams is a “source.”

**[0075]** FIG. 8B is a diagram showing two modules, module A 300 and module B 310 each having corresponding input streams 302 and 312 and output streams 304 and 314. The output streams 304 of Module A 300 are attached to the input streams 312 of Module B 310. The Module A 300 is mapped to run on a CPU core 308 and the Module B 310 is mapped to run on a second CPU core 318. The cores 308, 318 and 328 are similar to the nodes 180 in FIG. 2.

**[0076]** FIG. 8C is a diagram that shows the mapping of both module A 300 and module B 310 onto the same CPU core such as the CPU core 308. In this instance the modules 300 and 310 act like any other separate thread of control. An operating system which is running on the second core 318 may schedule the modules 300 and 310 based on preemptive multi-tasking or run to completion/release. Since both modules 300 and 310 and input/output streams 302, 312 and 304, 314 are “persistent” (that is they remain ready to perform processing) additional information must be provided to a conventional operating system about when to schedule a module based on both the availability of “enough” input stream data to perform a computation and “enough” space so that the output stream can deliver the computed data.

**[0077]** A variety of different algorithms can be used to perform the Module to Core Mapping. These may include cache proximity where modules which share the greatest number of streams are placed in cores which share a L1 cache followed by a shared L2 cache followed by a shared L3 cache followed by a shared DRAM. They may also include a physical proximity algorithm where modules which share the greatest number of streams are placed in cores which are physically adjacent to each other. For example the algorithm may start with the die and then the integrated circuit on the motherboard, then the motherboard in the rack, then the rack in the floor of the building, then the building geographically adjacent. Another algorithm may be the next available free where modules are allocated to cores based on the next “free” core based on either CPU usage (current or average weighted over time) or the next sequentially available core. Another algorithm may be a predictive load that selects the modules and cores based on estimated statistical sampling. A running average of core utilization is used to load modules to the lightest loaded core. Another algorithm may be user specified where a user specified virtual core ID is used to place all modules onto a physical

core ID. When the number of virtual core ID's exceeds the physically available cores then multiple modules are evenly loaded across all available physical cores.

**[0078]** FIG. 8D show various data structures 330, 332 and 334 that may reside in the module A 300 and are used in the input and output streams 302 and 304. The data structures 330, 332 and 334, which reside either in memory/cache or a TLB, contain the critical information which is required for either a single core or a multi-core system to schedule and transport data from input streams such as the input stream 302 to output streams such as the output stream 304, input streams 302 into modules such as the module A 300, and the module A 300 out to output streams 304. For each module there is information that uniquely identifies the module, uniquely identifies all the input streams into that module, uniquely identifies all the output streams of that module, uniquely identifies how input and output streams are "connected," uniquely identifies the core, and maintains state information so that a module may be relocated from a core to another core, or swapped out via virtual memory. Streams can be dynamically added or deleted from modules, and modules can be dynamically added or deleted from cores.

## STREAMS

**[0079]** The term stream in the Stream C programming language refers to a sequence of data values, all of the same type and typically made available over time. In Stream C, however, streams provide much more than a framework for input and output. Streams are elevated to first-class objects, a status roughly comparable to that of variables. This means that a stream may be bound to an identifier (i.e., it can be named), an input parameter of a function (i.e., an input parameter of a module), the output of a function (i.e., an input parameter of a module), a parameter within an expression and the output of an expression

**[0080]** A stream conveys values of a single type from one or more stream sources to one or more stream destinations. The precise details of how this transport is accomplished is implementation dependent, and depends upon, among other things, whether the stream is confined to a single semiconductor die or whether the stream spans several meters or possibly even thousands of kilometers. Except when dealing with performance issues, a programmer need not be concerned with those details, and need only be concerned with those aspects of a stream that relate to four stream attributes: the stream type, the stream name, the stream sources and the stream destinations.

**[0081]** The stream type indicates the type of values being conveyed. The type which may be any legitimate C type, including pointers and types defined via `typedef`, may be specified implicitly by context for example, by appearing as a module input or output parameter or explicitly using a stream declaration as described below.

**[0082]** The stream sources are the points at which values are placed into the stream. Possible stream sources are include an input parameter of a module definition, an output of a module instantiation, the output of a stream expression and a thread (discussed below). The stream destinations are the points to which the stream conveys values. Possible stream destinations include an output parameter of a module definition, an input argument of a module instantiation, an input of a stream expression and a thread. An optional stream name is a name/identifier is assigned to a stream when the stream appears as a module input or output parameter or when it is introduced in a stream declaration. An example of an unnamed stream is the output stream of a stream expression that has not been assigned a name via a stream assignment.

**[0083]** The notion of stream attributes is illustrated in the following code fragment containing a declaration of a function `F` and a partial definition of a module `M`.

```

stream int F(int, int);

stream (int zStrm) M(int xStrm, int yStrm)

{

:

:

zStrm = xStrm*yStrm + F(xStrm, yStrm);

:

:

}.

```

**[0084]** There are three named streams here: `xStrm`, `yStrm` and `zStrm`, all of type `int`. `xStrm` and `yStrm` each have a single source: an input parameter of module `M`. The destinations of `xStrm` and `yStrm` are represented by the two instances of `xStrm` and `yStrm`, respectively, appearing in the assignment expression in the body of `M`. (Recall that, in C, an assignment is also an expression.) Those instances represent inputs to the assignment expression. `xStrm` and `yStrm` thus each have a single source and two destinations.

**[0085]** A stream expression is identical to a C expression, except that in place of variables, there are now input streams. A stream expression also has an output stream, which

carries the results from expression evaluations. By default, this output stream is nameless, but it can be assigned a name using a stream assignment, which is just what we've done in the above assignment. Thus the output stream of the stream expression

$$xStrm * yStrm + F(xStrm, yStrm)$$

is assigned the name `zStrm` by the stream assignment

$$zStrm = xStrm * yStrm + F(xStrm, yStrm)$$

Either of these two expressions may be considered the source of `zStrm`. The destination of `zStrm` is the output stream of module `M`, which is denoted by the output parameter `zStrm` of module `M`.

```

stream (int zStrm) M(int xStrm, int yStrm)

```

`xStrm` thus has a single source and a single destination.

**[0086]** The most crucial properties of a stream relate to the stream's role as a conveyor of values. There are four such properties: a) values do not enter a stream except at stream sources or at system initialization using the `initialize()` function; b) Values entering a stream at a single source are totally ordered in time; c) once entered into a stream, a value is eventually delivered to all stream destinations; if there are multiple destinations, then a separate copy of the value is delivered to each destination; and d) values from a single source are received at each stream destination in the same order in which they entered the stream i.e., there is no leapfrogging of values in a stream. These four properties are the only guarantees that a stream provides regarding the transport of values. Any other property that does not follow as a logical consequence from these four is not a general stream property.

**[0087]** Because a stream is obliged to only deliver values eventually, the latency of a stream, the time it takes a value to travel from a stream source to a stream destination, is indeterminate. In fact, the latency may vary with time and between different source-destination pairs of the same stream. Fixed or at least, bounded latencies, however, can still be achieved by relying upon guarantees provided by the system implementation (rather than the programming model). A source-destination pair confined to a single semiconductor die, for example, will usually have bounds on its latency.

**[0088]** The above four properties also have implications for stream determinacy and indeterminacy (non-determinism). For a stream with a single source, the four properties ensure deterministic stream behavior. That means that the order in which values are placed

into a single-source stream completely determines the order in which values are delivered to all stream destinations. For a stream with multiple sources, however, the situation is very different. To illustrate the issues arising from multiple stream sources, consider the following adaption of the code fragment from the preceding section. (`out` is the default output stream of a single-output module).

```

int F(int);

stream int M(int xStrm, int xStrm)

{

:

:

:

out = xStrm*xStrm + F(xStrm);

:

:

:

}

```

**[0089]** The two input parameters of module M are the same: `xStrm`. From the four properties, values entering `xStrm` through the first input parameter of module M will be received at each of the three destinations of `xStrm` in the same order in which they entered the stream. Values entering `xStrm` through the second input parameter of module M will be received at each of the three destinations of `xStrm` in the same order in which they entered the stream. That means that the two streams of values are merged or interleaved before reaching each destination of `xStrm`.

**[0090]** How interleaving is carried out is influenced, in general, by program structure. The missing parts of the program above, for example, may be structured in a way that leads to an interleaving that strictly alternates between parameter-one and parameter-two values. So, for example, if the integers arriving on the two input parameters (streams) `xStrm` of module M begin with the sequences:

| <u>xStrm Source One</u> | <u>xStrm Source Two</u> |

|-------------------------|-------------------------|

| 6                       | 3                       |

| 8                       | 5                       |

| 1                       | 9                       |

| :                       | :                       |

| :                       | :                       |

| :                       | :                       |

then the sequence arriving at each of the three destinations of `xStrm` in the expression

`out = xStrm*xStrm + F(xStrm)`

might begin with

xStrm Destinations

6

3

8

5

1

9

.

.

Such program-imposed determinism though is not always the case, and there are situations in which values from multiple stream sources are interleaved non-deterministically. Moreover, depending on the target system, those nondeterministic interleavings may differ from one stream destination to another. Thus, for example, if the values arriving on the two input parameters (streams) of module M are the same as above, then the sequence arriving at the three destinations of xStrm might begin with:

| <u>xStrm Destination One</u> | <u>xStrm Destination Two</u> | <u>xStrm Destination Three</u> |

|------------------------------|------------------------------|--------------------------------|

| 6                            | 3                            | 3                              |

| 8                            | 5                            | 6                              |

| 1                            | 6                            | 5                              |

| 3                            | 8                            | 8                              |

| 5                            | 1                            | 1                              |

| 9                            | 9                            | 9                              |

| .                            | .                            | .                              |

| .                            | .                            | .                              |

| .                            | .                            | .                              |

This indeterminacy in order of arrival of values at the destinations of a multi-source stream contrasts with the fixed order of arrival across all destinations of a single-source stream. That fixed arrival order allows adopting notation that is useful in below. For a single-source stream `ssStrm` and a non-negative integer `i`,

`ssStrm(i)`

denotes the  $i^{\text{th}}$  value appearing at all destinations of `ssStrm`. By convention, `ssStrm(0)` denotes the first value appearing at all destinations.

**[0091]** When a value arrives at a stream destination, if the destination is an output parameter of a module definition or an input argument of a module instantiation, then the value is handed over to a stream on the other side of a module boundary. The value thus remains in transit. If the destination is an input of a stream expression or a thread then the value comes to rest in a FIFO queue.

**[0092]** To illustrate remaining in transit, the following code fragment is shown.

```

stream int module1(int);

stream int module2(int xStrm)

{

:

:

:

out = module1(xStrm);

:

:

:

}

```

The code fragment includes two modules, `module1` and `module2`, each with a single input stream and single output stream and two named streams, `xStrm` and `yStrm`, both within the definition (body) of `module2`. The sole destination of `xStrm: module1(xStrm)` is an input argument of an instantiation of `module1`. A value arriving at this destination is simply passed across `module1`'s boundary to an internal stream of `module1`. The situation is similar for values arriving at the sole destination of `yStrm`:

```

stream (int yStrm) module2(int xStrm)

```

Since this destination is an output parameter of a `module2`, arriving values are simply passed across `module2`'s boundary to a stream external to `module2`.

**[0093]** Another example is the case where a stream destination is an input of a stream expression such as the following code fragment.

```

stream int F(int, int);

stream int M(int xStrm, int yStrm)

{

:

:

:

out = xStrm*yStrm + F(xStrm, yStrm);

:

:

```

}

Within the body of module M is the stream expression

$$xStrm * yStrm + F(xStrm, yStrm)$$

which contains two destinations of  $xStrm$  and two destinations of  $yStrm$ . It also contains the two operators  $*$  and  $+$  and the function  $F$ , which are ordinary C constructs. That means that in order to evaluate this expression, the two operators and the function  $F$  must be supplied with individual values.

**[0094]** The queues are automatically inserted by the Stream C linker/loader and are managed by the Stream C runtime. Among the responsibilities of the runtime is signaling when a queue is empty and ensuring that no queue ever overflows. Each queue is guaranteed to have a capacity of at least two values of the associated data type, although a programmer may request a specific amount via a pragma as described below. In the stream of this example, there are four queues, one for each of the four stream destinations (stream expression inputs). These queues are largely invisible to the programmer.

**[0095]** Once a Stream C program begins executing (operating), the only way for a value to enter a stream is through a stream source. One or more streams may form a directed cycle which requires a value already in the stream. The simplest such cycle occurs when a stream appears on both sides of a stream assignment as in:

$$xStrm += yStrm$$

which is equivalent to

$$xStrm = xStrm + yStrm$$

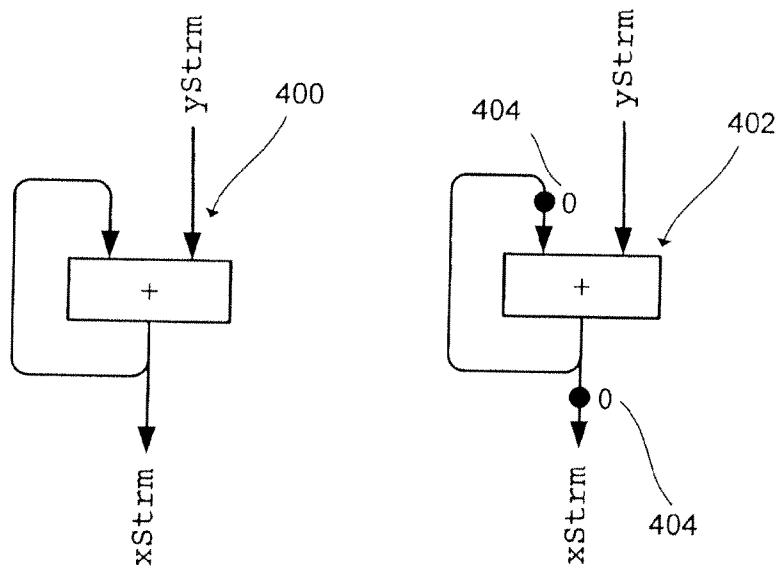

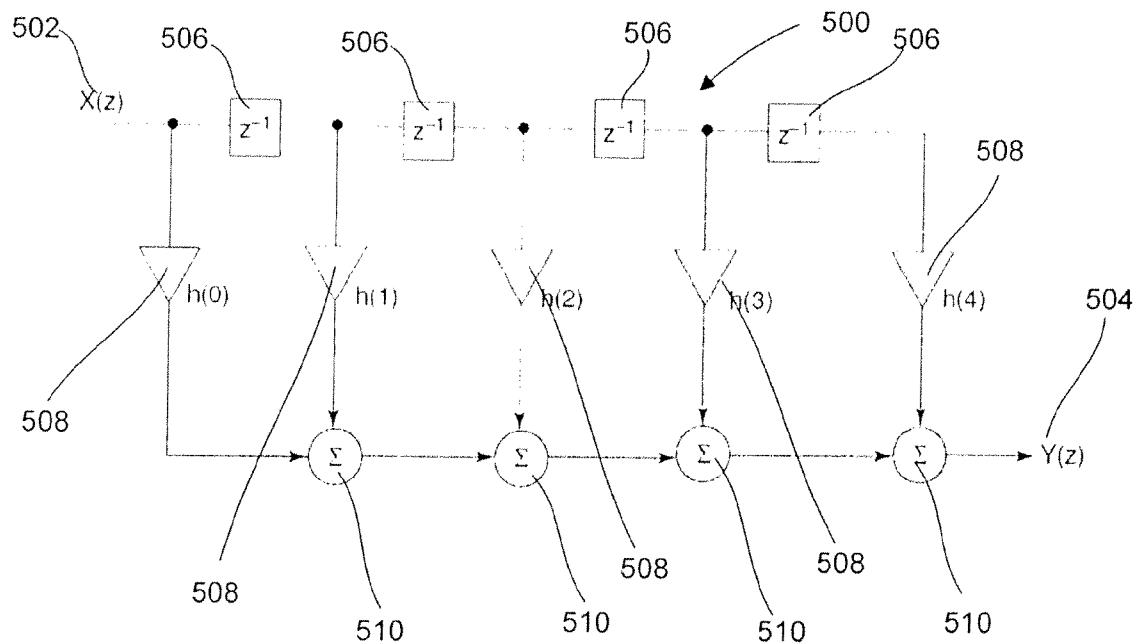

**[0096]** FIG. 9A is a first graphical representation 400 of this assignment where the directed cycle consists of the feedback path from the output of the  $+$  operator to one of the two inputs of the same operator. It is the lack of a value on this path that prevents the  $+$  operator from consuming a value from each input stream and producing a value on the output stream. So unless a value 404 is placed in the feedback path as shown in the second graphical representation 402 before execution begins, the  $+$  operator will never fire.

**[0097]** Another issue relates to changing the offset of one single-source stream relative to another single-source stream. For example, if  $aStrm$  and  $bStrm$  are both inputs to the same module or stream expression, as in

$$aStrm + bStrm$$

which is represented graphically in FIG. 9B, and the module or expression consumes values from the streams in pairs, one from aStrm and one from bStrm. If it is desired that aStrm(n) (i.e., the  $n^{\text{th}}$  value arriving on aStrm) to match up with bStrm(n+2) (i.e., the  $n+2^{\text{nd}}$  value arriving on bStrm). Thus aStrm(0) would match up with bStrm(2), aStrm(1) would match up with bStrm(3), and so on.

**[0098]** The solution to both issues is provided by the stream initialization statement, which has the form

```

<stream-identifier>.initialize(<value-list>);

```

**[0099]** When the Stream C compiler/linker/loader encounters this statement, it takes the statement as a directive to insert a FIFO queue at each destination of <stream-identifier> whether the destination is an output parameter of a module definition, an input argument of a module instantiation, an input of a stream expression or a thread; size the queue at each stream destination so that it is sufficient to hold at least  $n+1$  values of type T, where n is the number of values in <value-list> and T is the type of <stream-identifier>; and place the values in <value-list> into the queue in order, with the first value in <value-list> placed at the front (head) of the queue.

**[00100]** For example, in FIG. 9A, to prevent deadlock, a value 404 is inserted in the feedback path and also in the expression output in the graphic representation 402 by initializing xStrm with the value 0 via the statement

```

xStrm.initialize(0);

```

This statement causes two FIFO queues to be created, one for each destination of xStrm. (the queue at the destination of the feedback path will already have been inserted as described in the preceding section). Assuming that xStrm is of type int, then the size of each queue is at least `2*sizeof(int)`, and at the head of each queue at system initialization is the int value 0. This is illustrated graphically in the flow diagram 402 in FIG. 9A. With xStrm thus initialized, the values appearing on the output of the assignment `xStrm += yStrm` are:

```

0

yStrm(0)

yStrm(0) + yStrm(1)

```

```

yStrm(0) + yStrm(1) + yStrm(2)

```

```

·

·

·

```

Changing the offset of `aStrm` relative to `bStrm` in a second graphic representation 412 in FIG. 9B is handled in a similar manner. Here, however, *two values* are inserted into the `aStrm` FIFO queue since it may be desirable to offset `aStrm` by two values relative to `bStrm`. That is accomplished using the following stream initialization statement in which 1 and 2 have been chosen as two values 414 to be inserted into `aStrm`'s queue at system initialization.

```

aStrm.initialize(1, 2);

```

The effects of this initialization are illustrated graphically in the representation 412 in FIG. 9B. With `xStrm` thus initialized, the values appearing on the output of the assignment `xStrm += yStrm` are then:

```

1 + bStrm(0)

2 + bStrm(1)

aStrm(0) + bStrm(2)

aStrm(1) + bStrm(3)

·

·

·

```

**[00101]** As is the case for C variables, all streams must be declared before being used, although certain stream declarations are made implicitly by context, for example, by appearing as module input or output parameters. For explicit stream declarations, the syntax follows that for C variable declarations, but with the declaration now beginning with the keyword `stream`:

```

stream <storage-class-specifier>optional <type> <identifier-list>;

```

Some examples of stream declarations without a storage class specifier are:

```

stream int xStrm, yStrm;

```

```

stream char cStrm;

```

```

stream double dStrm;

```

Of the five storage class specifiers in C – `auto`, `register`, `static`, `extern` and `typedef` – only `static` is permitted in a stream declaration, as in

```

stream static int xStrm, yStrm;

```

**[00102]** The semantics of a `static`, as well as a non-`static`, stream declaration is determined by the context in which the declaration appears. There are three such contexts, each with its own scope rule. In each case, the stream-declaration scope rule is identical to that of the variable-declaration counterpart. For a stream declaration, with no storage class specifier and appearing inside a module, the declaration scope extends from the declaration to the end of the module. For a stream declaration, with no storage class specifier and appearing outside all modules (and functions), the declaration scope is global – that is, it is visible to the entire program. For a stream declaration, with the `static` storage class specifier and appearing outside all modules (and functions), the declaration scope extends from the declaration to the end of the source file in which the declaration appears.

**[00103]** Absent from this list are several declaration forms involving storage class specifiers that pertain to variables but not streams. In C, automatic variables, those variables declared with the `auto` storage class specifier or with no specifier at all, lose their values between function invocations. But since streams do their work only within modules and since modules are not invoked (they are always active), automatic streams are an incongruous concept. The `auto` storage class specifier is therefore not applied to stream declarations.

**[00104]** A variable declaration with the `static` specifier and appearing inside a function indicates that the declared variable retains its value between function calls (function invocations). In the case of modules, however, there is no notion of a call, and so the `static` specifier has no meaning inside a module. The `static` specifier is therefore not used within module scope.

**[00105]** For variable declarations, the `extern` storage class specifier helps to distinguish those declarations of global variables that act as declarations and definitions from those that act as merely declarations. In the case of streams, however, a declaration is never a definition because a stream declaration never causes storage to be set aside. Storage is allocated only at stream destinations as described below in the section on Stream FIFOs. The `register` and `typedef` storage class specifiers have no relevance to streams and do not appear in stream declarations.

**[00106]** Stream expressions are the stream counterpart to ordinary C expressions. Apart from substituting input streams for all variables and an output stream for the result, the two types of expressions are very similar. Expressions combine variables and constants to produce new values while stream expressions combine streams and constants to produce new streams. The structure of C expressions and stream expressions are nearly identical. All C operators are valid operators in stream expressions. The same operator precedence applies in both C expressions and stream expressions. C function calls are permitted in stream expressions, just as they are in C expressions. Instantiations of modules with a single output stream are permitted in stream expressions, and are treated similarly to function calls.

**[00107]** The differences between C expressions and stream expressions lie primarily in when and how they are evaluated. A C expression is evaluated when the thread of control reaches the statement containing the expression. The evaluation is carried out by first replacing each variable by its current value and then performing the requisite operations according to the rules of operator precedence. The value returned by the final operation is then supplied as the evaluation result.

**[00108]** Unlike evaluation of C expressions, evaluation of stream expressions in the C Stream programming language is not tied to a thread of control. Instead, stream expressions are evaluated opportunistically. As before, evaluation is carried out by performing the requisite operations according to the rules of operator precedence. Instead of substituting values for variables, a value is consumed (popped) from each FIFO queue belonging to an expression input. A FIFO queue is inserted at all stream destinations that are inputs of stream expressions. The evaluation is opportunistic because it is performed whenever there is at least one value in each input FIFO queue of the expression. The result produced by the evaluation, as before, is the value returned by the final operation of the evaluation. That result, however, is handled differently from the C expression case. For a C expression, the use to which the result is put is determined by the context of the expression. For a stream expression, the result is simply placed into the expression's output stream (which may or may not have a name, depending upon whether the expression is an assignment).

**[00109]** An example of the stream expression may be shown in the following expression in which `xStrm`, `yStrm` and `zStrm` are all streams of type `int`.

$$xStrm * yStrm + 5 * zStrm$$

The values arriving on the three streams begin as follows:

| <u>xStrm</u> | <u>yStrm</u> | <u>zStrm</u> |

|--------------|--------------|--------------|

| 1            | 2            | 3            |

| 4            | 5            | 6            |

| 7            | 8            | 9            |

| .            | .            | .            |

| .            | .            | .            |

| .            | .            | .            |

The first three values placed into the (unnamed) output stream of  $xStrm * yStrm + 5 * zStrm$  are then:

Output Stream of  $xStrm * yStrm + 5 * zStrm$

$$\begin{aligned}

17 &= 1 * 2 + 5 * 3 \\

50 &= 4 * 5 + 5 * 6 \\

101 &= 7 * 8 + 5 * 9 \\

&\vdots \\

&\vdots

\end{aligned}$$

**[00110]** Among stream expressions, stream assignments are of special interest. There are two types of such stream assignments, the first type has the form

$\langle\text{stream-identifier}\rangle = \langle\text{stream-expression}\rangle$

**[00111]** Like their C counterparts, assignments to variables, stream assignments of this type have a side effect. In addition to supplying values to its output stream, a stream assignment makes the output of the right-hand-side (RHS) expression a source of the left-hand-side (LHS) stream, and in the process makes the output stream of the RHS expression the output stream of the assignment. The stream assignment also gives a name to the otherwise nameless output stream of the RHS expression. Although a name is not needed for the output stream of a subexpression of a larger expression, a name is essential when the output stream must be directed to a destination outside any enclosing superexpression.

**[00112]** The stream assignment statement in the following code fragment is an example. A stream expression, assignment or otherwise, becomes a *stream statement* when it is followed by a semicolon.

```

int F(int, int);

int G(int);

stream int M(int xStrm, int yStrm)

{

.

}

```

```

.

out = F(xStrm, G(yStrm));

.

.

}

```

The expression, `F(xStrm, G(yStrm))` and the subexpression, `G(yStrm)` each have an output stream as stream expressions. In the case of `G(yStrm)`, the output stream is unnamed since the destination of the stream is clear from the context of the expression: the destination is the second input argument of the function `F` in the superexpression `F(xStrm, G(yStrm))`. In the case of the output stream of `F(xStrm, G(yStrm))`, however, a name is required since the destination is outside the expression. That name is assigned in the assignment expression

```

out = F(xStrm, G(yStrm))

```

With this assignment, the output of `F(xStrm, G(yStrm))` becomes a source of `zStrm`, which has a single destination, the output parameter of Module M.

**[00113]** The second type of stream assignment is of the form

```

(<comma-separated-list-of-stream-identifiers>) = <module-instantiation>

```

It arises when it is desirable to make the outputs of a multi-output module the sources of multiple named streams. To illustrate, the following multi-output module:

```

stream (int, int) tap(int, int, int);

```

If the first output of `tap` is the source of `int` stream `x`, and the second output of `tap` is the source of `int` stream `y`. That is accomplished with the stream assignment

```

(int x, int y) = tap(arg1, arg2, arg3);

```

The assignment makes the  $i^{\text{th}}$  output of the module a source of the  $i^{\text{th}}$  stream and gives names to the otherwise nameless output streams of the module.

**[00114]** Statements within the body of a module fall into two categories (domains), thread and stream. Stream statements deal with streams but not variables. Thread statements deal with variables, and, in a few cases, with streams as well. Statements in the thread domain are mostly C statements, and like C statements, they are imperative (procedural) in nature defining a step-by-step procedure. Associated with such a procedure is a sequential flow of

control, often called a thread, which governs the order in which statements are executed. Stream statements, in contrast, are declarative. Each such statement makes a declaration about the streams appearing in the statement. There is no notion of a step-by-step procedure, as there is in the thread domain, and the order of stream statements within a module body is therefore immaterial with one exception. Just as variables must be declared before being used, so too streams must be declared before being used.

**[00115]** Because of the nature of the stream domain, there are no counterparts to those C statements that deal with control flow, specifically, `if-else`, `else-if`, `switch`, `for`, `while`, `do-while`, `break`, `continue`, `goto` and `return`. In fact, the only statement type in the stream domain is the stream counterpart to the C expression statement, and, as in C, the most common expression statement is the assignment statement. A stream expression statement has one of the two forms

```

<stream-expression>;

stream <stream-expression>;

```

while a stream assignment statement has one of the two forms

```

<stream-identifier> = <stream-expression>;

stream <stream-identifier> = <stream-expression>;

(<comma-separated-list-of-stream-identifiers>) = <module-instantiation>

```