# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102013902173327 |

|------------------------------|-----------------|

| Data Deposito                | 09/07/2013      |

| Data Pubblicazione           | 09/01/2015      |

Classifiche IPC

Titolo

PROCEDIMENTO PER LA PROGETTAZIONE AUTOMATICA DI UN CIRCUITO ELETTRONICO, RELATIVO SISTEMA E PRODOTTO INFORMATICO **DESCRIZIONE** dell'invenzione industriale dal titolo:

"Procedimento per la progettazione automatica di un circuito elettronico, relativo sistema e prodotto informatico"

di: STMicroelectronics S.r.l., nazionalità italiana, Via C. Olivetti, 2 - 20864 Agrate Brianza (MB)

Inventori designati: Alberto BALZAROTTI, Mattia MONETTI

Depositata il: 9 luglio 2013

\*\*\*\*

#### TESTO DELLA DESCRIZIONE

#### Campo tecnico

La descrizione si riferisce a tecniche per la progettazione automatica di un circuito elettronico.

Nella presente descrizione con circuito elettronico si intende in generale un circuito integrato singolo o sistemi di circuiti elettronici integrati, da realizzare tramite tecnologie di fabbricazione di circuiti integrati su chip che definiscono un substrato per la fabbricazione del circuito.

Varie forme di attuazione possono trovare applicazione in apparati elaboratori quali workstation, elaboratori server e simili.

# Sfondo tecnologico

Sono noti strumenti per la progettazione di substrati che operano nell'ambiente di design di sistemi e circuiti elettronici, ossia ambienti EDA (Electronic Design Automation). In particolare fra gli ambienti EDA è nota ad esempio le suite di design Cadence, che comprende in una sua versione una piattaforma denominata Virtuoso Platform per il progetto di circuiti integrati full-custom che comprende l'inserimento degli schemi, behavioral modeling

(Verilog-AMS), simulazione dei circuiti, full custom layout, passi di verifica a livello fisico, estrazione di netlist.

Gli strumenti di progettazione elettronica assistita disponibili dunque forniscono un supporto molto limitato quando si tratti di valutare le interazioni fra dispositivi elettronici di detti sistemi e circuiti elettronici in un chip a livello del substrato di detto chip.

In questo contesto di esiguità di strumenti che operano a livello di substrato, ancora meno sono gli strumenti che permettono di effettuare valutazioni sul comportamento termico del circuito a tale livello.

E' noto ad esempio, disponibile anche per l'integrazione con programmi di design quale il sopracitato Cadence, un tool software denominato Gradient Heathwave, che impiega un modello termico che usa i dati di layout (ad esempio originati da Cadence Virtuoso) del circuito integrato e un file tecnico termico che contiene gli spessori degli strati e le proprietà dei materiali, incluse le loro dipendenze in temperatura.

Tuttavia, tale tool, nonostante riesca a ottenere complesse simulazioni termiche, tenendo conto anche di effetti del package, non fornisce un'informazione efficace sul comportamento a livello di substrato e non sono in grado di operare simulazioni elettro-termiche nello stesso ambiente di simulazione che siano contemporaneamente precise e veloci.

#### Scopo e sintesi

Nel contesto sopra delineato è avvertita l'esigenza di valutare le interazioni termiche fra dispositivi elettronici di detti sistemi e circuiti elettronici in un chip a livello del substrato di detto chip, superando gli

inconvenienti delineati in precedenza.

Varie forme di attuazione si prefiggono lo scopo di soddisfare tale esigenza.

Secondo varie forme di attuazione, tale scopo è raggiunto grazie ad un procedimento avente le caratteristiche richiamate nelle rivendicazioni che seguono.

Varie forme di attuazione possono riferirsi anche ad un corrispondente sistema di elaboratori, nonché ad un prodotto informatico caricabile nella memoria di almeno un elaboratore e comprendente porzioni di codice software suscettibili di realizzare le fasi del procedimento quando il prodotto è eseguito su almeno un elaboratore. Così come qui utilizzato, il riferimento ad un tale prodotto informatico è inteso essere equivalente al riferimento ad un mezzo leggibile da elaboratore contenente istruzioni per il controllo del sistema di elaborazione per coordinare l'attuazione del procedimento secondo l'invenzione. Il riferimento ad "almeno ad un elaboratore" è evidentemente inteso a mettere in luce la possibilità che la presente invenzione sia attuata in forma modulare e/o distribuita.

Le rivendicazioni formano parte integrante dell'insegnamento tecnico qui somministrato in relazione all'invenzione.

## Breve descrizione delle figure

Varie forme di attuazione saranno ora descritte, a puro titolo di esempio non limitativo, con riferimento alle figure annesse, in cui:

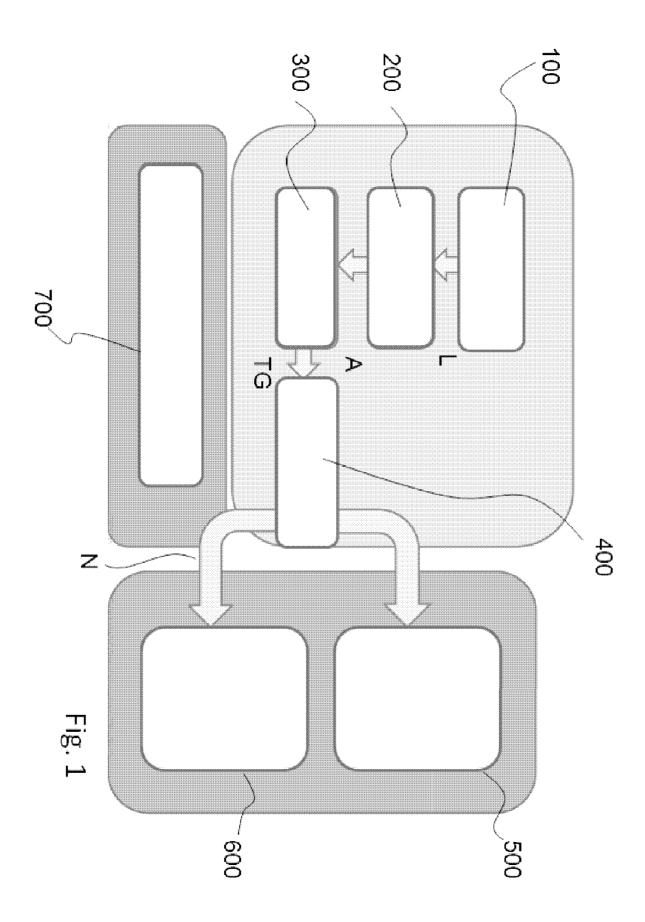

- la figura 1 è un diagramma di flusso di principio rappresentativo di forme di attuazione,

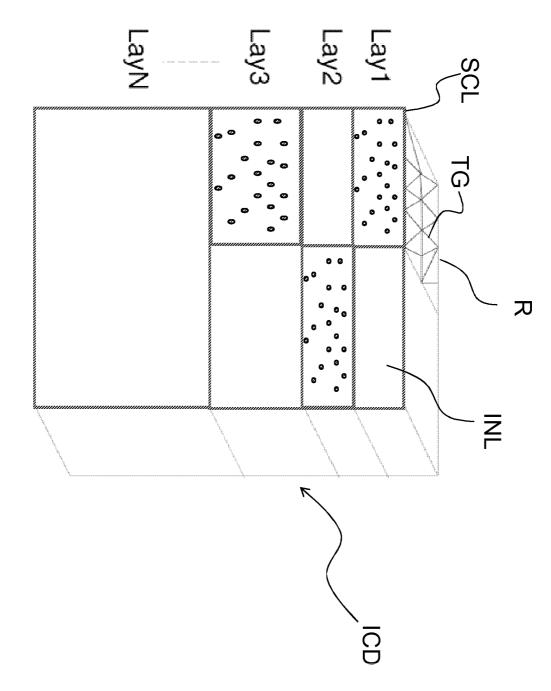

- la figura 2 è una vista schematica di un dispositivo rappresentativo di possibili modalità di funzionamento di

forme di attuazione,

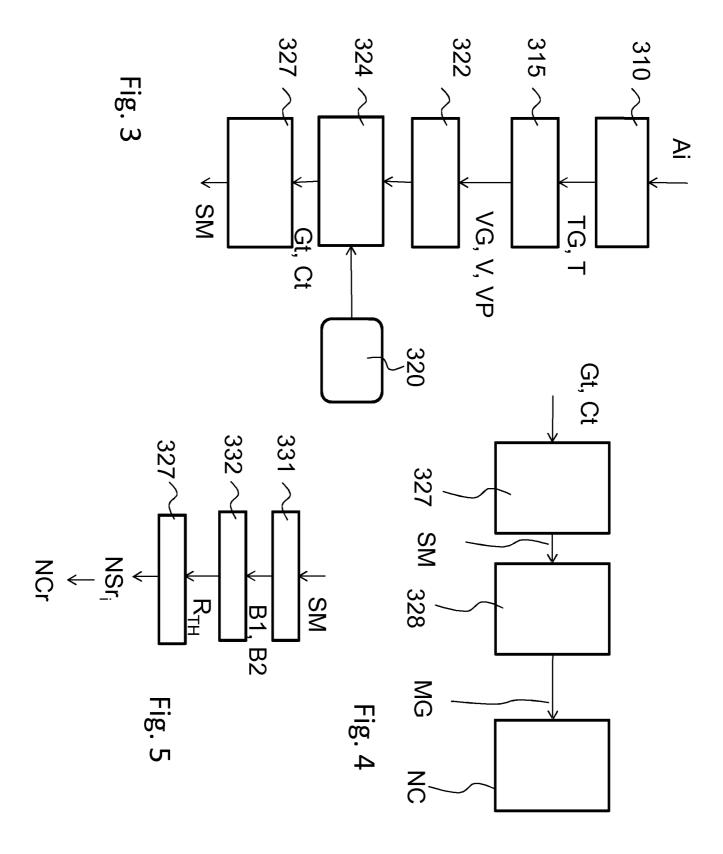

- le figure 3, 4, 5 rappresentano diagrammi di flusso rappresentativi di forme di attuazione del procedimento secondo l'invenzione,

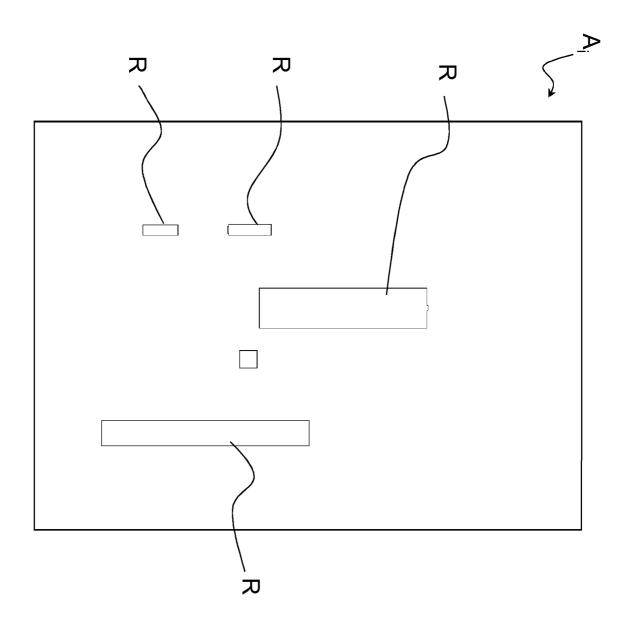

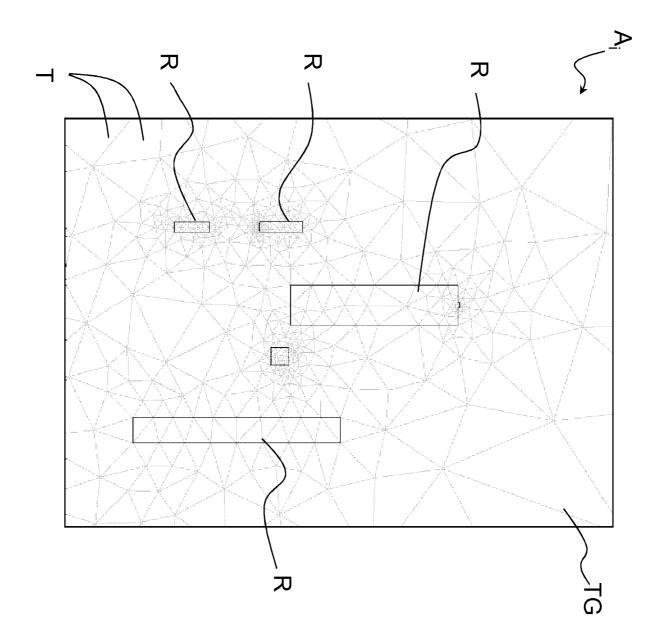

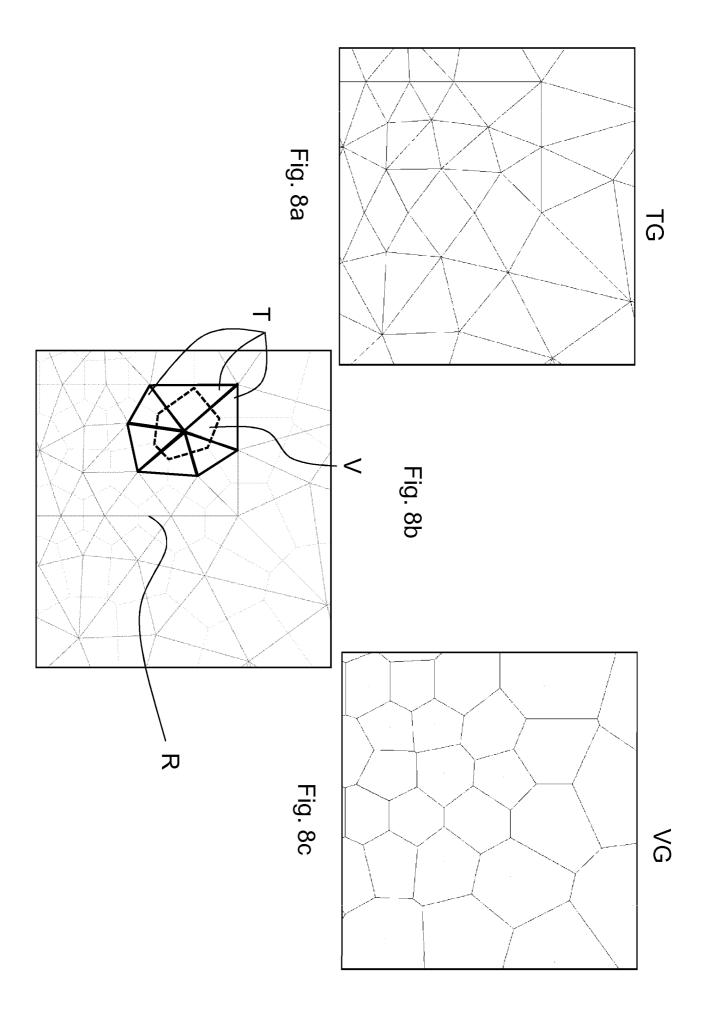

- le figure 6, 7, 8a, 8b, 8b rappresentano schematicamente viste di un layout sui cui opera il procedimento secondo l'invenzione,

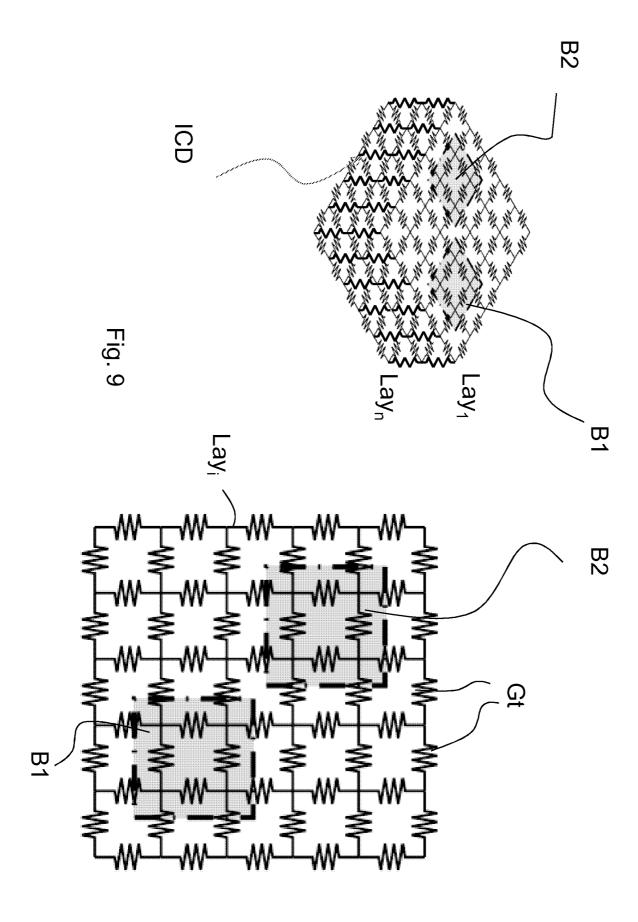

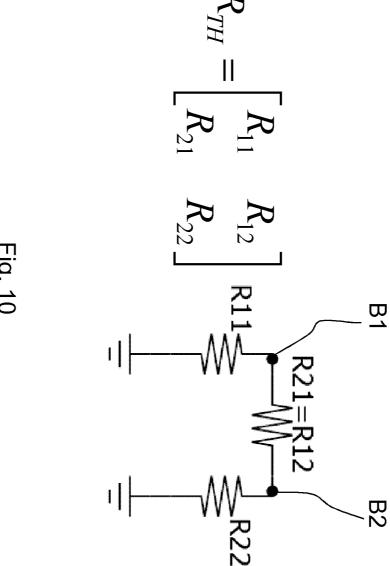

- le figure 9, 10 sono rappresentazioni equivalenti che illustrano passi di una specifica forma di simulazione implementata dal procedimento secondo l'invenzione,

# Descrizione particolareggiata

sequente descrizione sono illustrati Nella dettagli specifici finalizzati ad un'approfondita comprensione di vari esempi di attuazione. Le forme di attuazione possono essere realizzate senza uno o più dei dettagli specifici, o con altri metodi, componenti, materiali, etc. In altri casi, strutture, materiali operazioni noti non sono mostrati o descritti in dettaglio per evitare di rendere oscuri i vari aspetti delle forme di attuazione. Il riferimento ad "una forma di attuazione" nell'ambito di questa descrizione sta ad indicare che una particolare configurazione, struttura o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Quindi, frasi come "in una forma di attuazione", eventualmente presenti in diversi luoghi di questa descrizione non sono necessariamente riferite alla stessa di attuazione. forma Inoltre, particolari conformazioni, strutture o caratteristiche possono essere combinate in ogni modo adeguato in una o più forme di attuazione.

I riferimenti qui utilizzati sono soltanto per

comodità del lettore e non definiscono dunque l'ambito di tutela o la portata delle forme di attuazione.

La presente invenzione si riferisce a un procedimento per la progettazione automatica di sistemi e circuiti elettronici.

Secondo un aspetto dell'invenzione, tale procedimento comprende di generare un layout di detto elettronico, generare dati di abstract a livello substrato associati al layout di detto circuito elettronico, generare una griglia di suddivisione rispetto a una vista relativa a detto abstract in maglie e nodi e applicarla a detto substrato, estrarre in base a detta griglia di suddivisione una lista di nodi rappresentativa rete termica rappresentativa del comportamento termico del substrato o di sue porzioni o elementi, impiegare detta lista di nodi in operazioni di simulazione, in particolare di tipo SPICE, per compiere una valutazione di detti effetti termici in detto circuito elettronico.

E' previsto quindi di discriminare in detto layout regioni, in particolare in base a un criterio basato sulla dissipazione, suddividere il circuito elettronico secondo una pluralità di strati verticali, separare in ciascuno di detti strati differenti zone in base a determinati parametri tecnologici che le individuano, applicare detta griglia di suddivisione (TG) a ciascuna regione (R) di ciascuno strato.

Secondo un ulteriore aspetto dell'invenzione, detta operazione di applicare una griglia di suddivisione comprende di applicare una griglia triangolare di Delaunay e ottenere da detta griglia triangolare di Delaunay corrispondenti punti di Voronoi.

Secondo un ulteriore aspetto dell'invenzione è

previsto per ciascuno strato analizzare degli elementi di griglia ottenuti dall'operazione di suddivisione (300),

in funzione di un file di configurazione della tecnologia relativo all'elemento di griglia analizzato calcolare parametri termici da associare a detto elemento di griglia,

in base a detti parametri termici degli elementi di griglia costruire una rappresentazione dello strato come matrice sparsa di detti parametri termici. E' quindi previsto di costruire in base a dette matrici una matrice sparsa generale e convertire detta matrice sparsa generale in una netlist completa.

Secondo un aspetto dell'invenzione è previsto di estrarre dipendenze termiche fra due o più sorgenti termiche identificate in detta matrice tramite le operazioni di ridurre ciascuna sorgente a un singolo nodo, operare con la sovrapposizione degli effetti separatamente da ciascuna sorgente il calcolo di una matrice termica ridotta, estrarre una corrispondente netlist ridotta.

Secondo un ulteriore aspetto dell'invenzione è previsto di impiegare dette netlist per simulazioni termiche o elettro-termiche, in questo caso simulando contemporaneamente sia il comportamento elettrico che il comportamento termico del circuito elettronico o di un suo dispositivo, tenendo conto delle interazioni con il circuito elettronico o con parti di esso.

Secondo un ulteriore aspetto dell'invenzione è previsto di operare una simulazione elettro-termica tramite il configurare detta operazione di simulazione per operare con descrizioni di modelli o sotto-circuiti di detto circuito elettronico definite comprendenti un nodo termico, connettere a detto nodo termico un generatore di

corrente equivalente che forza in detto nodo termico una corrente equivalente alla potenza dissipata in detto modello o sottocircuito, associare alla tensione che si realizza su detto nodo termico un incremento di temperatura del modello o sotto-circuito rispetto alla temperatura globale, connettendo a detto nodo termico reti termiche rappresentative del mutuo riscaldamento del circuito elettronico rappresentate da detta netlist complete o da detta netlist ridotta, in particolare calcolata avendo come sorgenti detto modello o sottocircuito e un'altra sorgente termica del circuito elettronico.

Secondo un'ulteriore aspetto dell'invenzione è previsto di associare a nodi definiti da detta matrice sparsa capacità termiche calcolate in funzione del volume di un corrispondente elemento della suddivisione e dei rispetti parametri tecnologici e associata fra il nodo e un nodo di massa termica di riferimento.

La lista di nodi termica sopra citata viene fornita come una netlist, in particolare di tipo flat per un simulatore basato su istanze, in particolare una 'flat SPICE netlist' in modo da essere compatibile con differenti simulatori e simulatori SPICE veloci.

Per netlist o lista di nodi si intende qui in generale una descrizione della connettività di un progetto elettronico, in particolare del progetto elettronico di un circuito elettronico. Come verrà meglio spiegato nel seguito, una netlist termica rappresenta l'equivalente circuitale elettrico di un modello termico.

Per netlist flat si intende una netlist di un design flat, nella quale vengono istanziate solo le istanze primitive. Eventuali design gerarchici vengono esplosi in modo ricorsivo, creando nuove copie di ogni definizione ogni volta che viene adoperata. Le netlist flat per questa ragione tendono a creare basi dati della netlist molto più grandi.

ulteriore aspetto dell'invenzione, Secondo un previsto un sistema di progettazione automatica di circuito elettronico, comprendente almeno un elaboratore elettronico configurato per implementare il procedimento l'invenzione, nonché un prodotto secondo informatico direttamente caricabile nella memoria di almeno บาท elaboratore elettronico e comprendente porzioni di codice implementare il procedimento software per secondo l'invenzione.

Dunque, in figura 1 è mostrato uno schema generale del procedimento secondo l'invenzione.

Con 100 è indicata un'operazione di definizione del database del layout fino al livello di substrato tramite uno strumento software di design di layout, in particolare utilizzando ad esempio la piattaforma di EDA Cadence, Virtuoso Platform. In altre parole utilizzando uno strumento di design di dispositivi e circuiti viene generato un layout dei circuito elettronico e i dati che definiscono tale layout vengono immagazzinati in un database.

A partire da tale database del layout, dalla quale è generale una vista di layout L, in un passo 200 viene eseguita la generazione di abstract A e il raffinamento dei dati di abstract generati. Il procedimento prevede in una forma di attuazione di ottenere l'abstract generato A tramite un'operazione di semplificazione della vista del layout a livello di substrato, distinguendo ad esempio fra strutture termicamente dissipanti e strutture termicamente non dissipanti. Gli abstract vengono comunque creati a

partire dal dettagliato layout nel database degli abstract, ossia gli elementi per la cosiddetta abstract view, o vista sommaria, degli elementi (celle) definiti nel layout, comprendenti informazioni sintetiche quali nome della cella, orientamento, nomi dei pin e altre informazioni. Come opera un generatore di abstract a partire dal layout è di per sé noto al tecnico del settore. Si noti che il procedimento nella forma realizzativa qui descritta è integrato con l'ambiente Cadence, in quanto è possibile lanciare il corrispondente programma senza uscire da tale ambiente; inoltre per l'elaborazione del layout il procedimento o programma si basa sul database Cadence.

In un passo 300 viene eseguita quindi la generazione di una griglia di suddivisione TG rispetto all'abstract A e eventualmente il raffinamento di tale griglia procedura per la generazione della griglia TG viene eseguita ad esempio attraverso l'esecuzione di un modulo software esterno, ad esempio il software 'Triangle' (reperibile ad esempio all'URL https://www.cs.cmu.edu/~quake/triangle.html) libero di utilizzo. Il procedimento secondo l'invenzione il relativo prodotto informatico sono configurati per eseguire tale modulo software in maniera automatica e trasparente all'utente.

In un passo 400 viene quindi eseguita la generazione di netlist N, ad esempio una netlist completa NC del substrato che ne descrive la rete termica.

Tale netlist completa del substrato NC viene fornita a un ambiente di simulazione della netlist 500 incorporato nel procedimento e sistema come ulteriore servizio.

Tale netlist N o netlist completa del substrato NC viene fornita quindi a un ambiente di simulazione

elettrotermica accoppiata 600 (Coupled electrothermal simulation) incorporato nel procedimento e sistema come ulteriore servizio.

In figura 2 è illustrata in sezione una porzione del substrato di un generico chip circuito elettronico integrato, indicato con il riferimento ICD, al fine di illustrare una procedura di descrizione con approccio multistrato 1000 descritta più avanti con riferimento a figura 2. Tale porzione ICD, che può essere rappresentativa di un dispositivo, comprende strati con diverse proprietà, in particolare dal punto di vista termico. Nel presente esempio si fa riferimento a un modello semplificato in cui si considerano regioni di semiconduttore SCL, regioni di isolante INL e, non raffigurate, regioni di deep trench. La procedura di descrizione 1000 comprende di impiegare un approccio multistrato che, con riferimento alla sezione di porzione del substrato di fig. 1, prevede, data una vista a livello abstract A<sub>i</sub> del substrato e discriminate, esempio tramite un criterio basato sulla dissipazione, delle regioni poligonali, di solito corrispondenti dispositivi che dissipano potenza quali MOS o BJT, ma anche resistori e altri dispositivi, dalle regioni che non dissipano potenza, effettuare il procedimento di:

- suddividere il substrato in una pluralità di strati verticali, ossia disposti in direzione verticale, da uno strato di cima  $Lay_1$  a uno strato di fondo  $Lay_N$ ; tale suddivisione avviene di solito secondo gli strati individuati dai processi di fabbricazione;

- separare in ciascun i-esimo strato  $Lay_i$ , in figura 2 visto in sezione, le differenti regioni, che in una vista a livello di abstract, ciascuna associata

a un diverso tipo di parametri tecnologici che contraddistinguono tale regione, ossia parametri che indicano ad esempio se si tratti di una regione semiconduttore o isolante.

Tali operazioni sono in una forma d'attuazione completamente automatiche e si basano sulla vista abstract e sulle informazioni topologiche contenute in tale vista abstract. I dati relativi a ogni porzione di substrato vengono estratti incrociando tali informazioni topologiche contenute nell'abstract e i dati di processo contenuti nei file tecnologici.

Con riferimento alle operazioni di generazione di griglia descritte nel seguito, nella figura 2 si evidenzia come sia previsto di impiegare nel passo 400 per ciascuno strato  $\text{Lay}_1...\text{Lay}_N$  una medesima griglia TG di partizione tracciata sulla faccia superiore dello strato di cima  $\text{Lay}_1$ , che viene poi applicato a ogni strato  $\text{Lay}_i$ . Tale griglia TG, come dettagliato nel seguito, secondo un aspetto dell'invenzione, è una griglia di partizione triangolare di Delaunay.

I parametri tecnologici contenuti nei file tecnologici si riferiscono ad esempio alla resistività termica dei materiali strato per strato e/o alla loro capacità termica, oltre che a parametri termici di resistenza o capacità termica specifici delle interfacce fra strati o delle giunzioni.

In figura 3 è mostrato un diagramma di flusso che dettaglia il processo 300 di generazione della griglia, che comprende, per ciascun i-esimo strato Lay<sub>i</sub> un passo 310 di generazione di una griglia TG triangolare di Delaunay. Tale passo 310, come meglio mostrato in figura 7, determina l'individuazione di una pluralità di elementi triangolari T

in ciascun rispettivo strato  $Lay_1...Lay_N$  di spessore corrispondente allo spessore del rispettivo i-esimo strato  $Lay_i$ . Si noti che la griglia TG è unica e viene generata sul livello dell'abstract. Attraverso un processo di 'proiezione' la griglia viene replicata su ogni i-esimo strato  $Lay_i$ . Come meglio discusso nel seguito gli elementi triangolari T risultanti, che sono in realtà elementi dello i-esimo strato  $Lay_i$  aventi forma di prisma triangolare avente per base il triangolo determinato dalla suddivisione e per altezza lo spessore di tale strato, sono gli elementi base per calcolare per ciascuno strato una rispettiva matrice termica.

In un passo 315 tuttavia viene generata in base alla griglia triangolare di Delaunay TG, una griglia duale di Voronoi VG. Tale trasformazione di per sé nota determina, una tassellatura in celle di Voronoi V. Ai fini del procedimento non è di per sé d'interesse la tassellatura in celle, ma dei punti di Voronoi VP che esse individuano. Come noto si intende punto di Voronoi di un triangolo di Delaunay il centro della circonferenza circoscritta a detto triangolo.

Quindi, in un passo 322, ciascun elemento triangolare dell'i-esimo strato Lavi viene analizzato determinarne le dimensioni. Ad ogni elemento triangolare T dell'i-esimo layer Layi viene attribuito uno spessore ed un materiale, a seconda della tipo di sua posizione nell'abstract e dell'i-esimo layer Layi a cui è associato. Da queste informazioni in un passo 324 si estraggono i rispettivi valori di conduttanza termica Gt associati allo specifico triangolo T. Tali valori di conduttanza termica Gt vengono connessi fra il punto di Voronoi VP pertinente al triangolo T, e i punti di Voronoi ottenuti applicando il passo 315. In tale passo 324, in funzione di un file di 320, che configurazione della tecnologia fornisce informazioni sui parametri tecnologici di ogni strato e calcolati regione, vengono quindi gli elementi conduttanza termica Gt da associare ai punti della griglia di Voronoi VG, costruendo così una mesh di resistenze termiche. In un passo 327 viene costruita poi rappresentazione dell'i-esimo strato Layi come matrice sparsa SM di conduttanze termiche GT. La matrice sparsa SM è legata alla descrizione della mesh di resistenze termiche esempio tramite il cosiddetto 'metodo modificato'. Il valore di ogni elemento resistivo termico è calcolato ad esempio in base alla teoria degli 'elementi finiti'.

Tale matrice sparsa SM in una forma realizzativa mostrata in figura 4 è passata a un motore di calcolo matrice sparsa 328, che lega tutte le matrici sparse SM strati in un'unica matrice sparsa generale rappresentante la struttura tridimensionale completa. Ad esso si accompagna un passo di creazione di un file con l'information abstract. In base alla matrice generale MG viene quindi costruita in un passo 328 una netlist completa substrato, o full netlist, NC, che indica connessione dei nodi termici cui sono connessi componenti, in particolare le conduttanze termiche nell'esempio qui discusso, calcolate al passo 324.

Tale netlist completa del substrato NC, come detto, può essere una netlist flat, che è vantaggiosamente più semplice da instanziare, in quanto per questo, ad esempio. basta un comando 'include' nella netlist SPICE principale. Tale tipo di descrizione evita all'utente di dover dichiarare i punti di accesso alla rete, uno per ogni

elemento di abstract. In termini di struttura di database, una descrizione di tipo netlist flat non porta alcun detrimento dal punto di vista di memoria occupata durante la simulazione, rispetto a una descrizione di tipo sottocircuito, perché questo tipo di netlist viene instanziata una volta sola.

In figura 6 è mostrata la vista abstract  $A_i$  di un layer i-esimo Layi, come ottenibile ad esempio attraverso la Virtuoso Layout Suite, in cui sono presenti regioni R, rettangolari a puro titolo di esempio non limitativo, relative a cinque generici dispositivi che dissipano potenza. Ciò origina dal passo 200 di generazione di abstract precedentemente descritto. In particolare, ad esempio, viene aperta, in modo di per sé noto, la visualizzazione in modo layout di una suite di progetto quale Cadence Virtuoso Layout Suite e viene generata una sottovista abstract A del layout.

Su tale vista abstract  $A_i$  del layer i-esimo, individuare le regioni R è possibile in generale operare funzioni di 'merge', 'slice' e etichettatura di geometrie. Tali funzioni, dato uno strato visualizzato a livello di abstract permettono rispettivamente di fondere suddividere le geometrie generate automaticamente generare e assegnare nomi o etichette progressive alle geometrie della vista abstract  $A_i$ . E' possibile eseguire operazioni di definizione di regioni e compattazione di regioni che prevedono di operare sulla vista originale abstract Ai per modificarla o generare regioni artificiali. definizione delle regioni considerare opera per generiche aree di dissipazione da parte delle geometrie dell'abstract  $A_i$  comprese nella regione artificiale, la compattazione di regioni opera per preservare l'area complessiva delle geometrie comprese nella regione artificiale.

Data la generazione della griglia triangolare TG e di un associato database delle mesh, o maglie della griglia, è possibile eseguire aggiuntivamente anche operazioni di raffinamento locale/globale. Le operazioni di raffinamento locale/globale comprendono ad esempio indicare la qualità della maglia o mesh secondo un trade-off, o bilancio, fra la risoluzione che si desidera e il numero di elementi di maglia generati.

Come esemplificato in figura 7, viene quindi generata, secondo l'operazione 310 di figura 3, una griglia di Delaunay sulla vista abstract  $A_i$  del layer  $Lay_i$ .

Come esemplificato con riferimento alle figure 8a, 8b, 8c da una griglia di Delaunay TG come quella mostrata in figura 8a, si passa a una griglia di Voronoi VG, mostrata in figura 8c, come descritto nel passo 315. In figura 8b si possono vedere ambedue le griglie TG e VG. Nei punti di Voronoi VP di ciascuna cella V è previsto di connettere i resistori termici Gt per il caso statico e dei capacitori per il caso dinamico.

Come discusso in precedenza, l'associazione ai punti di Voronoi VP relativi a rispetti triangoli T delle rispettive conduttanze termiche Gt calcolate secondo i passi 322 e 324 produce la matrice sparsa SM di conduttanze termiche, come indicato in figura 3.

Tale matrice SM in definitiva è costruita assegnando a ciascuno dei punti di Voronoi VP individuati un indice progressivo, ad esempio da 1 a n, e costruendo la matrice quadrata A in cui ogni elemento  $a_{pq}$  con p indice da 1 a n delle righe e q indice da 1 a n delle colonne indica il valore di conduttanza termica G fra due nodi.

Ciò permette in generale una rappresentazione come rete termica a partire dalla matrice come raffigurata in figura 9. Per ciascun layer Layı...Layı si ha una rappresentazione layer per layer data dalla rispettiva matrice SM, dove sono indicate le conduttanze termiche Gt mentre i layer in corrispondenza dei nodi sono uniti da conduttanze termiche verticali che sono calcolati in base ai parametri tecnologici e in funzione dello spessore del layer.

In tale rappresentazione sono inoltre indicate due aree di nodi B1 e B2 che si comportano da sorgenti termiche, ad esempio due aree corrispondenti a due dispositivi, ad esempio due MOSFET.

Dunque, le operazioni descritte fino ad ora producono rappresentazione matriciale di conduttanze termiche del substrato dal punto di vista del modello termico e una corrispondente netlist, che può essere impiegata con i simulatori.

La netlist, ad esempio la netlist completa NC può essere fornita all'ambiente di simulazione della netlist 500 per una simulazione del solo comportamento termico. In altre parole, ad esempio un simulatore di tipo SPICE calcola ad esempio le temperature ai nodi, che sono di l'equivalente termico tensioni, applicando generatori di corrente rappresentativi di sorgenti dissipano potenza in specifici nodi. Naturalmente, questo può essere fatto anche a livello di netlist termica completa ridotta NCr.

Tuttavia, secondo una versione preferita del procedimento, le netlist prodotte dal procedimento secondo l'invenzione vengono impiegate nell'ambiente di simulazione elettrotermica accoppiata 600 (Coupled electrothermal

simulation), che provvede a simulare contemporaneamente, tramite un simulatore di tipo SPICE, sia il comportamento elettrico che il comportamento termico, di un dispositivo o circuito, tenendo conto delle interazioni con il chip o con parti di esso.

In questo ambito, secondo un ulteriore aspetto, è previsto, come detto di ottenere netlist ridotte per descrivere l'interazione mutua fra due sorgenti, quali B1 e B2 in figura 9.

Nel seguito viene fornita una descrizione di come viene operato il calcolo statico a questo riguardo.

Dato il sistema di equazioni lineari Ax=b, dove:

A rappresenta la matrice sparsa SM (simmetrica e definita non-negativa) di conducibilità termiche considerata tridimensionalmente

x è la soluzione di tale sistema, in particolare una temperatura per ciascun nodo termico della struttura;

b è il termine noto (le sorgenti applicate al sistema).

$$\begin{bmatrix} a_{11} & \cdots & a_{1n} \\ \vdots & \ddots & \vdots \\ a_{n1} & \cdots & a_{nn} \end{bmatrix} \bullet \begin{bmatrix} x_{11} & x_{12} \\ \vdots & \vdots \\ x_{n1} & x_{n2} \end{bmatrix} = \begin{bmatrix} b_{11} & b_{12} \\ \vdots & \vdots \\ b_{n1} & b_{n2} \end{bmatrix}$$

il procedimento secondo l'invenzione secondo una forma preferita comprende di risolvere tale sistema lineare e di estrarre le dipendenze termiche fra le sorgenti B1 e B2 in modo da ridurre in grande misura la dimensione della matrice della soluzione.

L'estrazione di tali dipendenze opera in maniera analoga alla sovrapposizione degli effetti. Il calcolo di autovalori e auto vettori può essere applicato per ottenere valori di frequenza da impiegare nel caso dinamico .

E' pertanto previsto di operare nel seguente modo,

come mostrato nel diagramma di flusso di figura 5:

- ridurre 331 ciascuna sorgente B1, B2, che si compone in generale di una pluralità di nodi nella rappresentazione matriciale e nella corrispondente rete termica rappresentata dalla netlist, a un singolo nodo termico. Il modo di eseguire tale operazione è di per sé noto, ad esempio tramite il Principio di Sovrapposizione degli Effetti;

- operare 332 con la sovrapposizione degli effetti separatamente dalla sorgente B1 e B2 il calcolo di una matrice termica ridotta  $R_{\it TH}$ .

La dimensione della matrice termica ridotta  $R_{TH}$  è eguale al numero di sorgenti, ad esempio  $2 \times 2$  in questo caso.

In figura 10 è mostrata la matrice termica ridotta  $R_{TH}$

$$R_{TH} = \begin{bmatrix} R_{11} & R_{12} \\ R_{21} & R_{22} \end{bmatrix}$$

e il corrispondente circuito risultante con i nodi B1, B2 corrispondenti alle sorgenti.

Gli elementi della matrice ridotta sono gli elementi della rappresentazione a doppio bipolo. Con  $R_{11}$  è indicata la resistenza termica equivalente al nodo della sorgente B1, quando il nodo della sorgente B2 è connesso a un circuito aperto,  $R_{22}$  viceversa la resistenza equivalente vista dal nodo della sorgente B2 con la sorgente B1 sostituita da circuito aperto, mentre  $R_{12}$  e  $R_{21}$  sono le resistenze termiche mutue (rapporto fra la tensione sul nodo della sorgente B1 a circuito aperto e la corrente determinata dalla sorgente al nodo B2 e viceversa). Tali resistenze mutue sono in generali equali,  $R_{12}$  =  $R_{21}$ .

La matrice  $R_{\text{TH}}$  può quindi essere passata al passo 327 di figura 3 per l'estrazione di una netlist ridotta NCr.

Fino ad ora il procedimento è stato descritto con riferimento alla modellizzazione tramite solo conduttanze termiche della rete termica e quindi anche solo alla simulazione del caso statico.

La rappresentazione della rete termica di conduttanze termiche può essere completata tuttavia tramite l'aggiunta di valori di capacità termica, il cui valore dipende dal volume dell'elemento di maglia, in particolare il prisma a base triangolare T ed altezza pari allo spessore del layer, oltre che dai parametri tecnologici. Il corrispondente capacitore viene connesso fra il nodo corrispondente all'elemento triangolare e il nodo di riferimento di massa termica.

Per quanto riguarda la simulazione dinamica, operando come appena descritto aggiungendo le capacità termiche, risulta dunque una rete complessa con una molteplicità di poli. Per ovviare alla complessità del sistema è possibile ottenere un sistema approssimato impiegando il metodo di Galerkin, che somma la risposta del sistema a differenti frequenze usando vettori di base (come le funzioni di Green). Esempi di tale approccio per le simulazioni elettrotermiche, di per sé noto, si ritrovano ad esempio nelle pubblicazioni "Compact Modeling of Electrical Devices for Electrothermal Analysis", L. Codecasa et all, TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: FUNDAMENTAL THEORY AND APPLICATIONS, VOL. 50, NO. 4, APRIL 2003 e "Compact Models of Dynamic Thermal Networks with Many Heat Sources", L. Codecasa, IEEE TRANSACTIONS ON COMPONENTS AND PACKAGING TECHNOLOGIES, VOL. 30, NO. 4, DECEMBER 2007.

E' da sottolineare come, secondo un aspetto importante dell'invenzione, è possibile operare, sulla base delle netlist complete o ridotte, la simulazione elettrotermica

600, in modo vantaggioso in quanto si permette di operare una simulazione che tiene conto sia dei parametri elettrici sia dei parametri termici del substrato.

Ulteriori vantaggi dal punto di vista computazionale nell'ambito della simulazione si realizzano dal poter operare con netlist ridotte e, a fine della procedura di figura 4, netlist complete ridotte NCr, ossia netlist che rappresentano l'interazione fra due o piu' dispositivi a livello di substrato.

Tali netlist ridotte risultano particolarmente vantaggiose quando, nell'ambito della simulazione elettrotermica di operare con netlist elettriche di componenti o sotto-componenti in cui è definito un nodo termico, ossia un nodo a cui connettere una rete termica per la simulazione elettro-termica.

E' nota ad esempio la presenza di tali nodi termici in dedicati compact model, ossia modelli compatti di componenti standard, ad esempio il nodo termico del modello del BSIM3SOI MOS. Naturalmente, anche una netlist termica completa può essere collegata a tale nodo.

Secondo un ulteriore aspetto, descritto in una domanda co-depositata dalla Richiedente, è previsto di includere un nodo termico nella descrizione a livello di netlist del modello o sottocircuito impiegato per la simulazione di un componente (MOS, BJT, HV MOS, resistore ...). La definizione di nodo termico viene applicato tramite uno statement dedicato nella netlist.

E' previsto dunque di configurare l'operazione di simulazione eseguita dal simulatore per operare con descrizioni di modelli o sotto-circuiti di dispositivi, che sono in particolare non-standard, definite come comprendenti un nodo termico. L'operazione di simulazione

comprende così di connettere al nodo termico un generatore di corrente equivalente che forza in tale nodo termico una corrente equivalente alla potenza dissipata in detto modello o sottocircuito, e inoltre di associare alla tensione che si realizza sul nodo termico un incremento di temperatura del modello o sotto-circuito rispetto alla temperatura globale.

Come detto, è previsto di connettere al nodo termico reti termiche rappresentative del mutuo riscaldamento circuito elettronico, che possono essere rappresentate dalle netlist complete NC o, in particolare, dalle netlist NCr, calcolate ad esempio fra il ridotte modello sottocircuito in questione e altre sorgenti termiche del chip. Inoltre, può essere connessa anche una rete termica che modella l'auto-riscaldamento del dispositivo o sottocircuito. Gli effetti termici di tali reti vengono simulati adoperando come sorgente la corrente forzata nel nodo termico. L'operazione di simulazione, associando tensione sul nodo termico a un incremento di temperatura del modello o sotto-circuito, aggiorna dunque i parametri dei modelli di dispositivo e i parametri di sotto-circuito (20)secondo la temperatura locale usando leggi dipendenza termica incorporate nei modelli o scritte nei parametri di sotto-circuito o modello.

Dunque il procedimento e sistema secondo l'invenzione permettono di estrarre una netlist termica del substrato, utile per simulare il comportamento termico a livello di substrato fra dispositivi in un chip e per la simulazione elettrotermica. Si include infatti così in un unico ambiente la simulazione elettro-termica completa dalla estrazione delle strutture rilevanti dal layout, al calcolo delle matrici (ossia equazioni) rappresentative del sistema

termico tramite metodo agli elementi finiti e il calcolo di netlist corrispondenti. In particolare il procedimento permette di estrarre in modo semplice netlist ridotte che agevolano il calcolo. E' inoltre vantaggiosamente possibile creare una rete elettrica equivalente che modellizza il comportamento termico in cui ogni sorgente è rappresentata da un nodo.

Le netlist ottenute con il procedimento secondo l'invenzione sono vantaggiosamente connettibili al circuito di partenza o a dispositivi di tale circuito tramite un nodo termico presente nella loro descrizione circuitale.

Vantaggiosamente, rispetto ad esempio a un metodo di generazione della griglia ortogonale, il procedimento impiegando il metodo di Delaunay aumenta la precisione diminuendo il numero di elementi. Infatti, per la sua caratteristica di massimizzare gli angoli minimi dei triangoli, questo tipo di triangolazione tende a produrre triangoli equiangoli, rendendo le griglie uniformi. La trasformazione di Voronoi dà una griglia duale per la connessione delle conduttanze termiche.

Naturalmente, fermo restando il principio dell'invenzione, i particolari di realizzazione e le forme di attuazione potranno variare, anche in modo significativo rispetto a quanto qui illustrato a puro titolo di esempio non limitativo, senza per questo uscire dall'ambito di protezione. Tale ambito di protezione è definito dalle rivendicazioni annesse.

Il procedimento per la progettazione automatica di un circuito elettronico secondo l'invenzione può essere naturalmente compreso nel processo di produzione del corrispondente circuito elettronico, che integra le operazioni di progetto o design con operazioni di

fabbricazione del circuito integrato, ad esempio nell'ambito della cosiddetta silicon foundry, ossia lo stabilimento o la parte di linea di produzione che esegue tali operazioni di fabbricazione.

Il procedimento per la progettazione automatica di un circuito elettronico secondo l'invenzione può essere adoperato non solo per ottenere una netlist termica a livello di dispositivo, ma anche per ottenere in modo analogo netlist a livello floorplan e macrocelle.

Le netlist di uscita sono scritte preferibilmente con puro formato sintattico SPICE e sono compatibili con simulatori veloci di tipo SPICE (Hsim e Ultrasim) quali Eldo, Spectre.

Il procedimento per la progettazione automatica di un circuito elettronico secondo l'invenzione può essere esteso grazie all'approccio multilayer, anche a tecnologie diverse dal BCDx, ed è comunque applicabile a tecnologie BCD8AS, BCD8SP, BCD8SAutoDTI, BCD8SOI, BCD8SP\_DTI, BCD9s e BCD9sL.

### RIVENDICAZIONI

1. Procedimento per la progettazione automatica di un circuito elettronico, del tipo che comprende operazioni di valutazione degli effetti termici in detto circuito elettronico, comprendente

generare (100) un layout (L) di detto circuito elettronico,

generare (200) dati di abstract (A) a livello di substrato associati al layout (L) di detto circuito elettronico,

generare (300) una griglia (TG) di suddivisione rispetto a una vista relativa a detto abstract (A) in maglie e nodi e applicarla a detto substrato (ICD),

estrarre (400) in base a detta griglia di suddivisione (TG) una lista (N, NC, NCr) di nodi rappresentativa di una rete termica rappresentativa del comportamento termico del substrato (IDC) o di sue porzioni o elementi (B1, B2),

detta lista (N, NC, NCr) di nodi essendo configura per essere impiegata in operazioni di simulazione, in particolare di tipo SPICE, per compiere una valutazione (500, 600) di detti effetti termici in detto circuito elettronico.

2. Procedimento secondo la rivendicazione 1, comprendente

discriminare in detto layout regioni (R), in particolare in base a un criterio basato sulla dissipazione,

suddividere il circuito elettronico secondo una pluralità di strati ( $\text{Lay}_1$ ... $\text{Lay}_N$ ) verticali,

separare in ciascuno di detti strati (Lay<sub>1</sub>...Lay<sub>N</sub>)

differenti zone in base a determinati parametri tecnologici che le individuano;

applicare detta griglia di suddivisione (TG) a ciascuna regione (R) di ciascuno strato ( $Lay_1...Lay_N$ ).

- 3. Procedimento secondo una delle rivendicazioni precedenti, in cui detta operazione di applicare una griglia (TG) di suddivisione comprende di applicare una griglia triangolare di Delaunay e ottenere da detta griglia triangolare di Delaunay corrispondenti punti di Voronoi (VP).

- 4. Procedimento secondo una delle rivendicazioni precedenti, che comprende

per ciascuno strato (La $y_i$ ) analizzare (322) degli elementi di griglia (T) ottenuti dall'operazione di suddivisione (300),

in funzione di un file di configurazione della tecnologia relativo all'elemento di griglia analizzato (T) calcolare (320) parametri termici (Gt;  $C_{\rm t}$ ) da associare a detto elemento di griglia (T),

in base a detti parametri termici (Gt;  $C_t$ ) degli elementi di griglia (T) costruire (325) una rappresentazione dello strato (Lay<sub>i</sub>) come matrice sparsa (SM) di detti parametri termici (Gt;  $C_t$ ).

5. Procedimento secondo una delle rivendicazioni precedenti, che comprende

inserire (327) dette matrici sparse (SM) dello strato (Lay $_{\rm i}$ ) in un'unica matrice sparsa generale (MG),

convertire (328) detta matrice sparsa generale (MG) in una netlist completa (NC).

- **6.** Procedimento secondo una delle rivendicazioni precedente, che comprende di estrarre dipendenze termiche fra due o più sorgenti termiche (B1, B2) identificate in detta matrice (SM) tramite le operazioni di

- ridurre (331) ciascuna sorgente (B1, B2) a un singolo nodo

- operare (332) con la sovrapposizione degli effetti separatamente da ciascuna sorgente (B1, B2) il calcolo di una matrice termica ridotta  $R_{TH}$

- estrarre una corrispondente netlist (NCr) ridotta.

- 7. Procedimento secondo una delle rivendicazioni precedenti, che comprende di fornire detta netlist (NC, NCr) a una operazione di simulazione (500) del comportamento termico e/o a un'operazione di simulazione elettrotermica accoppiata (600) (Coupled electrothermal simulation), che simula contemporaneamente sia il comportamento elettrico che il comportamento termico del circuito elettronico o di un suo dispositivo, tenendo conto delle interazioni con il circuito elettronico o con parti di esso.

- 8. Procedimento secondo la rivendicazione precedente, che comprende operare una simulazione elettro-termica (600) tramite il configurare detta operazione di simulazione per operare con descrizioni di modelli o sotto-circuiti di detto circuito elettronico definite comprendenti un nodo termico, connettere a detto nodo termico un generatore di corrente equivalente che forza in detto nodo termico una corrente equivalente alla potenza dissipata in detto modello o sottocircuito, associare alla tensione che si

realizza su detto nodo termico un incremento di temperatura del modello o sotto-circuito rispetto alla temperatura globale, connettendo a detto nodo termico reti termiche rappresentative del mutuo riscaldamento del circuito elettronico rappresentate da detta netlist completa (NC) o da detta netlist ridotta (NCr), in particolare calcolata avendo come sorgenti (B1, B2) detto modello o sottocircuito e un'altra sorgente termica del circuito elettronico.

- 9. Procedimento secondo la rivendicazione precedente, caratterizzato da fatto che comprende associare ai nodi definiti da detta matrice sparsa (SM) capacità termiche calcolate in funzione del volume di un corrispondente elemento (T) della suddivisione e dei rispetti parametri tecnologici e associata fra il nodo (VP) e un nodo di massa termica di riferimento.

- 10. Sistema di progettazione automatica di un circuito elettronico, comprendente almeno un elaboratore elettronico configurato per implementare il procedimento secondo una qualsiasi delle rivendicazioni 1 a 9.

- 11. Prodotto informatico direttamente caricabile nella memoria di almeno un elaboratore elettronico e comprendente porzioni di codice software per implementare il procedimento secondo una qualsiasi delle rivendicazioni 1 a 9.

Fig. 2

Fig. 6

Fig. 7

Fig. 10