# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 5:

A 1

(11) International Publication Number:

WO 91/04538

**A1**

(43) International Publication Date:

4 April 1991 (04.04.91)

(21) International Application Number:

PCT/US90/05119

(22) International Filing Date:

G06F 13/00

11 September 1990 (11.09.90)

(30) Priority data:

409,926

20 September 1989 (20.09.89) US

(71) Applicant: SQUARE D COMPANY [US/US]; Executive Plaza, Palatine, IL 60067 (US).

(72) Inventors: JANKE, Donald, R.; 3142 S. 42nd Street, Milwaukee, WI 53215 (US). SABROFF, Richard, R.; 931 East Prospect Street, Lake Mills, WI 53551 (US).

(74) Agent: GOLDEN, Larry, I.; Square D Company, Executive Plaza, Palatine, IL 60067 (US).

(81) Designated States: AT (European patent), BE (European patent), CA, CH (European patent), DE (European patent)\*, DK (European patent), ES (European patent), FR (European patent), GB (European patent), IT (European patent), JP, LU (European patent), NL (European patent), SE (European patent).

#### Published

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

(54) Title: INPUT/OUTPUT MODULE HAVING A COMBINATION INPUT/OUTPUT POINT

#### (57) Abstract

A combination input/output (I/O) module (11) for a microprocessor based device is disclosed. The combination I/O module (11) includes a combination point (15) which is operable as either an input point adapted for coupling to an input device (17), an output point adapted for coupling to an output device (19) or both. The combination I/O module (11) provides continuous sensing of the presence or absence of the output device (19). The combination I/O module (11) includes a triac (21) and provides for continuous sensing of the conductive state of the triac (21).

## **DESIGNATIONS OF "DE"**

Until further notice, any designation of "DE" in any international application whose international filing date is prior to October 3, 1990, shall have effect in the territory of the Federal Republic of Germany with the exception of the territory of the former German Democratic Republic.

#### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| ΑT   | Austria                  | ES | Spain                        | MC | Monaco                  |

|------|--------------------------|----|------------------------------|----|-------------------------|

| AU . | Australia                | FI | Finland                      | MG | Madagascar              |

| BB   | Barbados                 | FR | France                       | ML | Mali                    |

| BE   | Belgium                  | GA | Gabon                        | MR | Mauritania              |

| BF   | Burkina Fasso            | GB | United Kingdom               | MW | Malawi                  |

| BG   | Bulgaria                 | GR | Greece                       | NL | Netherlands             |

| BJ   | Benin                    | HU | Hungary                      | NO | Norway                  |

| BR   | Brazil                   | IT | Italy                        | PL | Poland                  |

| CA   | Canada                   | JР | Japan                        | RO | Romania                 |

| CF   | Central African Republic | KP | Democratic People's Republic | SD | Sudan                   |

| CG   | Congo                    |    | of Korea                     | SE | Sweden                  |

| CH   | Switzerland              | KR | Republic of Korea            | SN | Senegal                 |

| CM   | Cameroon                 | LI | Liechtenstein                | SU | Soviet Union            |

| DΕ   | Germany                  | LK | Sri Lanka                    | TD | Chad                    |

| DK   | Denmark                  | LU | Luxembourg                   | TG | Togo                    |

|      |                          |    | -                            | US | United States of Americ |

- 1 -

INPUT/OUTPUT MODULE HAVING

A COMBINATION INPUT/OUTPUT POINT

#### DESCRIPTION

#### Technical Field

5

10

20

The present invention relates to microprocessor based controllers, such as programmable logic controllers ("PLCs"), and more particularly to an input/output (or "I/O") module having a combination I/O point for use with a microprocessor based industrial controller.

## 15 Background Prior Art

Microprocessor based controllers, such as programmable logic controllers are becoming more and more prevalent, controlling today's modern manufacturing plants as well as relatively simple automated machines and operations.

5

10

15

20

25

30

35

Typically a PLC includes at least one input module having a plurality of input points and at least one output module having a plurality of output points. The PLC receives information from another device, such as a switch, via one of the input points, and the PLC transmits information, such as to a motor starter, via one of the output points. Requiring separate input modules and output modules greatly reduces the flexibility of the PLC because the user must know in advance how many input points are required and how many output points are req-In addition, because one would always require a separate input point for each input signal and a separate output point for each output signal; one point could not simultaneously be used as both an input point and an output point.

Further, it is often important to determine whether an output device (or load) is actually connected to an output device. This load detection is important both for diagnostics as well as for various PLC operations. However load detection typically has required additional circuitry which operates only when an output signal is actually applied to the load. One has not been readily able to determine prior to actuation of the output signal whether or not the load is connected to its respective output point.

Finally, an AC output point typically includes a triac which selectively provides power to its respective output device in response to an output command from the PLC. However, prior art output modules have been unable to readily detect whether the triac in fact does turn on in response to an output signal. Detection of whether a triac has actually turned on is important both for triacs in conjunction with output modules as well as for

- 3 -

triacs in many other applications. However this too has typically required additional, external components.

The present invention is provided to solve these and other problems.

# Summary of the Invention

5

10

15

20

25

30

35

It is an object of the invention to provide a combination input/output module for a microprocessor based device, such as a programmable logic controller (or PLC)

In accordance with the invention, the combination I/O module comprises first and second lines and means for providing AC power between said first and second lines.

The combination I/O module further comprises a terminal and means adapted for coupling an input device between said terminal and said first line and means adapted for coupling an output device between said terminal and said second line.

The input device is operable between a first conductive state and a second conductive state.

The combination I/O module still further comprises means for determining the conductive state of said input device and means for selectively providing said power to said output device.

Accordingly, the combination I/O module is operable as either an input point adapted for coupling to said input device, an output point adapted for coupling to the output device, or both.

It is comprehended that the combination I/O module provides continuous sensing of the presence or absence of the output device.

It is still further comprehended that the combination I/O module includes a triac and provides for continuous sensing of the conductive state of the triac.

Other features and advantages of the invention will be apparent from the following specification taken in conjunction with the following drawing.

Brief Description of Drawings

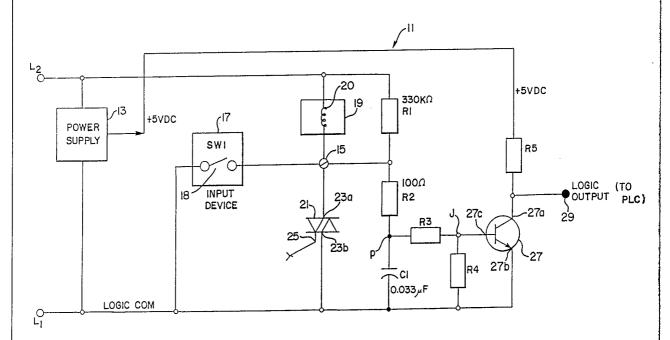

Figure 1 is a schematic illustration of one embodiment of the combination input/output module according to the invention;

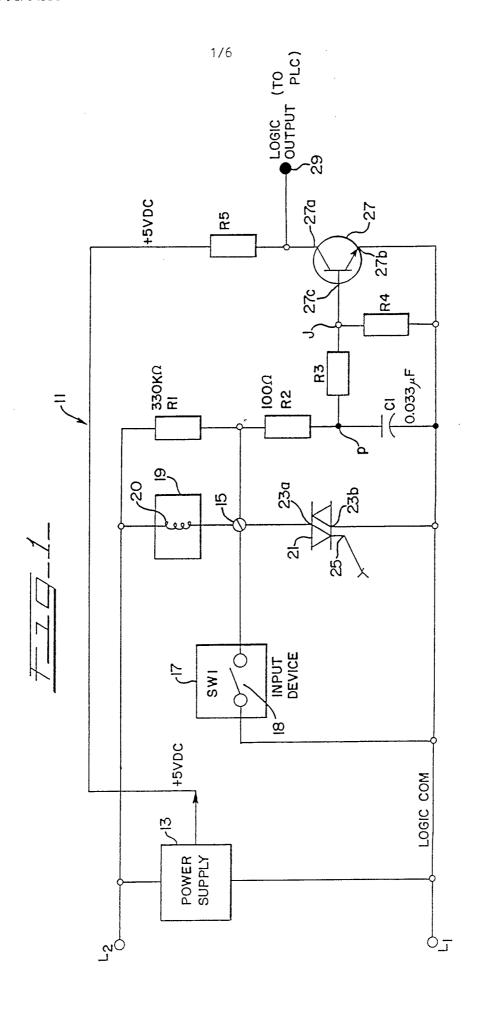

Figure 2 is a schematic illustration of the combination input/output module of Figure 1, connected as an input point;

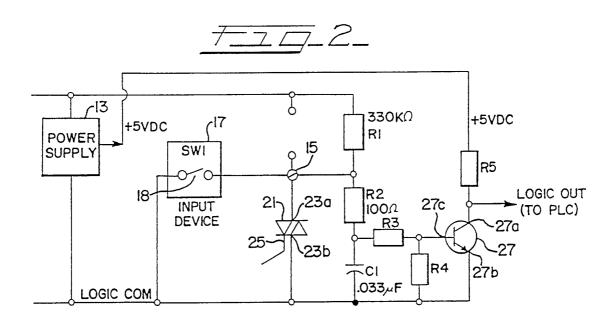

Figure 3 is a schematic illustration of the combination input/output module of Figure 1, connected as an output point;

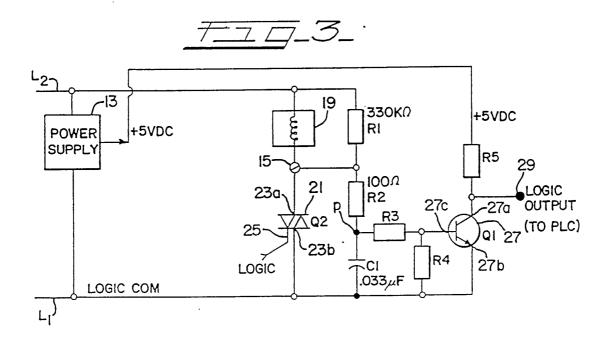

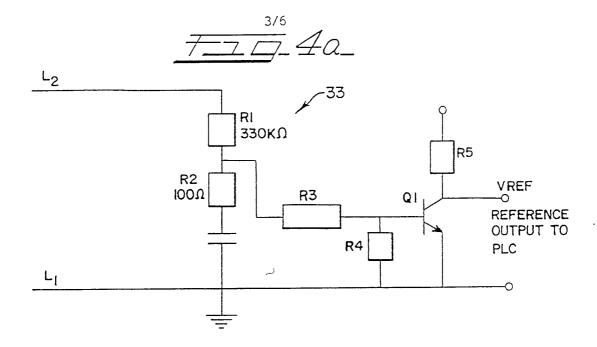

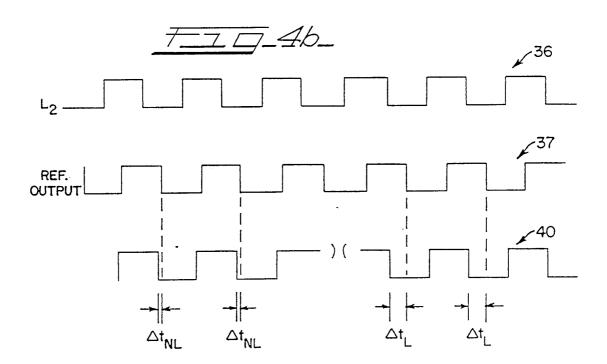

rigure 4 is a schematic diagram and wave form

diagram illustrating phase difference detection

circuitry;

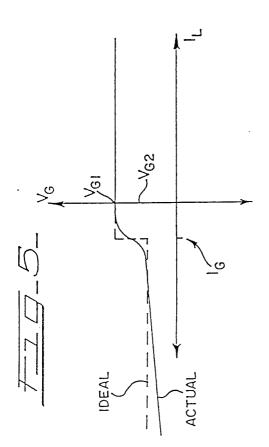

Figure 5 is a current versus voltage curve of the triac of the combination input/output module illustrating detection of whether the triac turned on:

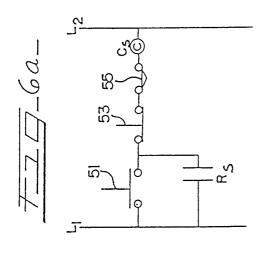

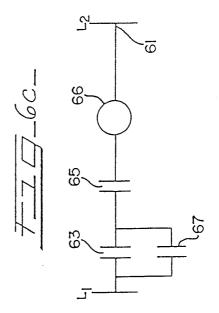

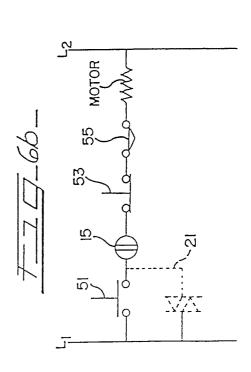

Figures 6a, b and c are ladder diagrams illustrating the combination input/output module of the present invention operative simultaneously as three inputs and one output point;

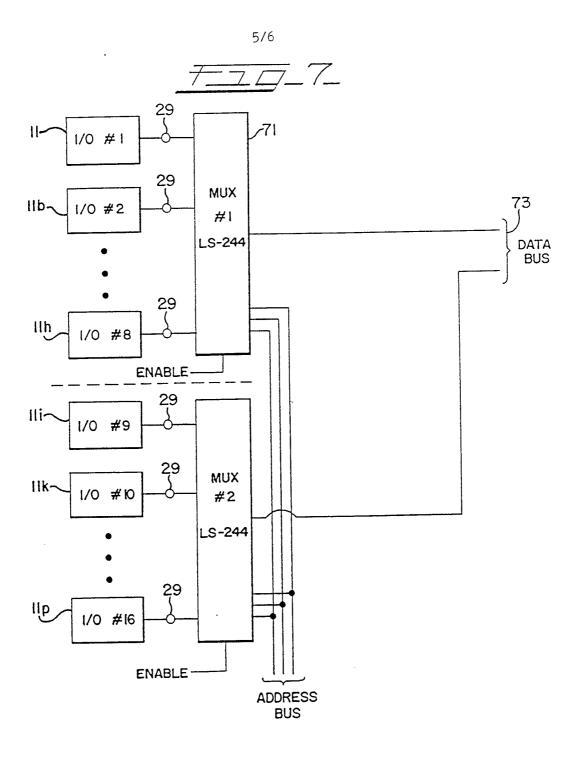

Figure 7 illustrates a combination I/O module including a plurality of combination I/O points.

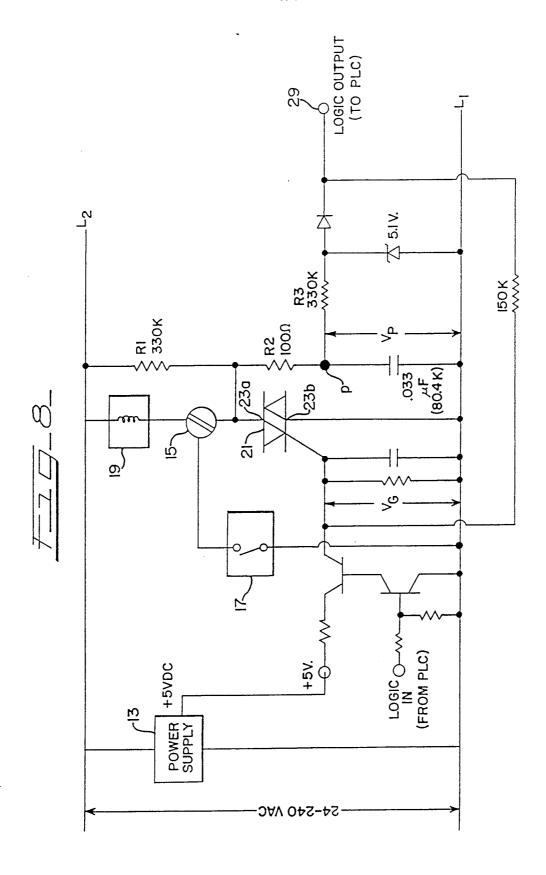

Figure 8 is a schematic diagram illustrating an alternative embodiment of the combination input/output module of Figure 1.

# 30 <u>Detailed Description</u>

5

10

15

20

25

35

While this invention is susceptible of embodiments in many different forms, there is shown in the drawings and will herein be described in detail, preferred embodiments of the invention with the understanding that the present disclosure is to be considered as an exemplification of the principles

of the invention and is not intended to limit the broad aspects of the invention to the embodiments illustrated.

A first embodiment of an I/O module having a combination I/O point, generally designated 11, is illustrated in Figure 1.

5

10

15

20

25

30

35

A power supply 13 (with a nominal potential of 24-240 volts AC) is connected between a first line L1 and a second line L2. The particular voltage used depends upon the load, though for purposes of this discussion, 120 volts will be assumed. The power supply 13 further provides 5 volts regulated DC, the use of which is discussed below.

A terminal 15 is provided which functions as the combination I/O point. If the combination I/O module 11 is to be used as an input point, an input device 17, such as a standard mechanical switch 18, is coupled between the terminal 15 and the first line L1. If the combination I/O module 11 is to be used as an output point, an output device 19, such as a coil 20 for a motor starter (not shown), is coupled between the terminal 15 and the line L2.

In certain applications discussed below, the combination I/O module 11 is operable simultaneously as both an input point and an output point. Accordingly, the input device 17 would be coupled between the terminal 15 and the first line L1, and the output device 19 would be coupled between the terminal 15 and the second line L2.

The combination I/O point 11 further includes a triac 21, such as 2N 6073 A, having first and second power electrodes 23a, 23b, respectively, and a gate electrode 25. The triac 21 is selectively switchable between a conductive, or 'on' state and a non-conductive, or 'off' state, as is well known.

- 6 -

5

10

15

20

25

30

35

The combination I/O module 11 further includes a first resister R1 (330 $\Omega$ ) coupled between the second line L2 and the terminal 15, a second resister R2 (100k $\Omega$ ) and a snubber capacitor C1 (0.033 $\mu$ F) coupled in series between the terminal 15 and the first line L1. Further included is a transistor 27 having power electrodes comprising a collector 27a and an emitter 27b, and a control electrode comprise a base 27c. A third resistor R3 is coupled between the transistor base 27c and a junction P of the second resistor R2 with the first capacitor C1. A fourth resistor R4 is coupled between the first line L1 and a junction J of the third resistor R3 with the transistor base 27c. A fifth resistor R5 is coupled between the 5 volt DC output of the power supply 13 and the collector 27a of the transistor 27.

Lower values of the first resister R1 will increase power loss and reduce load detection sensitivity. Higher values of the first resistor R1 reduce the base-emitter current  $I_{BR}$  of the transistor 27, increasing noise sensitivity. The 0.033 $\mu$ F value for the snubber capacitor C1 is based on tests with the power supply 13 at 120 VAC. Larger capacitance may be necessary for larger voltages.

The junction of the fifth resistor R5 with the collector 27a of the transistor 27 provides a logic output 29 which is utilized by the PLC, as is well known. As discussed below, the value of the logic output 29 indicates the status of the input device 17.

Referring to Figure 2, operation of the combination I/O module 11 as an input point is illustrated. The reference numerals relate to those elements discussed above with respect to Figure 1.

- 7 -

5

10

15

20

25

30

35

When the input device 17, such as the switch 18, is open, the voltage at the terminal 15 is determined by the voltage divider R1, R2, C1 (assuming the triac 21 is off). A current divider network comprising the third and fourth resistors R3 and R4 biases the transistor 27 on during positive line cycles. With the transistor 27 turned on, the voltage at the logic output 29 is logic low during positive half cycles. Thus, an open input device 17 results in a zero logic state output at the logic output 29 during positive half cycles.

When the input device 17 is closed, the voltage at the terminal 15 is shorted to ground, thus biasing the transistor 27 off for both positive and negative cycles. With the transistor 27 off, the voltage at the logic output 29 is held at the 5 volt DC supply voltage. Thus a closed input device 17 results in a 5 volt, or one logic state output at the logic output 29 for both positive and negative cycles.

The combination I/O module 11 utilized as an output point as illustrated in Figure 3. As with Figure 2, common reference numerals have been maintained in Figure 3.

To operate the combination I/O module 11 as an output point, the output device 19 is coupled between the terminal 15 and the second line L2. When the output device 19 is to be activated, the triac 21 receives a positive, logic on signal from the PLC (not shown) at the gate electrode 25 of the triac 21. The logic on signal turns on the triac 21, thus placing the output device 19 between the first and second lines L1, L2. Similarly, when the output device 19 is to be turned off, the triac 21 receives a logic off signal from the PLC, turning off the triac 21 at the next current zero crossing,

- 8 -

5

10

15

20

25

30

35

and thereby isolating the output device 19 from the first line L1. Since the triac 21 acts the same as the switch 18, the condition of the triac 21 can be monitored by the transistor circuit to determine if it is following its logic signals.

The combination I/O module 11 is further provided with load detection circuitry to detect the presence (or absence) of the output device 19 coupled between the second line L2 and the terminal 15 as well as circuitry to determine whether the triac 21 indeed turned on in response to a logic on signal from the PLC.

The following discussion describes how the load

19 is detected with both the triac 21 and the switch

17 'off'.

Typically, the impedance of the output device 19 is significantly lower than the impedance of the  $330k\Omega$  first resistor R1. Referring still to Figure 3, and assuming for the moment that the output device 19 is not coupled between the terminal 15 and the second line L2, the phase of the voltage  $(V_p)$  at the point P relative to the first line  $L_{\rm i}$  will lag the phase of the voltage  $(V_{L2})$  of the second line L2 relative to the first line L1 because of the capacitance of the snubber capacitor C1. impedance of the output device 19 is less than the impedance of the first resistor R1, when the output device 19 is coupled between the second line L2 and the terminal 15, the resistance of the first resistor R1 is effectively substantially reduced (in fact, R1 typically can be ignored).

In the limit, for example if the resistance of the output device 19 is  $0\Omega$ , the voltage  $V_p$  would be in phase with the voltage  $V_{L2}$ . In reality, because the output device 19 does have some impedance, the voltages  $V_p$  and  $V_{L2}$  will not be completely in phase;

**-** 9 **-**

5

10

15

20

25

30

35

however, their phases will be much closer than with no output device 19. Thus, by monitoring the phase relationship of the voltage  $V_{\rm p}$  relative to the voltage  $V_{\rm L2}$  one can constantly monitor the presence, of absence, of the output device 19.

A circuit for determining the phase difference between voltages  $V_p$  and  $V_{L2}$ , and hence the presence of absence of the output device 19, is illustrated Figures 4a and b.

A reference circuit 33 provides a square wave output  $V_{\rm ref}$  representing the voltage of an I/O point without a load connected. The reference circuit 33 is the same as the combination I/O module 11, but it does not have the terminal 15. A first wave form 36 representing the phase of the voltage of the second line L2 with respect to the voltage of the first line L1 is for reference only.

A second wave form 37 representing the phase of the voltage  $V_{\text{ref}}$  relative to the voltage on the first line L1 is generated at the collector of the transistor 27 of the reference circuit 33.

A third wave form 40 representing the phase of the voltage at the logic output 29 of the combination I/O module 11 with and without a load connected demonstrates the effect of the load on the phase of the voltage.

As illustrated, the load wave form is shifted by an amount t.

One way of detecting this phase delay is by sampling both the second and the third wave forms 37, 40, respectively, and passing the sampled data through a respective register of the PLC as a software oscilloscope of the wave forms 37, 40. By comparing these two registers, the PLC can determine the phase difference and, hence, the presence or absence of the output device 19. The particular

5

10

15

20

25

30

35

sampling rate necessary depends on the impedance of the components as well as of the output device 19, as such relative values determine the total phase difference between load and no-load conditions. In addition, by memorizing the phase shift for a given load when the triac 21 is off, one can detect changes in load characteristics such as the beginning failure of a motor starter coil.

The above discussion permits the combination I/O module 11 to detect the presence or absence of a load when the triac 21 is off. Detection of the presence or absence of a load when the triac 21 is on is illustrated in Figure 5.

Figure 5 illustrates the relationship between the load current through the triac 21,  $I_{L1}$  versus the gate voltage  $V_{\text{G}}$  for the triac 21. An "ideal" curve is illustrated in phantom while an actual curve is illustrated in solid

According to the ideal curve, there is a first gate voltage Vcl for all load currents greater than the gate current  $I_{c}$  and a second gate voltage  $V_{c}2$ for all load currents less than the gate current I. As illustrated however in the actual curve, there is a rounding of the curve about the gate current value in a progressive decline in the gate voltage with increased negative load current. The actual curve for a given triac is independent of the actual impedance of the load. In order to detect whether the triac 21 is actually conducting load current, one can detect the shift in the level of Vc between positive and negative current. In the event that the gate voltage  $\mathbf{V}_{\mathbf{G}}$  does not change, one knows that the triac 21 is not conducting.

Referring again to Figure 1, one application of the combination I/O module 11 illustrates how it can be used to permit a mechanical input, such as

PCT/US90/05119

5

10

15

20

25

30

35

well as a software input. The input device 17 is coupled between the first line L1 and the terminal 15 and the output device 19 on which one desires to perform the direct output, for example to turn on an indicator light, is coupled between the terminal 15 and the second line L2 when the switch 18 is closed, the indicator light is coupled directly between L1 and L2, bypassing the triac 21. In addition the logic output 29 goes from logic state zero to one on positive half cycles. Thus one can have a positive indication of the status of the switch 18 as well as a software indication thereof.

The combination I/O module 11 can also be used to replace a motor starter circuit which previously would have required three inputs and one output, as illustrated in Figures 6a, b and c. A traditional motor starter circuit is illustrated Figure 6a. The circuit includes a starter switch 51, a stop switch 53, various limit and emergency stop switches generally designated 55, a starter coil  $C_{\text{s}}$  and a As is well known, when the starter relay R<sub>s</sub>. starter switch 51 is closed, assuming the switches 53 and 55 are also closed, current from lines L1 to L2 energizes the starter coil Cs, closing the starter relay Rs, bypassing the starter switch 51. As long as the stop switch 53 and the emergency/ limit switches 55 remain closed, the starter coil C, will remain energized and the starter relay R, will stay closed, thereby providing continuous power to the motor. Typically to automate this function, a minimum of 4 points; three inputs and one output would be required. The three inputs would be from the starter switch 51, the stop switch 53 and the emergency/limit switches 55; and the output would be to the motor (not shown).

As illustrated in Figure 6b, a motor starter circuit utilizing the combination I/O module 11 of the present invention can be performed using a single point. Accordingly, the starter switch 51 is wired between the first line L1 and the terminal 15; the stop switch 53, the emergency/limit switches 55 and the motor are wired in series between the terminal 15 and the second line L2. The triac 21 is illustrated in phantom as extending between L1 and 15 (See Figures 1-3).

5

10

15

20

25

30

35

Software which would be resident in the PLC, to perform the above is illustrated in Figure 6c in ladder diagram form. A rung 61 includes a first relay 63 which is normally open, until continuity between L1 and the terminal 15 is established. The rung 61 further includes a second relay 65 which is open until continuity between the terminal 15 and the second line L2 is detected. A coil 66 represents the status of conduction of the triac 21. Parallel to the first relay 63 is a third relay 67 which is closed upon energization of the coil 66.

Accordingly, when the starter switch 51 closes, the module 11 detects continuity between the first line L1 and the terminal 15. One then measures continuity between the terminal 15 and the second line L2 as discussed above with respect to determining the presence of a load. If continuity is detected between the terminal 15 and the second line L2, this energizes the continuity coil 66, thereby closing the relay 67. The relay 67 will remain closed until continuity between terminal 15 and the second line L2 terminates, such as actuation of the stop switch 53 or the emergency/limit switch 55.

Typically, an input or output module contains more than one point. Accordingly, in the preferred embodiment, the module 11 actually contains 16

points, each of which is operable as an input point, an output point, or both, as illustrated in Figure 7. The logic outputs 29 of the first eight I/O points are coupled via a first multiplexor 71 (LS-244) to a data bus 73. Similarly, the 9th through 16th I/O points are coupled via a second multiplexor 77 (LS-244) to the data bus 73. The output of the reference circuit 33 is connected to an interrupt pin of a PLC, allowing phase detection of the other I/O points.

5

10

15

20

25

30

35

An alternate embodiment of the invention is illustrated in Figure 8. Common reference numerals have been maintained. As with the first embodiment, the input device 17 is coupled between the terminal 15 and the first line L1, and the output device 19 is coupled between the terminal 15 and the second line L2. The logic in signal from the PLC turns on the triac 21 providing power to the output device 19. Further, when the input device 17 is open, the voltage at the logic output 29 is zero, and when the input device 17 is closed the voltage at the logic output 29 is 5.1 volts, a logical 1. As also with the first embodiment, in the second embodiment, the presence or absence of the load 19 when the triac 21 is off is detected by monitoring the phase difference between the phase of the voltage of the second line L2 relative to the first line L1 with the phase of the voltage at point P relative to the first line L1. Further, detection of operation of triac current is performed by monitoring changes in the gate voltage  $V_c$ .

Although explained with respect to an I/O module, it should be understood that the technique for detecting whether a triac is conducting current by monitoring its gate voltage is equally applicable

- 14 -

to any device utilizing a triac, and this aspect of the invention should be accordingly interpreted.

It will be understood that the invention may be embodied in other specific forms without departing from the spirit or central characteristics thereof. The present examples and embodiments, therefore, are to be considered in all respects as illustrative and not restrictive, and the invention is not to be limited to the details given herein.

5

- 15 -

#### CLAIMS

1. A combination input/output module for a microprocessor based device, the combination I/O module comprising:

first and second lines;

means for providing AC power between said first and second lines;

a terminal;

5

10

15

means adapted for coupling an input device between said terminal and said first line, said input device operable between a first conductive state and a second conductive state;

means for determining the conductive state of said input device;

means adapted for coupling an output device between said terminal and said second line; and

means for selectively providing said power to said output device.

- 16 -

2. A combination input/output module for a microprocessor based device, the combination I/O module comprising:

a first line;

a second line;

5

10

15

20

25

30

means for providing AC power between said first line and said second line;

a terminal:

a triac coupled between said terminal and said first line and selectively operable between a conductive state and a non-conductive state;

means adapted for coupling an input device between said terminal and said first line, said input device operable between a first conductive state and a second conductive state;

means for determining the conductive state of said input device;

means adapted for coupling an output device between said terminal and said second line; and

means for selectively switching said triac between said conductive state and said non-conductive state, thereby selectively providing said AC power to said output device.

- 3. The combination input/output module of claim 2 including means for determining a presence or absence of said output device regardless of the conductive state of said triac.

- 4. The combination input/output module of claim 2 including means for determining said conductive state of said triac.

2/6

# INTERNATIONAL SEARCH REPORT

International Application No PCT/US90/05119 1. CLASSIFICATION OF SUBJECT MATTER (if several classification symbols apply, indicate all) 3 According to International Patent Classification (IPC) or to both National Classification and IPC G06F 13/00 IPC(5)364/900 U.S. Cl II. FIELDS SEARCHED Minimum Documentation Searched 4 Classification Symbols Classification System 364/200,900 U.S. Documentation Searched other than Minimum Documentation to the Extent that such Documents are Included in the Fields Searched 5 AUTOMATED PATENT SEARCH (APS): L1: S (IO or I"/O or INPUT"/"OUTPUT OR INPUT "AND" OUTPUT); L2: L1 AND 364/CLAS; L3: L4: L3 AND TERMINAL #; L5: L4 AND ((INPUT OR AND MICROPROCESSOF ((INPUT OR III. DOCUMENTS CONSIDERED TO BE RELEVANT 14 Relevant to Claim No. 19 Citation of Document, 16 with indication, where appropriate, of the relevant passages 17 Category • (CRUICKSHANK ET LA) 1-4 4,951,250 Y,P US,A 21 August 1990 See the entire document. 1-4 03 October 1989 4,872,136 (CIERI ET AL) Y,P US,A See the entire document. 03 June 1986 1-4 (KOCHER ET LA) 4,593,380 Y US,A See the entire document. (CALLAN) 12 March 1985 4,504,927 US,A Y See Column 6, Lines 24-32. "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the investors. \* Special categories of cited documents: 15 "A" document defining the general state of the art which is not considered to be of particular relevance invention "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step earlier document but published on or after the international filing date document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "O" document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family IV. CERTIFICATION Date of Mailing of this International Search Report 2 Date of the Actual Completion of the International Search 2 13 NOVEMBER 1990 International Searching Authority 1 .

BRIAN KLOCK

ISA/US