(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6013777号

(P6013777)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78

622

H01L 29/06 (2006.01)

H01L 29/06

618C

H01L 29/66 (2006.01)

H01L 29/66

601W

H01L 29/78

616V

H01L 29/66

T

請求項の数 15 外国語出願 (全 24 頁)

(21) 出願番号

特願2012-114056 (P2012-114056)

(22) 出願日

平成24年5月18日 (2012.5.18)

(65) 公開番号

特開2013-12723 (P2013-12723A)

(43) 公開日

平成25年1月17日 (2013.1.17)

審査請求日

平成27年4月17日 (2015.4.17)

(31) 優先権主張番号

61/488,934

(32) 優先日

平成23年5月23日 (2011.5.23)

(33) 優先権主張国

米国 (US)

(31) 優先権主張番号

11173950.4

(32) 優先日

平成23年7月14日 (2011.7.14)

(33) 優先権主張国

欧州特許庁 (EP)

(73) 特許権者 591060898

AI M E C

ベルギー、ペーー3001ルーヴァン、カ

ペルドリーフ75番

(73) 特許権者 599098493

カトリーケ・ユニフェルシティ・ルーヴ

アン

K a t h o l i e k e U n i v e r s i

t e i t L e u v e n

ベルギー、ペーー3000ルーヴァン、ワ

ーイストラート6番、ボックス5105、

カーユー・ルーヴァン・アール・アンド・

ディ

最終頁に続く

(54) 【発明の名称】 ライントンネリングトンネル電界効果トランジスタ (T F E T) 及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ドープされたソース領域(30)、ドープされたドレイン領域(22)、及び、ソース領域(30)とドレイン領域(22)との間に位置し、ソース領域(30)とソース・チャネル界面(201)を、ドレイン領域(22)とドレイン・チャネル界面(202)を形成するチャネル領域(21)、を有するソース・チャネル・ドレイン構造と、

ソース領域(30)の少なくとも一部を長手方向(L)に沿って覆うゲート電極(24)であって、チャネル領域(21)及びドレイン領域(22)がゲート電極(24)によって覆われないようにした電極(24)と、

ゲート電極(24)とソース領域(30)との間の長手方向(L)に沿ったゲート誘電体(29)とを備え、

ソース領域(30)は、第1ドーピング型の第1ドーパント元素を用いた、第1ピーク濃度(1021)を有する第1ドーピングプロファイル(1011)でドープされた第1ソースサブ領域(20)と、さらに、第1ドーパント元素と同じ第1ドーピング型を有する第2ドーパント元素を用いた、第2ピーク濃度(1022)を有する第2ドーピングプロファイル(1012)でドープされた、ソース・チャネル界面(201)に近接する第2ソースサブ領域(25)とを含み、

第1ソースサブ領域(20)と第2ソースサブ領域(25)との間で界面(1014)が規定され、

第2ドーピングプロファイル(1012)の第2ピーク濃度(1022)は、第1ソーティング

10

20

スサブ領域(20)と第2ソースサブ領域(25)との間の界面(1014)の位置又は該界面に近接する位置での第1ドーピングプロファイル(1011)の最大ドーピングレベル(1023)より高い、トンネル電界効果トランジスタ(TFET)(100)。

【請求項2】

第1ソースサブ領域(20)と第2ソースサブ領域(25)との間の界面に近接する位置は、該界面の位置、または該界面から第1ソースサブ領域に向かって5nm以下の距離を隔てた位置である、請求項1に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項3】

第2ソースサブ領域(25)は、幅Wによって規定され、

10

該幅Wは、単分子層以上10nm以下の範囲内である、請求項1又は2に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項4】

ソース領域(30)は、ゲート誘電体(29)に隣接する面を有し、

第2ソースサブ領域は、ゲート誘電体に隣接する面から距離Tの場所に位置し、

該距離Tは、0以上10nm以下である、請求項1～3のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項5】

第2ソースサブ領域(25)は、ソース-チャネル界面(201)から距離Dの場所に位置し、

20

該距離Dは、0以上10nm以下である、請求項1～4のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項6】

第2ピーク濃度(1022)は、第1ソースサブ領域(20)と第2ソースサブ領域(25)との間の界面(1014)の位置、又は該界面に近接する位置での第1ドーピングプロファイル(1011)の最大ドーピングレベル(1021)より4倍高い、請求項1～5のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項7】

ゲート電極(24)は、完全にソース領域(30)を覆う、請求項1～6のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

30

【請求項8】

ゲート電極(24)は、該ゲート電極(24)によって覆われないソース領域(30)の長さによって規定されるアンダーラップ(Lunderlap)を残してソース領域(30)を部分的に覆う、請求項1～7のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項9】

前記ソース-チャネル-ドレイン構造は、プレーナ構造であり、

ゲート電極(24)は、該プレーナ型のソース-チャネル-ドレイン構造のソース領域(30)の上部に位置するシングルゲート構造である、請求項1～8のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

40

【請求項10】

前記ソース-チャネル-ドレイン構造は、水平構造であり、

前記ゲート電極(24)は、水平ソース-チャネル-ドレイン構造のソース領域(30)の側壁に位置するダブルゲート構造である、請求項1～9のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

【請求項11】

ソース-チャネル-ドレイン構造は、水平構造又は垂直方向であり、

ゲート電極(24)は、水平型又は垂直型のソース-チャネル-ドレイン構造のソース領域(30)周囲のオールアラウンド型ゲート構造である、請求項1～10のいずれか1項に記載のトンネル電界効果トランジスタ(TFET)(100)。

50

## 【請求項 1 2】

T F E T は、ナノワイヤ T F E T であり、

ナノワイヤは、少なくとも T F E T のチャネル (21) を形成し、

ゲート電極 (24) は、オールアラウンド型ゲート構造である、請求項 1 ~ 11 のいずれか 1 項に記載のトンネル電界効果トランジスタ (T F E T) (100)。

## 【請求項 1 3】

半導体基板を準備する工程と、

前記基板上にドレイン半導体材料で作成されたドレイン領域 (22) を設ける工程と、

低ドープ又はアンドープ半導体材料で作成されたチャネル領域 (21) であって、前記ドレイン領域 (22) と接触してドレイン領域 (22) と該チャネル領域 (21) との間にドレイン - チャネル界面 (202) を形成するようにした領域 (21) を設ける工程と、

ソース半導体材料で作成されたソース領域 (30) であって、前記チャネル領域 (21) と接触して該ソース領域 (30) とチャネル領域 (21) との間にソース - チャネル界面 (201) を形成するようにした領域 (30) を設ける工程と、

ソース領域 (30) の少なくとも一部を長手方向に沿って覆うゲート電極 (24) を設ける工程であって、チャネル領域 (21) 及びドレイン領域 (22) が該ゲート電極 (24) によって覆われないようにする工程と、

ゲート電極 (24) と、ソース領域 (30) の覆われた部分との間にゲート誘電体 (29) を設ける工程と、

ソース領域 (30) 及びドレイン領域 (22) をドープする工程であって、ソース領域 (30) をドープすることは、第 1 ドーピング型を有する第 1 ドーパント元素を用いた、第 1 ピーク濃度 (1021) を有する第 1 ドーピングプロファイルで第 1 ソースサブ領域 (20) をドープすることと、第 1 ドーピング型と同じ第 2 ドーピング型を有する第 2 ドーパントを用いた、第 1 ソースサブ領域 (20) と第 2 ソースサブ領域 (25) との間の界面 (1014) に近接する位置での第 1 ドーピングプロファイル (1011) の最大ドーピングレベル (1023) より高い第 2 ピーク濃度 (1022) を有する第 2 ドーピングプロファイルで、ソース - チャネル界面 (201) に近接する第 2 ソースサブ領域をドープすることとを含むような工程とを含む、トンネル電界効果トランジスタ (T F E T) (100) の製造方法 (300)。

## 【請求項 1 4】

第 2 ピーク濃度 (1022) は、第 1 ソースサブ領域 (20) と第 2 ソースサブ領域 (25) との間の界面 (1014) に近接する位置での第 1 ドーピングプロファイルの最大ドーピングレベル (1023) より 4 倍高い、請求項 13 に記載の方法 (300)。

## 【請求項 1 5】

トンネル電界効果トランジスタは、N W - T F E T 半導体デバイスであり、

ソース - チャネル - ドレイン構造を設けることは、半導体材料で作成されたナノワイヤ構造を成長させることを含む、請求項 13 または 14 に記載の方法 (300)。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体デバイス及びナノテクノロジーの分野に関する。特に、本発明は、トンネル効果がバンド間 (band to band) トンネリングをベースとするトンネル電界効果トランジスタ (T F E T) に関する。

## 【0002】

さらに、本発明は、半導体デバイスの製造方法、特にトンネル電界効果トランジスタの製造方法に関する。さらに、該製造方法は、標準のプレーナ技術に制限されず、ダブルゲート技術、F I N F E T 技術及びナノテクノロジーに関する。これは、集積ナノワイヤを用いた実装を含む。

## 【背景技術】

10

20

30

40

50

## 【0003】

通常、ナノ電子デバイスは、半導体基板上に集積回路として製造される。相補型金属酸化膜半導体(CMOS)電界効果トランジスタは、集積回路の中核的なエレメントの1つである。CMOSトランジスタの寸法及び動作電圧は、集積回路のより高い性能及びパッケージ密度を得るべく、継続的に低減し、或いは小型化している。

## 【0004】

CMOSトランジスタの小型化に起因する問題の1つは、電力消費が増加し続けているということである。これは、一部には、リーク電流が増加している(例えば、短チャネル効果に起因して)こと、また、電源電圧を小さくするのが難しいこと、が原因である。これは、サブスレッショルドスイング(subthreshold swing)が最低限の約60mV/decadeに制限され、その結果、トランジスタをオンからオフへスイッチングすることが特定の電圧変化、したがって最小電源電圧を必要とする、という事実に主に起因する。

10

## 【0005】

一般に、トンネル電界効果トランジスタ(TFET)は、短チャネル効果が存在せず、生じるオフ電流が小さいので、金属酸化膜半導体電界効果トランジスタ(MOSFET)の後継として公表されている。TFETのもう1つの利点は、サブスレッショルドスイングを、従来のMOSFETの物理的限界である60mV/decadeより小さくすることができ、したがって低電源電圧を使用することができる可能性がある、ということである。しかしながら、通常、すべてのシリコンTFETが、小さいオン電流の問題を抱えている。これは、トンネル障壁の大きい抵抗に関する欠点である。

20

## 【0006】

過去には、TFETの製造を向上させるためにさまざまな試みがなされてきた。

## 【0007】

例えば、論文(Jhaveri et al. "Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor", IEEE Transactions on Electronic Devices Vol. 58, 1 (Jan. 2011))で、オン電流及びサブスレッショルドスロープ(subthreshold slope)を向上させるためのソースポケットTFETが提案されている。nTFETの場合、p+型ソースにおいて、n+ポケットがゲート(真正チャネル領域のみの上方に存在するゲート)の下に埋め込まれる。かかるトンネル接合は、p+領域と、ゲート下の狭い完全空乏ポケットn+領域との間に形成される。また、p+領域及びn+領域は、電子をチャネルに供給する。完全空乏n+ポケット層は、トンネル幅を減少させ、電界を増加させる。これは、トンネル接合を超えて電位降下を低減し、それゆえデバイス性能を向上させる。

30

## 【0008】

別の可能なTFETの構成は、論文(Vandenbergh et al. in "Analytical model for a tunnel field-effect transistor", published IEEE Mediterranean, Electrotechnical Conference 2008, MELECON 2008.)に公開されている。そこで、ソースの充分上側にゲートが位置する新しいTFETの構成が提案されている。ゲートは、TFETデバイスのチャネル領域を覆わない。かかるバンド間トンネリング(BTT)は、ゲートに直交する方向に発生し、ライントンネリング(line tunneling)と呼ばれる。一方、従来のTFETでは、BTTトンネリングはチャネル領域を経由して発生し、ポイントトンネリング(point tunneling)と呼ばれる。

40

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0009】

さらに改善したTFET設計に対するニーズが依然として存在する。

## 【0010】

本発明の特定の実施形態の目的は、改善した性能を有し、それゆえ、印加するゲートソース電圧 $V_{GS}$ での、ドレイン-ソース電圧の変化に起因するドレイン-ソース電流 $I_D$ のシフトを削除し、或いは少なくとも大幅に低下させるトンネル電界効果トランジスタ

50

(T F E T) を提供することである。

【0011】

本発明の特定の実施形態の目的は、優れたデバイス特性を有するトンネル電界効果トランジスタ (T F E T) 、特に、例えば優れた  $I_{D S} - V_{G S}$  特性、即ち  $60 \text{ mV} / \text{dec}$  未満のサブスレッショルドスイシングを有する、T F E T の製造方法を提供することである。

【課題を解決するための手段】

【0012】

上記の目的は、本発明の実施形態によるデバイス及び方法によって達成される。

【0013】

本発明の特定の且つ好ましい態様は、添付する独立請求項及び従属請求項において詳説する。従属請求項からの特徴は、独立請求項の特徴及び他の従属請求項の特徴と、適切に且つ単に請求項に明記されただけでないものとして組み合わせてもよい。

【0014】

第1の態様で、本発明の実施形態は、ソース - チャネル - ドレイン構造、ゲート電極及びゲート誘電体とを備えたトンネル電界効果トランジスタ (T F E T) を開示する。ソース - チャネル - ドレイン構造は、少なくとも1つのドープされたソース領域と、少なくとも1つのドープされたドレイン領域と、ソース領域とソース - チャネル界面を、ドレイン領域とドレイン - チャネル界面を形成するようにソース領域とドレイン領域との間に位置する、少なくとも1つのチャネル領域とを有する。ソース領域は、第1ドーピング型のドーパント元素を用いた、第1ピーク濃度を有する第1ドーピングプロファイルでドープされた第1ソースサブ領域を含む。さらに、ソース領域は、ソース - チャネル界面に近接し、該界面から0以上5nm以下の位置に境界を有する第2ソースサブ領域を含む。第2ソースサブ領域は、第1ドーパント元素と同じドーピング型を有する第2ドーパント元素を用い、第2ピーク濃度を有する第2ドーピングプロファイルでドープされる。第1ソースサブ領域と第2ソースサブ領域との間の界面が規定され、第2ドーピングプロファイルの第2ピーク濃度は、第1ソースサブ領域と第2ソースサブ領域との間の、界面の位置又は該界面に近接する位置（例えば界面から第1ソースサブ領域に向かって最大5nmの距離の位置）での第1ドーピングプロファイルの最大ドーピングレベルより充分高い。第1ドーピングプロファイルを有するソースサブ領域と第2ドーピングプロファイルを有するソースサブ領域との間の界面は、第1ドーピングプロファイルと第2ドーピングプロファイルとが同じドーピングレベルを有するソース領域での面位置又は深さ位置として規定される。

【0015】

ゲート電極は、チャネル領域及びドレイン領域が該ゲート電極に覆われないように、ソース領域の少なくとも一部を長手方向に沿って覆う。

【0016】

ゲート誘電体は、ゲート電極とソース領域との間で、その長手方向に延在している。

【0017】

第2ソースサブ領域はまた、ソース領域のポケット領域と呼ぶこともできる。

【0018】

本発明の実施形態によれば、第1ソースサブ領域と第2ソースサブ領域との間の界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルは、界面から第1ソースサブ領域に向かって最大5nmの距離での第1ドーピングプロファイルの最大ドーピングレベルである。

【0019】

本発明の実施形態によれば、第1ソースサブ領域と第2ソースサブ領域との間の界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルは、第1ソースサブ領域と第2ソースサブ領域との間の界面での第1ドーピングプロファイルのドーピングレベルである。

10

20

30

40

50

## 【0020】

本発明の実施形態によれば、第1ドーパント元素のドーピング元素と第2ドーパント元素のドーピング元素とは同じでもよい。n-T E F Tの場合、第1ドーパント元素及び/又は第2ドーパント元素は、好ましくは、ボロン(B)、アルミニウム(A1)を含む群から選択することができる。p-T E F Tの場合、第1ドーパント元素及び/又は第2ドーパント元素は、好ましくは、リン(Ph)、ヒ素(As)、アンチモン(Sb)を含む群から選択することができる。

## 【0021】

本発明の実施形態によれば、T F E Tのソース領域、即ち第1ソースサブ領域及び第2ソースサブ領域は、p型ドープ又はn型ドープされた半導体材料で作成されてもよい。

10

## 【0022】

本発明の実施形態によれば、T F E Tのドレイン領域は、p型ドープ又はn型ドープされた半導体材料で作成されてもよい。

## 【0023】

第2ソースサブ領域を構成する半導体材料は、好ましくは、第1ソースサブ領域を構成する材料と同じ半導体材料である。

## 【0024】

本発明の実施形態によれば、第2ソースサブ領域は、幅Wによって規定され、該第2ソースサブ領域の幅Wは、好ましくは単分子層以上10nm以下の範囲にある。第2ソースサブ領域の幅Wは、さらに好ましくは2nm以上6nm以下の範囲にある。第2ソースサブ領域の幅Wは、第2ドーピングプロファイルの幅によって規定されてもよい。例えば、第2ドーピングプロファイルがガウシアンプロファイルである場合、幅Wは、ガウシアンプロファイルの半値全幅(F W H M)によって規定されてもよい。

20

## 【0025】

ソース領域は、ゲート誘電体に隣接する面を有する。本発明の実施形態によれば、第2ソースサブ領域は、ゲート誘電体に隣接する面から距離Tを隔てた場所に位置し、該距離Tは長手方向に垂直に測定され、該距離Tは好ましくは0以上10nm以下であり、例えば0以上5nm以下である。

## 【0026】

本発明の実施形態によれば、第2ソースサブ領域、例えばソース-チャネル界面に最近接した第2ソースサブ領域のエッジは、ソース-チャネル界面から距離Dのところに位置し、該距離Dは好ましくは0以上10nm以下であり、例えば0以上5nm以下である。

30

## 【0027】

ドーピングプロファイルは、ピーカドーピング濃度によって規定され、また、ドーピング傾度又はドーピング勾配によって規定されてもよい。

## 【0028】

T F E T内の第1ソースサブ領域の第1ソースピーク濃度は、 $10^{18} / \text{cm}^3$ 以上 $10^{21} / \text{cm}^3$ 以下でもよく、例えば第1ソースサブ領域のピーカドーピング濃度(即ち、第1ドーピングレベル)は、 $10^{19} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下でもよい。

40

## 【0029】

T F E T内のドレイン領域のドレインピーク濃度は、 $10^{17} / \text{cm}^3$ 以上 $10^{21} / \text{cm}^3$ 以下でもよい。

## 【0030】

第2ドーピングプロファイルは、第2ピーカドーピング濃度によって規定されてもよい。第2ドーピングプロファイルについての最適ピーカ濃度は、さまざまなパラメータ、例えば第2ソースサブ領域の第2ドーピングプロファイルの形状(即ち、幅W、距離D及び距離W)、第2ソースサブ領域のドーピング元素、第1ソースサブ領域の第1ドーピングプロファイル(即ち、第1ピーカドーピング濃度、第1ドーピング元素及びソース-チャネル界面に向かっての第1ドーピング勾配)、T F E Tデバイスの所望のオン電流等に依

50

存する。

【0031】

実施形態によれば、第2ピーク濃度は、第1ソースサブ領域と第2ソースサブ領域との間の界面の位置で、又は該界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルより4倍高い。

【0032】

本発明の実施形態によれば、TFT内のチャネル領域は、アンドープ又は低度にドープされた(nドープ又はpドープされた)半導体材料で作成され、ソース領域とドレイン領域との間に位置してもよい。

【0033】

TFT内のチャネル領域のドーピングレベルは、アンドープ状態から最大 $10^{17}/cm^3$ の範囲でもよく、例えばチャネル領域のドーピングレベルは、アンドープ状態から最大 $5 \times 10^{15}/cm^3$ の範囲でもよい。

10

【0034】

本発明の実施形態によるTFTでは、全体的な半導体材料、即ち(第1及び第2)ソースサブ領域、チャネル領域及びドレイン領域を形成する材料は、Si、Ge、CのようなIV族材料及びその二元化合物、並びに、In、Ga、As、Sb、Al、P、B、NのようなIII/V族材料及びその二元化合物、三元化合物及び四元化合物、並びに、Cd、Zn、S、Se、Te、OのようなII/VI族材料及びその二元化合物、三元化合物及び四元化合物、並びにカーボンナノチューブの少なくとも1つから選択されてもよい。

20

【0035】

本発明の実施形態によれば、ゲート電極は、部分的に又は完全にソース領域を覆ってもよい。ソース領域を部分的にのみ覆うゲート電極についてさまざまな実施例が可能である。実施形態によれば、ゲート電極に覆われないソース領域の長さとして規定されるアンダーラップUnderlapが存在してもよい。このアンダーラップUnderlapは、ゲート電極の片側又は両側に存在してもよい。つまり、ソース-チャネル界面側での第1アンダーラップ及び/又はソース-電極側での第2アンダーラップが存在してもよい。

【0036】

30

本発明の実施形態によれば、ゲート電極材料は、導電性材料で作成されてもよい。ゲート電極材料は、ポリシリコン、ポリゲルマニウム、Al、W、Ta、Ti、Ru、Pd、Rh、Re、Ptのような金属及びこれらの合金、TaN及びTiNのような金属窒化物、TaSiNのような金属シリコン窒化物、RuO<sub>2</sub>及びReO<sub>3</sub>のような導電性酸化物、CoSi<sub>2</sub>、NiSi及びTiSi<sub>2</sub>のようなFUSI(fully silicided metal)、FUGE(fully germanided metal)の少なくとも1つから選択された材料でもよい。ゲート電極材料は、特定のゲート仕事関数が得られるように選択してもよい。

【0037】

本発明の実施形態によるTFTは、さらに第1ソースサブ領域及びドレイン領域への電気的コンタクトを含んでもよい。第1ソースサブ領域上及びドレイン領域上の電気的コンタクトは、シリサイド含有構造(NiSi、CoSi<sub>2</sub>、TiSi<sub>2</sub>等)、ゲルマニド含有構造、金属含有構造、ポリシリコン又はこれらの組み合わせの少なくとも1つから選択された導電性材料でもよい。前記ソース領域上及びドレイン領域上の電気的コンタクトは、金属とシリサイドとの化合物でもよい。

40

【0038】

本発明の特定の実施形態によれば、ソース-チャネル-ドレイン構造は、プレーナ構造でもよい。これらの実施形態では、TFT内のゲート電極は、プレーナ型ソース-チャネル-ドレイン構造のソース領域の上部に位置するシングルゲート構造でもよい。

【0039】

本発明の別の実施形態によれば、ソース-チャネル-ドレイン構造は、水平構造、即ち

50

、基板平面内に横たわる構造でもよい。また、ゲート電極は、前記水平ソース - チャネル - ドレイン構造のソース領域の側壁に位置するダブルゲート構造でもよい。

【0040】

本発明の別の実施形態によれば、T F E Tは、トリプルゲートF E T（例えばF i n F E T）でもよい。これらの実施形態では、ゲート電極は、トリプルゲートF E Tのソース - チャネル - ドレイン構造のソース領域の側壁及び上部に位置するトリプルゲート構造でもよい。

【0041】

本発明のさらに別の実施形態によれば、ソース - チャネル - ドレイン構造は、水平構造又は垂直構造でもよい。これらの実施形態では、ゲート電極は、水平又は垂直ソース - チャネル - ドレイン構造のソース周囲のオールアラウンド型ゲート構造でもよい。

10

【0042】

本発明の実施形態によれば、T F E Tは、ナノワイヤを備えてもよく、これはN W - T F E Tとも呼ばれる。長手軸に直交するナノワイヤの直径は、1 nm以上500 nm以下でもよく、例えばナノワイヤの直径は、2 nm以上200 nm以下でもよい。使用する長手軸に沿ったナノワイヤの長さは、5 nm以上50 μm以下でもよく、例えば本発明のT F E T内で使用するナノワイヤの長さは、10 nm以上1 μm以下でもよい。

【0043】

本発明の実施形態によれば、T F E Tは、ヘテロ部分(heterosection)又はヘテロ構造を有するN W - T F E Tでもよい。ヘテロ部分又はヘテロ構造の長さは、1 nm以上50 nm以下でもよく、例えばヘテロ部分の長さは2 nm以上10 nm以下でもよい。本発明のT F E Tのヘテロ部分のドーピングレベルは、 $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下でもよく、例えばヘテロ部分のドーピングレベルは $1 \times 10^{19} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下でもよい。ヘテロ部分又はヘテロ構造は、第2ソースサブ領域を含む。

20

【0044】

第2の態様で、本発明の実施形態は、トンネル電界効果トランジスタ（T F E T）の製造方法を開示する。該方法は、半導体基板上に、ドレイン領域、ソース領域及びチャネル領域を設けることを含む。ドレイン領域は、ドレイン半導体材料で作成される。チャネル領域は、低度にドープされた、又はアンドープのチャネル半導体材料で作成され、前記ドレイン領域と接触し、ドレイン領域とチャネル領域との間にドレイン - チャネル界面を形成する。ソース領域は、ソース半導体材料で作成され、チャネル領域と接触し、ソース領域とチャネル領域との間にソース - チャネル界面を形成する。該方法はさらに、ソース領域の少なくとも一部を長手方向に沿って覆うゲート電極を設けることを含み、チャネル領域及びドレイン領域が該ゲート電極に覆われないようにする。該方法はさらに、ゲート電極とソース領域の覆われる部分との間にゲート誘電体を設けることを含む。該方法はさらに、ソース領域及びドレイン領域をドープすることを含む。ソース領域をドープすることは、第1ソースサブ領域と呼ばれるソース領域の第1領域を、第1ドーピング型を有する第1ドーパント元素を用いて、第1ピーク濃度を有する第1ドーピングプロファイルでドープすることと、ソース - チャネル界面に近接する、第2ソ - スサブ領域とも呼ばれるソース領域の第2領域を、第1ドーピング型と同じドーピング型を有する第2ドーパント元素で、第1ソースサブ領域と第2ソースサブ領域との間の界面の位置又は該界面に近接する位置での最大ドーピングレベルより充分高い第2ピーク濃度を有する第2ドーピングプロファイルでドープすることとを含む。

30

【0045】

ドレイン領域は、ソース領域、即ち、第1，第2ソースサブ領域それぞれの第1，第2ドーピング型に対して反対のドーピング型を有するドーパント元素でドープする。

40

【0046】

第1ソースサブ領域及びドレイン領域は、所定のドーピングレベル（所定の第1ピーク濃度）まで所定のドーパント型に選択的にドープする。例えば、第1ソースサブ領域をp

50

型領域にドープして、ドレイン領域をn型領域にドープしてもよく、或いはその逆でもよい。

【0047】

本発明の実施形態によれば、第1ドーパント元素のドーピング元素及び第2ドーパント元素のドーピング元素は、同じでもよい。n-TFETの場合には、好ましくは、第1ドーパント元素及び/又は第2ドーパント元素はホウ素(B)、アルミニウム(Al)を含む群のいずれかから選択することができる。p-TFETの場合には、好ましくは、第1ドーパント元素及び/又は第2ドーパント元素は、リン(Ph)、ヒ素(As)、アンチモン(Sb)を含む群から選択することができる。

【0048】

本発明の実施形態によれば、TFETのソース領域、即ち第1及び第2ソースサブ領域は、p型又はn型ドープした半導体材料で作成してもよい。

【0049】

本発明の実施形態によれば、TFETのドレイン領域は、p型又はn型ドープした半導体材料で作成してもよい。

【0050】

好ましくは、第2ソースサブ領域の半導体材料は、第1ソースサブ領域の半導体材料と同じ半導体材料である。

【0051】

TFET内の第1ソースサブ領域の第1ソースピーク濃度は、 $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下でもよく、例えば第1ソースサブ領域のピークドーピング濃度(即ち第1ドーピングレベル)は、 $1 \times 10^{19} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下でもよい。

【0052】

TFET内のドレイン領域のドレインピーク濃度は、 $10^{17} / \text{cm}^3$ 以上 $10^{21} / \text{cm}^3$ 以下でもよい。

【0053】

本発明の実施形態によれば、TFET内のチャネル領域は、アンドープ又は低度にドープした(n又はpドープした)半導体材料で作成してもよく、ソース領域とドレイン領域との間に位置してもよい。TFET内のチャネル領域のドーピングレベルは、アンドープ状態から最大 $10^{17} / \text{cm}^3$ の範囲内でもよく、例えばチャネル領域のドーピングレベルは、アンドープ状態から最大 $5 \times 10^{15} / \text{cm}^3$ の範囲内でもよい。

【0054】

第2ソースサブ領域はまた、ポケット領域と呼んでもよい。第2の発明の態様の実施形態によれば、第2ソースサブ領域(ポケット領域)の第2ピーク濃度は、第1ピークドーピングプロファイルと第2ピークドーピングプロファイルとの間の界面の位置又は該界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルより4倍高い必要がある。

【0055】

本発明の実施形態によれば、ソースコンタクト及びドレインコンタクトを設けてもよい。

【0056】

さらに、ナノワイヤTFET(NW-TFET)半導体デバイスの製造方法を開示している。前記方法は、選択的に触媒を堆積し、基板に少なくとも1つのドレインコンタクトを設ける工程と、半導体材料で作成されるナノワイヤ構造を成長させる工程と、ソースサブ領域の第1サブ領域を所望の第1ドーピングレベルまで、第1ドーパント型で選択的にドープする工程と、ソース-チャネル界面に近接するソース領域の第2サブ領域(第1領域とは異なる)を、第1ドーパント元素と同じドーピング型を有する第2ドーパント元素で、第1ドーピングプロファイルと第2ドーピングプロファイルとの間の界面の位置又は該界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルより充分

10

20

30

40

50

に高い第2ピーク濃度でドープする工程と、任意に(選択的に)チャネル領域をドープする工程と、ナノワイヤのソース領域の側壁の少なくとも一部にゲート誘電体(例えば酸化物)を堆積する工程と、ゲート誘電体(例えば酸化物)の上部にゲート電極を堆積する工程と、ナノワイヤのソース領域の上部にソースコンタクトを形成する工程とを含み、前記ゲート電極は、前記ゲート誘電体を超えて広がらないように前記ゲート誘電体上に位置し、ゲート電極は、チャネル領域及びドレイン領域が該ゲート電極によって覆われないように、ソース-チャネル-ドレイン構造の少なくとも1つのソース領域の少なくとも一部を長手方向に沿って覆う。

【0057】

トンネル電界効果トランジスタデバイスに応用する場合、NW-TFET内のナノワイヤは、トンネル電界効果トランジスタのチャネルを形成してもよく、また、ソース領域及びドレイン領域を形成することができる可能性がある。或いは、トンネル電界効果トランジスタのソース領域及びドレイン領域のどちらかは、基板内に位置する。前記基板は、ソース領域及びドレイン領域として機能する高ドープ領域を含む。

10

【0058】

本発明の実施形態のTFETの概念、並びに本発明の他の特性、特徴及び利点は、プレーナTFET、ダブルゲートTFET、トリゲートTFET(FinFET等)及びオールアラウンドTFETを含むがこれらに限定されず、また、全水平及び全垂直TFETの実装を含むがこれらに限定されず、さらに、バルクコンタクトを含むものと含まないものの両方を含む、すべての種類のTFETの実装に適用可能である。

20

【0059】

本発明の実施形態のTFETの概念、並びに本発明の他の特性、特徴及び利点はさらに、p型チャネルドーピング、n型チャネルドーピング及び真正ドーピングを含むチャネルドーピングに依存しないすべてのTFETに適用可能である。

【0060】

本発明の実施形態のTFETの概念、並びに本発明の他の特性、特徴及び利点はさらに、チャネル材料とは異なるソース材料及び/又はドレイン材料とは異なるソース材料を有するTFETを含み、また、チャネル材料とは異なるドレイン材料を有するTFETを含む、ソース材料、チャネル材料及びドレイン材料として使用される半導体材料に依存しないすべてのTFETの実装に適用可能である。可能な半導体材料は、Si、Ge、CのようなIV族材料若しくはその二元化合物、又は、In、Ga、As、Sb、Al、P、B、NのようなIII/V族材料若しくはその二元化合物、三元化合物若しくは四元化合物、又は、Cd、Zn、S、Se、Te、OのようなII/VI族材料若しくはその二元化合物、三元化合物若しくは四元化合物、又は、カーボンナノチューブを含むが、これらに限定されない。

30

【0061】

本発明の実施形態のTFETの概念、並びに本発明の他の特性、特徴及び利点はさらに、ゲート誘電体の材料及び厚さに依存しないすべてのTFETの実装に適用可能である。可能な誘電体材料は、シリコンベースの酸化物(例えば二酸化ケイ素、酸窒化ケイ素)、酸化アルミニウム、hig - k酸化物(Hf、Ta、Ti、Nb、V、Y、Zrのような遷移金属の酸化物、窒化酸化物、ケイ酸塩及び窒化ケイ酸塩)を含むが、これらに限定されない。

40

【0062】

本発明の上記の、及び、他の特性、特徴及び利点は、例によって本発明の原理を説明する添付の図面と関連して、以下の詳細な説明から明らかとなるであろう。この説明は、本発明の技術的範囲を制限することなく、単なる例として与えられる。以下で引用される参照符号は、添付の図面を参照する。

【0063】

特定の発明の態様によるTFETデバイスについて達成される高い性能は、先行技術と比較した場合の利点である。

50

## 【0064】

特に本発明の実施形態による小さいゲート誘電体厚さ（即ち、小さい等価酸化膜厚EOT）を有する半導体デバイスの場合に、ソース-ドレイン電圧V<sub>DS</sub>を変化させたときの開始電圧V<sub>onset</sub>（即ち、BTBTトンネリングが発生する位置でのゲート電圧）の広がりを大きく低減できることは、本発明の利点である。

## 【0065】

本発明及び先行技術に対して達成される利点を要約する目的で、本発明の特定の目的及び利点を本明細書で上記の通り説明した。もちろん、かかる目的又は利点のすべてを、本発明の特定の実施形態によって達成することができるわけではないと理解すべきである。したがって、例えば、当業者は、本明細書で教示又は提示される他の目的又は利点を必ずしも達成することなく、本明細書で教示される利点を達成又は最適化する方法で具現又は実行することができると認識するであろう。

10

## 【0066】

本発明の上記の態様又は他の態様は、以下で説明する実施形態から明らかとなり、実施形態を参照して明瞭になるであろう。

## 【図面の簡単な説明】

## 【0067】

本発明は、添付の図面を参照して、例によってさらに説明することになる。すべての図は、本発明のいくつかの態様及び特定の実施形態を説明することを意図している。図は、明確性のために、簡略化した方法で描いている。すべての代替及び選択肢が示されているわけではなく、それゆえ、本発明の技術的範囲は与えられた図面の内容に限定されない。同様に、異なる図面で同様の部分を参照するために、数字が用いられている。

20

## 【0068】

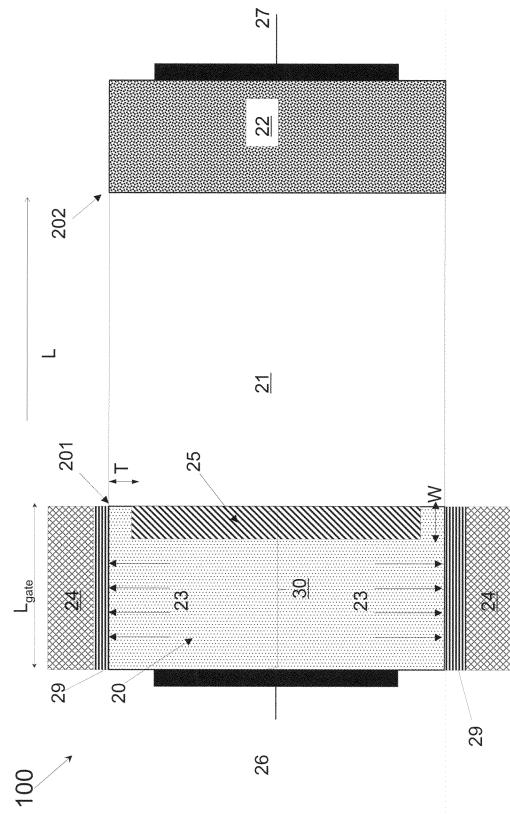

【図1】本発明の実施形態によるTFT構造の断面の概略図を示しており、ゲートはソース領域上にのみ存在してTFT構造のソース領域を完全に覆い、ポケット領域はソース-チャネル界面に隣接するソース領域に存在する。4つの平行な矢印は、ゲート電極と直交する方向で発生する支配的なトンネル現象の方向を示している。

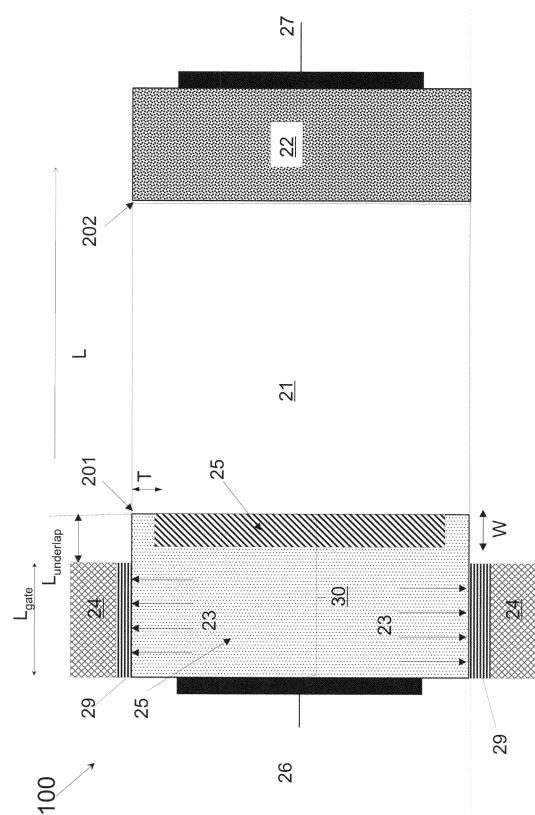

【図2】本発明の実施形態によるTFT構造の断面の概略図を示しており、ゲートはソース領域上にのみ存在し、ゲートとソース-チャネル界面との間のアンダーラップUnderlapでTFT構造のソース領域を部分的にのみ覆う。また、ポケット領域が、ソース-チャネル界面に隣接するソース領域に存在する。4つの平行な矢印は、ゲート電極と直交する方向で発生する支配的なトンネル効果の方向を示している。

30

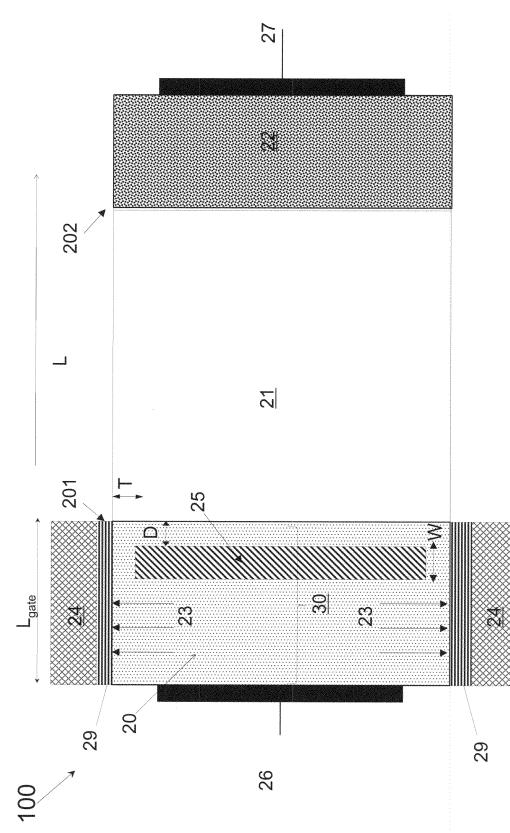

【図3】本発明の実施形態によるTFT構造の断面の概略図を示しており、ゲートはソース領域上にのみ存在してTFT構造のソース領域を完全に覆い、ポケット領域はソース-チャネル界面に近接し、ソース-チャネル界面から距離Dの場所に位置するソース領域に存在する。3つの平行な矢印は、ゲート電極と直交する方向で発生する支配的なトンネル効果の方向を示している。

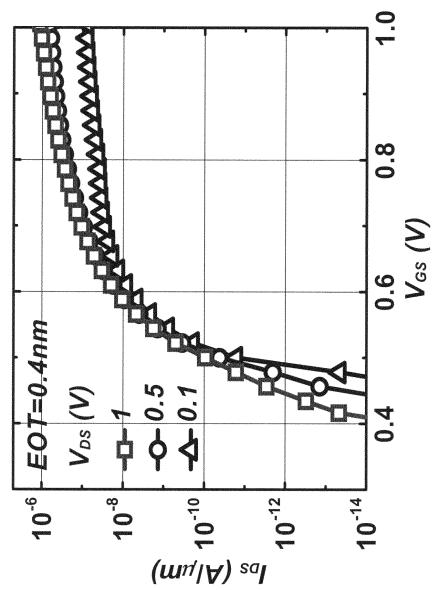

【図4】ソース領域で第2ソース（ポケット）領域を有さず、ソース領域上にのみ存在するゲート（したがって、チャネル領域及び/又はドレイン領域上に存在しない）を有するTFT構造についてシミュレーションした出力特性を示す。

40

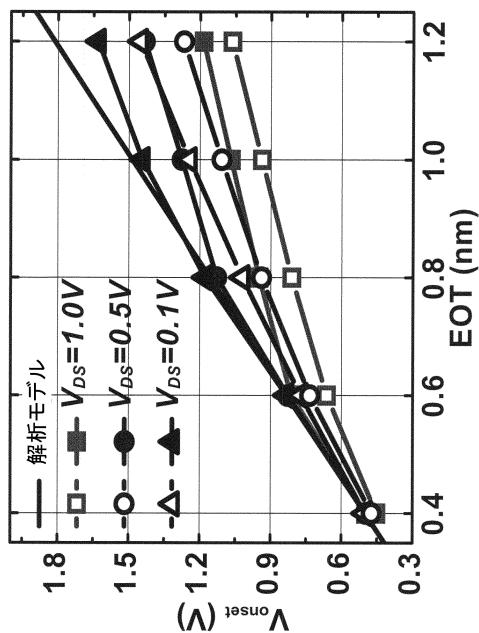

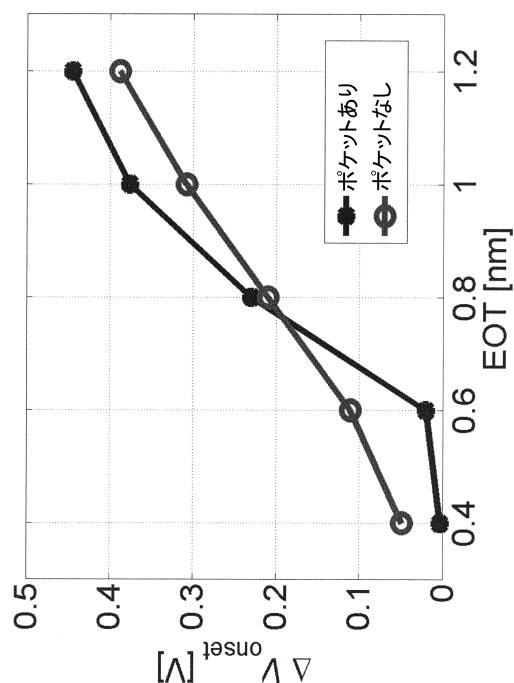

【図5】本発明の実施形態による第2（ポケット）ソースサブ領域を有するTFT構造（黒記号）及び第2（ポケット）ソースサブ領域を有しないTFT構造（白記号）についてシミュレーションした入力特性を示す。

【図6】本発明の実施形態による第2（ポケット）ソースサブ領域を有するTFT構造（黒記号）及び第2（ポケット）ソースサブ領域を有しないTFT構造（白記号）についてシミュレーションした入力特性を示す。

【図7】従来のTFT構造の断面図を示しており、ゲートはチャネル領域と重なり合っている。これは、ソース及び/又はドレイン領域と小さな重なり合いを含む（不図示）可能性がある。矢印は、ポイント間(point-to-point)トンネリングと呼ばれる、支配的なトンネル効果の方向を示す。

50

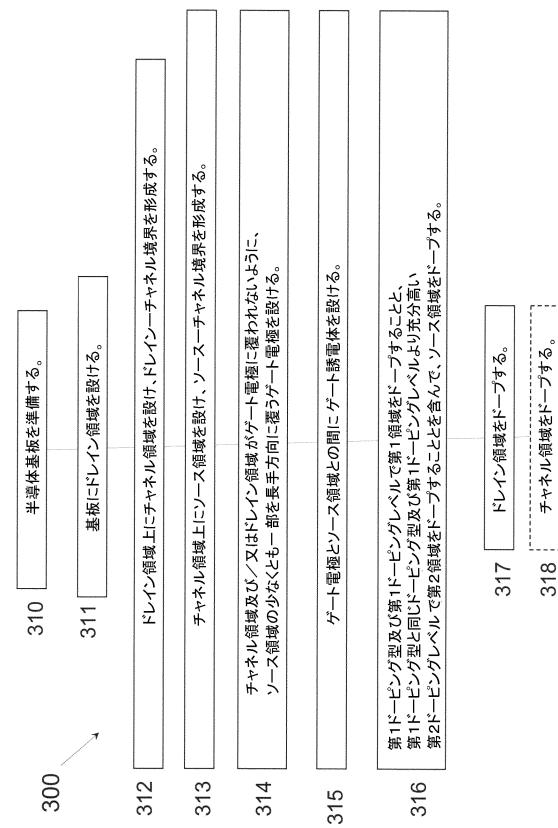

【図8】本発明の第2の態様による、TFT構造の製造方法についてのフローチャートを示す。

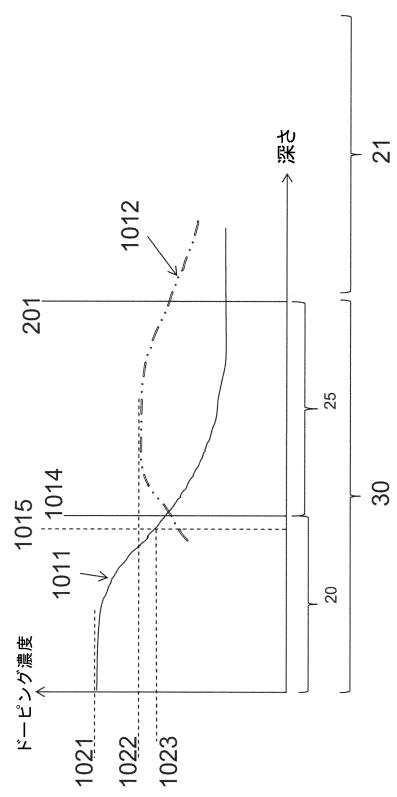

【図9】第1ソースサブ領域の急峻な第1ドーピングプロファイル及び急峻でない第1ドーピングプロファイルそれぞれの場合で、本発明の実施形態による第1ソースサブ領域及び第2ソースサブ領域についてのドーピングプロファイル曲線の概略を深さの関数で示す。

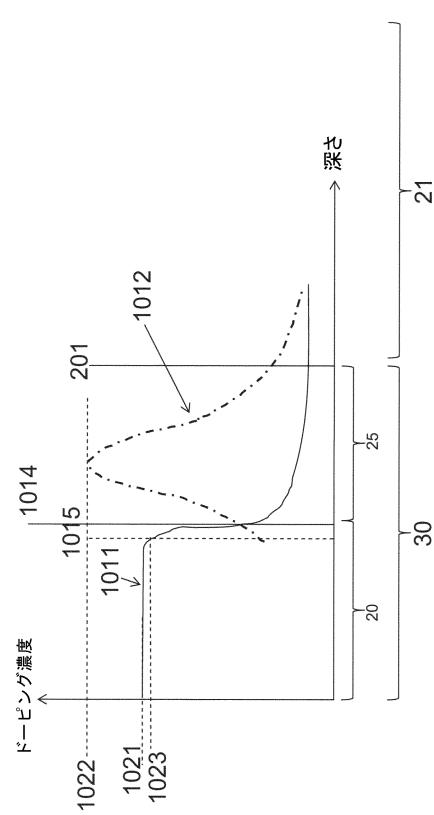

【図10】第1ソースサブ領域の急峻な第1ドーピングプロファイル及び急峻でない第1ドーピングプロファイルそれぞれの場合で、本発明の実施形態による第1ソースサブ領域及び第2ソースサブ領域についてのドーピングプロファイル曲線の概略を深さの関数で示す。

10

#### 【発明を実施するための形態】

##### 【0069】

本発明は、特定の実施形態について特定の図面を参照しながら説明するが、本発明はこれらに限定されず、請求項によってのみ限定される。記載した図面は概略的なものに過ぎず、限定的でない。図面において、いくつかのエレメントのサイズは、説明目的のため誇張し、スケールどおり描いていないことがある。寸法及び相対寸法は、本発明の実際の実施化と対応していない。

##### 【0070】

さらに、説明及び請求項での用語「上(top)」等は、説明目的で使用しており、必ずしも相対的な位置を記述するためのものでない。こうして用いた用語は、好適な状況下で交換可能であって、本明細書で説明した特定の実施形態が本明細書で説明又は図示した以外の他の向きで動作可能であると理解すべきである。

20

##### 【0071】

請求項で使用する用語「備える、有する、含む(comprising)」は、それ以降に列挙された手段に限定されるものと解釈すべきでなく、他のエレメント又は工程を除外していない。記述した特徴、整数、工程又はコンポーネントの存在を、参照したように特定するよう解釈する必要があるが、1つ以上の他の特徴、整数、工程又はコンポーネント、或いはこれらのグループの存在又は追加を除外していない。したがって、「手段A及びBを備えるデバイス」という表現の範囲は、コンポーネントA及びBだけからなるデバイスに限定すべきでない。本発明に関して、A及びBが、関連するデバイスのコンポーネントであることを意味するに過ぎない。

30

##### 【0072】

この明細書を通じて「一実施形態(one embodiment又はan embodiment)」が意味するのは、該実施形態と関連して説明される特定の特徴、構造又は特性は、本発明の少なくとも一実施形態に含まれるということである。したがって、この明細書を通じてさまざまな場所で現れるフレーズ「一実施形態」は、必ずしもすべてが同じ実施形態を参照するわけではないが、参照してもよい。さらに、特定の特徴、構造又は特性は、この開示から当業者にとって明らかなように、1以上の実施形態において、好適な方法で組み合わせができる。

##### 【0073】

同様に、例示的な特定の実施形態の説明において、本発明の種々の特徴は、開示を効率化し、1以上のさまざまな発明の態様を理解することを助ける目的で、時には単一の実施形態、図面、又はその説明の中に一緒にグループ化されることを認識するべきである。しかしながら、この開示の方法は、請求項記載の発明が、各請求項に明確に記載されたものより多くの特徴を必要とするという意図を反映していると解釈すべきではない。むしろ、以下の請求項が示すように、発明の態様は、先に開示された単一の実施形態のすべての特徴より少なくなる。したがって、詳細な説明に続く請求の範囲は、これにより詳細な説明中に明確に包含され、各請求項は、この発明の別々の実施形態としてそれ自身で成立する。

40

##### 【0074】

50

さらに、ここに記載したいいくつかの実施形態は、他の実施形態に含まれるいくつかの特徴は含むが、他の特徴は含まない。一方、当業者が理解することになるように、異なる実施形態の特徴の組み合わせは、本発明の範囲内であることを意味し、異なる実施形態を形成する。例えば、以下の請求の範囲において、請求項記載の実施形態のいずれもが、任意の組み合わせで使用可能である。

【0075】

本明細書でされる説明において、多くの具体的な詳細が明記される。しかしながら、特定の実施形態はこれらの具体的な詳細なしに実践してもよいことが理解される。他の例において、周知の方法、構造、及び技術は、この説明の理解を不明瞭にしないために、詳細には示さない。

10

【0076】

本発明は、以下、種々の特定の実施形態の詳細な説明によって説明されることとなる。添付の請求項によって規定される本発明の技術的教示から逸脱しない範囲で当業者の知識によって、他の特定の実施形態を構成することができることは明らかである。

【0077】

本文中、用語「トンネル電界効果トランジスタ（TFT）」を使用する場合、ゲートがいわゆるバンド間トンネリング（BTBT）の変調を通じてソース - ドレイン電流を制御する半導体デバイスを指す。バンド間トンネリングは、電子が、半導体バンドギャップを通じて価電子帯から導電性バンドまで、又はその逆に通過するプロセスである。

20

【0078】

本明細書で説明するいくつかの実施形態は、ダブルゲートTFTデバイス、特に、例えば半導体基板平面内の、水平ソース - チャネル - ドレイン構造のようなソース - チャネル - ドレイン構造と、水平ソース - チャネル - ドレイン構造のソース領域の側壁に位置するダブルゲート電極とを備えたTFTデバイスの実施例を含むところ、同様に、他のTFTデバイス、例えばトリゲートTFT、オールアラウンド型ゲートTFT、ナノワイヤTFT等を本発明の実施形態に加えてもよい。トリゲートTFTは、半導体基板平面内のソース - チャネル - ドレイン構造、例えば水平ソース - チャネル - ドレイン構造と、水平ソース - チャネル - ドレイン構造のソース領域の側壁及び上部にそれぞれ位置する3つのゲート電極部分を有するトリプルゲート電極とを備える。ゲートオールアラウンドTFTは、水平又は垂直ソース - チャネル - ドレイン構造、即ち基板平面内の、又は、基板平面に略垂直なソース - チャネル - ドレイン構造と、水平又は垂直ソース - チャネル - ドレイン構造のソース領域の周囲に位置する、即ち該領域を包囲する又は取り囲むオールアラウンド型ゲート電極とを備える。ナノワイヤTFTは、少なくともチャネル領域を形成するナノワイヤを備え、任意にチャネル領域並びにソース領域及びドレイン領域、並びにナノワイヤTFTのソース領域の周囲の、即ち該領域を包囲する又は取り囲むオールアラウンド型ゲート電極構造を備える。

30

【0079】

本明細書で説明するいくつかの実施形態は、nTFTの実施例を含む。これは、半導体デバイスが、p型ソース（ソース領域を少なくとも部分的に包囲するゲート電極、例えばソース領域又はその周囲に位置するゲート電極を有する）及びn型ドレインを備える（しばしばp - i - nダイオードとも呼ばれる）ことを意味する。また、例えばpTFTのような他のTFTデバイスの実装も可能である。これは、半導体デバイスが、n型ソース（ソース領域を少なくとも部分的に包囲するゲート電極、例えばソース領域又はその周囲に位置するゲート電極を有する）及びp型ドレインを備えることを意味する。

40

【0080】

本発明の第1の態様では、「ソースオンリーゲート（source only gate）デザイン」を有する新規なトンネル電界効果トランジスタ（TFT）デバイスが開示されている。該TFTは、ドープされたソース領域、ドープされたドレイン領域、及び、ドープされたソース領域とドープされたドレイン領域との間に位置するチャネル領域を有するソース - チャネル - ドレイン構造を備える。チャネル領域は、ソース領域とソース - チャネル界面を

50

形成し、ドレイン領域とドレイン - チャネル界面を形成する。T F E T はさらに、ゲート電極及びゲート誘電体を有するゲートを備え、ゲート電極は、T F E T デバイスのソース領域の少なくとも一部を覆い、T F E T デバイスのチャネル領域及びドレイン領域を覆わない。これは、バンド間トンネリングがゲート電極に略垂直な方向で発生するライントンネリングが、本発明の実施形態によるT F E T デバイスの主なトンネリング機構である、ということを意味する。ソース領域は、少なくとも2つの異なる領域、例えばそれぞれ同じドーパント型のドーパント元素でドープされており且つ異なるドーピングレベルを有するような2つの異なる領域を含む。ここで、ソース - チャネル界面に最近接した領域のドーピングレベルは、ソース - チャネル界面からさらに離れた他の領域のドーピングレベルよりも充分に高度にドープされている。

10

#### 【 0 0 8 1 】

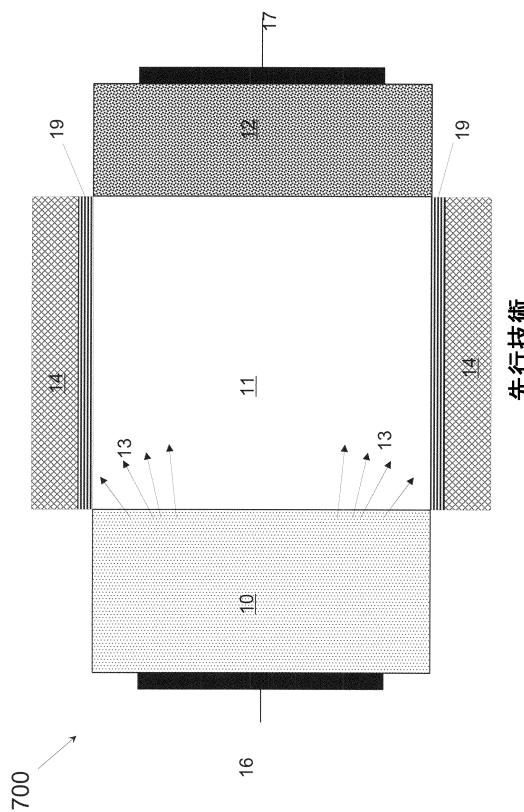

図7は、従来のT F E T 構造700の断面図を示しており、ゲート誘電体10及びゲート電極14を有するゲートは、全チャネル領域11と重なり合う。これは、任意に、T F E T 構造のソース領域10及びドレイン領域12の一方又は両方と小さく重なり合う(不図示)ことを含む。図7に示すようなT F E T 構造は、少なくともソース - チャネル - ドレイン構造とゲート電極14との間に、ゲート誘電体19を備える。T F E T 構造はさらに、ソースコンタクト16とドレインコンタクト17とを備える。ゲート電極がチャネル領域11の上に位置しているので、図7に示すようなT F E T 構造の場合のトンネリング機構は、矢印13で示す、チャネル領域11を経由する、ソース領域10とゲート電極14との間のポイントトンネリングによって支配される。

20

#### 【 0 0 8 2 】

図1は、本発明の一実施形態によるT F E T 構造100の断面図を示している。該T F E T 構造は、デバイスの長手方向Lに互いに隣接するソース領域30、チャネル領域21及びドレイン領域22を備える。ソース領域30とチャネル領域21との間に、ソース - チャネル界面201が存在する。ドレイン領域22とチャネル領域21との間に、ドレイン - チャネル界面202が存在する。図1に示すT F E T 構造はさらに、ソース領域30と少なくとも一部で重なり合うゲート電極24を備える。ソース領域30は、第1ソースサブ領域20と第2ソースサブ領域25とを含む。ゲート電極24は、チャネル領域21及びドレイン領域22と重なり合わない。本発明の実施形態による、図1に示すT F E T 構造100はさらに、ゲート電極24とソース領域30との間にゲート誘電体29を備える。第2ソースサブ領域25は、T F E T 構造のソース - チャネル界面に位置し、T F E T 構造100の長手方向Lに幅Wを有する。第2ソースサブ領域25の幅Wは、例えば単分子層以上10nm以下でもよい。第2ソースサブ領域25は、第1ソースサブ領域20と同じドーパント型を有するが、第2ソースサブ領域25でのピーク濃度は、第1ソースサブ領域20と第2ソースサブ領域25との間の界面の位置又は該界面に近接する位置での第1ソースサブ領域20のドーピングプロファイルの最大ドーピングレベルよりも充分に高い。ゲート電極24はソース領域30の上にのみ位置しているので、図1に示すT F E T 構造の場合のトンネリング機構は、矢印23で示す、ソース領域30とゲート電極24との間のライントンネリングによって支配される。T F E T 構造100はさらに、ソース領域30に電気的に接觸するソースコンタクト26と、ドレイン領域22に電気的に接觸するドレインコンタクト27とを備える。

30

#### 【 0 0 8 3 】

例えば、第1ソースサブ領域20は、ソース - チャネル界面201に向かうテールを有する傾斜した(例えばガウシアン)ドーピングプロファイルを有してもよい。好ましくは、第2ソースサブ領域25は、第1ソースサブ領域20と第2ソースサブ領域25との間の界面に近接する位置での第1ソースサブ領域20のドーピングプロファイルの最大ドーピングレベルより充分に高いドーピングレベルを有するソース - チャネル界面201の近くに位置し、例えば隣接している。

40

#### 【 0 0 8 4 】

本発明の実施形態によれば、ゲート電極24は、ソース領域30と完全に重なり合って

50

もよく、或いは、ソース領域30の一部のみと重なり合ってもよい。しかしながら、本発明の実施形態によれば、ゲート電極24は、TFTデバイス100のチャネル領域21及びドレイン領域22と重なり合わなくてよい。この構成により、ポイントトンネリングでなくライントンネリングが発生する。

【0085】

ゲート電極24が部分的にのみソース領域30と重なり合う実施形態では、例えば図2に示すように、ゲート電極24と重なり合わないソース領域30の距離であるアンダーラップ(underlap)  $L_{underlap}$  を規定できる。ゲート電極がソース領域を部分的にのみ覆う場合には、異なる例が可能である。アンダーラップ  $L_{underlap}$  は、ゲート電極24の長手方向Lの両側又は片側、即ち、第1アンダーラップは、ソース-チャネル界面201の側、及び/又は第2アンダーラップは、ソース20, 25-ソースコンタクト電極26の側に存在してもよい。図2は、アンダーラップ  $L_{underlap}$  がゲート電極24とソース-チャネル界面201との間の距離である場合の例である。

【0086】

第2ソースサブ領域25は、ポケット領域と呼んでもよい。第1ソースサブ領域20及び第2ソースサブ領域25の両方が同じドーピング型、即ち両方がp型(或いはn型)にドープされる。第2ソースサブ領域25でのドーパントのピーク濃度、即ち最大ドーピングレベルは、第1ソースサブ領域20と第2ソースサブ領域25との間の界面に近接する位置での第1ドーピングプロファイルの最大ドーピングレベルより充分高い必要がある。第2ピーク濃度とも呼ばれる第2ソースサブ領域25のピーク濃度は、好ましくは、第1ソースサブ領域20と第2ソースサブ領域25との間の界面の位置、又は該界面に近接する位置、例えば該界面から5nm以上10nm以下の範囲内での第1ドーピングプロファイルの最大ドーピングレベルより少なくとも4倍高い必要がある。例えば、第1ソースサブ領域について、急峻な、非常に急勾配のドーピングプロファイルの場合、第1ソースサブ領域20は、特定の型のドーパント、例えばホウ素のようなp型ドーパントで、 $1 \times 10^{20} / \text{cm}^3$  の第1ピーク濃度まで充分均一にドープされてもよい。第2ソースサブ領域25は、同じ型のドーパント、例えば同様にホウ素のようなp型ドーパントで、第1ソースサブ領域20のドーピングレベルの少なくとも4倍より高いドーピングレベル、例えば上述の例では(少なくとも)  $4 \times 10^{20} / \text{cm}^3$  のドーピングレベルまでドープしてもよい。第1ソースサブ領域20と第2ソースサブ領域25との間の界面の位置、又は該界面に近接する位置での第1ソースサブ領域20のドーピングプロファイルの最大ドーピングレベルは第1ドーピングプロファイルの特性(例えばピーク濃度、ドーピングプロファイルの傾斜の大きさ等)に応じて変化してもよい。図9及び図10に2つの例を概略的に示している。

【0087】

図9及び図10は、本発明の実施形態による、第1, 第2ソースサブ領域20, 25の第1, 第2ドーピングプロファイルについての可能な例をそれぞれ概略的に表している。

【0088】

図9は、第1ソースサブ領域20での第1ピーク濃度1021を有する第1ドーピングプロファイル1011と、第2ソースサブ領域25での第2ピーク濃度1022を有する第2ドーピングプロファイル1012とを示す。第1ソースサブ領域と第2ソースサブ領域との間の界面1014と同様に、ソース-チャネル界面201を示している。第2ピーク濃度1022は、界面1014に近接する位置(図9では、1014と1015との間の領域として示しており、位置1015は、界面1014から約5nm隔てた位置である)での第1ドーピングプロファイル1011の最大ドーピングレベルより高い必要がある。位置1015と界面1014との間のこの領域について、最大ドーピングレベル1023が規定される。第2ピーク濃度1022は、ドーピングレベル1023より充分高い必要がある。

【0089】

図10は、図9と同様の状況を示しているが、第1ソースサブ領域20の第1ドーピン

10

20

30

40

50

グローブファイル 1011 は、非常に急峻なドーピングプロファイルであり、これはプロファイル 1011 の傾斜の大きさからわかる。また、第 2 ドーピングプロファイル 1012 の第 2 ピーク濃度 1022 は、第 1 ソースサブ領域 20 と第 2 ソースサブ領域 25 との間の界面 1014 に近接する位置（図 10 では、1014 と 1015 との間の領域として示しており、位置 1015 は、界面 1014 から約 5 nm 隔てた位置である）での第 1 ドーピングプロファイルの最大ドーピングレベル 1023 より高い必要がある。結果として、第 2 ピーク濃度 1022 は、第 1 ドーピングプロファイル 1011 の第 1 ピーク濃度 1021 より充分高い必要がある。

#### 【0090】

本発明の実施形態による TFE T 構造 100 では、ドレイン領域 22 は、ソース領域 30 と反対のドーピング型、例えば p 型ソースに対して n 型ドレイン又はその逆、にドープされる。好ましくは、ドレイン領域 22 のドーピングレベルは、第 1 ソースサブ領域 20 のドーピングレベルと同程度であり、例えば約  $1 \times 10^{20} / \text{cm}^3$  である。間のチャネル領域 21 は、低ドープされ、又はドープされず、例えば、 $1 \times 10^{12} / \text{cm}^3$  以上  $1 \times 10^{15} / \text{cm}^3$  以下のドーピングレベルでドープされる。

#### 【0091】

第 1 ソースサブ領域 20 のドーピングレベルと比較してより高い第 2 ソースサブ領域 25 のドーピングレベルに起因して、ドレイン - ソース電圧  $V_{DS}$  の影響をより好適に制御することができる。第 2 ソースサブ領域 25 を使用することにより、かかる第 2 ソースサブ領域が存在しない先行技術の TFE T と比較して、ドレイン - ソース電流  $I_{DS}$  のシフトは、ドレイン - ソース電圧  $V_{DS}$  の変化に伴い、印加するゲート電圧  $V_G$  でより小さくなる。これは、ポイントトンネル電流を増強して全トンネル電流に寄与するように、ソース領域 30 からチャネル領域 21 に至る荷電キャリアのトンネリングを妨害する。そうでなければ、ポケット領域 25 は、キャリア（電子又はホール）がソース領域 30 とチャネル領域 21 との間を流れるための障壁を形成する。

#### 【0092】

第 2 ソースサブ領域 25 又はポケット領域は、ソース - チャネル界面 201 と直接接觸するように位置してもよく（図 1 及び図 2 に示すように）、又は、ソース - チャネル界面 201 から距離 D のところに位置してもよい（図 3 に示すように）。

#### 【0093】

本発明の実施形態では、ポケット領域 25 を長方形に図示している。しかしながら、これは例示的に過ぎず、使用するドーピング技術に応じて他の不規則な形状を提供してもよい。第 2 ソースサブ領域 25 は、長手方向に単分子層以上 10 nm 以下の幅 W を有する。第 2 ソースサブ領域 25 は、長手方向 L と垂直な方向に、ゲート誘電体 29 から距離 T 隔てて存在してもよい。この距離 T は、本体の寸法（即ち、ソース - チャネル - ドレイン構造の寸法）に応じて、0 以上 10 nm 以下でもよく、例えば 0 以上 5 nm 以下でもよい。

#### 【0094】

第 2 ソースサブ領域 25 のドーピングは、当業者に知られた技術で行われる。TFE T デバイス 100 の水平方向アーキテクチャの場合、つまり、TFE T デバイスの長手方向 L が略基板平面内にある場合、第 1 注入を実施して、第 1 ソースサブ領域 20 を第 1 ドーピングレベルでドープしてもよく、第 2 注入を実施して、第 2 ソースサブ領域 25 を第 1 ドーピングレベルよりも高い第 2 ドーピングレベルでさらにドープしてもよい。TFE T デバイスの垂直方向アーキテクチャの場合、つまり、TFE T デバイスの長手方向 L が基板平面と略直交する場合、チャネル領域 21 の上部にドープ層をエピタキシャル成長させることによって第 2 ソースサブ領域 25 を形成してもよく、その後、別の低ドープ層を第 2 ソースサブ領域の上部にエピタキシャル成長させて第 1 ソースサブ領域 20 を形成してもよい。

#### 【0095】

図 4、図 5 及び図 6 に示すシミュレーションは、デバイスシミュレータ（Synopsys（登録商標）社の Sentaurus Device）を用いて実施し、本発明の実施形態による TFE T 構造

10

20

30

40

50

100の特性を決定した。ゲート電極が完全にソース領域30を覆う、シミュレーションに用いたTFT構造を図1に示す。該TFT構造は2次元構造であり、ソース領域30の両側（例えば、図1の上下）にゲートを有するダブルゲート構造である。

#### 【0096】

シミュレーションでは、ソース領域の中央部分の高さ（ゲート誘電体29の間の）は、50nmである。ゲート誘電体29の等価酸化膜厚EOTは、0.4nm以上1.2nm以下で変化させた。チャネル領域21の長さは40nmであり、ゲート24の長さは30nmである（チャネル領域との重なり合いはない）。

#### 【0097】

TFT構造100で、電気的性能のために考慮するべき最も重要な寸法は、ゲートの長さ $L_{gate}$ 並びに第2ソースサブ領域（ポケット領域）25の厚さ及びドーピングレベルである。例えば、図4、図5及び図6に示すシミュレーションの場合、ポケット領域25は、ゲート誘電体29から0以上10nm以下の距離Tを隔てて存在し、約3nmの幅Wを有し、ソース-チャネル界面201に直接位置する（D=0）

10

#### 【0098】

（第1、第2）ソースサブ領域20、25及びドレイン領域22のドーピングは、更なる重要なパラメータである。第1ソースサブ領域20のドーピングの場合、p型ドーピングの例では、ドーピングレベルは $1 \times 10^{20} / \text{cm}^3$ である。第2ソースサブ領域25のドーピングの場合、p型ドーピングの例では、ドーピングレベルは $4 \times 10^{20} / \text{cm}^3$ である。ドレイン領域22のドーピングの場合、n型ドーピングの例では、ドーピングレベルは $1 \times 10^{20} / \text{cm}^3$ である。チャネル領域21のドーピングは、低ドープである限り重要でない。このシミュレーション例で使用したチャネル領域についてのドーピングレベルは、n型であり、 $10^{13} / \text{cm}^3$ である。

20

#### 【0099】

より高度にドープされた第2ソースサブ領域25の存在に起因するドレイン-ソース電圧の影響の減少を、図4、図5及び図6に示している。これらの図は、本発明の実施形態によるTFT構造についてのシミュレーション結果を示す。

#### 【0100】

図4は、ソース領域に第2ソースサブ領域がなく、ソース領域にのみゲートが存在するTFT構造についてシミュレーションした出力特性を示す。図4は、異なるドレイン電圧 $V_{DS}$ について、ドレイン電流 $I_{DS}$ 対ゲート電圧 $V_{GS}$ を示す。ソース領域は、第1ソースサブ領域のみで構成され、 $1 \times 10^{20} / \text{cm}^3$ のドーピングレベルを有する。ゲート誘電体は、ゲートとソース領域との間に存在し、0.4nmの等価酸化膜厚EOTを有する。ドレイン領域は、 $1 \times 10^{20} / \text{cm}^3$ のドーピングレベルを有し、チャネル領域は、 $1 \times 10^{13} / \text{cm}^3$ のドーピングレベルを有する。最低ドレイン-ソース電流（約 $10^{-9} \text{ A} / \mu\text{m}$ 未満）で、印加するドレイン電圧 $V_{DS}$ に応じたゲート-ソース電圧 $V_{GS}$ のシフトが観察される。1pA/ $\mu\text{m}$ の電流で、ドレイン電圧 $V_{DS}$ を0.1Vから最大1Vまで変化させた場合、ゲート-ソース電圧 $V_{GS}$ は、約50mVシフトする。 $10 \text{ fA} / \mu\text{m}$ でのゲート-ソース電圧 $V_{GS}$ （開始電圧）は、ドレイン電圧 $V_{DS}$ を0.1Vから最大1Vまで変化させる場合、約0.1Vシフトする。しかしながら、これは、回路におけるTFTの性能に影響（負の影響）を与えることになるため、有害であり、したがって望まれない。

30

#### 【0101】

図5は、本発明の実施形態による第2（ポケット）ソースサブ領域25を有するTFT構造100についてのシミュレーションした入力特性（黒記号）を示しており、また、これらを第2（ポケット）ソースサブ領域を有しないTFT構造についてのシミュレーションした入力特性（白記号）と比較している。第2（ポケット）ソースサブ領域を有する構造、有しない構造の両方について、ゲート24はソース領域30上にのみ存在する。 $4 \times 10^{20} / \text{cm}^3$ のドーピングレベルを有する3nm幅の第2（ポケット）ソースサブ領域25が使用される。図5は、 $10 \text{ fA} / \mu\text{m}$ の電流を得るために必要なゲート-ソ

40

50

ース電圧として定義される開始電圧  $V_{\text{onset}}$  を、ゲート 24 とソース領域 30 との間に存在するゲート誘電体 29 の等価酸化膜厚 EOT の関数として、異なるドレイン電圧  $V_{DS}$  (0.1V, 0.5V 及び 1V) について示す。異なるドレイン電圧  $V_{DS}$  についての  $V_{\text{onset}}$  の広がりは、EOT が小さい程小さくなっている。第 2 (ポケット) ソースサブ領域 25 を有する TFEET 構造 100 の場合 (黒記号)、0.6nm より小さい EOT では異なるドレイン電圧  $V_{DS}$  についての  $V_{\text{onset}}$  の広がりはほとんど無視できる。一方、第 2 (ポケット) ソースサブ領域を有しない TFEET 構造の場合 (白記号)、異なるドレイン電圧  $V_{DS}$  についての  $V_{\text{onset}}$  の広がりがずっと視認される。本発明の実施形態による、第 2 (ポケット) ソースサブ領域 25 を有する TFEET 構造 100 の場合、ドレイン - ソース電圧  $V_{DS}$  を変化させたときの  $V_{GS}$  の広がりは、小さい EOT 10、即ち 0.6nm より小さい EOT については無視できる。したがって、 $V_{\text{onset}}$  は、小さい EOT についてはドレイン電圧  $V_{DS}$  に依存しなくなる。EOT が大きい場合、即ち 0.6nm より EOT が大きい場合、 $V_{\text{onset}}$  の広がりは、第 2 (ポケット) ソースサブ領域 25 を有する TFEET 構造と有しない TFEET 構造とでほぼ同程度である。しかしながら、ドーピングレベル及びポケット 25 の幅を最適化した場合には、より大きい EOT の値でより小さい広がりを得ることができることが期待される。つまり、本発明の実施形態でのポケットを導入することにより、ドレイン - ソース電圧を変化させた際にゲート - ソース電圧の広がりを常に低下させることができることが期待される。

#### 【0102】

したがって、開始電圧が印加するドレイン電圧に依存しなくなることが、本発明の実施形態の利点である。 20

#### 【0103】

ゲートとソース領域との間に存在するゲート誘電体の等価酸化膜厚 EOT の関数での開始電圧の広がり  $V_{\text{onset}}$  を図 6 に示す (図 5 のデータをベースとして)。  $V_{\text{onset}}$  は、0.1V のドレイン電圧での開始電圧  $V_{\text{onset}} @ V_{DS} = 0.1V$  と 1V のドレイン電圧での開始電圧  $V_{\text{onset}} @ V_{DS} = 1V$  の差として定義される。図 6 は、本発明の実施形態による第 2 (ポケット) ソースサブ領域 25 を有する TFEET 構造 100 (黒記号) 及び有しない TFEET 構造 (白記号) についてのシミュレーションした入力特性を示す。第 2 (ポケット) ソースサブ領域 25 を有する場合と有しない場合の両方について、ゲート 24 はソース領域 30 上にのみ存在する。  $4 \times 10^{20} / \text{cm}^3$  のドーピングレベルを有する 3nm 幅の第 2 (ポケット) ソースサブ領域 25 が使用される。EOT の値が小さい場合、即ち、EOT の値が 0.6nm より小さい場合、本発明の実施形態による第 2 (ポケット) ソースサブ領域 25 (黒記号) を有する TFEET 構造についての  $V_{\text{onset}}$  を大幅に減少させる (ほぼ 0 となる) ことができる。 30

#### 【0104】

本発明の第 2 の態様では、本発明の実施形態による TFEET 構造を製造するための方法 300 が提供される。

#### 【0105】

TFEET 構造を製造するための特定の処理方法を図 8 にフローチャートで示す。以下、本発明の一実施形態による方法 300 を、図 1 (断面図) に示すような (ダブル) ゲート構造を備えた TFEET について説明することになる。これは、本発明の技術的範囲を制限するものではなく、該方法はまた、例えば上述の、本発明の実施形態による代替の TFEET 構造 (例えば、ナノワイヤ、第 2 ゲート構造を備えた等) の作成にも適用することができる、と理解する必要がある。 40

#### 【0106】

第 1 工程 310 では、基板を準備する。好ましくは、前記基板はシリコン基板又はシリコンオンインシュレータ (SOI) 基板のような半導体基板であるが、例えばガラス、セラミックス等のような他の好適な基板を使用してもよい。

#### 【0107】

本発明の実施形態によれば、少なくとも 1 つの n (又は p) ドープしたドレイン領域 2 50

2と、1つのチャネル領域21と、p(又はn)ドープした第1、第2ソースサブ領域20、25を含むソース領域とを有するソース-チャネル-ドレイン構造を形成する。例えば、CVD(化学気相成長法)、MOCVD(有機金属化学気相成長法)又はPECVD(プラズマ化学気相成長法)プロセスのような蒸着技術を使用することができる。代替として、エッチング技術を使用して、前記構造を基板内までエッチングすることも可能である。

#### 【0108】

ソース-チャネル-ドレイン構造において、ドレイン領域22、チャネル領域21及びソース領域30(第1、第2ソースサブ領域20、25)を形成するために、異なるドーピングレベル及び異なるドーピング型を有する異なる領域を作成する必要がある。これらの異なる領域を蒸着プロセス中にドープして、n型又はp型領域を得ることができる。代替として、ドーピングは、方法の工程316、317、318に示すように、追加のドーピング工程により蒸着工程の後に実施してもよい。一つの特定の領域、例えば第1ソースサブ領域22、第2ソースサブ領域25又はドレイン領域22でのドーピングは、均一でもよく、或いは代替として、不均一なドーピングプロファイルを有してもよい。ソース領域30をドープすることは、第1ソースサブ領域20を第1ドーピング型及び第1ドーピングレベルでドープすることと、第2ソースサブ領域25を第1ドーピング型と同じ第2ドーピング型及び第1ドーピングレベルより充分高い第2ドーピングレベルでドープすることとを含む。

#### 【0109】

図8に示す実施形態では、作成するソース-チャネル-ドレイン構造は垂直構造である。ドレイン領域22は、基板上に作成する(工程311)。前記ドレイン領域22は、n型TFTの場合には高度にnドープした第1半導体材料で作成してもよく、或いは、p型TFTの場合には、前記ドレイン領域22は、高度にpドープしてもよい。本発明の実施形態では、ドレイン領域のドーピングレベルは $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下であり、例えば $1 \times 10^{19} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下である。

#### 【0110】

TFTのチャネル領域21は、ドレイン領域22上に形成し、したがって、ドレイン-チャネル界面202を形成する(工程312)。本発明の実施形態では、前記チャネル領域21は、好ましくは第1半導体材料で作成してもよく、他の好適な/適合する材料を使用することもできる。本発明の実施形態では、チャネル領域21のドーピングレベルは、アンドープ状態から最大 $1 \times 10^{17} / \text{cm}^3$ でもよく、例えばアンドープ状態から最大 $1 \times 10^{14} / \text{cm}^3$ でもよい。

#### 【0111】

ソース領域30は、チャネル領域21に隣接して作成し、ソース-チャネル界面201を形成する(工程313)。前記ソース領域30は、第1半導体材料で作成してもよく、他の好適な/適合する材料を使用することもできる。n型TFTの場合、半導体材料は、高度にpドープしてもよい(或いは、p型TFTの場合、前記ソース領域30は高度にnドープしてもよい)。ソース領域30は、第1ドーピング型及び第1ドーピングレベルを有する第1ソースサブ領域25と、第1ドーピング型と同じ第2ドーピング型及び第1ドーピングレベルより充分高い第2ドーピングレベルを有する第2ソースサブ領域25とを含む。第1ソースサブ領域20のドーピングレベルは、 $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下でもよく、例えば $1 \times 10^{19} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下である。第2ソースサブ領域25のドーピングレベルは、 $5 \times 10^{18} / \text{cm}^3$ 以上 $4 \times 10^{21} / \text{cm}^3$ 以下でもよく、例えば $2 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下である。

#### 【0112】

nTFTかpTFTかに応じて、ソース領域30及び/又はドレイン領域22のために異なるドーパント型を使用してもよい。SiベースのTFTの場合、可能なp型ド

10

20

30

40

50

ーパントは、B、Al、Ga、In、Tl、Pd、Na、Be、Zn、Au、Co、V、Ni、Mo、Hg、Sr、Ge、Cu、K、Sn、W、Pb、O、Feであり、可能なn型ドーパントは、Li、Sb、P、As、Bi、Te、Ti、C、Mg、Se、Cr、Ta、Cs、Ba、S、Mn、Ag、Cd、Ptである。GeベースのTFTの場合、可能なp型ドーパントは、B、Al、Tl、Ga、In、Be、Zn、Cr、Cd、Hg、Co、Ni、Mn、Fe、Ptであり、可能なn型ドーパントは、Li、Sb、P、As、S、Se、Te、Cu、Au、Agである。

## 【0113】

ステップ314では、ゲート電極24をソース領域30に形成し、チャネル領域21及びドレイン領域22がゲート電極24によって覆われないように、少なくともソース領域30の一部を長手方向Lに覆い、特に、シングルゲート、ダブルゲート又はトリプルゲート構造をTFTの種類(ブレーナ型、MUGFET、水平型等)に応じて形成することができる。まず、ゲート誘電体(例えば酸化物)29を堆積する(工程315)。前記ゲート誘電体29は、少なくともゲート電極24の全長の下側に位置するが、TFT構造、即ち基礎となるソース-チャネル-ドレイン構造の全長を覆うことができる。次に、工程314で、ゲート電極24を前記ゲート誘電体29の上部に堆積する。

## 【0114】

ゲート誘電体29は、シリコンベースの酸化物(例えば二酸化ケイ素、酸窒化ケイ素)、酸化アルミニウム、high-k酸化物(Hf、Ta、Ti、Nb、V、Y、Zrのような遷移金属の酸化物、窒化酸化物、ケイ酸塩及び窒化ケイ酸塩)の少なくとも1つから選択してもよい。特定の実施形態では、前記ゲート誘電体は、酸化ハフニウムのようなhigh-k酸化物である。ゲート誘電体29、例えばゲート酸化物の厚さは、好ましくは0.5nm以上20nm以下である。

## 【0115】

ゲート電極24は、例えば、ポリシリコン、ポリゲルマニウム、Al、W、Ta、Ti、Ru、Pd、Rh、Re、Ptのような金属及びこれらの合金、Ta<sub>N</sub>及びTi<sub>N</sub>のような金属窒化物、TaSiNのような金属シリコン窒化物、RuO<sub>2</sub>及びReO<sub>3</sub>のような導電性酸化物、CoSi<sub>2</sub>、NiSi及びTiSi<sub>2</sub>のようなFUSI(fully silicided metal)、FUGE(fully germanided metal)、仕事関数を変更可能な金属、特定のゲート仕事関数を得るために設計した材料、の少なくとも1つから選択した材料で作成することができる。特定の実施形態では、前記ゲート電極24は、選択したチャネル材料21、ゲート誘電体材料、ゲート誘電体厚さ及びチャネルドーピングのために特別に設計した仕事関数を有する金属で作成する。

## 【0116】

さらに、電気的コンタクト26,27を、ソース領域30及び/又はドレイン領域22に形成してもよい。前記電気的コンタクト26,27は、シリサイド含有構造(NiSi、CoSi<sub>2</sub>、TiSi<sub>2</sub>等)、ゲルマニド含有構造、金属含有構造、ポリシリコン又はこれらの組み合わせの少なくとも1つから選択した導電性材料でもよい。特定の実施形態では、前記電気的コンタクトは、シリサイドと金属との化合物でもよい。また、例えば導電性酸化物及び更には導電性ポリマーで形成されたコンタクトが開示されている。特定の実施形態では、ソース及び/又はドレインコンタクト27は、シリサイド含有構造でもよい。

10

20

30

40

【 义 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(74)代理人 100101454

弁理士 山田 卓二

(74)代理人 100081422

弁理士 田中 光雄

(74)代理人 100100479

弁理士 竹内 三喜夫

(72)発明者 アン・エス・フェルフルスト

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 75 番 アイメック内

(72)発明者 クオ・シン・カオ

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 75 番 アイメック内

審査官 岩本 勉

(56)参考文献 特開2008-252086 (JP, A)

米国特許出願公開第2008/0224224 (US, A1)

米国特許出願公開第2006/0244077 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29/786

H 01 L 29/06

H 01 L 29/66