RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 476 893**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 81 00914**

(54) Registre à décalage statique I<sup>2</sup>L.

(51) Classification internationale (Int. Cl. <sup>3</sup>). **G 11 C 19/28.**

(22) Date de dépôt..... 19 janvier 1981.

(33) (32) (31) Priorité revendiquée : EUA, 21 février 1980, n° 123.434.

(41) Date de la mise à la disposition du

public de la demande..... B.O.P.I. — « Listes » n° 35 du 28-8-1981.

(71) Déposant : GENERAL INSTRUMENT CORPORATION, résidant aux EUA.

(72) Invention de : Kenneth L. Naiff.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Cabinet Harlé et Léchopiez,

21, rue de La Rochefoucauld, 75009 Paris.

La présente invention se rapporte à des registres à décalage, et elle a trait plus particulièrement à un registre à décalage statique pouvant être réalisé par des techniques  $I^2L$ .

5       Le principe  $I^2L$  (de circuit logique intégré à injection directe de porteurs) correspond à un progrès relativement récent réalisé dans le domaine de la fabrication des semi-conducteurs bipolaires et qui est couramment utilisé pour la réalisation de circuits intégrés de grande complexité.

10      Avec cette technique, il est possible de réunir des régions de différents transistors en vue d'augmenter la densité de circuit et d'éliminer les interconnexions entre transistors qui étaient auparavant nécessaires. En outre, les caractéristiques de fonctionnement de circuits  $I^2L$  peuvent être égales ou

15      même supérieures à celles de circuits fabriqués par d'autres techniques connues. Par exemple, des circuits  $I^2L$  peuvent opérer plus rapidement que des circuits MOS (métal-oxyde-semi-conducteur) à canal N et consommer moins d'énergie que des circuits CMOS (métal-oxyde-semi-conducteur complémentaire),

20      qui correspondent respectivement aux catégories à haute vitesse et basse puissance de la famille MOS. Dans le domaine bipolaire, la technique  $I^2L$  fournit un moyen pour maintenir une vitesse bipolaire supérieure, de sorte que les circuits atteignent, et même surpassent, les structures complexes

25      d'intégration à grande échelle LSI précédemment réalisées seulement par des techniques MOS.

L'unité logique fondamentale  $I^2L$  comprend un transistor inverseur et un transistor injecteur, qui joue le rôle d'une source de courant pour le transistor inverseur. Le transistor inverseur se compose physiquement d'un transistor bipolaire vertical à émetteurs multiples NPN, qu'on fait fonctionner dans le mode inverse. Dans ce mode, les émetteurs bipolaires classiques jouent le rôle de collecteurs.

Une excitation de base de l'inverseur NPN est assurée par 35 un transistor bipolaire PNP latéral, communément appelé un injecteur. Sur la pastille, certaines des zones diffusées de l'injecteur PNP sont intégrées (réunies) à celles de l'inver-

seur PNP du corps de silicium.

Le principe  $I^2L$  peut être mis en pratique par une technologie épitaxiale bipolaire classique. Il en résulte qu'on peut fabriquer des pastilles de circuits intégrés en utilisant le 5 principe  $I^2L$  sur des lignes de production bipolaire existantes, ce qui permet ainsi aux techniciens de conception de combiner une autre technologie bipolaire avec la logique  $I^2L$  sur la même pastille.

La haute compacité de  $I^2L$  résulte de la simplicité de 10 sa structure intégrée dans le corps de silicium. Cette simplicité est mise en évidence par plusieurs caractéristiques d'amélioration de densité de la pastille, notamment un petit nombre de contacts par portes, une absence complète de résistances diffusées, une absence de câblage dans les unités et 15 une facilité de mise en place du câblage entre des unités.

Comme autres avantages de la technologie  $I^2L$ , on peut citer la diminution de la tension de source, par comparaison à la technologie MOS, l'immunité au bruit et à d'autres interférences, et la possibilité de tolérer de grandes variations de la source de courant. En outre, dans de larges gammes 20 de vitesse et de dissipation d'énergie, la technologie  $I^2L$  permet d'obtenir un produit à retard de puissance presque constant.

Du fait des avantages précités de la technologie  $I^2L$ , 25 il est clair pour les spécialistes que des circuits fabriqués partiellement ou complètement par la technique  $I^2L$  joueront un grand rôle dans la fabrication future de circuits intégrés de grande complexité. Il est par conséquent nécessaire pour les techniciens de conception des circuits de mettre au point, 30 dans la technologie  $I^2L$ , des composants de traitement fondamental qui remplissent des fonctions semblables aux composants de traitement fondamental qui sont utilisés dans d'autres technologies. Cependant, du fait des propriétés différentes de la technologie  $I^2L$ , il est nécessaire d'adopter de nouvelles 35 conceptions de circuits pour exploiter intégralement les avantages de cette technologie.

Un des composants les plus couramment utilisés dans une

diversité d'applications de traitement différentes est constitué par le registre à décalage. Un registre à décalage est fondamentalement un dispositif qui mémorise des données pendant un nombre défini de périodes de temps, habituellement 5 représentées par des impulsions d'horloge. Le registre reçoit des signaux de données dans une certaine séquence temporelle à son entrée. Les signaux de données sont retenus par décalage ou par transfert à l'intérieur du registre, un décalage se produisant normalement pour chaque période de temps. Après 10 ledit nombre défini de périodes de temps, les signaux de données apparaissent dans la même séquence temporelle à la sortie du registre à décalage.

Un registre à décalage est composé d'un certain nombre de positions de bits ou étages qui déterminent sa capacité 15 de mémorisation. Les signaux de données sont transférés d'une position de bit à la suivante en réponse à des signaux de commande de transfert de données, dont l'échelonnement temporel détermine la vitesse à laquelle les données sont transférées d'une position de bit à la suivante.

20 D'une façon générale, on peut classer les registres à décalage en deux catégories, à savoir, une catégorie dynamique et une catégorie statique. Dans un registre à décalage dynamique, une charge représentant des données est temporairement mémorisée dans un élément à l'aide d'un condensateur, souvent la capacité 25 intrinsèque de la borne de commande d'un transistor. Une charge emmagasinée de cette manière est cependant dissipée dans un temps relativement court. Dans un registre à décalage dynamique, pour retenir les données dans celui-ci, on doit prévoir une fréquence de décalage des données (nombre de fois 30 par unité de temps où des données sont transférées d'un élément du registre au suivant) qui soit suffisamment élevée pour permettre un transfert de la charge emmagasinée avant que celle-ci se dissipe.

En conséquence, bien que des registres à décalage dynamiques soient extrêmement utiles dans certaines applications, ils possèdent un inconvénient intrinsèque, à savoir que la fréquence 35 de décalage doit toujours être plus grande qu'une limite infé-

rieure déterminée par le degré de dissipation de la charge emmagasinée. Si la fréquence de décalage tombe en-dessous de cette limite, les données mémorisées dans le registre à décalage sont perdues de façon irrécupérable.

5 D'autre part, un registre à décalage statique n'est affecté par aucune limite inférieure de la fréquence de décalage et, en conséquence, il conserve des données même à une fréquence de décalage nulle. Ce problème peut être résolu en assurant l'interconnexion des transistors qui

10 constituent le registre à décalage dans une relation de réaction, de manière que la charge emmagasinée par la capacité d'un élément de registre soit renforcée de façon continue par la sortie d'un autre élément, connecté en relation de réaction avec le premier, afin d'empêcher ainsi la dissipation de la

15 charge, même pour une fréquence de décalage nulle.

Un exemple excellent d'un registre à décalage statique réalisé conformément à la technologie MOS a été revendiqué dans le brevet des E.U.A. n° 3.683.203, ayant pour titre "ELECTRONIC SHIFT REGISTER SYSTEM".

20 Bien que la technologie  $I^2L$  commence à trouver un large domaine d'application, ce n'est que récemment qu'on a essayé de concevoir des registres à décalage en utilisant des techniques  $I^2L$ . Certaines de ces tentatives ont produit des registres à décalage semi-dynamiques, qui sont difficilement adaptables

25 aux paramètres opératoires et qui sont par conséquent difficiles et coûteux à fabriquer. Pour résoudre ces problèmes de fabrication, certains techniciens de conception ont essayé de mettre au point des registres à décalage statiques  $I^2L$  en copiant fonctionnellement presque directement la structure

30 des registres à décalage statiques MOS connus, ce qui a produit de gros registres statiques du type D qui sont très complexes et qui n'exploitent pas intégralement les avantages de la technologie  $I^2L$  connue.

35 L'invention a en conséquence pour but de fournir un registre à décalage statique qui puisse être réalisé par application de la technologie  $I^2L$ .

L'invention a en outre pour but de fournir un registre à

décalage  $I^2L$  qui soit simple, compact et facile à concevoir et fabriquer.

L'invention a également pour but de fournir un registre à décalage  $I^2L$  dans lequel chaque élément actif est identique 5 à tout autre élément actif, ce qui facilite la conception et la fabrication du registre à décalage.

L'invention a en outre pour but de fournir un registre à décalage statique  $I^2L$  où chaque élément actif est d'une conception simple.

10 L'invention a également pour but de fournir un registre à décalage statique  $I^2L$  qui soit bidirectionnel.

L'invention a en outre pour but de fournir un registre à décalage statique  $I^2L$  dans lequel la direction de transfert des données est déterminée uniquement par la séquence temporelle ou l'ordre des composants du signal de commande de transfert de données. 15

L'invention a également pour but de fournir un registre à décalage statique  $I^2L$  qui fonctionne bidirectionnellement sans qu'il soit nécessaire de prévoir des lignes de commande de sens de transfert de données, alors que celles-ci sont nécessaires dans des registres à décalage bidirectionnels classiques. 20

L'invention a en outre pour but de fournir un registre à décalage  $I^2L$  dans lequel une remise à zéro est effectuée 25 de façon simple en maintenant simultanément toutes les composantes du signal de commande à l'état bas ou "désactivé", puis en redéclenchant le signal de commande de façon que ses composantes soient dans la séquence temporelle normale.

L'invention a également pour but de fournir un registre 30 à décalage  $I^2L$  qui ne nécessite pas de lignes de commande de remise à zéro.

L'invention a en outre pour but de fournir un registre à décalage  $I^2L$  présentant une haute densité grâce à l'élimination des lignes de commande de remise à zéro et des lignes 35 de commande de sens de transfert de données, qui sont normalement nécessaires dans des registres à décalage de type bidirectionnel et pouvant être remis à zéro.

L'invention a également pour but de fournir un registre à décalage  $I^2L$  qui puisse être fabriqué dans un matériel de traitement bipolaire classique.

Conformément à la présente invention, il est prévu un 5 registre à décalage comprenant une position de bit. La position de bit comprend un nombre donné d'éléments actifs connectés fonctionnellement en série. Chaque élément actif comprend une unité  $I^2L$ , qui est couplée fonctionnellement en croix avec une unité adjacente. Il est prévu des moyens de génération 10 d'un signal de commande comportant plusieurs composantes, dont l'une est appliquée à un élément actif différent de la position de bit. Chaque composante du signal de commande comprend au moins une impulsion qui agit, lorsqu'elle est présente, pour exciter l'élément à laquelle elle est appliquée, 15 pendant la durée de l'impulsion.

Les composantes de signal de commande sont engendrées dans une séquence temporelle donnée ou dans un ordre donné. L'ordre ou la séquence temporelle détermine seul le sens de transfert des données dans le registre. En conséquence, une 20 inversion de la séquence temporelle provoque une inversion du sens de transfert des données au travers de la position de bit. Il n'est pas nécessaire de prévoir des lignes séparées de commande de sens de transfert de données qui aboutissent aux éléments actifs.

Il est prévu des moyens pour assurer la remise à zéro 25 des éléments. Ces moyens de remise à zéro comprennent des moyens pour désactiver temporairement le générateur de signaux de commande pendant une période de temps donnée, puis pour redéclencher ledit générateur de signaux de commande. En 30 conséquence, quand le générateur de signaux de commande est temporairement désactivé, le registre à décalage est automatiquement remis à zéro. De cette manière, il n'est pas nécessaire de prévoir des lignes séparées de commande de remise à zéro qui sont reliées aux différents éléments actifs.

Une composante de signal de commande est nécessaire pour 35 chaque unité  $I^2L$  dans une position de bit. Chaque composante de signal de commande comprend une série ou train d'impulsions

d'horloge positives et espacées. Les impulsions d'horloge des composantes du signal de commande peuvent ou non se chevaucher, suivant ce qui est souhaitable.

Chacun des éléments actifs comporte une entrée de données et une sortie de données. L'entrée de données de chaque élément est connectée fonctionnellement à la sortie de données de l'élément précédent. La sortie de données de chaque élément est connectée fonctionnellement à l'<sup>entrée de /</sup> données de l'élément précédent. En conséquence, l'entrée de données de chaque élément est connectée en relation directe avec la sortie de données de l'élément précédent et en relation de réaction avec la sortie de l'élément suivant. Sous un angle différent, chaque élément est couplé en croix avec les deux éléments précédent et suivant. On définit la caractéristique statique du registre à décalage sur la base de cette technique de couplage en croix. Chaque élément comprend une entrée de signal de commande qui est connectée au générateur de signaux de commande de manière à recevoir une composante du signal de commande.

Chaque élément est une unité  $I^2L$  qui comprend un transistor inverseur bipolaire et un transistor injecteur bipolaire. Le transistor inverseur et le transistor injecteur sont connectés entre l'entrée de signal de commande et la masse.

Le transistor injecteur est un transistor bipolaire comportant comme bornes une base, un collecteur et un émetteur. La base du transistor injecteur est connectée à la masse. L'émetteur est connecté fonctionnellement à l'entrée de signal de commande. Le collecteur est connecté fonctionnellement au transistor inverseur afin d'assurer l'excitation de sa base.

Le transistor inverseur de chaque unité est un transistor bipolaire comportant comme bornes une base, un premier et un second collecteur et un émetteur. La base est connectée fonctionnellement au transistor injecteur et, plus particulièrement, à son collecteur.

Les collecteurs du transistor injecteur sont connectés respectivement à l'unité  $I^2L$  précédente et à l'unité  $I^2L$  suivante. L'émetteur du transistor inverseur est connecté à la

masse.

La base du transistor inverseur est également connectée à l'entrée de données de l'unité. L'entrée de données de chaque unité est connectée directement à la sortie de données de l'unité précédente, sans interposition d'un dispositif d'isolement. L'élimination de l'obligation de prévoir un dispositif d'isolement entre des unités simplifie grandement la structure du registre à décalage.

Puisque chaque unité est identique à toutes les autres unités du registre, la conception, l'agencement et la fabrication du registre sont simplifiés et relativement peu coûteux. En outre, du fait qu'on élimine l'obligation de prévoir des dispositifs d'isolement, des lignes de commande de sens de transfert de données et des lignes de commande de remise à zéro, ont réduit la complexité et les dimensions des positions de bits, ce qui permet de fabriquer un plus grand nombre de positions de bits dans une zone donnée de pastilles.

D'autres avantages et caractéristiques de l'invention seront mis en évidence, dans la suite de la description, donnée à titre d'exemple non limitatif, en référence aux dessins annexés dans lesquels :

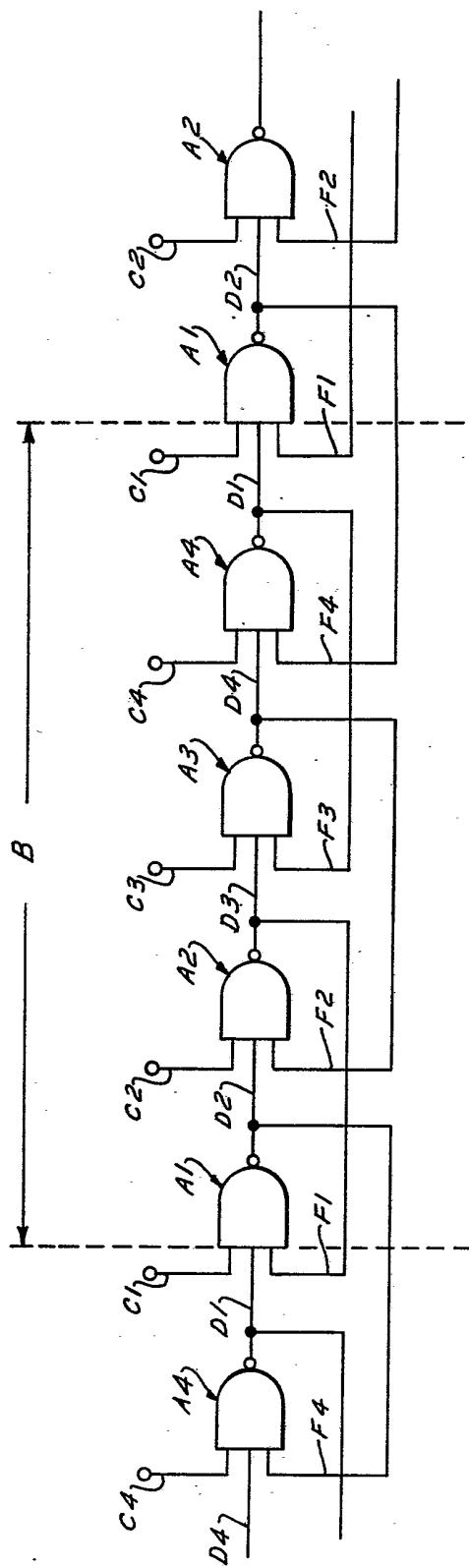

- La figure 1 est un schéma logique du registre à décalage selon l'invention ;

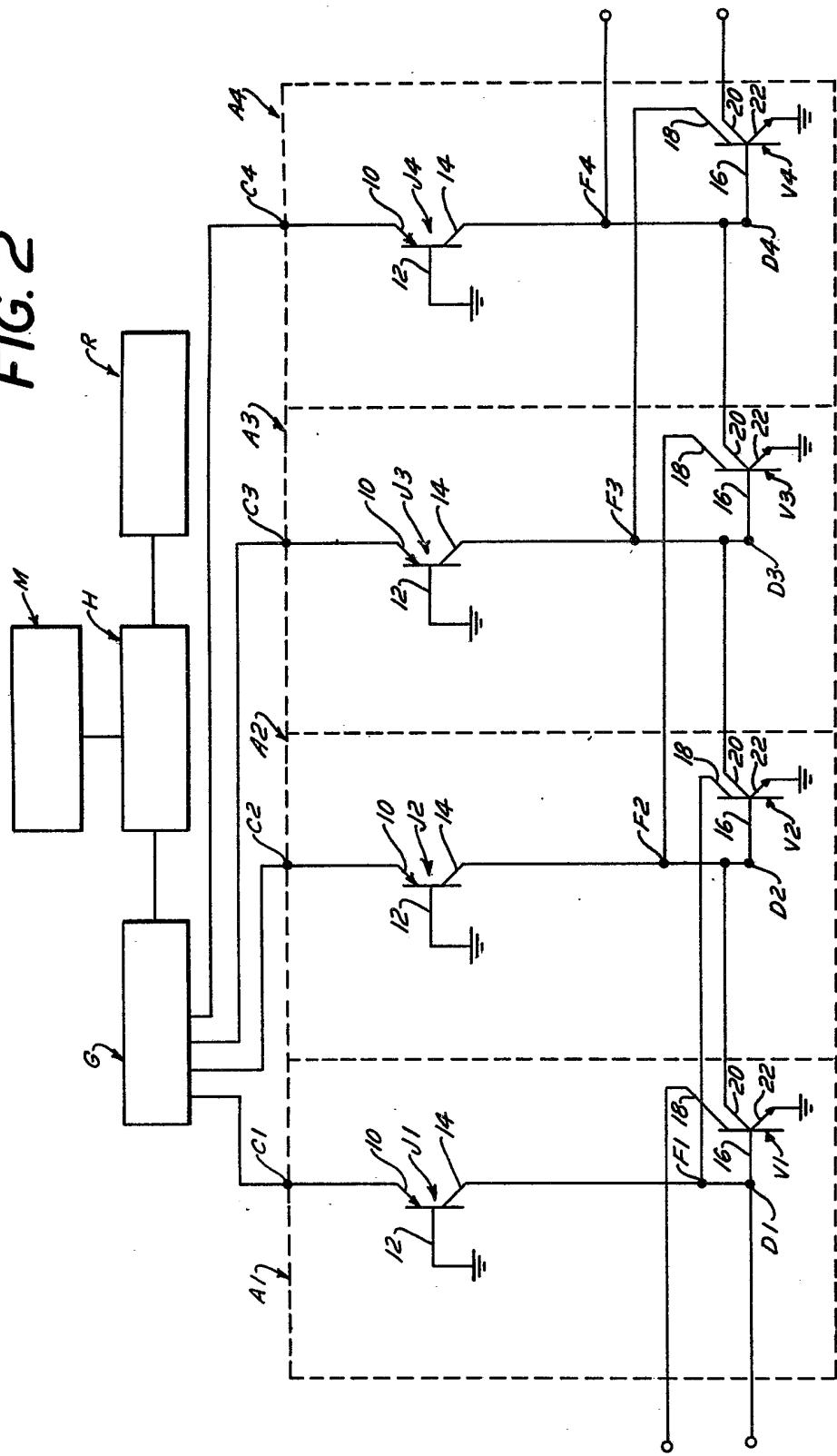

- La figure 2 est une représentation schématique d'une position de bit du registre à décalage selon l'invention ;

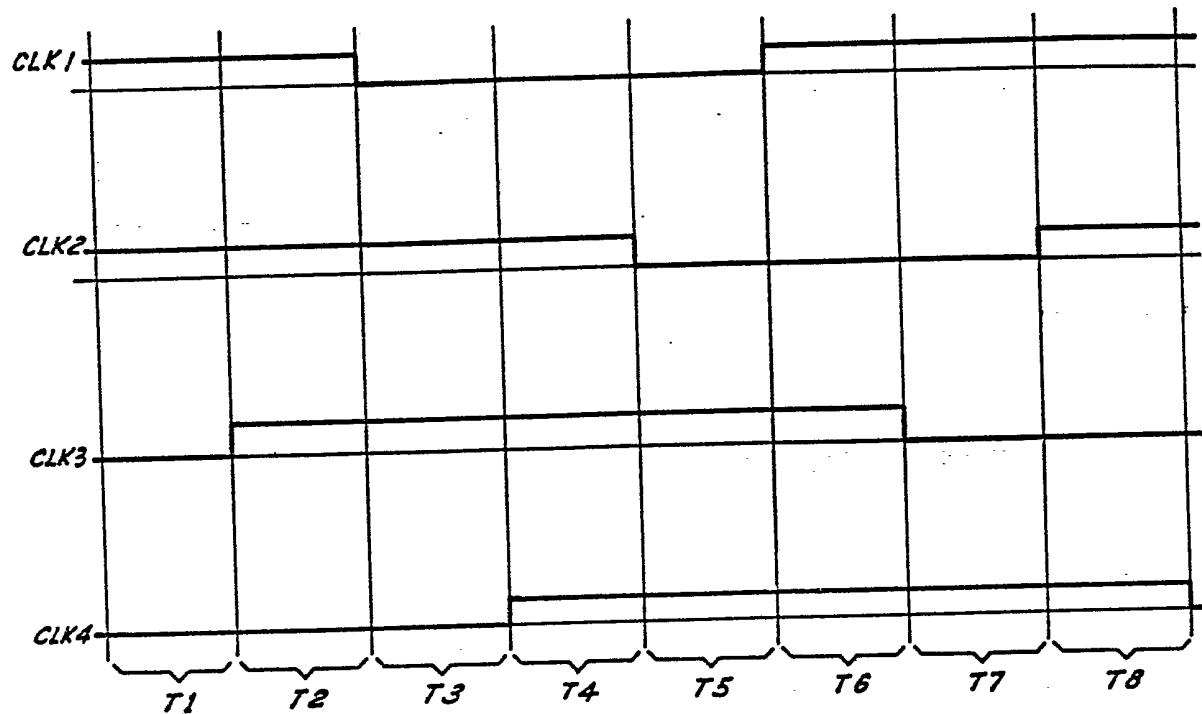

- La figure 3 est une représentation graphique du signal de commande utilisé pour obliger le registre à décalage selon l'invention à décaler des données dans un premier sens (direct) ; et

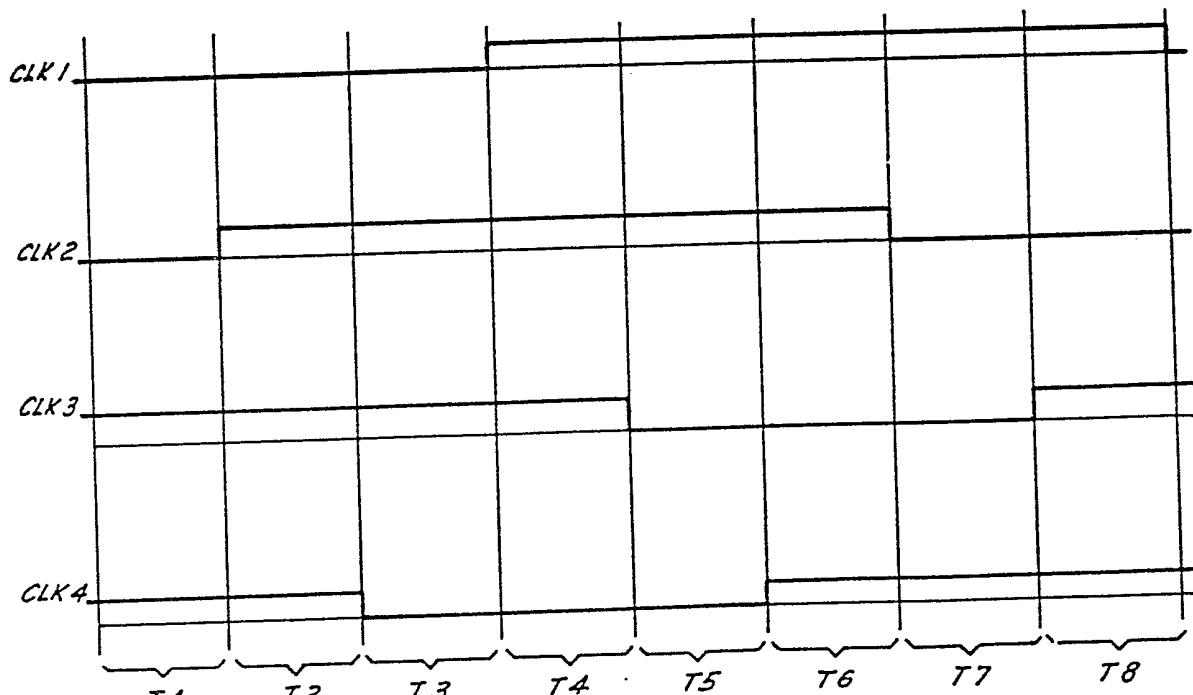

- La figure 4 est une représentation graphique du signal de commande nécessaire pour obliger le registre à décalage selon l'invention à transférer les données dans un second sens (inverse).

Comme le montre la figure 1, le mode préféré de réalisation de la présente invention est constitué par un registre à décalage comportant tout nombre désiré de positions de bits, qui sont chacune désignées par B. Chaque position de bit B

comprend quatre éléments actifs, désignés respectivement par  $A_1$ ,  $A_2$ ,  $A_3$  et  $A_4$ . Chaque élément actif A comporte une entrée de signal de commande, désignée respectivement par 5  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ , une entrée de données, désignée respectivement par  $D_1$ ,  $D_2$ ,  $D_3$ ,  $D_4$ , et une entrée de réaction, désignée respectivement par  $F_1$ ,  $F_2$ ,  $F_3$ ,  $F_4$ . Chaque élément actif A est représenté dans le schéma logique de la figure 1 avec un symbole NI du fait qu'un signal logique "1" appliqué soit à l'entrée de données D, soit à l'entrée de réaction F, soit aux deux entrées, 10 fait en sorte que l'élément actif produise à sa sortie un signal logique "0". D'autre part, si à la fois l'entrée de données D et l'entrée de réaction F se trouvent à l'état logique "0", l'élément actif produit à sa sortie un signal logique "1".

15 Chaque élément actif A est couplé en croix à la fois avec l'élément actif précédent et avec l'élément actif suivant. Ainsi, par exemple, la sortie de données de l'élément  $A_2$  est connectée avec l'entrée de données de l'élément  $A_3$  et avec l'entrée de données de l'élément  $A_1$ . L'entrée de données de 20 l'élément  $A_2$  est connectée avec la sortie de données de l'élément  $A_1$  ainsi qu'avec la sortie de données de l'élément  $A_3$ . C'est cette configuration de couplage en croix qui confère au registre à décalage selon l'invention sa caractéristique statique.

25 La figure 2 montre schématiquement la structure de chacun des éléments actifs  $A_1$  à  $A_4$ . Chacun des éléments actifs comprend un transistor injecteur, désigné respectivement par  $J_1$ ,  $J_2$ ,  $J_3$ ,  $J_4$ , et un transistor inverseur, désigné respectivement par  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ . Chaque transistor injecteur J est 30 un transistor PNP bipolaire qui agit comme une source de courant pour assurer une excitation de la base du transistor inverseur V auquel il est relié. Chaque transistor inverseur V est un transistor NPN bipolaire à émetteurs multiples qui fonctionne dans le mode inverse. Dans ce mode, les émetteurs NPN bipolaires 35 classiques fonctionnent comme des collecteurs.

L'émetteur 10 de chaque transistor injecteur J est connecté à l'entrée de signal de commande C de l'élément actif A

dont l'injecteur fait partie. La borne de commande ou base 12 de chaque transistor injecteur J est connectée à une source de potentiel donnée, dans ce cas la masse. Le collecteur 14 de chaque transistor injecteur J est connecté à la borne de 5 commande ou base 16 du transistor inverseur V, qui forme une partie de l'élément actif. La base 16 de chacun des transistors inverseurs est connectée à l'entrée de données D de l'élément actif dont le transistor inverseur fait partie.

Chaque transistor inverseur V comporte deux collecteurs 10 18 et 20. Chaque collecteur 18 est connecté à l'entrée de réaction F de l'élément actif A précédent suivant une séquence donnée. Chaque collecteur 20 de chaque transistor inverseur V est connecté à l'entrée de données D de l'élément actif suivant A suivant une séquence donnée. Chaque transistor 15 inverseur V comporte un émetteur 22 qui est connecté à une source de potentiel donnée, dans ce cas la masse. En conséquence, chaque élément actif A se compose d'un transistor injecteur J et d'un transistor inverseur V qui sont connectés fonctionnellement entre l'entrée de signal de commande et la masse. En 20 outre, chaque élément actif A est couplé en croix à la fois avec l'élément actif précédent et avec l'élément actif suivant.

Quatre composantes séparées de signal de commande sont nécessaires pour commander le mouvement des données au travers du registre. Une composante de signal de commande est établie 25 pour chaque élément actif A dans une position de bit B. Les quatre composantes du signal de commande, désignées respectivement par  $CLK_1$ ,  $CLK_2$ ,  $CLK_3$ ,  $CLK_4$ , sont appliquées aux entrées respectives de signal de commande  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ , à partir d'un générateur de signal de commande, désigné dans son 30 ensemble par G. Ce générateur de signal de commande G peut être constitué de quatre générateurs d'impulsions d'horloge classiques, qui produisent chacun un signal d'horloge CLK, et d'un moyen de synchronisation du fonctionnement des générateurs d'impulsions d'horloge dans une séquence temporelle ou un ordre 35 prédéterminé. Le générateur de signaux de commande G peut être également constitué de structures différentes, bien connues dans ce domaine et utilisées pour produire des signaux multiples

de ce type.

Comme mentionné précédemment, le sens de transfert des données au travers du registre à décalage est déterminé uniquement par la séquence temporelle ou l'ordre temporel des composantes de signal de commande. En conséquence, si le générateur de signaux de commande comprend quatre générateurs séparés d'impulsions d'horloge, la séquence ou l'ordre des composantes du signal de commande peut être déterminé d'une façon simple par un déclenchement successif des générateurs de signaux d'horloge à des instants déterminés en concordance avec des signaux provenant d'une horloge principale. Ainsi, par exemple, le signal d'horloge  $CLK_1$  peut être déclenché à un instant particulier (par exemple T) qui est déterminé par une horloge principale, le signal d'horloge  $CLK_2$  peut être déclenché d'une unité de temps ( $T + 1$ ) après l'instant défini par l'horloge principale, le signal d'horloge  $CLK_3$  peut être déclenché deux unités de temps ( $T + 2$ ) après l'instant déterminé par l'horloge principale, tandis que le signal d'horloge  $CLK_4$  peut être déclenché trois unités de temps ( $T + 3$ ) après l'instant déterminé par l'horloge principale. Pour inverser le sens de transfert des données, les signaux d'horloge sont simplement déclenchés dans la séquence opposée. Par exemple, le signal d'horloge  $CLK_4$  est déclenché à l'instant (T) déterminé par l'horloge principale, le signal d'horloge  $CLK_3$  est déclenché une unité de temps ( $T + 1$ ) après, le signal d'horloge  $CLK_2$  est déclenché deux unités de temps ( $T + 2$ ) après, tandis que le signal d'horloge  $CLK_1$  est déclenché trois unités de temps ( $T + 3$ ) après. Lorsque cette dernière séquence est utilisée, le transfert des données dans le registre à décalage s'effectue dans un sens qui est l'inverse du sens de transfert des données pour la première séquence.

Pour résoudre ce problème, il est prévu une horloge principale, désignée dans son ensemble par M et qui est connectée à un générateur de signaux de commande G par l'intermédiaire d'un circuit de commande de sens, désigné dans son ensemble par H. Ce circuit de commande de sens H détermine la séquence de déclenchement des quatre générateurs d'impulsions d'horloge du

générateur de signal de commande G, en concordance avec la sortie de l'horloge principale M.

Un circuit de commande de remise à zéro, désigné dans son ensemble par R, est également connecté à une entrée du circuit de commande de sens H. Lorsque le circuit de commande de remise à zéro R est activé, le circuit de commande de sens H oblige chacun des générateurs d'impulsions d'horloge du générateur de signaux de commande G à arrêter la génération des impulsions d'horloge pendant un temps prédéterminé (plus long que le temps de retard de la charge emmagasinée) et, ensuite, le circuit de commande de sens H fait en sorte que les générateurs d'impulsions d'horloge du générateur de signal de commande G soient redéclenchés dans la séquence correcte. Il résulte de ce processus que l'ensemble du registre à décalage est automatiquement remis à zéro.

Pour bien comprendre le fonctionnement du registre à décalage selon l'invention, il est nécessaire de considérer la nature des composantes du signal de commande ainsi que la manière dont ceux-ci assurent le transfert des données d'un élément actif au suivant à l'intérieur du registre à décalage. Dans ce but, on a mis en évidence sur les Figures 3 et 4 des représentations graphiques de deux séquences différentes du signal de commande. La séquence de signal de commande représentée sur la Figure 3 assure le transfert des données dans le registre à décalage dans le sens direct (c'est-à-dire de la gauche vers la droite en regardant les Figures 1 et 2). Inversement, la séquence de signal de commande représentée sur la Figure 4 assure le transfert des données dans le registre de décalage dans le sens inverse, c'est-à-dire de la droite vers la gauche, en regardant les Figures 1 et 2.

Dans chaque cas, les signaux de commande sont représentés dans huit créneaux de temps  $T_1$  à  $T_8$ , et les signaux engendrés par les quatre horloges sont en condition de chevauchement avec les signaux engendrés par les autres horloges. Cette forme a été choisie pour faciliter l'explication, mais il va de soi que la présente invention n'est pas limitée aux séquences particulières de signal de commande qui ont été

représentées. En fait, on peut adopter d'autres séquences de signal de commande, en fonction de l'application envisagée pour le registre à décalage. Par exemple, au lieu de huit créneaux de temps, on pourrait utiliser quatre créneaux de temps. En outre, on pourrait faire intervenir des impulsions ne se chevauchant pas, à la place des impulsions qui se chevauchent comme sur les figures.

Chaque générateur de signal d'horloge engendre un train d'impulsions qui se compose d'une série d'impulsions positives (niveau haut), ayant chacune une durée correspondant à cinq créneaux de temps, entre lesquels il existe des périodes de pause (niveau bas) ayant chacune une durée correspondant à trois créneaux de temps. Dans l'exemple considéré, chaque générateur de signal d'horloge opère deux créneaux de temps en avant du générateur de signal d'horloge suivant. Par exemple, si  $CLK_1$  passe au niveau haut au début du sixième créneau temporel  $T_6$ ,  $CLK_2$  passe au niveau haut au début du huitième créneau temporel  $T_8$ ,  $CLK_3$  passe au niveau haut au début du second créneau temporel  $T_2$  et  $CLK_4$  passe au niveau haut au début du quatrième créneau temporel  $T_4$ , etc... Dans le mode inverse, comme indiqué sur la Figure 4, les trains d'impulsions sont précisément identiques à ce qui a été décrit ci-dessus, excepté qu'ils sont déclenchés dans la séquence opposée. Ainsi, si  $CLK_4$  passe au niveau haut au début du sixième créneau temporel  $T_6$ ,  $CLK_3$  passe au niveau haut au début du huitième créneau temporel  $T_8$ ,  $CLK_2$  passe au niveau haut au début du second créneau temporel  $T_2$ , et  $CLK_1$  passe au niveau haut au début du quatrième créneau temporel  $T_4$ , etc...

L'application d'une impulsion positive à l'entrée de signal de commande C d'un élément actif A produit son excitation. L'absence d'une impulsion positive (niveau bas) provoque une désexcitation de l'élément actif. Cela s'explique par le fait que l'excitation de base de chaque transistor inverseur V est assurée par le transistor injecteur J qui joue le rôle d'une source de courant. Cependant, le transistor injecteur J agit seulement comme une source de courant si un potentiel positif est appliqué à son émetteur 10. En conséquence, si une

impulsion positive n'est pas appliquée à l'émetteur 10 du transistor injecteur d'un élément actif A particulier, l'ensemble de l'élément actif est désexcité et ne remplit aucune fonction.

5 En considérant la séquence de commande indiquée sur la figure 3, on va supposer que, avant le créneau temporel  $T_1$ , un signal logique L (niveau logique "1" ou niveau logique "0"), est appliqué à l'entrée de données  $D_1$  de l'élément actif  $A_1$ . Pendant le créneau temporel  $T_1$ , les signaux d'horloge  $CLK_1$  et

10  $CLK_2$  sont au niveau haut, tandis que les signaux d'horloge  $CLK_3$  et  $CLK_4$  sont au niveau bas. Les éléments actifs  $A_1$  et  $A_2$  sont par conséquent excités, tandis que les éléments actifs  $A_3$  et  $A_4$  sont désexcités. L'excitation de l'élément actif  $A_1$  provoque l'inversion du signal de données L et son application

15 à l'entrée de données  $D_2$  de l'élément actif suivant  $A_2$  sous la forme  $\bar{L}$ . Par exemple, si L se trouve au niveau logique "1", le transistor inverseur  $V_1$  est rendu conducteur, ce qui provoque la mise à la masse de son collecteur 20 par l'intermédiaire de l'émetteur 22. En conséquence, un niveau logique "0" apparaît à l'entrée de données  $D_2$ . Un niveau logique "0" appliqué

20 à l'entrée de données  $D_2$  maintient le transistor inverseur  $V_2$  dans la condition de blocage, de sorte qu'un signal L de niveau logique "1" apparaît à l'entrée de données  $D_3$ . En conséquence, le signal de données L d'origine a été deux fois

25 inversé, et il apparaît à nouveau sous la forme L.

Pendant le créneau temporel  $T_2$ ,  $CLK_1$ ,  $CLK_2$  restent au niveau haut,  $CLK_3$  passe au niveau haut et  $CLK_4$  est encore au niveau bas. Lorsque  $CLK_3$  passe au niveau haut, l'élément actif  $A_3$  est excité, et le signal appliqué à l'entrée de données  $D_3$  (L) est inversé par l'inverseur  $V_3$ , de sorte que  $\bar{L}$  apparaît à l'entrée de données  $D_4$  de l'élément actif  $A_4$ . Pendant le troisième créneau temporel  $T_3$ ,  $CLK_1$  passe au niveau bas, en désexcitant l'élément actif  $A_1$ , en effaçant des données continues dans celui-ci,  $CLK_2$ ,  $CLK_3$  restent au niveau haut, tandis que

30  $CLK_4$  reste au niveau bas. Pendant le créneau temporel  $T_3$ , les données restent dans la condition où elles étaient pendant le créneau

35

temporel  $T_2$  (c'est-à-dire qu'elles n'avancent pas), c'est-à-dire qu'un état L apparaît à l'entrée de données  $D_3$  et qu'un état  $\bar{L}$  apparaît à l'entrée de données  $D_4$ .

Pendant le quatrième créneau temporel  $T_4$ ,  $CLK_1$  reste au niveau bas en maintenant l'élément actif  $A_1$  dans l'état désexcité et les signaux d'horloge  $CLK_2$ ,  $CLK_3$  restent au niveau haut, tandis que  $CLK_4$  passe au niveau haut, ce qui provoque l'inversion de l'état logique  $\bar{L}$  existant à l'entrée de données  $D_4$  par l'intermédiaire du transistor inverseur  $V_4$ , cet état apparaissant sous la forme L au collecteur 20 du transistor inverseur  $V_4$ . En conséquence, au bout de quatre créneaux temporels, les données ont traversé la position de bit et elles apparaissent sous leur forme d'origine à la sortie du dernier élément de la position de bit. Pendant le créneau temporel  $T_5$  suivant,  $CLK_1$  reste au niveau bas,  $CLK_2$  passe au niveau bas, tandis que  $CLK_3$  et  $CLK_4$  restent au niveau haut. Pendant ce créneau, il ne se produit aucun transfert, L restant à la sortie de l'élément actif  $A_4$  et  $\bar{L}$  restant à la sortie de l'élément actif  $A_3$ . Cependant, l'élément actif  $A_2$  est désexcité.

Pendant le créneau temporel  $T_6$  suivant,  $CLK_1$  passe au niveau haut,  $CLK_2$  reste au niveau bas et  $CLK_3$  et  $CLK_4$  restent au niveau haut. Pendant ce créneau temporel, un second signal de données S (qui peut avoir l'état logique "1" ou l'état logique "0") peut être appliqué à l'entrée de données  $D_1$  pour l'élément actif  $A_1$ . Le transistor inverseur  $V_1$  inverse le second signal logique S de sorte que  $\bar{S}$  apparaît à l'entrée de données  $D_2$  de l'élément actif  $A_2$ . Les états logiques  $\bar{L}$  et L restent dans leurs états précédents, respectivement aux sorties des éléments actifs  $A_3$  et  $A_4$ . Pendant ce créneau temporel, le premier élément actif  $A_1$  de la position de bit suivante (non représentée) est excité, en provoquant l'inversion de L à la sortie de  $A_4$  pour former  $\bar{L}$  à l'entrée de  $A_2$  de la position de bit suivante.

Pendant le créneau temporel  $T_7$  suivant,  $CLK_1$  reste au niveau haut,  $CLK_2$  reste au niveau bas,  $CLK_3$  passe au niveau bas, tandis que  $CLK_4$  reste au niveau haut. Pendant ce créneau temporel, l'état inversé  $\bar{S}$  du second signal logique reste à

l'entrée de données  $D_2$  de l'élément actif  $A_2$ . Cet élément actif  $A_2$  est désexcité, de sorte qu'il n'agit plus pour réinverser le second signal de données à ce moment. L'élément actif  $A_3$  est désexcité en effaçant les données qu'il contient.

5 L'état de la sortie de l'élément actif  $A_4$  ( $L$ ) reste inchangé, de même que l'état ( $\bar{L}$ ) du premier élément actif (non représenté) de la position de bit suivante.

Pendant le créneau temporel  $T_8$  suivant,  $CLK_1$  reste au niveau haut,  $CLK_2$  passe au niveau haut,  $CLK_3$  reste au niveau bas, tandis que  $CLK_4$  reste au niveau haut. En conséquence,

10 l'état inversé du second signal logique  $\bar{S}$  appliqué à l'entrée de données  $D_2$ , est maintenant réinversé par le transistor inverseur  $V_2$ , et il apparaît sous la forme  $S$  à l'entrée de données  $D_3$  de l'élément actif  $A_3$ . Cependant, l'élément actif

15  $A_3$  est désexcité, et ne produit par conséquent pas une inversion du second signal logique appliquée à son entrée de données  $D_3$  à ce moment. L'état logique de l'élément actif  $A_4$  reste inchangé.

Une opération identique se produit dans la position de

20 bit suivante, avec inversion du signal  $\bar{L}$  appliqué à l'entrée de données  $D_2$  et qui apparaît sous la forme  $L$  à l'entrée de données  $D_3$ . A la fin du créneau temporel  $T_8$ , le cycle reprend avec le créneau  $T_1$ . On comprend bien maintenant comment le signal de commande assure le transfert des données au travers

25 des éléments actifs du registre de décalage dans le sens direct.

Il est important de noter que la sortie de chaque élément actif est renvoyée à l'entrée de l'élément actif précédent, de sorte que, si la fréquence du signal de commande se rapproche de zéro, les données contenues dans le registre

30 à décalage sont conservées (bien qu'elles ne soient pas décalées). Les interconnexions de réaction agissent de manière à conserver les données par un renforcement de l'entrée de données pour chaque élément actif excité. Par exemple, le signal logique apparaissant à la sortie de l'élément actif  $A_3$

35 est renvoyé à l'entrée de données de l'élément actif  $A_2$  et il renforce le signal logique agissant sur celui-ci avec le même signal logique que celui appliqué à partir de la sortie

- de l'élément actif  $A_1$ . La sortie de l'élément actif  $A_3$  est la version doublement inversée du signal logique apparaissant à la sortie de l'élément actif  $A_1$ . La version doublement inversée d'un signal logique est constituée par le signal logique proprement dit. En conséquence, la sortie de données d'un élément actif est identique à l'entrée de données de l'élément actif précédent. Une réaction se produit par l'intermédiaire de chaque collecteur 18 qui est connecté à l'entrée de réaction  $F$  de l'élément actif précédent.

- 5 Pour inverser le sens de transfert des données au travers du registre à décalage, il suffit d'engendrer la même séquence d'impulsions d'horloge, mais dans l'ordre inverse. Les signaux de commande nécessaires pour assurer le transfert des données au travers du registre à décalage dans le sens inverse ont été 10 représentés graphiquement sur la figure 4.

- Pendant le premier créneau temporel  $T_1$ ,  $CLK_1$  et  $CLK_2$  sont au niveau bas, ce qui provoque une désexcitation des éléments actifs  $A_1$  et  $A_2$ , tandis que  $CLK_3$  et  $CLK_4$  sont au niveau haut, en indiquant que les éléments actifs  $A_3$  et  $A_4$  15 sont excités. On va supposer que, pendant le créneau temporel  $T_1$ , un premier signal logique  $L$  a été appliqué à l'entrée de réaction  $F_4$  de l'élément actif  $A_4$ . Ce signal  $L$  est inversé dans un inverseur  $V_4$  et le résultat de l'inversion, correspondant à la forme  $\bar{L}$ , est appliqué à l'entrée de réaction  $F_3$  20 de l'élément actif  $A_3$ . L'inverseur  $V_3$  inverse le signal logique qui est appliqué à sa base 16 et il le ramène dans le même état logique  $L$  que celui appliqué à l'entrée de données  $D_4$  25 de l'élément actif  $A_4$ , ce qui renforce ainsi l'entrée de réaction.

- 30 Pendant le créneau temporel  $T_2$  suivant,  $CLK_1$  reste au niveau bas,  $CLK_2$  passe au niveau haut, tandis que  $CLK_3$  et  $CLK_4$  restent au niveau haut. En conséquence, l'élément actif  $A_2$  est excité de manière que l'état logique  $L$ , appliqué par l'intermédiaire de l'entrée de réaction  $F_2$ , soit inversé par 35 l'inverseur  $V_2$  et devienne  $\bar{L}$  à l'entrée de données  $D_3$  de l'élément actif  $A_3$ , en assurant ainsi le renforcement de son entrée.

Pendant le créneau temporel  $T_3$  suivant,  $CLK_1$  reste au niveau bas,  $CLK_2$  et  $CLK_3$  restent au niveau haut, tandis que  $CLK_4$  passe au niveau bas, en provoquant ainsi la désexcitation de l'élément actif  $A_4$ . Les états logiques des éléments actifs  $A_2$  et  $A_3$  restent inchangés.

Pendant le créneau temporel  $T_4$  suivant,  $CLK_1$  passe au niveau haut,  $CLK_2$  et  $CLK_3$  restent au niveau haut, tandis que  $CLK_4$  reste au niveau bas. En conséquence, pendant ce créneau  $T_4$ , l'élément actif  $A_1$  est excité, de sorte que le signal logique  $\bar{L}$  qui lui est appliqué par l'intermédiaire de l'entrée de réaction  $F_1$  à partir de la sortie de l'élément actif  $A_2$  est inversé par l'inverseur  $V_1$  et apparaît dans l'état logique  $L$  à l'entrée de données  $D_2$ .

Pendant le créneau temporel  $T_5$  suivant,  $CLK_1$  et  $CLK_2$  restent au niveau haut,  $CLK_3$  passe au niveau bas, tandis que  $CLK_4$  reste au niveau bas. En conséquence, les éléments actifs  $A_3$  et  $A_4$  sont désexcités, et les éléments actifs  $A_1$  et  $A_2$  restent excités, les états logiques étant inchangés.

Pendant le créneau temporel  $T_6$  suivant,  $CLK_1$  et  $CLK_2$  sont au niveau haut,  $CLK_3$  reste au niveau bas, tandis que  $CLK_4$  passe au niveau haut, en assurant l'excitation de l'élément actif  $A_4$  qui reçoit maintenant un second signal logique  $S$  à son entrée de réaction  $F_4$ .  $S$  est inversé dans l'inverseur  $V_4$  et, en conséquence, un état logique  $\bar{S}$  apparaît à l'entrée de réaction  $F_3$  de l'élément actif  $A_3$ . Les états logiques des éléments actifs  $A_1$  et  $A_2$  restent inchangés. L'état logique  $L$  est transféré à l'élément actif  $A_4$  de la position de bit précédente.

Pendant le créneau temporel  $T_7$  suivant,  $CLK_1$  reste au niveau haut,  $CLK_2$  passe au niveau bas,  $CLK_3$  reste au niveau bas, tandis que  $CLK_4$  reste au niveau haut. En conséquence, l'élément actif  $A_2$  est désexcité mais aucune donnée n'est transférée.

Dans le créneau temporel  $T_8$  suivant,  $CLK_1$  reste au niveau haut,  $CLK_2$  reste au niveau bas,  $CLK_3$  passe au niveau haut, tandis que  $CLK_4$  reste au niveau haut. En conséquence, l'élément actif  $A_3$  reste excité, en provoquant à nouveau une inversion

du second signal logique  $\bar{S}$  qui passe à l'état S à l'entrée de réaction  $F_2$  de l'élément actif  $A_2$ . En outre, l'état logique du premier signal logique est transféré de l'élément  $A_4$  à l'élément  $A_3$  de la position de bit précédente. Il est à noter que, par 5 une simple inversion de la séquence des signaux d'horloge, des données peuvent être transférées dans le sens inverse dans le registre à décalage.

En conséquence, la présente invention se rapporte à un registre à décalage statique, qui peut être réalisé conformément à la technologie  $I^2L$  et qui utilise des unités  $I^2L$  identiques de construction simple comme éléments actifs. Le registre à décalage est bidirectionnel et le sens de transmission des données est déterminé uniquement par la séquence temporelle des composantes du signal de commande qui est appliquée. En conséquence, il n'est pas nécessaire de prévoir des lignes externes de commande de sens de transfert de données. En outre, la remise à zéro du registre à décalage est effectuée simplement en faisant passer simultanément au niveau bas toutes les composantes du signal de commande, puis en 10 redéclenchant la séquence de signal de commande. Aucun dispositif d'isolation n'est nécessaire entre les éléments actifs du registre à décalage. L'élimination des dispositifs d'isolation, des lignes de commande de sens de transfert de données et des lignes de commande de remise à zéro, fait en sorte 15 qu'on obtient une structure simplifiée permettant une augmentation de la densité par surface unitaire de pastille.

Bien entendu, la présente invention n'est nullement limitée aux modes de réalisation décrits et représentés ; elle est susceptible de nombreuses variantes accessibles à 20 l'homme de l'art, suivant les applications envisagées et sans que l'on ne s'écarte de l'esprit de l'invention.

REVENDICATIONS

1. Registre à décalage, comprenant une position de bit (B), qui comporte un nombre donné d'éléments actifs (A) connectés fonctionnellement en série, un moyen (G) pour produire un signal de commande comprenant plusieurs composantes (CLK), chacune desdites composantes (CLK) étant appliquée en fonctionnement à un élément différent (A) dudit nombre et contenant au moins une impulsion agissant, lorsqu'elle est présente, pour exciter l'élément (A) auquel elle est appliquée, pendant sa durée, caractérisé en ce que chaque élément (A) comprend une unité  $I^2L$  (J, V), et en ce que chaque élément (A) est couplé en croix avec un élément adjacent (A).

2. Registre à décalage selon la revendication 1, caractérisé en ce que lesdites composantes (CLK) sont engendrées dans une séquence temporelle donnée, et en ce que ladite séquence temporelle détermine le sens de transfert des données au travers de ladite position de bit.

3. Registre à décalage selon la revendication 2, caractérisé en ce qu'il est conçu pour qu'une inversion de ladite séquence temporelle produise une inversion du sens de transfert des données au travers de ladite position de bit.

4. Registre à décalage selon la revendication 1, comprenant en outre un moyen (R) pour la remise à zéro de ladite position de bit (B), caractérisé en ce que ce moyen de remise à zéro (R) comporte un moyen pour désactiver le générateur de signaux de commande (G) pendant un intervalle de temps donné, puis pour le redéclencher.

5. Registre à décalage selon la revendication 1, caractérisé en ce que chacune desdites composantes (CLK) comprend un train d'impulsions.

6. Registre à décalage selon la revendication 5, caractérisé en ce que lesdits trains d'impulsions se chevauchent.

7. Registre à décalage selon la revendication 5, caractérisé en ce que lesdits trains d'impulsions ne se chevauchent pas.

8. Registre à décalage selon la revendication 1, dans lequel chacun desdits éléments (A) comporte une entrée de

données (D) et une sortie de données, caractérisé en ce que l'entrée de données (D) de chaque élément (A) est connectée en fonctionnement à la sortie de données de l'élément précédent (A) et en ce que la sortie de données de chaque élément 5 (A) est connectée en service à l'entrée de données (D) de l'élément précédent (A).

9. Registre à décalage selon la revendication 1, dans lequel chacun desdits éléments (A) comporte une entrée de données (D) et une sortie de données, caractérisé en ce que 10 la sortie de données de chaque élément (A) est connectée en fonctionnement à l'entrée de données (D) de l'élément suivant (A) et en ce que l'entrée de données (D) de chaque élément (A) est connectée en fonctionnement à la sortie de données de l'élément suivant.

15 10. Registre à décalage selon la revendication 1, dans lequel chacun desdits éléments (A) comporte une entrée de données (D) et une sortie de données, caractérisé en ce que l'entrée de données de chaque élément (A) est connectée en fonctionnement à la sortie de données de l'élément précédent, 20 ainsi qu'à la sortie de données de l'élément suivant.

11. Registre à décalage selon la revendication 1, caractérisé en ce que chaque élément (A) est couplé en croix avec les deux éléments adjacents (A).

12. Registre à décalage selon la revendication 1, caractérisé en ce que chaque élément (A) comprend une entrée de signal de commande (C) qui est connectée en fonctionnement audit générateur de signaux de commande (G) de manière à recevoir une composante différente (CLK) dudit signal de commande.

30 13. Registre à décalage selon la revendication 1, caractérisé en ce que chacun desdits éléments (A) comprend une entrée de signal de commande (C), un transistor inverseur (V) et un transistor injecteur (J), ledit transistor inverseur (V) et ledit transistor injecteur J étant connectés en 35 fonctionnement entre ladite entrée de signal de commande (C) et une source d'un potentiel donné.

14. Registre à décalage selon la revendication 13, carac-

térisé en ce que ladite source est la masse.

15. Registre à décalage selon la revendication 13, dans lequel ledit transistor injecteur (J) comprend une borne de commande (12) et une première et une seconde borne (10, 14),

5 caractérisé en ce que ladite borne de commande (12) est connectée à une source de potentiel donné, en ce que la première borne (10) est connectée à ladite entrée de signal de commande (C) et en ce que la seconde borne (14) est connectée au transistor inverseur (J).

10 16. Registre à décalage selon la revendication 15, caractérisé en ce que ladite source est la masse.

17. Registre à décalage selon la revendication 15, caractérisé en ce que la première borne (10) du transistor injecteur (J) est l'émetteur.

15 18. Registre à décalage selon la revendication 15, caractérisé en ce que la seconde borne (14) du transistor injecteur (J) est le collecteur.

20 19. Registre à décalage selon la revendication 13, caractérisé en ce que le transistor inverseur (V) comprend une borne de commande ainsi qu'une première, une seconde et une troisième borne (18, 20, 22), en ce que la borne de commande (16) du transistor inverseur (V) est connectée en fonctionnement au transistor injecteur (J), en ce que la première borne (18) du transistor inverseur est connectée à l'élément précédent (A), en ce que la seconde borne (20) du transistor inverseur est connectée à l'élément suivant (A) et en ce que la troisième borne (22) du transistor inverseur est connectée à une source d'un potentiel donné.

25

20 20. Registre à décalage selon la revendication 19, caractérisé en ce que ladite source est la masse.

21. Registre à décalage selon la revendication 19, caractérisé en ce que lesdites première et seconde bornes (18, 20) du transistor inverseur sont des collecteurs.

35 22. Registre à décalage selon la revendication 19, caractérisé en ce que ladite troisième borne (22) du transistor inverseur est un émetteur.

23. Registre à décalage selon la revendication 19, caractérisé en ce que ledit élément (A) comporte une entrée de

données (D) et en ce que la borne de commande (16) du transistor inverseur est connectée à ladite entrée de données (D).

24. Registre à décalage selon la revendication 15, caractérisé en ce que ledit transistor inverseur (V) comprend une 5 borne de commande (16) et des première, seconde et troisième bornes (18, 20, 22), en ce que la borne de commande (16) dudit transistor inverseur (V) est connectée au transistor injecteur (J), en ce que la première borne (18) du transistor inverseur est connectée à l'élément précédent (A), en ce que 10 la seconde borne (20) du transistor inverseur est connectée à un élément suivant (A), et en ce que la troisième borne (22) du transistor inverseur est connectée à une source d'un potentiel donné.

25. Registre à décalage selon la revendication 1, caractérisé en ce que chaque position de bit (B) contient un nombre 15 donné d'unités  $I^2L$  (A) et en ce que ledit signal de commande comprend ledit nombre donné de composantes (CLK).

26. Registre à décalage selon la revendication 25, caractérisé en ce que chacune desdites composantes (CLK) comprend 20 au moins une impulsion d'horloge positive.

27. Registre à décalage selon la revendication 26, caractérisé en ce que la séquence desdites impulsions détermine l'ordre d'excitation desdits éléments (A).

28. Registre à décalage selon la revendication 26, caractérisé en ce que la durée desdites impulsions détermine la 25 durée d'excitation desdits éléments (A).

FIG. 1

FIG. 2

FIG. 3

FIG. 4