(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 603 16 760 T2 2008.07.17**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 416 487 B1**

(21) Deutsches Aktenzeichen: **603 16 760.8**

(96) Europäisches Aktenzeichen: **03 254 643.4**

(96) Europäischer Anmeldetag: **25.07.2003**

(97) Erstveröffentlichung durch das EPA: **06.05.2004**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **10.10.2007**

(47) Veröffentlichungstag im Patentblatt: **17.07.2008**

(51) Int Cl.<sup>8</sup>: **G11B 20/10 (2006.01)**

**G11B 7/125 (2006.01)**

**G11B 7/0045 (2006.01)**

(30) Unionspriorität:

**2002313623 29.10.2002 JP**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**Hitachi, Ltd., Tokyo, JP; Intersil Corp., Yokohama, JP; Hitachi-LG Data Storage, Inc., Tokio/Tokyo, JP**

(72) Erfinder:

**Nishimura, Koichiro, Tokyo 100-8220, JP; Kaku, Toshimitsu, Tokyo 100-8220, JP**

(74) Vertreter:

**Strehl, Schübel-Hopf & Partner, 80538 München**

(54) Bezeichnung: **Optischer Plattenapparat und Verfahren zur Phasenjustierung**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine integrierte Lasertreiberschaltung zum Erzeugen einer Schreibstrategie anhand auf einem Aufzeichnungsmedium aufgezeichneter binärer Aufzeichnungssignale und Aufzeichnungstakte zur Verwendung mit einem optischen Plattenapparat mit einer Aufzeichnungsfähigkeit und einen optischen Plattenapparat, in den die integrierte Lasertreiberschaltung aufgenommen ist.

**[0002]** In den letzten Jahren ist die Geschwindigkeit der Aufzeichnung auf optischen Platten angestiegen. Wenn modulierte Daten mit hoher Geschwindigkeit auf einer optischen Platte aufzuzeichnen sind, muss ein Lasersteuersignal zu einem Lasertreiber gesendet werden, um eine für die aufzuzeichnenden Daten geeignete Schreibstrategie zu implementieren. Bei einem bekannten Verfahren zum Steuern der Signalübertragung, das in JP-A 283249/1999 oder in US-A-6 483 791 offenbart ist, werden die NRZ-Signale und Aufzeichnungstaktsignale, die von der Datenmodulation abgeleitet werden, einem Lasertreiber zugeführt, der dann intern eine Schreibstrategie anhand der NRZ-Signale und der Aufzeichnungstaktsignale erzeugt.

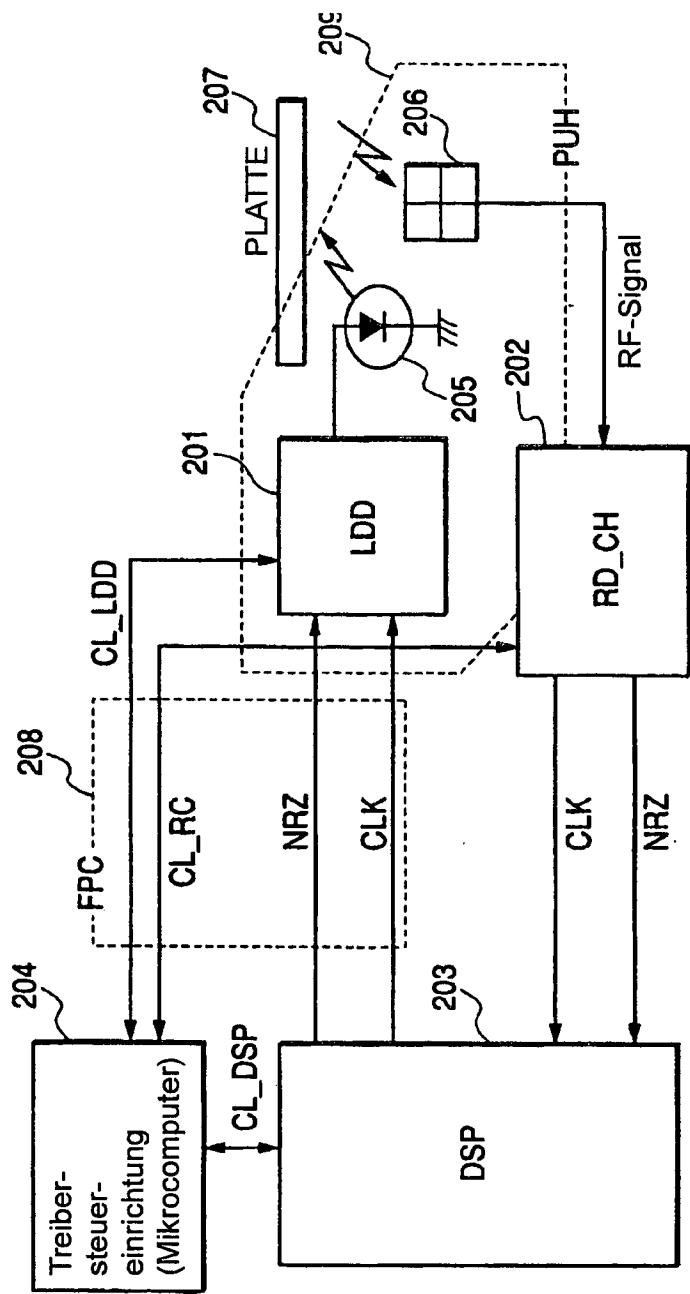

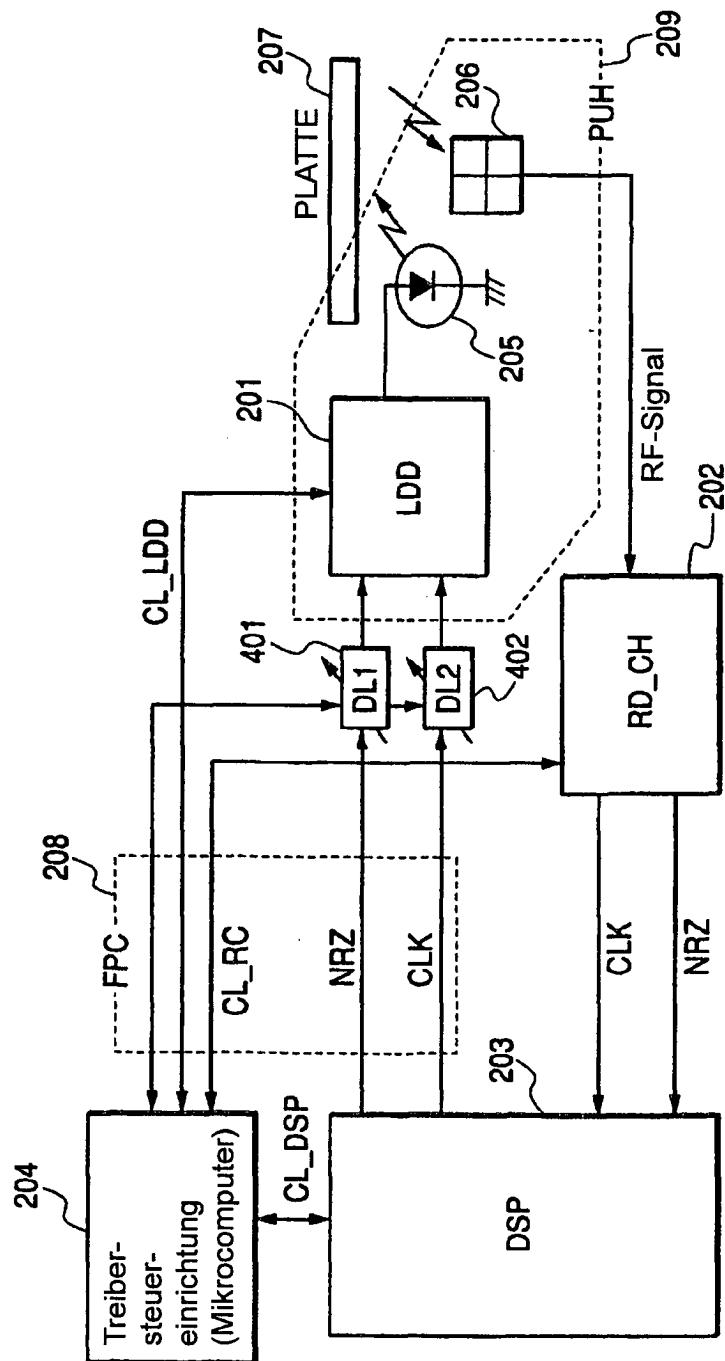

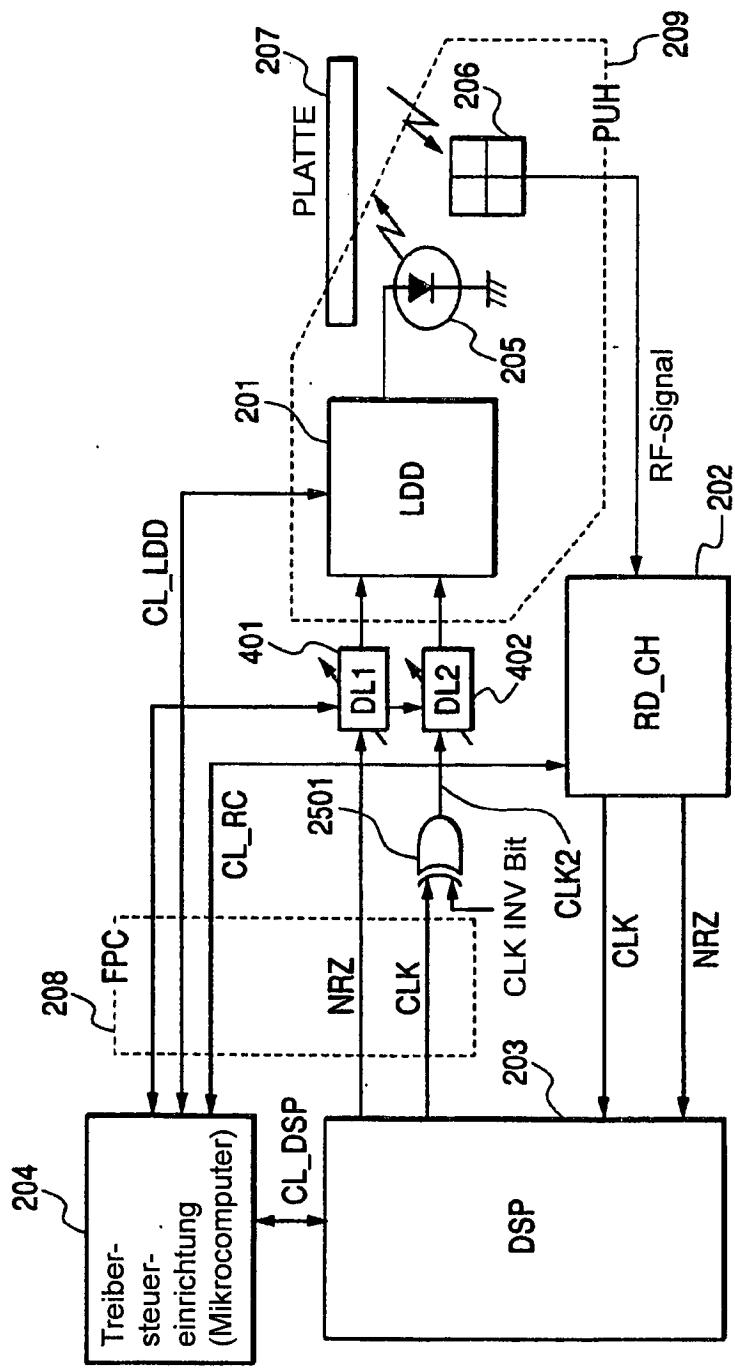

**[0003]** [Fig. 2](#) zeigt einen optischen Plattenapparat, der in US-A-6 483 791 beschrieben ist. Wie in dieser Figur dargestellt ist, erzeugt ein digitaler Signalprozessor (nachstehend als DSP bezeichnet) 203, der eine Signalmodulationsschaltung enthält, ein Aufzeichnungstaktsignal (nachstehend als ein CLK-Signal bezeichnet) und ein NRZ-Signal anhand eines Aufzeichnungssignals, das von einem Host oder einer Vorrichtung höherer Ebene (nicht dargestellt) zugeführt wird. Die erzeugten Signale CLK und NRZ werden dann in einen Lasertreiber 201 eingegeben, der über ein flexibles Kabel (nachstehend als FPC bezeichnet) 208 oberhalb eines Aufnahmekopfs (nachstehend als PUH bezeichnet) 209 montiert ist. Entsprechend dem eingegebenen NRZ-Signal zeichnet der Lasertreiber 201 ein Signal auf einer optischen Platte 207 auf, indem er so steuert, dass eine Laserdiode 205 Licht mit einem Aufzeichnungsleistungspegel emittiert. Wenn das aufgezeichnete Signal wiederzugeben ist, wird die Laserdiode 205 so gesteuert, dass sie Licht mit einem Wiedergabeleistungspegel emittiert. Das emittierte Licht wird dann durch die Platte 207 reflektiert, von einem Photodetektor 206 empfangen und einer photoelektrischen Wandlung unterzogen. Ein RF-Signal wird als Ergebnis der photoelektrischen Wandlung erhalten und in eine Lesekanalschaltung 202 eingegeben. Die Lesekanalschaltung 202 erzeugt einen Wiedergabetakt und ein NRZ-Wiedergabesignal anhand des eingegebenen RF-Signals und gibt sie in den vorstehend erwähnten DSP 203 ein. Der DSP 203 demoduliert den erhaltenen Wiedergabetakt und das NRZ-Wie-

derabesignal zu Wiedergabedaten und sendet sie zum Host oder einer anderen Vorrichtung höherer Ebene (nicht dargestellt).

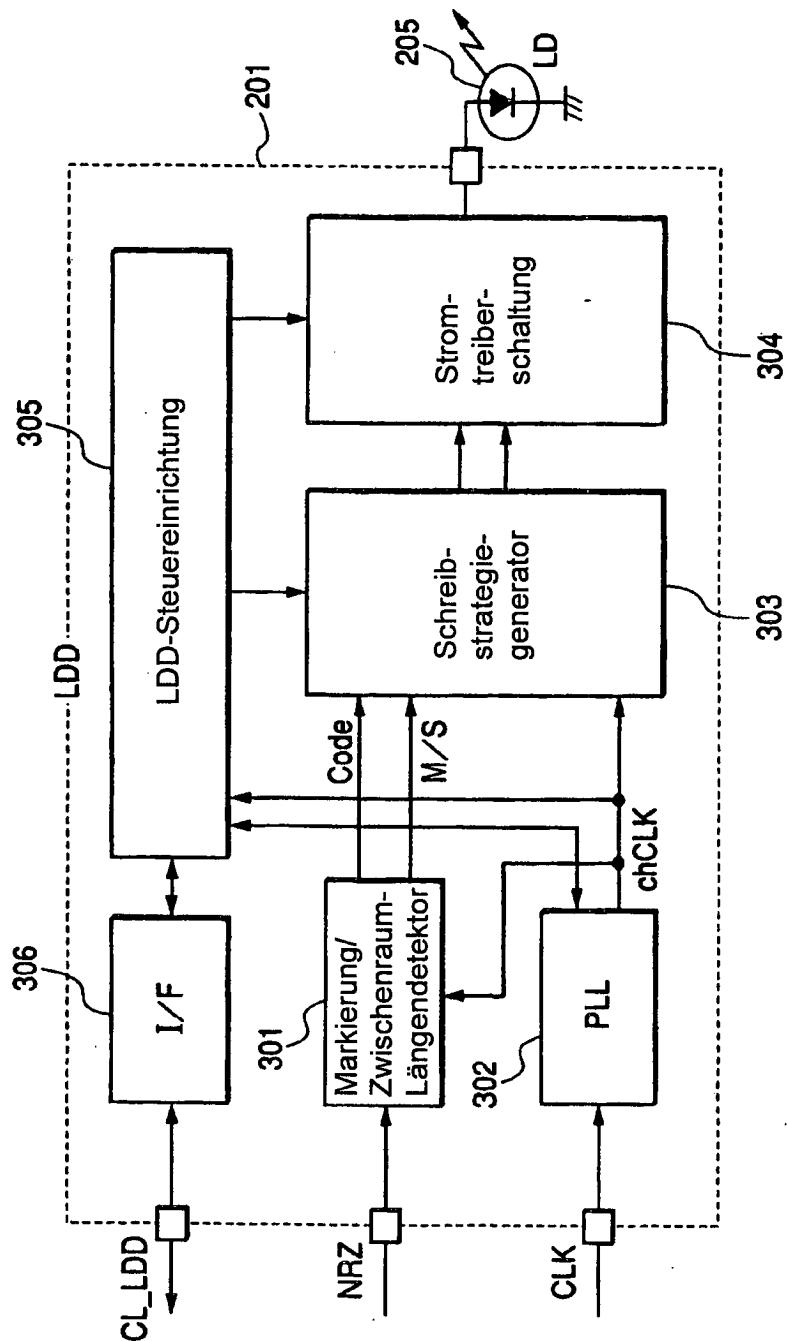

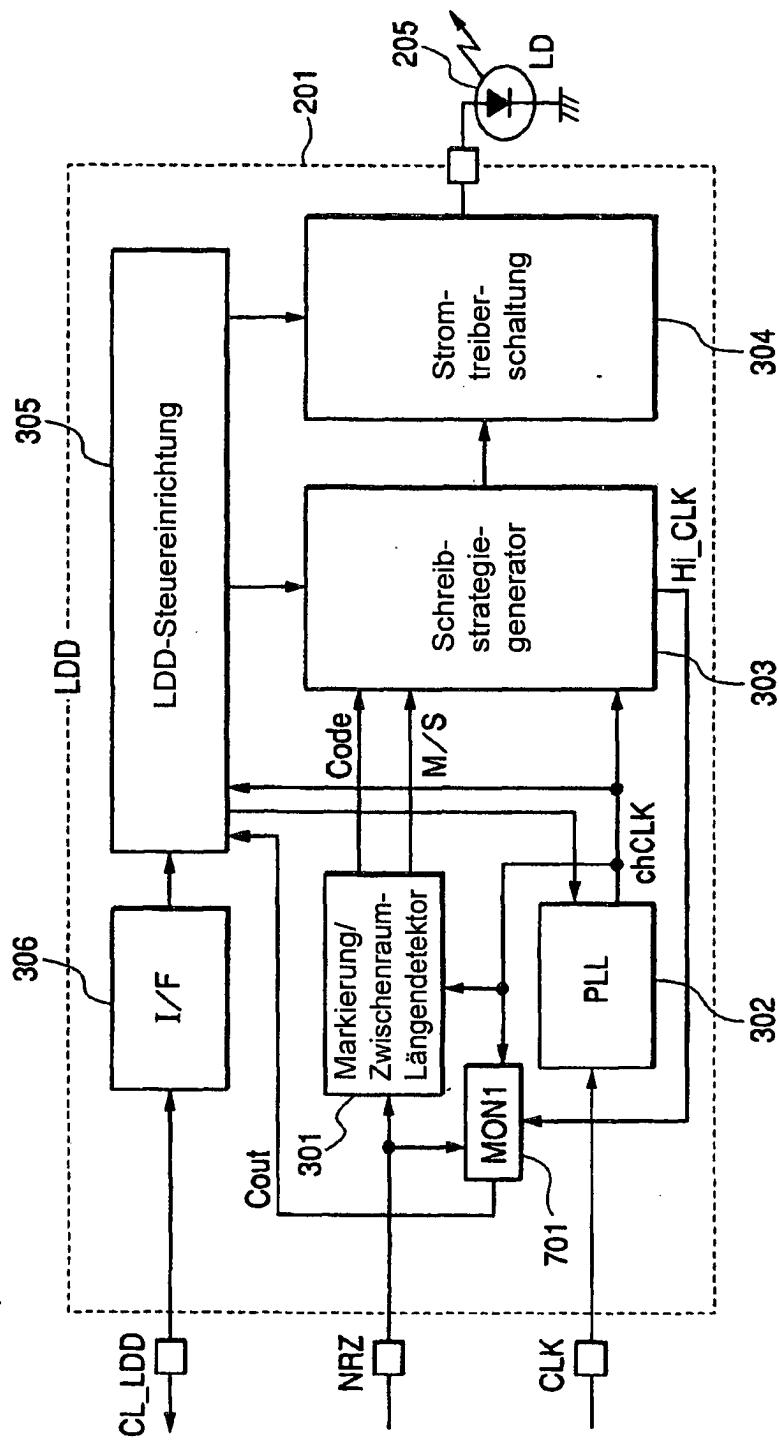

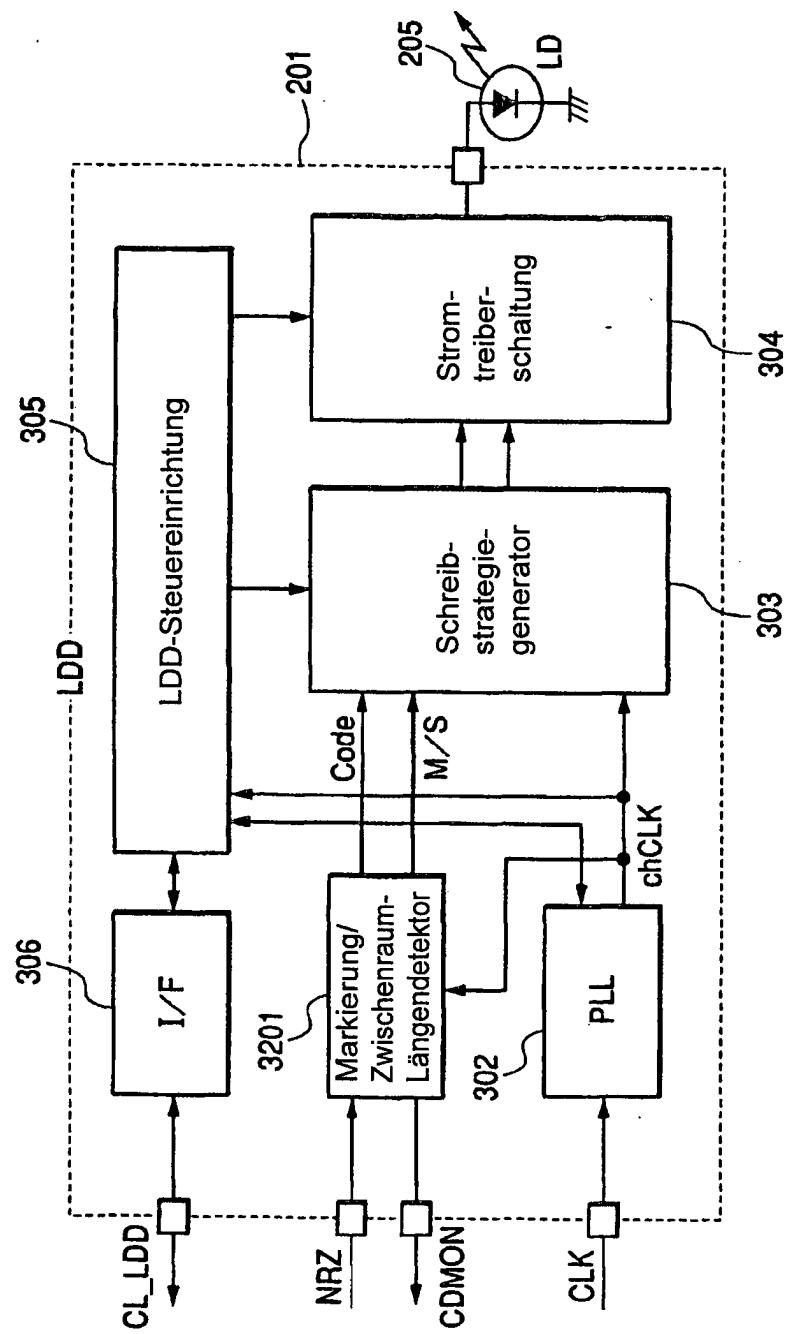

**[0004]** [Fig. 3](#) zeigt ein Beispiel der internen Struktur eines Lasertreibers, die innerhalb einer im Patentdokument 1 beschriebenen Konfiguration verwendet wird. Ein Markierung/Zwischenraum-Längendetektor 301 erzeugt Markierung/Zwischenraum-Informationen (M/S) und Impulsbreiteninformationen (Code) anhand des NRZ-Signals unter Verwendung des internen Takts chCLK, der durch eine PLL 302 mit CLK synchronisiert ist, und sendet die erzeugten Informationen zu einem Aufzeichnungswellenform-Generatorblock 303 in der nächsten Stufe. Der Aufzeichnungswellenform-Generatorblock 303 erzeugt die Informationen über die Aufzeichnungsimpulszeit und die Aufzeichnungsimpulseistung anhand der M/S- und Codeinformationen und sendet die erzeugten Informationen zu einem Stromsteuerblock 304. Der Stromsteuerblock 304 erzeugt ein Aufzeichnungsimpulssignal anhand der Informationen über die Aufzeichnungsimpulszeit und die Aufzeichnungsimpulseistung und treibt die Laserdiode 205. Alle vorstehend erwähnten Blöcke werden durch einen Steuerblock 305 im Lasertreiber gesteuert. Der Steuerblock 205 wird durch eine Steuereinrichtung (die in dem gegewöhnlich beschriebenen Beispiel ein Mikrocomputer 204 ist) in dem optischen Plattenapparat über eine Schnittstelle 306 gesteuert.

**[0005]** In US-A-6 414 932 ist ein Informations-Aufzeichnungs/Wiedergabe-Apparat beschrieben, der einen Lasertreiber aufweist, der ein NRZ-Binärsignal und ein mit dem NRZ-Binärsignal synchronisiertes Taktsignal von einer Modulationsschaltung empfängt und ein dem NRZ-Binärsignal entsprechendes Aufzeichnungsstromsignal erzeugt.

## ZUSAMMENFASSUNG DER ERFINDUNG

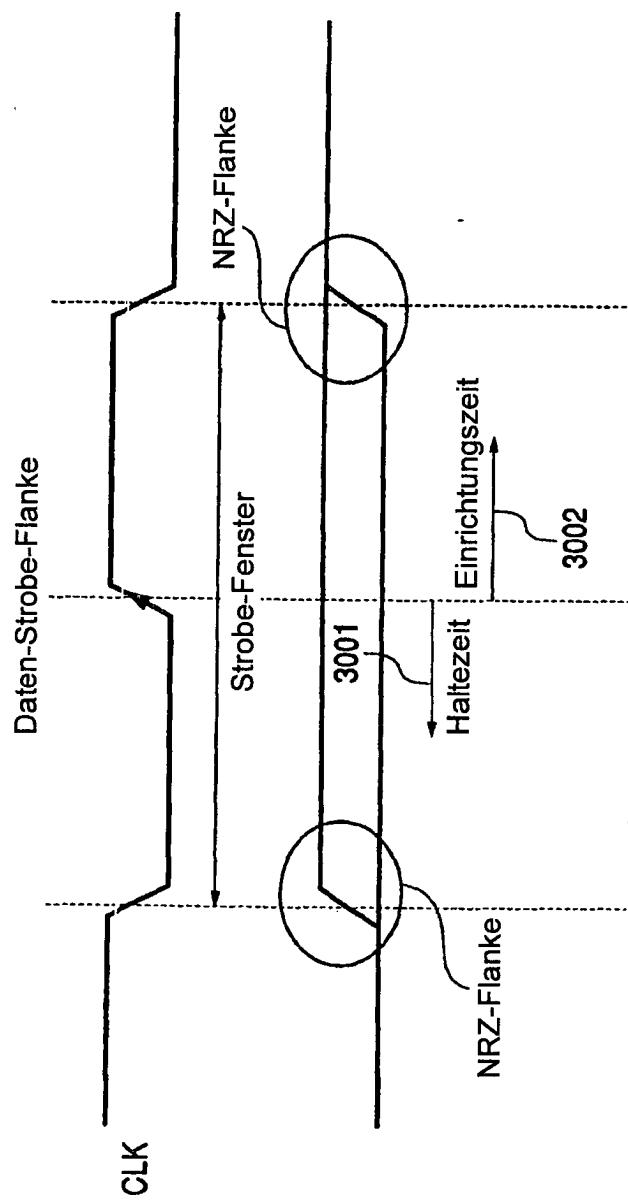

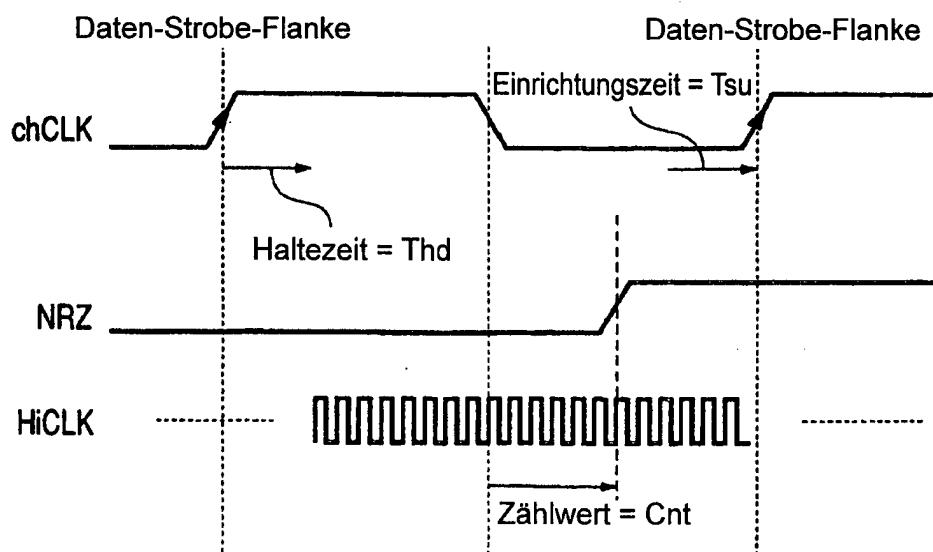

**[0006]** In dem vorstehend erwähnten Markierung/Zwischenraum-Längendetektor 301 werden die M/S-Informationen und die Codeinformationen gewöhnlich durch Abtasten des NRZ-Signals an einer CLK-Flanke erzeugt. Wenn beispielsweise eine ansteigende NRZ-Flanke abzutasten ist, wie in [Fig. 4](#) dargestellt ist, ist es notwendig, eine angemessene Einrichtungszeit 3001 für die Fertigstellung der Daten vor einer CLK-Abtast-Flanke und eine angemessene Haltezeit 3002 nach einer CLK-Abtast-Flanke für den Abschluss des Abtastens und der Datenerfassung bereitzustellen. Diese Anforderungen gelten auch in Fällen, in denen eine abfallende NRZ-Flanke abzutasten ist. Falls die bereitgestellte Einrichtungszeit oder Haltezeit nicht angemessen ist, werden die M/S-Informationen und die Codeinformationen, die vorstehend erwähnt wurden, unangemessen erzeugt, so dass inkorrekte Informationen auf einer optischen Platte aufgezeichnet werden.

**[0007]** Die Phasenbeziehung zwischen dem NRZ- und dem CLK-Signal hängt jedoch von dem Mittel zur Modulation, insbesondere der durch die Ausgabe des DSPs 203, wie in [Fig. 2](#) dargestellt ist, erzeugten Verzögerung, und dem Übertragungsweg zum Lasertreiber, insbesondere der durch das in [Fig. 2](#) dargestellte FPC 208 erzeugten Verzögerung oder der innerhalb des Lasertreibers erzeugten Verzögerung, ab. Wenn der Lasertreiber entsprechend dem vorstehend erwähnten Verfahren verwendet wird, ist es notwendig, die Phasenbeziehung zwischen NRZ und CLK zu steuern, um eine angemessene Einrichtungszeit und Haltezeit während eines CLK-Zyklus bereitzustellen. Je höher die Aufzeichnungsgeschwindigkeit ist, desto höher ist der für diese Phasensteuerung benötigte Genauigkeitsgrad.

**[0008]** Falls beispielsweise ein Lasertreiber, der eine Einrichtungszeit von 0,8 ns und eine Haltezeit von 0,6 ns bereitstellt, für eine DVD-R/RW-Aufzeichnung mit einer 10fachen Geschwindigkeit verwendet wird, beträgt ein CLK-Zyklus 3,8 ns. Wenn die vorstehend erwähnte Einrichtungszeit und Haltezeit von 3,8 ns subtrahiert werden, ergibt sich der Wert 2,4 ns. Es ist notwendig, die Phasenbeziehung zwischen NRZ und CLK zu steuern, so dass eine NRZ-Flanke innerhalb eines Zeitraums von 2,4 ns ankommt.

**[0009]** Ferner hängt die Phasenbeziehung zwischen den vorstehend erwähnten Signalen NRZ und CLK von dem Mittel zur Modulation, dem Übertragungsweg, Temperaturänderungen infolge der durch den Lasertreiber erzeugten Wärme, Temperaturänderungen, die durch die Umgebung des Lasertreibers hervorgerufen werden, und Schwankungen in der Versorgungsspannung ab. Es ist daher notwendig, einen angemessenen Spielraum für das Bestimmen der Phasenbeziehung zwischen NRZ und CLK bereitzustellen.

**[0010]** Eine bevorzugte Aufgabe der vorliegenden Erfindung besteht daher darin, eine Konfiguration bereitzustellen, die in der Lage ist, die Phasenbeziehung zwischen NRZ und CLK in einer Weise genau zu justieren, dass ein angemessener Spielraum für die Einrichtungszeit und die Haltezeit insbesondere in Situationen, in denen die Aufzeichnungsgeschwindigkeit erhöht ist, bereitgestellt wird.

**[0011]** Gemäß einem ersten Aspekt sieht die Erfindung einen optischen Plattenapparat nach Anspruch 1 vor. Der Apparat ist mit einem Lasertreiber versehen, der eine Treiberwellenform zum Ansteuern bzw. Treiben einer Laserdiode entsprechend dem binären Aufzeichnungssignal und dem auf einem Aufzeichnungsmedium aufzuzeichnenden Aufzeichnungstaktsignal erzeugt. Der optische Plattenapparat weist zwei Verzögerungsschaltungen auf, nämlich eine Binäraufzeichnungssignal-Verzögerungsschaltung und eine Aufzeichnungstaktsignal-Verzögerungsschalt-

tung. Die erstgenannte Verzögerungsschaltung verzögert das binäre Aufzeichnungssignal entsprechend einem Steuersignal, während die letztgenannte Verzögerungsschaltung das Aufzeichnungstaktsignal entsprechend dem Steuersignal verzögert. Die relative Zeit zwischen den Flanken des binären Aufzeichnungssignals und des Aufzeichnungstaktsignals kann durch Variieren der von den zwei Verzögerungsschaltungen bereitgestellten Verzögerungsgrößen justiert werden.

**[0012]** Der Oberbegriff der Ansprüche 1, 3, 4 und 5 beruht auf US-A-6 414 932.

## KURZBESCHREIBUNG DER ZEICHNUNGEN

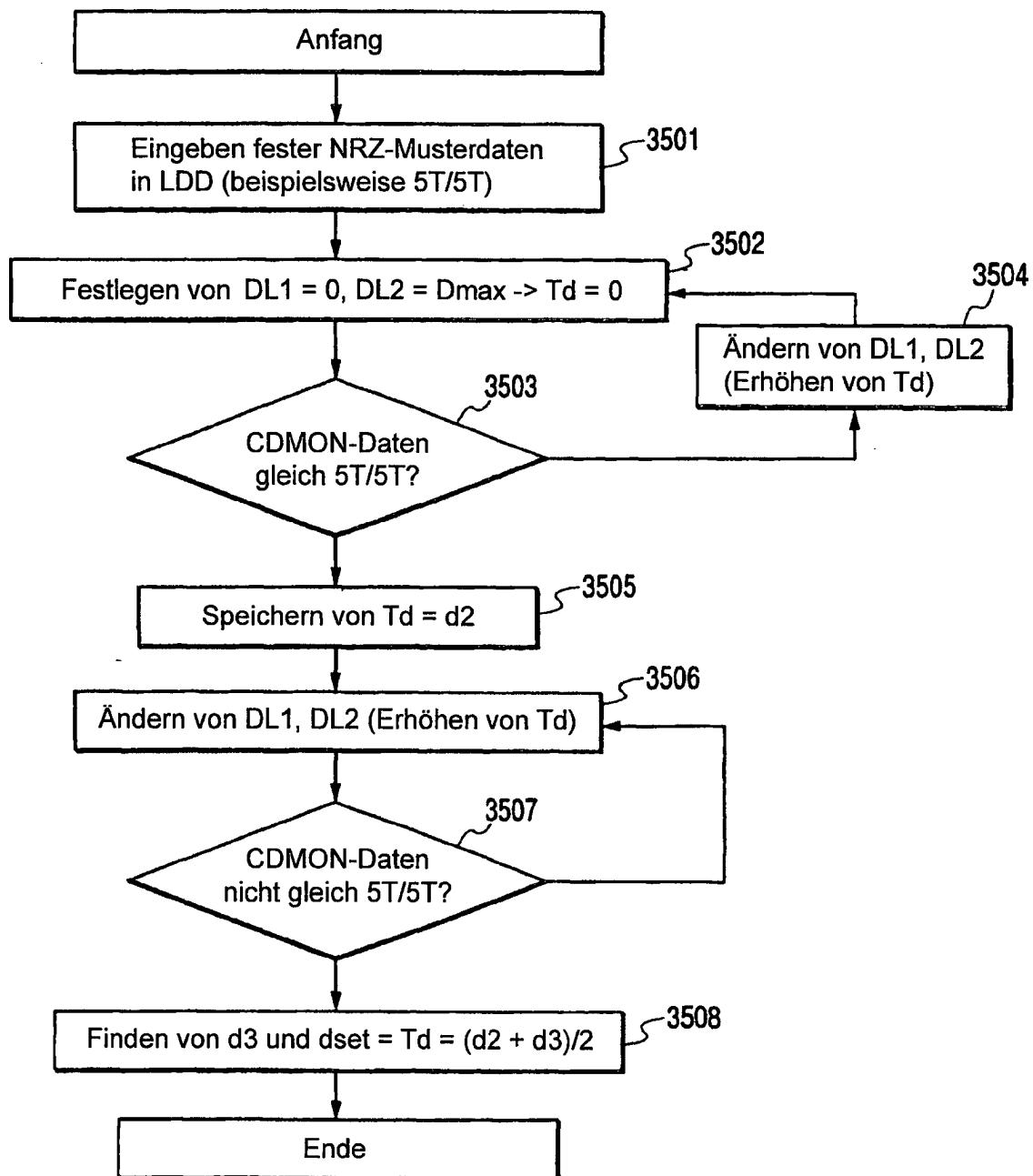

**[0013]** Es zeigen:

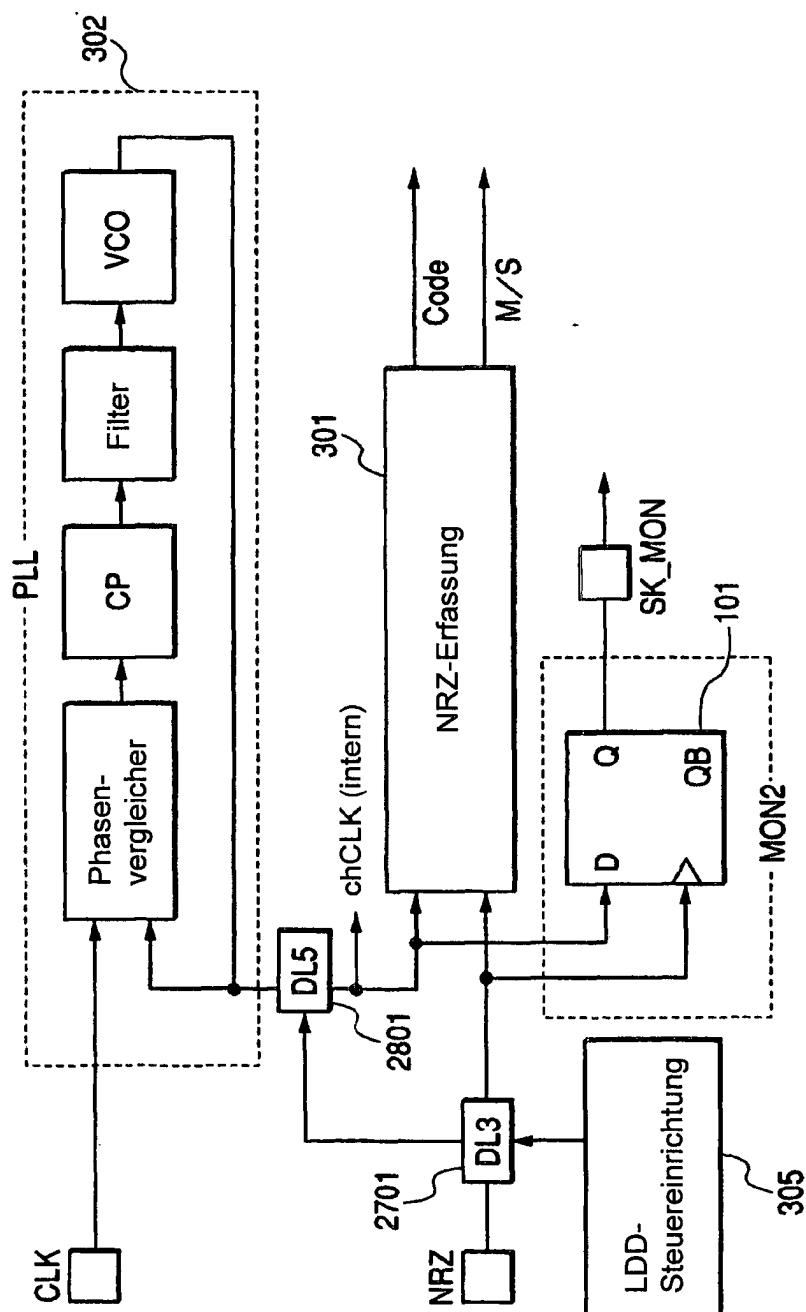

**[0014]** [Fig. 1](#) einen internen Schaltplan eines Lasertreibers gemäß einer vierten Ausführungsform der vorliegenden Erfindung,

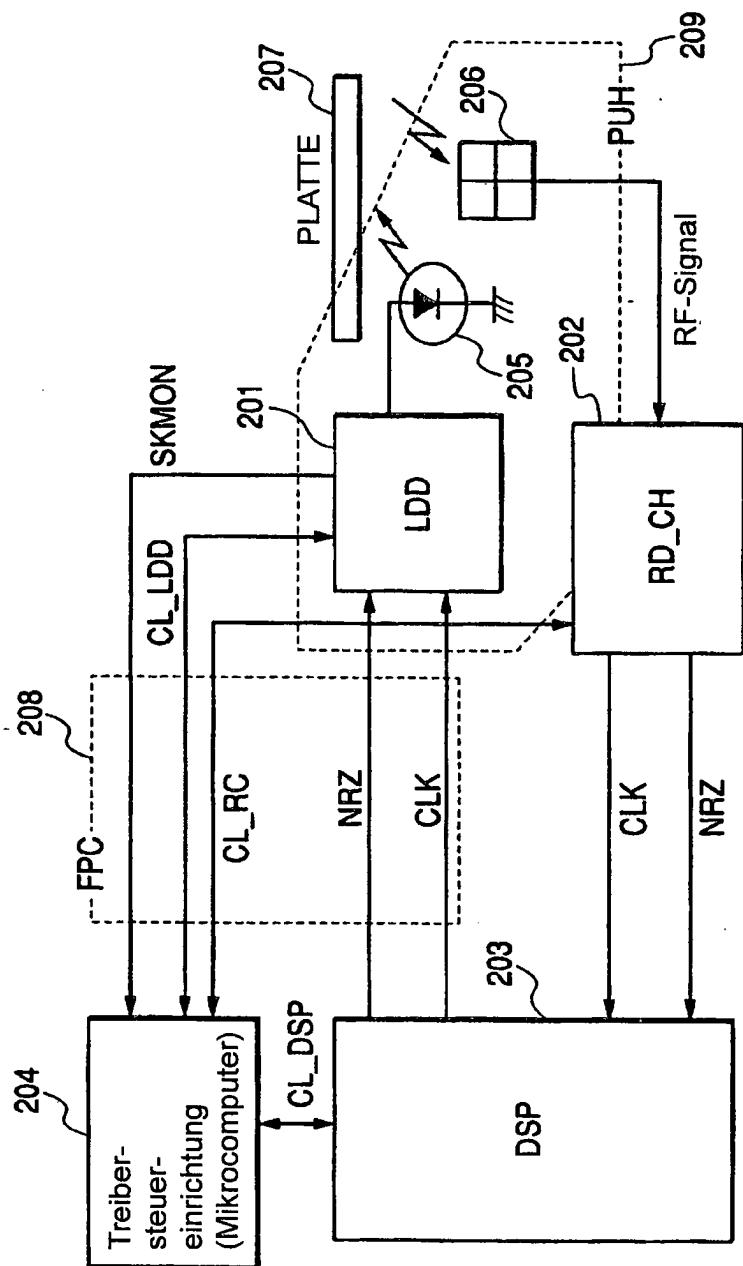

**[0015]** [Fig. 2](#) die Konfiguration eines herkömmlichen optischen Plattenapparats,

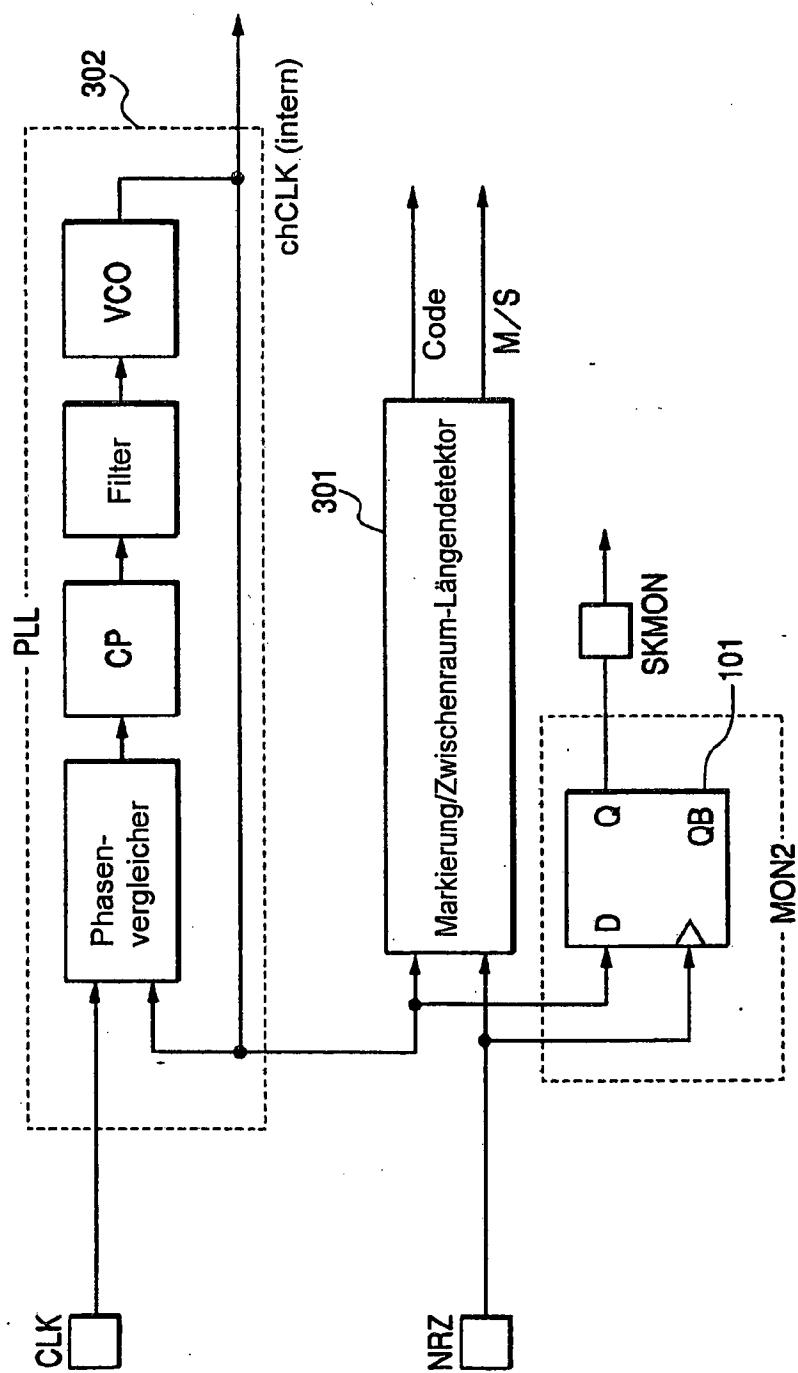

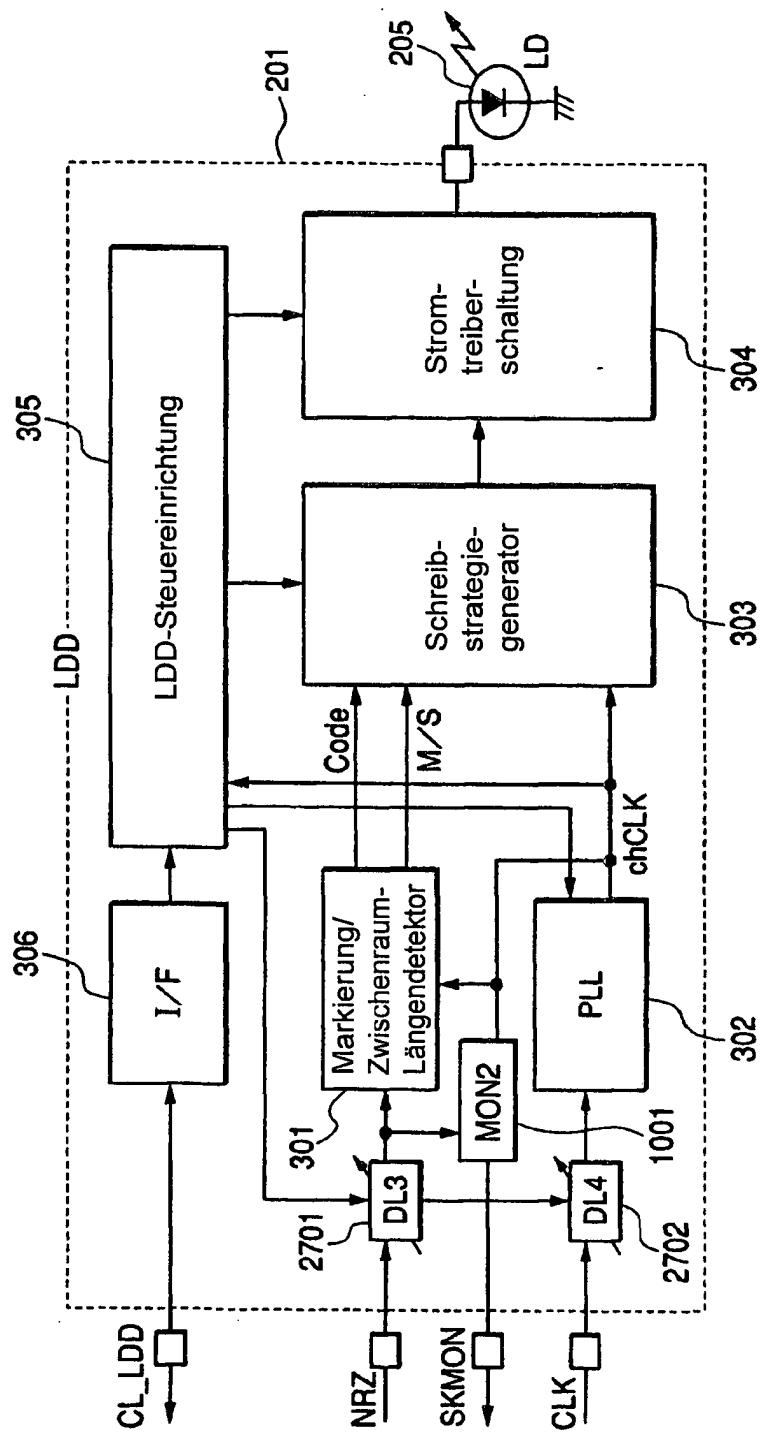

**[0016]** [Fig. 3](#) ein internes Blockdiagramm eines herkömmlichen Lasertreibers,

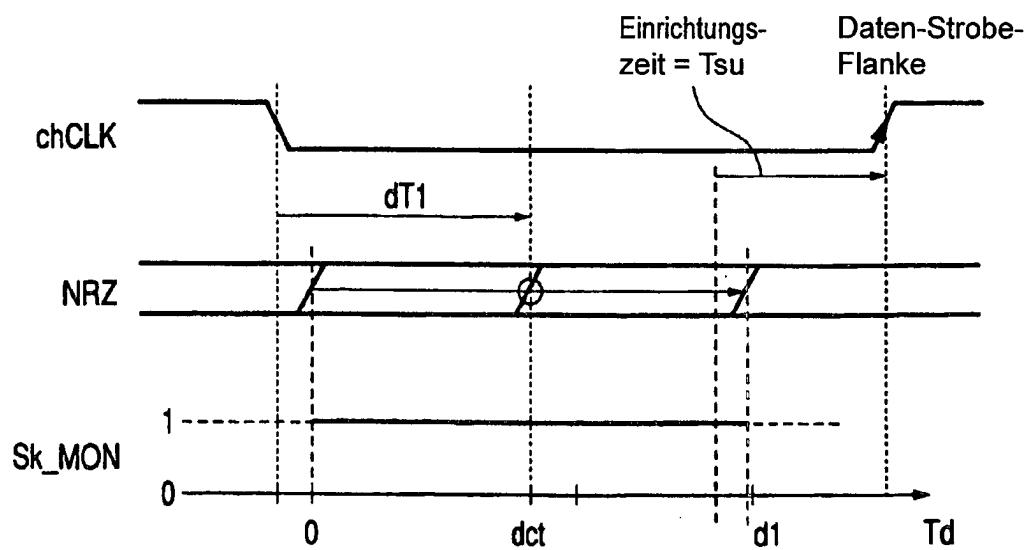

**[0017]** [Fig. 4](#) eine Einrichtungszeit und eine Haltezeit,

**[0018]** [Fig. 5](#) die Konfiguration eines optischen Plattenapparats gemäß einer ersten Ausführungsform der vorliegenden Erfindung,

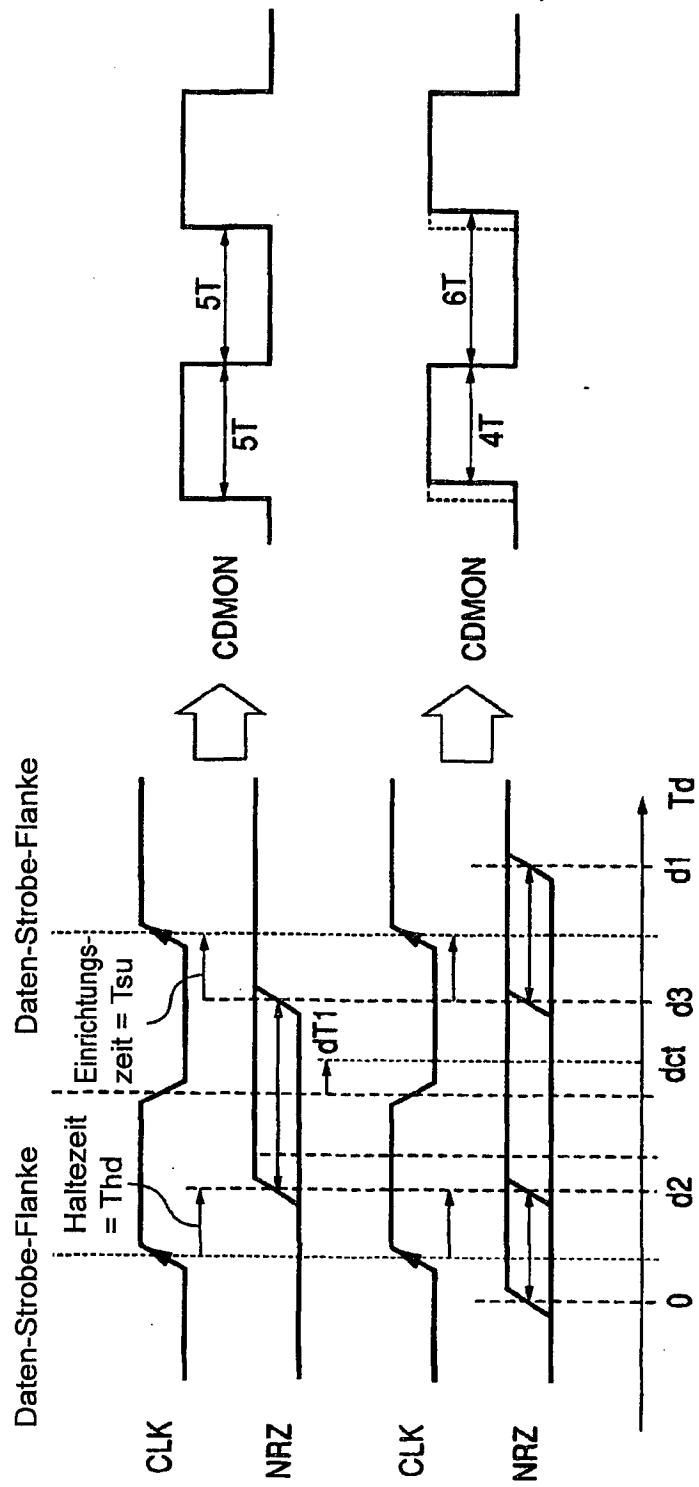

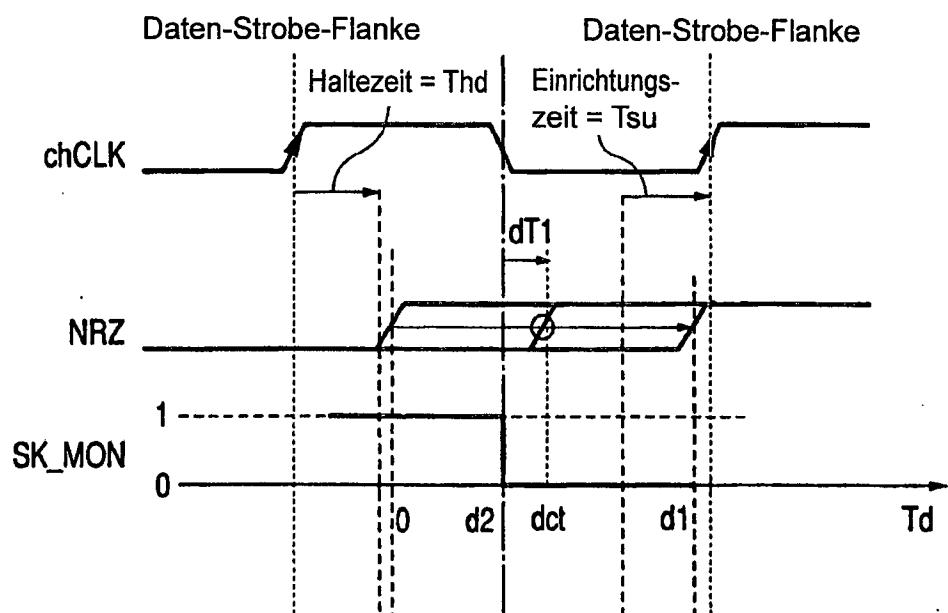

**[0019]** [Fig. 6](#) Operationswellenformen gemäß der ersten Ausführungsform der vorliegenden Erfindung,

**[0020]** [Fig. 7](#) ein Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die erste Ausführungsform der vorliegenden Erfindung justiert wird,

**[0021]** [Fig. 8](#) die Konfiguration eines optischen Plattenapparats gemäß einer zweiten Ausführungsform der vorliegenden Erfindung,

**[0022]** [Fig. 9](#) ein internes Blockdiagramm eines Lasertreibers gemäß einer dritten Ausführungsform der vorliegenden Erfindung,

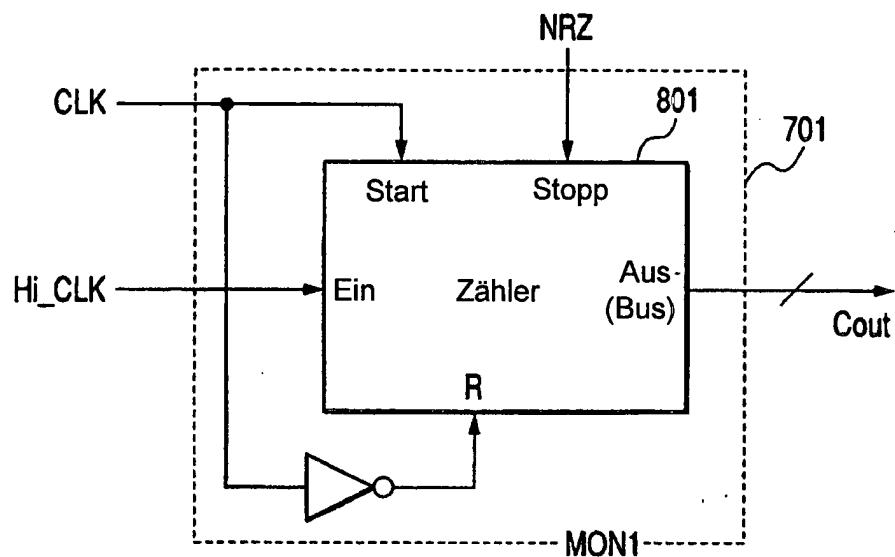

**[0023]** [Fig. 10](#) ein internes Blockdiagramm eines MON1-Blocks für den in [Fig. 7](#) dargestellten Lasertreiber,

**[0024]** [Fig. 11](#) Operationswellenformen gemäß der dritten Ausführungsform der vorliegenden Erfindung,

**[0025]** [Fig. 12](#) ein internes Blockdiagramm eines Lasertreibers gemäß der vierten Ausführungsform

der vorliegenden Erfindung,

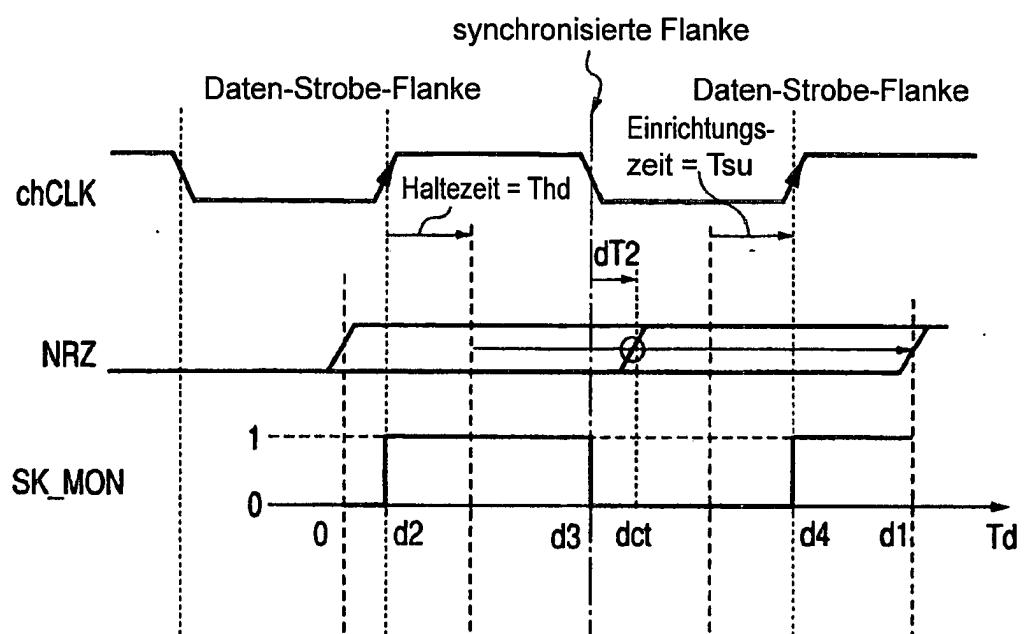

[0026] [Fig. 13](#) Operationswellenformen gemäß der vierten Ausführungsform der vorliegenden Erfindung,

[0027] [Fig. 14](#) ein Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die vierte Ausführungsform der vorliegenden Erfindung justiert wird,

[0028] [Fig. 15](#) ein internes Blockdiagramm eines Lasertreibers gemäß einer fünften Ausführungsform der vorliegenden Erfindung,

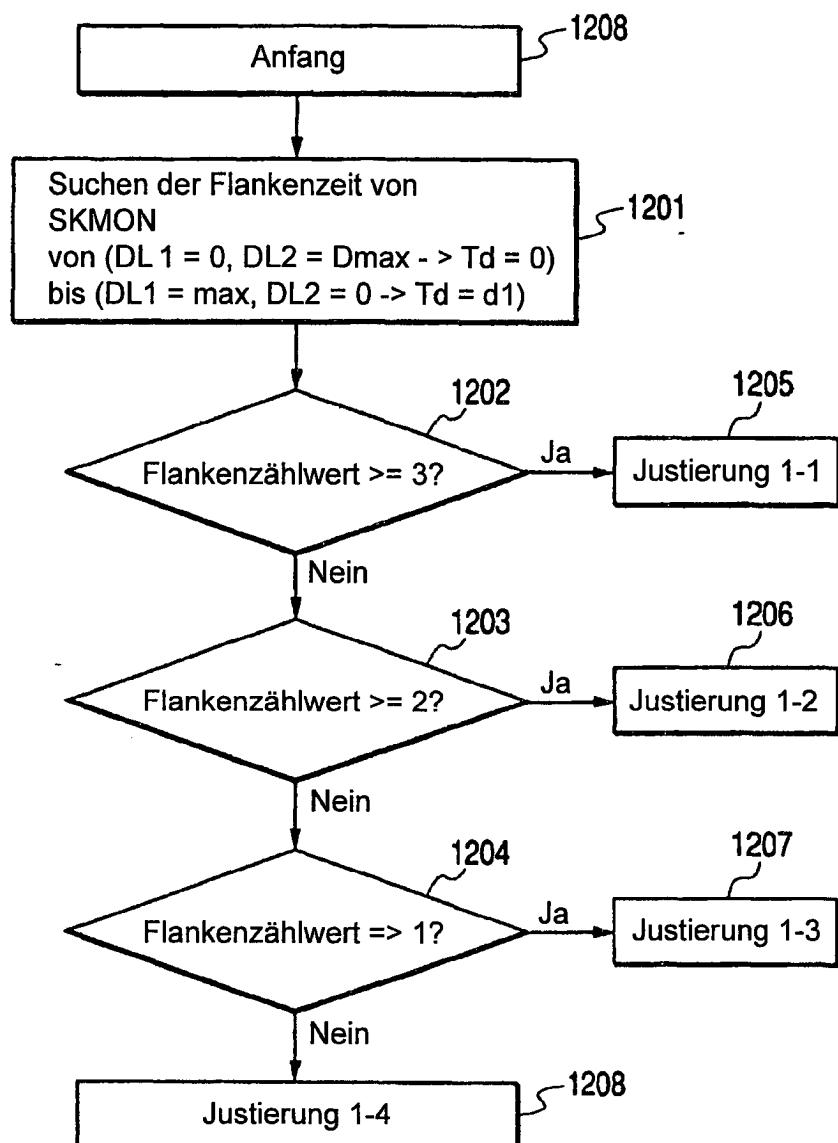

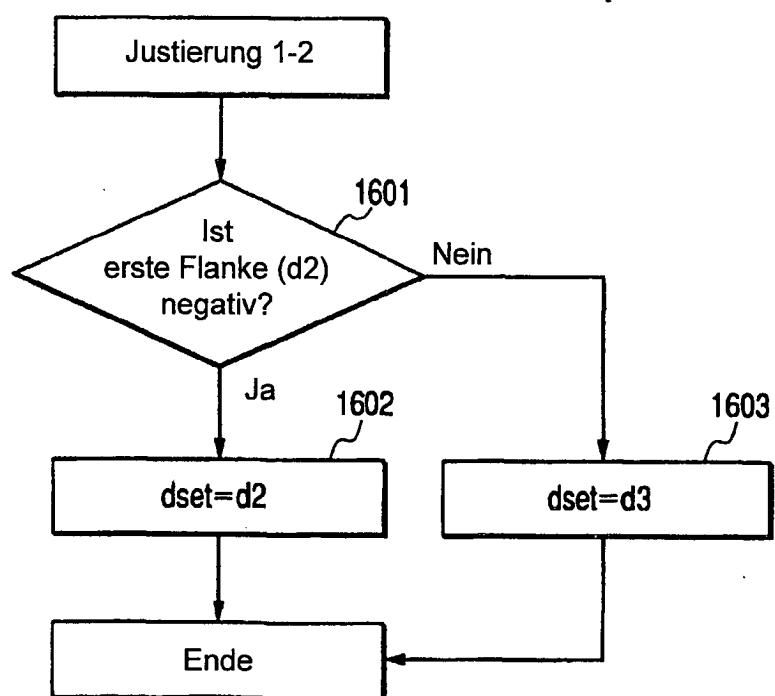

[0029] [Fig. 16](#) ein erstes Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die fünfte Ausführungsform der vorliegenden Erfindung justiert wird,

[0030] [Fig. 17](#) ein zweites Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die fünfte Ausführungsform der vorliegenden Erfindung justiert wird,

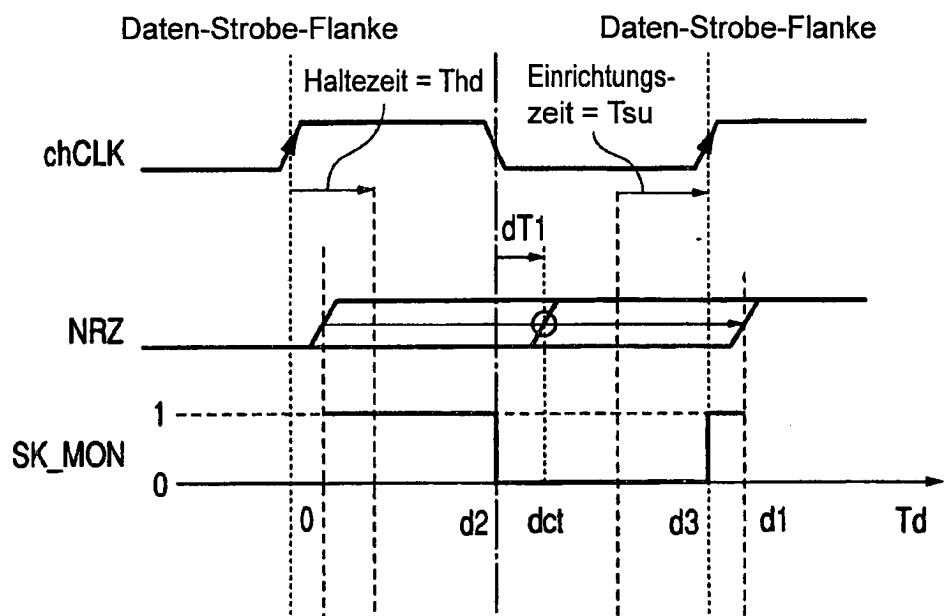

[0031] [Fig. 18](#) ein erstes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

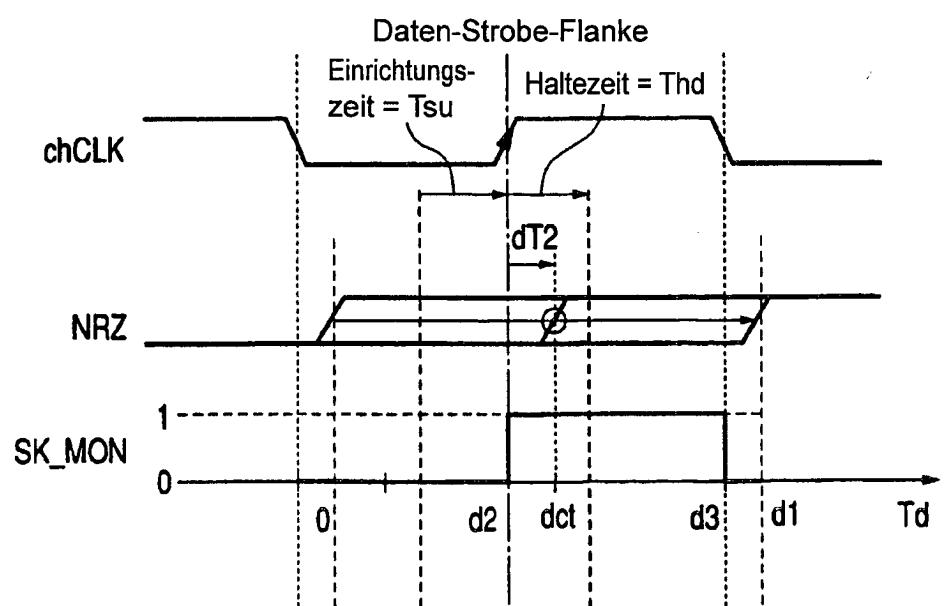

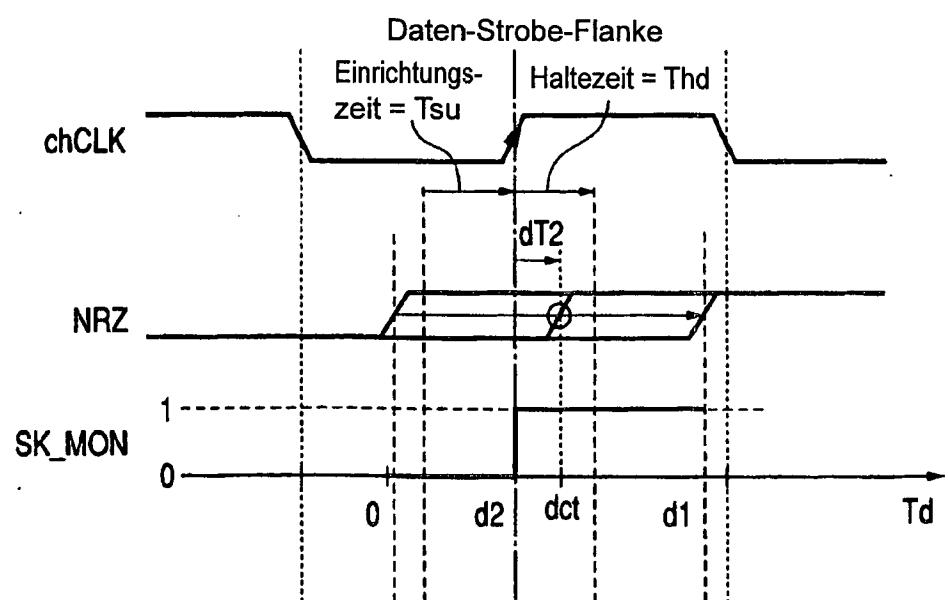

[0032] [Fig. 19](#) ein zweites Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

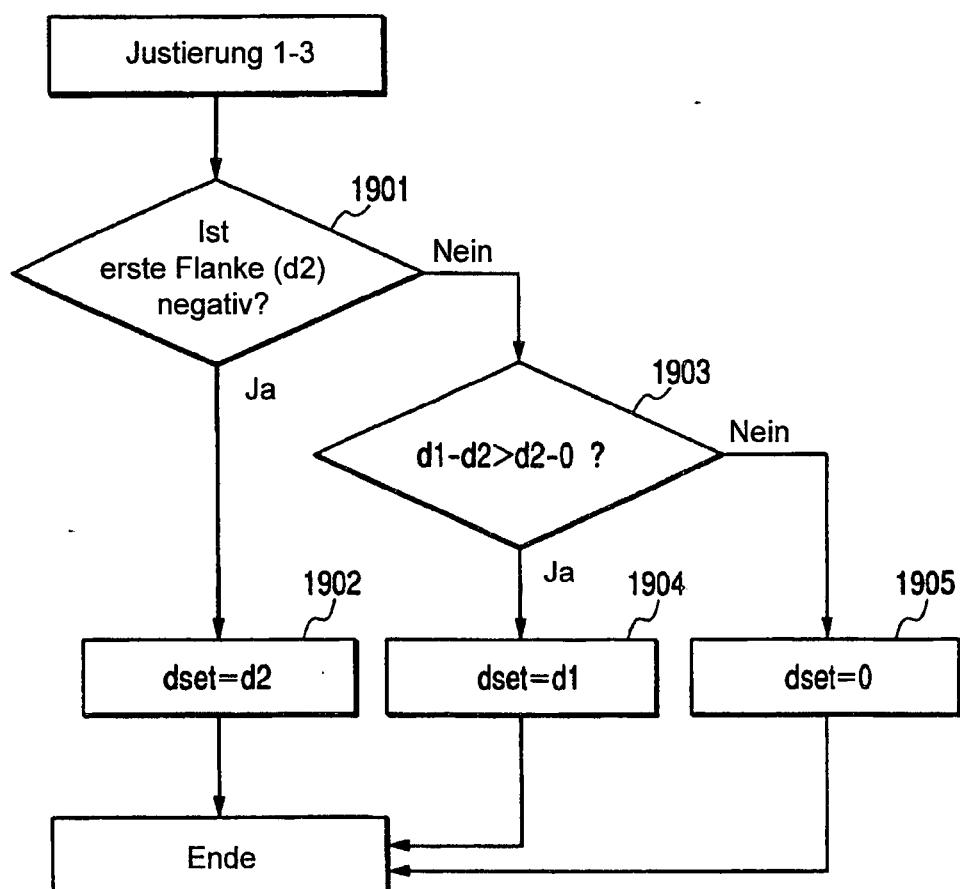

[0033] [Fig. 20](#) ein drittes Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die fünfte Ausführungsform der vorliegenden Erfindung justiert wird,

[0034] [Fig. 21](#) ein drittes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

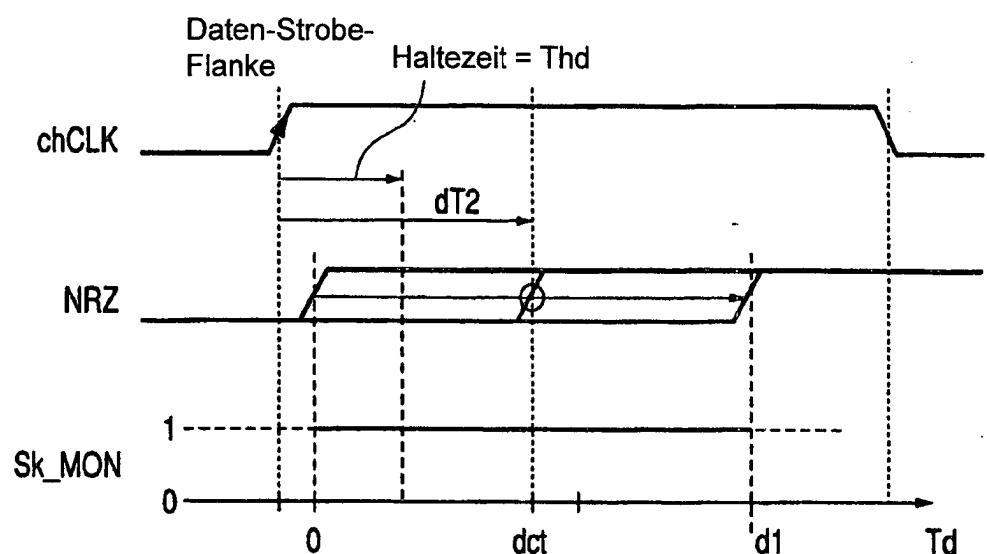

[0035] [Fig. 22](#) ein vierter Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

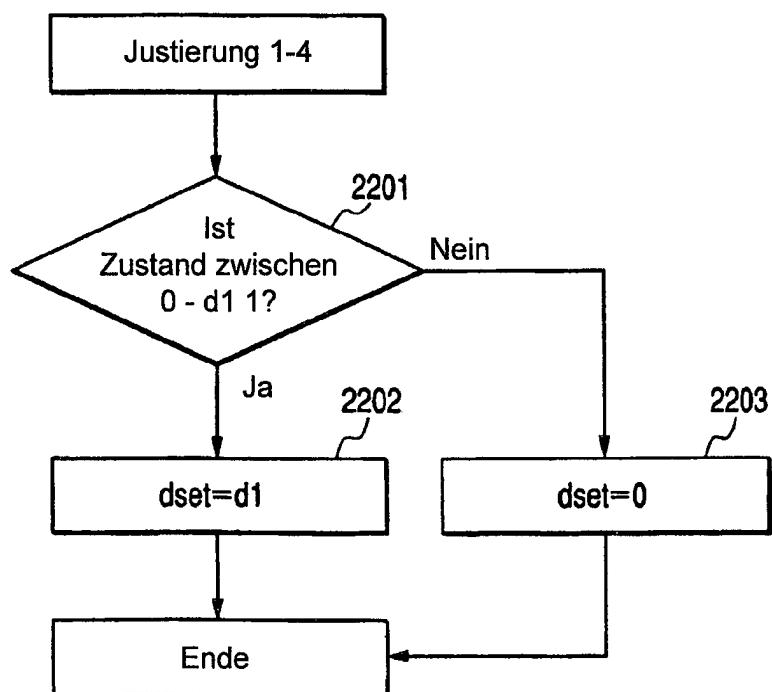

[0036] [Fig. 23](#) ein vierter Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und NRZ durch die fünfte Ausführungsform der vorliegenden Erfindung justiert wird,

[0037] [Fig. 24](#) ein fünftes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

[0038] [Fig. 25](#) ein sechstes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

[0039] [Fig. 26](#) ein fünftes Flussdiagramm, das zeigt, wie die Phasenbeziehung zwischen CLK und

NRZ durch die fünfte Ausführungsform der vorliegenden Erfindung justiert wird,

[0040] [Fig. 27](#) ein siebtes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

[0041] [Fig. 28](#) ein achtes Diagramm, das Operationswellenformen gemäß der fünften Ausführungsform der vorliegenden Erfindung zeigt,

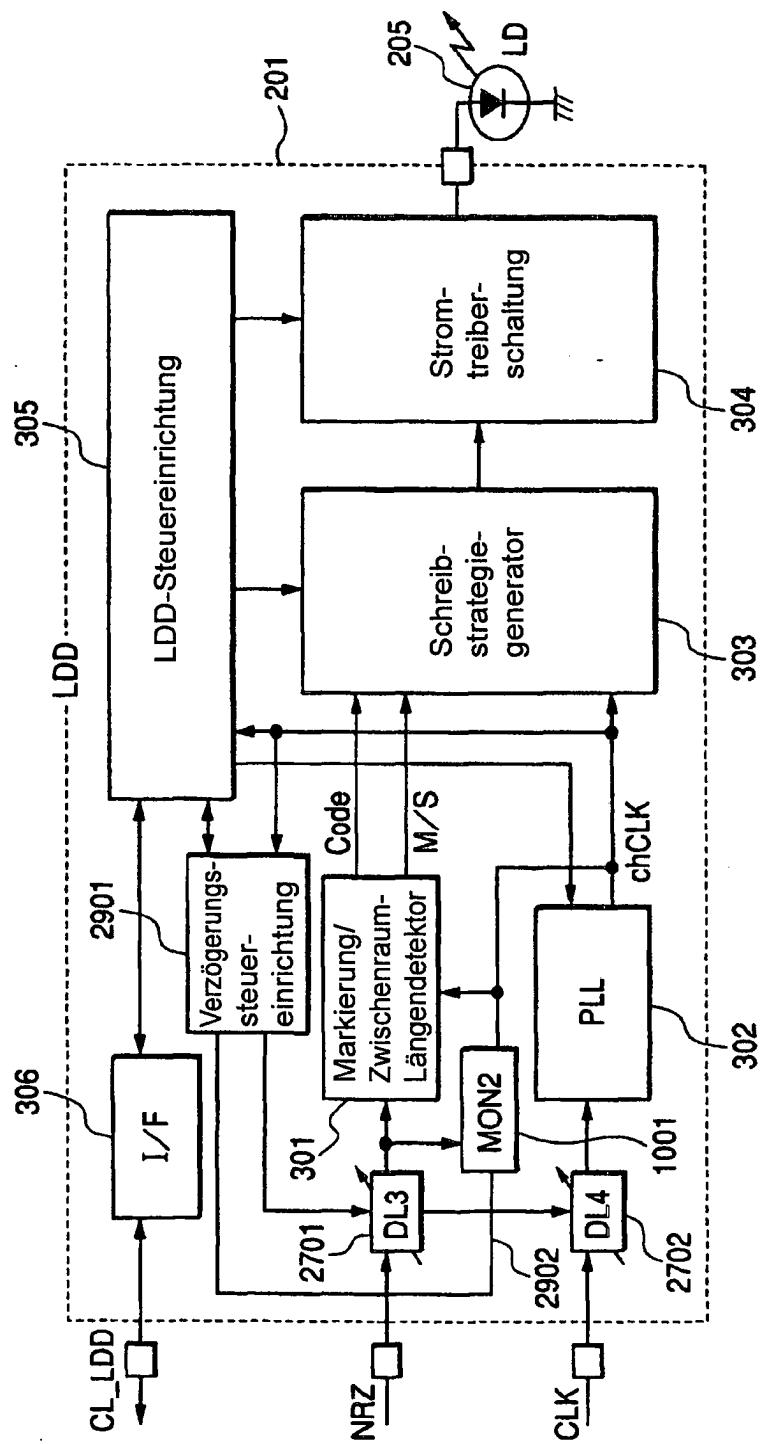

[0042] [Fig. 29](#) die Konfiguration eines optischen Plattenapparats gemäß einer sechsten Ausführungsform der vorliegenden Erfindung,

[0043] [Fig. 30](#) ein internes Blockdiagramm eines Lasertreibers gemäß der sechsten Ausführungsform der vorliegenden Erfindung,

[0044] [Fig. 31](#) einen internen Schaltplan eines Lasertreibers gemäß einer siebten Ausführungsform der vorliegenden Erfindung und

[0045] [Fig. 32](#) ein internes Blockdiagramm eines Lasertreibers gemäß einer achten Ausführungsform der vorliegenden Erfindung.

#### DETAILLIERTE BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSFORMEN

[0046] Die Hauptbezugszahlen, die in der anliegenden Zeichnung verwendet werden, sind: **101**, D-Flipflop; **201**, Lasertreiber; **202**, Lesekanal; **203**, digitaler Signalprozessor (DSP); **204**, Mikrocomputer; **205**, Laserdiode; **206**, photoelektrischer Wandler; **207**, wiederbeschreibbare optische Platte; **208**, flexibles Kabel; **301**, Markierung/Zwischenraum-Längendetektor; **303**, Aufzeichnungswellenform-Generatorblock; **305**, Lasertreiber-Steuerblock; **306**, Lasertreiber-Steuerschnittstellenblock; **401**, erste veränderliche Verzögerungsvorrichtung; **402**, zweite veränderliche Verzögerungsvorrichtung; **701**, erste Überwachungssignal-Generatorschaltung; **801**, Start/Stopp/Rücksetz-Zähler; **1001**, zweite Überwachungssignal-Generatorschaltung; **2501**, EOR-Gatterschaltung; **2701**, dritte veränderliche Verzögerungsvorrichtung; **2702**, vierte veränderliche Verzögerungsvorrichtung; **2801**, fünfte veränderliche Verzögerungsvorrichtung und **2901**, Verzögerungssteuerschaltung.

[0047] Die bevorzugten Ausführungsformen der vorliegenden Erfindung werden nun mit Bezug auf die anliegende Zeichnung beschrieben. [Fig. 5](#) zeigt die Konfiguration eines optischen Plattenapparats gemäß einer ersten Ausführungsform der vorliegenden Erfindung. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 2](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung

verzichtet. Die Bezugszahlen **401** und **402** in [Fig. 5](#) geben veränderliche Verzögerungsvorrichtungen an. Diese veränderlichen Verzögerungsvorrichtungen werden durch einen Mikrocomputer **204** gesteuert. Die Phasenbeziehung zwischen NRZ und CLK wird durch Ändern der von diesen veränderlichen Verzögerungsvorrichtungen bereitgestellten Verzögerungsgrößen justiert.

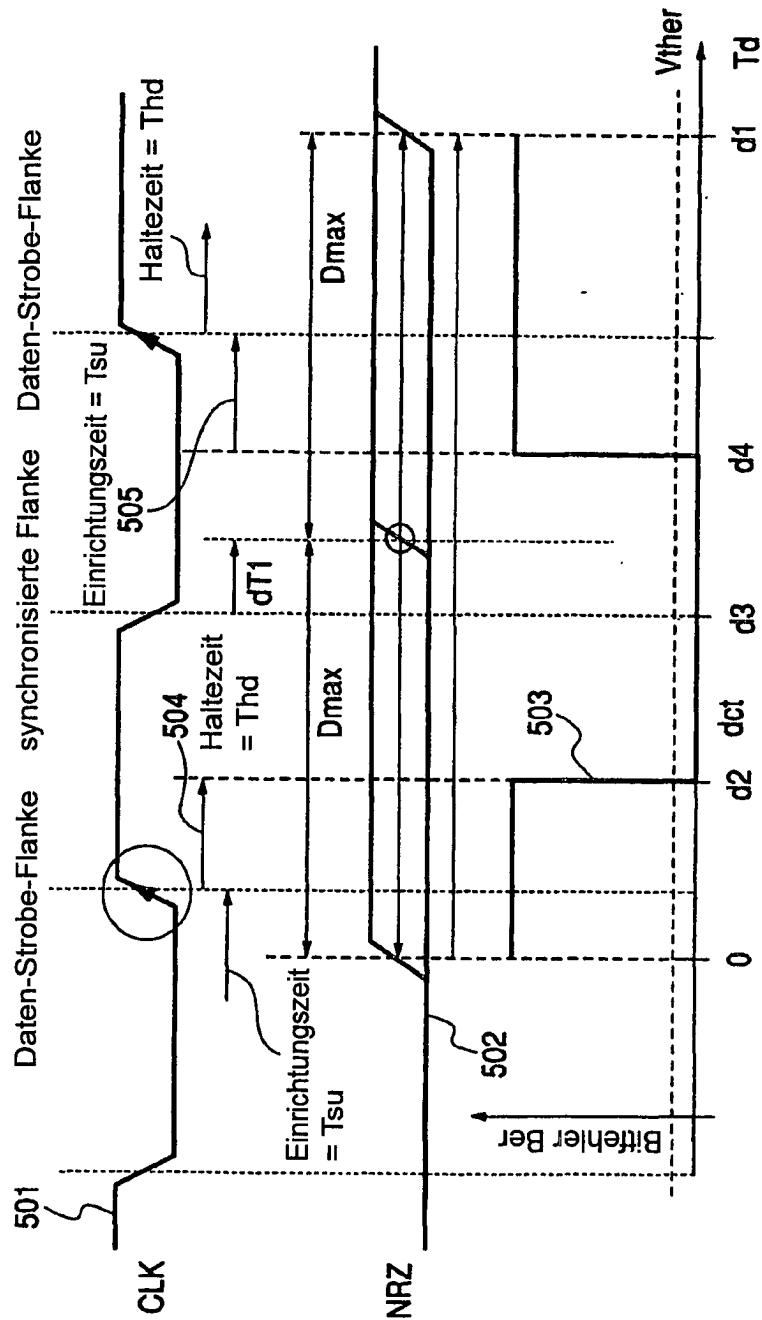

**[0048]** Die Operation, die ausgeführt wird, um die Phasenbeziehung zwischen NRZ und CLK gemäß der vorliegenden Ausführungsform zu justieren, wird nun mit Bezug auf die [Fig. 6](#) und [Fig. 7](#) beschrieben. Wenngleich es sowohl ansteigende als auch abfallende NRZ-Flanken gibt, wird in den NRZ/CLK-Phasenbeziehungsdarstellungen, auf die von nun an Bezug genommen wird, nur die Phasenbeziehung für eine ansteigende Flanke von NRZ als Beispiel erläutert. In allen bevorzugten Ausführungsformen, einschließlich der vorliegenden Ausführungsform, wird angenommen, dass eine NRZ-Daten-Abtastung an einer ansteigenden Flanke von CLK erfolgt.

**[0049]** In Bezug auf die Phasenbeziehung zwischen NRZ und CLK, die durch einen DSP **203** in [Fig. 5](#) ausgegeben werden, wird angenommen, dass eine Synchronisation an einer abfallenden Flanke von CLK (in entgegengesetzter Phase zu einer Abtast-Flanke) ausgeführt wird, wie in [Fig. 6](#) angegeben ist, und dass der DSP intern gewährleistet, dass eine NRZ-Flanke mit einer Verzögerung mit einer festen Zeit  $dT1$  nach einer abfallenden Flanke von CLK zeitlich festgelegt ist. Die NRZ-Flanke in Bezug auf CLK wird justiert, wobei die vorstehend erwähnte Position als Zentrum angesehen wird.

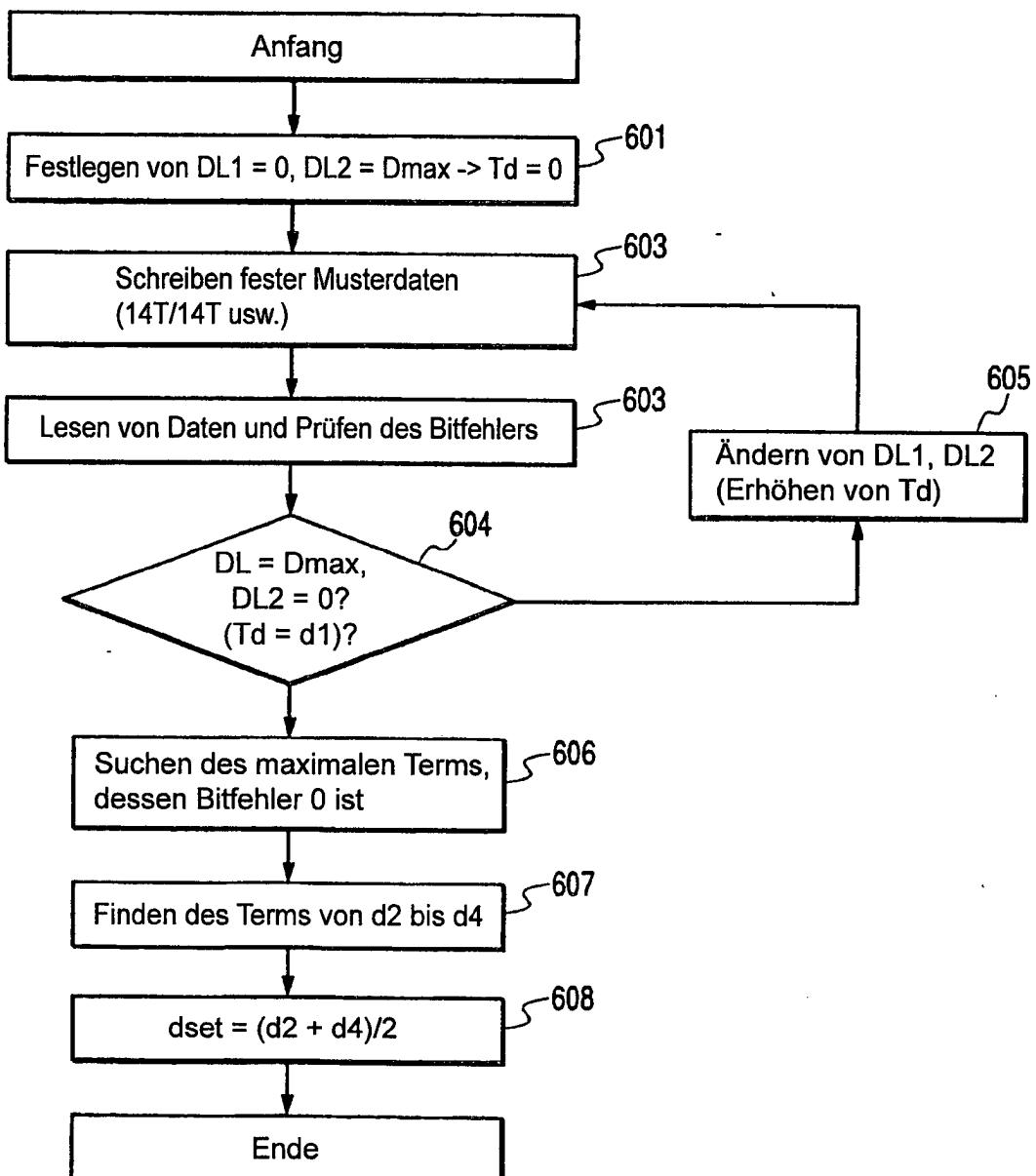

**[0050]** Die Phasenjustieroperation wird nun mit Bezug auf ein Flussdiagramm in [Fig. 7](#) beschrieben. Wir definieren die Verzögerungsgröße  $Td1$  für  $DL1$  (**401**) als 0 und die Verzögerungsgröße  $Td2$  für  $DL2$  (**402**) als  $Dmax$  (**601**). Ferner wird definiert, dass die Verzögerungsjustiergröße  $Td = (Dmax - Td2) + Td1$  ist.

**[0051]** Unter Verwendung der vorstehend erwähnten Einstellungen wird ein "14T – 14T"-Muster oder ein anderes bekanntes festes Muster auf einer Platte aufgezeichnet (**602**). Der vorstehend erwähnte Vorgang wird wiederholt (**604**), indem die Werte  $Td1$  und  $Td2$  geändert werden (**605**), um den Wert  $Td$  zu erhöhen, bis  $Td1 = Dmax$  und  $Td2 = 0$  ( $Td = d1$ ) sind. Falls beispielsweise  $Td = 0$  ist, ist das Zeitintervall zwischen einer NRZ-Flanke und der CLK-Abtastung kürzer als die in [Fig. 6](#) angegebene Einrichtungszeit. In Bezug auf den Wert  $Ber$  tritt daher ein Fehler in einer innerhalb des Lasertreibers gelesenen Pulsbreite auf, so dass sich ein Aufzeichnungsfehler ergibt. Folglich weisen die sich ergebenden Wiedergabedaten eine hohe Bitfehlerrate ("sehr fehlerhaft") auf. Falls andererseits  $Td = d3$  ist, tritt kein Bitfehler auf, weil die Einrichtungszeit und die Haltezeit angemes-

sen bereitgestellt sind.

**[0052]** Als nächstes wird eine Suche ausgeführt, um einen Term zu lokalisieren, während dessen der Bitfehler kleiner als ein Schwellenwert  $V_{ther}$  ist (**606**). Weil der Bitfehler innerhalb des Terms zwischen einer Verzögerungsgröße  $d2$  und einer Verzögerungsgröße  $d4$  kleiner als der Schwellenwert  $V_{ther}$  ist (**607**), werden die Verzögerungsgrößen  $DL1$  und  $DL2$  so festgelegt, dass  $dT = dset = (d2 + d4)/2$  ist (**608**). Die NRZ/CLK-Phasenjustierung ist nun abgeschlossen.

**[0053]** Aus den vorstehend erwähnten Gründen kann die Phasenbeziehung zwischen CLK und NRZ, d. h. die CLK- und NRZ-Flankenzeit-Achsenpositionen, auf eine Position gelegt werden, die am weitesten von der Phasenbeziehung entfernt ist, bei der ein Bitfehler hervorgerufen wird, wenn die auf einer Platte aufgezeichneten Daten wiedergegeben werden. Dadurch ermöglicht es die vorstehend erwähnte Justierung, die Phasenbeziehung zwischen CLK und NRZ an eine Position zu legen, die einen angemessenen Spielraum für Temperaturänderungen in den Bestandteilen eines optischen Plattenapparats, Temperaturänderungen in dem Bereich um die Bestandteile, Änderungen in der Stromversorgung der Schaltung und schwankungsinduzierte Änderungen in der Phasenbeziehung zwischen CLK- und NRZ-Signalen bereitstellt. Eine wesentliche Wirkung kann daher einfach dadurch erzeugt werden, dass die vorstehend erwähnte Justierung beispielsweise zu der Zeit einer anfänglichen Justierung für einen Ausgangsinspektionsprozess vorgenommen wird.

**[0054]** [Fig. 8](#) zeigt einen optischen Plattenapparat gemäß einer zweiten Ausführungsform der vorliegenden Erfindung. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 5](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Der in [Fig. 8](#) dargestellte optische Plattenapparat unterscheidet sich in der Hinsicht von dem Apparat in [Fig. 5](#), dass der erstgenannte mit einer EOR-Vorrichtung **2501** versehen ist, die an einer Stufe nach jener einer veränderlichen Verzögerungsvorrichtung **402** zum Ändern der CLK-Phase positioniert ist. Das CLK-Signal wird in einen Eingang der EOR-Vorrichtung **2501** eingegeben, und ein  $CLK\_INV\_bit$  wird in den anderen Eingang eingegeben. Wenn das  $CLK\_INV\_bit = 1$  ist, gibt die EOR-Vorrichtung ein  $CLK2$ -Signal aus, das die gleiche Phase aufweist wie das CLK-Signal. Wenn das  $CLK\_INV\_bit = 0$  ist, gibt die EOR-Vorrichtung andererseits ein phaseninvertiertes  $CLK2$ -Signal aus.

**[0055]** Falls beispielsweise die Phasensynchronisation zwischen den NRZ- und CLK-Ausgaben vom DSP **203** im Gegensatz zu dem in [Fig. 5](#) dargestellten Fall (in Phase mit einer Abtast-Flanke) an einer

ansteigenden Flanke von CLK erreicht wird, kann die Phasenjustierung nicht durch das Verfahren gemäß der ersten Ausführungsform der vorliegenden Erfindung vorgenommen werden. Die vorstehend erwähnte EOR-Schaltung kann jedoch verwendet werden, um eine Phasenumkehr bereitzustellen, so dass der sich ergebende Zustand mit dem von der ersten Ausführungsform bereitgestellten Zustand identisch ist. Daher erzeugt die zweite Ausführungsform die gleiche Wirkung wie die erste Ausführungsform.

[0056] [Fig. 9](#) zeigt die Konfiguration eines Lasertreibers gemäß einer dritten Ausführungsform der vorliegenden Erfindung. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 3](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Weil die Konfiguration des optischen Plattenapparats ferner jener gleicht, die in [Fig. 5](#) angegeben ist, wird auf seine Beschreibung hier verzichtet.

[0057] Ein in [Fig. 9](#) dargestellter MON1-Block 701 ist eine Schaltung, die die Zeitdifferenz zwischen einer NRZ-Flanke und einer CLK-Flanke in der Nähe der NRZ-Flanke misst. [Fig. 10](#) zeigt ein Schaltungs-konfigurationsbeispiel des MON1-Blocks.

[0058] Ein Zähler 801, der in [Fig. 10](#) dargestellt ist, ist mit einer Startfunktion, einer Stopfunktion und einer Rücksetzfunktion versehen. HiCLK ist ein Takt, den ein Strategiegeneratorblock mit einer Aufzeichnungsimpulsflanken-Justiergenauigkeit (einige Zehntel eines CLK-Zyklus) erzeugt. Dieser Takt wird zum Messen der vorstehend erwähnten Zeitdifferenz verwendet. Zähldaten werden als ein Registerwert zur Steuereinrichtung des Lasertreibers gesendet und dann über die Schnittstelle zum Mikrocomputer des optischen Plattenapparats weitergeleitet.

[0059] Die zum Justieren der Phasenbeziehung zwischen NRZ und CLK gemäß der vorliegenden Ausführungsform ausgeführte Operation wird nun mit Bezug auf [Fig. 11](#) beschrieben.

[0060] Wie in [Fig. 11](#) angegeben ist, erfolgt eine Daten-Abtastung an einer ansteigenden Flanke von CLK. Wenn daher die NRZ/CLK-Schwankung berücksichtigt wird, ist es notwendig, eine NRZ-Flanke mit einer abfallenden CLK-Flanke zu justieren.

[0061] Demgemäß wird der Anfang in [Fig. 10](#) auf eine abfallende Flanke von CLK gesetzt, wobei das Rücksetzen auf NRZ-Flanken gesetzt wird (sowohl ansteigende als auch abfallende Flanken). Während der unter dem CLK-Zykluspegel vorherrschende Zählerwert Cnt überwacht wird, werden die durch DL1 und DL2, die in [Fig. 5](#) dargestellt sind, bereitgestellten Verzögerungsgrößen justiert, bis der Zählerwert Cnt nahe bei 0 ist.

[0062] Die vorliegende Ausführungsform erzeugt nicht nur die gleiche Wirkung wie die erste und die zweite Ausführungsform der vorliegenden Erfindung, sondern sie macht es auch unnötig, eine Aufzeichnungs-/Wiedergabeoperation in Bezug auf die Platte auszuführen. Daher kann die vorliegende Ausführungsform anders als die erste und die zweite Ausführungsform die Verwendung eines Plattenbereichs während der Justierung verhindern, und sie verringert die Verwendung des Plattenraums für andere Aufzeichnungen als Daten während der Verwendung einer DVD-R-Platte oder einer anderen einmal beschreibbaren Platte. Ferner bringt die vorliegende Ausführungsform eine kürzere Justierperiode mit sich als die erste und die zweite Ausführungsform, weil die vorliegende Ausführungsform einen Aufzeichnungsvorgang und einen Wiedergabevorgang nicht gleichzeitig ausführt. Wenn Bitfehler wie gemäß der ersten und der zweiten Ausführungsform verwendet werden, ist es jedoch schwierig, zwischen Bitfehlern, die durch einen Plattenfaktor, wie Mängel oder Fingerabdrücke auf der Platte hervorgerufen werden, und Bitfehlern, die durch die Phasenjustierung hervorgerufen werden, zu unterscheiden. Die vorliegende Ausführungsform verwendet jedoch nicht einen Plattenfaktor, wie Fingerabdrücke. Daher bietet die vorliegende Ausführungsform einen höheren Grad an Justiergenauigkeit als die erste und die zweite Ausführungsform und ermöglicht es, den Spielraum für NRZ- und CLK-Phasenfehler zu vergrößern.

[0063] Nun wird eine vierte Ausführungsform der vorliegenden Erfindung beschrieben. Es wird angenommen, dass die Konfiguration eines optischen Plattenapparats gemäß der vierten Ausführungsform jener gemäß der ersten Ausführungsform gleicht, die in [Fig. 5](#) dargestellt ist. Es wird auch angenommen, dass ein Lasertreiber 201 ein NRZ/CLK-Phasenjustierungs-Überwachungssignal CDMON an einen Mikrocomputer 204, der Verzögerungsvorrichtungen 401, 402 steuert, ausgibt.

[0064] [Fig. 12](#) zeigt die Konfiguration eines Lasertreibers 201 gemäß der vierten Ausführungsform. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 3](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Die verwendete Konfiguration unterscheidet sich von derjenigen in [Fig. 3](#) in der Hinsicht, dass ein Block 3201, der die gleiche Funktion hat wie der Markierung/Zwischenraum-Längendetektor 301 in [Fig. 3](#), das Überwachungssignal CDMON für die NRZ/CLK-Phasenjustierung ausgibt. Als das CDMON-Signal wird eine durch CLK innerhalb des Markierung/Zwischenraum-Längendetektors abgetastete Wellenform in Bezug auf ein eingegebenes NRZ-Signal ausgegeben.

[0065] [Fig. 13](#) zeigt CDMON-Ausgangswellenfor-

men gemäß der vorliegenden Ausführungsform. [Fig. 14](#) ist ein Flussdiagramm, das zeigt, wie die veränderlichen Verzögerungsvorrichtungen **401**, **402** Justierungen vornehmen. Die zum Justieren der Phasenbeziehung zwischen NRZ und CLK gemäß der vorliegenden Ausführungsform ausgeführte Operation wird nun mit Bezug auf diese Darstellungen beschrieben.

**[0066]** Zuerst wird ein bekanntes festes Mustersignal in einen NRZ-Eingang des Lasertreibers eingegeben. Gemäß der vorliegenden Ausführungsform wird ein 5T-5T-Muster eingegeben. Als nächstes werden die anfänglichen Verzögerungsgrößen  $Td1$ ,  $Td2$  für DL1 (**401**) und DL2 (**402**) so festgelegt, dass die Verzögerungsjustiergröße  $Td$ , die in der ersten Ausführungsform definiert wurde, 0 ist. In dem sich ergebenen Zustand wird der Mikrocomputer **204** verwendet, um zu verifizieren, dass die Signalausgabe vom CDMON nicht 5T-5T ist. Anschließend werden die Verzögerungsgrößen  $Td1$ ,  $Td2$  von DL1 und DL2 variiert, um die Verzögerungsjustiergröße  $Td$  zum Bestimmen der Verzögerungsjustiergröße  $Td = d2$ , bei der das CDMON-Signal 5T-5T ist, zu erhöhen. Der Wert  $Td$  wird dann erhöht, bis das CDMON-Signal nicht mehr 5T-5T ist, um die Verzögerungsjustiergröße  $Td = d3$  zu bestimmen, bei der das CDMON-Signal nicht mehr 5T-5T ist. Der Bereich zwischen den Verzögerungsjustiergrößen  $d2$  und  $d3$  stellt die NRZ/CLK-Phasenbeziehung dar, die eine richtige NRZ-Datenabtastung bereitstellt. Zum Maximieren des Spielraums für NRZ/CLK-Phasenänderungen werden die Verzögerungsgrößen  $Td1$ ,  $Td2$  von DL1 und DL2 justiert, bis die Verzögerungsjustiergröße  $Td$  die folgende Gleichung erfüllt. Wenn die Gleichung erfüllt ist, ist die NRZ/CLK-Phasenjustierung abgeschlossen.

$$dT = dset = (d2 + d3)/2$$

**[0067]** Die vorliegende Ausführungsform erzeugt die gleiche Wirkung wie die Ausführungsformen eins bis drei gemäß der vorliegenden Erfindung. Ferner benötigt die vorliegende Ausführungsform, anders als die dritte Ausführungsform, keine Takte mit einer Frequenz, die innerhalb des Lasertreibers mit  $n$  multipliziert wird. Daher verringert die vorliegende Ausführungsform nicht nur den für das Justieren benötigten Leistungsverbrauch, sondern unterdrückt auch die Erzeugung von Wärme. Daher ermöglicht sie das Vermeiden einer Verformung im PUH-Fall und anderer Probleme, die sich aus der lokalen Wärmeerzeugung durch den Lasertreiber innerhalb des PUHs ergeben können.

**[0068]** Eine fünfte Ausführungsform der vorliegenden Erfindung wird nun beschrieben. Es wird angenommen, dass die Konfiguration eines optischen Plattenapparats gemäß der fünften Ausführungsform jener gemäß der ersten Ausführungsform gleicht, die

in [Fig. 5](#) dargestellt ist. Es wird auch angenommen, dass ein Lasertreiber **201** ein NRZ/CLK-Phasenjustierungs-Überwachungssignal SKMON an einen Mikrocomputer **204**, der Verzögerungsvorrichtungen **401**, **402** steuert, ausgibt.

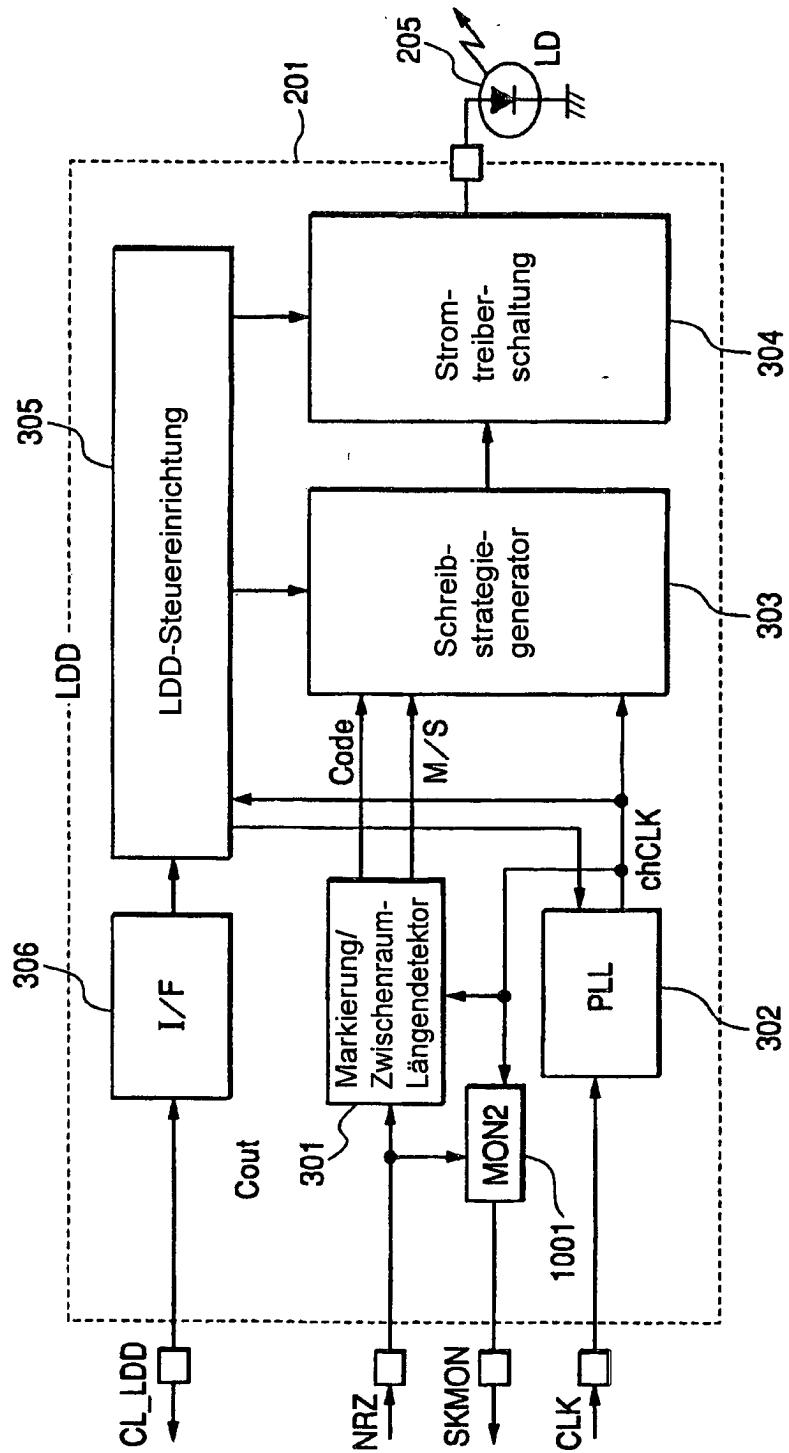

**[0069]** [Fig. 15](#) zeigt die Konfiguration eines Lasertreibers **201** gemäß der fünften Ausführungsform. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 3](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Der in [Fig. 15](#) dargestellte Lasertreiber unterscheidet sich von jenem in [Fig. 3](#) in der Hinsicht, dass der erstgenannte zusätzlich mit einem Block MON2 versehen ist, der ein Überwachungssignal SKMON für die NRZ/CLK-Phasenjustierung von NRZ und des internen Takts chCLK erzeugt.

**[0070]** [Fig. 1](#) ist ein Schaltplan, der den vorstehend erwähnten Block MON2 und seine Peripherievorrichtungen zeigt. Die Bezugszahl **101** in der Figur gibt einen D-Flipflop **101** an, der ein Überwachungssignal SKMON für die NRZ/CLK-Phasenjustierung erzeugt.

**[0071]** [Fig. 16](#) ist ein Flussdiagramm, das die NRZ/CLK-Phasenjustieroperation gemäß der vorliegenden Ausführungsform zeigt. Die Operation gemäß der vorliegenden Ausführungsform wird nun mit Bezug auf [Fig. 16](#) beschrieben. Die vorliegende Ausführungsform nimmt an, dass die NRZ-Abtastung wie im Fall der ersten Ausführungsform der vorliegenden Erfindung an einer ansteigenden Flanke von CLK erfolgt.

**[0072]** Zuerst wird die SKMON-Ausgabe gespeichert (**1201**), während die Verzögerungsgrößen  $Td1$ ,  $Td2$  von DL1 (**401**) und DL2 (**402**), die für die erste Ausführungsform definiert sind, variiert werden, um die Verzögerungsjustiergröße  $Td$  von 0 zu  $d1$  (Maximalwert) zu ändern. Als nächstes wird das Speicherergebnis geprüft, um festzustellen, ob der Flankenzählwert 0, 1, 2 oder 3 ist (**1202**–**1204**). Anschließend wird eine geeignete Steuerung für den bestimmten Flankenzählwert ausgeführt (**1205**–**1208**).

1. Wenn der Flankenzählwert 3 ist (Justierung 1-1, **1205**)

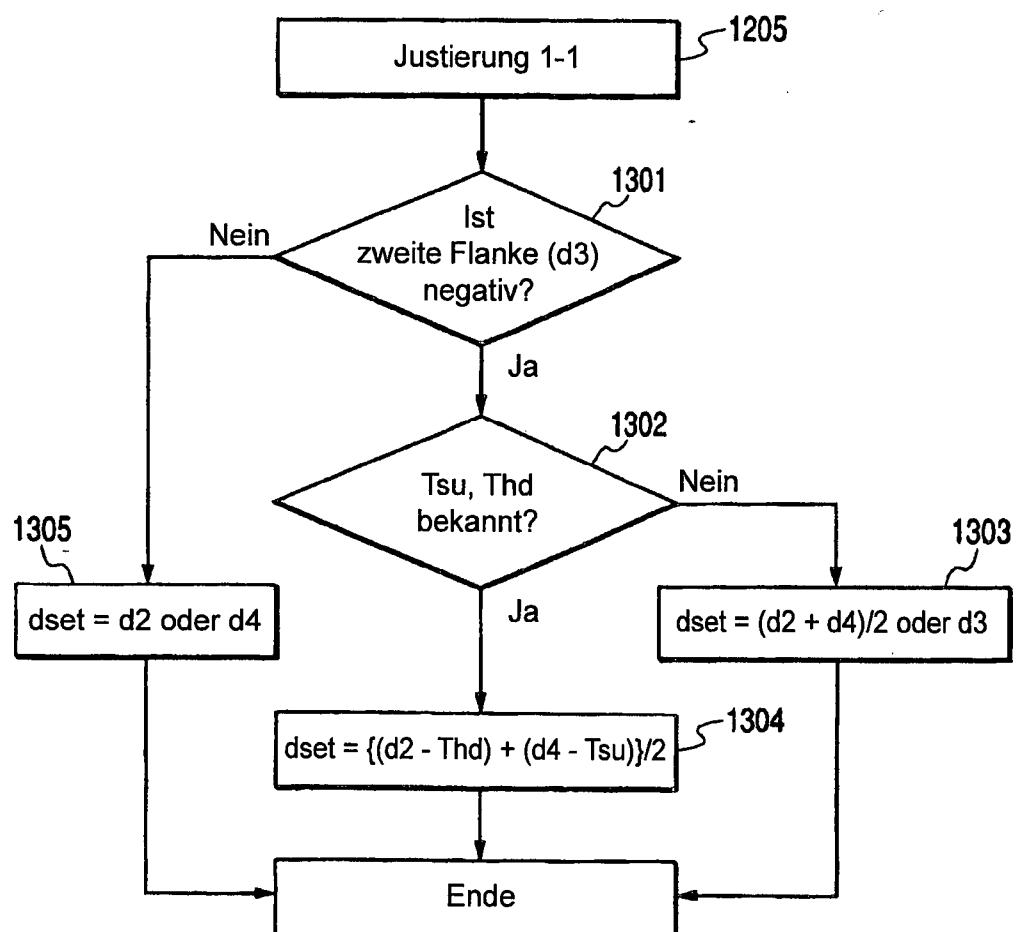

**[0073]** Dies ist ein Fall, in dem die NRZ/CLK-Verzögerungsjustierbreite größer als ein CLK-Zyklus ist. Das Flussdiagramm in [Fig. 17](#) zeigt, wie die Verzögerungsjustiergröße  $Td$  justiert wird. Zuerst wird geprüft, ob die zweite Flanke ansteigend oder abfallend ist (**1301**).

1.1 Wenn die zweite Flanke abfallend ist (**1302**)

**[0074]** Dies ist ein Fall, in dem der DSP **203** eine Synchronisation erreicht, wie in [Fig. 18](#) dargestellt

ist, wenn die NRZ- und CLK-Phasen abfallend sind (in entgegengesetzter Phase zu einer Abtast-Flanke) und der DSP intern gewährleistet, dass eine NRZ-Flanke mit einer Verzögerung einer festen Zeit  $dT2$  nach einer abfallenden Flanke von CLK zeitlich festgelegt ist. Weil die NRZ/CLK-Phasenjustierung vorgenommen wird, während die vom DSP ausgegebenen NRZ- und CLK-Phasen als Anfangspunkte behandelt werden, ist die zweite Flanke im vorstehend erwähnten Fall eine abfallende Flanke. In dieser Situation wird der Zweck erreicht, wenn die NRZ-Flanke in entgegengesetzter Phase zu einer Takt-Abtast-Flanke positioniert ist. Daher werden DL1 und DL2 justiert, bis der folgende  $Td$ -Wert erhalten wird (1303):

$$Td = dset = (d2 + d4)/2$$

**[0075]** Falls der garantierte CLK-Tastgrad 50% ist, kann die Justierung so ausgeführt werden, dass der folgende  $Td$ -Wert erhalten wird:

$$Td = dset = d3$$

**[0076]** Falls die Einrichtungszeit  $Tsu$  und die Haltezeit  $Thd$  bekannt sind (1304), werden die DL1- und DL2-Verzögerungszeitwerte unter Berücksichtigung der Einrichtungszeit und der Haltezeit justiert, bis der Wert  $Td$  die folgende Gleichung erfüllt:

$$Td = dset = \{(d2 - Thd) + (d4 - Tsu)\}/2$$

**[0077]** Dadurch kann ein größerer Phasenfehlerspielraum für die Beziehung zwischen NRZ und CLK bereitgestellt werden, als wenn die Werte  $Tsu$  und  $Thd$  unbekannt sind.

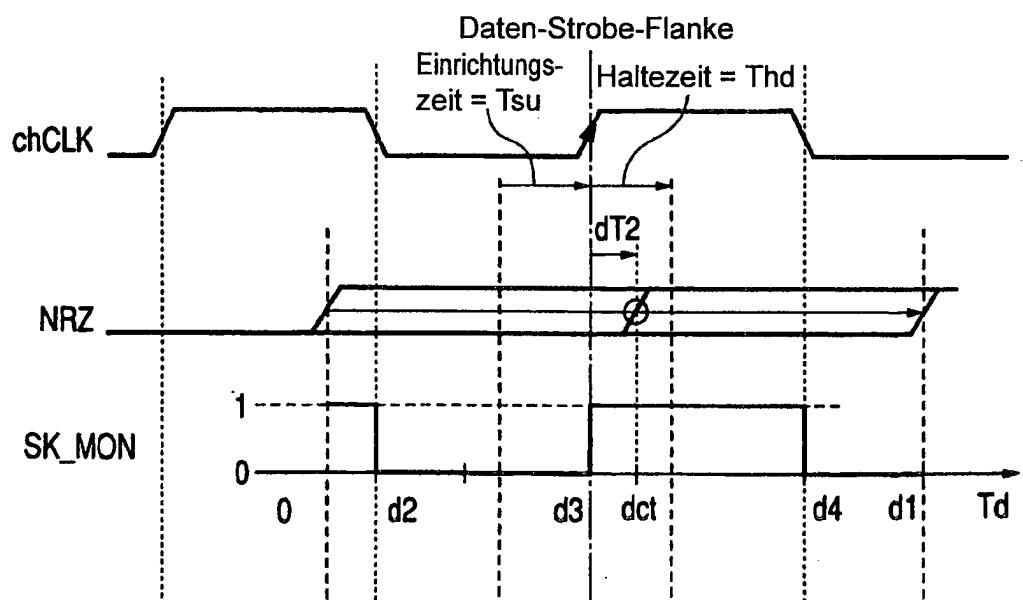

### 1.2 Wenn die zweite Flanke ansteigend ist (1305)

**[0078]** Dies ist ein Fall, in dem, wie in [Fig. 19](#) dargestellt ist, der DSP 203 eine Synchronisation erreicht, wenn die NRZ- und CLK-Phasen an einer ansteigenden Flanke (in Phase mit einer Abtast-Flanke) sind und der DSP intern gewährleistet, dass eine NRZ-Flanke mit einer Verzögerung einer festen Zeit  $dT3$  nach einer abfallenden Flanke von CLK zeitlich festgelegt ist. In dieser Situation werden die DL1- und DL2-Verzögerungsgrößen justiert, bis der folgende  $Td$ -Wert erhalten wird, um die NRZ-Flanke mit einer CLK-Flanke zu justieren, deren Phase zu einer Abtast-Flanke entgegengesetzt ist:

$$Td = dset = d2 \text{ oder } d4$$

### 2. Wenn der Flankenzählerwert 2 ist (Justierung 1-2, 1206)

**[0079]** Dies ist ein Fall, in dem die NRZ/CLK-Verzögerungsjustierbreite kleiner als ein CLK-Zyklus ist. Dieser Fall gilt beispielsweise in einer Situation, in

der die CLK-Frequenz kleiner als im Fall 1 ist. Das Flussdiagramm in [Fig. 20](#) zeigt, wie die Verzögerungsjustiergröße  $Td$  justiert wird. Zuerst wird geprüft, ob die erste Flanke ansteigend oder abfallend ist (1601).

#### 2.1 Wenn die erste Flanke abfallend ist (1602)

**[0080]** Dieser Fall ähnelt dem in [Fig. 21](#) dargestellten Fall 1.1. Weil die NRZ/CLK-Phasenjustierung ausgeführt wird, während die vom DSP ausgegebenen NRZ- und CLK-Phasen als Anfangspunkte behandelt werden, ist die erste Flanke eine abfallende Flanke. In dieser Situation wird der Zweck erreicht, wenn die NRZ-Flanke in entgegengesetzter Phase zu einer Takt-Abtast-Flanke positioniert wird. Daher werden die DL1- und DL2-Verzögerungsgrößen justiert, bis der folgende  $Td$ -Wert erhalten wird:

$$Td = dset = d2$$

#### 2.2 Wenn die erste Flanke ansteigend ist (1603)

**[0081]** Dieser Fall ähnelt dem in [Fig. 22](#) dargestellten Fall 1.2. Weil die Position mit einer entgegengesetzten Phase zu einer Takt-Abtast-Flanke in der gleichen Weise wie vorstehend beschrieben bestimmt werden kann, wird der Zweck erreicht, wenn die DL1- und DL2-Verzögerungsgrößen justiert werden, bis der folgende  $Td$ -Wert erhalten wurde:

$$Td = dset = d3$$

#### 3. Wenn der Flankenzählerwert 1 ist (Justierung 1-3, 1207)

**[0082]** Dies ist ein Fall, in dem die NRZ/CLK-Verzögerungsjustierbreite kleiner als ein CLK-Zyklus ist, wie in der Beschreibung von Fall 2 erklärt wurde. Das Flussdiagramm in [Fig. 23](#) zeigt, wie die Verzögerungsjustiergröße  $Td$  justiert wird. Zuerst wird geprüft, ob die erste Flanke ansteigend oder abfallend ist (1901).

#### 3.1 Wenn die erste Flanke abfallend ist (1902)

**[0083]** Dieser Fall ähnelt dem in [Fig. 24](#) dargestellten Fall 1.1. Weil die Position mit einer entgegengesetzten Phase zu einer Takt-Abtast-Flanke in der gleichen Weise wie vorstehend beschrieben bestimmt werden kann, wird der Zweck erreicht, wenn die DL1- und DL2-Verzögerungsgrößen justiert werden, bis der folgende  $Td$ -Wert erhalten wurde:

$$Td = dset = d2$$

#### 3.2 Wenn die erste Flanke ansteigend ist (1903)

**[0084]** Dieser Fall ähnelt dem in [Fig. 25](#) dargestellten Fall 1.2. Die Position mit einer entgegengesetzten

Phase zu einer Takt-Abtast-Flanke kann jedoch nicht bestimmt werden. Daher sollte der Abstand zwischen der NRZ-Flanke und der CLK-Abtast-Flanke maximiert werden. Zum Erreichen dieses Zwecks wird die Phasendifferenz zwischen der NRZ-Flanke und der CLK-Abtast-Flanke bestimmt (1903), wenn die Verzögerungsjustiergröße  $Td = 0$  ist und  $Td = d1$  ist (maximal). Falls die Phasendifferenz größer als  $Td = 0$  ist, werden die DL1- und DL2-Verzögerungsgrößen so justiert, dass  $Td = 0$  ist. Falls dagegen die Phasendifferenz größer als  $Td = d1$  ist, werden die DL1- und DL2-Verzögerungsgrößen so justiert, dass  $Td = d1$  ist.

4. Wenn der Flankenzählwert 0 ist (Justierung 1-4, 1208)

[0085] Dies ist ein Fall, in dem die NRZ/CLK-Verzögerungsjustierbreite kleiner als die Hälfte des CLK-Zyklus ist. Das Flussdiagramm in [Fig. 26](#) zeigt, wie die Verzögerungsjustiergröße  $Td$  justiert wird. Wenn die SKMON-Ausgabe verwendet wird und die Flanke 0 ist, ist die Beziehung zwischen der NRZ-Flanke und der CLK-Flanke unbekannt. Daher wird die Beziehung zwischen der NRZ-Flanke und der CLK-Flanke anhand des Zustands (1 oder 0) der SKMON-Ausgabe abgeleitet. Die Verzögerungsjustiergröße wird dann entsprechend der NRZ/CLK-Flankenbeziehung bestimmt (2201).

4.1 Wenn  $SKMON = 1$  ist (2202)

[0086] In diesem Fall ist der Bereich der durch eine  $Td$ -Änderung hervorgerufenen NRZ-Flankenvariation nach einer Abtast-Flanke positioniert, wie in [Fig. 27](#) dargestellt ist. Daher wird der Zweck erreicht, wenn die DL1- und DL2-Verzögerungsgrößen justiert werden, bis der Wert  $Td$  gleich  $d1$  ist (maximal).

4.2 Wenn  $SKMON = 0$  ist (2203)

[0087] In diesem Fall ist der Bereich der durch eine  $Td$ -Änderung hervorgerufenen NRZ-Flankenvariation vor einer Abtast-Flanke positioniert, wie in [Fig. 28](#) angegeben ist. Daher wird der Zweck erreicht, wenn die DL1- und DL2-Verzögerungsgrößen justiert werden, bis der Wert  $Td$  gleich 0 ist (minimal).

[0088] Wie vorstehend beschrieben wurde, erzeugt die vorliegende Ausführungsform nicht nur die gleiche Wirkung wie die Ausführungsformen eins bis vier, sondern sie führt auch zu den folgenden Verbesserungen:

- (1) Die vorliegende Ausführungsform unterscheidet sich dadurch von den Ausführungsformen eins bis drei, dass sie weder eine Eingabe mit einem festen Muster noch ein anderes spezielles Signal für den Lasertreiber benötigt.

- (2) In erheblichem Kontrast zur zweiten Ausführungsform benötigt die vorliegende Ausführungs-

form keinen schnellen Takt für die Flankenintervallmessung und kann den Leistungsverbrauch und das Ausmaß der Wärmeerzeugung verringern.

(3) Die vorliegende Ausführungsform unterscheidet sich von den Ausführungsformen eins und zwei dadurch, dass sie Verzögerungsjustierungen vornehmen kann, ohne von der Phasenbeziehung zwischen den durch den DSP erzeugten NRZ- und CLK-Ausgaben abzuhängen.

[0089] Ferner kann die optimale NRZ-Flankenposition innerhalb eines Justierbereichs selbst dann festgestellt werden, wenn der NRZ-Phasenjustierbereich schmäler als ein CLK-Zyklus ist.

[0090] [Fig. 29](#) zeigt die Konfiguration eines optischen Plattenapparats gemäß einer sechsten Ausführungsform der vorliegenden Erfindung. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 5](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet: [Fig. 30](#) zeigt die Konfiguration eines Lasertreibers 201 gemäß der vorliegenden Ausführungsform. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 15](#) angegebenen Gegenstücke, sind mit den gleichen Bezugszahlen wie diese bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Die vorliegende Ausführungsform unterscheidet sich von der fünften Ausführungsform der vorliegenden Erfindung dadurch, dass die veränderlichen Verzögerungsvorrichtungen DL1 und DL2 für die NRZ/CLK-Phasenjustierung, die sich an einer Stufe vor dem Lasertreiber 201 befinden, in den Lasertreiber aufgenommen sind und als DL3 bzw. DL4 (2701, 2702) bezeichnet sind. Das Verfahren für das Justieren der veränderlichen Verzögerungsvorrichtungen DL3 und DL4 gleicht jenem für die fünfte Ausführungsform.

[0091] Die vorliegende Ausführungsform erzeugt die gleiche Wirkung wie die fünfte Ausführungsform und verwendet eine kleinere Anzahl von Bestandteilen für den optischen Plattenapparat als die fünfte Ausführungsform. Daher trägt die vorliegende Ausführungsform dazu bei, die Geräte zu verkleinern und die Kosten zu verringern. Für das Justieren der veränderlichen Verzögerungsvorrichtungen DL3 und DL4 kann die vorliegende Ausführungsform das gleiche Verfahren wie die fünfte Ausführungsform verwenden, sie erzeugt die gleiche Wirkung jedoch selbst dann, wenn sie das gleiche DL3/DL4-Justierverfahren wie die Ausführungsformen eins bis vier verwendet.

[0092] [Fig. 31](#) ist ein Schaltplan, der eine PLL im Lasertreiber und einen Markierung/Zwischenraum-Detektorblock gemäß einer siebten Ausführungsform der vorliegenden Erfindung zeigt. Die vorliegende Ausführungsform gleicht der sechsten Aus-

führungsform in Bezug auf die Konfiguration des optischen Plattenapparats und des Lasertreibers. Der Unterschied zwischen der vorliegenden Ausführungsform und der sechsten Ausführungsform besteht darin, dass in der erstgenannten die veränderliche Verzögerungsvorrichtung DL4 (2702) für die CLK-Phasenjustierung fortgelassen ist und die veränderliche Verzögerungsvorrichtung DL5 (2801) für die Phasenjustierung für die PLL-Ausgabe des internen Takts chCLK, der durch die PLL 302 mit CLK synchronisiert ist, bereitgestellt ist. Das Verfahren zum Justieren der veränderlichen Verzögerungsvorrichtungen DL3 und DL4 gleicht jenem gemäß der fünften Ausführungsform.

**[0093]** Die vorliegende Ausführungsform erzeugt die gleiche Wirkung wie die sechste Ausführungsform. Weil ein interner Takt im Allgemeinen ein höheres Maß der Stabilität des Tastgrads bereitstellt als ein externer Takt, bietet die Konfiguration gemäß der vorliegenden Ausführungsform ein höheres Maß an CLK/NRZ-Phasenjustiergenauigkeit als jene gemäß der fünften Ausführungsform. Daher kann ein vergrößerter Spielraum für eine Phasenverschiebung zwischen NRZ und CLK bereitgestellt werden. Für das Justieren der veränderlichen Verzögerungsvorrichtungen DL3 und DL4 kann die vorliegende Ausführungsform das gleiche Verfahren wie die fünfte Ausführungsform verwenden, sie erzeugt die gleiche Wirkung jedoch selbst dann, wenn sie das gleiche DL3/DL4-Justierverfahren wie die Ausführungsformen eins bis vier verwendet.

**[0094]** [Fig. 32](#) zeigt ein Blockdiagramm eines Lasertreibers gemäß einer achten Ausführungsform der vorliegenden Erfindung. Bestandteile, die die gleichen Funktionen haben wie die in [Fig. 30](#), welche die sechste Ausführungsform beschreibt, dargestellten Gegenstücke, sind mit den gleichen Bezugszahlen wie die Gegenstücke in [Fig. 30](#) bezeichnet, und es wird hier auf ihre Beschreibung verzichtet. Die Konfiguration des optischen Plattenapparats gemäß der achten Ausführungsform ähnelt der in [Fig. 29](#) dargestellten Konfiguration, abgesehen davon, dass die erstgenannte das Überwachungssignal SKMON nicht aufweist, das der Lasertreiber 201 zum Mikrocomputer 204 sendet. Der Unterschied zwischen [Fig. 29](#) und [Fig. 32](#) ist folgender:

1. Der SKMON-Ausgang vom MON2-Block 1001 zum Mikrocomputer 204, der sich außerhalb des Lasertreibers befindet, ist fortgelassen.

2. Ein Verzögerungssteuerblock 2901 ist hinzugefügt, so dass die Verzögerungsgrößen der veränderlichen Verzögerungsschaltungen 2701, 2702 entsprechend dem durch den MON2-Block erzeugten Ausgangssignal 2902 automatisch und ohne Kommunikation mit dem Mikrocomputer 203 justiert werden.

**[0095]** Gemäß der vorliegenden Ausführungsform

wird durch die Verzögerungsschaltungen 2701, 2702 die gleiche Verzögerungsgrößen-Justiersequenz verfolgt wie gemäß der fünften Ausführungsform.

**[0096]** Die vorliegende Ausführungsform erzeugt die gleiche Wirkung wie die fünfte Ausführungsform. Zusätzlich benötigt die vorliegende Ausführungsform weniger Verbindungsleitungen zwischen dem Lasertreiber 201 und dem Mikrocomputer 204 zum Steuern des Lasertreibers und verwendet eine geringere Anzahl von FPC-Verdrahtungsleitungen als die vierte Ausführungsform. Ferner benötigt die vorliegende Ausführungsform eine kürzere Steuerzeitperiode als die vierte Ausführungsform, weil der Mikrocomputer und andere Komponenten nicht an der Justierung beteiligt sind. Zum Justieren der veränderlichen Verzögerungsvorrichtungen DL3 und DL4 kann die vorliegende Ausführungsform das gleiche Verfahren wie die fünfte Ausführungsform verwenden, sie erzeugt jedoch selbst dann die gleiche Wirkung, wenn sie das gleiche DL3/DL4-Justierverfahren wie die Ausführungsformen eins bis vier und sieben verwendet. Ferner kann die vorliegende Ausführungsform die gleiche Einfügeposition für die veränderliche Verzögerungsvorrichtung wie die sechste Ausführungsform verwenden, sie erzeugt jedoch selbst dann die gleiche Wirkung, wenn sie die gleiche Einfügeposition für die veränderliche Verzögerungsvorrichtung wie die achte Ausführungsform verwendet.

**[0097]** Gemäß den Ausführungsformen eins bis acht, bei denen das NRZ- bzw. das CLK-Signal einer Phasenjustierung durch veränderliche Verzögerungsschaltungen für NRZ/CLK-Phasenjustierzwecke unterzogen werden, kann die gleiche Wirkung selbst dann erzeugt werden, wenn entweder das NRZ- oder das CLK-Signal einer Phasenjustierung durch die veränderlichen Verzögerungsschaltungen unterzogen wird.

**[0098]** In der vorstehenden Beschreibung wird das NRZ-Signal als ein Beispiel eines Binärsignals verwendet. Es ist jedoch selbstverständlich, dass nicht nur das NRZ-Signal, sondern auch ein NRZI- oder anderes Signal als das Binärsignal für die vorliegende Erfindung verwendet werden kann.

**[0099]** Die vorliegende Erfindung betrifft einen Lasertreiber für einen optischen Plattenapparat mit einem als Aufzeichnungsstrategie bekannten Mittel zum Erzeugen einer Aufzeichnungswellenform anhand eines Aufzeichnungstaktsignals und des aufzuzeichnenden modulierten Signals, und sie ermöglicht das Justieren der Phasen eines Aufzeichnungstaktsignals und des von einem DSP oder einer anderen Einrichtung für die Erzeugung eines modulierten Signals gesendeten modulierten Signals, um die Möglichkeit eines Aufzeichnungsstrategie-Erzeugungsfehlers zu verringern, der sich aus einer unangemessenen Phasenbeziehung zwischen den beiden Sig-

nalen ergeben kann.

### Patentansprüche

1. Optischer Plattenapparat, ausgestattet mit einem Lasertreiber (201) zum Erzeugen einer Treiberwellenform, die eine Laserdiode (205) entsprechend einem binären Aufzeichnungssignal und einem Aufzeichnungstaktsignal ansteuert, wobei das binäre Aufzeichnungssignal zur Aufzeichnung auf einem Aufzeichnungsmedium (207) ausgelegt ist, und wobei der optische Plattenapparat aufweist:

eine Binäraufzeichnungssignal-Verzögerungsschaltung (401) zur Durchführung eines Verzögerungsvorgangs an dem binären Aufzeichnungssignal entsprechend einem Steuersignal,

wobei der optische Plattenapparat **dadurch gekennzeichnet** ist, dass er ferner aufweist:

eine Aufzeichnungstaktsignal-Verzögerungsschaltung (402) zur Durchführung eines Verzögerungsvorgangs an dem Aufzeichnungstaktsignal entsprechend dem Steuersignal,

wobei die von den beiden Verzögerungsschaltungen erzeugten Verzögerungsgrößen so geändert werden, dass sie die relative Zeit zwischen den Kanten des binären Aufzeichnungssignals und des Aufzeichnungstaktsignals justieren.

2. Optischer Plattenapparat nach Anspruch 1, wobei die Verzögerungsschaltungen in dem Lasertreiber eingebaut sind.

3. Optischer Plattenapparat, ausgestattet mit einem Lasertreiber (201) zum Erzeugen einer Treiberwellenform, die eine Laserdiode (205) entsprechend einem binären Aufzeichnungssignal und einem Aufzeichnungstaktsignal ansteuert, wobei das binäre Aufzeichnungssignal zur Aufzeichnung auf einem Aufzeichnungsmedium (207) ausgelegt ist, wobei der Lasertreiber (201) aufweist:

eine Binäraufzeichnungssignal-Verzögerungsschaltung (2701) zur Durchführung eines Verzögerungsvorgangs an dem binären Aufzeichnungssignal, und eine Phasensynchronisiereinrichtung (302), wobei der optische Plattenapparat dadurch gekennzeichnet ist, dass die Phasensynchronisiereinrichtung zum Synchronisieren der Phase des dem Lasertreiber zuführenden Aufzeichnungstaktsignals und der Phase eines internen Taktsignals des Lasertreibers dient, und der Lasertreiber ferner aufweist:

eine Interntaktausgangs-Verzögerungsschaltung (2801), die einem Interntaktausgang der Phasensynchronisiereinrichtung nachgeschaltet ist, und wobei die von der Interntaktausgangs-Verzögerungsschaltung (2801) erzeugte Verzögerungsgröße zum Justieren der relativen Zeit zwischen den Kanten des binären Aufzeichnungssignals und des Aufzeichnungstaktsignals geändert wird und die von den beiden Verzögerungsschaltungen erzeugten Verzögerungsgrößen so geändert werden, dass die relative

Zeit zwischen den Kanten des binären Aufzeichnungssignals und des Aufzeichnungstaktsignals justiert wird.

4. Phasenjustierverfahren, das entsprechend einem eingegebenen Binärsignal und einem Taktsignal beim Erfassen des Wertes des Binärsignals verwendet wird, wobei das Verfahren umfasst:

einen Binäraufzeichnungssignal-Verzögerungsvorgang zur Durchführung eines Verzögerungsvorgangs an dem Binäraufzeichnungssignal entsprechend einem Steuersignal,

dadurch gekennzeichnet, dass das Verfahren ferner umfasst:

einen Aufzeichnungstaktsignal-Verzögerungsvorgang zur Durchführung eines Verzögerungsvorgangs an dem Aufzeichnungstaktsignal entsprechend dem Steuersignal,

wobei die Verzögerungsvorgänge während der Änderung der Verzögerungsgrößen für das binäre Aufzeichnungssignal und das Aufzeichnungstaktsignal ein Binärsignal erfassen, mit diesem ein eingegebenes bekanntes Binärsignal vergleichen und die auf das binäre Aufzeichnungssignal und das Aufzeichnungstaktsignal anzuwendenden Verzögerungsgrößen justieren.

5. Lasertreiber (201) zum Erzeugen einer Treiberwellenform, die eine Laserdiode (205) entsprechend einem binären Aufzeichnungssignal und einem Aufzeichnungstaktsignal ansteuert, wobei das binäre Aufzeichnungssignal zur Aufzeichnung auf einem Aufzeichnungsmedium (207) ausgelegt ist, und wobei der Lasertreiber aufweist:

eine Binäraufzeichnungssignal-Verzögerungsschaltung (401) zur Durchführung eines Verzögerungsvorgangs an dem binären Aufzeichnungssignal, wobei der Lasertreiber dadurch gekennzeichnet ist, dass er ferner aufweist:

eine Aufzeichnungstaktsignal-Verzögerungsschaltung (402) zur Durchführung eines Verzögerungsvorgangs an dem Aufzeichnungstaktsignal, und eine Eingabeeinrichtung zum Eingeben eines Steuersignals, das die Verzögerungsgröße der Binäraufzeichnungssignal-Verzögerungsschaltung oder der Aufzeichnungstaktsignal-Verzögerungsschaltung steuert,

wobei die Verzögerungsgröße mindestens einer der Verzögerungsschaltungen entsprechend dem Steuersignal geändert wird, um die relative Zeit zwischen den Kanten des binären Aufzeichnungssignals und des Aufzeichnungstaktsignals zu justieren.

Es folgen 27 Blatt Zeichnungen

Figur 1

Figur 2

Figur 3

*Figur 4*

Figur 5

Figur 6

Figur 7

Figur 8

Figur 9

Figur 10

Figur 11

Figur 12

Figur 13

Figur 14

Figur 15

Figur 16

Figur 17

Figur 18

Figur 19

*Figur 20*

Figur 21

Figur 22

Figur 23

Figur 24

Figur 25

Figur 26

Figur 27

Figur 28

Figur 29

Figur 30

Figur 31

Figur 32