(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6123510号

(P6123510)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

(51) Int.Cl.

F 1

G06F 12/06 (2006.01)

G06F 12/02 (2006.01)G06F 12/06 540C

G06F 12/02 580H

G06F 12/06 523C

請求項の数 7 (全 12 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-124053 (P2013-124053)  |

| (22) 出願日  | 平成25年6月12日 (2013.6.12)        |

| (65) 公開番号 | 特開2014-241107 (P2014-241107A) |

| (43) 公開日  | 平成26年12月25日 (2014.12.25)      |

| 審査請求日     | 平成28年3月10日 (2016.3.10)        |

|           |                                                   |

|-----------|---------------------------------------------------|

| (73) 特許権者 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (74) 代理人  | 100090273<br>弁理士 國分 孝悦                            |

| (72) 発明者  | 毛利 真寿<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

| 審査官 後藤 彰  |                                                   |

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のバンクを有するデータメモリと、

前記データメモリへのアクセス命令に応じてアクセスを行うプロセッサとを有し、

前記プロセッサは、

入力された前記アクセス命令が、配列のデータを配置する前記データメモリのバンクの振り分けを指定する指定情報を含むアクセス命令である場合には、前記指定情報により指定されるバンクの振り分けに応じて、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換し、変換した前記インデックスに従って前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする半導体装置。

10

## 【請求項 2】

前記プロセッサは、

入力された前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを、前記指定情報により指定されるバンクの振り分けに応じて変換するインデックス変換部を有し、

前記アクセス命令が前記指定情報を含むアクセス命令である場合には、変換したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする請求項 1 記載の半導体装置。

## 【請求項 3】

20

前記インデックス変換部は、

配列のインデックスと前記配列のデータを配置する前記バンクとの対応関係を示すテーブルと、

前記指定情報に応じて選択した前記テーブルを参照して、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する変換部とを有することを特徴とする請求項2記載の半導体装置。

**【請求項4】**

前記インデックス変換部が有する前記テーブルには、配列のインデックスの下位ビットの値と前記配列のデータを配置する前記バンクとが一意に対応するテーブルを含むことを特徴とする請求項3記載の半導体装置。 10

**【請求項5】**

前記プロセッサは、

前記アクセス命令が、前記指定情報を含むアクセス命令である場合には、変換したインデックスを選択し、前記指定情報を含むアクセス命令でない場合には、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを選択する選択部を有し、

前記選択部により選択したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行うことを特徴とする請求項2記載の半導体装置。 20

**【請求項6】**

複数のバンクを有するデータメモリと、前記データメモリへのアクセス命令に応じてアクセスを行うプロセッサとを有する半導体装置の制御方法であって、

入力された前記アクセス命令が、配列のデータを配置する前記データメモリのバンクの振り分けを指定する指定情報を含むアクセス命令である場合に、前記指定情報により指定されるバンクの振り分けに応じて、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する工程と、

変換したインデックスに基づいて前記バンクの選択を行い、前記配列に係る前記データメモリへのアクセスを行う工程とを有することを特徴とする半導体装置の制御方法。

**【請求項7】**

前記配列のインデックスを変換する工程は、

前記指定情報に応じて、配列のインデックスと前記配列のデータを配置する前記バンクとの対応関係を示すテーブルを選択する工程と、

選択した前記テーブルを参照して、前記アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換する工程とを有することを特徴とする請求項6記載の半導体装置の制御方法。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置及び半導体装置の制御方法に関する。

**【背景技術】**

**【0002】**

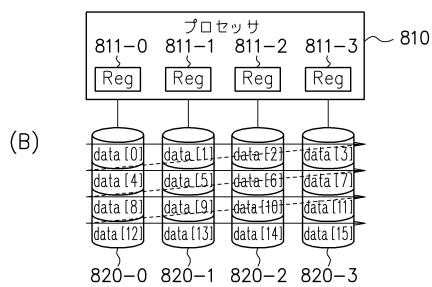

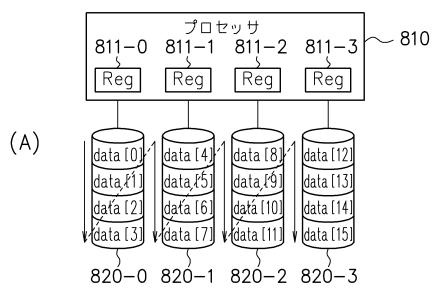

プロセッサのデータメモリの実装方法の1つに、バンクインターリーブ方式がある。バンクインターリーブ方式では、一般には2の累乗個の複数のバンク(メモリバンク)に対応するデータメモリがプロセッサに接続される。バンクインターリーブ方式において、アドレスは、図8(A)に示すように各バンクの深さ方向に連続するように割り振るのではなく、図8(B)に示すようにバンクをまたいで横方向に連続するように割り振る。バンクインターリーブ方式では、例えば、アドレスの下位ビット(4バンクであれば下位2ビット、8バンクであれば下位3ビット)で、アドレスに対応するバンクが一意に決まる。

**【0003】**

図8(A)及び図8(B)は、データメモリの実装方法の例を示す図である。図8(A) 40

50

) 及び図 8 (B) には、4つのバンクを有する例を示しており、810はプロセッサであり、820-pはデータメモリ(バンクp)(p=0、1、2、3)である。プロセッサ810は、データメモリ(バンクp)820-pとの間でデータを入出力するためのレジスタ等を含むインタフェース811-pを、データメモリ(バンクp)820-pの各々に対応して有しており、データメモリ(バンクp)820-p毎に独立してアクセスすることが可能である。

#### 【0004】

バンクインターリープ方式は、配列等の連續に並んだデータに順にアクセスする連續アクセス(シーケンシャルアクセス)が速いという利点がある。例えば、図8(C)に示すように、連続したアドレスの領域に記憶された配列dataのデータ(要素)を、data[0]、data[1]、data[2]、…、data[15]というように順に読み出して加算し、総和sumを求める処理を行うとする。

10

#### 【0005】

図8(A)に示したデータメモリの実装方式では、例えばdata[0]とdata[1]とは同じデータメモリ(バンク0)820-0上に存在しているため、同時に読み出すことができない。つまり、図8(A)に示したデータメモリの実装方式では、図8(C)に示した処理のほとんどで1サイクルに1つのデータを読み出すことしかできないため、data[0]～data[15]のすべての読み出しに13サイクルを要する。

#### 【0006】

それに対して、図8(B)に示したバンクインターリープ方式では、例えばdata[0]、data[1]、data[2]、及びdata[3]は、異なるデータメモリ(バンクp)820-p上に存在しているため、同時に読み出すことができる。つまり、図8(B)に示したバンクインターリープ方式では、図8(C)に示した処理を行う際に1サイクルに4つのデータを読み出すことが可能であるため、data[0]～data[15]のすべての読み出しに4サイクルしか要しない。

20

#### 【0007】

また、例えば配列のデータを順に書き込むシーケンシャルアクセスにおいても、図8(A)に示した実装方式では1サイクルに1つのデータを書き込むことしかできない。それに対して、図8(B)に示したバンクインターリープ方式では、1サイクルに4つのデータを書き込むことが可能である。

30

#### 【0008】

複数のプロセッサと共有メモリとを有し、メモリへのアクセス命令におけるアクセスアドレスを基に、そのアクセス命令を行うプロセッサがアクセスするメモリ領域を、アクセスアドレスに局所性がある場合にはスタック式に割り当て、アクセスアドレスに局所性がない場合にはインターリープ式に割り当てるようにした装置が提案されている(例えば、特許文献1参照)。また、インターリープされたアドレスを備えたメモリのバンクを複数有するマルチバンクメモリ型のメモリシステムが提案されている(例えば、特許文献2、3参照)。メモリシステムにおける並行性を向上させるために、複数のメモリアクセス要求を再順序付けする技術が提案されている(例えば、特許文献3参照)。

#### 【先行技術文献】

40

#### 【特許文献】

#### 【0009】

【特許文献1】特開2008-234156号公報

【特許文献2】特表2003-520368号公報

【特許文献3】特開平10-228417号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

前述したようにバンクインターリープ方式は、配列のデータに順にアクセスするシーケンシャルアクセスが速いという利点がある。しかし、アプリケーションによっては、配列

50

に対して、シーケンシャルアクセスだけでなく、連続しない順序でアクセスすることもある。例えば、無線通信の信号処理アプリケーションや暗号化アプリケーションでは、シーケンシャルアクセスだけでなく、特殊な順序のアクセスパターンでアクセスすることがある。シーケンシャルアクセスではない特殊な順序でのアクセスでは、バンクインターリーブ方式の利点が活かせないことがあり、1サイクルあたり1つのデータしかデータメモリに対する読み出しや書き込みが行えなくなってしまうことも考えられる。

#### 【0011】

本発明は、配列に対するアクセスパターンに応じて、データメモリにおける配列のデータのバンク配置を制御できるようにすることを目的とする。

#### 【課題を解決するための手段】

10

#### 【0012】

半導体装置の一態様は、複数のバンクを有するデータメモリと、データメモリへのアクセス命令に応じてアクセスを行うプロセッサとを有する。プロセッサは、入力されたアクセス命令が、配列のデータを配置するデータメモリのバンクの振り分けを指定する指定情報を含むアクセス命令である場合には、指定情報により指定されるバンクの振り分けに応じて、アクセス命令がアクセスするデータを配置するバンクに対応するインデックスを変換し、変換したインデックスに従ってバンクの選択を行い、配列に係るデータメモリへのアクセスを行う。

#### 【発明の効果】

#### 【0013】

20

開示の半導体装置は、指定されるバンクの振り分けに従って配列のデータを配置するバンクの選択を行うことで、配列に対するアクセスパターンに応じた配列のデータのバンク配置が可能になり、アプリケーションを修正することなく適切なメモリアクセスが実現でき、性能向上を図ることができる。

#### 【図面の簡単な説明】

#### 【0014】

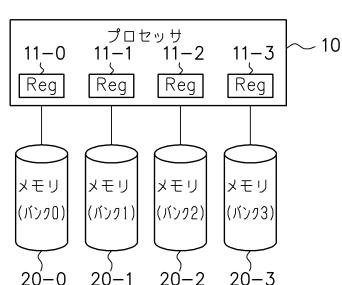

【図1】本発明の実施形態における半導体装置の構成例を示す概略図である。

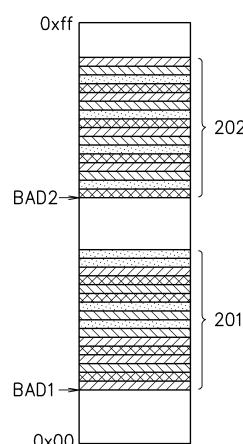

【図2】本実施形態におけるメモリマップの例を示す図である。

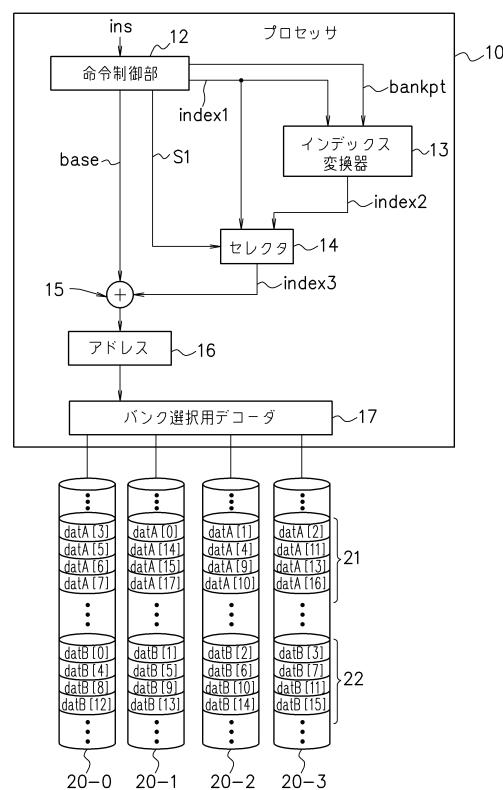

【図3】本実施形態における半導体装置の構成例を示す図である。

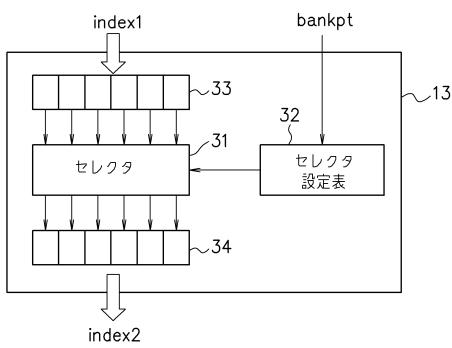

【図4】本実施形態におけるインデックス変換器の構成例を示す図である。

30

【図5】本実施形態におけるセレクタ設定表の例を示す図である。

【図6】本実施形態におけるソースコード及びアクセス命令の一例を示す図である。

【図7】本実施形態におけるメモリアクセスの例を示す図である。

【図8】データメモリの実装方法を説明するための図である。

#### 【発明を実施するための形態】

#### 【0015】

以下、本発明の実施形態を図面に基づいて説明する。

#### 【0016】

図1は、本発明の一実施形態における半導体装置の構成例を示す概略図である。本実施形態における半導体装置は、プロセッサ10及びデータメモリ(バンクp)20-pを有する。なお、pは添え字であり、p=0、1、2、3である(以下についても同様)。図1には、4つのバンクを有する例を示しているが、バンクの数は複数であれば任意であり、2の累乗個であることが好ましい。

40

#### 【0017】

プロセッサ10は、データメモリ(バンクp)20-pの各々に対応して、データメモリ(バンクp)20-pとの間でデータを入出力するためのインタフェース11-pを有する。プロセッサ10は、各インタフェース11-pにより、データメモリ(バンクp)20-p毎に独立してアクセスすることが可能である。インタフェース11-pは、データメモリ(バンクp)20-pに対する入出力データを保持するレジスタ等を有する。

#### 【0018】

50

本実施形態における半導体装置は、配列に対するデータメモリのバンクの割り振り、すなわちデータメモリにおいて配列のデータ（要素）をどのバンクに配置するかを制御可能である。例えば、データに特殊な順序でアクセスを行いたい配列は、図2の領域201に示すように、ユーザが指定するバンクパターンで配列のデータを各バンクに配置する。また、例えば、データに順にアクセスするシーケンシャルアクセスを行いたい配列は、図2の領域202に示すように、通常のバンクパターンで配列のデータを各バンクに配置する。ここで、通常のバンクパターンとは、アドレス（配列のインデックス）の下位ビットの値によりバンクが一意に決定するバンクインターリープ方式のバンクパターンであり、例えば図8（B）に示したような配置となる一定の規則を有するパターンである。

## 【0019】

10

図2は、本実施形態におけるメモリマップの例を示す図である。図2において、塗りつぶしのパターンが、データメモリにおけるバンクの違いを示している。例えば、右下がり斜線と左下がり斜線とが交差しているブロックがデータメモリのバンク0に対応し、ドット塗りつぶしのブロックがデータメモリのバンク1に対応し、右下がり斜線のブロックがデータメモリのバンク2に対応し、左下がり斜線のブロックがデータメモリのバンク3に対応する。図2に示す例では、領域201では、アドレス方向に対して任意にバンクが割り当てられ、領域202では、アドレス方向に対して順に（規則的に）バンクが割り当てられている。

## 【0020】

20

また、図2において、BAD1は領域201のベースアドレスであり、BAD2は領域202のベースアドレスである。なお、ユーザが指定するバンクパターンで配列のデータを配置する場合でも、その領域のサイズは、通常のバンクパターンで配置する際の領域のサイズと同じである。すなわち、配列のデータを配置する領域は、配列のデータを格納するのに過不足のないサイズの領域である。

## 【0021】

30

このように本実施形態では、配列のデータ（要素）のデータメモリにおけるバンク配置をユーザ指定可能にして制御することで、配列に対するアプリケーションのデータアクセスパターンに応じた配列のデータの配置が可能になる。したがって、特殊な順序で配列のデータにアクセスするアプリケーションであっても、アプリケーションを修正（変更）することなく、アプリケーションに応じたデータ配置を行うことで適切なメモリアクセスを実現することができ、性能向上を図ることができる。

## 【0022】

図3は、本実施形態における半導体装置の構成例を示す図である。図3において、図1に示した構成要素と同一の構成要素には同一の符号を付している。なお、図3には、本実施形態の半導体装置におけるデータメモリへのアクセス制御に係る構成を示したが、プロセッサ10は、データメモリに対するデータ入出力に係る構成や、一般的なプロセッサが有する、図示しない演算処理等の他の処理に係る構成も有している。

## 【0023】

プロセッサ10は、命令制御部12、インデックス変換器13、セレクタ14、加算器15、アドレス保持部16、及びバンク選択用デコーダ17を有する。命令制御部12は、図示しない命令メモリから読み出された命令insが入力され、命令insをデコードして、デコード結果に応じた処理を行う。例えば、命令制御部12は、命令insがデータメモリ（バンクp）20-pへのアクセス命令である場合には、データメモリ（バンクp）20-pに対するアクセスを行う。

## 【0024】

40

命令制御部12は、命令insが配列に係るデータメモリ（バンクp）20-pへのアクセス命令である場合には、アクセス命令で指定されたベースアドレスbase及びインデックスindexを出力する。ここで、アクセス命令で指定されるベースアドレスは、アクセスする配列に係るメモリ領域のベースアドレスであり、アクセス命令で指定されるインデックスは、アクセスする配列のデータを識別するためのインデックスである。

50

**【0025】**

また、命令制御部12は、命令`ins`が配列に係るデータメモリ(バンクp)20-pへのアクセス命令であり、さらに配列のデータのデータメモリにおけるバンクの振り分け(バンク配置)を示すバンクパターンを指定する指定情報を含むアクセス命令である場合には、その指定情報`bankpt`を出力する。また、命令制御部12は、命令`ins`がバンクの振り分けを指定するバンクパターンの指定情報を含むアクセス命令であるか否かを示す信号S1を出力する。

**【0026】**

インデックス変換器13は、命令制御部12から出力されたインデックス`index1`及びバンクパターンの指定情報`bankpt`が入力され、インデックス`index2`を出力する。インデックス変換器13は、指定情報`bankpt`により指定されるバンクの振り分け(バンクパターン)に基づいて、入力されるインデックス`index1`をインデックス`index2`に変換して出力する。10

**【0027】**

セレクタ14は、命令制御部12から出力された信号S1に基づいて、命令制御部12から出力されたインデックス`index1`又はインデックス変換器13から出力されたインデックス`index2`の一方を選択してインデックス`index3`として出力する。セレクタ14は、命令`ins`がバンクパターンの指定情報を含むアクセス命令であることを信号S1が示した場合には、インデックス`index2`をインデックス`index3`として出力する。一方、セレクタ14は、命令`ins`がバンクパターンの指定情報を含むアクセス命令ではないことを信号S1が示した場合には、インデックス`index1`をインデックス`index3`として出力する。20

**【0028】**

加算器15は、命令制御部12から出力されたベースアドレス`base`に、セレクタ14から出力されたインデックス`index3`を加算して、データメモリ(バンクp)20-pにアクセスするためのメモリアドレスを生成する。加算器15により生成されたメモリアドレスは、アドレス保持部16に保持される。バンク選択用デコーダ17は、アドレス保持部16に保持されたメモリアドレスをデコードし、デコード結果に基づいてバンクを選択してアクセスを行う。すなわち、バンク選択用デコーダ17は、セレクタ14から出力されたインデックス`index3`に応じたバンクの選択を行う。30

**【0029】**

データメモリ(バンクp)20-pには、例えば、配列`dataA`のデータ`dataA[0] ~ dataA[31]`を、図5に例示するセレクタ設定表での設定0のバンクパターンのテーブルに従ったバンク配置で配置する場合、領域21に示すように配置される。図5に例示するセレクタ設定表については、後述する。また、例えば、配列`dataB`のデータ`dataB[0] ~ dataB[31]`を、通常のバンクパターンに応じたバンク配置で配置する場合、領域22に示すように配置される。

**【0030】**

図4は、インデックス変換器13の構成例を示す図である。インデックス変換器13は、図4に示すように、セレクタ31、セレクタ設定表32、及びレジスタ33、34を有する。レジスタ33は、入力されるインデックス`index1`を保持するレジスタであり、レジスタ34は、セレクタ31の出力であるインデックス`index2`を保持するレジスタである。なお、図4においては、インデックス`index1`、`index2`が6ビットである場合を一例として示しているが、インデックス`index1`、`index2`のビット数は、これに限定されるものではない。40

**【0031】**

セレクタ31は、セレクタ設定表32が有するテーブルの内からバンクパターンの指定情報を`bankpt`に応じて選択されたバンクパターンのテーブルを参照して、インデックス`index1`をインデックス`index2`に変換し出力する。セレクタ設定表32は、図5に一例を示すような、配列のインデックスと配列のデータを配置するバンクとの対応50

関係（バンクパターン）を示すテーブルを有し、バンクパターンの指定情報 bankpt に応じて 1 つのテーブルが選択される。

#### 【0032】

図 5 は、セレクタ設定表 3 2 の例を示す図である。セレクタ設定表は、配列のインデックスに対して、配列のデータを配置するバンクを振り分けるテーブルを有している。バンクパターンの指定情報 bankpt に応じて 1 つのテーブルが選択され、インデックスに応じた配列のデータが、選択されたテーブルにより指定されたバンクに配置される。図 5 においては、ハードウェア（HW）により固定の値が設定されている設定 0 及び設定 1 のテーブルと、ソフトウェア（SW）により任意の値を設定可能な設定 2 のテーブルを有する例を示している。

10

#### 【0033】

ここで、セレクタ設定表は、すべてのテーブルをハードウェアで実現しても良いし、すべてのテーブルをソフトウェアで実現しても良い。また、セレクタ設定表の一部のテーブルをハードウェアで実現し、残りのテーブルをソフトウェアで実現しても良い。セレクタ設定表のテーブルをハードウェアにより実現する場合には、テーブルをアプリケーションに合わせて後から変更することはできないが、アプリケーションの開発者が、既存のテーブルの内からシミュレーション等でアクセス効率が高くなるようなテーブルを選択するだけで適切なメモリアクセスを実現できるアプリケーションの開発が可能になる。また、セレクタ設定表のテーブルをソフトウェアにより実現する場合には、アプリケーションの開発者がテーブルを入力しなくてはいけないが、アプリケーションに合わせたテーブルを自由に設定することができる。

20

#### 【0034】

図 6 (A) は、本実施形態における半導体装置で動作させるアプリケーションのソースコードの例を示す図である。コード 601 は、配列 proposal のデータをバンクパターン 3 に従って各バンクに配置することを指示するコードであり、コード 602、603 は、配列 proposal、normal をそれぞれ定義するコードである。なお、配列 normal は、アドレス（配列のインデックス）の下位ビットの値によりバンクが一意に決定する通常のバンクパターンで配列のデータを配置する配列である。

#### 【0035】

コード 604 は、配列 proposal におけるインデックス値 0 のデータ proposal[0] を、データメモリから読み出して変数 a に代入するコードである。また、コード 605 は、配列 proposal におけるインデックス値 4 のデータ proposal[4] を、データメモリから読み出して変数 b に代入するコードである。同様に、コード 606 は、配列 normal におけるインデックス値 0 のデータ normal[0] を、データメモリから読み出して変数 x に代入するコードである。また、コード 607 は、配列 normal におけるインデックス値 4 のデータ normal[4] を、データメモリから読み出して変数 y に代入するコードである。

30

#### 【0036】

バンクパターン 3 で配置するバンクを振り分ける配列 proposal に係るデータメモリへのアクセスには、通常の命令とは異なる特別な命令を利用することになる。例えば、コンパイラは、変数の型に基づいて、通常の命令を使用するか、特別な命令を使用するかを判別して、ソースコードをコンパイルする。

40

#### 【0037】

図 6 (B) に、バンクパターンに従って、配置するバンクを振り分ける配列 proposal のデータを読み出すためのロード命令の例を示す。配列 proposal のデータをデータメモリから読み出す命令 loadProposalにおいて、Register は読み出したデータを格納するレジスタを示し、base は配列のベースアドレスを示し、index は配列におけるインデックスを示している。また、bankPattern は、配列のバンク配置を示すバンクパターンを指定する指定情報である。

#### 【0038】

50

図3に示した命令制御部12は、入力された命令insが命令loadProposal1である場合には、命令loadProposalにおけるbase及びindexを、ベースアドレスbase及びインデックスindex1として出力する。また、命令制御部12は、命令loadProposalにおけるbankPatternを、バンクパターンの指定情報bankptとして出力するとともに、入力された命令insがバンクパターンの指定情報を含むアクセス命令であることを信号S1により示す。

#### 【0039】

また、図6(C)に、通常のバンクパターンで配置するバンクを振り分ける配列normalのデータを読み出すためのロード命令の例を示す。配列normalのデータをデータメモリから読み出す命令loadにおいて、Registerは読み出したデータを格納するレジスタを示し、baseは配列のベースアドレスを示し、indexは配列におけるインデックスを示している。

10

#### 【0040】

図3に示した命令制御部12は、入力された命令insが命令loadである場合には、命令loadにおけるbase及びindexを、ベースアドレスbase及びインデックスindex1として出力する。また、命令制御部12は、入力された命令insがバンクパターンの指定情報を含むアクセス命令ではないことを信号S1により示す。

#### 【0041】

本実施形態によれば、配列に対するデータメモリのバンクの任意な割り振りを可能にし、指定されるバンクの振り分けに従ってバンクの選択を行うことで、アプリケーションの配列に対するアクセスパターンに応じて、配列のデータのデータメモリにおけるバンク配置を制御することができる。したがって、特殊な順序で配列のデータにアクセスするアプリケーションであっても、アプリケーションを修正(変更)することなく、アプリケーションに応じたデータ配置を行うことで適切なメモリアクセスを実現することができ、性能向上を図ることができる。

20

#### 【0042】

例えば、インデックスが0～31の32個のデータ(要素)を有する配列について、インデックスが0、1、2、…、31というように1ずつ増加させて順にデータの書き込みを行うとする。その後、インデックスが0、4、8、12、16、20、24、28、1、5、9、13、17、21、25、29、2、6、10、14、18、22、26、30、3、7、11、15、19、23、27、31という順にデータの読み出しを行うとする。

30

#### 【0043】

アドレス(配列のインデックス)の下位ビットによりバンクが一意に決定するバンクインターリーブ方式の通常のバンクパターン(アドレスの下位ビットによりバンクが一意に決定するバンクインターリーブ方式のバンクパターン)で配列のデータを各バンクに配置する場合には、図7(A)に示すように、データの書き込みに8サイクルを要し、データの読み出しに29サイクルを要し、全体で37サイクルを要する。それに対して、図5に示したセレクタ設定表での設定0のバンクパターンで配列のデータを各バンクに配置する場合には、図7(B)に示すように、データの書き込みに15サイクルを要し、データの読み出しに13サイクルを要し、全体で28サイクルを要する。このように、本実施形態では、配列のデータアクセスパターンに応じて、配列のデータのバンク配置を制御することで、適切なメモリアクセスを実現することができ、メモリアクセスに要するサイクル数を低減することができる。

40

#### 【0044】

なお、前述した実施形態では、通常のバンクパターンでバンク配置する配列については通常のアクセス命令を用い、セレクタ設定表が有するテーブルのバンクパターンでバンク配置する配列については特別なアクセス命令を用いるようにして区別している。本実施形態はこれに限定されるものではなく、例えば、セレクタ設定表に、アドレス(配列のインデックス)の下位ビットの値とデータを配置するバンクとが一意に対応するバンクインタ

50

一リード方式の通常のバンクパターンのテーブルを備え、常にバンクパターンを指定するようにして1種類のアクセス命令でメモリアクセスを実現するようにしても良い。

### 【0045】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

### 【符号の説明】

#### 【0046】

- 10 プロセッサ

- 11 - 0 ~ 11 - 3 インタフェース

- 20 - 0 ~ 20 - 4 データメモリ

- 12 命令制御部

- 13 インデックス変換器

- 14 セレクタ

- 15 加算器

- 16 アドレス保持部

- 17 バンク選択用デコーダ

- 31 セレクタ

- 32 セレクタ設定表

- 33、34 レジスタ

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

| index   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 設定0(HW) | 1 | 2 | 3 | 0 | 2 | 0 | 0 | 0 | 0 | 2 | 2  | 3  | 0  | 3  | 1  | 1  | 2  | 1  | 1  | 2  | 0  | 3  | 3  | 0  | 2  | 1  | 2  | 3  |    |    |    |    |

| 設定1(HW) | 1 | 2 | 2 | 0 | 0 | 1 | 0 | 3 | 1 | 2 | 3  | 0  | 1  | 2  | 1  | 2  | 2  | 3  | 0  | 3  | 0  | 3  | 1  | 0  | 2  | 1  | 2  | 3  |    |    |    |    |

| 設定2(SW) |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

【図6】

```

#pragma bankPattn 3          ↗~601

int_proposal proposal[16];   ↗~602

int nomal[16];   ↗~603

(A) int a=proposal[0];   ↗~604

int b=proposal[4];   ↗~605

int x=nomal[0];   ↗~606

int y=nomal[4];   ↗~607

```

(B)

(C)

【図7】

|                 |   |   |   |    |    |    |    |    |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

|-----------------|---|---|---|----|----|----|----|----|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--|

| write 8(cycle)  | 0 | 1 | 2 | 3  | 4  | 5  | 6  | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |  |

| read 24(cycle)  | 0 | 4 | 8 | 12 | 16 | 20 | 24 | 28 | 1 | 5 | 9  | 13 | 17 | 21 | 25 | 29 | 2  | 6  | 10 | 14 | 18 | 22 | 26 | 30 | 3  | 7  | 11 | 15 | 19 | 23 | 27 | 31 |  |

| wrt 37(cycle)   | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 2  | 2  | 2  | 2  | 2  | 2  | 2  | 2  | 2  | 2  | 2  |    |  |

| write 15(cycle) | 0 | 1 | 2 | 3  | 0  | 2  | 0  | 0  | 0 | 1 | 2  | 3  | 0  | 1  | 1  | 3  | 1  | 2  | 1  | 1  | 2  | 0  | 3  | 1  | 3  | 0  | 1  | 2  | 3  |    |    |    |  |

| read 13(cycle)  | 0 | 4 | 8 | 12 | 16 | 20 | 24 | 28 | 1 | 5 | 9  | 13 | 17 | 21 | 25 | 29 | 2  | 6  | 10 | 14 | 18 | 22 | 26 | 30 | 3  | 7  | 11 | 15 | 19 | 23 | 27 | 31 |  |

| wrt 28(cycle)   | 1 | 2 | 0 | 0  | 3  | 1  | 3  | 2  | 2 | 0 | 2  | 3  | 1  | 1  | 3  | 1  | 3  | 0  | 2  | 1  | 2  | 3  | 2  | 0  | 0  | 3  | 1  | 1  | 0  | 3  |    |    |  |

(A)

(B)

【図8】

(C)

```

int data[16];

int sum =0;

sum += data[0];

sum += data[1];

sum += data[2];

⋮

⋮

sum += data[14];

sum += data[15];

```

---

フロントページの続き

(56)参考文献 特開平05-143326(JP,A)

特開2004-157695(JP,A)

米国特許第06553478(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 02

G 06 F 12 / 06