(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4622335号

(P4622335)

(45) 発行日 平成23年2月2日(2011.2.2)

(24) 登録日 平成22年11月12日(2010.11.12)

(51) Int.Cl.

H01S 5/042 (2006.01)

F 1

H01S 5/042 612

請求項の数 10 (全 19 頁)

(21) 出願番号 特願2004-185255 (P2004-185255)

(22) 出願日 平成16年6月23日 (2004. 6. 23)

(65) 公開番号 特開2005-72562 (P2005-72562A)

(43) 公開日 平成17年3月17日 (2005. 3. 17)

審査請求日 平成19年5月31日 (2007. 5. 31)

(31) 優先権主張番号 特願2003-285813 (P2003-285813)

(32) 優先日 平成15年8月4日 (2003. 8. 4)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000226057

日亜化学工業株式会社

徳島県阿南市上中町岡491番地100

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100117422

弁理士 堀川 かおり

(72) 発明者 米田 章法

徳島県阿南市上中町岡491番地100

日亜化学工業株式会

社内

審査官 土屋 知久

最終頁に続く

(54) 【発明の名称】半導体レーザ素子

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、第1導電型半導体層、活性層及び第2導電型半導体層がこの順に積層され、かつ前記基板に対して同一面側において、前記第1導電型半導体層に接続された第1電極及び前記第2導電型半導体層に接続された第2電極を有する半導体レーザ素子であって、

前記第2電極は、オーミック電極とパッド電極とからなり、前記オーミック電極は、前記第2導電型半導体層上におけるストライプ状の接続領域において該第2導電型半導体層とオーミック接続され、前記パッド電極は、その表面であって、前記接続領域の延長によって分けられた2つの領域の実質的に一方側においてのみ延長され、かつワイヤボンディングに十分な領域が確保されており、

前記第1電極は、平面視において、前記オーミック電極に隣接し、該オーミック電極の延設方向に沿って延設され、前記オーミック接続された領域に対して前記パッド電極と同じ一方側にのみ配置され、かつ該パッド電極と同じ側で第2電極と絶縁膜を介してオーバーラップしており、

前記第2導電型半導体層は、前記オーミック接続された領域によって分けられた領域の両側で光の閉じ込めを確保し得る0.5~20μmの範囲内の幅に設定されてなることを特徴とする半導体レーザ素子。

## 【請求項 2】

基板上に、第1導電型半導体層、活性層及び第2導電型半導体層がこの順に積層され、かつ前記基板に対して同一面側において、前記第1導電型半導体層に接続された第1電極

10

20

及び前記第2導電型半導体層に接続された第2電極を有する半導体レーザ素子であって、前記第2電極は、オーミック電極とパッド電極とからなり、前記オーミック電極は、ストライプ状に延設され、前記第2導電型半導体層上におけるストライプ状の接続領域において該第2導電型半導体層とオーミック接続され、前記パッド電極は、前記オーミック電極に電気的に接続され、少なくとも前記オーミック電極の延設方向とは異なる方向に突出しており、さらに、その表面であって、前記接続領域の延長によって分けられた2つの領域の実質的に一方側においてのみ延長され、かつ外部と電気的な接続をするための十分な領域が確保されており、

前記第1電極は、平面視において、前記オーミック電極に隣接して、該オーミック電極の延設方向に沿って延設され、前記オーミック接続された領域に対して前記パッド電極と同じ一方側にのみ配置され、かつ該パッド電極と同じ側で第2電極と絶縁膜を介してオーバーラップしていることを特徴する半導体レーザ素子。

【請求項3】

第2電極が、ストライプ状に延設されたオーミック電極と、該オーミック電極に電気的に接続され、少なくとも前記オーミック電極の延設方向とは異なる方向に突出したパッド電極とからなる請求項1に記載の半導体レーザ素子。

【請求項4】

ワイヤボンディングに十分な領域が、 $1000 \mu m^2$ 以上の面積を有してなる請求項1又は3に記載の半導体レーザ素子。

【請求項5】

外部と電気的な接続をするための十分な領域が、 $1000 \mu m^2$ 以上の面積を有してなる請求項2に記載の半導体レーザ素子。

【請求項6】

第2電極は、絶縁膜を介して第1導電型半導体層上にまで延設されてなる請求項1～5のいずれか1つに記載の半導体レーザ素子。

【請求項7】

第2導電型半導体層表面にストライプ状のリッジが形成されており、該リッジの上面において第2導電型半導体層とオーミック電極とがオーミック接続した領域を有する請求項1～6のいずれか1つに記載の半導体レーザ素子。

【請求項8】

リッジが、第2導電型半導体層の端部から、リッジ幅の2～50倍の範囲内に配置してなる請求項7に記載の半導体レーザ素子。

【請求項9】

第1電極は、第2導電型半導体層側から少なくとも該第2導電型半導体層の一部が除去されて第1導電型半導体層が露出された領域に形成されており、該露出された第1導電型半導体層が、第2導電型半導体層の幅の1/2～10倍の範囲内の幅に設定されてなる請求項1～8のいずれか1つに記載の半導体レーザ素子。

【請求項10】

第1導電型半導体層の上に、第2電極に接続された第2導電型半導体層及び活性層とは電気的に分離されたダミー層が配置されてなる請求項1～9のいずれか1つに記載の半導体レーザ素子。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体レーザ素子に関し、より詳細には、III-V族窒化物半導体を用いた半導体レーザ素子に関する。

【背景技術】

【0002】

近年、半導体レーザ素子は、小型、軽量、高信頼性及び高出力化が進み、パーソナルコンピュータ、DVD等の電子機器、医療機器等の光源に利用されている。なかでも、III

10

20

30

40

50

- V 族窒化物半導体は、比較的短波長の発光が可能であるため、盛んに研究されている。

【0003】

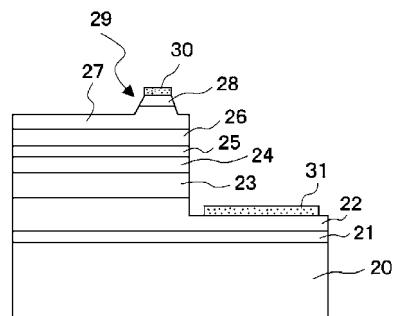

例えば、窒化物半導体を用いた半導体レーザとして、図7に示すように、サファイア基板20上に、GaN層21を介してn型GaN層22、n型AlGaNクラッド層23及びn型GaN光閉じ込め層24、活性層25（例えば、InGaN多重量子井戸層）、p型GaN光閉じ込め層26、p型AlGaNクラッド層27及びp型GaN層28がこの順に積層され、一部の領域において、p型GaN層28表面からp型AlGaNクラッド層27の深さ方向の一部でエッチングされてリッジ29が形成された半導体レーザがある（例えば、特許文献1）。

【0004】

この半導体レーザは、n型GaN層22の電気抵抗の増加に起因する動作電圧の上昇を防止するために、レーザ素子に加わる直列抵抗分を、p電極30とn電極31との距離を短くすることにより小さくして、過剰な素子の温度上昇を抑制している。これにより、動作電圧の低減及びレーザ素子の信頼性の向上が図られている。

【特許文献1】特開平10-256660号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

従来技術の半導体レーザにおいては、上述したように、直列抵抗分を低減したとしても、活性層を構成する半導体層の種類によっては、十分な特性を実現できず、素子の応用範囲に制約が生じるものがあるのが現状である。

【0006】

本発明は、上記課題に鑑みなされたものであり、どのような種類の半導体を用いたレーザ素子、特にIII-V族窒化物半導体を用いたレーザ素子においても、レーザ駆動初期のインピーダンスを安定化させ、ひいては低電流での発振、応答速度の高速化、ノイズの低減等が実現された高性能かつ高品質の半導体レーザ素子を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の半導体レーザ素子は、第1導電型半導体層、活性層及び第2導電型半導体層が積層され、かつ前記第1導電型半導体層に接続された第1電極及び前記第2導電型半導体層に接続された第2電極を有する半導体レーザ素子であって、

（1）前記第2電極は、オーミック電極とパッド電極とからなり、前記オーミック電極は、前記第2導電型半導体層上におけるストライプ状の接続領域において該第2導電型半導体層とオーミック接続され、前記パッド電極は、その表面であって、前記接続領域の延長によって分けられた2つの領域の実質的に一方側においてのみ延長され、かつワイヤボンディングに十分な領域が確保されており、

前記第1電極は、平面視において、前記オーミック電極に隣接し、該オーミック電極の延設方向に沿って延設され、前記オーミック接続された領域に対して前記パッド電極と同じ一方側にのみ配置され、かつ該パッド電極と同じ側で第2電極と絶縁膜を介してオーバーラップしてあり、

前記第2導電型半導体層は、前記オーミック接続された領域によって分けられた領域の両側で光の閉じ込めを確保し得る0.5~20μmの範囲内の幅に設定されてなるか、あるいは、

（2）前記第2電極は、オーミック電極とパッド電極とからなり、前記オーミック電極は、ストライプ状に延設され、前記第2導電型半導体層上におけるストライプ状の接続領域において該第2導電型半導体層とオーミック接続され、前記パッド電極は、前記オーミック電極に電気的に接続され、少なくとも前記オーミック電極の延設方向とは異なる方向に突出しており、さらに、その表面であって、前記接続領域の延長によって分けられた2つの領域の実質的に一方側においてのみ延長され、かつ外部と電気的な接続をするための十分な領域が確保されており、

10

20

30

40

50

前記第1電極は、平面視において、前記オーミック電極に隣接して、該オーミック電極の延設方向に沿って延設され、前記オーミック接続された領域に対して前記パッド電極と同じ一方側にのみ配置され、かつ該パッド電極と同じ側で第2電極と絶縁膜を介してオーバーラップしていることを特徴する。

## 【0008】

このような半導体レーザ素子では、

第2電極が、ストライプ状に延設されたオーミック電極と、該オーミック電極に電気的に接続され、少なくとも前記オーミック電極の延設方向とは異なる方向に突出したパッド電極とからなるか、

ワイヤボンディングに十分な領域が、 $1000 \mu m^2$ 以上の面積を有してなるか、

外部と電気的な接続をするための十分な領域が、 $1000 \mu m^2$ 以上の面積を有してなるか、

第2電極は、絶縁膜を介して第1導電型半導体層上にまで延設されてなるか、

第2導電型半導体層表面にストライプ状のリッジが形成されており、該リッジの上面において第2導電型半導体層とオーミック電極とがオーミック接続した領域を有するか、

リッジが、第2導電型半導体層の端部から、リッジ幅の2~50倍の範囲内に配置してなるか、

第1電極は、第2導電型半導体層側から少なくとも該第2導電型半導体層の一部が除去されて第1導電型半導体層が露出された領域に形成されており、該露出された第1導電型半導体層が、第2導電型半導体層の幅の1/2~10倍の範囲内の幅に設定されてなるか

10

、

第1導電型半導体層の上に、第2電極に接続された第2導電型半導体層及び活性層とは電気的に分離されたダミー層が配置されてなることが好ましい。

## 【発明の効果】

## 【0009】

本発明の半導体レーザ素子によれば、レーザ駆動初期のインピーダンスを安定化させることができる。これにより、ウォーミングアップ時間を短縮させて、レーザ光の発振をより迅速に行うことができ、半導体レーザ素子を用いた機器において、タイムロスを生じることなく、応答速度の高速化を実現することが可能となる。しかも、発振を早めることができるために、閾値を低下させ、低電流で発振させることができが可能となり、低消費電力化を実現することができる。さらに、レーザ駆動初期のインピーダンスの安定化に起因して、ノイズを低減することができる、高性能かつ高品質の半導体レーザ素子を提供することができる。

30

## 【発明を実施するための最良の形態】

## 【0010】

本発明の半導体レーザ素子は、主として、第1導電型半導体層、活性層及び第2導電型半導体層が積層されてなり、さらに、第1導電型半導体層に接続された第1電極と、第2導電型半導体層に接続された第2電極とを備えて構成されている。ここで第1導電型とは、n型又はp型を意味し、第2導電型とは、第1導電型と異なる導電型、つまりp型又はn型を意味する。

40

## 【0011】

第1導電型半導体層、活性層及び第2導電型半導体層は、この順に積層されており、通常、活性層及び第2導電型半導体層と、任意に第1導電型半導体層の膜厚方向の一部が除去されて、第1導電型半導体層が部分的に露出するように配置されている。これらの層を構成する半導体層の種類は特に限定されるものではないが、少なくともいずれか1層が、あるいは第1導電型半導体層、活性層及び第2導電型半導体層の全てが窒化物半導体からなるものが適当である。さらに、III-V族窒化物半導体からなるもの、特にGaN、AlN、InN又はこれらの混晶（例えば、 $In_xAl_yGaN_{1-x-y}$ 、 $0 < x, y < 1$ ）等が好ましい。例えば、第1導電型半導体層がn型の窒化物半導体層、第2導電型半導体層がp型の窒化物半導体層により構成されることが好ましい。ただし、第1導

50

電型及び第2導電型半導体層に含まれる全ての層がp型又はn型のいずれかの導電型を示さなくてもよい。

【0012】

第1導電型半導体層、活性層及び第2導電型半導体層（特に窒化物半導体層）は、MOCVD、MOCVD（有機金属化学気相成長法）、HYPE（ハライド気相成長法）、MBE（分子線気相成長法）等、半導体層を成長させることができる公知の方法のいずれによっても形成することができる。

【0013】

活性層は、例えば、第1導電型半導体層と第2導電型半導体層との接合面に平行な面内であって、その内部においてストライプ状に電流が狭窄された領域、いわゆる導波路を有している。この電流が狭窄された領域（あるいは導波路）は、後述する第2導電型半導体表面に形成されたリッジ（主としてストライプ状）により規定される。活性層は、単一の材料（元素又は化合物等、以下同義）での単層又は多層構造であってもよいが、異なる材料（組成元素が異なる化合物、組成元素の種類が同じで組成比が異なる化合物等、以下同義）での多層構造、特に量子井戸構造であることが好ましい。量子井戸構造は、单一量子井戸であってもよいし、多重量子井戸であってもよい。また、活性層は、Inを含む窒化物半導体層であることが好ましい。これにより、紫外線及び可視領域において青色系から赤色系の波長のレーザ光を得ることができる。

【0014】

活性層は、通常、後述する第1導電型半導体層よりも平面形状が小さく形成されており、第2導電型半導体層とほぼ同じ平面形状及び平面積で形成されていてもよいし、やや大きめ又は小さめに形成されていてもよい。また、通常、第1導電型半導体層上において、レーザ素子の一端部方向に偏って配置されていることが適当である。活性層の膜厚は、特に限定されるものではなく、例えば、0.01~1μm程度が挙げられる。また、活性層の大きさは特に限定されるものではないが、光の導波、つまり光の閉じ込めに必要な幅を確保し、さらに露出面における表面劣化等の製造工程、後述する第2導電型半導体層との容量結合等を考慮して適宜調整することが好ましい。例えば、0.5~20μm程度の幅、好ましくは1~7μm程度の幅が適当である。活性層の長さは、光の導波、共振の程度等に応じて適宜調整することができる。例えば、共振器長が200μm以上であることが適当である。

【0015】

第1導電型半導体層及び第2導電型半導体層は、活性層をサンドイッチするように配置しており、例えば、それぞれn型及びp型のクラッド層等として形成されていることが適当である。また、クラッド層の他に、第1導電型半導体層としては、クラッド層と活性層との間あるいはクラッド層の、活性層とは反対側に、光ガイド層、クラック防止層、コンタクト層、キャップ層等が、第2導電型半導体層としては、活性層とクラッド層との間あるいはクラッド層の活性層とは反対側に、電子閉じ込め層、光ガイド層、キャップ層、コンタクト層等が、1種又は2種以上組み合わせられて設けられていてもよい。

【0016】

特に、クラッド層は、光を閉じ込め及び/又はキャリアを閉じ込めることができるように、活性層（特に井戸層）よりも低い屈折率及び広いエネルギー・ギャップを有する層として形成されていることが好ましい。これらの層はA1を含有する層として形成されることがより好ましい。これらの層は、単一の材料で単層又は多層構造として形成されていてもよいし、例えば、AlGaNとGaNとを交互に積層したような、異なる材料での超格子構造であってもよい。さらに、これらの層は不純物がドープされていてもよいし、アンドープであってもよく、多層膜の場合はそれを構成する少なくとも1つの層がドープされたものであってもよい。発振波長が430~550nm程度という長波長の半導体レーザ素子では、これらクラッド層は、p型層にはp型不純物（例えば、Mg、Zn、Cd、Be、Ca、Ba等）を、n型層にはn型不純物（例えば、Si、Sn、Ge、Se、C、Ti等）をドープしたGaNが好ましい。これらの層の膜厚は、特に限定されるものではな

10

20

30

40

50

く、例えば、10 nm ~ 5 μm 程度の範囲が適当であり、さらに、50 nm ~ 2 μm 程度の範囲で、十分な光閉じ込め効果を有する。

【0017】

電子閉じ込め層は、p型クラッド層と活性層との間に配置することが好ましく、例えば、AlGaN、p型不純物をドープしたAlGaN等により形成することができる。これにより、活性層へのキャリア閉じ込め効果を増加させることができ、得られた半導体レーザ素子の閾値電流を低下させて、より容易に発振を得ることができる。膜厚は、例えば、50 nm 程度以下が適当である。

【0018】

ガイド層は、活性層を挟むように両側に配置することにより、活性層とともに電流狭窄領域、いわゆる導波路を確保することができる。ガイド層の膜厚は特に限定されるものではなく、活性層の両側に配置される場合には、両ガイド層は、同じ膜厚に形成することが好ましい。例えば、10 nm ~ 1 μm 程度が適当であり、50 nm ~ 200 nm 程度が好ましい。ガイド層を構成する半導体層は、その外側に設けられる半導体層、つまり、上述したクラッド層と比較して、導波路形成のために十分な屈折率を有していることが好ましい。ガイド層は、単一の材料での単層又は多層構造として形成されていてもよいし、異なる材料での多層構造として形成されていてもよい。例えば、発振波長が370 nm ~ 470 nm には、アンドープのGaNが好ましく、比較的長波長の領域（例えば、450 nm 以上）では、In を含む層が好ましい。具体的には、単一のInGaNからなる層、InGaNを含む超格子、例えば、InGaN/GaN、InGaN/AlGaN、InGaN/InGaN（組成比が異なる層）の多層膜を用いることが好ましい。なお、ガイド層は、活性層とともに構成する電流狭窄領域の膜厚が600 nm 程度以下となるように設定されることにより、発振閾値電流の急激な増大を抑制することができる。さらに450 nm 程度以下となるように設定することにより、低く抑えられた発振閾値電流で、基本モードでの連続発振をより長寿命化させることができる。

【0019】

第2導電型半導体層の表面には、ストライプ状のリッジが形成されていることが好ましい。リッジは、その底面側の幅が広く上面に近づくにつれてストライプ幅が小さくなる順メサ形状、逆にリッジの底面に近づくにつれてストライプの幅が小さくなる逆メサ形状、積層面に垂直な側面を有する形状であってもよいし、これらが組み合わされた形状でもよい。リッジの幅は特に限定されるものではなく、1 ~ 7 μm 程度が適当である。リッジの高さは、第2導電型半導体層の膜厚に依存して適宜調整することができ、例えば、0.2 ~ 1 μm 程度が挙げられる。なお、リッジの幅は、長手方向（共振器方向）においてすべて同じでなくてもよい。

【0020】

ストライプ状のリッジの形成位置は、このリッジによって規定される電流狭窄領域に対する一方向側に、後述するような第2電極を構成するパッド電極へのワイヤボンディングのために、あるいは、パッド電極と外部とを電気的に接続させるために（以下、単に「ワイヤボンド等のために」と記す）十分な又は適当な領域が確保されるように配置されていることが重要である。つまり、リッジ直上でのワイヤボンディング等は、ワイヤボンディング等時における押圧により、リッジ自体の割れや欠け等のダメージを招くことがある。したがって、リッジ直上でのワイヤボンディング及び接続を避けるために、電流狭窄領域、つまり、リッジの一方向側のみにおいてワイヤボンディング等を行うことができる十分な又は適当な領域を確保するように配置していることが必要である。そのために、リッジは、レーザ素子全体として捕らえた場合に、通常、他方向側に偏って配置していることが好ましい。これにより、パッド電極へのワイヤボンディング等を行うための十分な領域をリッジの一方向側において確保することができ、リッジ自体のダメージを防止することができる。

【0021】

具体的なリッジの位置は、半導体レーザ素子自体の大きさ、用いる半導体材料、得よう

10

20

30

40

50

とする性能等により適宜調整することができる。例えば、リッジは、第2導電型半導体層の幅方向の端部から、リッジ幅の2～50倍程度、2～30倍程度、さらに2～10倍程度の範囲内に配置していることが好ましい。また、別の観点から、リッジ端部と後述する第1電極端部との最小の距離が300μm程度以下、200μm程度以下、好ましくは100μm程度以下、さらに好ましくは50μm程度以下となるようにリッジが配置されていてもよい。なお、リッジは、実質的にワイヤボンディング等される領域を除いた場合に、第2導電型半導体層のほぼ中央に、共振器方向に延設されていることが好ましい。また、リッジが複数形成されるアレイレーザの場合には、第2導電型半導体層の幅方向の端部からの距離がすべてのリッジをまとめたリッジ領域の幅の2～50倍程度、2～30倍程度、さらに2～10倍程度の範囲内に配置されていることが好ましい。リッジ領域と第1電極との最小の距離は、第1電極にもっとも近いリッジとの距離が上記単一のリッジの場合と同様の範囲内に配置することが適当である。10

#### 【0022】

第2導電型半導体層は、上述した活性層と電気的に接続しており、活性層・第2導電型半導体層間（あるいは、さらに活性層・第1導電型半導体層間）の容量が、周波数・インピーダンス特性を阻害しないように設定されていることが好ましい。ここで、周波数・インピーダンス特性を阻害しないとは、通常、周波数が大きくなるにつれてインピーダンスが減少しないことを意味し、周波数が大きくなるにつれてインピーダンスが変動しないか、あるいは増加すればよい。また、第2導電型半導体層は、上述したように、通常、活性層とほぼ同じ平面形状及び平面積で形成されているため、第2導電型半導体層の上面積が、活性層におけるレーザ光の発振に影響を与えることなく、かつ、光の閉じ込めを確保し得る幅（好ましくは最小限の幅）であって、さらに、活性層・第2導電型半導体層間において小さな（好ましくは最小限の）容量に抑えるように設定されることが適当である。これにより、駆動初期のインピーダンスが安定し、より迅速にレーザ光を発振させることができ、ウォーミングアップを短くし、タイムロスなく、応答速度の速い装置を得ることができる。しかも、閾値を低下させて、低電流で発振させることができ、低消費電力の装置を得ることができる。20

#### 【0023】

第2導電型半導体層の平面形状は、矩形形状に限らず、多角形、円形、橢円形等、任意の形状とすることができ、後述するパッド電極の形状にあわせて、共振器方向とは異なる方向に突出するような形状を有していてもよい。なかでも、共振器となる2面は互いに平行であることが好ましく、さらに、側面においても互いに平行な面を含んでいることが好ましく、矩形形状であることがより好ましい。30

#### 【0024】

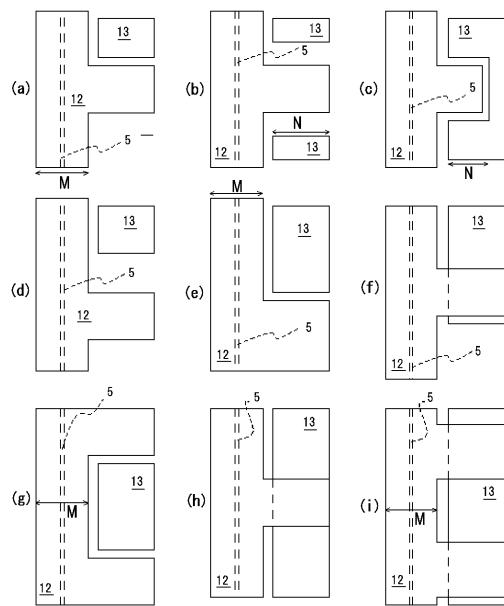

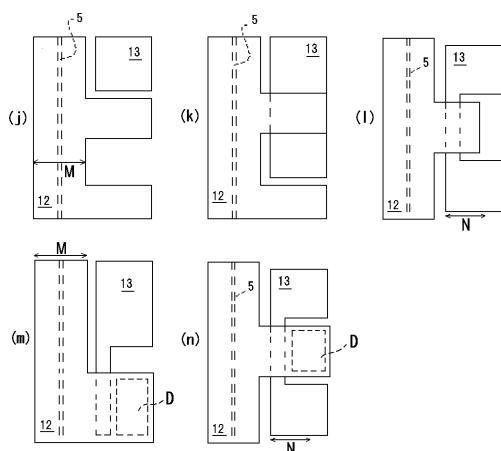

なお、本発明においては、パッド電極のワイヤボンディング等に十分な領域を無視して考えた場合、第2導電型半導体層は、主として導波路又は電流狭窄領域に一致する領域、あるいは導波路又は電流狭窄領域とそれらの外周の領域を含む領域が、本来の第2導電型半導体層として期待する機能を有しており、このような領域の幅を、第2導電型半導体層の幅として表す（例えば、図1のW）。また、図3（a）、（e）、（g）、（i）、図4（j）において、矢印Mで表した第2電極にほぼ相当する幅又は第2電極よりもやや大きな幅とすることができます。40

#### 【0025】

また、第2導電型半導体層は、表面にストライプ状のリッジを形成した後に、リッジの両側に半導体結晶を再成長させた埋め込み構造を有していてもよい。

#### 【0026】

本発明においては、第1導電型半導体層、活性層及び第2導電型半導体層の積層構造を、レーザ素子において発生する熱容量を低下させることができる構造としてもよい。例えば、活性層は、第2導電型半導体層よりも相当に大きな平面積を有しているが、分断されることにより、本来活性層として機能する領域をほぼ第2導電型半導体層と同等の大きさとして、その全体には実質的に電流が流れないように形成してもよい。第1導電型半導体50

層及び第2導電型半導体層についても、活性層とともに、あるいは、個々独立して、実質的に電流が流れないように分断してもよい。つまり、第1導電型半導体層、活性層及び／又は第2導電型半導体層が、レーザ素子構造の一部としては機能しない、レーザ発振に寄与しない、あるいは電気的に分離された、いわゆるダミー層として形成されていてもよい（例えば、図4（m）及び（n）中のD参照）。なお、ダミー層は、これら第1導電型半導体層等とは別個に形成されてもよい。ダミー層の存在により、その上に第2電極が形成される場合には、段差が緩和され、第2電極の断線等を有効に防止することができる。また、キャパシタンスを増加させることなく、段差を緩和することができるため、例えば、フェイスダウン実装を平行に、良好に行うことができる。

## 【0027】

10

このダミー層は、第1の電極を形成するために、第1導電型半導体層の表面を露出する際のエッティングによって、半導体層を残すことで、効率的に設けることができるが、必ずしも半導体層でなくともよく、別の材料などによって形成してもよい。これによっても段差を緩和することができる。

## 【0028】

第1電極及び第2電極は、通常、第1導電型半導体層及び第2導電型半導体層上にそれぞれ、少なくともその一部が電気的に接続されるように形成されている。これら電極は、導電性材料により形成されているのであればその材料は特に限定されるものではなく、第1導電型半導体層及び第2導電型半導体層に対してオーミック接触が得られる材料であることが好ましい。例えば、アルミニウム、ニッケル、金、銀、銅、クロム、モリブデン、チタン、インジウム、ガリウム、タンゲステン、白金族系材料（例えば、Pt、Rh、Pd、Ir、Ru、Os等）等の金属及びITO、ZnO、SnO<sub>2</sub>等の導電性酸化物、等の単層又は積層層により形成することができる。より具体的には、第2電極は、Ni-Au系、Ni-Au-Pt系、Pd-Pt系、Ni-Pt系の電極材料、第1電極は、Ti-Al系、V-Pt系、Ti-Al-Ti-Pt系、W-Al-W系、Ti-Mo-Ti-Pt系の電極材料等が挙げられる。これら電極は、例えば、100nm～10μm程度の膜厚で形成することができる。

20

## 【0029】

第2電極は、第2導電型半導体層の一部にオーミック接続されたオーミック電極とパッド電極とから構成されることが好ましい。半導体とのオーミック性の向上と、ワイヤとの整合性という2つの機能を分離することで、より信頼性に優れた素子を得ることができるからである。オーミック電極とパッド電極とが積層される場合には、両者の界面には同一の材料を配置することが好ましく、特に、白金族系材料を配置させることが好ましい。また、オーミック接続される部分とパッド電極の機能を有する部分とを有する、つまり、オーミック電極とパッド電極とを兼用するように一体的に構成されていてもよい。この場合には、双方の電極を別個に形成する必要がなく、製造工程を簡略化することができるのみならず、オーミック電極とパッド電極との間に形成される界面準位をなくすことができ、より低抵抗の電極を得ることができる。オーミック電極とパッド電極とは、同じ材料で構成されていてもよいし、異なる材料で構成されていてもよい。なお、例えば、Ni-Au系の電極材料で第2電極を形成した後、パッド電極となる部分に形成されたNi酸化物をエッティング除去するなどして形成してもよい。

30

## 【0030】

40

オーミック電極は、電流狭窄領域の延設方向、つまり共振器方向に延設され、第2導電型半導体層のほぼ全面又は一部、好ましくは電流狭窄領域の直上、上述したリッジ直上にオーミック接続されている。オーミック電極の共振器方向の長さは、第2導電型半導体層及び／又は半導体レーザ素子の大きさによって適宜調整することができる。共振器方向に対して垂直方向である横方向の幅（長さ）は、第2導電型半導体層の表面に形成されたりッジの上表面のみを被覆する幅に設定されていてもよいし、リッジの両側面をも被覆する幅、さらにはリッジ両側の第2導電型半導体層の全部又は一部をも被覆する幅に設定されていてもよい。これにより、十分かつ均一に導波路に電圧を印加し、電流を与えることが

50

できる。なお、オーミック電極は、リッジに対して非対称に形成されていてもよいが、対称に形成されていることが好ましい。

#### 【0031】

パッド電極は、少なくともオーミック電極に電気的に接続されていれば、オーミック電極の全ての表面と接触するように配置されていてもよいし、一部の表面と接触するように配置されていてもよい。また、第2導電型半導体層とオーミック電極とがオーミック接続された領域の、実質的に一方向側においてのみワイヤボンディング等に十分な領域が確保されるように配置されていることが適当である。ここで、ワイヤボンディング等に十分な領域とは、ワイヤボンディング等が、第2導電型半導体層表面の電流狭窄領域上のみで、厳密にはリッジ直上で行われないように、つまり、リッジが存在しない領域のみで行うことができるような領域を意味する。なお、ワイヤボンディング等を押圧して形成するなどの場合には、ボンディング材が、加重付加部分から広がった状態で形成され、リッジ直上にボンディング材の外周がオーバーラップすることがある。しかし、このような場合でも、ボンディング材がリッジ直上にオーバーラップしないように、十分な領域が確保されるように配置されることが好ましい。具体的には、ボンディング等しようとするワイヤの太さ及び材料、パッド電極の材料等により適宜調整することができるが、例えば、 $1000 \mu m^2$ 以上、 $2000 \mu m^2$ 以上、 $5000 \mu m^2$ 以上、 $5000 \sim 20000 \mu m^2$ 程度、さらに $7000 \sim 12000 \mu m^2$ 程度の面積が適当である。また、別の観点から、 $30 \mu m \times 30 \mu m \sim 200 \mu m \times 200 \mu m$ 程度、 $80 \mu m \times 80 \mu m \sim 120 \mu m \times 120 \mu m$ 程度の大きさが適当である。さらに別の観点から、例えば、共振器長が $200 \mu m$ 以上である場合、オーミック電極とパッド電極との総幅は $100 \sim 200 \mu m$ 程度以上が適当である。

#### 【0032】

上述の領域を確保するために、パッド電極は、少なくともオーミック電極が延設される方向とは異なる方向に突出した形状を有していることが好ましい。つまり、通常、電流狭窄領域は、上述したように、半導体レーザ素子内でのリッジの形成位置の偏りに起因して、レーザ素子の端部方向に偏って配置している。したがって、パッド電極は、電流狭窄領域の一方向側、言い換えると、第2導電型半導体層とオーミック電極とがオーミック接続された領域の一方向側に配置している（図3（a）～図4（1）参照）。さらに、リッジに対して、後述する第1電極が形成されている側に、オーミック電極から突出するように配置していることが好ましい。これにより、上述したように、ワイヤボンディング等時ににおけるリッジの欠け等のダメージを回避することができるとともに、短絡等することなく第2電極へ確実かつ十分に電流を与えることができる。なお、ワイヤボンディング等は、上述したダミー層の上方において行われてもよい。これにより、レーザ素子を構成する半導体層又は電極等のダメージを最小限に止めることができる。

#### 【0033】

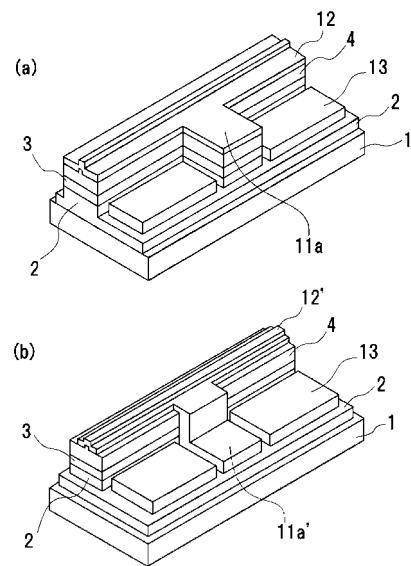

また、第2電極は、図2（a）に示すように、第2導電型半導体層とほぼ同じ平面形状及び平面積に設定されて、第2導電型半導体とその全部が接触していてもよいが、オーミック電極の一部又は全部と接触していることが好ましい。その場合には、第2電極は、絶縁膜等を介して第2導電型半導体層上に配置していることが好ましい。また、電気的に接続されない状態で（つまり、絶縁膜を介して）、図2（b）に示すように、第1導電型半導体層上にまで延設されていてもよい（但し、図2（a）及び（b）は第2電極の形状を説明するための図面であり、絶縁膜等は省略している）。ここで、絶縁膜としては、酸化シリコン、酸化チタン、酸化ジルコニアム、酸化ハフニウム、酸化ニオブ等の単層又は多層構造が挙げられる。この膜は、絶縁膜としてのみならず、露出した層又は側面を保護するために配置してもよい。また、パッド電極は、図2（a）及び（b）に示されるような半導体積層構造上に配置されるのみならず、例えば、パッド電極が配置される領域の全部又は一部において、半導体積層構造が階段状に、あるいは、絶縁膜や保護膜等によって階段状に形成された領域に、階段状に配置されていてもよい。

#### 【0034】

10

20

30

40

50

第1電極は、第1導電型半導体層に電気的に接続されており、第1導電型半導体の表面に対して第2電極と同一面側に形成されている。つまり、図3(a)～図4(n)に示すように、半導体レーザ素子の上面図において、第1電極13は、第2電極12と同一面側に配置されている。この場合、第1電極は、絶縁膜等を介して電気的に接触しない形態で、第2電極とオーバーラップしていてもよい(例えば、図3(f)、(h)、(i)、(k)、図4(l)、(m)及び(n)参照)。このような形状により、第1電極を大きくとることができるとため、電流の注入効率をより高めることができる。

#### 【0035】

また、第1電極は、電流狭窄領域(又はリッジ5)に対して、パッド電極のワイヤボンディング等するための領域と同一方向にのみ配置されている。言い換えると、第1電極は、第2電極のオーミック電極に隣接し、かつオーミック電極から突出して配置されたパッド電極に対しても隣接するように配置されている。例えば、第1電極は、オーミック電極の延設方向に対する一方向側であって、半導体レーザ素子の2つの対向する端面の一方に配置することができる。この場合、パッド電極は、オーミック電極の延設方向に対する一方向側であって、半導体レーザ素子の2つの対向する端面の他方に配置される。具体的には、突出したパッド電極により第2電極がL字状に形成され、第1電極は、四角形又はこれに近似した形状で、2方向においてパッド電極に取り囲まれるように配置されていてよい。(例えば、図3(e)参照)。また、突出したパッド電極により第2電極がT字状に形成されている場合には、第1電極は、四角形、これに近似した形状又は2分された形状とすることができます。ここで、2分された形状とは、第1電極が2つの四角形に分割された形状(例えば、図3(b)参照)又は電気的に接続された2つの領域に分けられた形状(例えば、図3(c)、図4(l)、(n)参照)等を意味する。突出したパッド電極により第2電極がC字状、F字状又はこれらに近似する形状に形成されている場合には、第1電極を取り囲む及び/又は第1電極を一部被覆するように配置していくてもよい(例えば、図3(g)、(i)、図4(j)、(k)参照)。なお、パッド電極の形状にかかわらず、第1電極は、オーミック電極の延設方向においてパッド電極を挟んでいてよいし、オーバーラップされていてよいし、2分されていてよい。

#### 【0036】

なお、第1電極は、第2電極のうちワイヤボンディング等のために確保された領域を無視した場合、第2電極の幅の1/2～10倍程度、好ましくは1～5倍程度の範囲内の幅に設定されていることが適当である。ここで、第2電極の幅は、例えば、図3(a)、(e)、(g)、(i)、図4(j)中における矢印Mで表すことができ、第1電極の幅は、図3(b)、(c)の矢印Nで表すことができる。これらの範囲は、第2電極のがリッジの幅より大きい幅で形成され、例えば、リッジ側面に形成される保護膜の上に形成されるような構造の場合に適用される範囲である。この第2電極は、リッジ形成後に、スパッタ法などで形成することができる。また、第2電極がセルフアライメント方式で形成される場合は、リッジの幅とほぼ同じ幅の第2電極となるので、第1電極は、第2電極のうちワイヤボンディング等のために確保された領域を無視した場合、第2電極の幅の10～120倍程度、好ましくは30～80倍程度の範囲内の幅に設定することが適当である。

#### 【0037】

本発明の半導体レーザ素子は、基板上に、第1導電型半導体層、活性層及び第2導電型半導体層がこの順に積層されて構成されていることが適当である。基板としては、絶縁性基板、半絶縁性基板、導電性基板のいずれであってもよく、例えば、C面、R面及びA面のいずれかを主面とするサファイア、スピネル、ZnS、ZnO、GaAs、Si、SiC、AlN及び窒化物半導体と格子整合する酸化物基板等が挙げられる。なかでも、窒化物半導体を成長させることができ可能な基板であることが好ましく、このような基板としてはサファイア、スピネルが挙げられる。基板は、オフアングルしていくてもよく、この場合ステップ状にオフアングルしたものを用いると、特に窒化ガリウムからなる層の成長が結晶性よく行えるので好ましい。なお、基板上に、第1導電型半導体層等を形成する前に、バッファ層、下地層等の半導体層を成長させた後、基板を研磨などの方法により除去しても

10

20

30

40

50

よいし、素子構造を形成した後に除去してもよい。バッファ層、下地層等を形成することにより、第1導電型半導体の成長を良好なものとすることができます。

【0038】

下地層として、例えば、ELO (Epitaxially Laterally Overgrowth) 成長させた窒化物半導体を用いると結晶性が良好な成長基板が得られる。ELO成長層の具体例としては、基板上に、窒化物半導体層を成長させ、その表面に窒化物半導体の成長を抑制する保護膜を設ける等して形成したマスク領域と、窒化物半導体を成長させる非マスク領域とをストライプ状に設け、その非マスク領域から窒化物半導体を成長させることで、膜厚方向への成長に加えて横方向への成長が成されることにより、マスク領域にも窒化物半導体が成長して成膜させたものや、基板上に成長させた窒化物半導体層に開口部を設け、その開口部側面から横方向への成長が成されて成膜されたもの等、いわゆる選択成長を利用したものが挙げられる。

【0039】

また、本発明の半導体レーザ素子は、端面保護膜、例えば、Si、Mg、Al、Hf、Nb、Zr、Sc、Ta、Ga、Zn、Y、B、Ti及びこれらの酸化物、窒化物（例えば、AlN、AlGaN、BN等）、フッ化物等の化合物（これらは単独で用いてもよいし、複数を組み合わせた化合物又は複数を組み合わせた多層膜であってもよい。）が、活性層で発生する光を効率よく共振させるために、共振器面の表面に形成されていてよい。

【0040】

なお、本発明の半導体レーザ素子は、通常の半導体レーザ素子の製造方法のいかなる方法によっても形成することができる。例えば、電流狭窄領域の延設方向（第2導電型半導体層のリッジの延設方向）を共振器方向とするために、端面に設けられている一対の共振器面は、劈開及びエッティング（RIE法等）のいずれによって形成してもよい。また、一方が劈開面、他方がエッティング端面でもよい。劈開で形成する場合には、基板や半導体層が劈開性を有していることが必要であり、その劈開性を利用すると優れた鏡面を容易に得ることができる。エッティングで形成する場合には、後に詳述するように、第1電極形成面を露出させる際に同時に共振器面を形成してもよい。また、第2導電型半導体層表面にリッジを形成する場合には、いわゆるセルフアライメント方式を利用してもよい。つまり、酸化シリコン等の絶縁膜又は保護膜をマスクとして利用してエッティングしてもよいし、金属膜を、得ようとするリッジに対応する形状に形成し、この金属膜をマスクとして用いてリッジを形成し、その後にこの金属膜を第2電極として利用してもよい。さらに、第2電極を構成するオーミック電極及びパッド電極並びに第1電極を形成する場合には、酸化シリコン等の絶縁膜又は保護膜やフォトレジスト等をマスクとして利用して加工してもよいし、フォトレジストを利用してリフトオフ法によって加工してもよい。

【0041】

また、本発明の半導体レーザ素子は、フェイスアップ実装（すなわち基板側をサブマウント基板に対向させる）、フェイスダウン実装（すなわちリッジ側をサブマウント基板に対向させる）のいずれで実装してもよい。この場合、p電極及びn電極の上には、外部電極等と接続させるためのメタライズ層（バンプ：Ag、Au、Sn、In、Bi、Cu、Zn等）がそれぞれ形成され、このメタライズ層がサブマウント上に設けられた正負一対の外部電極とそれぞれ接続される。さらにサブマウント基板に対してワイヤなどが配線される。フェイスダウン実装する場合には、実装する側の回路基板の回路を簡略化することができる。これによって、複数のレーザ素子を同じ基板に密に実装することが可能となる。例えば、オーミック電極から見て、ストライプ状に延設されたオーミック電極の延設方向とは異なる方向に突出するパッド電極の突出方向と反対の方向に、同様のレーザ素子を実装することができ、また赤色半導体レーザ素子や、赤外半導体レーザ素子を実装することもできる。また、発熱するリッジ側がサブマウント基板近傍に位置するために放熱性を向上させることができる。

【0042】

10

20

30

40

50

以下に、本発明の半導体レーザ素子の実施例を、図面に基づいて詳細に説明する。

#### 実施例 1

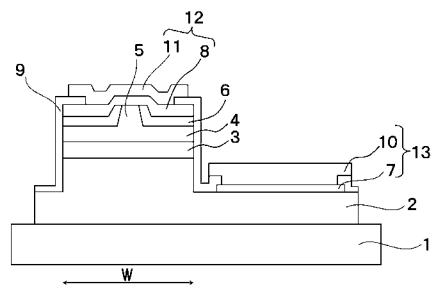

この実施例の半導体レーザ素子は、図 1 及び図 2 ( a ) に示すように、基板 1 上に、第 1 導電型半導体層である n 型半導体層 2 、活性層 3 及び第 2 導電型半導体層である p 型半導体層 4 が順次積層されて構成されている。

#### 【 0 0 4 3 】

n 型半導体層 2 は、一部の領域において、その上に配置する活性層 3 及び p 型半導体層 4 が除去されるとともに、膜厚方向に部分的に除去されている。また、 p 型半導体層 4 の上面には、ストライプ状のリッジ 5 が形成されている。

#### 【 0 0 4 4 】

p 型半導体層 4 の上面には、リッジ 5 上面以外の領域を被覆する第 1 絶縁膜 6 が形成されている。また、活性層 3 及び p 型半導体層 4 が除去された n 型半導体層 2 の上面には、n 型半導体層 2 の一部に接続された n 型オーミック電極 7 が形成され、リッジ 5 上面には、リッジ 5 上面に接続された p 型オーミック電極 8 が形成されている。これら n 型及び p 型オーミック電極 7 、 8 上の一部を残して、n 型半導体層 2 及び p 型半導体層 4 の表面には、第 2 絶縁膜 9 が被覆されている。さらに、n 型オーミック電極 7 及び p 型オーミック電極 8 上には、これらオーミック電極 7 、 8 とその一部で接続するように、n 型パッド電極 10 及び p 型パッド電極 11 が形成され、それぞれ第 1 電極 13 及び第 2 電極 12 を構成している。

#### 【 0 0 4 5 】

なお、リッジ 5 は、素子全体の一方側に極端に偏って配置している。例えば、素子全体の幅が 200 ~ 240  $\mu\text{m}$  であって、p 型半導体層の幅 ( 例えば、図 3 ( a ) の M ) が 60  $\mu\text{m}$  程度、また、導波路のストライプ長が 600 ~ 650  $\mu\text{m}$  程度の大きさの素子とし、p 型半導体層の端部が素子端部から 10  $\mu\text{m}$  程度離間するように設けられているとした場合、リッジは素子端部から 40  $\mu\text{m}$  程度の距離、p 型半導体層の端部から 30  $\mu\text{m}$  程度の距離の位置に配置されている。この場合のリッジ 5 の幅は 1.5  $\mu\text{m}$  程度、高さは 0.5  $\mu\text{m}$  程度である。

#### 【 0 0 4 6 】

なお、図 1 及び図 2 ( a ) には表されていないが、p 型半導体端部が素子端部と一致する場合には、リッジが、素子の端部及び p 型半導体層 4 の端部から 30  $\mu\text{m}$  程度の距離の位置に配置されていてもよい。

#### 【 0 0 4 7 】

また、p 型パッド電極 11 は、図 5 に示すように、半導体レーザ素子のほぼ中央で、ワイヤボンディングに十分な領域を確保するために、リッジ 5 の一方向側、つまり第 1 電極 13 が配置する側に、突出部 11a として形成されている。この突出部 11a によって、n 型オーミック電極 7 及び n 型パッド電極 10 が 2 つに分割されて配置している。この場合の第 1 電極は、110  $\mu\text{m} \times 200 \mu\text{m}$  である。

#### 【 0 0 4 8 】

このような半導体レーザ素子は、以下の方法で形成することができる。

#### ( 基板 )

まず、直径 2 インチ、C 面を主面とするサファイア基板を M O V P E 反応容器内にセットし、温度を 500 にしてトリメチルガリウム ( T M G ) 、アンモニア ( N H 3 ) を用い、 G a N からなるバッファ層を 200 の膜厚で成長させる。バッファ層形成後、温度を 1050 にして、 T M G 、アンモニアを用い、アンドープ G a N からなる窒化物半導体層を 4  $\mu\text{m}$  の膜厚で成長させる。この層は、素子構造を形成する各層の成長において下地層 ( 成長基板 ) として作用する。

#### 【 0 0 4 9 】

#### ( 第 1 導電型半導体層の形成 )

次に、下地層の上に、 T M G 、アンモニア、不純物ガスとしてシランガスを用い、 1050 で S i を  $1 \times 10^{-8} / \text{cm}^3$  ドープさせた G a N からなる n 型コンタクト層を 4

10

20

30

40

50

. 5  $\mu\text{m}$  の膜厚で成長させる。

【0050】

続いて、T M G、T M I (トリメチルインジウム)、アンモニアを用い、温度を800にして  $\text{In}_{0.06}\text{Ga}_{0.94}\text{N}$  からなるクラック防止層を0.15  $\mu\text{m}$  の膜厚で成長させる。なお、このクラック防止層は省略可能である。

【0051】

その上に、温度を1050にして、原料ガスにT M A (トリメチルアルミニウム)、T M G 及びアンモニアを用い、アンドープのA1GaNからなるA層を25の膜厚で成長させ、続いてT M Aを止め、不純物ガスとしてシランガスを用い、S iを $5 \times 10^{18}$  /  $\text{cm}^3$  ドープしたGaNからなるB層を25の膜厚で成長させる。そしてこの操作をそれぞれ160回繰り返してA層とB層を交互に積層し、総膜厚1.2  $\mu\text{m}$  程度の多層膜(超格子構造)からなるn型クラッド層を成長させる。この時、アンドープA1GaNのA1の混晶比としては、0.01以上0.3以下の範囲であれば、十分にクラッド層として機能する屈折率差を設けることができる。

【0052】

次に、同様の温度で原料ガスにT M G 及びアンモニアを用い、アンドープのGaNからなるn型光ガイド層を0.15~0.17  $\mu\text{m}$  程度の膜厚で成長させる。この層は、n型不純物をドープさせてもよい。

【0053】

(活性層の形成)

続いて、温度を800にして、原料にT M I (トリメチルインジウム)、T M G 及びアンモニアを用い、不純物ガスとしてシランガスを用い、S iを $5 \times 10^{18}$  /  $\text{cm}^3$  ドープした  $\text{In}_{0.05}\text{Ga}_{0.95}\text{N}$  からなる障壁層を140の膜厚で成長させる。続いてシランガスを止め、アンドープの  $\text{In}_{0.1}\text{Ga}_{0.9}\text{N}$  からなる井戸層を70の膜厚で成長させる。この操作を2回繰り返し、最後に障壁層を積層させて総膜厚560の多重量子井戸構造(M Q W)の活性層を成長させる。

【0054】

(第2導電型半導体層の形成)

次いで、同様の温度で、原料ガスにT M A、T M G 及びアンモニアを用い、不純物ガスとしてC p<sub>2</sub>M g (シクロペンタジエニルマグネシウム)を用い、M gを $1 \times 10^{19}$  /  $\text{cm}^3$  ドープしたA1GaNからなるp型電子閉じ込め層を100の膜厚で成長させる。

次に、温度を1050にして、原料ガスにT M G 及びアンモニアを用い、アンドープのGaNからなるp型光ガイド層を1500の膜厚で成長させる。このp型光ガイド層はアンドープとして成長させるが、M gをドープさせてもよい。

【0055】

続いて、1050でアンドープA<sub>1</sub><sub>0.16</sub>GaNからなる層を25の膜厚で成長させ、続いてT M Gを止め、C p<sub>2</sub>M gを用いてM gドープGaNからなる層を25の膜厚で成長させ、総膜厚0.45  $\mu\text{m}$  の超格子層からなるp型クラッド層を成長させる。p型クラッド層は少なくとも一方がA1を含む窒化物半導体層を含み、互いにバンドギャップエネルギーが異なる窒化物半導体層を積層した超格子で作製した場合、不純物はいずれも一方の層に多くドープして、いわゆる変調ドープを行うと結晶性がよくなる傾向にあるが、両方に同じようにドープさせてもよい。

【0056】

最後に、1050でp型クラッド層の上にM gを $1 \times 10^{20}$  /  $\text{cm}^3$  ドープしたp型GaNからなるp型コンタクト層を150の膜厚で成長させる。p型コンタクト層はp型の  $\text{In}_x\text{Al}_y\text{Ga}_{1-x-y}\text{N}$  ( $x > 0$ 、 $y > 0$ 、 $x + y < 1$ ) で構成することができ、好ましくはM gをドープしたGaNとすればp電極と最も好ましいオーミック接触が得られる。

反応終了後、反応容器内において窒素雰囲気中でウェハを700でアニーリングして

10

20

30

40

50

、p型半導体層をさらに低抵抗化する。

【0057】

(第1導電型半導体層の露出)

以上のようにして得られた窒化物半導体の積層構造体を、ウェハを反応容器から取り出し、最上層のp型コンタクト層の表面にSiO<sub>2</sub>からなるエッティング用マスクを形成する。このマスクを所定の形状に加工し、Cl<sub>2</sub>ガスを用いたRIE(反応性イオンエッティング)によってp型半導体層、活性層、n型半導体層の一部を順次エッティングし、n電極を形成するn型コンタクト層の表面を露出させる。つまり、図2(a)に示したように、p型半導体層と、活性層と、一部のn型半導体層とは、2つの分割された矩形形状で、n型コンタクト層が露出するように除去する。なお、この際、露出した活性層の側面に共振器面を形成してもよい。

【0058】

次に、ストライプ状の導波路領域(電流狭窄領域)を形成するために、最上層のp型コンタクト層のほぼ全面に、CVD装置により、Si酸化物(主としてSiO<sub>2</sub>)からなる保護膜を0.5μmの膜厚で形成する。その後、フォトリソグラフィー技術により保護膜の上に所定の形状のマスクを形成し、RIE装置によりCHF<sub>3</sub>ガスを用いて、保護膜をストライプ状に加工し、さらに、この保護膜をマスクとして用いて、p型コンタクト層にストライプ状のリッジを形成する。

【0059】

(第1絶縁膜の形成)

続いて、保護膜を存在させたまま、p型層表面にZrO<sub>2</sub>からなる第1絶縁膜を形成する。この第1絶縁膜は、n型オーミック電極形成面をマスクして半導体層の全面に設けてもよい。また、共振器面を形成した場合には、後に分割し易いように、共振器面の近傍において第1絶縁膜を形成しない領域を、10μm程度のストライプ状で、リッジと直交するよう設けてもよい。

第1絶縁膜を形成した後、BHF液に浸漬して、ストライプ状のリッジの上面に形成したSiO<sub>2</sub>を溶解除去し、リフトオフ法によりSiO<sub>2</sub>と共に、p型コンタクト層上(さらにはn型コンタクト層上)にあるZrO<sub>2</sub>を除去する。これにより、ストライプ状のリッジの上面が露出され、リッジの側面はZrO<sub>2</sub>で覆われた構造となる。

【0060】

(オーミック電極の形成)

次に、p型コンタクト層上のリッジ最表面の第1絶縁膜上にp型オーミック電極を形成する。このp型オーミック電極は、Ni-Auからなる。また、エッティングにより露出されたn型コンタクト層の表面にも、図2(a)に示すような、セパレート状のn型オーミック電極を形成する。n型オーミック電極はTi-Alからなる。これらを形成後、それぞれを酸素と窒素との混合雰囲気中、600にてアニーリングすることによって、p型及びn型オーミック電極を合金化し、良好なオーミック特性を得る。なお、p型オーミック電極は、素子の端から端まで配置する長さであることが好ましいが、後工程等を考慮して、端部よりも内側にその端面が配置していてもよい。

【0061】

(第2絶縁膜の形成)

次いで、リッジ上のp型オーミック電極とn型オーミック電極とが形成されている領域の全面にレジストを形成し、所望の形状に加工する。このレジスト上を含む全面に、Si酸化物(主としてSiO<sub>2</sub>)からなる第2絶縁膜を形成し、リフトオフする。これにより、p型オーミック電極上とn型オーミック電極上の一とを露出させる。

(パッド電極の形成)

次に、第2絶縁膜の一部を覆うようにp型パッド電極及びn型パッド電極をそれぞれ形成する。これらの電極は、Ni-Ti-Auからなる。これらのパッド電極は、露出したオーミック電極とストライプ状に接続されることにより、第1電極13及び第2電極12を構成する。なお、パッド電極はオーミック電極と同じ長さで形成されていなくてもよ

10

20

30

40

50

、例えば、オーミック電極の端部上面が露出するような長さで形成されていてもよい。

#### 【0062】

##### (劈開及び共振器面形成)

次いで、基板を研磨して、約  $150 \mu\text{m}$  程度の膜厚に加工した後、基板裏面にスクリープ溝を形成し、図4の二点鎖線で示した位置で、半導体層側からブレーキングして劈開したり、基板側からスクリープを数回繰り返す等によって、バー状のレーザを得る。半導体層の劈開面は、半導体のM面(1100)面となっており、この面を共振器面とすることができます。

##### (端面保護膜の形成)

上記のように形成された共振器面に、活性層で発生する光を効率よく共振させ、特にモニター側の共振器面に出射側の共振器面と屈折率差を設けるために、スパッタ装置を用い、 $\text{ZrO}_2$  からなる保護膜を形成し、次いで  $\text{SiO}_2$  と  $\text{ZrO}_2$  とを交互に3ペア積層して高反射膜を形成した。ここで、保護膜と、高反射膜を構成する  $\text{SiO}_2$  膜と  $\text{ZrO}_2$  膜の膜厚は、それぞれ活性層からの発光波長に応じて好ましい厚さに設定することができる。

次いで、ストライプ状の第2電極に平行な方向に、スクリープにより溝を形成し、図4の一点鎖線で示した位置で、基板側からバー状に切断して本発明の半導体レーザ素子を得る。

#### 【0063】

##### (半導体レーザ素子の特性評価)

得られた半導体レーザ素子の特性を評価した。

その結果、温度60°、出力  $30.6 \text{ mW}$  における電流及び電圧特性は、約700時間経過後においても変化せず、良好な素子寿命が認められた。

また、レーザ素子25チップ平均のRCL特性において、比較例とR及びLが同等であるにもかかわらず、Cについて低減が認められた。

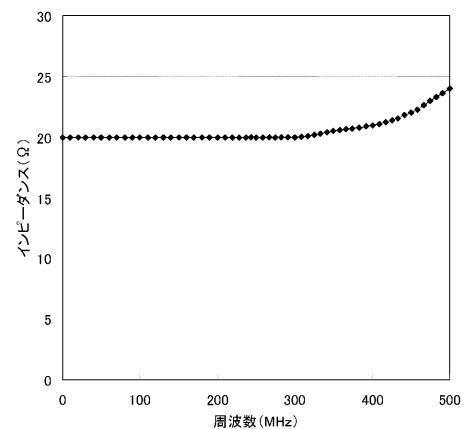

さらに、周波数 - インピーダンス曲線は、図5に示すように、周波数の増加にしたがってインピーダンスの低減は認められず、理論値に近づく結果が得られた。

また、閾値を低下させることができ、低電流での発振が可能になった。

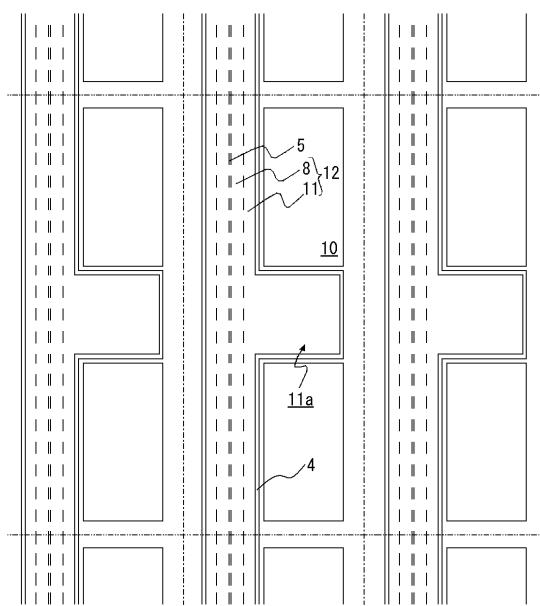

さらに、図4に示すように、ウェハ上に半導体レーザ素子を構成する第2電極12及び第1電極13、さらにはそれらに対応させて第2導電型半導体層4及びリッジ5を配置することにより、従来例に比較して、ほぼ1.5倍の素子数を確保することができるとともに、歩留まりを向上させることができた。

#### 【0064】

##### 実施例2

この実施の形態の半導体レーザ素子は、図2(b)に示すように、n型半導体層2の深さ方向の一部、活性層3及びp型半導体層4がストライプ状に形成されており、第2電極12'がこれらの積層体上に形成されているとともに、第2電極12'を構成するパッド電極の突出部11a'が絶縁膜(図示せず)を介して、n型半導体層2の直上にわたって配置されている点を除いて、図1及び図2(a)の半導体レーザ素子と実質的に同様である。

#### 【0065】

このような半導体レーザ素子は、実質的に上記と同様の方法で形成することができる。なお、パッド電極を形成した後、半導体層をチップサイズにするために、網目状にサファイア基板が露出するまで半導体層をRIEによってエッティングする。このとき、レーザ出射面はレーザを発振させたときのFFP(ファーフィールドパターン)が良好となるようにレーザ出射端面の直前でエッティングする。エッティング後、サファイアが露出した網目に沿って裏面からサファイアをスクリーピングし、レーザチップを得る。

#### 【産業上の利用可能性】

#### 【0066】

本発明は、レーザ素子を応用することができる全てのデバイス、例えば、CDプレーヤ

10

20

30

40

50

、M D プレーヤ、各種ゲーム機器、D V D プレーヤ、電話回線や海底ケーブル等の基幹ライン・光通信システム、レーザメス、レーザ治療機、レーザ指圧機等の医療機器、レーザビームプリンタ、ディスプレイ等の印刷機、各種測定装置、レーザ水準器、レーザ測長機、レーザスピードガン、レーザ温度系等の光センシング機器、レーザ電力輸送等の種々の分野において利用することができる。

【図面の簡単な説明】

【0067】

【図1】本発明の半導体レーザ素子の実施の形態を示す概略断面図である。

【図2】(a)は図1に示す半導体レーザの概略斜視図であり、(b)は別の実施の形態の半導体レーザの概略斜視図である。 10

【図3】本発明の半導体レーザにおける第1電極及び第2電極の配置を説明するための概略平面図である。

【図4】本発明の半導体レーザにおける第1電極及び第2電極の配置を説明するための概略平面図である。

【図5】本発明の半導体レーザの製造工程における第1電極及び第2電極等のレイアウトを説明するための概略平面図である。

【図6】本発明の半導体レーザの周波数・インピーダンス特性を示すグラフである。

【図7】従来の半導体レーザを示す断面図である。

【符号の説明】

【0068】

- |        |                   |    |

|--------|-------------------|----|

| 1      | 基板                | 20 |

| 2      | n型半導体層(第1導電型半導体層) |    |

| 3      | 活性層               |    |

| 4      | p型半導体層(第2導電型半導体層) |    |

| 5      | リッジ               |    |

| 6      | 第1絶縁膜             |    |

| 7      | n型オーミック電極         |    |

| 8      | p型オーミック電極         |    |

| 9      | 第2絶縁膜             |    |

| 10     | n型パッド電極           | 30 |

| 11     | p型パッド電極           |    |

| 11 a   | 突出部               |    |

| 12、12' | 第2電極              |    |

| 13     | 第1電極              |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開平10-093186 (JP, A)

特開2003-101147 (JP, A)

特開平07-022704 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50