US010374846B2

## (12) United States Patent

### Shokrollahi et al.

### (10) Patent No.: US 10,374,846 B2

(45) **Date of Patent:** Aug. 6, 2019

# (54) CLOCK-EMBEDDED VECTOR SIGNALING CODES

(71) Applicant: Kandou Labs, S.A., Lausanne (CH)

(72) Inventors: Amin Shokrollahi, Préverenges (CH);

**Brian Holden**, Monte Sereno, CA (US); **Richard Simpson**, Bedford (GB)

(73) Assignee: KANDOU LABS, S.A., Lausanne (CH)

(\*) Notice: Subject to any disclaimer, the term of thi

Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 16/031,875

(22) Filed: Jul. 10, 2018

(65) Prior Publication Data

US 2018/0324008 A1 Nov. 8, 2018

### Related U.S. Application Data

- (63) Continuation of application No. 15/390,293, filed on Dec. 23, 2016, now Pat. No. 10,020,966, which is a (Continued)

- (51) **Int. Cl. H04L 25/00** (2006.01) **H04L 25/49** (2006.01)

(Continued)

- (52) U.S. Cl. CPC ....... *H04L 25/49* (2013.01); *H04L 25/03006* (2013.01); *H04L 25/03057* (2013.01); *H04L 25/08* (2013.01); *H04L 25/085* (2013.01)

- (58) Field of Classification Search

CPC . H04L 25/49; H04L 25/085; H04L 25/03057;

H04L 25/03006; H04L 25/08

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,196,351 A 7/1965 David 3,970,795 A 7/1976 Allen (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1864346 A 11/2006 CN 101276645 A 10/2008 (Continued)

### OTHER PUBLICATIONS

Abbasfar, Aliazam , "Generalized Differential Vector Signaling", IEEE International Conference on Communications, ICC '09, Jun. 14, 2009, 1-5 (5 pages).

(Continued)

Primary Examiner — Dac V Ha (74) Attorney, Agent, or Firm — Invention Mine LLC

### (57) ABSTRACT

Vector signaling codes providing guaranteed numbers of transitions per unit transmission interval are described, along with methods and systems for their generation and use. The described architecture may include multiple communications sub-systems, each having its own communications wire group or sub-channel, clock-embedded signaling code, pre- and post-processing stages to guarantee the desired code transition density, and global encoding and decoding stages to first distribute data elements among the sub-systems, and then to reconstitute the received data from its received sub-system elements.

### 20 Claims, 25 Drawing Sheets

# US 10,374,846 B2 Page 2

| Related U.S. Application Data                        |                                                  |                   | 7,167,01                            | 19 B2                | 1/2007           | Broyde et al.      |                                    |             |

|------------------------------------------------------|--------------------------------------------------|-------------------|-------------------------------------|----------------------|------------------|--------------------|------------------------------------|-------------|

| continuation of application No. 15/176,085, filed on |                                                  |                   | 7,180,94<br>7,184,48                | 49 B2                | 2/2007<br>2/2007 | Kleveland et al.   |                                    |             |

|                                                      | Jun. 7, 2016, now Pat. No. 9,686,106, which is a |                   |                                     | 7,184,46             |                  |                    | Chau et al.                        |             |

|                                                      |                                                  |                   | ation No. 14/636,098, filed on      | 7,356,2              | 13 B1            | 4/2008             | Cunningham et al.                  |             |

|                                                      |                                                  |                   | t. No. 9,363,114.                   | 7,358,86<br>7,389,33 |                  |                    | Chiarulli et al.<br>Moore et al.   |             |

|                                                      |                                                  |                   |                                     | 7,400,23             | 76 B1            |                    | Sotiriadis et al.                  |             |

| (60)                                                 | Provisional a                                    | pplication        | n No. 61/946,574, filed on Feb.     | 7,535,95             | 57 B2            | 5/2009             | Ozawa et al.                       |             |

| ` /                                                  | 28, 2014.                                        |                   |                                     | 7,583,20             |                  | 9/2009             |                                    |             |

|                                                      |                                                  |                   |                                     | 7,613,23<br>7,620,11 |                  |                    | Raghavan et al.<br>Bessios et al.  |             |

| (51)                                                 | Int. Cl.                                         |                   | (2006.04)                           | 7,633,85             | 50 B2            | 12/2009            | Ahn                                |             |

|                                                      | H04L 25/03                                       |                   | (2006.01)                           | 7,656,32<br>7,706,45 | 21 B2            | 2/2010             | Wang<br>Laroia et al.              |             |

|                                                      | H04L 25/08                                       |                   | (2006.01)                           | 7,706,52             |                  | 4/2010             |                                    |             |

| (56)                                                 |                                                  | Referen           | ces Cited                           | 7,746,76             | 54 B2            |                    | Rawlins et al.                     |             |

|                                                      | 110                                              |                   | DOCUMENTE                           | 7,808,45<br>7,808,83 |                  | 10/2010            | Chen et al.<br>Kasuta              |             |

|                                                      | U.S.                                             | PALENT            | DOCUMENTS                           | 7,841,90             | )9 B2            | 11/2010            | Murray et al.                      |             |

|                                                      | 4,163,258 A                                      | 7/1979            | Ebihara et al.                      | 7,868,79<br>7,869,54 |                  | 1/2011<br>1/2011   |                                    |             |

|                                                      | 4,499,550 A                                      |                   | Ray et al.                          | 7,809,65             |                  | 3/2011             |                                    |             |

|                                                      | 4,722,084 A<br>4,974,211 A                       | 1/1988<br>11/1990 | Morton<br>Corl                      | 8,050,33             | 32 B2            | 11/2011            | Chung et al.                       |             |

|                                                      | 5,053,974 A                                      | 10/1991           |                                     | 8,055,09<br>8,064,53 |                  | 11/2011<br>11/2011 | Palotai et al.                     |             |

|                                                      | 5,166,956 A                                      |                   | Baltus et al.                       | 8,085,13             |                  |                    | Li et al.                          |             |

|                                                      | 5,283,761 A<br>5,287,305 A                       |                   | Gillingham<br>Yoshida               | 8,149,90             | 06 B2            |                    | Saito et al.                       |             |

|                                                      | 5,311,516 A                                      |                   | Kuznicki et al.                     | 8,159,37<br>8,159,37 |                  |                    | Abbasfar<br>Abbasfar               |             |

|                                                      | 5,331,320 A                                      |                   | Cideciyan et al.                    | 8,180,93             |                  |                    | Lee et al.                         |             |

|                                                      | 5,412,689 A<br>5,449,895 A                       |                   | Chan et al.<br>Hecht et al.         | 8,199,84             |                  |                    | Oh et al.                          |             |

|                                                      | 5,461,379 A                                      |                   | Weinman                             | 8,199,86<br>8,209,58 |                  |                    | Chen et al.<br>Varnica             | H03M 13/033 |

|                                                      | 5,511,119 A                                      |                   | Lechleider                          | 0,203,31             | ,, DI            | 0/2012             | , talling                          | 714/752     |

|                                                      | 5,553,097 A<br>5,689,509 A                       |                   | Dagher<br>Gaytan et al.             | 8,218,67             |                  | 7/2012             |                                    |             |

|                                                      | 5,856,935 A                                      | 1/1999            | Moy et al.                          | 8,245,09<br>8,274,3  |                  | 8/2012<br>9/2012   | Jiang et al.                       |             |

|                                                      | 5,889,981 A                                      |                   | Betker et al.                       | 8,279,09             |                  |                    | Abbasfar                           |             |

|                                                      | 5,949,060 A<br>5,982,954 A                       |                   | Schattschneider et al. Delen et al. | 8,279,74             |                  | 10/2012            |                                    |             |

|                                                      | 5,995,016 A                                      | 11/1999           | Perino                              | 8,279,97<br>8,284,84 |                  |                    | Lin et al.<br>Nam et al.           |             |

|                                                      | 6,005,895 A<br>6,084,883 A                       |                   | Perino et al. Norrell et al.        | 8,289,9              | 14 B2            | 10/2012            | Li et al.                          |             |

|                                                      | 6,084,958 A                                      |                   | Blossom                             | 8,295,25<br>8,359,44 |                  |                    | Gorokhov et al.<br>Perego et al.   |             |

|                                                      | 6,097,732 A                                      | 8/2000            |                                     | 8,365,03             |                  | 1/2013             |                                    |             |

|                                                      | 6,154,498 A<br>6,242,321 B1                      |                   | Dabral et al.<br>Acosta et al.      | 8,406,3              |                  | 3/2013             | Tsai                               |             |

|                                                      | 6,278,740 B1                                     | 8/2001            | Nordyke                             | 8,437,44<br>8,442,09 |                  |                    | Zhang et al.<br>Sederat            |             |

|                                                      | 6,317,465 B1<br>6,359,931 B1                     |                   | Akamatsu et al.<br>Perino et al.    | 8,442,21             | 10 B2            | 5/2013             | Zerbe                              |             |

|                                                      | 6,378,073 B1                                     |                   | Davis et al.                        | 8,451,91<br>8,472,51 |                  |                    | Oh et al.                          |             |

|                                                      | 6,404,820 B1                                     | 6/2002            |                                     | 8,472,51<br>8,498,34 |                  |                    | Malipatil et al.<br>Wilson et al.  |             |

|                                                      | 6,452,420 B1<br>6,483,828 B1                     | 9/2002            | Wong<br>Balachandran et al.         | 8,498,36             | 58 B1            | 7/2013             | Husted et al.                      |             |

|                                                      | 6,504,875 B2                                     |                   | Perino et al.                       | 8,520,49<br>8,539,31 |                  |                    | Goulahsen<br>Shokrollahi et al.    |             |

|                                                      | 6,556,628 B1                                     |                   | Poulton et al.                      | 8,577,28             |                  |                    | Seo et al.                         |             |

|                                                      | 6,621,427 B2<br>6,621,945 B2                     |                   | Greenstreet<br>Bissessur            | 8,578,24             |                  |                    | Mittelholzer et al.                |             |

|                                                      | 6,650,638 B1                                     |                   | Walker et al.                       | 8,588,25<br>8,588,28 |                  |                    | Diab et al.<br>Oh et al.           |             |

|                                                      | 6,661,355 B2                                     |                   | Cornelius et al.                    | 8,593,30             |                  |                    | Tajalli et al.                     |             |

|                                                      | 6,766,342 B2<br>6,865,234 B1                     |                   | Kechriotis<br>Agazzi                | 8,620,16             |                  | 12/2013            |                                    |             |

|                                                      | 6,865,236 B1                                     | 3/2005            | Terry                               | 8,638,24<br>8,649,44 |                  |                    | Sudhakaran et al.<br>Cronie et al. |             |

|                                                      | 6,876,317 B2<br>6,898,724 B2                     |                   | Sankaran                            | 8,649,46             |                  |                    | Ware et al.                        |             |

|                                                      | 6,927,709 B2                                     | 5/2005<br>8/2005  |                                     | 8,687,96             |                  |                    | Nosaka et al.                      |             |

|                                                      | 6,954,492 B1                                     |                   | Williams                            | 8,718,18<br>8,755,42 |                  |                    | Cronie et al. Cronie et al.        |             |

|                                                      | 6,976,194 B2<br>6,982,954 B2                     | 1/2005            | Cypher<br>Dhong et al.              | 8,773,96             | 64 B2            | 7/2014             | Hsueh et al.                       |             |

|                                                      | 6,990,138 B2                                     |                   | Bejjani et al.                      | 8,780,68             |                  |                    | Clausen et al.                     |             |

|                                                      | 6,999,516 B1                                     | 2/2006            | Rajan                               | 8,831,44<br>8,879,66 |                  |                    | Yu et al.<br>Peng et al.           |             |

|                                                      | 7,023,817 B2<br>7,038,486 B2                     |                   | Kuffner et al.<br>Aoyama et al.     | 8,897,13             |                  |                    | Kern et al.                        |             |

|                                                      | 7,038,486 B2<br>7,039,136 B2                     |                   | Olson et al.                        | 8,938,17             | 71 B2            | 1/2015             | Tang et al.                        |             |

|                                                      | 7,053,802 B2                                     | 5/2006            | Cornelius                           | 8,949,69             |                  |                    | Ordentlich et al.                  |             |

|                                                      | 7,075,996 B2<br>7,085,153 B2                     |                   | Simon et al.<br>Ferrant et al.      | 8,951,07<br>8,989,31 |                  |                    | Hashim et al.<br>Holden et al.     |             |

|                                                      | 7,083,133 B2<br>7,127,003 B2                     |                   | Rajan et al.                        | 8,996,74             |                  |                    | Wiley et al.                       |             |

|                                                      | 7,142,612 B2                                     |                   | Horowitz et al.                     | 9,015,50             | 66 B2            | 4/2015             | Cronie et al.                      |             |

|                                                      |                                                  |                   |                                     |                      |                  |                    |                                    |             |

| (56)                               | References Cited |                                   | 2011/0127                  |            |                   | Wilson et al.                                                        |

|------------------------------------|------------------|-----------------------------------|----------------------------|------------|-------------------|----------------------------------------------------------------------|

| U.S                                | S. PATENT        | DOCUMENTS                         | 2011/0235<br>2011/0268     | 3225 A1    | 11/2011           | Goulahsen<br>Cronie et al.                                           |

| 0.071.476 D2                       | 6/2015           | Francis of all                    | 2011/0286<br>2011/0299     |            | 11/2011           | Nervig<br>Cronie et al.                                              |

| 9,071,476 B2<br>9,077,386 B1       |                  | Fox et al.<br>Holden et al.       | 2011/0302                  | 2478 A1    | 12/2011           | Cronie et al.                                                        |

| 9,093,791 B2                       | 7/2015           | Liang                             | 2011/0317<br>2012/0082     |            |                   | Kern et al.<br>Narroschke H04N 19/423                                |

| 9,100,232 B1<br>9,124,557 B2       |                  | Hormati et al.<br>Fox et al.      | 2012/0082                  | .242 A1*   | 4/2012            | 375/240.25                                                           |

| 9,165,615 B2                       |                  | Amirkhany et al.                  | 2012/0213                  |            |                   | Cronie et al.                                                        |

| 9,197,470 B2                       | 11/2015          | Okunev                            | 2012/0243                  |            |                   | Desjardins                                                           |

| 9,231,790 B2<br>9,246,713 B2       |                  | Wiley et al.<br>Shokrollahi       | 2013/0010<br>2013/0013     |            |                   | Cronie et al. Cronie et al.                                          |

| 9,251,873 B1                       |                  | Fox et al.                        | 2013/0114                  | 392 A1     | 5/2013            | Sun et al.                                                           |

| 9,288,082 B1                       |                  | Ulrich et al.                     | 2013/0159<br>2013/0188     |            |                   | Nygren et al.<br>Ferraiolo et al.                                    |

| 9,288,089 B2<br>9,331,962 B2       |                  | Cronie et al.<br>Lida et al.      | 2013/0186                  |            | 10/2013           |                                                                      |

| 9,362,974 B2                       |                  | Fox et al.                        | 2013/0346                  | 830 A1     | 12/2013           | Ordentlich et al.                                                    |

| 9,363,114 B2                       |                  | Shokrollahi et al.                | 2014/0177<br>2014/0198     |            |                   | Cronie et al.                                                        |

| 9,401,828 B2<br>9,432,082 B2       |                  | Cronie et al.<br>Ulrich et al.    | 2014/0196                  |            |                   | George et al. Fox et al.                                             |

| 9,432,298 B1                       |                  |                                   | 2014/0269                  | 130 A1     | 9/2014            | Maeng et al.                                                         |

| 9,455,765 B2                       |                  | Schumacher et al.                 | 2015/0063                  |            |                   | Simpson et al.                                                       |

| 9,461,862 B2<br>9,479,369 B1       |                  | Holden et al.<br>Shokrollahi      | 2015/0078<br>2015/0092     |            |                   | Whitby-Strevens<br>Shokrollahi et al.                                |

| 9,509,437 B2                       |                  | Shokrollahi                       | 2015/0222                  | 2458 A1    | 8/2015            | Hormati et al.                                                       |

| 9,537,644 B2                       |                  | Jones et al.                      | 2015/0236                  |            |                   | Ling et al.                                                          |

| 9,634,797 B2<br>9,667,379 B2       |                  | Benammar et al.<br>Cronie et al.  | 2015/0249<br>2015/0333     |            |                   | Shokrollahi et al.<br>Shokrollahi                                    |

| 9,710,412 B2                       |                  | Sengoku                           | 2015/0349                  | 9835 A1    | 12/2015           | Fox et al.                                                           |

| 10,055,372 B2                      |                  | Shokrollahi                       | 2015/0380                  |            |                   | Mittelholzer et al.                                                  |

| 2001/0006538 A1<br>2002/0044316 A1 |                  | Simon et al.<br>Myers             | 2015/0381<br>2016/0020     |            |                   | Fox et al.<br>Ulrich et al.                                          |

| 2002/0057592 A1                    | 5/2002           | Robb                              | 2016/0036                  | 616 A1     | 2/2016            | Holden et al.                                                        |

| 2002/0152340 A1                    |                  | Dreps et al.                      | 2016/0218                  |            |                   | Fox et al.                                                           |

| 2002/0154633 A1<br>2002/0174373 A1 |                  | Shin et al.                       | 2016/0380<br>2017/0272     |            |                   | Hormati et al.<br>Shokrollahi et al.                                 |

| 2002/01/43/3 A1<br>2002/0181607 A1 |                  |                                   | 201110212                  |            | 3/2011            | 21011 011 11 11 11 11 11 11 11 11 11 11 1                            |

| 2003/0086366 A1                    |                  | Branlund et al.                   |                            | FOREIC     | 3N PATE           | NT DOCUMENTS                                                         |

| 2003/0117184 A1<br>2004/0057525 A1 |                  | Fecteau et al.<br>Rajan et al.    | CN                         | 10195      | 4222 4            | 10/2010                                                              |

| 2004/0146117 A1                    |                  | Subramaniam et al.                | CN<br>CN                   |            | 4223 A<br>9116 A  | 10/2010<br>3/2011                                                    |

| 2004/0155802 A1                    |                  | Lamy et al.                       | CN                         | 10225      | 4571 B            | 6/2015                                                               |

| 2004/0161019 A1<br>2004/0169529 A1 |                  | Raghavan et al.<br>Afghani et al. | EP<br>JP                   |            | 9221 B1           | 2/2013                                                               |

| 2004/0170231 A1                    |                  | Bessios et al.                    | WO                         |            | 3612 A<br>4121 A1 | 6/2003<br>7/2009                                                     |

| 2004/0239374 A1                    |                  |                                   | WO                         | 201003     | 1824 A1           | 3/2010                                                               |

| 2005/0027876 A1<br>2005/0174841 A1 |                  | Umei et al.                       | WO<br>WO                   |            | 9359 A2           | 9/2011<br>12/2011                                                    |

| 2005/0213686 A1                    |                  | Love et al.                       | WO                         | 201113     | 3000 A2           | 12/2011                                                              |

| 2006/0013331 A1                    |                  | Choi et al.                       |                            | ОТ         | HER DII           | BLICATIONS                                                           |

| 2006/0126751 A1<br>2006/0159005 A1 |                  | Bessios<br>Rawlins et al.         |                            | 01         | IILK I O          | BLICATIONS                                                           |

| 2006/0236174 A1                    |                  |                                   |                            |            |                   | code", Wikipedia.org, retrieved on                                   |

| 2006/0291589 A1                    |                  | Eliezer et al.                    | Feb. 6, 201                |            |                   | a Last Dial II. Madaus?" IEEE                                        |

| 2007/0030796 A1<br>2007/0164883 A1 |                  | Furtner                           |                            |            |                   | e Last Dial-Up Modem?", IEEE s, IEEE Service Center, Piscataway,     |

| 2007/0263711 A1                    | 11/2007          | Theodor et al.                    | NJ. USA, v                 | ol. 52, No | . 1, Jan. 1       | , 2004, 54-61 (8 pages).                                             |

| 2008/0013622 A1                    |                  | Bao et al.<br>Mohamed             |                            | -          |                   | nory Bus Encoding for Low Power:                                     |

| 2008/0104374 A1<br>2008/0159448 A1 |                  | Anim-Appiah et al.                |                            |            |                   | ne IEEE 2001. 2nd International ic Design, Mar. 28, 2001, 199-204    |

| 2008/0192621 A1                    | 8/2008           | Suehiro                           | (6 pages).                 | on Quant   | y Electron        | le Design, War. 20, 2001, 155 201                                    |

| 2008/0316070 A1<br>2009/0046009 A1 |                  | Van et al.                        |                            |            |                   | p "Slide Rule" Works with Logs,                                      |

| 2009/0040009 A1<br>2009/0059782 A1 |                  |                                   |                            |            |                   | sing", Analog Devices, Computa-<br>n Electronic Design, May 2, 1985, |

| 2009/0112551 A1                    | 4/2009           | Hollis                            | 3-9 (7 page                |            | inited noi        | ii Electionic Design, Way 2, 1965,                                   |

| 2009/0154604 A1<br>2009/0195281 A1 |                  | Lee<br>Tamura et al.              |                            |            |                   | rrier Orthogonal Cdma Signals for                                    |

| 2010/0046644 A1                    |                  | Mazet                             | ` '                        |            |                   | ation Systems", IEEE Journal on                                      |

| 2010/0081451 A1                    | 4/2010           | Mueck et al.                      | Selected At<br>842-852 (11 |            | ommunicat         | tions, vol. 12, No. 5, Jun. 1994,                                    |

| 2010/0122021 A1<br>2010/0215112 A1 |                  | Lee et al.<br>Tsai et al.         | ,                          |            | ıl., "A 1.8       | 128-Mb 125-MHz Multi-level Cell                                      |

| 2010/0215112 A1<br>2010/0215118 A1 |                  | Ware et al.                       |                            |            |                   | ead While Write", IEEE Journal of                                    |

| 2010/0235673 A1                    | 9/2010           | Abbasfar                          |                            | Circuits,  | vol. 38, N        | No. 11, Nov. 2003, 1929-1933 (5                                      |

| 2010/0296556 A1                    |                  | Rave et al.                       | pages).                    | mran ete   | 1 "Codin          | g Schemes for Chip-to-Chip Inter-                                    |

| 2010/0309964 A1<br>2011/0014865 A1 |                  | Oh et al.<br>Seo et al.           |                            |            |                   | ransactions on Very Large Scale                                      |

| 2011/0014865 A1<br>2011/0072244 A1 |                  | Lindholm et al.                   |                            |            |                   | . 14, No. 4, Apr. 2006, 393-406 (14                                  |

| 2011/0084737 A1                    | 4/2011           | Oh et al.                         | pages).                    |            |                   |                                                                      |

|                                    |                  |                                   |                            |            |                   |                                                                      |

### (56) References Cited

### OTHER PUBLICATIONS

Giovaneli, Carlos Lopez, et al., "Space-Frequency Coded OFDM System for Multi-Wire Power Line Communications", Power Line Communications and Its Applications, 2005 International Symposium on Vancouver, BC, Canada, IEEE XP-002433844, Apr. 6-8, 2005, 191-195 (5 pages).

Healey, Adam, et al., "A Comparison of 25 Gbps NRZ & PAM-4 Modulation used in Legacy & Premium Backplane Channels", Tyco Electronics Corporation, DesignCon 2012, Jan. 2012, 1-16 (16 pages).

Holden, Brian, "An exploration of the technical feasibility of the major technology options for 400GE backplanes", IEEE 802.3 400GE Study Group, Geneva, CH, Jul. 16, 2013, 1-18 (18 pages). Holden, Brian, "Simulation results for NRZ, ENRZ & PAM-4 on 16-wire full-sized 400GE backplanes", IEEE 802.3 400GE Study Group, York, UK, Sep. 2, 2013, 1-19 (19 pages).

Holden, Brian, "Using Ensemble NRZ Coding for 400GE Electrical Interfaces", IEEE 802.3 400GE Study Group, May 17, 2013, 1-24 (24 pages).

Jiang, Anxiao, et al., "Rank Modulation for Flash Memories", IEEE Transactions of Information Theory, vol. 55, No. 6, Jun. 2009, 2659-2673 (16 pages).

Oh, Dan, et al., "Pseudo-Differential Vector Signaling for Noise Reduction in Single-Ended Signaling Systems", DesignCon 2009, Rambus Inc., Jan. 2009, (22 pages).

Poulton, John, "Multiwire Differential Signaling", UNC-CH Department of Computer Science Version 1.1, Aug. 6, 2003, 1-20 (20 pages).

She, James, et al., "A Framework of Cross-Layer Superposition Coded Multicast for Robust IPTV Services over WiMAX", IEEE Wireless Communications and Networking Conference, Apr. 15, 2008, 3139-3144 (6 pages).

Skliar, Osvaldo, et al., "A Method for the Analysis of Signals: the Square-Wave Method", Revista de Matematica Teoria y Aplicationes, vol. 15, No. 2, Mar. 2008, 109-129 (21 pages).

Slepian, David, "Permutation Modulation", Proceedings of the IEE, vol. 53, No. 3, Mar. 1965, 228-236 (9 pages).

Stan, Mircea, et al., "Bus-Invert Coding for Low-Power I/O", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 3, No. 1, Mar. 1995, 49-58 (10 pages). Tallini, Luca, et al., "Transmission Time Analysis for the Parallel

Tallini, Luca, et al., "Transmission Time Analysis for the Parallel Asynchronous Communication Scheme", IEEE Transactions on Computers, vol. 52, No. 5,, May 2003, 558-571 (14 pages).

Wang, Xin, et al., "Applying CDMA Technique to Network-on-Chip", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 15, No. 10, Oct. 1, 2007, 1091-1100 (10 pages).

<sup>\*</sup> cited by examiner

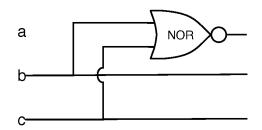

FIG. 1 (PRIOR ART)

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12A

FIG. 12B

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 24

FIG. 25

# CLOCK-EMBEDDED VECTOR SIGNALING CODES

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. No. 15/390,293, filed Dec. 23, 2016, entitled "Vector Signaling Codes with High Pin-Efficiency for Chip-to-Chip Communication and Storage", which is a continuation of <sup>10</sup> U.S. application Ser. No. 15/176,085, filed Jun. 7, 2016, entitled "Clock-Embedded Vector Signaling Codes", which is a continuation of U.S. application Ser. No. 14/636,098, filed Mar. 2, 2015, entitled "Clock-Embedded Vector Signaling Codes", which claims the benefit of U.S. Provisional <sup>15</sup> Application No. 61/946,574 filed on Feb. 28, 2014, all of which are hereby incorporated herein by reference in their entirety for all purposes.

The field of the invention generally relates to communications systems for conveying information with vector signaling codes.

### REFERENCES

The following references are herein incorporated by ref- 25 erence in their entirety for all purposes:

U.S. Patent Publication No. 2011/0268225 of U.S. patent application Ser. No. 12/784,414, filed May 20, 2010, naming Harm Cronie and Amin Shokrollahi, entitled "Orthogonal Differential Vector Signaling", hereinafter identified as 30 [Cronie I];

U.S. patent application Ser. No. 13/030,027, filed Feb. 17, 2011, naming Harm Cronie, Amin Shokrollahi and Armin Tajalli, entitled "Methods and Systems for Noise Resilient, Pin-Efficient and Low Power Communications with Sparse 35 Signaling Codes", hereinafter identified as [Cronie II];

U.S. Provisional Patent Application No. 61/753,870, filed Jan. 17, 2013, naming John Fox, Brian Holden, Peter Hunt, John D Keay, Amin Shokrollahi, Richard Simpson, Anant Singh, Andrew Kevin John Stewart, and Giuseppe Surace, 40 entitled "Chip-to-Chip Communication with Reduced SSO Noise", hereinafter identified as [Fox I];

U.S. patent application Ser. No. 13/842,740, filed Mar. 15, 2013, naming Brian Holden, Amin Shokrollahi and Anant Singh, entitled "Methods and Systems for Skew Tolerance in 45 and Advanced Detectors for Vector Signaling Codes for Chip-to-Chip Communication", hereinafter identified as [Holden I];

U.S. Provisional Patent Application No. 61/934,804, filed Feb. 2, 2014, naming Ali Hormati and Amin Shokrollahi, 50 entitled "Methods for Code Evaluation Using ISI Ratio", hereinafter identified as [Hormati I];

U.S. Provisional Patent Application No. 61/934,807, filed Feb. 2, 2014, naming Amin Shokrollahi, entitled "Vector Signaling Codes with High pin-efficiency and their Application to Chip-to-Chip Communications and Storage", hereinafter identified as [Shokrollahi I];

U.S. Provisional Patent Application No. 61/839,360, filed Jun. 23, 2013, naming Amin Shokrollahi, entitled "Vector Signaling Codes with Reduced Receiver Complexity", hereinafter identified as [Shokrollahi II].

The following additional references to prior art have been cited in this application:

U.S. Pat. No. 7,053,802, filed Apr. 22, 2004 and issued May 30, 2006, naming William Cornellus, entitled "Single-65 Ended Balance-Coded Interface with Embedded-Timing", hereinafter identified as [Cornelius];

2

U.S. Pat. No. 8,064,535, filed Mar. 2, 2007 and issued Nov. 22, 2011, naming George Wiley, entitled "Three Phase and Polarity Encoded Serial Interface, hereinafter identified as [Wiley].

### FIELD OF THE INVENTION

The present invention relates generally to the field of communications, and more particularly to the transmission of signals capable of conveying information within and between integrated circuit devices.

### BACKGROUND

In communication systems, a goal is to transport information from one physical location to another. It is typically desirable that the transport of this information is reliable, is fast and consumes a minimal amount of resources. One common information transfer medium is the serial communications link, which may be based on a single wire circuit relative to ground or other common reference, or multiple such circuits relative to ground or other common reference. A common example uses singled-ended signaling ("SES"). SES operates by sending a signal on one wire, and measuring the signal relative to a fixed reference at the receiver. A serial communication link may also be based on multiple circuits used in relation to each other. A common example of the latter uses differential signaling ("DS"). Differential signaling operates by sending a signal on one wire and the opposite of that signal on a matching wire. The signal information is represented by the difference between the wires, rather than their absolute values relative to ground or other fixed reference.

There are a number of signaling methods that maintain the desirable properties of DS while increasing pin efficiency over DS. Vector signaling is a method of signaling. With vector signaling, a plurality of signals on a plurality of wires is considered collectively although each of the plurality of signals might be independent. Each of the collective signals is referred to as a component and the number of plurality of wires is referred to as the "dimension" of the vector. In some embodiments, the signal on one wire is entirely dependent on the signal on another wire, as is the case with DS pairs, so in some cases the dimension of the vector might refer to the number of degrees of freedom of signals on the plurality of wires instead of exactly the number of wires in the plurality of wires.

With binary vector signaling, each component or "symbol" of the vector takes on one of two possible values. With non-binary vector signaling, each symbol has a value that is a selection from a set of more than two possible values. Any suitable subset of a vector signaling code denotes a "sub code" of that code. Such a subcode may itself be a vector signaling code.

A vector signaling code, as described herein, is a collection C of vectors of the same length N, called codewords. The ratio between the binary logarithm of the size of C and the length N is called the pin-efficiency of the vector signaling code.

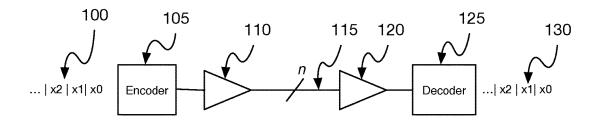

FIG. 1 illustrates a prior art communication system employing vector signaling codes. Bits x0, x1, . . . enter block-wise 100 into an encoder 105. The size of the block may vary and depends on the parameters of the vector signaling code. The encoder generates a codeword of the vector signaling code for which the system is designed. In operation, the encoder may generate information used to control PMOS and NMOS transistors within driver 110,

generating voltages or currents on the N communication wires 115. Receiver 120 reads the signals on the wires, possibly including amplification, frequency compensation, and common mode signal cancellation. Receiver 120 provides its results to decoder 125, which recreates the input 5

Depending on which vector signaling code is used, there may be no decoder, or no encoder, or neither a decoder nor an encoder. For example, for the 8b8w code disclosed in [Cronie II], both encoder 105 and decoder 125 exist. On the other hand, for the Hadamard code disclosed in [Cronie I], an explicit decoder may be unnecessary, as the system may be configured such receiver 120 generates output bits 130

The operation of the transmitter, consisting of elements 100, 105, and 110, and that of the receiver, consisting of elements 120, 125, 130 have to be completely synchronized in order to guarantee correct functioning of the communication system. In some embodiments, this synchronization is 20 performed by an external clock shared between the transmitter and the receiver. Other embodiments may combine the clock function with one or more of the data channels, as in the well-known Biphase encoding used for serial communications.

One important example is provided by memory interfaces in which a clock is generated on the controller and shared with the memory device. The memory device may use the clock information for its internal memory operations, as well as for I/O. Because of the burstiness and the asynchronicity of memory operations, the I/O may not be active all the time. Moreover, the main clock and the data lines may not be aligned due to skew. In such cases, additional strobe signals are used to indicate when to read and write the data.

### **BRIEF DESCRIPTION**

Vector signaling codes providing guaranteed numbers of transitions per unit transmission interval are described, along with a generalized system architecture. Elements of 40 the architecture may include multiple communications subsystems, each having its own communications wire group or sub-channel, clock-embedded signaling code, pre- and postprocessing stages to guarantee the desired code transition density, and global encoding and decoding stages to first 45 distribute data elements among the sub-systems, and then to reconstitute the received data from its received sub-system elements. Example embodiments of each architectural elements are described, as well as example code embodiments suitable for sub-channel communication.

### BRIEF DESCRIPTION OF FIGURES

FIG. 1 illustrates a prior art communication system employing vector signaling codes.

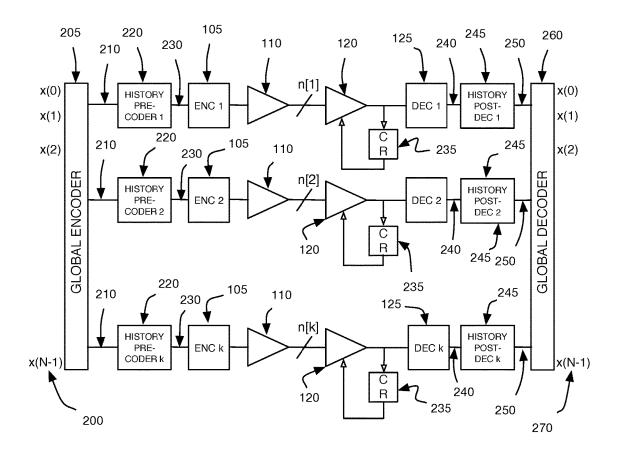

FIG. 2 shows an embodiment of a vector signaling communications system with embedded clock information.

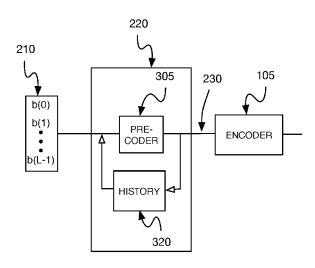

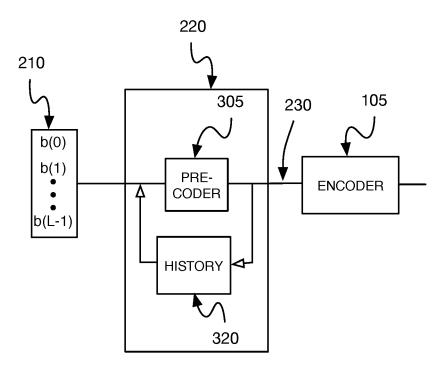

FIG. 3 is a block diagram of one embodiment of the history pre-coder.

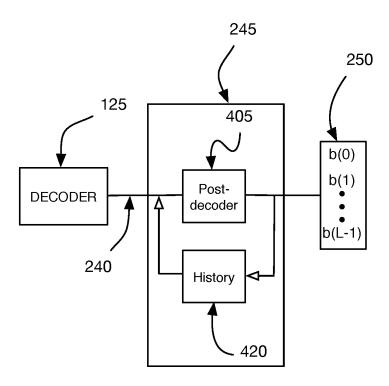

FIG. 4 is a block diagram of one embodiment of the 60 history post-decoder.

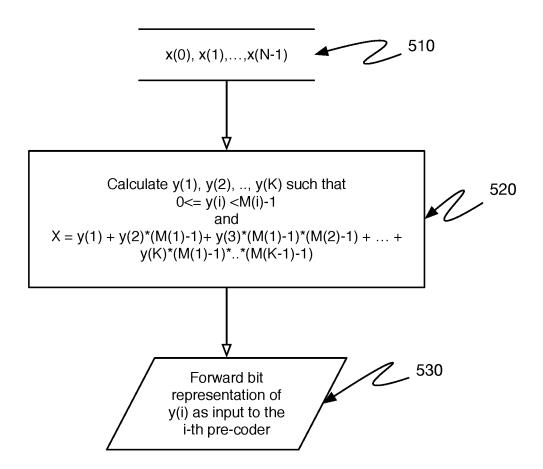

FIG. 5 is a flow chart for one embodiment of the Global Encoder.

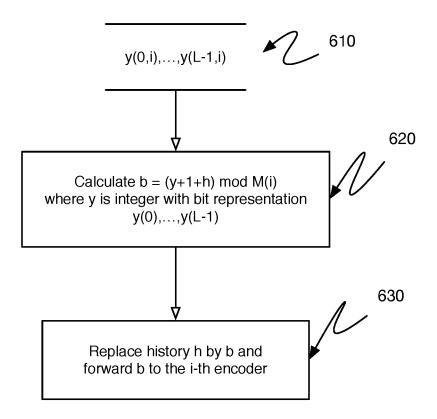

FIG. 6 is a flow chart for one embodiment of the pre-code

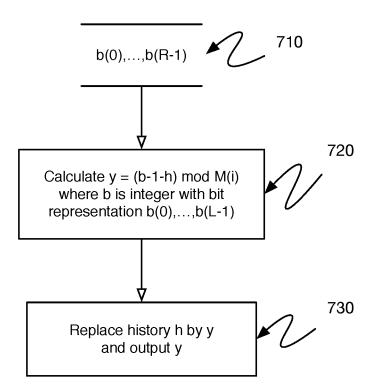

FIG. 7 is a flow chart for one embodiment of the postdecoder unit.

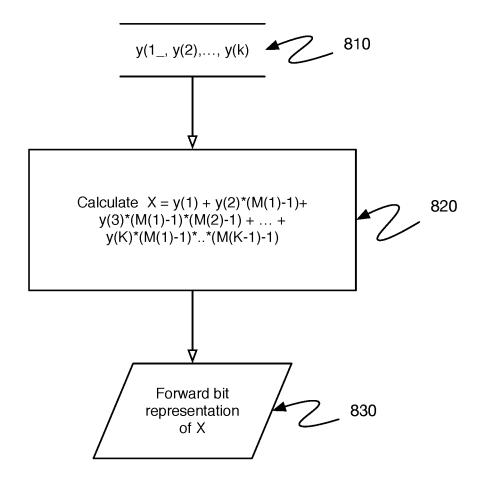

FIG. 8 is a flow chart for one embodiment of the Global

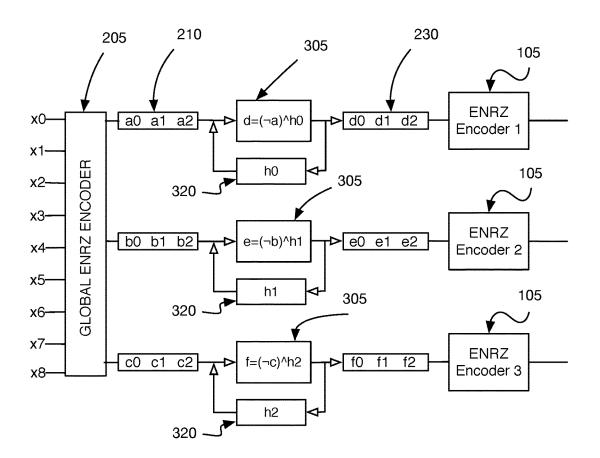

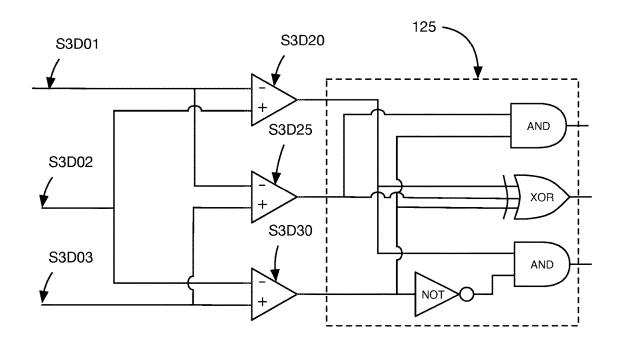

FIG. 9 is a block diagram of one embodiment of the transmitter encoding portions of an ENRZ3 communications

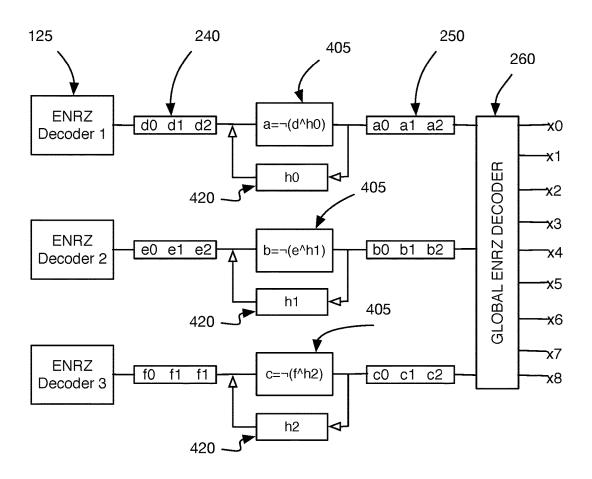

FIG. 10 is a block diagram of one embodiment of the receiver decoding portions of an ENRZ3 communications

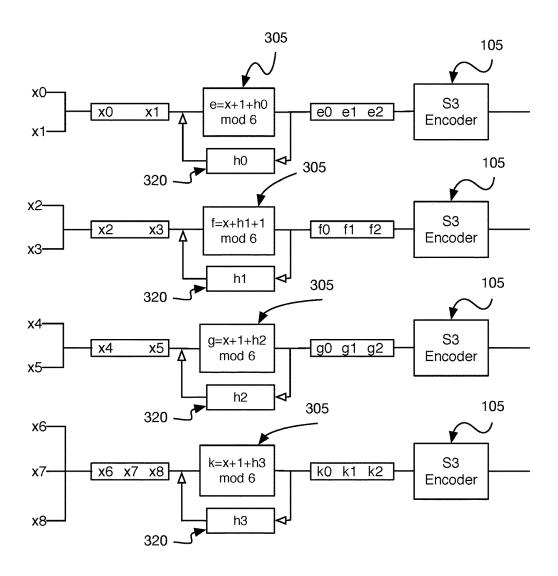

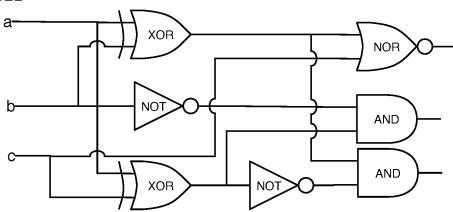

FIG. 11 is a block diagram of one embodiment of the transmission encoding portions encoder of a S34 communications system.

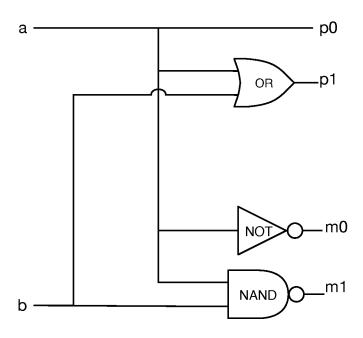

FIGS. 12A and 12B show schematic diagrams of two circuits providing an embodiment of an encoder for S34.

FIG. 13 is a block diagram of one embodiment of the 15 receiver decoding portions of a S34 communications system.

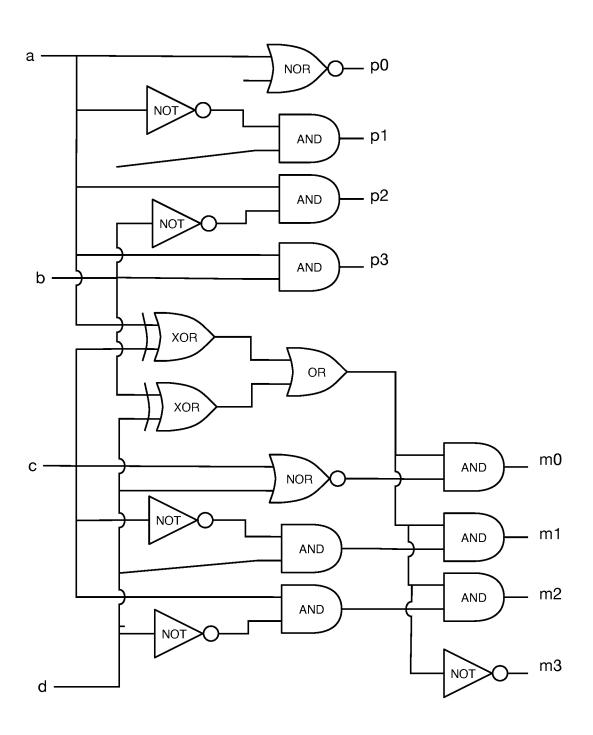

FIG. 14 shows one embodiment of an encoder for S4 vector signaling code.

FIG. 15 shows one embodiment of an encoder for P3 vector signaling code.

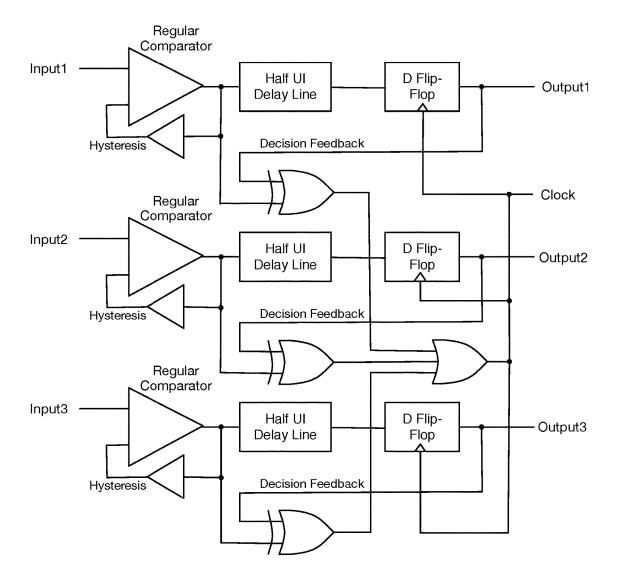

FIG. 16 shows an embodiment of clock extraction using Analog Hysterisis plus Decision Feedback High Pass Filter

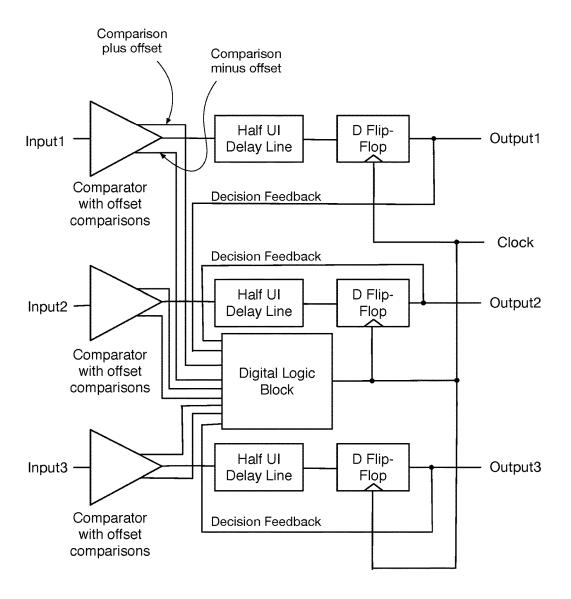

FIG. 17 shows an embodiment of clock extraction using 25 Digital hysteresis plus Decision Feedback High Pass Filter clocking.

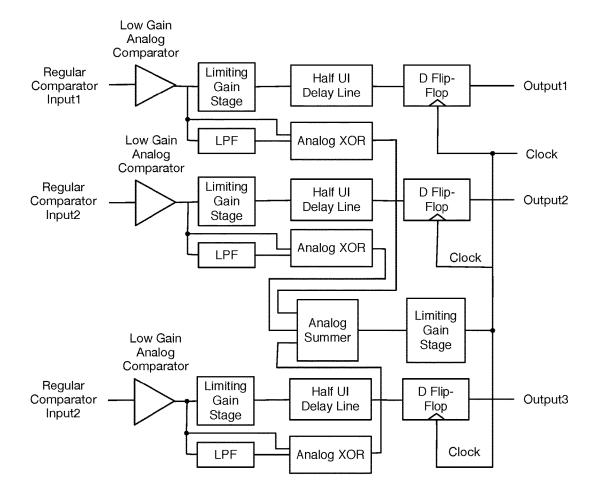

FIG. 18 illustrates an embodiment of clock extraction using Analog XOR clocking.

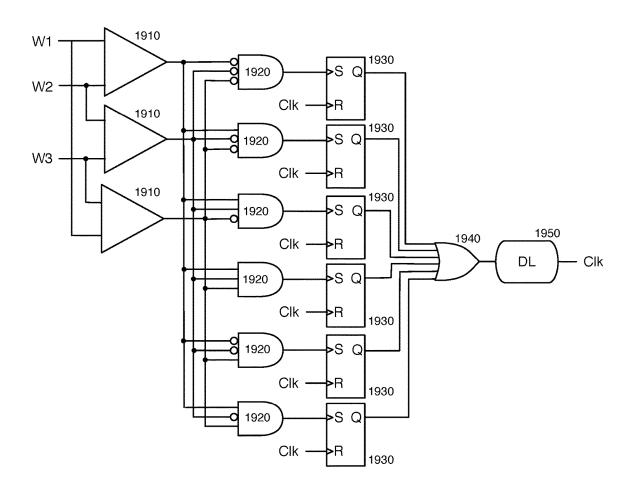

FIG. 19 illustrates an embodiment of clock extraction using per-codeword detectors and digital hysteresis.

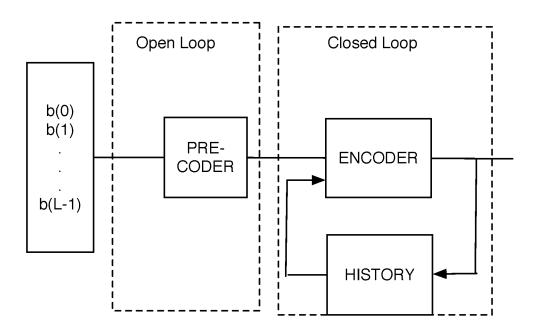

FIG. 20 is a block diagram of an encoder embodiment, highlighting its open- and closed-loop processing circuit portions.

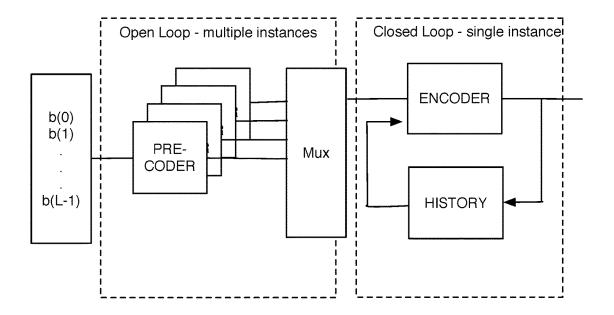

FIG. 21 is a block diagram of an encoder embodiment as 35 in FIG. 20, where multiple instantiations of the open-loop portion of the circuit are implemented in parallel.

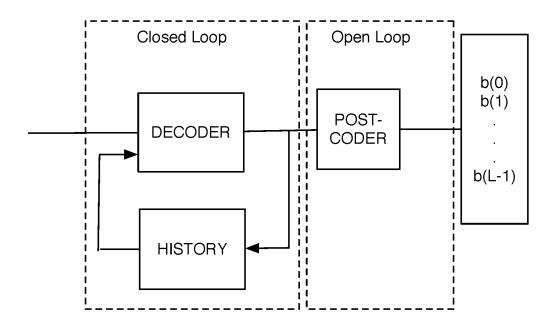

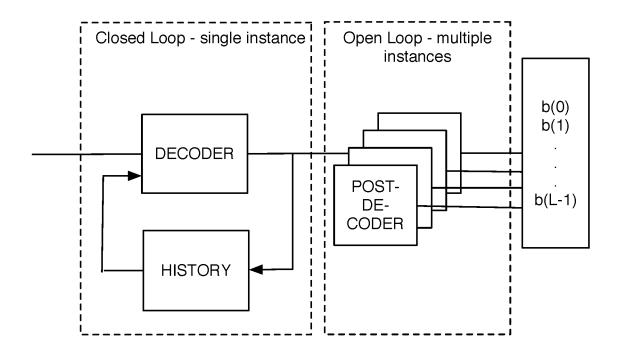

FIG. 22 is a block diagram of a decoder embodiment, highlighting the open- and closed-loop processing circuit portions.

FIG. 23 is a block diagram of an encoder embodiment as in FIG. 22, where multiple instantiations of the open-loop portion of the circuit are implemented in parallel.

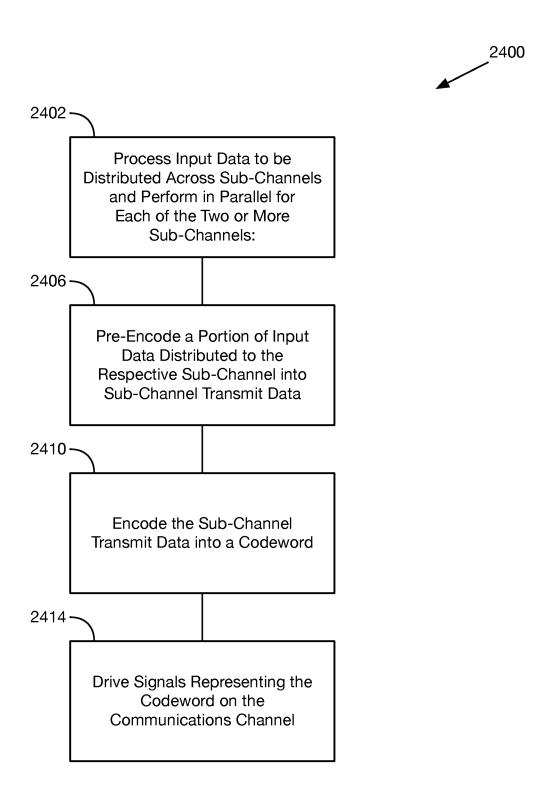

FIG. 24 is a flowchart of a transmission method.

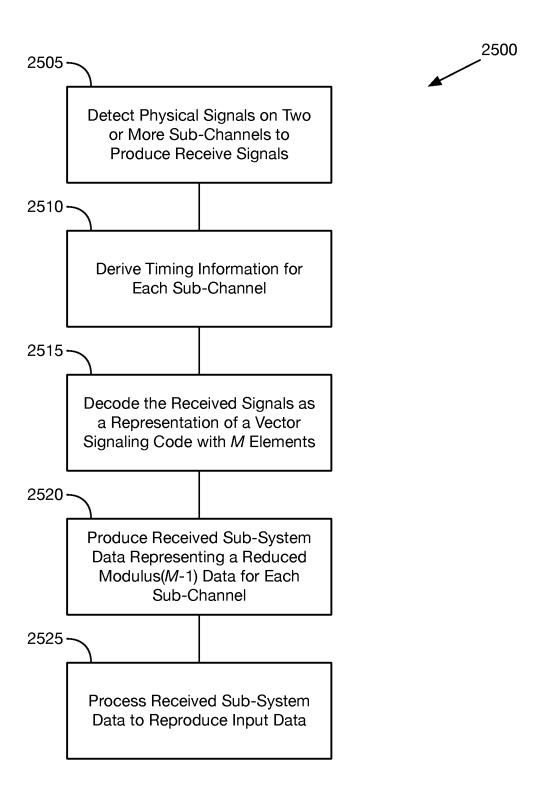

FIG. 25 is a flowchart of a reception method.

### DETAILED DESCRIPTION

An embodiment of a vector signaling communication system with embedded clock information is shown in FIG. 50 2. Elements of this system will be referenced and further described in descriptions of subsequent figures.

The communication system of FIG. 2 consists of k distinct communication sub-systems, each comprising a history precoder 220, encoder 105, driver 110, n[i] communication wires, receiver 120, a clock-recovery unit 235, decoder 125, history post-decoder unit 245. There are a total of n[1]+n  $[2]+ \dots +n[k]$  communication wires, subdivided into k groups having  $n[1], n[2], \ldots, n[k]$  wires, respectively. Each communication sub-system i utilizes a vector signaling code in which the codewords have n[i] coordinates.

As exemplified in this figure, bits  $x(0), \ldots, x(N-1)$  enter as a block into "Global Encoder" unit 205. In some embodiments, this unit may only forward the bits in subgroups, while in other embodiments this unit may perform further computations on the incoming bits 200. Global Encoder 205 outputs k groups of bits 210, one for each of the communication sub-systems.

The i-th group of bits 210 enters the i-th history pre-coder unit 220, which in turn outputs another group of bits 230 which is forwarded to encoder 105 of the communication sub-system. Encoder 105 generates a codeword of its corresponding vector signaling code, and driver 110 drives the 5 coordinates of this codeword on the n[i] communication wires as voltages or currents.

The communication wire voltages or currents are received as signals by receiver 120, which may perform further equalization and processing of the received signals, and may generate information for the clock-recovery unit 235 which recovers the clock information from the received signals. The received signals are further forwarded to decoder 125, which generates a group of bits 240 forwarded to the corresponding history post-decoder unit 245. This unit cal- 15 culates a possibly new set of bits 250 and forwards these to the Global Decoder unit 260. As with the corresponding Global Encoder, in some embodiments Global Decoder 260 simply concatenates or combines inputs 250 to obtain output bits 270, while in other embodiments Global Decoder 260 20 performs additional calculations on the bits received 250 from the various history post-decoder units to re-generate the bits  $x(0), \ldots, x(N-1)$  output as 270. The number of codewords of the vector signaling codes used in the i-th communication sub-system of FIG. 2 is denoted by M(i) in 25 the following.

In accordance with at least one embodiment, reception of distinct codewords in each unit interval provides a selfclocking capability. Thus, decoder 125 may consider a previous unit interval ended and a new unit interval (and 30 thus, a new need to decode a codeword) begun each time a new (i.e., different from the preceding codeword) appears at its input. In such an embodiment, for every unit interval a codeword is transmitted on each communication sub-system that is different from the codeword sent in the previous unit 35 interval. Thus, the number of possible codewords across all the communication sub-systems is

$$(M(1)-1)*(M(2)-1)*...*(M(k)-1)$$

(Eqn. 1)

shown in FIG. 3. One task of this unit is to make sure that the same codeword of the vector signaling code is not sent on the corresponding communication wires (also referred to herein as a sub-channel) in two consecutive unit intervals. Where the vector signaling code receiver uses comparators 45 for the detection of the codeword, that condition guarantees that the output of at least one of the comparators changes value from one unit interval to the next. This value change can then be used to recover the clock information, to be subsequently described in more detail.

As shown in FIG. 3, the history pre-coder unit comprises a pre-coder 305 and a history memory unit 320. Upon receiving the block of bits  $b(0), \dots b(L-1)$  from the Global Encoder 205, the pre-coder 305 computes its output using these bits, and the history bits in 320. It forwards the 55 resulting bits 230 to the encoder 105, and simultaneously replaces the value of the history memory 320 with these bits. In some embodiments described below, the history memory 320 may keep the vector signaling codeword that was transmitted in the previous clock cycle and use a pre-coder 60 which makes sure that the next transmitted codeword differs from the previous one. Such examples are given below for various types of vector signaling codes.

Similarly, an embodiment of the history post-decoder unit 245 is shown in FIG. 4. It comprises a post-decoder unit 405 and a history memory unit 420. Upon receiving the block 240 of bits from encoder 125, the post-decoder calculates a

possibly new block of bits from the bits in 240 and the bits in its history unit 420, forwards the new bits 250 to the Global Decoder 260, and replaces the bits in its history unit with these bits.

A flow-chart of an exemplary embodiment of the Global Encoder 205 is given in FIG. 5. The main task of the Global Encoder is to compute from the given block of bits x(0), . . . , x(N-1) a number k of blocks of bits, one for every communication sub-system in FIG. 2, such that these blocks are uniquely determined by the incoming bits 200, and vice-versa. In the procedure described in FIG. 5, the incoming bits  $x(0), \ldots, x(N-1)$  in 510 are used in Step 520 to compute bit-representations of reduced-modulus integers  $y(1), y(2), \dots, y(k)$ , wherein each y(i) is an integer from 0to M(i)-2 inclusive (note that y(i) is strictly less than M(i)-1, and hence referred to herein as having a reducedmodulus), and wherein M(i) is the number of codewords of the vector signaling code used in the i-th communication sub-system in FIG. 2.

It might be expected that when converting a number to a mixed-based representation (i.e., a mixed modulus), the digits in each position would range from 0 to M-1, where the modulus M is determined by the number of possible signals, M. That is, if there are M possible signals or codes available to represent the digits (e.g., base 10 uses ten digits: 0 through 9, and base 5 uses five digits: 0 through 4), a typical conversion might use M values: 0 to M-1. Note, however, that the conversions described herein uses digits 0 through M-2, and thus uses a reduced modulus of M-1 compared to what would normally be available with a set of M signals, or vector code codewords. The advantages of using the reduced modulus values are described below.

The particular way this calculation is done in Step 520 is by representing the integer X whose binary representation is  $x(0), \ldots, x(N-1)$ , with x(0) being the least significant and x(N-1) being the most significant bit, as

$$X = \sum_{i=1}^{k} y(i) \prod_{i=1}^{i-1} (M(j)-1).$$

(Eqn. 2)

Many different algorithms may be used to perform this An embodiment of the history pre-coder unit 220 is 40 computation, as is known to those of skill in the art. For example, where  $0 \le X < 257$ , so N=9, M(1)=M(2)=12, M(3)=6, then we have  $y(1)=X \mod 11$ ,  $y(2)=(X-y(1))/11 \mod 11$ , and y(3)=(X-y(1)-11\*y(2))/121.

One embodiment of a general procedure for pre-code unit 220 is outlined in FIG. 6. It is assumed that the bits in the history memory unit 320 of FIG. 3 represent an integer, called h, in this figure. Upon receiving the block of L bits  $y(0,i), \dots, y(L-1,i)$  as the i-th output **210** of Global Encoder 205, the pre-coder calculates in Step 620 the integer b=(y+ 1+h) mod M(i), wherein y is the integer with bit-representation y(0,i), . . . , y(L-1,i), and M(i) is the number of codewords of the i-th vector signaling code. It is assumed that the integer h is between 0 and M(i)-1, so it corresponds uniquely to a codeword of the i-th vector signaling code. Moreover, since the value of y is, by construction, smaller than M(i)-1 (i.e.,  $\leq M(i)-2$ ), we always have that b is not equal to h mod M(i). Since h corresponds to the index of the codeword in the i-th vector signaling code transmitted in the last unit interval, and b corresponds to the index of the codeword transmitted in the current unit interval, this type of calculation makes sure that no two consecutive codewords are the same. The use of the reduced modulus in calculating the integers y causes the encoder to generate an output codeword that is different from the immediately prior codeword based on the reduced modulus digit (y) and the prior codeword (h). In summary, after an initial codeword h, selected from M codewords (0 to M-1), has been sent in a

first signaling interval, a subsequent codeword is selected based on h+1+y, where y is a data-dependent reduced-modulus (M-1) integer and is in the range 0 to M-2, such that no valid data-dependent reduced modulus integer will result in the subsequent codeword equaling the initial codeword b.

Other types of operations or the pre-code unit are also possible. For example, where M(i) is a power of 2, it is possible to ensure the distinctness of b and h using simple XOR arithmetic, as will be shown in the subsequent example of an ENRZ encoder.

An embodiment of the operation of the post-decoder unit **245** is shown in FIG. **7**. The input to this procedure is a block of bits  $b(0), \ldots, b(R-1)$  in Step **710**. This block may have been produced by the decoder **125** of the i-th communication sub-system illustrated in FIG. **2**. In Step **720**, the post-decoder unit may use the bits in its memory history unit, interpreted as an integer h, to calculate an integer y=(b-1-h) mod M(i), wherein b is the integer with bit-representation  $b(0), \ldots, b(R-1)$ . In Step **730** the history value h is replaced by b, and simultaneously, b is forwarded to the Global Decoder **260**.

The operation of an embodiment of the Global Decoder **260** is given in FIG. **8**. The input to this procedure are y(1), 25, ..., y(k), wherein each y(i) is a block of bits generated by the post-decoder unit of the i-th communication sub-system. In Step **820** an integer X is calculated from y(1), ..., y(k) according to the formulation in (Eqn. 2). The bit representation of this integer is the desired sequence of bits **270** in FIG. **2**.

As mentioned above, in some applications the Global Encoder **205** may only forward the incoming bits in subgroups to the corresponding communication sub-systems, and the Global Decoder **260** may just collect the incoming bit blocks and concatenate them to obtain the bits **270**. Some such examples are discussed further below. Clock Extraction

[Holden I] describes comparator-based detectors for vector signaling codes designed such that no comparator is presented with ambiguous decision conditions; that is, at all times each comparator output is either explicitly true, or explicitly false. An embodiment based on such codes and detectors may be combined with a simple transition detector to extract sub-system transition information (herein called the "edge signal") to drive a clock extraction circuit, as in 235 of FIG. 2. Three circuits for these codes are detailed below. These are referred to in said descriptions as AH-DF-HPF, UDH-DF-HPF, and A-XOR.

The fourth type of clock extractor, referred to in said descriptions as PCD-DH, uses a per-codeword detector. This type of detector works with vector signaling codes in which the comparator outputs have ambiguous outputs.

In general, clock extraction embodiments detect changes in sub-system detector outputs. In some embodiments, only changes from one valid codeword to another valid codeword are detected, and in other embodiments decision feedback and/or hysteresis is provided to the input signal comparators to avoid extraneous transitions caused by signal reflections and noise. Any of a number of methods may then be used to analyze the edge signal to eliminate artifacts caused by near-simultaneous detector output transitions, including methods known to the art, producing a reliable sampling clock derived from the detector edges. One such embodiment incorporates fixed or variable delay stages and a simple state machine configured such that a clock output is pro-

8

duced a fixed delay time after the last edge signal transition, suppressing the effect of multiple edge signal transitions within the delay interval.

As will be apparent to one of skill in the art, propagation delay differences (also know as skew) within a communications channel group will result in different arrival times for receive data. If the amount of this skew is significant (i.e. more than a transmit unit interval), the teachings of [Holden I] may be applied to permit the coherent reconstruction of aggregated receive data.

Similarly, a communications system utilizing multiple sub-systems may generate a global receive clock by applying the same edge signal generation and sampling clock derivation methods using the individual sub-system receive clocks as inputs, and producing a global sampling clock suitable for sampling the aggregated receive data as obtained at 270 of FIG. 2. As in sub-system clock extraction, embodiments presenting significant skew between sub-system results must carefully control generation of an aggregate or global decoder output clock, such that all of the global decoder's component inputs are valid and the result meets all necessary set-up and hold times for subsequent circuits. Some embodiments may require intermediary holding latches on the sub-system results and/or other skew mitigation measures as taught by [Holden I] or as generally applied in practice.

Code/Receiver Categories for Clock Extraction

The codes and the receivers that accompany them that are used with these clocking solutions can be divided into two categories. The first group of codes can be described as Unambiguous Comparator Output code/receiver (UCO). For these code/receiver combinations, the binary or multiwire comparator circuits used in the defined receiver have unambiguous outputs for every codeword in the code. An example of a code that is always UCO is the ENRZ code, also known as H4 code or Hadamard code of size 4, as described in [Cronie I].

The second group of codes can be called Ambiguous Comparator Output codes/receiver (ACO). In these code/receiver combinations, a given comparator is sometimes presented with inputs at the same level and thus has an ambiguous output for some codewords. These ambiguous outputs are later resolved in a decoder stage. An example of a code that is always ACO is the 8b8w code described in Cronie II.

In practical implementations, most codes are either UCO or ACO. There are a few codes that are ACO with one receiver implementation and UCO with another receiver implementation, typically with more complex multi-input analog detectors.

AH-DF-HPF—Analog Hysteresis Plus Decision Feedback High Pass Filter Clocking Solution

The following clocking solution is only applicable to UCO code/receiver solutions.

The simplest clock extraction embodiment adds an analog hysteresis function to each of the comparators in order to filter out the multiple zero crossing on the wires that are caused by noise and reflections, as illustrated in FIG. 16. However, there are known disadvantages to such solutions. The maximum amplitude of any reflections on the communications channel must be known, so that the hysteresis offset value may be chosen correctly. Such embodiments are known to add jitter to the recovered clock, as noise or reflections on the leading edge can cause the transition to occur early, causing the effective eye opening in the timing dimension to close, and reducing the ability of the receiver to handle difficult channels. Similarly, the added hysteresis

lowers the receive sensitivity of the comparators, reducing the eye opening in the amplitude dimension as well. Finally, such analog hysteresis embodiments contain a closed loop circuit that must be implemented carefully.

The function of the hysteresis comparator can be 5 described as follows:

```

HysOut = Hysteresis(HysIn, HysOffset)

If HysOut == 0

If HysIn > HysOffset, HysOut = 1;

Else HysOut = 0;

If HysIn > - HysOffset, HysOut = 1;

Else HysOut = 0;

```

For each detector, the hysteresis functions are applied to the comparators:

HysOffset=voltage value determined either statically or adaptively that exceeds the expected amplitude of reflections and other noise sources in the receive signal.

C(x)=Hysteresis(detector inputs(x), HysOffset)

In the following example, the value "x" is shown to range 25 HysCompOutHigh(2)=OffComparator(Inputs(2), from 0 to 2 for clarity. This is the case for the ENRZ code. For other UCO codes, the value that "x" would range over is equal to the number of comparators.

The clock signal is created by using an exclusive- or delivers a transition on one wire each clock:

Clock=(C(0) XOR Q(0)) OR (C(1) XOR Q(1)) OR (C(2) XOR Q(2))

For each comparator, the data is delayed by a delay line that has a nominal delay of one half of the unit interval (UI). The actual delay would depend on the implementation and may be somewhat less or more than one half the UI:

D(0)=HalfUIDelayLine(C(0))

D(1)=HalfUIDelayLine(C(1))

D(2)=HalfUIDelayLine(C(2))

For each comparator, recover each bit with a D Flip-Flop (DFF) or cascade of latches in some implementations:

Q(0)=DFF(Clock, D(0))

Q(1)=DFF(Clock, D(1))

Q(2)=DFF(Clock, D(2))

/\*Decode and retime the data\*/

DecodedData = Decode(Q(0), Q(1), Q(2))

RetimedDecodedData=DFFs(Clock, DecodedData)

UDH-DF-HPF—Unrolled Digital Hysteresis Plus Deci- 50 sion Feedback High Pass Filter Clocking Solution

The following clocking solution is only applicable to UCO code/receiver solutions.

An embodiment of clocking solution AH-DF-HPF shown in FIG. 17 performs six additional binary comparisons, such 55 that two values of a hysteresis comparison is provided along with each data comparison. This embodiment has the advantage that the closed loop portion of the hysteresis function is digital, and the data path portion of the circuit has better sensitivity than AH-DF-HPF. The disadvantages include 60 greater implementation size and higher power consumption, because of the additional comparators needed to produce the required hysteresis comparisons.

One embodiment uses two extra separate comparators that add and subtract a fixed value from the analog inputs, rather than using analog hysteresis feedback. The hysteresis function may then be implemented digitally.

10

Another embodiment uses a combined comparator that delivers three outputs, the regular comparator output, an output with the comparison done with the offset added, and a third with the comparison done with the offset subtracted.

This example uses the embodiment with separate comparators. In this example, the function of the regular comparators is described as follows:

Comparator(Inputs)

The operation of the offset comparators adds the offset value to the comparator inputs before the comparison is done. It is be described as follows:

OffComparator(Inputs, HysOffset)

For a three-comparator code/receiver solution such as for the ENRZ code, the comparators are:

OffCompOutHigh(0)=OffComparator(Inputs(0), HysOffset) CompOut(0) = Comparator(Inputs(0))

OffCompOutLow(0)=OffComparator(Inputs(0), -HysOff-

20 HysCompOutHigh(1)=OffComparator(Inputs(1), HysOff-

CompOut(1) = Comparator(Inputs(1))

HysCompOutLow(1) = OffComparator(Inputs(1), -HysOff-

CompOut(2)=Comparator(Inputs(2)) HysCompOutLow(2) =OffComparator(Inputs(2), -HysOffset)

This circuit recovers the clock by comparing the flip-flop function to look for changes on any of the wires. The code 30 outputs with the comparator outputs from the opposite side of center:

Clock=

((NOT Q(0)) AND CompOutHigh(0)) OR (Q(0) AND (NOT CompOutLow(0))) OR

((NOT Q(1)) AND CompOutHigh(1)) OR (Q(1) AND (NOT CompOutLow(1))) OR

((NOT Q(2)) AND CompOutHigh(2)) OR (Q(2) AND (NOT CompOutLow(2)))

The rest is the same as in the AH-DF-HPF embodiment. A-XOR—Analog XOR Clocking Solution

An embodiment of clock extraction using Analog XOR clocking is shown in FIG. 18. This embodiment is compatible with both UCO and ACO code/receiver solutions

Each comparator function is divided into two halves. The 45 first half of each comparator is a linear low gain comparator that performs the function of the comparator with a linear output. Each of these linear values is then passed through an analog low-pass filter. Each linear value is compared against the analog low-pass filtered version of itself by an analog XOR circuit, which serves as the second half of the comparison function. Analog XOR circuits are well known in the art. The analog XOR circuit will produce a voltage output that has a higher value if the inputs have different values than if they have the same value.

The outputs of the three analog XOR circuits are summed. The output of the summer is passed through a limiting gain stage to give the signal sharp edges. This signal then forms the clock.

In parallel to the clock path, in the data path, the output of the low gain comparator is passed through a gain stage to form a regular binary comparator. The clock is used to sample this data.

A challenge with this circuit is that the detected change is less for some code transitions than for others. This circuit is also sensitive to reflections and noise.

PCD-DH-Per Codeword Detectors, Digital Hysteresis Clocking Solution

This embodiment is compatible with both UCO and ACO code/receiver solutions.

As illustrated in FIG. 19, this embodiment of a clock extraction circuit does not use an analog hysteresis circuit. Instead it uses normal comparators 1910. A special unrolled 5 and equal-delay digital detector is implemented that has one output for each of the allowed codewords.

These per-codeword outputs put out a high value if that codeword is present on the output of comparators 1910, and a low value if that codeword is not present. The circuit is 10 implemented to have a roughly equal delay from the output of each of the comparators to the output of each of the per-codeword detector. An example of such an equal-delay circuit is a circuit that has a AND gate 1920 per codeword. That AND gate has the same number of legs as the number of comparators. The inputs of the legs of the AND gates are wired to the appropriate true or complement outputs of the comparators, here shown distinct true and complimentary inputs to each AND gate 1920. The particular decoded values shown are exemplary, and non-limiting.

When ACO codes are employed with this detector, the per-codeword detectors are only connected to those comparator outputs that are needed to detect that codeword and not to those that have an ambiguous value for that codeword.

The outputs of each of the per-codeword detectors is 25 wired to the Set input of a per-codeword Resettable D Flip-Flop with the D input set to a high value (or equivalent circuit.) For purposes of illustration, the flip-flops 1930 are shown in FIG. 19 as edge triggered set/reset devices, with the output Q going true on a rising edge of input S, and going false on a rising edge of input R. Thus, any detected codeword by AND gates 1920 will cause the corresponding flip-flop 1930 to set. The outputs of all of these Flip-Flops 1930 are ORed together 1940 and delayed by a delay line 1950 that is statically or dynamically calibrated to create a 35 rising edge in the middle of the data eye. Said rising edge signal is used as the clock in a data re-timer circuit. Said rising edge signal is also connected to the Reset input of each flip-flop 1930 to clear the detectors for the next clock cycle.

The described embodiment will catch the first instance within a clock cycle of a codeword being detected and will ignore subsequent reflections that cause zero-crossings. Memory Links

As one specific example applying the previously 45 described systems and methods, an embodiment is described of links connecting one or more Dynamic Random Access Memory (DRAM) units to a memory controller.

Traditionally, such links are byte-oriented, with each data byte communicated over 8 wires in a single-ended manner, 50 and a 9th wire communicating a write mask signal identifying whether the data byte is to be applied or ignored in the associated memory operation. Two more wires provide a strobe signal using differential signaling. As has been noted in prior art such as [Wiley] and [Cornelius], the ability to 55 embed the clock information into the data and hence eliminate the need for separate strobe signals can be advantageous. The following examples show several examples of vector signaling codes and how they can be used in conjunction with the general principles described above.

In order to have a system according to FIG. 2 for such a memory link, the number of vector signaling codewords in these applications has to satisfy the inequality

$$257 \le (M(1)-1)^* \dots *(M(k)-1)$$

(Eqn. 3)

as 256 distinct codewords are required to communicate 8 bits of data, and at least a 257th codeword is required to

12

communicate the notification provided by the write mask signal that this data byte is to be ignored for this memory operation.

### Example 1: ENRZ3

ENRZ is a vector signaling code obtained from a 4×4 Hadamard transform, as described in [Cronie I]. It has eight codewords and transmits them on 4 wires. The eight codewords are the four permutations of the vector  $(1, -\frac{1}{3}, -\frac{1}{3}, -\frac{1}{3})$  and the four permutations of  $(-1, \frac{1}{3}, \frac{1}{3}, \frac{1}{3})$ . In this case, k=3, and M(1)=M(2)=M(3)=8. The inequality of (Eqn. 3) is satisfied. The resulting embodiment is hereinafter called ENRZ3, referring to its three sub-systems, each utilizing ENRZ vector signaling code.

An exemplary operation of the encoder is detailed in FIG.

9. The input to the Global Encoder consists of 9 bits x0, x1,

..., x8 corresponding to an integer between 0 and 256

inclusive (that is, 257 distinct values.) The Global Encoder

may have an implementation as previously described in FIG.

5. It produces 3 groups of 3 bits, called (a0, a1, a2), (b0, b1,

b2), and (c0, c1, c2), one group of bits for each ENRZ

sub-system. Each of these vectors corresponds to the bitrepresentation of an integer modulo 7. This means that none

of these vectors consists of three 1's. The history units 320

each contain 3 bits corresponding to the bit sequences

transmitted in the previous unit interval, and called respectively h0, h1, and h2.

The pre-coding units 305 used in this example operate differently than the general pre-coding units described in FIG. 6, as the particular input characteristics permit simplification. Here, each pre-coding unit computes the XOR of the complement of the inputs 210 from the Global Encoder 205, with its corresponding history bits. Since none of the vectors 210 consists entirely of 1's, the complement of none of these vectors consists entirely of 0's, and hence the operation of the pre-coding unit ensures that the result of the operation is always different from the bits in the corresponding history units 320. Each of the pre-coding units forwards the computed bits to the corresponding ENRZ encoders 105, and simultaneously replaces the history bits with these bits.

Each communication sub-system in this embodiment transmits 3 bits on its corresponding 4-wire interface. The number of wires is therefore 12. Each sub-system uses 3 multi-input comparators (also known as generalized comparators, as described in [Holden I]) to recover its bits. The output of these comparators can be used to do a clock recovery on every one of the sub-systems, according to the teachings above. There are therefore a total of 9 comparators.

FIG. 10 is an exemplary embodiment of the receiver portion of the decoder for this communication system. In operation, the ENRZ decoders 125 forward a group 240 of three bits each to the post-decoder units 405. These units XOR the incoming bits with the 3 bits in their history units 420, complement the result, and forward it to the Global Decoder 260. Simultaneously, they replace their three history bits with the forwarded bits.

The operation of the Global Decoder **260** in this embodiment may be as described in FIG. **8**.

The ISI ratio of this coding system, as defined in [Hor(Eqn. 3) 65 mati] is 1, which is the lowest ISI ratio possible. This means

that this coding system has a low susceptibility to ISI noise.

ired to This communication system uses 12 signal wires, and 9

comparators. To enable operation at high data rates, the wires have to be routed in 3 low-skew groups of 4 wires each.

### Example 2: S34

S3 is a vector signaling code on three wires consisting of the 6 permutations of the vector (+1, 0, -1). In this case, we may choose k=4, corresponding to four communication sub-systems in FIG. 2, and M(1)=M(2)=M(3)=M(4)=6, satisfying the inequality of (Eqn. 3). The resulting embodiment is hereinafter called S34, referring to its four sub-systems, each utilizing S3 vector signaling code. This coding scheme is similar to the one reported in [Wiley], though the details of the encoding and decoding are different.

An embodiment of the encoder is detailed in FIG. 11. The input to the Global Encoder are the 9 bits x0, x1, ..., x8 corresponding to an integer between 0 and 256 inclusive. This means that x0=x1=...=x7=0 if x8=1. In this  $_{20}$ communication system there is no Global Encoder unit. Instead, the incoming bits are subdivided into three groups (x0, x1), (x2, x3), (x4, x5) of two bits, and (x6, x7, x8) of three bits. Because of the restriction of the input bits, the fourth group corresponds to an integer between 0 and 4, 25 routed in 4 low-skew groups of 3 wires each. inclusive.

The history units 320 each contain 3 bits corresponding to the bit sequences transmitted in the previous unit interval, and can be viewed as integers modulo 6, and called h0, h1, h2, and h3, respectively.

The pre-coding units 305 operate as described in FIG. 6. Each of the pre-coding units forwards the computed bits to the corresponding S3 encoders 105, and simultaneously replaces the history bits with these bits.