(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5144903号

(P5144903)

(45) 発行日 平成25年2月13日(2013.2.13)

(24) 登録日 平成24年11月30日(2012.11.30)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 617U

H01L 21/336 (2006.01)

H01L 29/78 616A

H01L 29/78 619A

請求項の数 4 (全 21 頁)

(21) 出願番号 特願2006-174684 (P2006-174684)

(22) 出願日 平成18年6月26日 (2006.6.26)

(65) 公開番号 特開2007-13145 (P2007-13145A)

(43) 公開日 平成19年1月18日 (2007.1.18)

審査請求日 平成21年6月18日 (2009.6.18)

(31) 優先権主張番号 10-2005-0058437

(32) 優先日 平成17年6月30日 (2005.6.30)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2005-0058444

(32) 優先日 平成17年6月30日 (2005.6.30)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 柳春基

大韓民国 京畿道 華城市 泰安邑 餅店

里 グボンマウル ウーナム ファースト

ビル アパート 105棟1205号

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に半導体層を形成する段階と、

前記半導体層上に第1のゲート絶縁膜、第2のゲート絶縁膜、及び金属膜を順次に形成する段階と、

前記金属膜上に形成された感光膜パターンをエッチングマスクとして前記金属膜をパターニングしてゲート電極を形成する段階と、

前記感光膜パターンをエッチングマスクとして前記第2のゲート絶縁膜をパターニングして前記ゲート電極よりも幅の広い第2のゲート絶縁膜パターンを形成する段階と、

前記感光膜パターンを除去した後、前記ゲート電極と前記ゲート電極よりも幅の広い第2のゲート絶縁膜パターンをイオン注入マスクとして使用して一回の不純物イオン注入工程にて、前記半導体層の前記ゲート電極の下部に対応する領域にはチャネル領域を、前記パターニングされた第2のゲート絶縁膜のうち前記ゲート電極によって被覆されていない部分の下部に対応する前記半導体層の領域には低濃度ドーピング領域を、前記パターニングされた第2のゲート絶縁膜に覆われていない下部に対応する前記半導体層の領域には、ソース領域及びドレーン領域を形成する段階と、

前記ゲート電極、前記第1のゲート絶縁膜、及び前記第2のゲート絶縁膜上に層間絶縁膜を形成する段階と、

第1のコンタクトホールを通じて前記ソース領域に電気的に連結されたソース電極を形成する段階と、

10

第2のコンタクトホールを通じて前記ドレーン領域に電気的に連結されたドレーン電極を形成する段階とを有し、

前記一回の不純物イオン注入にて、前記チャネル領域、前記低濃度ドーピング領域、前記ソース領域及びドレーン領域を形成する段階は、前記不純物イオンである高濃度n型不純物イオンの注入を相対的に低エネルギーで行うことを特徴とする薄膜トランジスタ基板の製造方法。

**【請求項2】**

前記パターニングされた第2のゲート絶縁膜は、前記ゲート電極から遠くなるほどその厚さが縮小されるように形成されることを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

10

**【請求項3】**

前記第2のゲート絶縁膜がパターニングされた後、前記第1のゲート絶縁膜の両側壁を前記パターニングされた第2のゲート絶縁膜の両側壁に実質的に整列する段階をさらに含むことを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

**【請求項4】**

前記第1のゲート絶縁膜は酸化珪素を含み、前記第2のゲート絶縁膜は窒化珪素を含むことを特徴とする請求項1に記載の薄膜トランジスタ基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

20

本発明は、薄膜トランジスタ基板の製造方法に係り、より詳しくは、性能低下がなく、工程効率が良い薄膜トランジスタ基板の製造方法に関するものである。

**【背景技術】**

**【0002】**

最近、ノートパソコンや携帯機器などの表示装置として用いられる液晶表示装置において、その駆動方式は、単純マトリックス方式からアクティブマトリックス方式に移行し、特にガラス基板上に多くの薄膜トランジスタ(Thin Film Transistor; TFT)を形成した薄膜トランジスタアクティブマトリックス駆動方式が主流を構成している。

**【0003】**

30

薄膜トランジスタは、ゲート線の一部であるゲート電極、チャネルを形成する半導体層、データ線の一部であるソース電極、半導体層を挟んでソース電極と対向するドレーン電極などからなる。

薄膜トランジスタは、ゲート線を通じて伝達される走査信号に応じて、データ線を通じて伝達される画像信号を画素電極に伝達又は遮断するスイッチング素子である。

**【0004】**

この時、半導体層は非晶質珪素又は多結晶珪素からなり、半導体層とゲート電極との相対的な位置によって、薄膜トランジスタは、トップゲート方式とボトムゲート方式に分けることができる。

多結晶珪素薄膜トランジスタの場合、ゲート電極が半導体層の上部に設けられるトップゲート方式が主に用いられる。

40

**【0005】**

多結晶珪素薄膜トランジスタの駆動速度は、非晶質珪素薄膜トランジスタよりはるかに速いので、画素の薄膜トランジスタと共にこれを動作させるための駆動回路を同時に形成できるという長所がある反面、パンチスルーなどの問題が発生する。

そこで半導体層のチャネル領域とソース領域及びドレーン領域の間に低濃度ドーピング領域を形成することが好ましい。

**【0006】**

従来技術による低濃度ドーピング領域の形成方法は、先ず半導体層上にゲート電極を二重の導電膜としてパターニング形成し、一つの導電膜は低濃度ドーピング領域を限定する

50

マスクとして使用し、他の導電膜は低濃度ドーピング領域を形成した後、ソース領域とドレーン領域とを形成する限定するマスクとして使用する。

しかしながら、一回のフォトエッチング工程において、二つの導電膜を異なるパターンに形成しなければならないなど工程が複雑であり、低濃度ドーピング領域の幅を精度よく限定し難い。

また、それにより工程時間が長くなり製造収率が低下する。

【特許文献1】特開第2001-274413号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

10

本発明の他の技術的課題は、性能低下がなく、工程効率が良い薄膜トランジスタ基板の製造方法を提供するところにある。

【課題を解決するための手段】

【0012】

20

前述した他の技術的課題を達成するための本発明による薄膜トランジスタ基板の製造方法は、基板上に半導体層を形成する段階と、前記半導体層上に第1のゲート絶縁膜、第2のゲート絶縁膜、及び金属膜を順次に形成する段階と、前記金属膜上に形成された感光膜パターンをエッチングマスクとして前記金属膜をパターニングしてゲート電極を形成する段階と、前記感光膜パターンをエッチングマスクとして前記第2のゲート絶縁膜をパターニングして前記ゲート電極よりも幅の広い第2のゲート絶縁膜パターンを形成する段階と、前記感光膜パターンを除去した後、前記ゲート電極と前記ゲート電極よりも幅の広い第2のゲート絶縁膜パターンをイオン注入マスクとして使用して一回の不純物イオン注入工程にて、前記半導体層の前記ゲート電極の下部に対応する領域にはチャネル領域を、前記パターニングされた第2のゲート絶縁膜のうち前記ゲート電極によって被覆されていない部分の下部に対応する前記半導体層の領域には低濃度ドーピング領域を、前記パターニングされた第2のゲート絶縁膜に覆われていない下部に対応する前記半導体層の領域には、ソース領域及びドレーン領域を形成する段階と、前記ゲート電極、前記第1のゲート絶縁膜、及び前記第2のゲート絶縁膜上に層間絶縁膜を形成する段階と、第1のコンタクトホールを通じて前記ソース領域に電気的に連結されたソース電極を形成する段階と、第2のコンタクトホールを通じて前記ドレーン領域に電気的に連結されたドレーン電極を形成する段階とを有し、前記一回の不純物イオン注入にて、前記チャネル領域、前記低濃度ドーピング領域、前記ソース領域及びドレーン領域を形成する段階は、前記不純物イオンである高濃度n型不純物イオンの注入を相対的に低エネルギーで行うことを特徴とする。

30

【0014】

その他実施形態の具体的な事項は、詳細な説明及び図面に含まれている。

【発明の効果】

【0015】

40

本発明によれば、一つの感光膜パターンによってゲート電極及び二重のゲート絶縁パターンをパターニングし、一回の不純物イオン注入工程によってソース領域及びドレーン領域と低濃度ドーピング領域を同時に形成することによって、製造工程を単純化して工程効率を高めながらも、漏洩電流が抑制されて性能低下がない薄膜トランジスタの製造方法を提供できる。

【発明を実施するための最良の形態】

【0016】

本発明の利点及び特徴、そしてそれらを達成する方法は添付する図面と共に詳細に後述している実施形態を参照すれば明確になる。

しかしながら、本発明は、以下で開示される実施形態に限定されるものではなく、相異なる多様な形態で具現されるものである。

50

即ち、本実施形態は単に、本発明の開示が完全となり、当業者に発明の範疇を完全に知らせるために提供されるものである。

従って、本発明の権利範囲は、本実施形態ではなく特許請求の範囲の記載に基づいて決められなければならない。

なお、明細書全体にかけて同一参照符号は同一構成要素を示すものとする。

【実施例 1】

【0017】

以下、添付した図1～図3を参照して本発明の第1の実施形態による薄膜トランジスタ基板を詳細に説明する。

【0018】

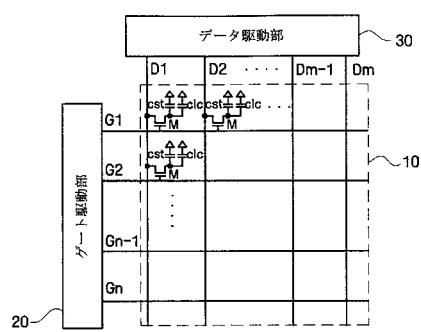

図1を参照して、本発明の第1の実施形態による薄膜トランジスタ基板について説明する。

図1は、本発明の第1の実施形態による薄膜トランジスタ基板の概略構成図である。

薄膜トランジスタ基板は、図1に示されているように、画素部10と、ゲート駆動部20及びデータ駆動部30と、を含む。

【0019】

画素部10は、多数のゲート線(G1～Gn)と多数のデータ線(D1～Dm)に連結されている多数の画素を含み、各画素は多数のゲート線(G1～Gn)と多数のデータ線(D1～Dm)に連結されたスイッチング素子(M)とこれに連結された液晶キャパシタ(C1c)及びストレージキャパシタ(Cst)を含む。

【0020】

行方向に形成されている多数のゲート線(G1～Gn)は、スイッチング素子(M)に走査信号を伝達し、列方向に形成されている多数のデータ線(D1～Dm)は、スイッチング素子(M)に画像信号に該当される階調電圧を伝達する。

そして、スイッチング素子(M)は三端子素子として、制御端子はゲート線(G1～Gn)に連結されており、入力端子はデータ線(D1～Dm)に連結されており、出力端子は液晶キャパシタ(C1c)及びストレージキャパシタ(Cst)の一つの端子に連結されている。

液晶キャパシタ(C1c)は、スイッチング素子(M)の出力端子と共通電極(図示せず)との間に連結され、ストレージキャパシタ(Cst)はスイッチング素子(M)の出力端子と共通電極との間に連結(独立配線方式)されるか、或いはスイッチング素子(M)の出力端子と真上の(直近に隣接する)ゲート線(G1～Gn)との間に連結(前端(前段)ゲート方式)できる。

【0021】

ゲート駆動部20は、多数のゲート線(G1～Gn)に連結されており、スイッチング素子(M)を活性化させる走査信号を多数のゲート線(G1～Gn)に提供し、データ駆動部30は多数のデータ線(D1～Dm)に連結されている。

【0022】

ここで、スイッチング素子(M)は、MOSトランジスタが用いられ、このようなMOSトランジスタは多結晶珪素をチャネル領域とする薄膜トランジスタに実現できる。

そして、ゲート駆動部20やデータ駆動部30もMOSトランジスタから構成され、このようなMOSトランジスタは多結晶珪素をチャネル領域とする薄膜トランジスタで実現できる。

【0023】

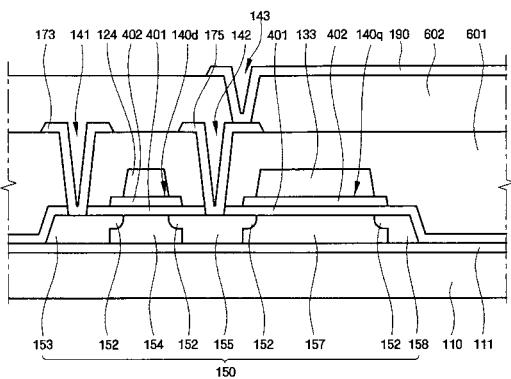

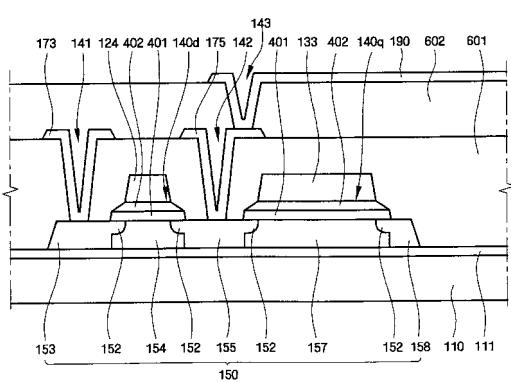

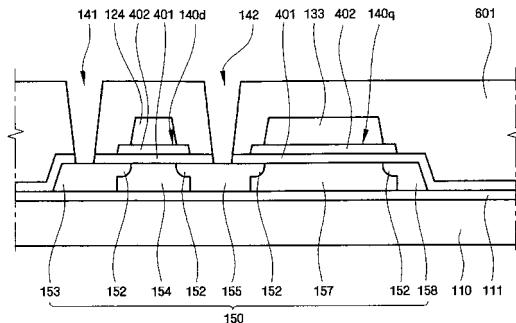

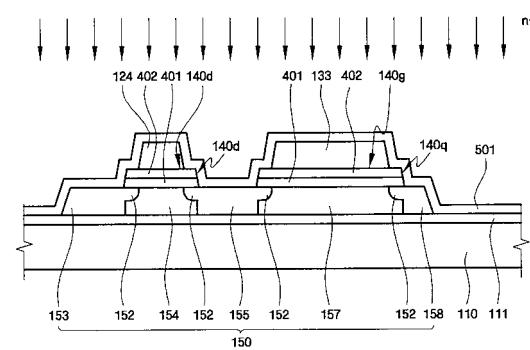

図2及び図3を参照して、多結晶珪素をチャネル領域とする薄膜トランジスタ基板について説明する。

図2は、本発明の第1の実施形態による薄膜トランジスタ基板の画素部の構造を示したレイアウト図であり、図3は図2の薄膜トランジスタ基板をI—I—I—I—I’線に沿って切って示した断面図である。

【0024】

10

20

30

40

50

図2及び図3に示すように、透明な絶縁基板110上に酸化珪素又は窒化珪素からなる遮断層111が形成されており、遮断層111上には、例えばn型不純物イオンが高濃度に注入されているソース領域及びドレーン領域153、155及びこれらの間に設けられ、不純物イオンが注入されないチャネル領域154が含まれた薄膜トランジスタの多結晶珪素からなる半導体層150が形成されている。

そして、ソース領域153とチャネル領域154の間、ドレーン領域155とチャネル領域154との間には、例えばn型不純物イオンが低濃度に注入されている低濃度ドーピング領域152がそれぞれ形成されている。

ここで、遮断層111は、基板110から半導体層150に不純物などが拡散することを防止するためのものであり、省略する場合もある。

10

#### 【0025】

多結晶珪素からなる半導体層150を含む基板110上には、ゲート絶縁膜パターン140d、140qが形成されている。ゲート絶縁膜パターン140d、140qは各々、酸化珪素からなる第1のゲート絶縁膜401と窒化珪素からなる第2のゲート絶縁膜402を含んでいる。

多結晶珪素からなる半導体層を含む薄膜トランジスタのスレッショルド電圧(Vth)を減少するためにはゲート絶縁膜パターンの厚さを薄くすることが必要である。

従来、酸化珪素膜の単一膜によりゲート絶縁膜パターンを形成する場合、酸化珪素膜の誘電定数は3.9程度に過ぎないので、Vthの減少に限界があり、さらにVthを減少するためにゲート絶縁膜パターンの厚さを縮小すると降伏電圧が減少するので、静電気による不良の増加の恐れがあった。

20

これに対して本発明の一実施形態による薄膜トランジスタでは、ゲート絶縁パターンとして二重膜構造、すなわち第1のゲート絶縁膜401として酸化珪素膜を、第2のゲート絶縁膜402として酸化珪素膜の誘電定数の約2倍値を有する窒化珪素膜を、各々使用することによってスレッショルド電圧(Vth)の減少及び薄膜トランジスタの性能向上が可能である。

#### 【0026】

第1のゲート絶縁膜401は、多結晶珪素からなる半導体層150が形成されている透明絶縁基板110全面に第1の絶縁膜の形態で形成される。

この時、第1のゲート絶縁膜401には、半導体層150のソース領域153及びドレーン領域155と、後述するソース電極及びドレーン電極をそれぞれ電気的に連結するための通路としての第1及び第2のコンタクトホール141、142が形成されている。

30

また、第2のゲート絶縁膜402は、両側壁が各々、半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部に実質的に整列して形成される。

このようにして、各々、第1、第2のゲート絶縁膜401、402からなるゲート絶縁膜パターン140d、140qが形成される。

第2のゲート絶縁膜402は、多結晶珪素からなる半導体層150とゲート電極124及び維持電極133をそれぞれ絶縁する役割を果たす。

また第2のゲート絶縁膜402は、後述するソース領域及びドレーン領域を形成するための不純物イオンの注入の際のイオン注入マスクの役割も果たす。

40

従って、第2のゲート絶縁膜402の両側壁を境界として半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155が分けられるので、工程上必然的に第2のゲート絶縁膜402の両側壁が半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部に実質的に整列して形成される。

#### 【0027】

ゲート絶縁膜パターン140d上には、一方向(図2では横方向)に長いゲート線121が形成されており、ゲート線121の一部が延長されて多結晶珪素からなる半導体層150のチャネル領域154と重畳されており、重畳されたゲート線121の一部分は、薄

50

膜トランジスタ基板のゲート電極 124 として使用される。

また、ゲート絶縁膜パターン 140q 上には、画素の維持容量を増加させるための維持電極線 131 が、ゲート線 121 と同一の層において同一の材質から、ゲート線 121 と概ね平行に形成されている。

多結晶珪素からなる半導体層 150 と重畳する維持電極線 131 の一部分は、維持電極 133 になり、維持電極 133 と重畳する多結晶珪素からなる半導体層 150 は、維持電極領域 157 になり、維持電極領域 157 の両側にも低濃度ドーピング領域 152 がそれぞれ形成されており、維持電極領域 157 の一側には高濃度ドーピング領域 158 が設けられる。

ゲート線 121 の一側端部分（図示せず）は、外部回路と連結するためにゲート線 121（の図示した部分の）幅より広く形成され、ゲート駆動部 20 の出力端に直接連結され、図 1 のゲート線 G1 ~ Gn となる。

#### 【0028】

ゲート線 121、維持電極線 131、ゲート電極 124、維持電極 133 が形成されているゲート絶縁膜パターン 140d、140q 及び半導体層 150 上には、第 1 の層間絶縁膜 601 が形成されている。

第 1 の層間絶縁膜 601 は、ソース領域及びドレーン領域 153、155 をそれぞれ露出する第 1 及び第 2 のコンタクトホール 141、142 を含んでいる。

#### 【0029】

第 1 の層間絶縁膜 601 上には、ゲート線 121 と交差して画素領域を限定するデータ線 171 が形成されている。

データ線 171 の一部分又は分枝形部分（本実施例（図 2）は、分枝形がない場合である）は、第 1 のコンタクトホール 141 を通じてソース領域 153 と連結されており、ソース領域 153 と連結されている部分は、薄膜トランジスタ基板のソース電極 173 として使用される。

データ線 171 の一側端部分（図示せず）は、外部回路と連結するためにデータ線 171（の図示した部分の）幅より広く形成され、データ駆動部 30 の出力端に直接連結され、図 1 のデータ線 D1 ~ Dm となる。

#### 【0030】

そして、データ線 171 と同一の層には、同一の材質からなり、第 2 のコンタクトホール 142 を通じてドレーン領域 155 と連結されているドレーン電極 175 が、ソース電極 173 と一定距離離れて形成されている。

#### 【0031】

ソース電極 173、ドレーン電極 175 及びデータ線 171 を含む第 1 の層間絶縁膜 601 上に第 2 の層間絶縁膜 602 が形成されている。

第 2 の層間絶縁膜 602 は、ドレーン電極 175 を露出する第 3 のコンタクトホール 143 を有する。

第 2 の層間絶縁膜 602 上には、第 3 のコンタクトホール 143 を通じてドレーン電極 175 と連結されている画素電極 190 がそれぞれの画素領域に形成されている。

#### 【実施例 2】

#### 【0032】

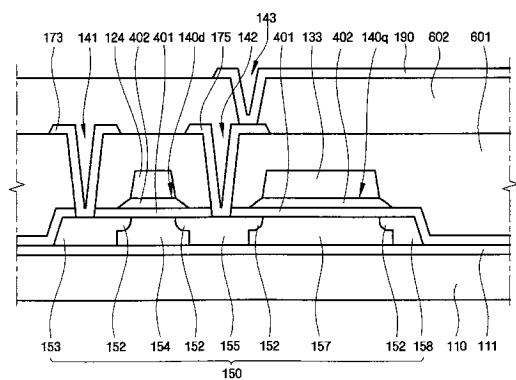

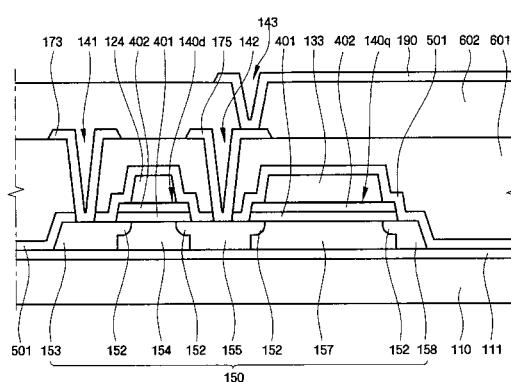

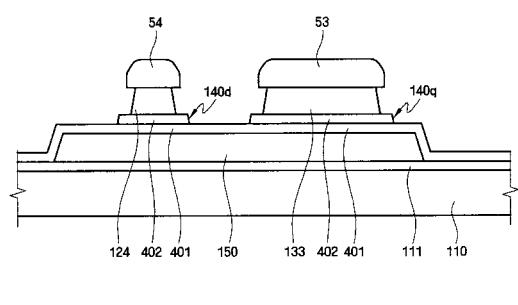

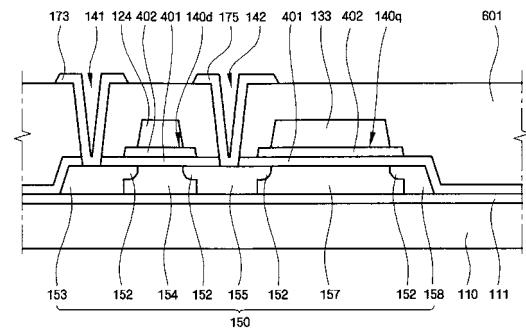

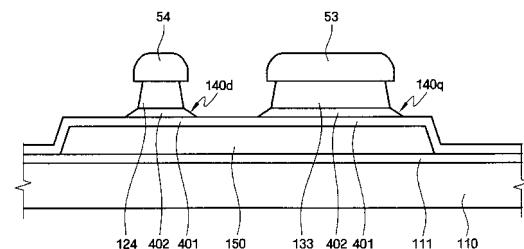

次に、図 4 を参照して本発明の第 2 の実施形態による薄膜トランジスタ基板について説明する。

図 4 は、本発明の第 2 の実施形態による薄膜トランジスタ基板の断面図である。

本発明の第 2 の実施形態による薄膜トランジスタ基板は、第 2 のゲート絶縁膜 402 の両側壁の上部がゲート電極 124 の両側壁に実質的に整列され、両側壁の下部が各々、半導体層 150 の低濃度ドーピング領域 152 とソース領域及びドレーン領域 153、155 の境界部、低濃度ドーピング領域 152 と高濃度ドーピング領域 158 の境界部に実質的に整列されていることを除外すると、本発明の第 1 の実施形態による薄膜トランジスタ基板と同一であるので、重複する部分については便宜上説明を省略する。

10

20

30

40

50

前述したように、第2のゲート絶縁膜402の両側壁の上部124は、ゲート電極124の両側壁に実質的に整列され、両側壁の下部は各々、低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部、低濃度ドーピング領域152と高濃度ドーピング領域158の境界部に実質的に整列されることによって、第2のゲート絶縁膜402の両側壁の上部と下部とを連結する面は傾斜を成す。

このような傾斜面を含む傾斜部の下部に対応する半導体層150領域である低濃度ドーピング領域152の不純物イオンの濃度は、低濃度ドーピング領域152とチャネル領域154の境界部から、低濃度ドーピング領域152とソース領域、ドレーン領域153、155の境界部に向かって、及び、低濃度ドーピング領域152とチャネル領域（維持電極領域157）の境界部から、低濃度ドーピング領域152とドレーン領域155、高濃度ドーピング領域158の境界部に向かって、各々、漸進的に増加する。

10

これについては、後述の薄膜トランジスタ基板の製造方法で詳しく説明する。

【実施例3】

【0033】

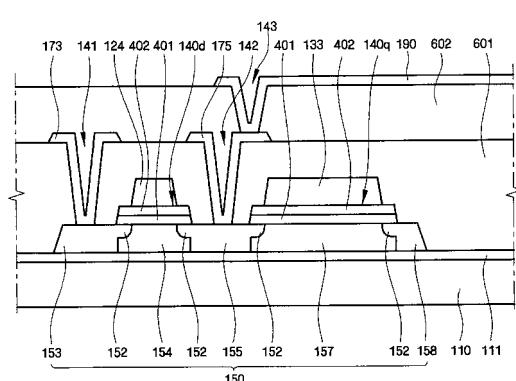

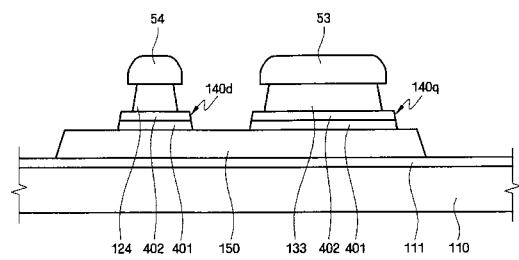

次に、図5を参照して本発明の第3の実施形態による薄膜トランジスタ基板について説明する。

図5は、本発明の第3の実施形態による薄膜トランジスタ基板の断面図である。

本発明の第3の実施形態による薄膜トランジスタ基板は、第2のゲート絶縁膜402の両側壁が各々、半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部、低濃度ドーピング領域152と高濃度ドーピング領域158の境界部に実質的に整列され、第1のゲート絶縁膜401の両側壁が第2のゲート絶縁膜402の両側壁に実質的に整列されていることを除外すると、本発明の第1の実施形態による薄膜トランジスタ基板と同一であるので、重複する部分については便宜上説明を省略する。

20

【実施例4】

【0034】

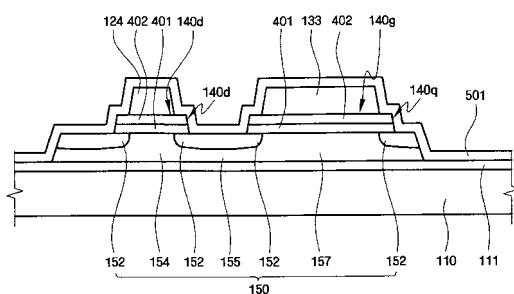

次に、図6を参照して本発明の第4の実施形態による薄膜トランジスタ基板について説明する。

図6は、本発明の第4の実施形態による薄膜トランジスタ基板を含む薄膜トランジスタ基板の断面図である。

30

本発明の第4の実施形態による薄膜トランジスタ基板は、第2のゲート絶縁膜402の両側壁の上部がゲート電極124の両側壁に実質的に整列され、両側壁の下部が各々、半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部、低濃度ドーピング領域152と高濃度ドーピング領域158の境界部に実質的に整列され、第1のゲート絶縁膜401の両側壁が第2のゲート絶縁膜402の両側壁の下部に実質的に整列されていることを除外すると、本発明の第1の実施形態による薄膜トランジスタ基板と同一であるので、重複する部分については便宜上説明を省略する。

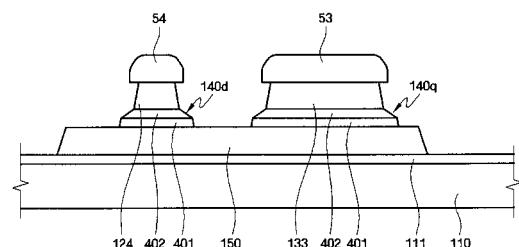

【実施例5】

【0035】

次に、図7を参照して本発明の第5の実施形態による薄膜トランジスタ基板について説明する。

40

図7は、本発明の第5の実施形態による薄膜トランジスタ基板の断面図である。

本発明の第5の実施形態による薄膜トランジスタ基板は、第2のゲート絶縁膜402の両側壁が各々、半導体層150の低濃度ドーピング領域152とソース領域及びドレーン領域153、155の境界部、低濃度ドーピング領域152と高濃度ドーピング領域158の境界部に実質的に整列され、第1のゲート絶縁膜401の両側壁が第2のゲート絶縁膜402の両側壁に実質的に整列され、さらに、このような構造上にキャッピング膜501がさらに形成されていることを除外すると、本発明の第1の実施形態による薄膜トランジスタと同一であるので、重複される部分については便宜上説明を省略する。

キャッピング膜501は、第1の層間絶縁膜601の第1及び第2のコンタクトホール

50

141、142が形成されている位置と実質的に同一な位置に形成されているコンタクトホールを含む。

キャッピング膜の役割についても、後述の薄膜トランジスタ基板の製造方法で詳しく説明する。

【0036】

以下には、前述した本発明の各実施形態による薄膜トランジスタ基板について、それらの製造方法を添付した図面を参照して詳細に説明する。

【実施例6】

【0037】

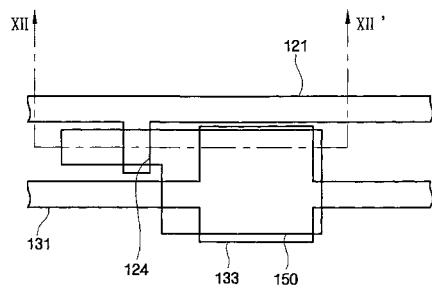

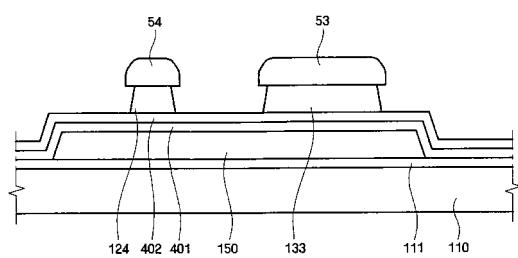

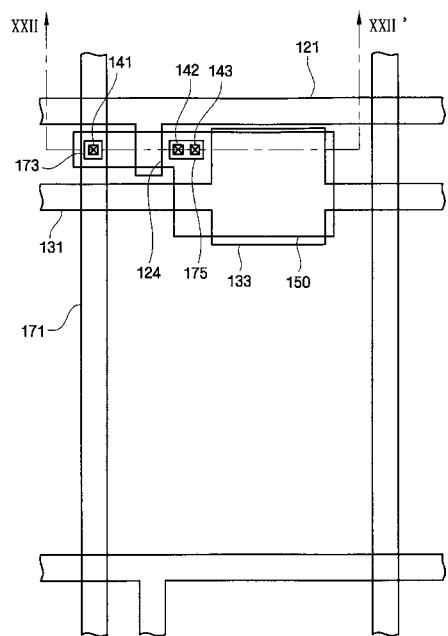

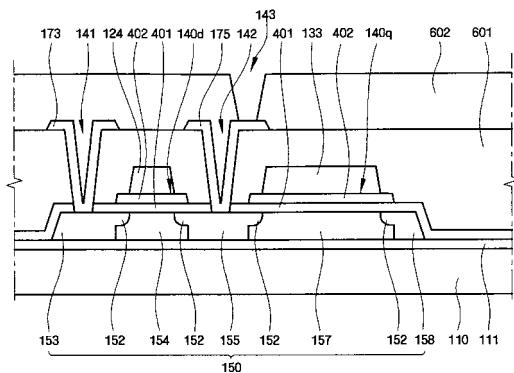

図8、図11、図17、図19及び図21は、図2及び図3に示した本発明の第1の実施形態に係る薄膜トランジスタ基板の画素部を製造する方法の、中間段階でのレイアウト図を工程順序通り羅列したものである。 10

一方、図9及び図10は図8の薄膜トランジスタ基板をIX-IX'線に沿って切って示した断面図であり、図12～図16は、図11の薄膜トランジスタ基板をXII-XII'線に沿って切って示した断面図であり、図18は図17の薄膜トランジスタ基板をXVIII-XVIII'線に沿って切って示した断面図であり、図20は図19の薄膜トランジスタ基板をXX-XX'線に沿って切って示した断面図であり、図22は図21の薄膜トランジスタ基板をXXII-XXII'線に沿って切って示した断面図である。

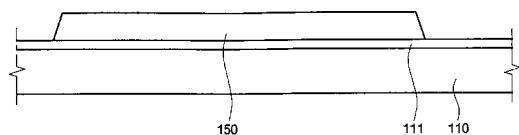

【0038】

最初に、図8及び図9に示すように、透明な絶縁基板110上に遮断層111を形成する。 20

この時使用される透明絶縁基板110としてはガラス、石英又はサファイアなどを使用し、遮断層111は酸化珪素(SiO<sub>2</sub>)又は窒化珪素(SiNx)を蒸着して形成する。このような遮断層111は、基板110から半導体層150に不純物などが拡散することを防止するためのものであり、省略する場合もある。

そして遮断層111上に非晶質珪素を蒸着して非晶質珪素膜を形成する。

【0039】

次に、非晶質珪素膜をレーザー熱処理、炉熱処理又は固相結晶化工程によって非晶質珪素を結晶化した後、写真エッチング方法にパターニングして多結晶珪素からなった半導体層150を形成する。 30

【0040】

次に、図10に示すように、多結晶珪素からなる半導体層150が形成されている基板110上部に酸化珪素及び窒化珪素の絶縁物質を順次に蒸着して第1のゲート絶縁膜401と第2のゲート絶縁膜402とを形成する。

そして第2のゲート絶縁膜402上にアルミニウム、クロム、モリブデン又はこれらの合金からなる単一膜又は多層膜を蒸着してゲート用金属膜120を形成する。

この時、第1のゲート絶縁膜401と第2のゲート絶縁膜402及びゲート用金属膜120の厚さは特に限定されておらず、素子特性によって多様な厚さを有することができる。

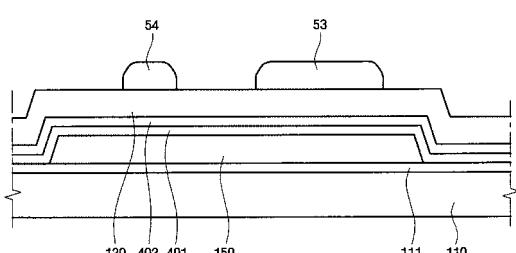

次に、ゲート用金属膜120上に感光膜を形成し、フォトマスクを用いてフォトリソグラフィにより、感光膜を選択的に露光及び現像して感光膜パターン53、54を形成する。

このような感光膜パターン53、54は、ゲート用金属膜120をゲート電極にパターニングするためのエッチングマスクとして使用されるだけではなく、後述するように、第2のゲート絶縁膜又は第1のゲート絶縁膜を各々パターニングするためのエッチングマスクとして使用できる。

感光膜パターン53、54は、例えば感光膜を所定の形状にパターニングした後、加熱収縮してその断面が梯形になるようにしてもよく、また、溶融形感光膜を使用して加過熱してその断面が半球形とするなど目的に沿って多様な形状を有するように形成できる。

【0041】

10

20

30

40

50

ゲート電極 124 を形成するためのゲート用金属膜 120 は、物理的性質が異なる二つの膜を含むことができる。

一つの膜は、走査信号の遅延や電圧降下を減らすことができるように低い比抵抗の金属、アルミニウム (A1) やアルミニウム合金、例えばアルミニウム - ネオジム (A1Nd) 合金などのアルミニウム系列の金属にすることができるが、これに限定されない。

これとは違って、他の膜は異なる物質、酸化インジウム亜鉛 (Indium Zinc Oxide; IZO) 又は酸化インジウム錫 (Indium Tin Oxide;ITO) との物理的、化学的、電気的接触特性に優れた物質、モリブデン (Mo)、モリブデン合金、例えばモリブデン - タングステン (MoW) 合金、クロム (Cr) などにすることができるが、これに限定されない。

例えば、アルミニウム - ネオジム (A1Nd) の金属膜は、アルミニウムについて側面傾斜を形成できるエッティングができるアルミニウムエッティング液である  $\text{CH}_3\text{COOH}$  (8% ~ 15%) /  $\text{HNO}_3$  (5% ~ 8%) /  $\text{H}_3\text{PO}_4$  (50% ~ 60%) /  $\text{H}_2\text{O}$  (残り) を使用した湿式エッティングにより処理できる。

このようなエッティング液は、モリブデン - タングステン (MoW) の導電膜についても同一なエッティング条件で側面傾斜を形成できるエッティングができるので、二つの導電膜を連続して側面傾斜を形成しながらエッティングできる。

#### 【0042】

次に、図 11 及び図 12 に示すように、感光膜パターン 53、54 をマスクとしてゲート用金属膜 120 を、等方性エッティングによりアンダーカット構造になるようにパターンングして、ゲート電極 124 を有するゲート線 121 及び維持電極 133 を有する維持電極線 131 を形成する。

ゲート線 121 及び維持電極線 131 の切断面側壁は、以後に形成される上部層との密着性を増加させるために傾斜するように形成することが好ましい。

#### 【0043】

次に、図 13 に示すように、感光膜パターン 53、54 をエッティングマスクとして、図 12 の第 2 のゲート絶縁膜 402 を異方性エッティングによりパターンングして、ゲート電極 124 及び維持電極 133 の幅より各々少し広い幅を有する第 2 のゲート絶縁膜 402 を形成する。

この時、第 2 のゲート絶縁膜 402 は、多結晶珪素からなる半導体層 150 とゲート電極 124 及び維持電極 133 の間にそれぞれ設けられて、多結晶珪素からなる半導体層 150 とゲート電極 124 及び維持電極 133 をそれぞれ絶縁する役割を果たすと同時に、後述するように、ソース領域及びドレーン領域を形成するための不純物イオンを注入する場合のイオン注入マスクの役割も果たす。

#### 【0044】

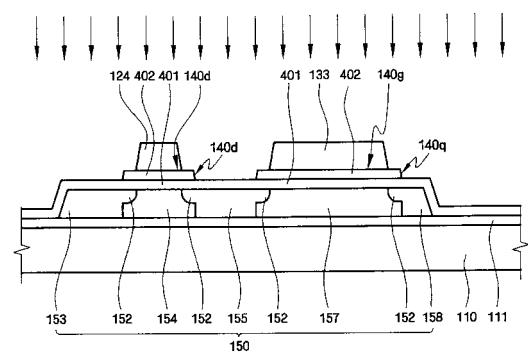

次に、半導体層 150 内に低濃度ドーピング領域、ソース領域及びドレーン領域を形成する。

これらは一回の不純物イオン注入によって形成してもよく、低濃度不純物イオン注入と高濃度不純物イオン注入とを順次に行って形成してもよい。

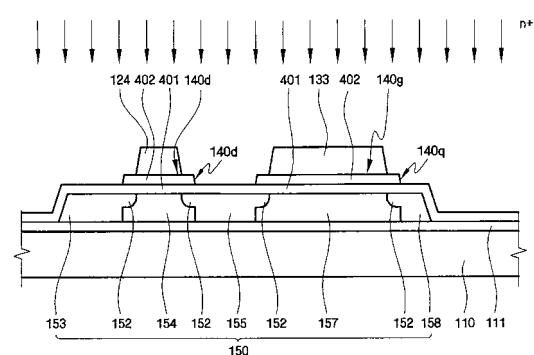

#### 【0045】

第 1 に、一回の不純物イオン注入によって低濃度ドーピング領域、ソース領域及びドレーン領域を形成する場合について説明する。

図 14 に示すように、感光膜パターン 53、54 を除去した後、ゲート電極 124、維持電極 133 及びゲート絶縁膜パターン 140d、140q をマスクとして例えば、プラズマイマージョン方法を使用して例えば、n 型不純物イオン注入を実施する。

ドーズ量は、例えば単位  $\text{cm}^2$  当たり  $1.0 \times 10^{15} \sim 5.0 \times 10^{15}$  粒子にすることができるが、これに限定されずゲート絶縁膜の厚さ、素子の特性などによってドーズ量を変えることができる。

これにより一回のイオン注入のみで、低濃度ドーピング領域 152、ソース領域及びドレーン領域 153、155 を含む薄膜トランジスタ構造を形成できる。

10

20

30

40

50

すなわち、第2のゲート絶縁膜402のうちゲート電極124又は維持電極133によって被覆されていない部分の下の半導体層150には、イオン注入が部分的に防止される結果、低濃度ドーピング領域152が形成される。

そして、第2のゲート絶縁膜402によって覆われない部分の半導体層150には、酸化珪素膜からなる第1のゲート絶縁膜401を突き抜き、投射されたイオンの大部分がされるので、ソース領域及びドレーン領域153、155と高濃度ドーピング領域158が形成される。

また、ゲート電極124及び維持電極133の下の半導体層150には不純物イオンが注入されないので、チャネル領域154と維持電極領域157が形成されて、それぞれソース領域153、ドレーン領域155及び高濃度ドーピング領域158を分離する。 10

前述したように一回の不純物イオン注入のみで、低濃度ドーピング領域152と、ソース領域及びドレーン領域153、155を含む薄膜トランジスタ構造を形成することは、高濃度n型不純物イオン注入が比較的低エネルギーの場合に可能である。

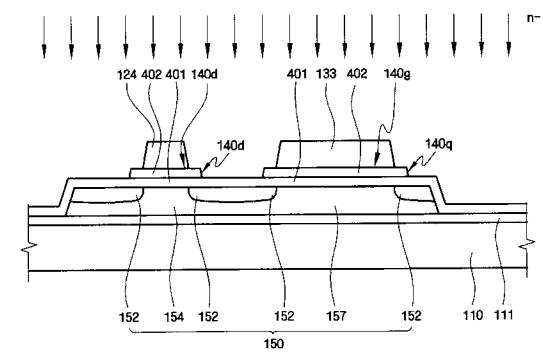

#### 【0046】

第2に、低濃度不純物イオン注入と高濃度不純物イオン注入によって、低濃度ドーピング領域と、ソース領域及びドレーン領域を別個に形成する場合について説明する。

図15に示すように、感光膜パターン53、54を除去した後、ゲート電極124、維持電極133及びゲート絶縁パターン140d、140qをマスクとして例えれば、n型不純物イオンをスキャニング設備又はイオンビーム設備を用いて半導体層150に低濃度(n-)に注入して低濃度ドーピング領域152及びチャネル領域154、157を形成する。 20

すなわち、ゲート電極124又は維持電極133によって覆われた部分の半導体層150には、イオンが注入されないので、それぞれチャネル領域154と維持電極領域157が形成され、第2のゲート絶縁膜402のうちゲート電極124及び維持電極133によって覆われていない部分の下の半導体層150には、第2、第1のゲート絶縁膜402、401を突き抜き、投射されたイオンが部分的に注入されて低濃度ドーピング領域152が形成される。

この時、ドーザ量は、例えば単位cm<sup>2</sup>当たり $5.0 \times 10^{12} \sim 1.0 \times 10^{13}$ 粒子にすることができるが、これに限定されずゲート絶縁膜の厚さ、素子の特性によってドーザ量を変えることができる。 30

#### 【0047】

続いて、図16に示すように、ゲート電極124、維持電極133及びゲート絶縁膜パターン140d、140qをマスクとして例えれば、n型不純物イオンをスキャニング設備又はイオンビーム設備を用いて半導体層150に高濃度(n+)に注入してソース領域及びドレーン領域153、155、高濃度ドーピング領域158を形成する。

すなわち、第2のゲート絶縁膜402によって覆われない部分の半導体層150には、酸化珪素膜からなる第1のゲート絶縁膜401を突き抜き、投射されたイオンの大部分が注入されるので、ソース領域及びドレーン領域153、155と高濃度ドーピング領域158が形成される。

この時、ドーザ量は、例えば単位cm<sup>2</sup>当たり $1.0 \times 10^{15} \sim 3.0 \times 10^{15}$ 粒子にすることができるが、これに限定されずゲート絶縁膜の厚さ、素子の特性によってドーザ量を変えることができる。 40

#### 【0048】

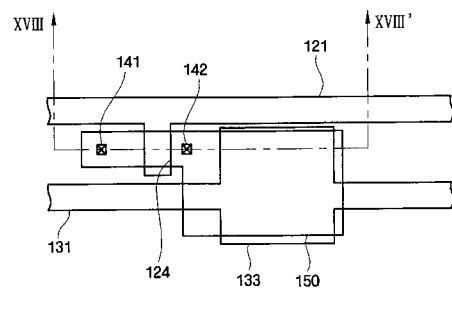

以上第1又は第2のいずれかの方法により半導体層150内に低濃度ドーピング領域、ソース領域及びドレーン領域を形成した後、図17及び図18に示すように、多結晶珪素からなる半導体層150を覆うように基板110の全面上部に絶縁物質を積層して第1の層間絶縁膜601を形成する。

次に第1の層間絶縁膜601を、マスクを用いたフォトエッチング工程によりパターニングして、ソース領域及びドレーン領域153、155を露出する第1、第2のコンタクトホール141、142を形成する。 50

## 【0049】

その次に、図19及び図20に示すように、第1の層間絶縁膜601の全面上部にデータ用金属膜を形成した後、マスクを用いたフォトエッチング工程によりパターニングして、データ線171、ドレーン電極175、及びソース電極173を形成する。

ソース電極173は、第1のコンタクトホール141を通じてソース領域153とそれ連結し、ドレーン電極175は第2のコンタクトホール142を通じてドレーン領域155とそれぞれ連結する。

## 【0050】

データ線171は、アルミニウム又はアルミニウム合金などのアルミニウム含有金属、又はモリブデン又はモリブデン合金の単一層、もしくはアルミニウム合金層とクロム(Cr)、モリブデン(Mo)合金層などからなる複数層、の導電物質を蒸着してデータ用金属膜を形成した後パターニングして形成する。10

この時、データ用金属膜もゲート用金属膜と同一の導電物質及び同一のエッチング方法によりパターニングし、データ線171及びドレーン電極175の断面は、上部層との密着性のために一定した傾斜を有するテーパー構造に形成することが好ましい。

## 【0051】

次に、図21及び図22に示すように、データ線171及びドレーン電極175が形成された第1の層間絶縁膜601上に、さらに、平坦化特性に優れ、感光性を有する有機物質を積層して第2の層間絶縁膜602を形成する。

そして第2の層間絶縁膜602を、マスクを用いたフォトエッチング工程によりパターニングして、ドレーン電極175を露出する第3のコンタクトホール143を形成する。20

## 【0052】

最後に、図2及び図3に示すように、第3のコンタクトホール143内部を含む第2の層間絶縁膜602上に透明な物質である酸化インジウム錫又は酸化インジウム亜鉛を全面蒸着した後、これをパターニングして画素電極190と多数の信号線を電気的に連結するための連結部材(図示せず)を形成する。

画素電極190は、第3のコンタクトホール143を通じてドレーン電極175と連結する。

コンタクト補助部材は、第1及び第2の層間絶縁膜601、602にかけて形成されている第4のコンタクトホール(図示せず)、第1及び第2の層間絶縁膜601、602とゲート絶縁膜140にかけて形成されている第5のコンタクトホール(図示せず)を通じてそれぞれデータ線171及びゲート線121に電気的に連結されている連結部と連結する。30

## 【0053】

以上説明したように、本実施例(実施例6)に係る薄膜トランジスタ基板の製造方法では、ゲート電極をパターニングするための感光膜パターンを用いて絶縁膜をパターニングしてゲート絶縁膜パターンを形成する。

さらに別途のフォトエッチング工程を追加せず、このゲート絶縁膜パターンを、低濃度ドーピング領域と、ソース及びドレーン領域を限定するためのイオン注入マスクとして用いて一回の高濃度イオン注入を通じて、低濃度ドーピング領域と、ソース及びドレーン領域を同時に形成する。40

これによって製造工程を単純にすることができ、製造コストを最小化できる。

## 【実施例7】

## 【0054】

次に本実施例では、本発明の第2の実施形態(図4)に係る薄膜トランジスタ基板の製造方法について説明する。

図23は、本発明の第7の実施形態による薄膜トランジスタ基板の製造方法の、中間段階における断面図である。

図23に示すように本発明の第2の実施形態に係る薄膜トランジスタ基板の製造方法では、ゲート電極124及び維持電極133のエッチングマスクとして使用した感光膜バタ50

ーン 5 4、5 3 により第 2 のゲート絶縁膜 4 0 2 をパターニングする。

その際、第 2 のゲート絶縁膜 4 0 2 の両側壁において、ゲート電極 1 2 4 又は維持電極 1 3 3 によって被覆された部分から外側に離隔するにつれて、第 2 のゲート絶縁膜 4 0 2 の厚さが縮小されるように形成することを除外すると、本発明の第 6 の実施形態による製造方法と同一である。

すなわち本実施形態では、ゲート電極 1 2 4 及び維持電極 1 3 3 を形成するためのエッチングマスクとして使用した感光膜パターン 5 4、5 3 を用いて第 2 のゲート絶縁膜 4 0 2 をパターニングする際に、ゲート電極 1 2 4 (又は維持電極 1 3 3 ) によって被覆されていない領域を例えば、エッチング気体として  $S F_6 + O_2$  を使用する異方性エッチング工程によってゲート電極 1 2 4 (又は維持電極 1 3 3 ) が形成された領域の外側に傾斜面を形成する。

#### 【 0 0 5 5 】

第 2 のゲート絶縁膜 4 0 2 は、前述したように低濃度ドーピング領域 1 5 2、ソース領域及びドレーン領域 1 5 3、1 5 5 と高濃度ドーピング領域 1 5 8 とを形成するためのイオン注入マスクの役割を果たす。

このような第 2 のゲート絶縁膜 4 0 2 の傾斜した両側壁に対応する半導体層 1 5 0 に注入される不純物イオン濃度は、傾斜部の厚さの差によって第 2 のゲート絶縁膜 4 0 2 の両側壁の外側に行くほど濃度が高くなり、このような不純物イオンの濃度変化は、傾斜部の形状によって決定される。

両側壁の傾斜による厚さの変化によって低濃度ドーピング領域 1 5 2 に注入される不純物イオンの濃度が漸進的に変化する。

本実施形態による製造方法によって製造される薄膜トランジスタ基板は、前述したように漸進的な濃度変化を有する低濃度ドーピング領域 1 5 2 を含むことによって、漏洩電流が抑制されて薄膜トランジスタの性能が低下しない。

#### 【 0 0 5 6 】

以上説明した第 7 の実施形態では、二重のゲート絶縁膜のうち一つの絶縁膜のみをエッチングして、ソース及びドレーン領域と、低濃度ドーピング領域を限定するイオン注入マスクとして使用したが、二重のゲート絶縁膜の双方をパターニングしてゲート絶縁膜パターンを形成することができるので、これについて説明する。

#### 【 実施例 8 】

#### 【 0 0 5 7 】

本実施形態では、本発明の第 3 の実施形態 (図 5) に係る薄膜トランジスタ基板の製造方法について説明する。

図 2 4 は、本発明の第 8 の実施形態による薄膜トランジスタ基板の製造方法の、中間段階における断面図である。

図 2 4 に示すように本発明の第 3 の実施形態に係る薄膜トランジスタ基板の製造方法では、ゲート電極 1 2 4 及び維持電極 1 3 3 のエッチングマスクとして使用した感光膜パターン 5 4、5 3 により第 2 のゲート絶縁膜 4 0 2 をパターニングする。

その際、ゲート電極 1 2 4 及び維持電極 1 3 3 の幅より各々少し広い幅を有する第 2 のゲート絶縁膜 4 0 2 を形成し、次に同一な感光膜パターン 5 4、5 3 をエッチングマスクとして第 1 の絶縁膜をパターニングして第 2 のゲート絶縁膜 4 0 2 の両側壁に第 1 のゲート絶縁膜 4 0 1 の両側壁が実質的に整列された第 1 のゲート絶縁膜 4 0 1 を形成することを除外すると、本発明の第 6 の実施形態による製造方法と同一である。

すなわち、本実施形態によって製造された薄膜トランジスタ基板は、第 1 のゲート絶縁膜 4 0 1 を第 2 のゲート絶縁膜 4 0 2 と同じく、チャネル領域 1 5 4 と低濃度ドーピング領域 1 5 2 上にのみ形成することによって、低濃度ドーピング領域 1 5 2 の不純物イオン濃度を目的の濃度に制御することがより容易になり、結局、漏洩電流を抑制して薄膜トランジスタの性能を向上できる。

#### 【 実施例 9 】

#### 【 0 0 5 8 】

10

20

30

40

50

次に、本発明の第4の実施形態(図6)に係る薄膜トランジスタ基板の製造方法について説明する。

図25は、本発明の第9の実施形態による薄膜トランジスタ基板の製造方法の、中間段階における断面図である。

図25に示すように本発明の第4の実施形態に係る薄膜トランジスタ基板の製造方法では、ゲート電極124及び維持電極133のエッチングマスクとして使用した感光膜パターン54、53により第2の絶縁膜をパターニングする。

その際、第2のゲート絶縁膜402の両側壁において、ゲート電極124又は維持電極133によって被覆された部分から外側に離隔するにつれて、第2のゲート絶縁膜402の厚さが縮小されるように形成し、同一の感光膜パターン54、53をエッチングマスクとして第1のゲート絶縁膜401をパターニングして、その両側壁を第2のゲート絶縁膜402の両側壁の下部に実質的に整列させることを除外すると、本発明の第6の実施形態による製造方法と同一である。

10

本実施形態による製造方法によって製造された薄膜トランジスタ基板では、第2のゲート絶縁膜402の両側壁が傾斜し、かつ第1のゲート絶縁膜401がチャネル領域154と低濃度ドーピング領域152上にのみ存在するように形成されるので、低濃度ドーピング領域152の不純物イオン濃度を目的の濃度に制御することがより容易になり、漏洩電流を抑制できて薄膜トランジスタの性能を向上できる。

#### 【実施例10】

#### 【0059】

20

次に、本発明の第5の実施形態(図7)に係る薄膜トランジスタ基板の製造方法について説明する。

図26及び図27は、本発明の第10の実施形態による薄膜トランジスタ基板の製造方法の、中間段階における断面図である。

最初に、本発明の第6の実施形態による製造方法と同一の方法により、ゲート電極124及び維持電極133を形成する(図12参照)。

続いて、図26に示すようにゲート電極124及び維持電極133のエッチングマスクとして使用した感光膜パターン(図12の54、53)により、第1及び第2の絶縁膜をパターニングして第1及び第2のゲート絶縁膜401、402をゲート電極124及び維持電極133の幅より少し広い幅に形成した後、ゲート電極124及び維持電極133をイオン注入マスクとして、例えば、スキャニング設備又はイオンビーム設備を用いて低濃度不純物イオンを注入して低濃度ドーピング領域152を形成する。

30

この時、ドーズ量は、例えば単位 $\text{cm}^2$ 当たり $5.0 \times 10^{12} \sim 1.0 \times 10^{13}$ 粒子にすることができるが、これに限定されずゲート絶縁膜パターンの厚さ、素子の特性によってドーズ量を変えることができる。

次に、このようにして得られた半導体層150を含む基板110の全体上にキャッピング膜501を形成する。

このようなキャッピング膜は例えば化学気相蒸着(Chemical Vapour Deposition; CVD)法によって形成できるが、これに限定されない。

キャッピング膜501を形成することによって、後述する高濃度不純物イオン注入時に、低濃度ドーピング領域152に高濃度不純物イオンが注入されることを十分に防止すると同時に、ソース領域及びドレーン領域153、155、158に目的とする濃度の不純物イオン注入が可能になる。

40

従って、ソース領域及びドレーン領域と電気的にそれぞれ連結されるソース電極及びドレーン電極とのコンタクト抵抗が増加することを抑制できる。

このようなキャッピング膜501は、例えば窒化珪素膜又は酸化珪素膜からなることができるが、これに限定されることではない。

また、キャッピング膜の厚さは素子の特性によって多様に変更できる。

#### 【0060】

次に、図27に示すように、キャッピング膜501が形成されている状態でゲート電極

50

124、維持電極 133 及びゲート絶縁膜パターン 140d、140q をマスクとして例えれば、スキャニング設備又はイオンビーム設備を用いて約 50 eV ~ 80 eV のエネルギーで高濃度不純物イオンを注入して、第 1 及び第 2 のゲート絶縁膜 401、402 によって覆われない半導体層に、ソース領域及びドレーン領域 153、155 と高濃度ドーピング領域 158 を形成する。

残りの工程は本発明の第 6 の実施形態による製造方法と同一の方法により、図 7 に示すように、本発明の第 5 の実施形態による薄膜トランジスタを製造する。

この時、ドーズ量は、例えば単位  $\text{cm}^2$  当たり  $1.0 \times 10^{15} \sim 3.0 \times 10^{15}$  粒子にすることができるが、これに限定されずゲート絶縁膜パターンの厚さ、素子の特性によってドーズ量を変えることができる。

10

#### 【0061】

以上の実施例 1 ~ 10 は、前述したように、n 型不純物イオンドーピングによって形成された薄膜トランジスタについて説明したが、p 型不純物イオンを用いる場合についても本発明が適用可能なことは勿論である。

#### 【0062】

以上、添付した図面を参照して本発明の好適な実施形態を説明したが、当業者であれば、本発明の技術的思想や必須的な特徴を変更せずに他の具体的な形態を実施できることを容易に理解できるであろう。

したがって、上述した好適な実施形態は、例示的なものであり、限定的なものではないと理解されるべきである。

20

#### 【産業上の利用可能性】

#### 【0063】

本発明は、ノートパソコンや携帯機器などの表示装置として用いられる液晶表示装置などの基板として使用される薄膜トランジスタ基板及びその製造方法に適用できる。

#### 【図面の簡単な説明】

#### 【0064】

【図 1】本発明の第 1 の実施形態による薄膜トランジスタ基板の概略構成図である。

【図 2】本発明の第 1 の実施形態による薄膜トランジスタ基板の画素部の構造を示すレイアウト図である。

【図 3】図 2 の薄膜トランジスタ基板を I I I - I I I' 線に沿って切って示す断面図である。

30

【図 4】本発明の第 2 の実施形態による薄膜トランジスタ基板の断面図である。

【図 5】本発明の第 3 の実施形態による薄膜トランジスタ基板の断面図である。

【図 6】本発明の第 4 の実施形態による薄膜トランジスタ基板の断面図である。

【図 7】本発明の第 5 の実施形態による薄膜トランジスタ基板の断面図である。

【図 8】本発明の第 6 の実施形態により、第 1 の実施形態に係る薄膜トランジスタ基板を製造する方法の、第 1 の中間段階におけるレイアウト図である。

【図 9】図 8 の薄膜トランジスタ基板を I X - I X' 線に沿って切って示す断面図である。

【図 10】図 8 の薄膜トランジスタ基板を I X - I X' 線に沿って切って示す断面図である。

40

【図 11】本発明の第 6 の実施形態により、第 1 の実施形態に係る薄膜トランジスタ基板を製造する方法の、第 2 の中間段階におけるレイアウト図である。

【図 12】図 11 の薄膜トランジスタ基板を X I I - X I I' 線に沿って切って示す断面図である。

【図 13】図 11 の薄膜トランジスタ基板を X I I - X I I' 線に沿って切って示す断面図である。

【図 14】図 11 の薄膜トランジスタ基板を X I I - X I I' 線に沿って切って示す断面図である。

【図 15】図 11 の薄膜トランジスタ基板を X I I - X I I' 線に沿って切って示す断面

50

図である。

【図16】図11の薄膜トランジスタ基板をXII-XII'線に沿って切って示す断面図である。

【図17】本発明の第6の実施形態により、第1の実施形態に係る薄膜トランジスタ基板を製造する方法の、第3の中間段階におけるレイアウト図である。

【図18】図17の薄膜トランジスタ基板をXVII-XVII'線に沿って切って示す断面図である。

【図19】本発明の第6の実施形態により、第1の実施形態に係る薄膜トランジスタ基板を製造する方法の、第4の中間段階におけるレイアウト図である。

【図20】図19の薄膜トランジスタ基板をXX-XX'線に沿って切って示す断面図である。

10

【図21】本発明の第6の実施形態により、第1の実施形態に係る薄膜トランジスタ基板を製造する方法の、第5の中間段階におけるレイアウト図である。

【図22】図21の薄膜トランジスタ基板をXXII-XXII'線に沿って切って示す断面図である。

【図23】本発明の第7の実施形態により、第2の実施形態に係る薄膜トランジスタ基板を製造する方法の、第2の中間段階における断面図である。

【図24】本発明の第8の実施形態により、第3の実施形態に係る薄膜トランジスタ基板を製造する方法の、第2の中間段階における断面図である。

【図25】本発明の第9の実施形態により、第4の実施形態に係る薄膜トランジスタ基板を製造する方法の、第2の中間段階における断面図である。

20

【図26】本発明の第10の実施形態により、第5の実施形態に係る薄膜トランジスタ基板を製造する方法の、第2の中間段階における断面図である。

【図27】本発明の第10の実施形態により、第5の実施形態に係る薄膜トランジスタ基板を製造する方法の、第2の中間段階における断面図である。

#### 【符号の説明】

##### 【0065】

10：画素部

20：ゲート駆動部

30：データ駆動部

30

53、54：感光膜パターン

110：基板

111：遮断層

120：ゲート用金属膜

121：ゲート線

124：ゲート電極

131：維持電極線

133：維持電極

140d、140q：ゲート絶縁膜パターン

141：第1のコンタクトホール

40

142：第2のコンタクトホール

143：第3のコンタクトホール

150：半導体層

152：低濃度ドーピング領域

153：ソース領域

154：チャネル領域

155：ドレーン領域

157：維持電極領域

158：高濃度ドーピング領域

171：データ線

50

- 173 : ソース電極

175 : ドレーン電極

190 : 画素電極

401 : 第1のゲート絶縁膜

402 : 第2のゲート絶縁膜

601 : 第1の層間絶縁膜

602 : 第2の層間絶縁膜

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図20】

【図21】

【図22】

【図23】

【図24】

【図26】

【図25】

【図27】

---

フロントページの続き

(72)発明者 朴 慶 ミン

大韓民国 京畿道 城南市 盆唐区 亭子洞 ハンソルマウル 住公6団地アパート 607棟1

004号

(72)発明者 朴 京 淳

大韓民国 京畿道 龍仁市 器興区 農書洞 7-1番地 三星電子株式会社 寄宿舎 月桂樹棟

334号

審査官 井上 弘亘

(56)参考文献 特開2005-150736 (JP, A)

特開平07-211912 (JP, A)

特開平04-196328 (JP, A)

特開2003-142687 (JP, A)

特開2000-047263 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336