(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4768012号

(P4768012)

(45) 発行日 平成23年9月7日(2011.9.7)

(24) 登録日 平成23年6月24日(2011.6.24)

(51) Int.Cl.

H01L 25/10 (2006.01)

H01L 25/11 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/14

Z

請求項の数 5 (全 15 頁)

(21) 出願番号 特願2008-506456 (P2008-506456)

(86) (22) 出願日 平成18年2月23日 (2006.2.23)

(65) 公表番号 特表2008-537333 (P2008-537333A)

(43) 公表日 平成20年9月11日 (2008.9.11)

(86) 國際出願番号 PCT/US2006/006426

(87) 國際公開番号 WO2006/112949

(87) 國際公開日 平成18年10月26日 (2006.10.26)

審査請求日 平成21年2月23日 (2009.2.23)

(31) 優先権主張番号 11/108,223

(32) 優先日 平成17年4月18日 (2005.4.18)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 マングラム、マーク エイ.

アメリカ合衆国 78652 テキサス州

マンチャカ カトルマン ドライブ 3

800

審査官 今井 拓也

最終頁に続く

(54) 【発明の名称】集積回路の他の集積回路への積層構造

## (57) 【特許請求の範囲】

## 【請求項 1】

第1面及び第2面を備える第1半導体パッケージを準備することであって、前記第1面は該第1面に設けられて前記第1半導体パッケージへの電気的接続を行う複数の第1導電バンプを有し、前記第1面の反対側にある非平面状の前記第2面はモールドキャップ及び隣接する複数の半田ランを有することと、

第2半導体パッケージを前記第1半導体パッケージの上に重ねるように配置することであって、前記第2半導体パッケージは第1面及び該第1面の反対側にある第2面を備え、前記第2面は該第2面の中央部の外側に位置して前記第1半導体パッケージの前記隣接する複数の半田ランと接触する第2の複数の導電バンプを有することと、

介在要素を前記第1半導体パッケージと前記第2半導体パッケージとの間に直接接觸するように配置することであって、前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージの各々に接着し且つ前記介在要素に接觸する前記第1半導体パッケージ及び前記第2半導体パッケージの隣接面に剛性を提供するのに十分な粘着性を有することと、

前記介在要素を前記第1半導体パッケージ及び前記第2半導体パッケージの少なくとも一つの周囲の外側へ横方向に延出させるとともに前記介在要素を一つの角度に曲折させることと、

前記第2の複数の導電バンプ及び前記半田ランを介して、前記第1半導体パッケージと前記第2半導体パッケージとの間の直接的な電気的接觸を行うことと、

10

20

下部基板を前記第1半導体パッケージに接続することであって、前記下部基板は複数の接点を有し、各接点を前記第1半導体パッケージの前記第1の複数の導電バンプのうちの少なくとも1つに接触させることと、

を備える半導体パッケージの積層方法。

**【請求項2】**

前記第1半導体パッケージ又は前記第2半導体パッケージのうちの一つの外側に沿って前記介在要素を延出させるとともに曲折させることと、

前記下部基板に向かって且つ同下部基板を通過するように前記介在要素を曲折することと、

前記介在要素に電気的又は物理的接触のうちの少なくとも一方を前記下部基板の背面側から行うことと、

を更に備える請求項1に記載の方法。

**【請求項3】**

第1面及び第2面を備える第1半導体パッケージであって、前記第1面は該第1面に設けられて前記第1半導体パッケージへの電気的接続を行う複数の第1導電バンプを有し、前記第1面の反対側にある非平面状の前記第2面はモールドキャップ及び隣接する複数の電気的接点を有することと、

前記第1半導体パッケージに重なり合う第2半導体パッケージであって、前記第2半導体パッケージは第1面及び該第1面の反対側にある第2面を備え、その第2面は該第2面の中央部の外側に位置して前記第1半導体パッケージの前記隣接する複数の電気的接点と接触する複数の第2導電バンプを有し、前記第2半導体パッケージは複数の第2導電バンプを介して前記第1半導体パッケージと直接的な電気的接触を行うことと、

前記第1半導体パッケージと前記第2半導体パッケージとの間に直接接觸するように配置される介在要素であって、前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージの各々に接着し且つ前記介在要素に接觸する前記第1半導体パッケージ及び前記第2半導体パッケージの隣接面に剛性を提供するのに十分な粘着性を有し、前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージに対して表面適合性を有し、前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージの少なくとも一つの周囲の外側へ横方向に延出するとともに所定量だけ曲折することと、

複数の接点を有する下部基板であって、前記下部基板における前記複数の接点の各々は前記第1半導体パッケージにおける前記複数の第1導電バンプのうちの少なくとも1つに接觸することと、

を備える積層半導体パッケージアッセンブリ。

**【請求項4】**

前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージの周囲から外側に向けて横方向に延びる請求項3に記載の積層半導体パッケージアッセンブリ。

**【請求項5】**

前記介在要素は、前記第1半導体パッケージ及び前記第2半導体パッケージの周囲から外側に向けて横方向に延びるとともに、電気的又は物理的接觸のうちの少なくとも一方を前記下部基板の背面側から行うために前記下部基板に向かって且つ同下部基板を通過するように曲げられる請求項4に記載の積層半導体パッケージアッセンブリ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体に係り、より具体的には複数の集積回路を互いに積層することによる半導体実装に関する。

**【背景技術】**

**【0002】**

様々な半導体パッケージ構造が提案され、半導体ダイを収容するために用いられている。これらの構造の多くは雑音遮断及び熱散逸を提供する構成要素を有している。更に小型

10

20

30

40

50

のデバイスの必要性及び要求に伴い、いくつかの集積回路が互いの上に直接積層されるようになった。集積回路パッケージを積層することには様々な課題が付随する。このような課題には、効果的に散逸されない熱の増大、パッケージ及びパッケージリードの配列、並びにパッケージの設置面積内における及びパッケージの外部リードに沿った固有の相互電気干渉が含まれる。

#### 【0003】

例えば、半導体パッケージが積層される時、熱の影響が線形的に結合する。その結果、パッケージ同士の間に熱対流を得るのに十分な空気ギャップを設けつつパッケージを積層することが提案されている。しかしながら、空気ギャップを使用することは、数ワットの電力を消費する多くの最新の半導体に限られた熱的な強化をもたらすだけである。半導体パッケージと直接的に接触する熱的に強化された材料の利用は、半導体パッケージの電力消費を改善する。

10

#### 【0004】

ノイズを相殺する過去の取り組みは、半導体アッセンブリの周囲全体を取り囲むように完成した半導体アッセンブリ全体を遮蔽することに向けられていた。絶縁ワイヤをワイヤボンドパッケージに使用することもできる。

#### 【0005】

加えて、フラッシュメモリが積層されたパッケージに含まれる場合、フラッシュメモリに格納されるデータの安全性が問題となる。積層されたアッセンブリからフラッシュメモリパッケージを除去することによって、フラッシュメモリの重要なデータ及び制御ピンが物理的にアクセス可能な場合、フラッシュメモリの内容は抽出によって容易に得られる。その上、様々な公知の積層半導体パッケージ技術にしばしば直面する更なる問題は、半導体パッケージを互いに接合する高温リフロー中におけるパッケージ基板の反りの影響である。例えば、所定の状況において、下部パッケージの基板表面は凹状になるとともに、上部パッケージの基板表面は凸状になる場合がある。この反りは効果的且つ信頼性のある半田接合構造を防げ、電気的接続及び作用の異常をもたらす。したがって、2つ以上の半導体パッケージを積層することには様々な問題が存在する。

20

#### 【発明を実施するための最良の形態】

#### 【0006】

概して、ここでは半導体ダイと対向するように、増大された熱及びノイズ特性、配列特性、及び安全性を有する半導体パッケージを積層する改善された方法及び装置が提供される。半導体パッケージの積層は様々な形態で実施することができ、以下そのうちのいくつかの形態が詳述される

30

図1には、第1半導体パッケージ12及び重ね合わされる第2半導体パッケージ14を有する積層半導体パッケージ10が示される。第1半導体パッケージ12と第2半導体パッケージ14との間には薄膜材16の形態の介在要素が配置される。薄膜材16の両側（すなわち上面及び下面）には粘着性があり、一形態において粘着剤は熱によって活性化する。膜として、薄膜16は前もって比較的的確な寸法を有する所望の的確な形状に形成することができる。他の種類の粘着剤を使用することもできる。薄膜材16は柔軟性及び適合性（すなわち表面一致性）があり、半導体パッケージによって定義されるどのような厚み、すなわち寸法をも有し得る。第1半導体パッケージ12は、第1半導体パッケージ12内の半導体ダイ（図示略）への電気的接続を行う複数の導電ボールを有している。例えば、導電ボール18はこのような複数の導電ボールのうちの一つである。ここで定義され用いられるように、導電ボールはどのような導電材からも作られる。導電ボールは下部基板、すなわち複数の導電接点を有するマザーボード30上に配置される。また、第1半導体パッケージ12は基板20を有している。基板20は、半導体パッケージ基板に共通して用いられる導電フィルム（すなわち、基板）、FR4、ビスマレイミドノトリアジン（BT）積層板又は他の有機材料のような様々な材料から形成可能である。基板20にはモールドキャップ22が重ね合わされ、その大きさは半導体パッケージ本体の大きさ及び半田ラン24等の近接する半田ランによって決定される。ここで用いられる単語「半田ラン

40

50

」はいずれの形状の電気接点をも含む。更に、単語「半田」は従来の半田組成に加えて導電ペースト、ポリマーバンプ等の様々な導電材料を含む。モールドキャップ 22 は一般的に樹脂成形材である。成形が完了すると、基板 20 及びモールドキャップ 22 は互いに一体化される。第 2 半導体パッケージ 14 もまた導電ボール 28 のような複数の導電ボールを有している。導電ボールはパッケージ基板 27 と当接している。半導体パッケージ基板 27 にはモールドキャップ 26 が重ね合わされる。成形が完了すると、モールドキャップ 26 は、パッケージ基板 27 と一体化される。モールドキャップ 26 は様々な従来のモールド複合材のうちのいずれかからも形成される。2つの半導体パッケージのみが図示されているが、この構造においていくつの半導体パッケージが積層されても良い。したがって最後、すなわち頂部側半導体パッケージは下側のパッケージ基板における一端から他端へ完全に延びるモールドキャップを有することができる。また、モールドキャップ以外の構造が用いられても良い。例えば、例示されたモールドキャップに代えて、グロブトップ、所定のセラミック中空構造、所定の金属中空構造、ガラス等を用いても良い。また、最後、すなわち頂部側半導体パッケージは下側のパッケージ基板の一端から他端まで延びない構造によって実施されても良い。

#### 【 0 0 0 7 】

図 2 は図 1 の 2 つの半導体パッケージの完成したアッセンブリを示している。説明の便宜上、参照符号はこれら図 1 及び 2 において同一とする。組み付け方法において、第 1 半導体パッケージ 12 はマザーボード 30 上の所望の所定位置に配置される。第 1 半導体パッケージ 12 の導電ボールはマザーボード 30 の所定の露出接点と直接的に接触するように配置される。マザーボード 30 は増設構成要素（図示略）に接触する各面から延びる電気配線（図示略）を有する。薄膜材 16 はその後、第 1 半導体パッケージ 12 のモールドキャップ 22 の上面に配置される。一般的に、薄膜材 16 は十分に粘着性があるので、第 2 半導体パッケージ 14 が第 1 半導体パッケージ 12 の上面に配置された場合に所定位置に留まる。この配設は一般的に自動化されており、ロボット設備によって行われる。一形態において、所定半田リフロー工程に特化される全ての構成要素は、マザーボード上に配置又は密集される。その後、半導体積層パッケージアッセンブリ全体はリフロー・オーブン（図示略）におけるリフロー工程を通過する。熱が供給されるリフロー工程中において、2つのパッケージはそれら同士が組み合わされるとともに、マザーボード 30 へ他の構成要素が取り付けられ、且つ薄膜材 16 は 2 つの半導体積層パッケージを互いに固着させる。例示した形態において、薄膜材 16 はリフロー工程の熱の影響によって引き起こされる反りを小さくするとともに、第 1 半導体パッケージ 12 を第 2 半導体パッケージ 14 に固着し、それらが容易に離間することを妨げる。薄膜材 16 は両半導体パッケージの露出面に適合し且つ一致する。いくつかの構成において、頂部側すなわち第 2 半導体パッケージ 14 の底面はペアシリコンである。最下部側すなわち第 1 半導体パッケージ 12 のモールドキャップ 22 の表面は、成形用プラスチックを含む様々な材料のうちのいずれかであれば良い。したがって、薄膜材 16 はその特性によって効果的に 2 つの半導体パッケージに接着し、最終積層パッケージアッセンブリの剛性を増加させる。このような剛性の増加は、接触接合の信頼性を考察すること及び落下試験能力の改善に重要である。

#### 【 0 0 0 8 】

一形態において、第 2 半導体パッケージ 14 は不正な検索から保護されるべき保護データを格納するデータ格納又はメモリ集積回路として実施される。例えば、一般的にフラッシュメモリが情報を格納するために使用される。使用者が第 2 半導体パッケージ 14 から第 1 半導体パッケージ 12 を分離させようとすると、第 2 半導体パッケージ 14 は薄膜材 16 の粘着性により損傷し、メモリ集積回路へはアクセスできず、データをアクセス及び抽出から保護する。したがって、薄膜材 16 は積層パッケージアッセンブリに剛性を提供することに加えて、データへのアクセスを困難にすることにより機密データの安全性を提供する。

#### 【 0 0 0 9 】

加えて、薄膜材 16 に RFI 及び EMI 材を用いた場合、第 1 半導体パッケージ 12 と

10

20

30

40

50

第2半導体パッケージ14との間に電気的シールドが提供される。したがって、近接するパッケージからの干渉信号に対して、近接するノイズ源から薄膜材16によって隔離された電気回路網の部位が保護される。2つの積層半導体パッケージ間における薄膜材の挿入及び一体化は、最下部側又は下側パッケージ位置に配置される高速ロジック集積回路のノイズ低減を可能にする。ノイズ低減性はパッケージアッセンブリの能力全体を向上し、このパッケージを携帯無線製品に見られるような様々なノイズに敏感なアプリケーションに使用可能とする。

#### 【0010】

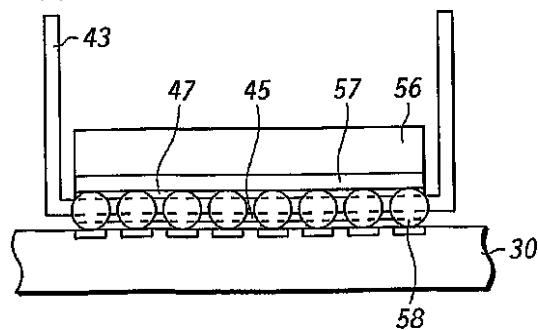

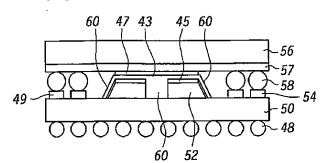

図3には本発明の他の形態に係る積層半導体パッケージアッセンブリ40が示される。導電接点を有するマザーボード30は第1半導体パッケージ42の下側に存在し、該第1半導体パッケージ42は第2半導体パッケージ44の下側に存在する。第1半導体パッケージ42は第1半導体パッケージ42内の半導体ダイ(図示略)への電気的接点を成す複数の導電ボールを有する。例えば、導電ボール48はこのような複数の導電ボールのうちの一つである。上述のように、導電ボールはいかなる導電材からも形成される。導電ボールはマザーボード30の接点上に配置される。第1半導体パッケージ42は基板50を有している。基板50は、導電膜(例えば基板)FR4、ビスマレイミド/トリアジン(BT)積層板又は有機材料のような半導体パッケージ基板に一般的に使用される様々な材料から作られることができる。基板50にはモールドキャップ52が重ね合わされ、その大きさは半導体パッケージ体の大きさ及び近接する半田ラン49, 51, 53及び54等の半田ランによって決定される。モールドキャップ52は一般的に樹脂成形材である。成形が完了すると、基板50及びモールドキャップ52は互いに一体化される。第2半導体パッケージ44もまた導電ボール58のような複数の導電ボールを有している。導電ボールはパッケージ基板57と当接している。半導体パッケージ基板57にはモールドキャップ56が重ね合わされる。成形が完了すると、モールドキャップ56は、パッケージ基板57と一体化される。2つの半導体パッケージのみが図示されているが、この構造においていくつの半導体パッケージが積層されても良い。また、最後、すなわち頂部側半導体パッケージは、下側のパッケージ基板の一端から他端へ完全に延びるモールドキャップ、又は下側のパッケージの上面に對して類似又は変形した形状を有しても良い。

#### 【0011】

第1半導体パッケージ42と第2半導体パッケージ44との間には、薄膜材45及び47のような挿入部材、及び部材43がノイズ低減及び/又は熱強化を目的として設けられる。図3の部材43は、図示された側部とほぼ垂直な1つ以上の辺上に延長部を有している。延長部は長さLを有するように例示されている。長さLは仕様に応じて変更されることができる。図3の実施形態に示されるように、Lはアッセンブリが形成される時に少なくとも部材43の側部からマザーボード30の上面にまで延びるのに十分な長さとなるように示されている。他の形態において、長さは積層パッケージアッセンブリから横方向に延びるとともに1つ以上の目的のための接点を規定するのに十分な長さで実施されても良く、又はマザーボード30のビアを通って様々に延びるのに十分な長さで実施されても良い。図3から理解できるように、部材43は、下方へ曲げられる場合又は他の構造と接触するように構成される場合のいずれかにおいて、マザーボード30と接觸するように積層半導体パッケージアッセンブリ40から外側へ向けて延びている。

#### 【0012】

反り又は安全性が懸案事項でない場合、薄膜材45及び47は付加物であると考えることができる。使用される場合の薄膜材の利点は、薄膜材16に関して前述した利点と類似である。例示された形態において、薄膜材45は第1半導体パッケージ42のモールドキャップ52に対して配置され、薄膜材47は第2半導体パッケージ44の底面に対して配置される。薄膜材45及び47は異なる材料組成及び異なる寸法でも良い。

#### 【0013】

部材43は、積層パッケージアッセンブリの熱特性を強化する目的、及び/又はRFI及びEMI保護及び/又は防護を提供する目的のために、使用に応じて2つの半導体パッ

10

20

30

40

50

ケージ 4 2 及び 4 4 の間、並びに薄膜材 4 5 及び 4 7 の間に配置される。薄膜材 4 5 及び 4 7 が使用される場合、この積層半導体パッケージアッセンブリ 4 0 の安全性は著しく改善される。部材 4 3 は、熱伝導性及びノイズ防護特性の一方又は両方を有する、容易に利用可能な範囲の材料から選択される。この積み上げアッセンブリへの部材 4 3 の導入は、従来手段による 2 つのパッケージ分離を阻止しつつ、底部側パッケージへのアクセスを妨げることによって安全性を改善する。薄膜材 4 5 及び 4 7 が適切に配置された場合、このパッケージ積層の安全性は著しく強化される。底部側パッケージと部材 4 3 、及び頂部側パッケージと部材 4 3 という異種部材間の薄膜による接合は、分離を不可能にする。

#### 【 0 0 1 4 】

特に、部材 4 3 が表面相互接続又は貫通固定方法のいずれかによってマザーボード 3 0 に取り付けられる場合、部材セット間の機械的及び熱的な非類似性は構造を一つに統合する。二つのパッケージを分離しようとする場合、薄膜材 4 5 はモールドキャップ 5 2 及び部材 4 3 への粘着接合材を形成する。薄膜材 4 7 は部材 4 3 とパッケージ基板 5 7 との間に粘着接合材を形成する。2 つのパッケージを分離しようとする場合、熱及び機械応力が積層パッケージアッセンブリ構造の分離を妨げる。記載されたような場合において、分離によって積層パッケージアッセンブリは破壊される。したがって、特に集積回路が保護データを含むメモリである場合、集積回路パッケージのうちの一つからのデータの除去は著しい機能障害となる。

#### 【 0 0 1 5 】

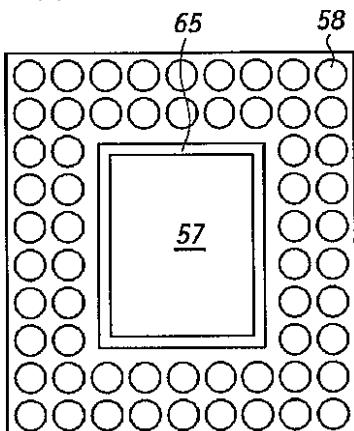

図 4 は図 3 の 4 - 4 線に沿った平面図であって、部材 4 3 の物理的な構成を示している。この構成は上述のように部材 4 3 を使用することを可能とする。2 辺上に長さ L の延長部 6 0 が示され、該延長部 6 0 は部材 4 3 をマザーボード 3 0 に装着するのに用いられる。図 5 に示すように底面の 2 辺のみに導電ボール 5 8 のような導電ボールが密集したパッケージ基板 5 7 を有する第 2 半導体パッケージ 4 4 を考慮して、2 つの延長部のみが例示される。

#### 【 0 0 1 6 】

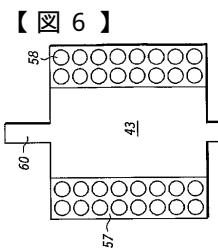

図 6 は図 4 の部材 4 3 が半導体パッケージ 4 4 のパッケージ基板 5 7 の底面に重ね合わされた状態を示している。例示された形態において、延長部は導電ボールが密集していないパッケージ基板 5 7 の底面の 2 辺から伸びるように配置される。延長部 6 0 の長さ L は変更可能である。延長部 6 0 は、半導体パッケージ 4 4 から横方向に伸びるだけでも良いし、マザーボード 3 0 から遠ざかるように上方に向かって、或いはマザーボード 3 0 上にまで又はマザーボード 3 0 を貫通するように下方に向かって構成されても良い。

#### 【 0 0 1 7 】

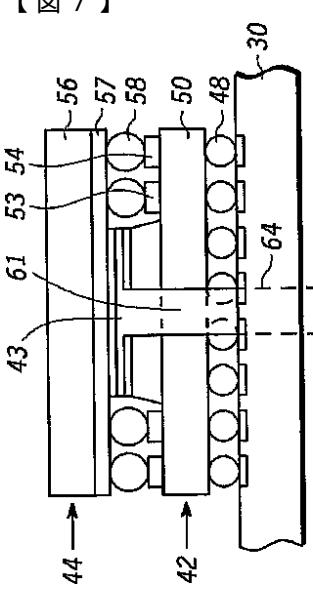

図 7 は、図 3 の 2 つの半導体パッケージを含む完成した積層半導体パッケージアッセンブリ 4 0 を、第 1 半導体パッケージ 4 2 と第 2 半導体パッケージとの間に挿入される部材 4 3 及び薄膜材 4 5 及び 4 7 と共に示す側面図である。部材 4 3 は介在要素として機能し、下側に存在する基板、すなわちマザーボード 3 0 に物理的に接触するように、モールドキャップ 5 2 の上方から、半導体パッケージ 4 2 から横方向に離れて伸びる。延長部の様々な選択肢が存在する。例えば、一形態において、延長部 6 1 はマザーボード 3 0 の上面に接触する。延長部 6 1 への電気的な接触は様々な方法によって行われる。例えば、延長部 6 1 はマザーボード 3 0 の上面に配置され且つ完成した積層半導体パッケージアッセンブリ 4 0 に近接又は一体化された構成要素（図示略）と接触してもよい。他の形態において、部分 6 4 によって示される延長部 6 1 の延出部は、マザーボード 3 0 の背面側へ突出又は貫通する。その結果、延長部 6 1 への電気的な接触はマザーボード 3 0 の背面側から行われることができる。

#### 【 0 0 1 8 】

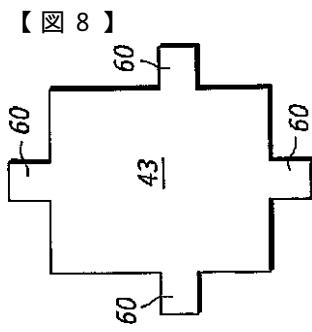

図 8 は、図 3 の 4 - 4 線に沿った平面図であって、部材 4 3 の更に他の物理的な構成を示している。この構成は、半導体パッケージ 4 4 のパッケージ基板 5 7 の底面の 4 辺全てに導電ボールが密集する状況において部材 4 3 が使用されることを可能とする。所定長さの 4 つの延長部 6 0 が図示される。互いの長さは同一でも良いし、いくつか又は全てが異

10

20

30

40

50

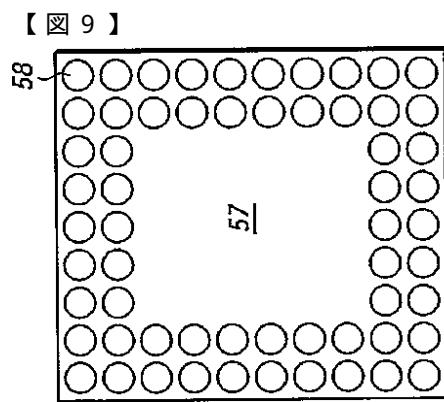

なっていても良い。図9に示されるように底面の4辺に導電ボール58のような導電ボールが密集したパッケージ基板57を有する第2半導体パッケージ44を考慮して、4つの延長部が例示される。

#### 【0019】

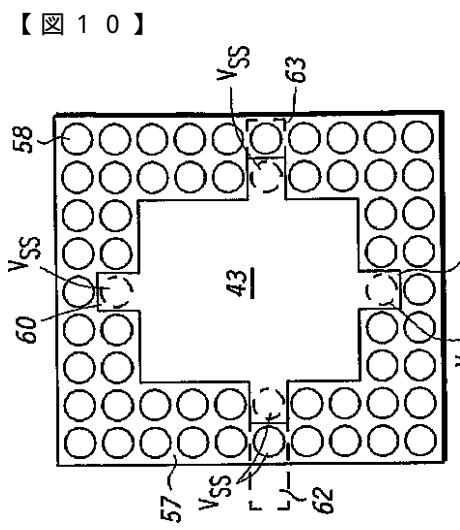

図10は、半導体パッケージ44のパッケージ基板57に図8の部材43が重ね合わされた図である。図示された形態において、延長部はパッケージ基板57の底面の4辺全てから延びるように配置されている。一構成において、延長部60は、パッケージ基板57の底面の左側に図示されるように、内側の列のみの導電ボールと接触することができる。例示された形態において、導電ボールは接地電位又はV<sub>SS</sub>電位である。しかしながら、他の信号電位とすることもできる。他の構成において、延長部62は横方向に隣接する2つの導電ボールを捕捉するとともに、所定量だけ半導体パッケージ44を越えて突出してもよい。横方向に隣接する2つの導電ボールは、それぞれが接地電位又はV<sub>SS</sub>電位、或いは他の電位のような同じ電位に接続される。他の構成において、延長部63は横方向に隣接する2つの導電ボールを捕捉するのに十分なだけの長さである。この場合も、2つの横方向に隣接する導電ボールは、それぞれが接地電位又はV<sub>SS</sub>電位、或いは他の電位のような同じ電位に接続される。これらのような構造の変形例は容易に考えられる。例えば、半導体パッケージ44の側部上の横方向の導電ボールの数は異なっても良いし、2列又は2行よりも多くしても良い。延長部62の長さLは変更されてもよい。また、延長部62は半導体パッケージ44から横方向に延びるだけでも良いし、マザーボード30から離間するように上方に向けて、或いはマザーボード30上にまで又はマザーボード30を貫通するように下方に向けて構成されても良い。10

#### 【0020】

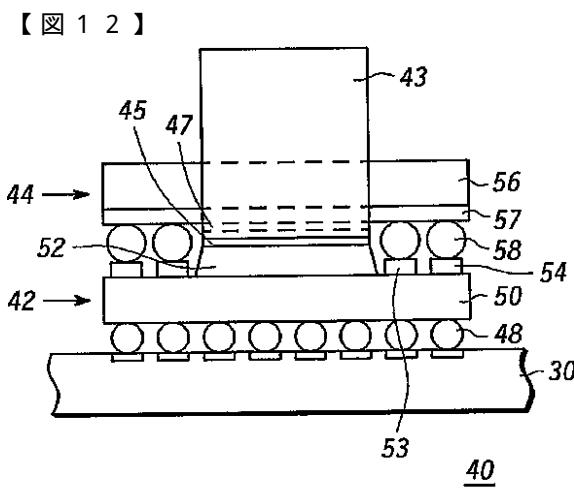

図11は、図8に示される部材43を用いた図3の2つの半導体パッケージの完成アッセンブリを示す。説明の便宜上、参照符号はこれら両図において同一とする。組み付け方法において、第1半導体パッケージ42はマザーボード30上の所望の所定位置に配置される。そして薄膜材45は第1半導体パッケージ42のモールドキャップ52の上面に配置される。一般的に、薄膜材45は十分に粘着性があるので、部材43が薄膜材45の上面に配置された場合に所定位置に留まる。そして薄膜材47は部材43の上面に配置される。そして第2半導体パッケージ44の底面は薄膜材47と当接するように配置される。全ての配設は一般的に自動化されており、ロボット設備によって行われる。一形態において、所定半田リフロー工程に特化される全ての構成要素は、マザーボード上に配置又は密集される。その後、半導体積層パッケージアッセンブリ全体はリフローオープン（図示略）におけるリフロー工程を通過する。リフロー工程中において、2つのパッケージ及び部材43はマザーボード30に設けられる他の構成要素と共に薄膜材45及び47によって所定位置に固着される。半導体パッケージ44及び42は導電ボールを介して互いに取り付けられる。例示された形態において、薄膜材45及び47はリフロー工程の熱の影響によって引き起こされる反りを小さくする。また、薄膜材45及び47は、半導体パッケージ42及び半導体パッケージ44を部材43に固着し、それらが容易に離間することを妨げる。加えて、部材43は半導体パッケージアッセンブリへの熱及びノイズ強化を提供する。薄膜材45及び47は両半導体パッケージ及び部材43の露出面に適合し且つ一致する。部材43、45及び47は同じ材料でも良いし、同じ組成を有しても良い。いくつかの構成において、頂部側半導体パッケージ44の底面はベアシリコンである。底部側半導体パッケージ42のモールドキャップ52の表面は、成形用プラスチックを含む様々な材料のうちのいずれかであれば良い。したがって、薄膜材45及び47の特性は2つの半導体パッケージを部材43に接着し、最終積層パッケージアッセンブリの剛性を増加させる。30

#### 【0021】

図11に例示された形態において、延長部60は終端までに内側の列の導電ボールを1つだけ捕捉する。したがって、半導体パッケージ42及び半導体パッケージ44の端部を越える部材43の延長部は表現されていない。半田ラン51及び半田ラン53はそれぞれ40

半田ラン49及び半田ラン54よりも薄く、部材43への連結部を収容する。一形態において、半田ラン49及び半田ラン54の薄層化はエッティングによって達成される。他の形態において、厚みの増減は従来の半田マスク技術によって達成されても良い。

#### 【0022】

図11の積層パッケージアッセンブリの変形例が形成されても良い。例えば、延長部60はいずれの半田ランと導電バンプとの間にも配置されなくて良い。このような実施において、下側半導体パッケージのモールドキャップに近接する半田ラン及び導電バンプは、延長部用空間から離れるように更に遠くへ押圧され、基板50の上面に直接接続される。一形態において、延長部60は、モールドキャップ52を360度完全に囲む材料の連続片として実施されても良い。したがって、完全な包囲延長部60はドーム形状を有している。この形態において、ノイズ防護は、モールドキャップを完全に囲む半導体パッケージ及び積層パッケージアッセンブリの縁部の内側に留まる延長部60によって得られる。他の形態において、延長部60は長方形又は箱型を成すように構成される。更に他の形態において、延長部60は1つの辺にのみ沿って延びるように、1つの辺の一部に沿って延びるように、又はモールドキャップ52の全ての辺よりも少ない辺に沿って延びるように構成される。これらの形態において、一般的に延長部60はモールドキャップ52と形状において一致するが、必ずしも一致する必要はない。他の形態において、モールドキャップに隣接する導電バンプの横列の数は、例示されている数と別の数となるように実施されても良い。図11に示された形態において、2列の導電バンプが提供されている。しかしながら、1列のみ、3列又はそれ以上を備えても良い。

10

20

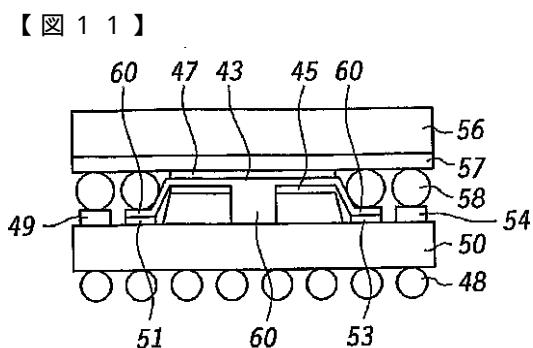

#### 【0023】

図12は、部材43が2つの半導体パッケージ間を横方向に突出するとともに、積層半導体パッケージアッセンブリ40の外側で上方へ曲折された積層半導体パッケージアッセンブリ40の他の形態を示す。この構成の部材43は1つ以上の目的を達成するために機能することができる。特に、外気への露出は熱散逸を強化する熱分散特性として機能する。加えて、部材43は導電材であるので、部材43が積層半導体パッケージアッセンブリ40の外部に位置することは、部材43が積層半導体パッケージアッセンブリ40の所定箇所を電気的に防護することを許容する。部材43が上方に曲折していることに加えて、部材43が外部に露出していることにより、部材43への接地電位又は他の電圧の接触をどの様に達成するかについて、使用者は柔軟に対処できる。他の形態において、部材43は曲折されなくても良く、熱散逸強化又は電気接触の目的のために積層半導体パッケージアッセンブリ40から横方向に延びることが許容されなくても良い。さらに、例示された90度に加えて、部材43を形成する他の角度が用いられても良い。

30

#### 【0024】

図13は図12に示された積層半導体パッケージアッセンブリ40の側面図を示す。図には部材43を用いた単体フィン構造が示されている。この方法の熱散逸特性を更に強化するために、増設フィン(図示略)が付加されても良い。また、図13では略90度に曲折した例が示されているが、使用に応じてどのような角度に曲折しても良い。

#### 【0025】

図14は、前述の図11の説明の積層パッケージアッセンブリの変形例のうちの1つである。説明の便宜上、図11の構成要素に類似している図14の構成要素には同様の符号が付される。図14に例示された形態において、延長部60は図11に示される導電ボールと半田ランとの間を延びていない。正しくは、延長部60は、基板50に対して少なくとも1つの物理的又は電気的接点を備えることにより基板50と物理的に当接している。半田ラン及び導電ボールは、積層パッケージアッセンブリの中央部から位置ずれしており、延長部60が半田ラン又は導電ボールと当接せずに基板50と当接できるだけの空間が提供される。図14に例示された形態において、延長部60は効果的にモールドキャップを取り囲み、防護性を提供する。

40

#### 【0026】

図15は、図14の積層パッケージアッセンブリの頂部側半導体パッケージの底面図を

50

示している。接触領域 6 5 はパッケージ基板 5 7 を包囲するように例示されている。例示された形態において、接触領域 6 5 は長方形であるが、他の形状が用いられても良い。接触領域 6 5 は、延長部 6 0 が接触する基板 5 0 の領域と重なり合う所定領域である。加えて、下側半導体パッケージと接触する延長部 6 0 に代えて、延長部 6 0 は接触領域 6 5 によって画定された領域内で頂部側半導体パッケージと接触することができるよう、上方に傾斜させられても良い。導電ボール 5 8 のような導電ボールを増設又は減少させても良い。

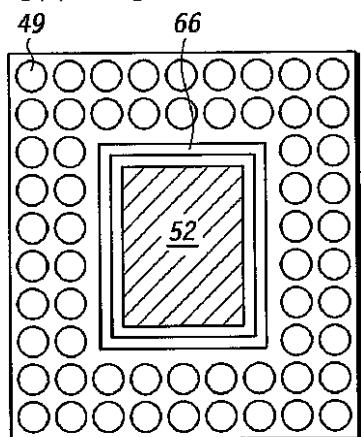

#### 【 0 0 2 7 】

図 1 6 は、図 1 4 の積層パッケージアッセンブリの底部又は下側半導体パッケージを示す平面図である。接触領域 6 6 はモールドキャップ 5 2 を包囲するように示されている。

接觸領域 6 6 は、延長部 6 0 が接触する基板 5 0 上の所定領域である。図 1 5 と関連して、導電ボールの総数を変更しても良い。延長部 6 0 が覆うモールドキャップ 5 2 の周囲の量は、1 辺分の割合から全周囲までの範囲で変更されても良い。

10

#### 【 0 0 2 8 】

以上によって、積層半導体パッケージ及びその形成方法が提供されたことが理解されるであろう。ここで記載されているように複数の集積回路パッケージが積層することにより、パッケージ剛性が増加され、これにより製造歩留まりが向上する。また、不正な検索からのデータ安全性の強化、熱強化及びノイズ低減が提供される。

#### 【 0 0 2 9 】

一形態において、積層半導体構造が提供される。第 1 半導体パッケージは第 1 面及び第 2 面を備える。前記第 1 面は該第 1 面に設けられて前記第 1 半導体パッケージへの電気的接続を行う複数の第 1 導電バンプを有し、前記第 1 面の反対側にある非平面状の前記第 2 面はモールドキャップ及び隣接する複数の半田ランを有する。第 2 半導体パッケージは前記第 1 半導体パッケージに重なり合う。前記第 2 半導体パッケージは第 1 面及び該第 1 面の反対側にある第 2 面を備え、その第 2 面は該第 2 面の中央部の外側に位置して前記第 1 半導体パッケージの前記複数の半田ランと接触する複数の第 2 導電バンプを有し、前記第 2 半導体パッケージは複数の第 2 導電バンプを介して前記第 1 半導体パッケージと直接的な電気的接觸を行う。介在要素は、前記第 1 半導体パッケージと前記第 2 半導体パッケージとの間に直接接觸するように配置される。前記介在要素は前記第 1 半導体パッケージ及び前記第 2 半導体パッケージの各々並びに前記介在要素に接觸する前記第 2 半導体パッケージに接着するのに十分な粘着性を有し、前記介在要素は前記第 1 半導体パッケージ及び前記第 2 半導体パッケージに対して表面適合性を有する。下部基板は複数の接点を有する。前記下部基板における前記複数の接点の各々は前記第 1 半導体パッケージにおける前記複数の第 1 導電バンプのうちの少なくとも 1 つに接觸する。

20

#### 【 0 0 3 0 】

一形態において、前記介在要素は熱活性材である。前記介在要素は破断することなく形成するのに十分な可塑性を有する。他の形態において、前記第 2 半導体パッケージは、保護データを格納するデータ格納集積回路である。他の形態において、前記介在要素は前記第 1 半導体パッケージ及び前記第 2 半導体パッケージの周囲から外側に向けて横方向に延びる。更に他の形態において、前記介在要素は、前記第 1 半導体パッケージ及び前記第 2 半導体パッケージの周囲から外側に向けて横方向に延びるとともに、下部基板から離間する方向に曲げられる。更に他の形態において、前記介在要素は、前記第 1 半導体パッケージ及び前記第 2 半導体パッケージの周囲から外側に向けて横方向に延びるとともに、前記下部基板に向かって電気的接觸を行うように曲げられる。更に他の形態において、前記介在要素は、前記下部基板への電気的接觸が行われる場合に、導電端子又は絶縁端子のうちの少なくとも 1 つに接続される。前記導電端子は基準電圧端子、電力供給端子、接地端子、信号端子又は他の種類の端子でも良い。絶縁端子はハウジング端子、ケーシング端子、搭載金具、酸化物又は窒化物のような絶縁材への接続部、又は他の種類の非導電端子でも良い。更なる形態において、前記介在要素は、前記第 1 半導体パッケージ及び前記第 2 半導体パッケージの周囲から外側に向けて横方向に延びるとともに、電気的又は物理的接觸

30

40

50

のうちの一方を前記下部基板の背面側から行うために前記下部基板に向かって且つ同下部基板を通過するように曲げられる。更に他の形態において、前記第2面の中央部の外側に位置する前記第2半導体パッケージの前記複数の第2導電バンプは、前記第2面において互いに反対側に位置する2辺のみに沿って配置され、前記介在要素は前記第2面において前記2辺と隣接して互いに反対側に位置する2辺から、前記積層半導体パッケージアッセンブリの横方向に延びる。他の形態において、前記介在要素は、前記積層半導体パッケージアッセンブリのノイズ隔離及び熱強化のために、前記下部基板と物理的に接触するよう前記モールドキャップ上から延びる。

## 【0031】

更なる形態において、積層半導体パッケージアッセンブリは第1面及び第2面を有する第1半導体パッケージを備える。前記第1面は前記第1半導体パッケージへの電気的接続を行う複数の第1接点を有する。前記第1面の反対側にある前記第2面は複数の第2接点を有する。第2半導体パッケージは前記第1半導体パッケージの上に配置され、第1面及び該第1面の反対側にある第2面を備える。前記第2面は該第2面上に位置する複数の第3接点を有し、該複数の第3接点はそれぞれ前記第1半導体パッケージの前記複数の第2接点と接触する。前記第2半導体パッケージは前記第1半導体パッケージと直接的な電気的接觸を行う。介在要素は前記第1半導体パッケージの一部と前記第2半導体パッケージとの間に直接接觸するように配置される。前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージの各々に接着し且つ前記介在要素に接觸する前記第1半導体パッケージ及び前記第2半導体パッケージの隣接面に剛性を提供するのに十分な粘着性を有する。前記介在要素は前記第1半導体パッケージ及び前記第2半導体パッケージに対して表面適合性を有するとともに、前記積層半導体パッケージアッセンブリの周囲から横方向に延びる部位を有する。下部基板は複数の第4接点を有する。前記基板における前記複数の第4接点の各々は前記第1半導体パッケージにおける前記複数の第1接点のうちの少なくとも1つに接觸する。

## 【0032】

一形態において、前記介在要素は下部基板から離間する方向に曲げられる。他の形態において、前記介在要素は、前記第1半導体パッケージ及び前記第2半導体パッケージの周囲から外側に向けて横方向に延びるとともに、前記下部基板に向かって電気的接觸を行うように曲げられる。更に他の形態において、前記介在要素は、前記下部基板への電気的接觸が行われる場合に、定電圧端子に接続される。

## 【0033】

更に別の形態において、本願では第1半導体パッケージを備える積層半導体パッケージアッセンブリが提供される。第1半導体パッケージの第1面は、該第1面に設けられて前記第1半導体パッケージへの電気的接続を行う複数の第1導電バンプを有する。前記第1半導体パッケージは、モールドキャップ及び隣接する複数の半田ランを有し前記第1面の反対側にある非平面状の前記第2面を備える。第2半導体パッケージは、前記第1半導体パッケージに重なり合い、第1面及び該第1面の反対側にある第2面を備える。前記第2面は該第2面の中央部の外側に位置して前記第1半導体パッケージの前記複数の半田ランと電気的に接觸する複数の第2導電バンプを有する。前記第2半導体パッケージは複数の第2導電バンプを介して前記第1半導体パッケージと電気的接觸を行う。伝導粘着層は、前記積層半導体パッケージアッセンブリの中央領域に配置され且つ前記第1半導体パッケージと前記第2半導体パッケージとの間に直接接觸する。前記伝導粘着層の一部は前記中央領域から延びるとともに前記複数の第1接点のうちの少なくとも1つ及び前記複数の第2接点のうちの1つの間にあり且つ電気的に接觸する。下部基板は複数の接点を有する。前記下部基板における前記複数の接点の各々は前記第1半導体パッケージにおける前記複数の第1導電バンプのうちの少なくとも1つに接觸する。

## 【0034】

一形態において、前記第1半導体パッケージと前記第2半導体パッケージとの間の電気的防護又は熱散逸のうちの少なくとも1つを強化するために、前記複数の第1接点のうち

10

20

30

40

50

の少なくとも 1 つ及び前記複数の第 2 接点のうちの 1 つは定電圧端子と接続される。更に他の形態において、前記伝導粘着層は、熱活性及び可塑性を有する膜である。更なる形態において、前記第 2 半導体パッケージは、保護データを格納するデータ格納集積回路である。また更なる形態において、前記中央領域から延びる伝導粘着層の部位は、前記複数の半田ラン及び前記複数の第 2 導電バンプの幾つかの間を、前記積層半田パッケージアッセンブリの少なくとも 2 辺に向かって横方向に延びる。更なる別の形態において、前記伝導粘着層の第 2 部位は、前記積層半導体パッケージアッセンブリの外縁を越えて横方向に延びる。

### 【 0 0 3 5 】

上記説明において、本発明は具体的な実施形態を参照して記述された。しかしながら、当業者には、後の請求の範囲に規定される本発明の範囲から逸脱しない限り様々な改良及び変更を行うことができる事が理解できる。例えば、部材 16, 45 及び 47 の薄膜材を例示して記述したが、厚みが変更された部材を用いることができる事が理解され、産業上の「薄膜」と見なしたり分類したりする必要は全くない。本願において電気的に又は熱的に伝導性があると記載される構成要素のそれぞれ及び全てに様々な伝導材を用いることができる。積層される半導体パッケージとして、様々な半導体封止材を用いることができる。例えば、樹脂成形化合物、セラミック及び他の半導体材料を用いることができる。積層される半導体装置の数はいくつでも良い。本願に記載された積層半導体パッケージアッセンブリは、ボール・グリッド・アレイ・パッケージズに加えて、鉛半導体パッケージ、ダイレクト・チップ・アタッチ (DCA) フリップ・チップ・デバイス、ランド・グリッド・アレイズ (LGAs) 及びリードレス・チップ・キャリアズ (LCCs) と組み合わせて使用することもできる。したがって、明細書及び図面は限定的な意図ではなく例示であると見なされ、このような変更の全てが本発明の範囲に含まれるように意図されている。

### 【 0 0 3 6 】

特定の実施形態を参照しながら種々の利益、種々の他の利点及び問題の解決方法を説明してきたが、このような種々の利益、種々の他の利点、問題の解決方法および任意の利益、利点または問題の解決方法を実行し、より優れたものにすることができる任意の要素は、請求項のいずれかまたはすべての重要で、必要なまたは不可欠な機能または要素であると解釈すべきではない。

### 【 図面の簡単な説明 】

### 【 0 0 3 7 】

【図 1】本発明の一形態に係る積層半導体パッケージ構造の構成要素を示す断面図。

【図 2】図 1 の構成要素のうちのパッケージアッセンブリを示す断面図。

【図 3】本発明の他の形態に係る積層半導体パッケージ構造の構成要素を示す断面図。

【図 4】図 3 の半導体パッケージ間に挿入される構成要素の一形態を示す平面図。

【図 5】2 辺のみに導電バンプを備える図 3 の頂部側半導体パッケージの基板を示す底面図。

【図 6】図 4 の構成要素を図 5 に示された頂部側半導体パッケージの底面に重ね合わせて示す図。

【図 7】本発明の更なる他の形態に係る図 3 の構成要素のパッケージアッセンブリを示す断面図。

【図 8】図 3 の半導体パッケージ間に挿入される構成要素の他の形態を示す平面図。

【図 9】4 辺に導電バンプを備える図 3 の頂部側半導体パッケージの基板を示す底面図。

【図 10】図 8 の構成要素を図 9 に示された頂部側半導体パッケージの底面に重ね合わせて示す図。

【図 11】本発明の他の形態に係る積層半導体パッケージのパッケージアッセンブリの構成要素を示す断面図。

【図 12】本発明の更なる形態に係る積層半導体パッケージのパッケージアッセンブリの構成要素を示す断面図。

10

20

30

40

50

【図13】図12の積層半導体パッケージ構造を示す側面図。

【図14】本発明の更なる形態に係る積層半導体パッケージのパッケージアッセンブリの構成要素を示す断面図。

【図15】図14の頂部側半導体パッケージを示す底面図。

【図16】図14の下側半導体パッケージを示す平面図。

*FIG. 3*

**【図4】**

*FIG. 4*

【図5】

The diagram consists of two separate groups of 15 circles arranged in a 3x5 grid. The top group is labeled '58' and the bottom group is labeled '57'. The circles are represented by simple outlines.

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 12

FIG. 11

【図 1 3】

***FIG. 13***

【図 1 4】

***FIG. 14***

【図 1 5】

***FIG. 15***

【図 1 6】

***FIG. 16***

---

フロントページの続き

(56)参考文献 特開平11-330306(JP,A)

特開平9-283697(JP,A)

特開2006-59871(JP,A)

特開2004-111656(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/10

H01L 25/11

H01L 25/18