(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3739297号

(P3739297)

(45) 発行日 平成18年1月25日(2006.1.25)

(24) 登録日 平成17年11月11日(2005.11.11)

(51) Int.C1.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |             |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>57O</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>631B</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>641P</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>650M</b> |

請求項の数 3 (全 21 頁)

(21) 出願番号

特願2001-96101 (P2001-96101)

(22) 出願日

平成13年3月29日 (2001.3.29)

(65) 公開番号

特開2002-297104 (P2002-297104A)

(43) 公開日

平成14年10月11日 (2002.10.11)

審査請求日

平成16年4月13日 (2004.4.13)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100094525

弁理士 土井 健二

(74) 代理人 100094514

弁理士 林 恒徳

(72) 発明者 鈴木 俊明

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 米村 浩舟

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】高速応答の為に駆動補償を行う液晶表示装置の制御回路

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶表示装置の制御回路において、

現フレームの画像データと前フレームの駆動後状態データとから表示用駆動データを生成する表示駆動データ生成部を有し、

当該表示駆動データ生成部は、前記現フレームの画像データ及び前フレームの駆動後状態データの組合せに対応して表示用駆動データまたはその補正值を格納した第1の変換テーブルを有し、

更に、前記表示駆動データ生成部は、前記現フレームの画像データ及び前フレームの駆動後状態データとから現フレームの駆動後状態データを生成する駆動後状態データ生成部を有し、

当該駆動後状態データ生成部は、前記現フレームの画像データの上位ビットと前フレームの駆動後状態データの上位ビットの組合せに対応して現フレームの駆動後状態データまたはその差分値を格納した第2の変換テーブルと、

前記現フレーム画像データの下位ビットにしたがって、前記第2の変換テーブルから読み出した隣接する複数の駆動後状態データまたはその差分値から、補間演算により当該下位ビットに対応する補間された駆動後状態データまたはその差分値を求める第1の補間演算部とを有し、

前記駆動後状態データは、次のフレームで表示駆動レベルを求めるために、画素に対応して記憶領域を有するフレームメモリ内に一旦格納されることを特徴とする液晶表示装置

の制御回路。

【請求項 2】

請求項 1において、

前記第1の変換テーブルは、前記現フレーム画像データの上位ビットと前フレームの駆動後状態データの上位ビットの組合せについて、所定の範囲でグループ化され、当該グループ化された単位に対応して、前記表示用駆動データまたはその差分値が格納されることを特徴とする液晶表示装置の制御回路。

【請求項 3】

請求項 1または2に記載された制御回路と、

前記制御回路により表示制御される液晶表示パネルとを有することを特徴とする液晶表示装置。 10

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、液晶表示装置の制御回路に関し、特に、セルの駆動電圧に補正值を加えて駆動補償することで高速応答を可能にし、更に駆動補償のための回路構成を簡単化した液晶表示装置の制御回路を提供することにある。

【0002】

【従来の技術】

液晶表示装置は、省エネルギーで省スペースの表示装置として広く普及している。従来のコンピュータの静止画像を表示する表示装置としての利用から、近年において、動画を表示するテレビ用表示装置としての利用も提案されている。 20

【0003】

液晶表示パネルは、表示データに従う表示駆動電圧が印加されるソース電極と、走査タイミングで駆動されるゲート電極と、それらの交差位置に配置されたセルトランジスタ及び画素電極とを有し、セルトランジスタを介して、画素電極間の液晶層に表示駆動電圧を印加して液晶の透過率を変化させることで、所望の画像表示を行う。

【0004】

テレビ用の表示装置として液晶表示パネルを利用する場合は、例えば1秒間に60フレームの画像を表示する必要があり、その為には、約16 msecからなる1フレーム期間内に液晶層の透過率の変化を完了させる必要がある。1フレーム期間内にソース電極に表示駆動電圧を印加して画素電極間に同電圧を印加することは、比較的容易に行うことができるが、1フレーム期間内に液晶層の光学特性（例えば透過率）を完全に変化させることは、表示画像によっては困難な場合がある。例えば、透過率ゼロの黒色表示の状態から、透過率25%の中間色表示の状態まで変化させるためには、比較的長い時間を要する。 30

【0005】

液晶材料の応答特性にもよるが、応答特性の悪い液晶材料が利用される場合は、1フレーム期間内で透過率ゼロの状態から透過率25%の状態に変化させることが困難なこともある。また、液晶材料によっては、透過率ゼロの状態からある程度の透過率に変化させるための応答時間が、透過率25%の状態からそれより高い透過率に変化させるための応答時間よりも長い場合もある。或いは、透過率が上記と逆方向に変化する場合も同様の問題がある。 40

【0006】

このような液晶材料の応答性の遅さを補償する方法として、補償駆動方式が提案されている。この駆動方式では、前フレームでの駆動後の状態と現フレームでの駆動レベルとを考慮して、1フレーム期間内で液晶層が透過率の変化を完了できる最適の駆動レベルを算出し、その駆動レベルの電圧を画素電極に印加する。例えば、前フレーム期間で透過率ゼロの状態になっている時に現フレームで透過率50%に変化させる場合は、透過率50%に対応する駆動レベルの電圧で画素電極を駆動するのではなく、それよりも高い駆動レベルの電圧で画素電極を駆動する。その結果、液晶層の応答特性が遅くても、より高い駆動電 50

圧に対して液晶層の応答が速くなり，1フレーム期間内に目標の透過率状態に変化することができる。透過率が高い状態から低い透過率に変化させる場合も同様である。

#### 【0007】

##### 【発明が解決しようとする課題】

上記の駆動補償を行う為には，液晶表示装置の制御回路内に，入力画像データから表示用の駆動データに変換する表示駆動データ生成回路を設ける必要がある。表示駆動データ生成回路は，現フレームの入力画像データと前フレームの駆動後の状態データとから，補償された表示駆動データを演算により生成する。かかる演算は複雑であり，それを特殊な論理回路で実行しようとすると，演算回路が複雑化し，液晶表示装置のコストアップを招く。

10

#### 【0008】

そこで，表示駆動データ生成回路内に，表示駆動データを直接求めることができる変換テーブルを設けることが考えられる。しかし，かかる変換テーブルは，高速アクセスが可能なSRAMなどの比較的高価な回路を必要とし，変換テーブル自体も液晶表示装置のコストアップの原因となる。

#### 【0009】

そこで，本発明の目的は，コストダウンされた駆動補償を行う液晶表示装置の制御回路を提供することにある。

#### 【0010】

更に，本発明の別の目的は，駆動補償のための表示駆動データ生成回路をより簡略化することができる液晶表示装置の制御回路を提供することにある。

20

#### 【0011】

##### 【課題を解決するための手段】

上記の目的を達成するために，本発明の第1の側面は，液晶表示装置の制御回路において，現フレームの画像データと前フレームの画像データとから表示用駆動データを生成する表示駆動データ生成部を有し，当該表示駆動データ生成部は，現フレームの画像データ及び前フレームの画像データの組合せに対応して表示用駆動データまたはその補正值を格納した変換テーブルを有する。更に，変換テーブルは，現フレーム画像データの上位ビットと前フレーム画像データの上位ビットの組合せに対応して表示用駆動データまたはその補正值を格納して，その変換テーブルのサイズを小さくしている。更に，表示駆動データ生成部は，現フレーム画像データの下位ビットにしたがって，前記変換テーブルから読み出した複数の隣接する表示用駆動データまたはその補正值から，補間演算により当該下位ビットに対応する補間された表示用駆動データまたはその補正值を求める補間演算部を有する。そして，補間演算部が補正值を求める場合は，その求められた補正值にしたがって現フレーム画像データを補正して，表示駆動データを生成する駆動レベル演算部を有する。表示駆動データはソースドライバに供給され，表示駆動データに対応する駆動電圧がソース電極，セルトランジスタを経由して，画素電極に印加される。

30

#### 【0012】

上記の制御回路によれば，変換テーブルを，現フレーム画像データの上位ビットと前フレーム画像データの上位ビットとの組合せに対応して，表示用駆動データまたはその補正值を格納しているので，変換テーブルを格納する高速メモリ回路の容量を少なくすることができる。変換テーブルの容量を小さくしたことに伴い，表示用駆動データまたはその補正值の精度が低くなるので，補間回路を設けて，補間演算により精度を高めた表示用駆動データまたはその補正值を生成し，それにしたがって入力画像データを補正して表示駆動データを求める。

40

#### 【0013】

更に，上記の目的を達成するために，本発明の第2の側面によれば，液晶表示装置の制御回路において，現フレームの画像データと前フレームの駆動後状態データとから表示用駆動データを生成する表示駆動データ生成部を有し，当該表示駆動データ生成部は，現フレームの画像データ及び前フレームの駆動後状態データの組合せに対応して表示用駆動データを生成する。

50

タまたはその補正值を格納した第1の変換テーブルを有する。更に、表示駆動データ生成部は、現フレームの画像データ及び前フレームの駆動後状態データとから現フレームの駆動後状態データを生成する駆動後状態データ生成部を有する。そして、この駆動後状態データ生成部は、現フレームの画像データと前フレームの駆動後状態データの組合せに対応して現フレームの駆動後状態データまたはその差分値を格納した第2の変換テーブルを有する。更に、第2の変換テーブルは、現フレーム画像データの上位ビットと前フレーム駆動後状態データの上位ビットの組合せに対応して現フレームの駆動後状態データまたはその差分値を格納して、その変換テーブルのサイズを小さくしている。それに伴い、現フレーム画像データの下位ビットにしたがって、前記第2の変換テーブルから読み出した隣接する複数の駆動後状態データまたはその差分値から、補間演算により当該下位ビットに対応する補間された駆動後状態データまたはその差分値を求める第1の補間演算部を有する。そして、第1の補間演算部が差分値を求める場合は、その求められた差分値にしたがって現フレーム画像データを修正して、現フレームの駆動後状態データを生成する駆動後レベル演算部を有する。駆動後状態データは、次のフレームで表示駆動レベルを求めるために、画素に対応して記憶領域を有するフレームメモリ内に一旦格納される。

#### 【0014】

上記本発明の第2の側面において、より好ましくは、第1の側面の如く、第1の変換テーブルは、現フレーム画像データの上位ビットと前フレームの駆動後状態データの上位ビットとの組合せに対応して、表示用駆動データまたはその補正值を格納して、変換テーブルのサイズを小さくする。それに伴い、表示駆動データ生成部は、現フレーム画像データの下位ビットにしたがって、前記第1の変換テーブルから読み出した複数の隣接する表示用駆動データまたはその補正值から、補間演算により当該下位ビットに対応する補間された表示用駆動データまたはその補正值を求める第2の補間演算部を有する。そして、第2の補間演算部が補正值を求める場合は、その求められた補正值にしたがって現フレーム画像データを補正して、表示駆動データを生成する駆動レベル演算部を有する。

#### 【0015】

本発明の第3の側面は、フレーム期間の前半で画素電極に駆動電圧を印加して、フレーム期間の後半で階調値ゼロに対応する駆動電圧を印加するチャージリセット駆動方式の液晶表示装置の制御回路において、現フレームの画像データと前フレームの画像データとから表示用駆動データを生成する表示駆動データ生成部を有し、当該表示駆動データ生成部は、現フレーム画像データ及び前フレーム画像データの組合せに対応して表示用駆動データまたはその補正值を格納した第1の変換テーブルを有する。そして、前記変換テーブルから読み出された表示用駆動データまたはその補正值にしたがって、前記駆動電圧が決定される。

#### 【0016】

上記第4の側面は、フレーム期間の前半で画素電極に駆動電圧を印加して、フレーム期間の後半で階調値ゼロに対応する駆動電圧を印加するチャージリセット駆動方式の液晶表示装置の制御回路において、表示用駆動データを生成する表示駆動データ生成部を有し、当該表示駆動データ生成部は、現フレーム画像データ及び前フレーム駆動後状態データの組合せに対応して表示用駆動データまたはその補正值を格納した第1の変換テーブルと、現フレームの画像データと前フレーム駆動後状態データの組合せに対応して現フレームの駆動後状態データを格納した第2の変換テーブルとを有する。そして、前記第1の変換テーブルから読み出された表示用駆動データまたはその補正值にしたがって、前記駆動電圧が決定される。更に、前記第2の変換テーブルから読み出された現フレームの駆動後状態データは、フレームメモリに一旦格納され、次のフレームのデータを求めるために利用される。

#### 【0017】

上記の第3及び第4の側面において、好ましい実施例では、上記本発明の第1及び第2の側面の容量サイズを小さくした変換テーブルを適用することができる。

#### 【0018】

10

20

30

40

50

上記の第3及び第4の側面において、好ましい実施例では、同一階調を有する現フレーム画像データが隣接する画素に対して供給された時、隣接する画素に対して生成された現フレーム駆動データの階調値を、隣接する画素間で所定の階調値だけ異ならせることを特徴とする。

#### 【0019】

上記の第3及び第4の側面において、好ましい実施例では、階調レベルが異なる現フレーム画像データが隣接する画素に対して供給された時、当該隣接する画素に対する現フレーム画像データの階調レベルをそれぞれ増加・減少、又は減少・増加して、エッジ部分を強調するエッジフィルタを設けることを特徴とする。

#### 【0020】

10

#### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態例を説明する。しかしながら、本発明の保護範囲は、以下の実施の形態例に限定されるものではなく、特許請求の範囲に記載された発明とその均等物にまで及ぶものである。

#### 【0021】

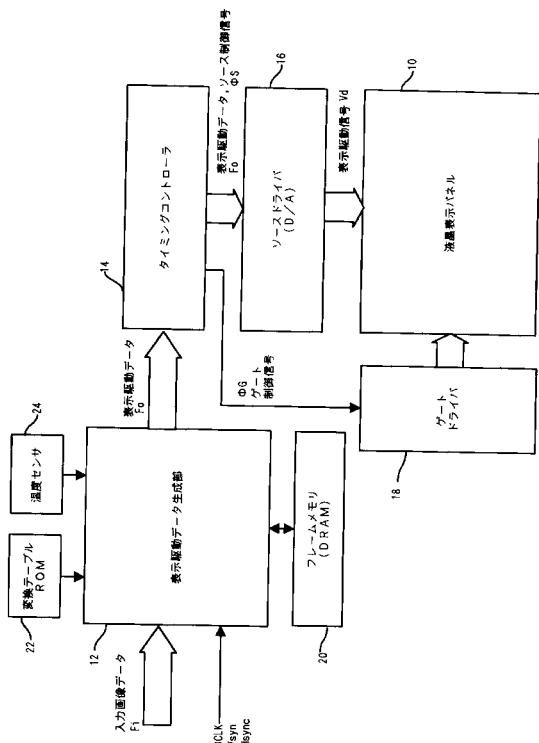

図1は、本実施の形態例における液晶表示装置の全体構成図である。図の液晶表示装置は、TFTなどの液晶表示パネル10に対して、ソース電極を表示駆動電圧Vdで駆動するソースドライバ16と、セルトランジスタのゲートに接続されたゲート電極を駆動するゲートドライバ18とを有する。画素に対応し階調値を有する入力画像データFiが、ホストコンピュータからドットクロックDCLKに同期して供給され、表示駆動データ生成部12が、その入力画像データFiから表示駆動に必要な階調値を有する表示駆動データFoを生成する。この表示駆動データFoは、後述する駆動補償方式を考慮して求められる。表示駆動データFoは、タイミングコントローラ14に供給され、シリアル・パラレル変換され、1ライン分の表示駆動データFoがソースドライバ16に所定のタイミングで供給される。ここまでがデジタルデータの処理回路である。

20

#### 【0022】

更に、ソースドライバ16は、デジタル・アナログ変換回路を有し、デジタル信号の表示駆動データFoをアナログ信号に変換し、液晶特性に対応した表示駆動信号Vdを生成する。

#### 【0023】

30

また、液晶表示装置は、表示駆動データ生成部12が内蔵する変換テーブルにダウンロードする変換テーブルデータを格納した変換テーブルROM22と、温度センサ24と、前フレームの画像データ等を格納するフレームメモリ20とを有する。

#### 【0024】

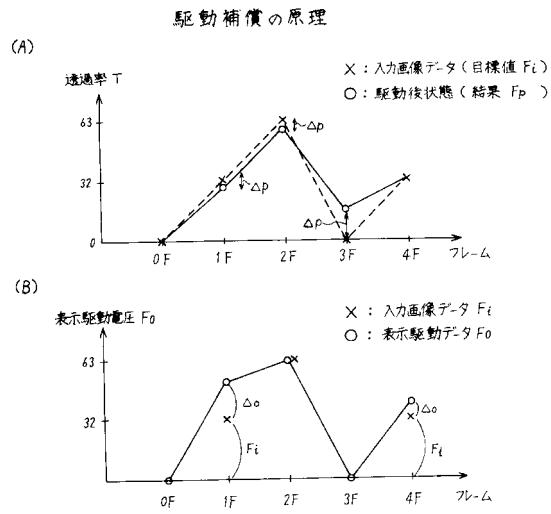

図2は、駆動補償の原理を説明するための図である。図2(A)は、横軸にフレーム期間、縦軸に画素の液晶層の光学特性である透過率T(64階調)を示し、図中×は入力画像データFiを、○は液晶層の駆動後の状態を示す。また、図2(B)は、横軸にフレーム期間、縦軸に表示駆動電圧Fo(64階調)を示す。

#### 【0025】

図2の例では、入力画像データFiは、フレーム0Fで階調値=0、次のフレーム1Fで階調値=32、次のフレーム2Fで階調値=63、次のフレーム3Fで階調値=0、そして次のフレーム4Fで階調値=32である。この場合、フレーム1Fでは、入力画像データFi=32であるが、液晶層の応答特性が遅いことを考慮して、表示駆動データFoは入力画像データFiに補正值oを加えた階調値に設定する。この補正值oを加えることで、前フレームの透過率=0の状態から目標値である透過率T=32に、フレーム1Fの期間内にできるだけ近くまで到達することが可能になる。これが、駆動補償である。

40

#### 【0026】

フレーム2Fでは、目標値である入力画像データはFi=63と最大階調レベルである。従って、表示駆動データFoは、最大階調の駆動電圧レベル「63」に設定される。図2(A)に示される通り、フレーム1Fでは液晶層の透過率Tは目標値の入力画像データの階調

50

値まで達せず，差分  $p$ だけ低い透過率  $T$  に達する。更に，フレーム2Fでも，目標値まで達せずに，差分  $p$ だけ低い透過率  $T$  に達する。

#### 【0027】

次に，フレーム3Fでは，目標値である入力画像データは  $F_i = 0$  と最小階調レベルである。この場合も，表示駆動データ  $F_o$  には補正值を加えることができず，最小階調の駆動電圧 = 0 に設定される。その結果，フレーム3Fの期間内では，液晶層の透過率は最小階調に達することなく，最小階調レベルより差分  $p$ だけ高いレベルにしかならない。

#### 【0028】

次に，フレーム4Fでは，目標値である入力画像データは  $F_i = 32$  である。この場合の表示駆動レベル  $F_o$  は，入力画像データ  $F_i$  のレベルより補正值  $o$ だけ高く設定される。

しかし，フレーム1Fのようにその前のフレームでの液晶層の状態（透過率  $T = 0$ ）から透過率  $T = 32$  に変化する場合とは異なり，フレーム4Fでは透過率  $T = 16$  から透過率 = 32への変化と変化が少ない。従って，フレーム4Fでの補正值  $o$ は，フレーム1Fでの補正值  $o$ よりも小さく設定される。

#### 【0029】

以上の様に，駆動補償方式によれば，液晶駆動電圧に対応する表示駆動データ  $F_o$  が，前フレームの入力画像データ  $F_i$  と現フレームの入力画像データ  $F_i$ との関係にしたがって設定される。両者の差が大きければそれに対応して補正值  $o$ が現フレームの入力画像データ  $F_i$ に加えられる。

#### 【0030】

更に，応答特性が遅い液晶層の場合は，上記のように駆動レベルに補正值を加えても1フレーム期間内に目標値の入力画像データ  $F_i$  のレベルに達しない場合がある。その場合は，前フレームの入力画像データ  $F_i$  の代わりに，前フレームの駆動後の液晶状態（透過率  $T$ ）のデータ  $F_p$  を利用する。即ち，前フレームの駆動後状態データ  $F_p$  と現フレームの入力画像データ  $F_i$  とにしたがって，現フレームでの表示駆動データ  $F_o$  が設定され，それにしたがって駆動電圧が生成される。

#### 【0031】

かかる方法を実行するために，駆動後状態データ  $F_p$  を次のフレームの表示駆動データ  $F_o$  を算出するために一時的にメモリに格納しておく必要があり，各フレームにおいて，表示駆動データ  $F_o$  と共にそのフレームでの駆動後状態データ  $F_p$  とを求めることが必要になる。この演算が，図1の表示駆動データ生成部12にて行われる。表示駆動データ生成部12は，演算を高速に行うために，参照テーブルとして，補正值変換テーブルと差分値変換テーブルとを有し，変換テーブルROM22内のテーブルデータを内蔵する2つの変換テーブルにそのテーブルデータをダウンロードする。その場合，必要に応じて，温度センサ24からの検出温度や垂直同期信号などの周波数に従って，最適のテーブルデータが選択され，ダウンロードされる。

#### 【0032】

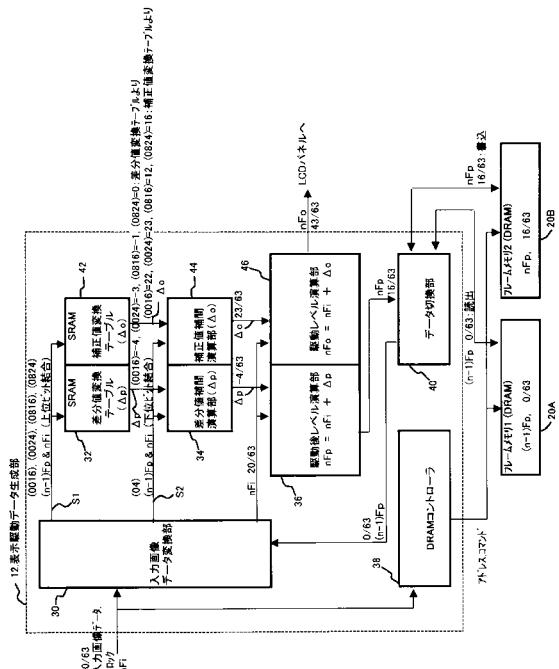

図3は，本実施の形態例における表示駆動データ生成部12の構成図である。図中，現フレーム（n番目）の入力画像データを  $nFi$ ，現フレームの表示画像データを  $nFo$ ，現フレームの駆動後状態データを  $nFp$  とし，更に，前フレーム（n-1番目）のそれぞれのデータを  $(n-1)Fi$ ， $(n-1)Fo$ ， $(n-1)Fp$  とする。表示駆動データ生成部12は，駆動補償の為に，駆動レベルの補正值変換テーブル42と駆動後レベルの差分値変換テーブル32とを有する。これらのテーブル42，32は，現フレームの入力画像データ  $nFi$  と前フレームの駆動後状態データ  $(n-1)Fp$  との組合せに対応して，補正值と差分値とを有する。

#### 【0033】

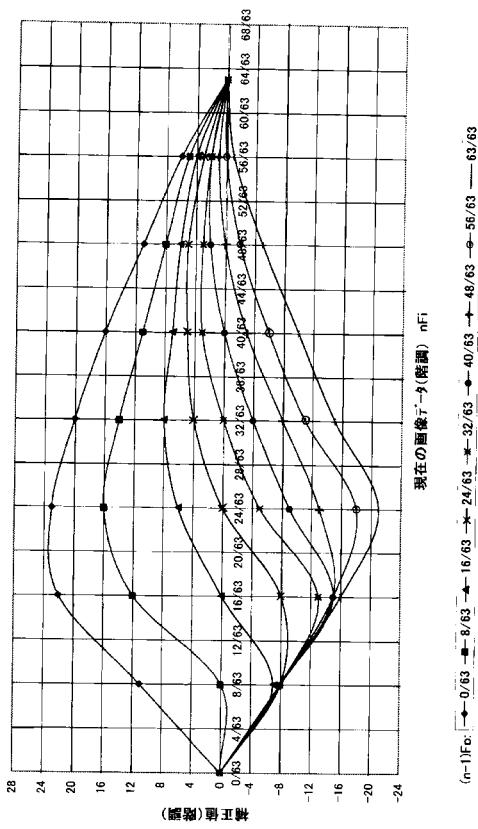

図4は，補正值変換テーブルの一例を示す図である。図示されるとおり，補正值変換テーブルには，前フレームの駆動後状態データ  $(n-1)Fp$  と現フレームの入力画像データ  $nFi$  との組合せに対する駆動レベルの補正值  $o$ が格納されている。この例では，前フレームの駆動後状態データ  $(n-1)Fp$  と現フレームの入力画像データ  $nFi$  は，共に64階調（6ビット）のデータである。

10

20

30

40

50

**【 0 0 3 4 】**

例えば、前フレームの駆動後状態データ $(n-1)F_p$ が $0/63$ （63階調のレベル0）に対して、現フレームの入力画像データ $nF_i$ が $8/63$ （63階調のレベル8）であれば、補正值 $o = 11$ である。従って、入力画像データ $nF_i$ に補正值 $o$ を加えたレベルが表示駆動データ $nF_o = 19/63$ になる。同様に、現フレームの画像データ $nF_i$ が $32/63$ であれば、補正值 $o = 20$ となり、表示駆動データ $nF_o = nF_i + o = 32 + 20 = 52/63$ となる。

**【 0 0 3 5 】**

逆に、前フレームの駆動後状態データ $(n-1)F_p$ が $63/63$ と最高レベルの場合は、逆に補正值 $o$ はマイナス値となり、表示駆動データ $nF_o$ は、入力画像データ $nF_i$ よりも補正值 $o$ だけ高いレベルになる。また、前フレームの駆動後状態データ $(n-1)F_p$ が $32/63$ の場合は、現フレームの画像データ $nF_i$ が $32/63$ より低ければ、補正值 $o$ はマイナス、 $32/63$ より高ければプラスになっている。10

**【 0 0 3 6 】**

尚、現フレームの画像データ $nF_i$ が $0/63$ と $63/63$ の最小レベル、最大レベルの時は、それぞれ補正值を加えることができず、表示駆動データ $nF_o$ は入力画像データ $nF_i$ そのままのレベルになる。

**【 0 0 3 7 】**

図5は、差分値変換テーブルの一例を示す図である。このテーブルは、前フレームの駆動後状態データ $(n-1)F_p$ と現フレームの入力画像データ $nF_i$ との組合せに対する駆動レベルの差分値 $p$ が格納されている。この例でも、前フレームの駆動後状態データ $(n-1)F_p$ と現フレームの入力画像データ $nF_i$ とは、共に64階調（6ビット）のデータである。20

**【 0 0 3 8 】**

これに示されるとおり、現フレームの画像データ $nF_i$ が $0/63$ の場合は、前フレームの駆動後状態データ $(n-1)F_p$ のレベルが高いほど、差分値 $p$ が大きくなり、現フレームの駆動後状態のレベルは、目標値に満たないレベルになる。つまり、図2(A)のフレーム2Fから3Fに移行した状態である。逆に、現フレームの画像データ $nF_i$ が $63/63$ の場合は、前フレームの駆動後状態データ $(n-1)F_p$ のレベルが低いほど、差分値 $p$ が大きくなり、現フレームの駆動後状態のレベルは、目標値に満たないレベルになる。

**【 0 0 3 9 】**

図6は、補正值変換テーブルのグラフを示す図である。このグラフは、図4の補正值変換テーブルの補正值 $o$ を縦軸に、現フレームの画像データ $nF_i$ を横軸にとって、9種類の前フレームの駆動後データ $(n-1)F_p$ に対する補正值をプロットしたものである。このグラフにより、補正值の設定が容易に理解できる。30

**【 0 0 4 0 】**

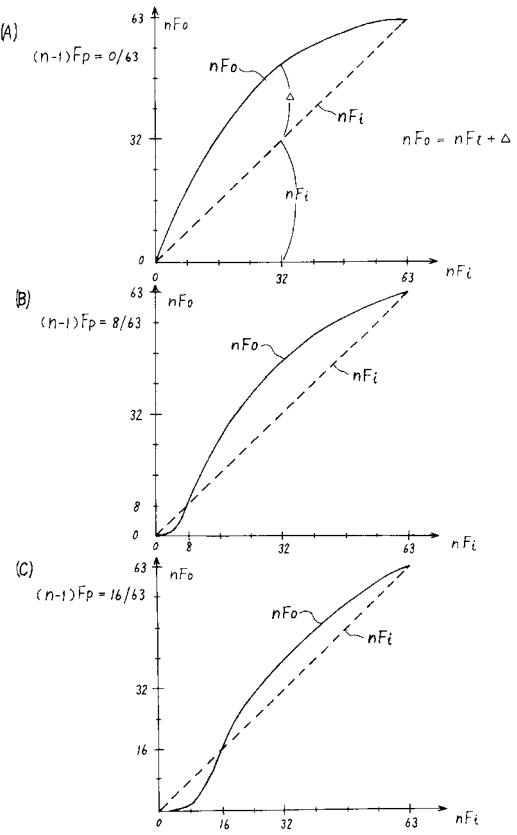

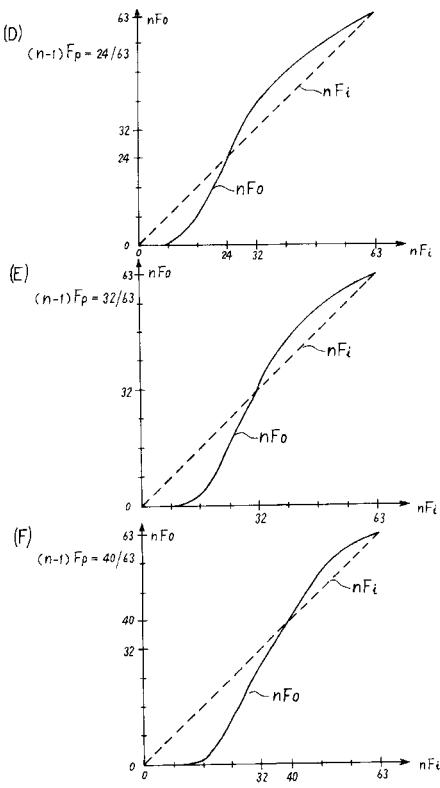

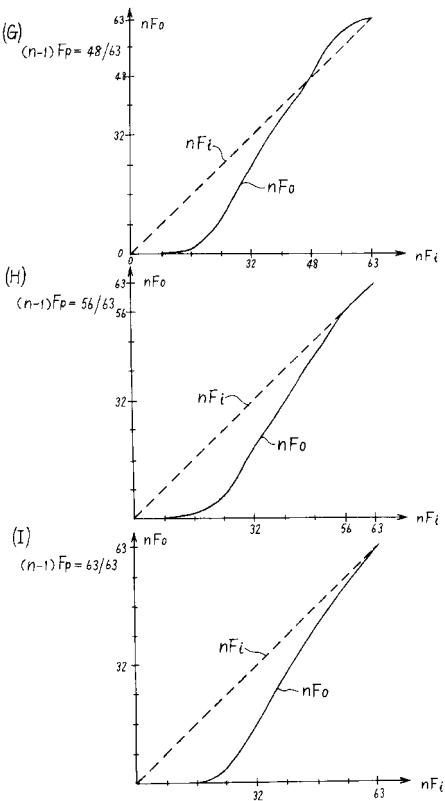

図7～9は、図6の補正值を現フレームの画像データ $nF_i$ に加算して求められる表示駆動データ $nF_o$ を示す図である。つまり、図7～9の破線が現フレームの画像データ $nF_i$ を示し、実線が現フレームの表示駆動データ $nF_o$ をそれぞれ示す。図7中(A)に示される通り、前フレームの $0/63$ レベルから現フレーム画像データ $nF_i$ を表示するためには、表示駆動データ生成部12にて、実線で示したような駆動レベル $nF_o$ が生成される。この場合、補正值 $o$ は常にプラスである。逆に、図9中(I)に示される通り、前フレームの $63/63$ レベルから現フレーム画像データ $nF_i$ を表示するためには、実線で示したような駆動レベル $nF_o$ が生成される。40

**【 0 0 4 1 】**

図3に戻り、表示駆動データ生成部12の構成を更に説明する。表示駆動データ生成部12は、入力画像データ $nF_i$ とドットクロックCCLKを受信し、変換テーブル32、42を参照するための前フレームの駆動後状態データと現フレームの画像データの組合せ信号S1を生成する入力画像データ変換部30を有する。更に、表示駆動データ生成部12には、補正值変換テーブル42と差分値変換テーブル32と、それらの変換テーブルから読み出した補正值 $o$ と差分値 $p$ とを補間演算によって高精度の補正值 $o$ と差分値 $p$ とを求める補間演算部34、44と、更に、現フレーム画像データ $nF_i$ に補正值 $o$ と差分値 $p$ と

を加算する演算部 3 6 , 4 6 を有する。そして、DRAMコントローラ 3 8 は、2つのフレームメモリ20A, 20Bに対して読み出し、書き込みのコマンドと、アドレスを供給し、データ切換部 4 0 は、2つのフレームメモリ20A, 20Bの切換を行う。

#### 【 0 0 4 2 】

フレームメモリ20A, 20Bは、一方に前フレームの駆動後状態データ $(n-1)Fp$ を格納し、他方に現フレームの駆動後状態データ $nFp$ を格納する。そして、表示駆動データを生成するときは、メモリコントローラ 3 8 により、前フレームの駆動後状態データ $(n-1)Fp$ が一方のフレームメモリから読み出されて、入力画像データ変換部 3 0 に供給され、演算部 3 6 により求められた現フレームの駆動後状態データ $nFp$ が他方のフレームメモリに書き込まれる。

10

#### 【 0 0 4 3 】

本実施の形態例では、補正值変換テーブル 4 2 と差分値変換テーブル 3 2 が格納されるSRAMの容量を減らすために、参照のための組合せデータ S 1 は、前フレームの駆動後データ $(n-1)Fp$ と現フレーム画像データ $nFi$ のそれぞれ上位ビットの組合せになっている。例えばそれぞれのデータ $(n-1)Fp$ ,  $nFi$ が 6 ビット（64階調）とすると、ここでの例では、上位 3 ビットの組合せが参照データになる。その場合は、図 4 に示した通り、補正值変換テーブル 4 2 は、 $8 \times 8 = 64$  個の補正值  $o$  が格納されることになる。同様に、差分値変換テーブル 3 2 も、図 5 に示した通り  $8 \times 8 = 64$  個の差分値  $p$  が格納される。従って、64 階調の前フレームの駆動後データ $(n-1)Fp$ と現フレーム画像データ $nFi$ の組合せ（=  $64 \times 64 = 4096$  個）による場合と、変換テーブル 3 2 , 4 2 に使用されるSRAMの容量が 64 分の 1 に小さくすることができる。

20

#### 【 0 0 4 4 】

上記のように、変換テーブル 4 2 , 3 2 の容量を小さくしたことに伴い、それぞれの変換テーブルから読み出される補正值  $o$  と差分値  $p$  は、精度が落ちている。そこで、表示駆動データ生成部 1 2 は、前フレームの駆動後データ $(n-1)Fp$ と現フレーム画像データ $nFi$ それぞれの下位ビットの組合せに従って、補間演算を行う補正值補間演算部 4 4 と差分値補正演算部 3 4 とを有する。この補間演算部 3 4 , 4 4 には、入力画像データ変換部 3 0 から、前フレームの駆動後データ $(n-1)Fp$ と現フレーム画像データ $nFi$ それぞれの下位 3 ビットの組合せ S 2 が供給され、変換テーブル 3 2 , 4 2 の格子点の間のデータに対する補正值と差分値とが直線補間ににより求められる。

30

#### 【 0 0 4 5 】

そして、補間演算部 4 4 , 3 4 で求められた補正值  $o$  と差分値  $p$  を、現フレーム画像データ $nFi$ に加算する駆動レベル演算部 4 6 と、駆動後データ演算部 3 6 とを有する。駆動レベル演算部 4 6 は、図中に示された計算式によって、現フレームの表示駆動データ $nF$  $o$  を求め、液晶パネル側に出力する。また、駆動後レベル演算部 3 6 は、図中に示された計算式によって、現フレームの駆動後データ $nFp$  を求め、データ切換部 4 0 を介して、一方のフレームメモリ20Bに書き込む。書き込まれた駆動後データ $nFp$  は、次の $(n+1)$  番目のフレームでは、前フレームの駆動後データとして読み出され、入力画像データ変換部 3 0 に供給され、 $(n+1)$  番目のフレームでの表示駆動データと駆動後データの生成に利用される。

40

#### 【 0 0 4 6 】

一方のフレームメモリ20Bには、駆動後データ $nFp$  の上位ビットのみが書き込まれても良い。その場合は、その駆動後データの上位ビットは、変換テーブル 3 2 , 4 2 への上位ビット結合信号 S 1 に含められるが、補間演算部 3 4 , 4 4 への下位ビット結合信号 S 2 には含められない。従って、その場合は、補間演算部 3 4 , 4 4 は、現フレームの画像データ $nFi$  の下位ビットのみに従って補間演算を行う。

#### 【 0 0 4 7 】

今仮に、前フレーム $(n-1)F$ で駆動後の状態が透明度  $T = 0/63$  の状態から、次のフレーム 1F で入力画像データ $nFi$  が  $20/63$  の場合について、表示駆動データ生成部 1 2 の動作説明を行う。

50

## 【0048】

最初の状態として、第1のフレームメモリ20Aには、6ビットの前フレームの駆動後データ $(n-1)Fp = 0/63$ が格納されている。そこで、6ビットの入力画像データ $nFi = 20/63$ が入力される。DRAMコントローラ38は、第1のフレームメモリ20Aから前フレームの駆動後データ $(n-1)Fp = 0/63$ を読み出し、そのデータは、データ切換部40を介して、入力画像データ変換部30に供給される。入力画像データ変換部30は、現フレームの画像データ $nFi$ と、前フレームの駆動後データ $(n-1)Fp$ とから、変換テーブル32、42を参照するための上位ビット結合データS1を生成する。この場合、図4の変換テーブルに示されるとおり、 $nFi = 20/63$ 、 $(n-1)Fp = 0/63$ に対して、これらの組合せに対応する変換テーブル上の格子点には補正值、差分値データがないので、その格子点に隣接する複数の格子点、例えば4点のデータを読み出す必要がある。そこで、 $nFi = 20/63$ 、 $(n-1)Fp = 0/63$ に対して、入力画像データ変換部30は、上位ビット結合データS1として、図示されるとおり、 $(n-1)Fp \& nFi = (00, 16), (00, 24), (08, 16), (08, 24)$

を生成する。この上位ビット結合データは、説明の都合上64階調のデータで表記しているが、実際にはそれぞれ3ビット(8階調)のデータを結合したものである。

## 【0049】

この上位ビット結合データS1に対応して、補正值変換テーブル42と差分値変換テーブル32から、次の補正值oと差分値pが読み出される。

$$o : (00, 16) = 22, (00, 24) = 23, (08, 16) = 12, (08, 24) = 16$$

$$p : (00, 16) = -4, (00, 24) = -3, (08, 16) = -1, (08, 24) = 0$$

次に、補間演算部44、34が、これらの4点の補正值と差分値から、 $nFi = 20/63$ 、 $(n-1)Fp = 0/63$ に対応する高精度の補正值と差分値を補間演算により求める。そのために入力画像データ変換部30は、 $nFi = 20/63$ 、 $(n-1)Fp = 0/63$ の下位ビット結合データS2を生成して、補間演算部44、34に供給する。即ち、下位ビット結合データS2は、図示されるとおり、

$$(n-1)Fp \& nFi = (0, 4)$$

となる。その結果、補正值補間演算部44は、

$$o = [ [ \{ 22 \times (8-4) + 23 \times 4 \} / 8 ] \times (8-0) + [ \{ 12 \times (8-4) + 16 \times 4 \} / 8 ] \times 0 ] \div 8 = 22 \\ .5 \quad 23$$

$$p = [ [ \{ (-4) \times (8-4) + (-3) \times 4 \} / 8 ] \times (8-0) + [ \{ (-1) \times (8-4) + 0 \times 4 \} / 8 ] \times 0 ] \div 8 = -3.5 \quad -4$$

をそれぞれ算出する。この補間演算は、直線補間演算により行われている。

## 【0050】

次に、駆動レベル演算部46は、補正值 $o = 23/63$ と現フレームの画像データ $nFi = 20/63$ を加算して、表示駆動データ $nFo = 43/63$ を算出する。同様に、駆動後レベル演算部36は、差分値 $p = -4/63$ と現フレームの画像データ $nFi = 20/63$ を加算して、駆動後状態データ $(n-1)Fp = 16/63$ を算出する。表示駆動データ $nFo$ は、図1のタイミングコントローラ14に供給され、ソースドライバ16により駆動電圧に変換される。また、駆動後状態データ $(n-1)Fp$ は、第2のフレームメモリ20Bに書き込まれる。

## 【0051】

以上の通り、駆動補償方式を採用するために入力画像データを表示駆動データに変換するための変換テーブル42の容量を、参照データの低ビット化により小さくしたので、それに対応して、補間演算部44を設けて、精度の低下を防止している。

## 【0052】

更に、変換テーブル42に格納されるデータを、表示駆動データそのものではなく、入力画像データに対する補正值oにしている。補正值であれば、図4に示されるとおり、必要な階調数が小さくなるので、変換テーブル内に格納されるデータのビット数も小さくすることができる。それにより、変換テーブルのSRAMの容量を更に小さくすることができる。もちろん、変換テーブル42内のデータを表示駆動データ(入力画像データに補正值を加えたデータ)にすることもできる。その場合は、駆動レベル演算部46は不要になる。

10

20

30

40

50

変換テーブル42内のデータを補正值にするか表示駆動データにするかは、変換テーブルのSRAMの容量を減らす効果と駆動レベル演算部を設ける効果との比較により決定される。

#### 【0053】

液晶層の応答特性が遅い場合は、前述のとおり、駆動補償してもフレーム期間内に目標の透明度に達しない場合がある。その場合は、液晶層を駆動した後の透明度の状態を考慮する必要がある。のために、本実施の形態例では、差分値変換テーブル32を設け、その補間演算部34を設けた。この差分値変換テーブル32も参照データのビット数を少なくして、テーブルの容量を減らしている。また、差分値変換テーブル32内のデータを、差分値ではなく、駆動後状態データnFpそのものを格納する場合は、駆動後レベル演算部36は、不要になる。

10

#### 【0054】

変換テーブル32についても、差分値ではなく、駆動後状態データを格納することができる。その場合は、駆動後レベル演算部36は不要になる。

#### 【0055】

表示駆動データ生成部12は、好ましい実施例では、ASICにより構成される。変換テーブル42、32を構成するSRAMの容量を減らすことにより、SRAMに必要な周辺回路のゲート数を大幅に減らすことができ、SRAM用のゲート数を節約することができる。

#### 【0056】

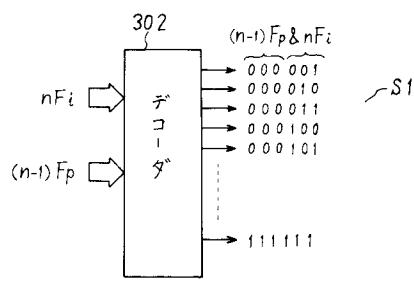

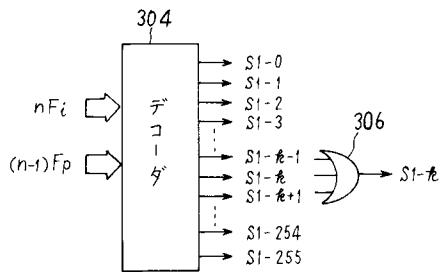

図10は、入力画像データ変換部30の構成例を示す図である。入力画像データ変換部30内には、デコーダ302が設けられ、そのデコーダ302により、入力画像データnFiと前フレームの駆動後データ(n-1)Fpとから、参照すべき変換テーブル42のアドレスとして、結合データS1((n-1)Fp&nFi)が生成される。

20

#### 【0057】

図11は、入力画像データ変換部30の別の構成例を示す図である。この例では、デコーダ304が、6ビットの入力画像データnFiと6ビットの駆動後データ(n-1)Fpとから、8ビット(256階調)の出力を生成する。更に、256本の出力S1-0~S1-255のうち、補正值0や差分値pの変動が少ない領域の複数の出力を束ねる論理和ゲート306を有する。つまり、変換テーブルのデータの変化が大きい領域では、分解能を高くしてデータを格納し、変化が少ない領域では、間引いて分解能を粗くしてデータを格納する。それにより、変換テーブルの容量を小さくすることができると共に、生成される補正值や差分値の精度を上げることができる。

30

#### 【0058】

##### [第2の実施の形態例]

液晶表示装置の駆動方法として、画像の動画特性を改善するために、CR駆動が提案されている。CR(Charge and Reset)駆動では、フレーム期間の前半で画素電極に駆動電圧を印加して、後半で駆動電圧をゼロにすることで、フレーム期間の一定部分を黒表示する。それにより、動画の動きがなめらかに見えることが報告されている。一般に、デューティ比が50%以下になるように設定され、従って、CR駆動を行うためには、液晶層が高速応答可能であることが条件になる。フレーム期間が16msの場合は、8ms未満の応答速度が必要になり、適用される液晶層の材料に限りがある。

40

#### 【0059】

第2の実施の形態例では、このCR駆動を応答速度が20ms程度の中速の液晶層にも適用できるようにするために、CR駆動に駆動補償方式を採用する。即ち、前フレームの駆動後データと現フレームの画像データとから、現フレームの表示駆動データを求めてパネルドライバに供給すると共に、前フレームの駆動後データと現フレームの画像データとから、現フレームの駆動後データを求めて、フレームメモリに格納する。それぞれの演算には、変換テーブルを参照することで高速化を図る。より好ましくは、この変換テーブルを参照するためのデータを低ビット化して、変換テーブルの容量を減らす。

#### 【0060】

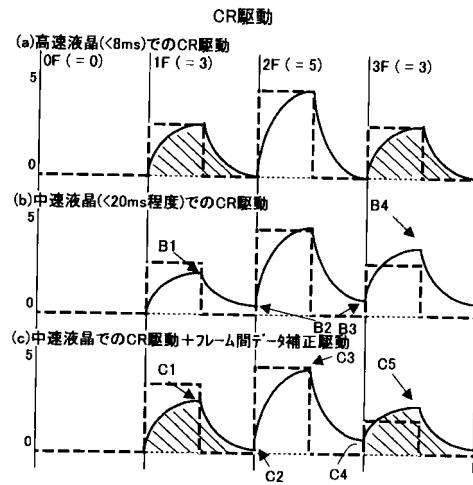

図12は、本実施の形態例におけるCR駆動を説明するための図である。図12(a)は

50

、高速応答の液晶層を利用した場合の C R 駆動波形（破線）と液晶透過率の変化を示す図である。この例では、簡単のために 5 階調の表示画像データとする。最初のフレーム 0F では、表示画像データが 0 であり、その後のフレーム 1F, 2F, 3F では表示画像データが 3, 5, 3 と変化したとする。フレーム 1F の前半に、表示画像データ「3」に対応する駆動パルスが印加され、後半は駆動電圧ゼロにリセットされる。それに伴い、液晶層の透過率は、前半で目標の透過率に達して、後半で透過率ゼロ（黒色）に戻る。フレーム 2F, 3F でも同じである。高速応答特性を有するので、フレーム期間の半分で目標透過率に達することができ、残りの半分で透過率ゼロに戻ることができる。

#### 【 0 0 6 1 】

図 12 ( b ) は、中速応答特性の液晶層を利用した場合の C R 駆動波形と液晶透過率の変化を示す。この例でも、フレーム 0F, 1F, 2F, 3F で、入力画像データが 0, 3, 5, 3 と変化している。フレーム 1F では、フレーム期間前半の駆動パルスでは、液晶層が十分に応答を完了することができずに、応答不足 B 1 が発生し、フレーム期間の後半のリセットパルスでも、液晶層が十分にリセットを完了することができずに、応答不足 B 2 が発生している。そして、フレーム 2F では、駆動レベルが最大の「5」であったため、リセット時には大きな応答残り B 3 が発生している。この駆動後状態 B 3 から、次のフレーム 3F にて画像データ「3」に対応する駆動パルスを印加すると、今度は、過剰応答 B 4 を招いてしまう。

#### 【 0 0 6 2 】

このように、C R 駆動方式は、1 フレームの期間内に、目標の透過率にする駆動電圧印加期間と放電期間とが設けられ、中速応答特性の液晶層では、応答不足や過剰応答が発生する。

#### 【 0 0 6 3 】

そこで、本実施の形態例では、図 12 ( c ) に示されるとおり、駆動レベルを、前フレームのリセット後の液晶状態（駆動後データ）と現フレームの画像データとから、現フレームでの駆動レベルとリセット後の液晶状態を示す駆動後データとを生成する。図の例では、フレーム 1F にて、入力画像データが「3」のところ、表示駆動レベルは「4」に設定されている。その結果、駆動パルス終了までに液晶の透過率は目標値まで達している（図中 C 1）。但し、リセット終了時は応答残りが発生し（図中 C 2），完全に黒の状態にはなっていない。そして、フレーム 3F のリセット終了時の応答残り（図中 C 4）により、フレーム 4F での駆動レベルは、入力画像データが「3」にもかかわらず、駆動レベルは目標値よりも低く設定される。その結果、駆動パルス終了時において、過剰な応答は発生していない（図中 C 5）。

#### 【 0 0 6 4 】

第 2 の実施の形態例では、C R 駆動を行うために、図 3 に示した表示駆動データ生成部 12 を有する。表示駆動データ生成部 12 において、C R 駆動の場合は、補正值変換テーブル 42, 补正值補間演算部 44, 駆動レベル演算部 46 は、最初の実施の形態例と同じである。第 2 の実施の形態例では、差分値変換テーブル 32 には、リセット終了時の応答残りデータが格納され応答残りデータが出力される。そして、補間演算部 34 により精度の高い応答残りデータが生成される。この応答残りデータは、一種の駆動後状態データ Fp である。

#### 【 0 0 6 5 】

そして、第 2 の実施の形態例では、駆動後レベル演算部 36 は不要であり、補間演算部 34 により求められた応答残りデータ（駆動後状態データ）が、フレームメモリ 20A, 20B のいずれか一方に格納され、次のフレームの表示駆動データを求めるために利用される。

#### 【 0 0 6 6 】

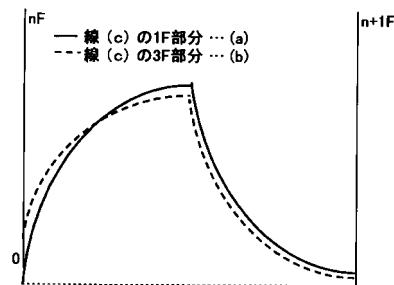

図 12 に示されるとおり、C R 駆動方式において駆動補償方式を採用すると、同じ表示画像データ「3」の場合でも、フレーム 1F と 3F とでは、駆動パルスも異なり、それに応答する液晶層の透過率の変化も異なる。図 13 は、同じ表示画像データを駆動した時の液晶層の光学応答を詳細に示す波形図である。図中、実線が図 12 ( c ) のフレーム 1F の光学応

10

20

30

40

50

答波形，破線がフレーム3Fの光学応答波形である。

#### 【0067】

このように，同じ表示画像データであっても，画素の履歴に応じて液晶層の光学応答波形が異なる。かかる現象は，隣接する画素において同一の階調レベルの画像データが供給された場合，画素毎に透過率が異なり，擬似輪郭の原因になる。

#### 【0068】

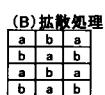

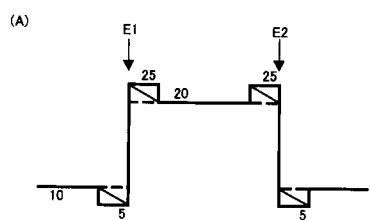

図14は，擬似輪郭と拡散処理を説明するための図である。図14(A)は，4行3列の画素領域が示されている。そして，上の6画素は，図13の実線の光学応答(a)で表示され，下の6画素は，同図破線の光学応答(b)で表示されているとする。この場合，光学応答の違いにより2グループの画素領域の境界部分に擬似輪郭が発生する。かかる擬似輪郭は画質の低下を招く。10

#### 【0069】

そこで，本実施の形態例では，図14(B)に示されるとおり，同じ入力画像データであっても，隣接する画素間で階調レベルを一定の微少値だけ上下する拡散処理を行う。特に，この拡散処理は，光学応答が異なる境界部分で行うことが好ましい。拡散処理を行うためには，隣接する画素の入力画像レベルを比較して，同じであれば，ランダムに或いは一定の規則のもとに表示駆動データのレベルを微少値だけプラス・マイナス処理する。それにより，擬似輪郭がはっきりと現れることを防止することができる。

#### 【0070】

この拡散処理を行うことに伴い，表示すべき画像の輪郭がぼけることが予想される。従つて，好ましい実施の形態例では，拡散処理を行うことに対応して，エッジフィルタを設けて，画像の輪郭部分のエッジを強調する処理を行う。20

#### 【0071】

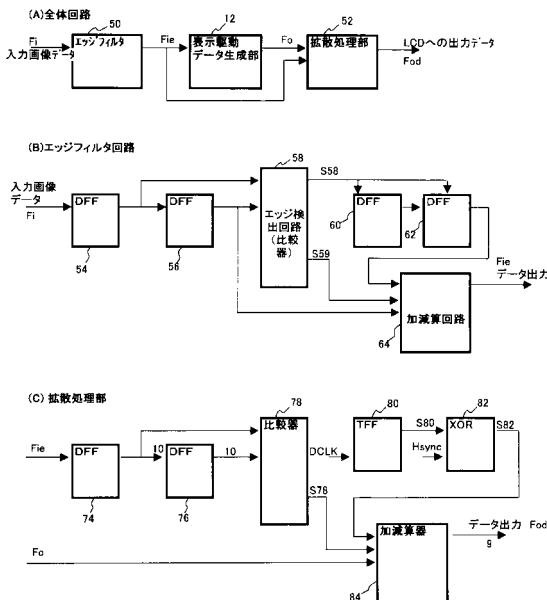

図15は，エッジフィルタと拡散処理部とを設けた制御回路図である。図15(A)は制御回路の全体回路を，図15(B)はエッジフィルタを，図15(C)は拡散処理部をそれぞれ示す。また，図16は，エッジフィルタと拡散処理部により処理されたデータを示す図である。両図を参照して，エッジフィルタと拡散処理について説明する。

#### 【0072】

エッジフィルタ50は，表示駆動データ生成部12の前段に設けられ，入力画像データFiの階調レベルが大きく変化するのを検出して，変化の前後のレベルを強調する処理を行う。また，拡散処理部52は，表示駆動データ生成部12の後段に設けられ，生成される駆動データFoに対して，同一の入力画像データFiのレベルを有する隣接する画素を検出して，それらの画素の表示駆動レベルFoを微少値だけプラス・マイナスする。30

#### 【0073】

図15(B)のエッジフィルタ回路は，入力画像データFiをシフトする遅延フリップフロップ54，56と，両フリップフロップの出力を比較するエッジ検出回路58と，エッジ検出回路からの加減算指令ビットS58をシフトする遅延フリップフロップ60，62と，エッジ検出回路からのエッジ検出信号S59と加減算指令ビットS58とにより，入力画像データFiに強調レベルを加減算する加減算回路64とを有する。

#### 【0074】

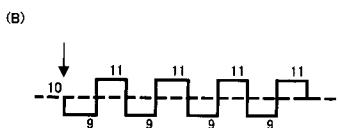

例として，図16(A)に示されるとおり，入力画像データが階調レベル「10」「20」「10」と変化したとする。エッジE1とE2で階調レベルが大きく異なっているので，このタイミングが画像のエッジであることがエッジ検出回路58により検出される。入力画像データのレベルが低いレベルから高いレベルに変化したことで，エッジ検出回路58は，エッジ検出信号S59を活性化レベルにすると共に，それに同期して加減算指令ビットS58を，順にマイナス「0」，プラス「1」にする。これらの加減算指令ビットS58が遅延フリップフロップ60，62でシフトされ，加減算回路64に供給される。40

#### 【0075】

加減算回路64では，エッジ直前の入力画像データ「10」から所定値「5」をマイナスし，エッジ直後の入力画像データ「20」に所定値「5」をプラスして，エッジ強調済み50

の画像データFieを出力する。

**【0076】**

同様に、エッジE2のタイミングでは、階調レベルが高いレベルから低いレベルに変化しているので、エッジ検出回路58は、加減算指令ビットS58を順にプラス「1」、マイナス「0」にする。その結果、加減算回路64では、エッジ直前の入力画像データ「20」から所定値「5」をプラスし、エッジ直後の入力画像データ「10」から所定値「5」をマイナスして、エッジ強調済みの画像データFieを出力する。

**【0077】**

次に、図15(C)の拡散処理回路について、図16(B)の波形図を参照して説明する。

拡散処理回路は、入力画像データFieをシフトする遅延フリップフロップ74, 76と

、それらの出力を比較して同じ階調レベルか否かを検出する比較器78と、ドットクロックDCLKに同期して出力を「0」「1」にトグルするT型フリップフロップ80と、水平同期信号Hsyncに同期してフリップフロップ80の出力S80を反転して加減算器に加減指令ビットS82を出力する排他的論理回路82と、比較器78からの検出信号S78に同期して加減指令ビットS82にしたがって駆動データFoに微少値を加減算する加減算器84とを有する。

10

**【0078】**

図16(B)に示されるとおり、入力画像データの階調レベルが「10」と一定の場合に、比較器78がそれを検出し、加減算器84が微少値「1」を画素毎にプラス・マイナスする。次の表示ラインでは、加減指令ビットS82が逆のパターンに反転される。従って、加減算器84は微少値「1」を画素毎にマイナス・プラスする。その結果、拡散処理された駆動データFodは、図14(B)のように階調レベルが拡散したレベルになる。

20

**【0079】**

図1に戻り、本実施の形態例の液晶表示装置の制御回路には、温度センサ24を有する。温度センサ24は、使用状態での温度を検出して、変換テーブルROMから最適な変換テーブルをダウンロードするために利用される。表示駆動データ生成部12は、垂直同期信号をカウントして、一定周期毎に、温度センサからの温度情報にしたがって、それに対応する最適の変換テーブルをROMからダウンロードして、内蔵するSRAMに展開する。それにより、駆動補償された駆動データnFoは、周囲環境の変化による液晶材料の応答特性を考慮した最適の変換テーブルから求められる。

30

**【0080】**

具体的には、検出温度が高いほど、液晶層の応答速度が速くなるので、補正值変換テーブル内の補正值の絶対値は、比較的低いレベルになる。また、検出温度が低いほど、液晶層の応答速度が遅くなるので、補正值変換テーブル内の補正值の絶対値は、比較的高いレベルになる。

**【0081】**

更に、表示駆動データ生成部12は、垂直同期信号Vsyncの周波数fを監視する。そして、検出される周波数に応じて、最適の変換テーブルをROMからダウンロードして、内蔵するSRAM内に展開する。例えば、周波数fが高い時は、フレーム期間が短くなるので、変換テーブル内の補正值の絶対値は、比較的高くなる。また、逆に周波数fが低い時は、フレーム期間が長くなるので、変換テーブル内の補正值の絶対値は、比較的短くなる。

40

**【0082】**

以上、実施の形態例をまとめると以下の付記の通りである。

**【0083】**

(付記1)液晶表示装置の制御回路において、

現フレームの画像データと前フレームの画像データとから表示用駆動データを生成する表示駆動データ生成部を有し、

当該表示駆動データ生成部は、前記現フレームの画像データ及び前フレームの画像データの組合せに対応して表示用駆動データまたはその補正值を格納した変換テーブルを有し、前記変換テーブルは、前記現フレーム画像データの上位ビットと前フレーム画像データの

50

上位ビットの組合せに対応して前記表示用駆動データまたはその補正值を格納して，更に，前記表示駆動データ生成部は，前記現フレーム画像データの下位ビットにしたがって，前記補正值変換テーブルから読み出した複数の隣接する表示用駆動データまたはその補正值から，補間演算により当該下位ビットに対応して補間された表示用駆動データまたはその補正值を求める補間演算部とを有することを特徴とする液晶表示装置の制御回路。

#### 【0084】

(付記2)付記1において，

前記変換テーブルは，前記現フレーム画像データの上位ビットと前フレーム画像データの上位ビットの組合せについて，所定の範囲でグループ化され，当該グループ化された単位に対応して，前記表示用駆動データまたはその補正值が格納されることを特徴とする液晶表示装置の制御回路。

10

#### 【0085】

(付記3)液晶表示装置の制御回路において，

現フレームの画像データと前フレームの駆動後状態データとから表示用駆動データを生成する表示駆動データ生成部を有し，

当該表示駆動データ生成部は，前記現フレームの画像データ及び前フレームの駆動後状態データの組合せに対応して表示用駆動データまたはその補正值を格納した第1の変換テーブルを有し，

更に，前記表示駆動データ生成部は，前記現フレームの画像データ及び前フレームの駆動後状態データとから現フレームの駆動後状態データを生成する駆動後状態データ生成部を有し，

当該駆動後状態データ生成部は，前記現フレームの画像データの上位ビットと前フレームの駆動後状態データの上位ビットの組合せに対応して現フレームの駆動後状態データまたはその差分値を格納した第2の変換テーブルと，

前記現フレーム画像データの下位ビットにしたがって，前記第2の変換テーブルから読み出した隣接する複数の駆動後状態データまたはその差分値から，補間演算により当該下位ビットに対応する補間された駆動後状態データまたはその差分値を求める第1の補間演算部とを有し，

前記駆動後状態データは，次のフレームで表示駆動レベルを求めるために，画素に対応して記憶領域を有するフレームメモリ内に一旦格納されることを特徴とする液晶表示装置の制御回路。

30

#### 【0086】

(付記4)付記3において，

前記第1の変換テーブルは，前記現フレーム画像データの上位ビットと前フレームの駆動後状態データの上位ビットとの組合せに対応して，前記表示用駆動データまたはその補正值を格納し，

前記表示駆動データ生成部は，更に，前記現フレーム画像データの下位ビットにしたがって，前記第1の変換テーブルから読み出した複数の隣接する表示用駆動データまたは補正值から，補間演算により当該下位ビットに対応する補間された表示用駆動データまたは補正值を求める第2の補間演算部を有することを特徴とする液晶表示装置の制御回路。

40

#### 【0087】

(付記5)付記3において，

前記第1の変換テーブルは，前記現フレーム画像データの上位ビットと前フレーム画像データの上位ビットの組合せについて，所定の範囲でグループ化され，当該グループ化された単位に対応して，前記表示用駆動データまたはその差分値が格納されることを特徴とする液晶表示装置の制御回路。

#### 【0088】

(付記6)付記1又は3において，

更に，前記第1及び/又は第2の変換テーブルを複数セット格納する変換テーブルメモリと，温度検出手段とを有し，

50

前記表示駆動データ生成部は、所定周期毎に、前記温度検出手段により検出される温度に応じて、前記変換テーブルメモリから変換テーブルをダウンロードすることを特徴とすることを特徴とする液晶表示装置の制御回路。

#### 【0089】

(付記7)付記1又は3において、

前記表示駆動データ生成部は、所定周期毎に、水平同期信号または垂直同期信号の周波数に応じて、前記変換テーブルメモリから変換テーブルをダウンロードすることを特徴とすることを特徴とする液晶表示装置の制御回路。

#### 【0090】

(付記8)フレーム期間の前半で画素電極に駆動電圧を印加して、フレーム期間の後半で前記画素電極に階調値ゼロに対応する駆動電圧を印加するチャージリセット駆動方式の液晶表示装置の制御回路において、10

現フレームの画像データと前フレームの画像データとから表示用駆動データを生成する表示駆動データ生成部を有し、

当該表示駆動データ生成部は、前記現フレーム画像データ及び前フレーム画像データの組合せに対応して前記表示用駆動データまたはその補正值を格納した第1の変換テーブルを有し、

前記第1の変換テーブルから読み出された前記表示用駆動データまたはその補正值にしたがって、前記駆動電圧が求められることを特徴とする液晶表示装置の制御回路。

#### 【0091】

(付記9)フレーム期間の前半で画素電極に駆動電圧を印加して、フレーム期間の後半で前記画素電極に階調値ゼロに対応する駆動電圧を印加するチャージリセット駆動方式の液晶表示装置の制御回路において、20

表示用駆動データを生成する表示駆動データ生成部を有し、

当該表示駆動データ生成部は、現フレーム画像データ及び前フレーム駆動後状態データの組合せに対応して前記表示用駆動データまたはその補正值を格納した第1の変換テーブルと、前記現フレームの画像データと前フレーム駆動後状態データの組合せに対応して現フレームの駆動後状態データを格納した第2の変換テーブルとを有し、

前記第1の変換テーブルから読み出された表示用駆動データまたはその補正值にしたがって、前記駆動電圧が決定され、前記第2の変換テーブルから読み出された駆動後状態データがフレームメモリ内に一旦格納されることを特徴とする液晶表示装置の制御回路。30

#### 【0092】

(付記10)付記8または9において、

更に、同一階調を有する現フレーム画像データが隣接する画素に対して供給された時、当該隣接する画素に対して生成された前記現フレームの表示用駆動データの階調値を、当該隣接する画素間で所定の階調値だけ異なる分散処理部を有することを特徴とする液晶表示装置の制御回路。

#### 【0093】

(付記11)付記8または9において、

更に、階調レベルが異なる現フレーム画像データが隣接する画素に対して供給された時、当該隣接する画素に対する現フレーム画像データの階調レベルをそれぞれ増加・減少、又は減少・増加するエッジフィルタを、前記表示駆動データ生成部の前段に設けることを特徴とする液晶表示装置の制御回路。40

#### 【0094】

(付記12)付記8または9において、

前記第1の変換テーブルは、前記現フレーム画像データの上位ビットと前フレーム画像データの上位ビットの組合せについて、所定の範囲でグループ化され、当該グループ化された単位に対応して、前記表示用駆動データまたはその差分値が格納されることを特徴とする液晶表示装置の制御回路。

#### 【0095】

50

(付記 13) 付記 8 又は 9 において、

更に、前記第 1 及び / 又は第 2 の変換テーブルを複数セット格納する変換テーブルメモリと、温度検出手段とを有し、

前記表示駆動データ生成部は、所定周期毎に、前記温度検出手段により検出される温度に応じて、前記変換テーブルメモリから変換テーブルをダウンロードすることを特徴とすることを特徴とする液晶表示装置の制御回路。

#### 【0096】

(付記 14) 付記 8 又は 9 において、

前記表示駆動データ生成部は、所定周期毎に、水平同期信号または垂直同期信号の周波数に応じて、前記変換テーブルメモリから変換テーブルをダウンロードすることを特徴とすることを特徴とする液晶表示装置の制御回路。 10

#### 【0097】

(付記 15) 付記 1, 3, 8 または 9 のいずれか 1 に記載された制御回路と、前記制御回路により表示制御される液晶表示パネルとを有することを特徴とする液晶表示装置。

#### 【0098】

##### 【発明の効果】

以上、本発明によれば、液晶表示装置の応答特性を改善し、動画表示における画質向上させることができる。

##### 【図面の簡単な説明】

【図 1】 本実施の形態例における液晶表示装置の全体構成図である。 20

【図 2】 駆動補償の原理を説明するための図である。

【図 3】 本実施の形態例における表示駆動データ生成部 12 の構成図である。

【図 4】 補正值変換テーブルの一例を示す図である。

【図 5】 差分値変換テーブルの一例を示す図である。

【図 6】 補正值変換テーブルのグラフを示す図である。

【図 7】 図 6 の補正值を現フレームの画像データ  $nFi$  に加算して求められる表示駆動データ  $nFo$  を示す図である。

【図 8】 図 6 の補正值を現フレームの画像データ  $nFi$  に加算して求められる表示駆動データ  $nFo$  を示す図である。

【図 9】 図 6 の補正值を現フレームの画像データ  $nFi$  に加算して求められる表示駆動データ  $nFo$  を示す図である。 30

【図 10】 入力画像データ変換部 30 の構成例を示す図である。

【図 11】 入力画像データ変換部 30 の別の構成例を示す図である。

【図 12】 本実施の形態例における C R 駆動を説明するための図である。

【図 13】 同じ表示画像データを駆動した時の液晶層の光学応答を詳細に示す波形図である。

【図 14】 擬似輪郭と拡散処理を説明するための図である。

【図 15】 エッジフィルタと拡散処理部とを設けた制御回路図である。

【図 16】 エッジフィルタと拡散処理部により処理されたデータを示す図である。

##### 【符号の説明】

1 0 液晶表示パネル

1 2 表示駆動データ生成部

2 0 フレームメモリ

4 2 第 1 の変換テーブル、補正值変換テーブル

4 4 第 2 の補間演算部、補正值補間演算部

3 2 第 2 の変換テーブル、差分値変換テーブル

3 4 第 1 の補間演算部、差分値補間演算部

40

【図1】

【図2】

【図3】

【図4】

補正値変換テーブル (表示駆動データ  $nF_0 \leq$  入力画像データ  $nF_1 +$  補正値  $\Delta o$ )

| $(n-1)F_p$ | 0/63 | 8/63 | 16/63 | 24/63 | 32/63 | 40/63 | 48/63 | 56/63 | 63/63 |

|------------|------|------|-------|-------|-------|-------|-------|-------|-------|

| 0/63       | -    | 11   | 22    | 23    | 20    | 16    | 11    | 6     | 0     |

| 8/63       | 0    | -    | 12    | 16    | 14    | 11    | 8     | 5     | 0     |

| 16/63      | 0    | -7   | -     | 6     | 8     | 7     | 6     | 4     | 0     |

| 24/63      | 0    | -8   | -8    | -     | 4     | 5     | 5     | 3     | 0     |

| 32/63      | 0    | -8   | -13   | -5    | -     | 3     | 3     | 2     | 0     |

| 40/63      | 0    | -8   | -15   | -9    | -4    | -     | 2     | 2     | 0     |

| 48/63      | 0    | -8   | -15   | -13   | -8    | -3    | -     | 1     | 0     |

| 56/63      | 0    | -8   | -15   | -18   | -11   | -6    | -2    | -     | 0     |

| 63/63      | 0    | -8   | -16   | -21   | -15   | -10   | -5    | -1    | -     |

【図5】

差分値変換テーブル (駆動後データ  $nF_p \leq$  入力画像データ  $nF_1 +$  差分値  $\Delta p$ )

| $(n-1)F_p$ | 0/63 | 8/63 | 16/63 | 24/63 | 32/63 | 40/63 | 48/63 | 56/63 | 63/63 |

|------------|------|------|-------|-------|-------|-------|-------|-------|-------|

| 0/63       | -    | 0    | -4    | -3    | -1    | -1    | 0     | 0     | -7    |

| 8/63       | 0    | -    | -1    | 0     | 0     | 0     | 0     | 0     | -3    |

| 16/63      | 0    | 0    | -     | 0     | 0     | 0     | 0     | 0     | -2    |

| 24/63      | 2    | 0    | 0     | -     | 0     | 0     | 0     | 0     | -1    |

| 32/63      | 4    | 0    | 0     | 0     | -     | 0     | 0     | 0     | -1    |

| 40/63      | 8    | 0    | 0     | 0     | 0     | -     | 0     | 0     | -1    |

| 48/63      | 11   | 4    | 0     | 0     | 0     | 0     | -     | 0     | 0     |

| 56/63      | 14   | 6    | 0     | 0     | 0     | 0     | 0     | -     | 0     |

| 63/63      | 16   | 8    | 0     | 0     | 0     | 0     | 0     | 0     | -     |

【図6】

各階層における補正値(各系列は前フレームのエラーを示す)

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図 16】

---

フロントページの続き

(72)発明者 平木 克良

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 山崎 浩

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 田中 克憲

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 濱本 穎広

(56)参考文献 特開平11-126050(JP,A)

特開2000-338935(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38

G02F 1/133