(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-246404

(P2009-246404A)

(43) 公開日 平成21年10月22日(2009.10.22)

|                        |                    |             |

|------------------------|--------------------|-------------|

| (51) Int.Cl.           | F 1                | テーマコード (参考) |

| HO 1 L 23/12 (2006.01) | HO 1 L 23/12 501 P |             |

| HO 1 L 21/60 (2006.01) | HO 1 L 21/92 602 K |             |

審査請求 有 請求項の数 6 O L (全 16 頁)

|            |                                     |          |                                               |

|------------|-------------------------------------|----------|-----------------------------------------------|

| (21) 出願番号  | 特願2009-177168 (P2009-177168)        | (71) 出願人 | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号    |

| (22) 出願日   | 平成21年7月30日 (2009.7.30)              | (72) 発明者 | 脇坂 伸治<br>東京都青梅市今井3丁目10番6号<br>カシオ計算機株式会社青梅事業所内 |

| (62) 分割の表示 | 特願2003-347798 (P2003-347798)<br>の分割 |          |                                               |

| 原出願日       | 平成15年10月7日 (2003.10.7)              |          |                                               |

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】相対向する一対の導電層を有するコンデンサを備えた半導体装置において、製造工程数を増加することなく、コンデンサを形成する。

【解決手段】半導体構成体2は、保護膜9上に再配線14、下層導電層18、第1の接続配線(図示せず)および第2の接続配線16が同時に形成された構造となっている。そして、下層導電層18は、第1の接続配線を介して、半導体基板4上的一方のコンデンサ用接続パッドに接続されている。半導体構成体2上に設けられた上層絶縁膜24の上面には、上層再配線27、上層導電層32および第3の接続配線28が同時に形成されている。そして、上層導電層32は、第3の接続配線28、第2の接続配線16の接続パッド部上面に設けられた柱状電極21および第2の接続配線16を介して、半導体基板4上の他方のコンデンサ用接続パッド6に接続されている。

【選択図】 図3

## 【特許請求の範囲】

## 【請求項 1】

ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、前記半導体構成体および前記絶縁層上に設けられた少なくとも1層の上層絶縁膜と、前記上層絶縁膜の何れかの層上に前記半導体構成体の再配線の接続パッド部に電気的に接続されて設けられ、外部接続用の接続パッド部を備える少なくとも1層の上層再配線と、相対向する一対の導電層を有し、前記一対の導電層の各々が前記接続パッドに電気的に接続される対向導電層回路素子と、を備えた半導体装置の製造方法において、

前記対向導電層回路素子の少なくとも一方の導電層を前記上層再配線の何れかの層と同一の平面上に前記上層再配線と同一の材料によって同時に形成することを特徴とする半導体装置の製造方法。

## 【請求項 2】

請求項1に記載の発明において、前記対向導電層回路素子の他方の導電層を前記再配線と同一の平面上に前記再配線と同一の材料によって同時に形成することを特徴とする半導体装置の製造方法。

## 【請求項 3】

請求項1に記載の発明において、前記上層絶縁膜は複数層であり、前記上層再配線も複数層であって、前記上層絶縁膜の各層上に層間で互いに接続されて形成され、前記複数層の上層再配線のうちの1層と同一の平面上に前記対向導電層回路素子の一方の導電層を当該1層と同一の材料によって同時に形成し、前記複数層の上層再配線のうちの他の1層と同一の平面上に前記対向導電層回路素子の他方の導電層を当該他の1層と同一の材料によって同時に形成することを特徴とする半導体装置の製造方法。

## 【請求項 4】

請求項1に記載の発明において、前記半導体構成体は、前記再配線に接続された柱状電極と、該柱状電極の上端面を除き、少なくとも前記半導体基板の上面を覆う封止膜と、を有するものであることを特徴とする半導体装置の製造方法。

## 【請求項 5】

請求項1に記載の発明において、前記対向導電層回路素子は容量素子であることを特徴とする半導体装置の製造方法。

## 【請求項 6】

請求項1に記載の発明において、前記対向導電層回路素子はアンテナ素子であることを特徴とする半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は半導体装置の製造方法に関する。

## 【背景技術】

## 【0002】

従来の半導体装置には、集積回路が形成されて接続パッドを有する半導体基板が配線基板に埋め込まれ、接続パッドに接続される外部接続用の端子が配線基板上に形成されるようとしたものがある。また、このような半導体装置において、半導体基板上に2つの端子部を有する薄膜回路素子が設けられ、薄膜回路素子の両端子部が接続パッドに接続されるように構成されたものがある。そして、薄膜回路素子として容量素子やアンテナ素子等の対向電極を備えて構成される対向導電層回路素子を設ける場合、半導体基板状に設けられた第1の絶縁層上に、第1の導電層、第2の絶縁層および第2の導電層を積層して、第1の導電層、第2の絶縁層および第2の導電層により対向導電層回路素子を形成し、各導電層を接続用の配線を介して接続パッドに接続するようにしたものがある。（例えば、特許文献1参照）

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2002-57291号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

しかしながら、上記従来の半導体装置では、半導体基板上に対向電極を備えて構成される対向導電層回路素子を設けるようにした場合、第1の導電層、第2の絶縁層および第2の導電層を積層して構成しているため、半導体基板上に1層の再配線を形成する場合と比較して、少なくとも第2の導電層を形成しなければならず、製造工程数が増加するという問題がある。

10

**【0005】**

そこで、この発明は、製造工程数を増加することなく、容量素子等の相対向する一対の導電層を有する対向導電層回路素子を形成することができる半導体装置およびその製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

請求項1に記載の発明は、ベース板と、前記ベース板上に設けられ、且つ、複数の接続パッドを有する半導体基板および該半導体基板上に前記接続パッドに電気的に接続されて設けられた再配線を有する半導体構成体と、前記半導体構成体の周囲における前記ベース板上に設けられた絶縁層と、前記半導体構成体および前記絶縁層上に設けられた少なくとも1層の上層絶縁膜と、前記上層絶縁膜の何れかの層上に前記半導体構成体の再配線の接続パッド部に電気的に接続されて設けられ、外部接続用の接続パッド部を備える少なくとも1層の上層再配線と、相対向する一対の導電層を有し、前記一対の導電層の各々が前記接続パッドに電気的に接続される対向導電層回路素子と、を備えた半導体装置の製造方法において、前記対向導電層回路素子の少なくとも一方の導電層を前記上層再配線の何れかの層と同一の平面上に前記上層再配線と同一の材料によって同時に形成することを特徴とするものである。

20

請求項2に記載の発明は、請求項1に記載の発明において、前記対向導電層回路素子の他方の導電層を前記再配線と同一の平面上に前記再配線と同一の材料によって同時に形成することを特徴とするものである。

30

請求項3に記載の発明は、請求項1に記載の発明において、前記上層絶縁膜は複数層であり、前記上層再配線も複数層であって、前記上層絶縁膜の各層上に層間で互いに接続されて形成され、前記複数層の上層再配線のうちの1層と同一の平面上に前記対向導電層回路素子の一方の導電層を当該1層と同一の材料によって同時に形成し、前記複数層の上層再配線のうちの他の1層と同一の平面上に前記対向導電層回路素子の他方の導電層を当該他の1層と同一の材料によって同時に形成することを特徴とするものである。

請求項4に記載の発明は、請求項1に記載の発明において、前記半導体構成体は、前記再配線に接続された柱状電極と、該柱状電極の上端面を除き、少なくとも前記半導体基板の上面を覆う封止膜と、を有するものであることを特徴とするものである。

40

請求項5に記載の発明は、請求項1に記載の発明において、前記対向導電層回路素子は容量素子であることを特徴とするものである。

請求項6に記載の発明は、請求項1に記載の発明において、前記対向導電層回路素子はアンテナ素子であることを特徴とするものである。

**【発明の効果】****【0007】**

この発明によれば、接続パッドと接続パッドに接続される再配線を有する半導体基板が埋め込まれ、再配線に接続されて形成される上層再配線を介して外部接続用の端子が形成される半導体装置およびその製造方法において、相対向する一対の導電層を有する対向導

50

電層回路素子の少なくとも一方の導電層を上層再配線と同一の平面上に設けているので、上層再配線と対向導電層回路素子の一方の導電層とを同一の材料によって同時に形成することができ、したがって製造工程数を増加することなく、容量素子やアンテナ素子等の対向導電層回路素子を形成することができる。

【図面の簡単な説明】

【0008】

【図1】この発明の第1実施形態としての半導体装置の一部の平面図。

【図2】図1のA-A線にほぼ沿う断面図。

【図3】図1のB-B線にほぼ沿う断面図。

【図4】図2に示す半導体装置の製造方法の一例において、当初用意したもの断面図。 10

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

【図7】図6に続く工程の断面図。

【図8】図7に続く工程の断面図。

【図9】図8に続く工程の断面図。

【図10】図9に続く工程の断面図。

【図11】図10に続く工程の断面図。

【図12】図11に続く工程の断面図。

【図13】図12に続く工程の断面図。

【図14】図13に続く工程の断面図。 20

【図15】図14に続く工程の断面図。

【図16】図15に続く工程の断面図。

【図17】図16に続く工程の断面図。

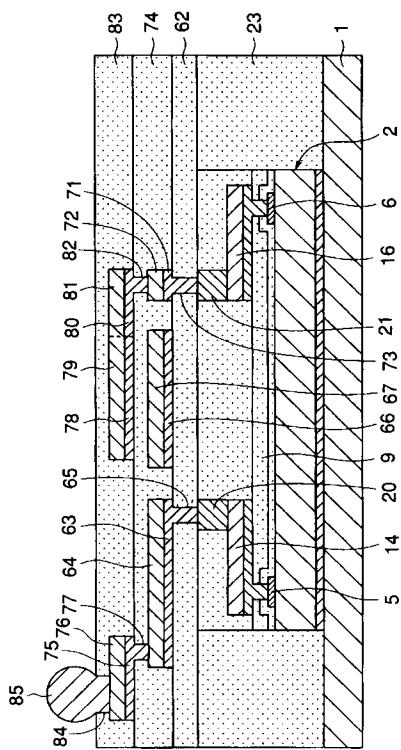

【図18】この発明の第2実施形態としての半導体装置の図2同様の断面図。

【図19】第2実施形態としての半導体装置の図3同様の断面図。

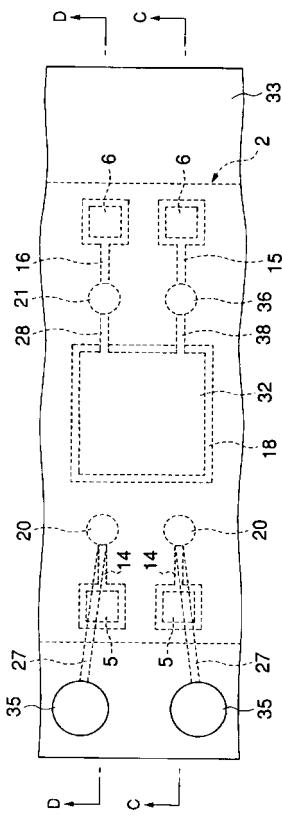

【図20】この発明の第3実施形態としての半導体装置の一部の平面図。

【図21】図20のC-C線にほぼ沿う断面図。

【発明を実施するための形態】

【0009】

(第1実施形態)

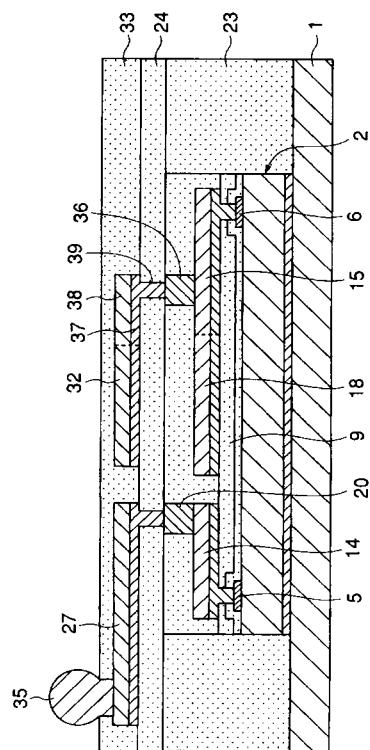

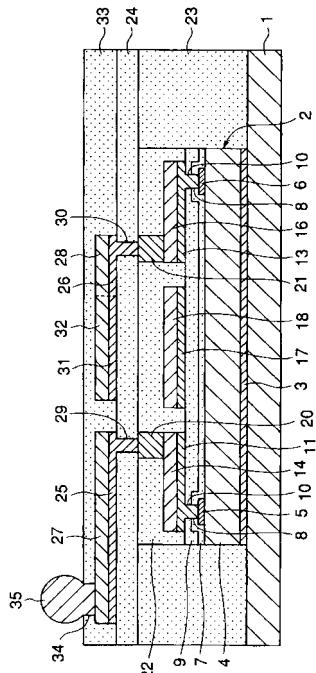

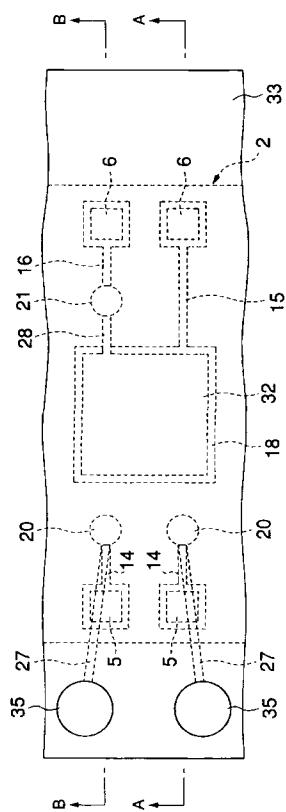

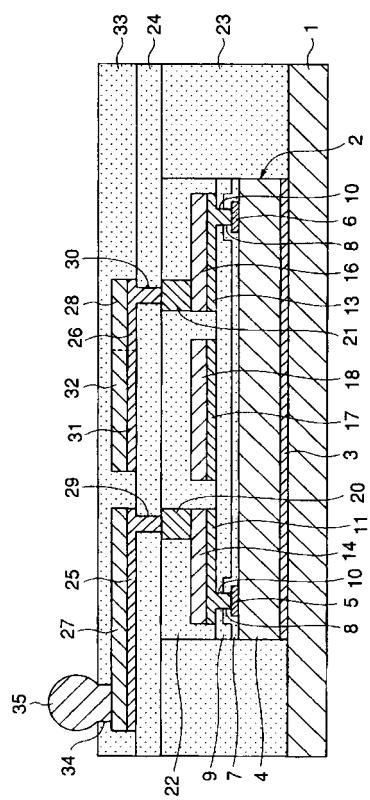

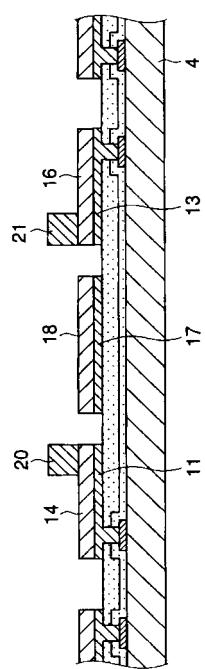

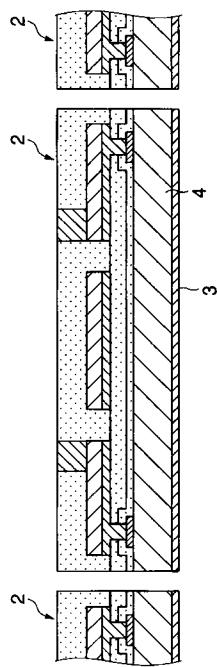

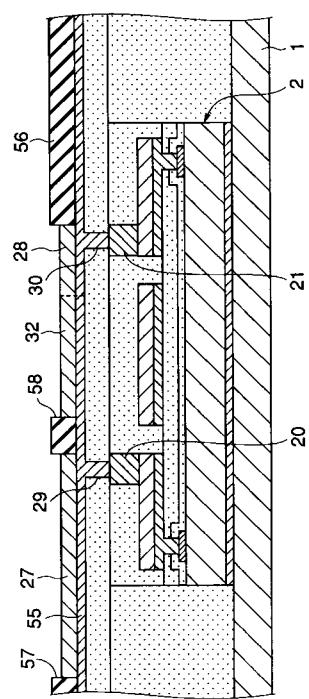

図1はこの発明の第1実施形態としての半導体装置の一部の平面図を示し、図2は図1のA-A線にほぼ沿う断面図を示し、図3は図1のB-B線にほぼ沿う断面図を示す。この半導体装置は平面方形状のベース板1を備えている。ベース板1は、ガラス纖維、アラミド纖維、液晶纖維等にエポキシ系樹脂、ポリイミド系樹脂、BT(ビスマレイミド・トリアジン)樹脂、PPE(ポリフェニレンエーテル)等を含浸させたもの、シリコン、ガラス、セラミックス、樹脂単体等の絶縁材料、あるいは、銅やアルミニウム等の金属材料からなっている。

【0010】

ベース板1の上面には、ベース板1のサイズよりもある程度小さいサイズの平面方形状の半導体構成体2の下面がダイボンド材からなる接着層3を介して接着されている。この場合、半導体構成体2は、後述する再配線、柱状電極、封止膜を有しており、一般的にはCSP(chip size package)と呼ばれるものであり、特に、後述の如く、シリコンウエハ上に再配線、柱状電極、封止膜を形成した後、ダイシングにより個々の半導体構成体2を得る方法を採用しているため、特に、ウエハレベルCSP(W-CSP)とも言われている。ただし、この場合、半導体構成体2は、後述する、相対向する一対の導電層を有するコンデンサ(容量素子)等の対向導電層回路素子を形成する構成の一部を備えている。以下に、半導体構成体2の構成について説明する。

【0011】

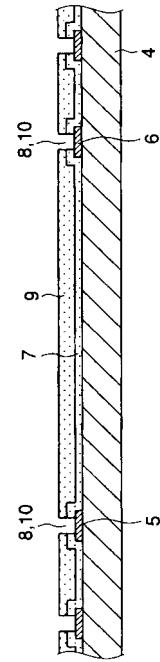

半導体構成体2は平面方形状のシリコン基板(半導体基板)4を備えている。シリコン基板4は接着層3を介してベース板1に接着されている。シリコン基板4の上面には所定

10

20

30

40

50

の機能の集積回路（図示せず）が設けられ、上面周辺部にはアルミニウム系金属等からなる複数の接続パッド5、6が集積回路に接続されて設けられている。この場合、符号6で示す接続パッドは、後述するコンデンサの一対の導電層に接続されるものであり、シリコン基板4上に少なくとも2つ設けられている。

【0012】

接続パッド5、6の中央部を除くシリコン基板4の上面には酸化シリコン等からなる絶縁膜7が設けられ、接続パッド5、6の中央部は絶縁膜7に設けられた開口部8を介して露出されている。絶縁膜7の上面にはエポキシ系樹脂やポリイミド系樹脂等からなる保護膜（絶縁膜）9が設けられている。この場合、絶縁膜7の開口部8に対応する部分における保護膜9には開口部10が設けられている。

10

【0013】

両開口部8、10を介して露出された接続パッド5、6の上面から保護膜9の上面の所定の箇所にかけて、銅等からなる下地金属層11、12、13が設けられている。下地金属層11、12、13の上面全体には銅からなる再配線14および第1、第2の接続配線15、16が設けられている。

【0014】

保護膜9の上面には銅等からなる正方形状の下地金属層17が設けられている。下地金属層17の上面全体には銅からなる下層導電層18が設けられている。下地金属層17を含む下層導電層18の一部は、下地金属層12を含む第1の接続配線15を介して一方のコンデンサ用の接続パッド6に接続されている。

20

【0015】

再配線14の接続パッド部上面には銅からなる柱状電極20が設けられている。第2の接続配線16の接続パッド部上面には銅からなる柱状電極21が設けられている。再配線14、第1、第2の接続配線15、16および下層導電層18を含む保護膜9の上面にはエポキシ系樹脂やポリイミド系樹脂等からなる封止膜22がその上面が柱状電極20、21の上面と面一となるように設けられている。

【0016】

このように、W-CSPと呼ばれる半導体構成体2は、シリコン基板4、接続パッド5、絶縁膜7を含み、さらに、保護膜9、再配線14、第1、第2の接続配線15、16、下層導電層18、柱状電極20、21、封止膜22を含んで構成されている。

30

【0017】

半導体構成体2の周囲におけるベース板1の上面には方形枠状の絶縁層23がその上面が半導体構成体2の上面とほぼ面一となるように設けられている。絶縁層23は、例えば、熱可塑性樹脂中にガラス繊維やシリカフィラー等の補強材を分散させたものである。

【0018】

半導体構成体2および絶縁層23の上面には上層絶縁膜24がその上面を平坦とされて設けられている。上層絶縁膜24は、ビルドアップ基板に用いられる、通常、ビルドアップ材と言われるもので、例えば、エポキシ系樹脂やBT樹脂等の熱硬化性樹脂中に繊維やフィラー等の補強材を含有させたものである。この場合、繊維は、ガラス繊維やアラミド繊維等である。フィラーは、シリカフィラーやセラミック系フィラー等である。

40

【0019】

上層絶縁膜24の上面には銅等からなる下地金属層25、26が設けられている。下地金属層25、26の上面全体には銅からなる上層再配線27および第3の接続配線28が設けられている。下地金属層25を含む上層再配線27の一端部は、柱状電極20の上面中央部に対応する部分における上層絶縁膜24に設けられた開口部29を介して柱状電極20の上面に接続されている。下地金属層26を含む第3の接続配線28の一端部は、柱状電極21の上面中央部に対応する部分における上層絶縁膜24に設けられた開口部30を介して柱状電極21の上面に接続されている。

【0020】

上層絶縁膜24の上面には銅等からなる正方形状の下地金属層31が設けられている。

50

下地金属層 3 1 の上面全体には銅からなる上層導電層 3 2 が設けられている。下地金属層 3 1 を含む上層導電層 3 2 の一部は、下地金属層 2 6 を含む第 3 の接続配線 2 8 の他端部に接続されている。すなわち、上層導電層 3 2 の一部は、第 3 の接続配線 2 8 、柱状電極 2 1 および第 2 接続配線 1 6 を介して他方のコンデンサ用の接続パッド 6 に接続されている。ここで、上層導電層 3 2 と下層導電層 1 8 とは、その間に封止膜 2 2 および上層絶縁膜 2 4 が介在された状態で、相対向して配置され、コンデンサを構成している。

#### 【 0 0 2 1 】

上層再配線 2 7 、第 3 の接続配線 2 8 および上層導電層 3 2 を含む上層絶縁膜 2 4 の上面にはソルダーレジスト等からなるオーバーコート膜（最上層絶縁膜）3 3 が設けられている。上層再配線 2 7 の接続パッド部に対応する部分におけるオーバーコート膜 3 3 には開口部 3 4 が設けられている。開口部 3 4 内およびその上方には半田ボール 3 5 が上層再配線 2 7 の接続パッド部に接続されて設けられている。複数の半田ボール 3 5 は、図 1 では、オーバーコート膜 3 3 の上面外周部のみに図示しているが、実際には、オーバーコート膜 3 3 の上面周辺部にマトリクス状に配置されている。

10

#### 【 0 0 2 2 】

ところで、ベース板 1 のサイズを半導体構成体 2 のサイズよりもある程度大きくしているのは、シリコン基板 4 上の接続パッド 5 の数の増加に応じて、半田ボール 3 5 の配置領域を半導体構成体 2 のサイズよりもある程度大きくし、これにより、上層再配線 2 7 の接続パッド部（オーバーコート膜 3 3 の開口部 3 4 内の部分）のサイズおよびピッチを柱状電極 2 0 のサイズおよびピッチよりも大きくするためである。

20

#### 【 0 0 2 3 】

このため、マトリクス状に配置された上層再配線 2 7 の接続パッド部は、半導体構成体 2 に対応する領域のみでなく、半導体構成体 2 の側面の外側に設けられた絶縁層 2 3 に対応する領域上にも配置されている。つまり、マトリクス状に配置された半田ボール 3 5 のうち、少なくとも最外周の半田ボール 3 5 は半導体構成体 2 よりも外側に位置する周囲に配置されている。

20

#### 【 0 0 2 4 】

次に、この半導体装置の製造方法の一例について説明する。ただし、この場合、図示の都合上、図 3 に示す半導体装置の製造方法について説明し、図 2 に示す第 1 の接続配線 1 5 等についてはその説明を省略する。まず、半導体構成体 2 の製造方法について説明する。

30

#### 【 0 0 2 5 】

図 4 に示すように、ウエハ状態のシリコン基板 4 上にアルミニウム系金属等からなる接続パッド 5 、 6 、酸化シリコン等からなる絶縁膜 7 およびエポキシ系樹脂やポリイミド系樹脂等からなる保護膜 9 が設けられ、接続パッド 5 、 6 の中央部が絶縁膜 7 および保護膜 9 に形成された開口部 8 、 1 0 を介して露出されたものを用意する。上記において、ウエハ状態のシリコン基板 4 には、各半導体構成体が形成される領域に所定の機能の集積回路が形成され、接続パッド 5 、 6 は、それぞれ、対応する領域に形成された集積回路に電気的に接続されている。

40

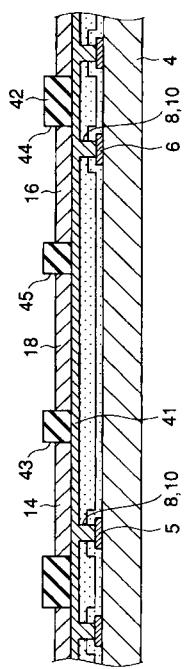

#### 【 0 0 2 6 】

次に、図 5 に示すように、両開口部 8 、 1 0 を介して露出された接続パッド 5 、 6 の上面を含む保護膜 9 の上面全体に下地金属層 4 1 を形成する。この場合、下地金属層 4 1 は、無電解メッキにより形成された銅層のみであってもよく、またスパッタにより形成された銅層のみであってもよく、さらにもスパッタにより形成されたチタン等の薄膜層上にスパッタにより銅層を形成したものであってもよい。これは、後述する下地金属層 5 5 の場合も同様である。

#### 【 0 0 2 7 】

次に、下地金属層 4 1 の上面にメッキレジスト膜 4 2 をパターン形成する。この場合、再配線 1 4 形成領域、第 2 の接続配線 1 6 形成領域および下層導電層 1 8 形成領域に対応する部分におけるメッキレジスト膜 4 2 には開口部 4 3 、 4 4 、 4 5 が形成されている。

50

次に、下地金属層 4 1 をメッキ電流路として銅の電解メッキを行なうことにより、メッキレジスト膜 4 2 の開口部 4 3、4 4、4 5 内の下地金属層 4 1 の上面に再配線 1 4、第 2 の接続配線 1 6 および下層導電層 1 8 を形成する。次に、メッキレジスト膜 4 2 を剥離する。

【 0 0 2 8 】

次に、図 6 に示すように、再配線 1 4、第 2 の接続配線 1 6 および下層導電層 1 8 を含む下地金属層 4 1 の上面にメッキレジスト膜 4 6 をパターン形成する。この場合、柱状電極 2 0 形成領域および柱状電極 2 1 形成領域に対応する部分におけるメッキレジスト膜 4 6 には開口部 4 7、4 8 が形成されている。次に、下地金属層 4 1 をメッキ電流路として銅の電解メッキを行なうことにより、メッキレジスト膜 4 6 の開口部 4 7、4 8 内の再配線 1 4 および第 2 の接続配線 1 6 の接続パッド部上面に柱状電極 2 0、2 1 を形成する。

10

【 0 0 2 9 】

次に、メッキレジスト膜 4 6 を剥離し、次いで、柱状電極 2 0、2 1、再配線 1 4、第 2 の接続配線 1 6 および下層導電層 1 8 をマスクとして下地金属層 4 1 の不要な部分をエッチングして除去すると、図 7 に示すように、再配線 1 4 下、第 2 の接続配線 1 6 下および下層導電層 1 8 下にのみ下地金属層 1 1、1 3、1 7 が残存される。

20

【 0 0 3 0 】

次に、図 8 に示すように、スクリーン印刷法、スピンドルコート法、ダイコート法等により、柱状電極 2 0、2 1、再配線 1 4、第 2 の接続配線 1 6 および下層導電層 1 8 を含む保護膜 9 の上面全体にエポキシ系樹脂やポリイミド系樹脂等からなる封止膜 2 2 をその厚さが柱状電極 2 0、2 1 の高さよりも厚くなるように形成する。したがって、この状態では、柱状電極 2 0、2 1 の上面は封止膜 2 2 によって覆われている。

20

【 0 0 3 1 】

次に、封止膜 2 2 および柱状電極 2 0、2 1 の上面側を適宜に研磨し、図 9 に示すように、柱状電極 2 0、2 1 の上面を露出させ、且つ、この露出された柱状電極 2 0、2 1 の上面を含む封止膜 2 2 の上面を平坦化する。ここで、柱状電極 2 0、2 1 の上面側を適宜に研磨するのは、電解メッキにより形成される柱状電極 2 0、2 1 の高さにばらつきがあるため、このばらつきを解消して、柱状電極 2 0、2 1 の高さを均一にするためである。

【 0 0 3 2 】

次に、図 1 0 に示すように、シリコン基板 4 の下面全体に接着層 3 を接着する。接着層 3 は、エポキシ系樹脂、ポリイミド系樹脂等のダイボンド材からなるものであり、加熱加圧により、半硬化した状態でシリコン基板 4 に固着する。次に、シリコン基板 4 に固着された接着層 3 をダイシングテープ（図示せず）に貼り付け、図 1 1 に示すダイシング工程を経た後に、ダイシングテープから剥がすと、図 3 に示すように、シリコン基板 4 の下面に接着層 3 を有する半導体構成体 2 が複数個得られる。

30

【 0 0 3 3 】

このようにして得られた半導体構成体 2 では、シリコン基板 4 の下面に接着層 3 を有するため、ダイシング工程後に各半導体構成体 2 のシリコン基板 4 の下面にそれぞれ接着層を設けるといった極めて面倒な作業が不要となる。なお、ダイシング工程後にダイシングテープから剥がす作業は、ダイシング工程後に各半導体構成体 2 のシリコン基板 4 の下面にそれぞれ接着層を設ける作業に比べれば、極めて簡単である。

40

【 0 0 3 4 】

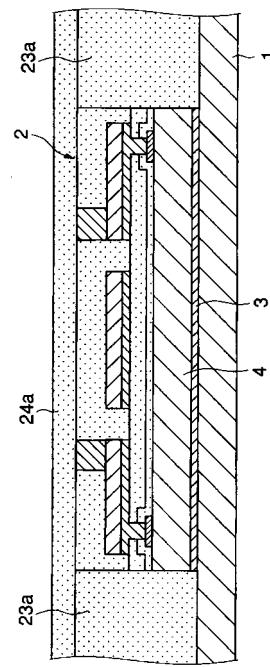

次に、このようにして得られた半導体構成体 2 を用いて、図 3 に示す半導体装置を製造する場合の一例について説明する。まず、図 1 2 に示すように、図 3 に示すベース板 1 を複数枚採取することができる大きさで、限定する意味ではないが、平面形状が方形状のベース板 1 を用意する。次に、ベース板 1 の上面の所定の複数箇所にそれぞれ半導体構成体 2 のシリコン基板 4 の下面に接着された接着層 3 を接着する。ここでの接着は、加熱加圧により、接着層 3 を本硬化させる。

【 0 0 3 5 】

次に、半導体構成体 2 間および最外周に配置された半導体構成体 2 の外側におけるベー

50

ス板1の上面に、例えばスクリーン印刷法やスピンドルコートティング法等により、第1の絶縁材料23aを形成し、さらにその上面にシート状の第2の絶縁材料24aを配置する。第1の絶縁材料23aは、例えば、熱硬化性樹脂や、熱硬化性樹脂中にガラス繊維やシリカフィラー等の補強材を分散させたものからなる。

【0036】

シート状の第2の絶縁材料24aは、限定する意味ではないが、ビルドアップ材が好ましく、このビルドアップ材としては、エポキシ系樹脂やBT樹脂等の熱硬化性樹脂中にシリカフィラーを混入させ、熱硬化性樹脂を半硬化状態にしたものがある。しかしながら、第2の絶縁材料24aとして、ガラス繊維にエポキシ系樹脂等の熱硬化性樹脂を含浸させ、熱硬化性樹脂を半硬化状態にしてシート状となしたプリプレグ材、またはフィラーが混入されない、熱硬化性樹脂のみからなる材料を用いるようにしてもよい。

10

【0037】

次に、図13に示す一対の加熱加圧板53、54を用いて、第1および第2の絶縁材料23a、24aを加熱加圧する。かくして、図13に示すように、半導体構成体2間および最外周に配置された半導体構成体2の外側におけるベース板1の上面に絶縁層23が形成され、半導体構成体2および絶縁層23の上面に上層絶縁膜24が形成される。

【0038】

この場合、上層絶縁膜24の上面は、上側の加熱加圧板53の下面によって押さえ付けられるため、平坦面となる。したがって、上層絶縁膜24の上面を平坦化するための研磨工程は不要である。このため、ベース板1のサイズが例えば500×500mm程度と比較的大きくても、その上に配置された複数の半導体構成体2に対して上層絶縁膜24の上面の平坦化を一括して簡単に行なうことができる。

20

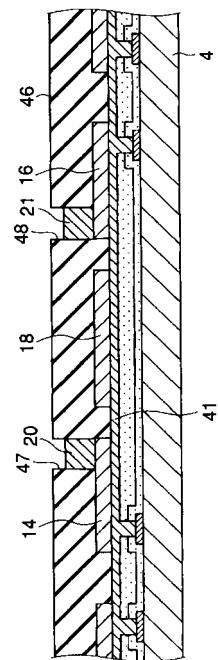

【0039】

次に、図14に示すように、レーザビームを照射するレーザ加工あるいはフォトリソグラフィ法により、柱状電極20、21の上面中央部に対応する部分における上層絶縁膜24に開口部29、30を形成する。次に、必要に応じて、開口部29、30内等に発生したエポキシスミア等をデスマニア処理により除去する。

【0040】

次に、図15に示すように、開口部29、30を介して露出された柱状電極20、21の上面を含む上層絶縁膜24の上面全体に下地金属層55を形成する。次に、下地金属層55の上面にメッキレジスト膜56をパターン形成する。この場合、上層再配線27形成領域および第3の接続配線28形成領域を含む上層導電層32形成領域に対応する部分におけるメッキレジスト膜56には開口部57、58が形成されている。

30

【0041】

次に、下地金属層55をメッキ電流路として銅の電解メッキを行なうことにより、メッキレジスト膜56の開口部57、58内の下地金属層55の上面に上層再配線27および第3の接続配線28を含む上層導電層32を形成する。次に、メッキレジスト膜56を剥離し、次いで、上層再配線27、第3の接続配線28および上層導電層32をマスクとして下地金属層55の不要な部分をエッチングして除去すると、図16に示すように、上層再配線27、第3の接続配線28および上層導電層32下にのみ下地金属層25、26、31が残存される。

40

【0042】

次に、図17に示すように、スクリーン印刷法やスピンドルコートティング法等により、上層再配線27、第3の接続配線28および上層導電層32を含む上層絶縁膜24の上面にソルダーレジスト等からなるオーバーコート膜33を形成する。この場合、上層再配線27の接続パッド部に対応する部分におけるオーバーコート膜33には開口部34が形成されている。

【0043】

次に、開口部34内およびその上方に半田ボール35を上層再配線27の接続パッド部に接続させて形成する。次に、互いに隣接する半導体構成体2間ににおいて、オーバーコー

50

ト膜 3 3、上層絶縁膜 2 4、絶縁層 2 3 およびベース板 1 を切断すると、図 3 に示す半導体装置が複数個得られる。

【 0 0 4 4 】

以上のように、上記製造方法では、図 5 に示す工程において、下地金属層 4 1 の上面に再配線 1 4、第 2 の接続配線 1 6 および下層導電層 1 8 を同一の材料によって同時に形成し、図 6 に示す工程において、再配線 1 4 および第 2 の接続配線 1 6 の接続パッド部上面に柱状電極 2 0、2 1 を同一の材料によって同時に形成し、図 1 5 に示す工程において、下地金属層 5 5 の上面に上層再配線 2 7、第 3 の接続配線 2 8 および上層導電層 3 2 を同一の材料によって同時に形成しているので、製造工程数を増加することなく、一対の導電層 1 8、3 2 を有するコンデンサを形成することができる。

10

【 0 0 4 5 】

また、上記製造方法では、ベース板 1 上に複数の半導体構成体 2 を接着層 3 を介して配置し、複数の半導体構成体 2 に対して、特に、上層再配線 2 7、第 3 の接続配線 2 8 および半田ボール 3 5 の形成を一括して行い、その後に分断して複数個の半導体装置を得ているので、製造工程を簡略化することができる。また、図 1 3 に示す工程以降では、ベース板 1 と共に複数の半導体構成体 2 を搬送することができるので、これによっても製造工程を簡略化することができる。

【 0 0 4 6 】

( 第 2 実施形態 )

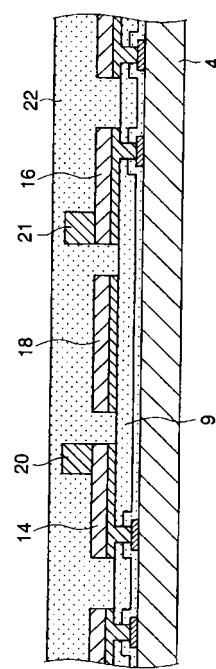

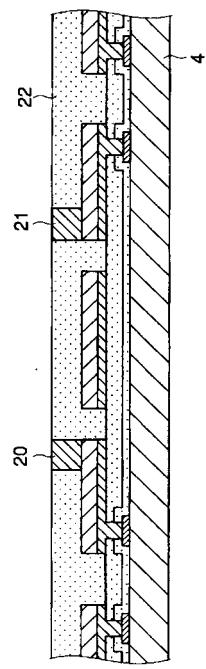

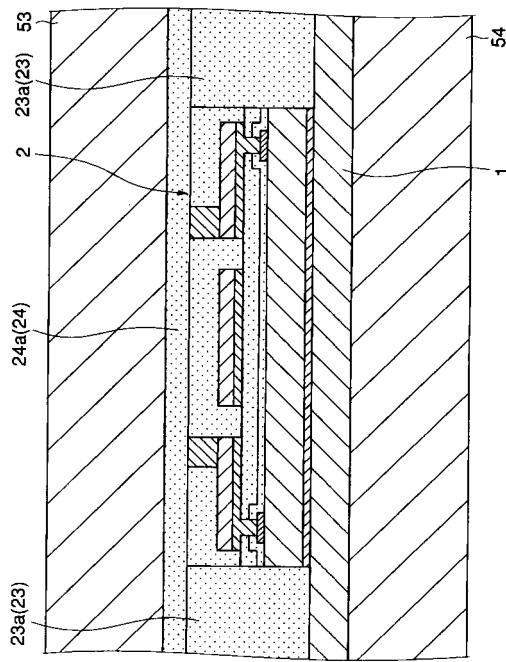

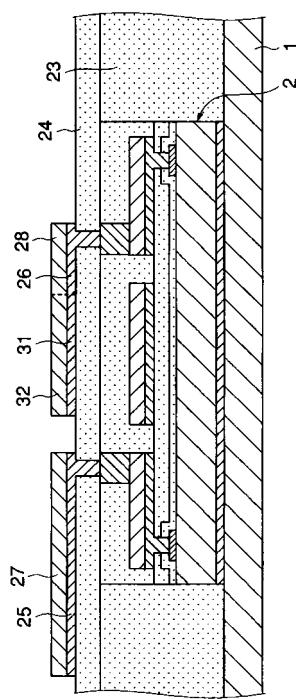

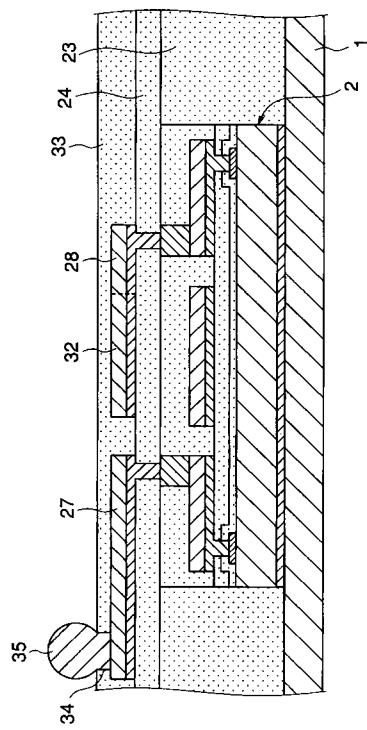

上記第 1 実施形態では、図 2 および図 3 に示すように、上層絶縁膜 2 4 上に上層再配線 2 7 を 1 層だけ形成した場合について説明したが、これに限らず、2 層以上としてもよく、例えば、図 1 8 および図 1 9 に示すこの発明の第 2 実施形態のように、2 層としてもよい。この場合、図 1 8 は図 2 同様の断面図を示し、図 1 9 は図 3 同様の断面図を示す。

20

【 0 0 4 7 】

この半導体装置の半導体構成体 2 では、保護膜 9 の上面に下層導電層が設けられておらず、その代わりに、第 1 の接続配線 1 5 の接続パッド部上面に柱状電極 6 1 が設けられている。そして、半導体構成体 2 および絶縁層 2 3 の上面にはビルトアップ材等からなる第 1 の上層絶縁膜 6 2 が設けられている。第 1 の上層絶縁膜 6 2 の上面には下地金属層 6 3 を含む第 1 の上層再配線 6 4 が第 1 の上層絶縁膜 6 2 に設けられた開口部 6 5 を介して柱状電極 2 0 の上面に接続されて設けられている。

30

【 0 0 4 8 】

第 1 の上層絶縁膜 6 2 の上面には下地金属層 6 6 を含む下層導電層 6 7 が設けられている。下地金属層 6 6 を含む下層導電層 6 7 の一部は、第 1 の上層絶縁膜 6 2 の上面に設けられた下地金属層 6 8 を含む第 3 の接続配線 6 9 の一端部に接続されている。下地金属層 6 8 を含む第 3 の接続配線 6 9 の他端部は、第 1 の上層絶縁膜 6 2 に設けられた開口部 7 0 を介して柱状電極 6 1 の上面に接続されている。第 1 の上層絶縁膜 6 2 の上面には下地金属層 7 1 を含む中継接続パッド 7 2 が第 1 の上層絶縁膜 6 2 に設けられた開口部 7 3 を介して柱状電極 2 1 の上面に接続されて設けられている。

【 0 0 4 9 】

第 1 の上層再配線 6 4、下層導電層 6 7、第 3 の接続配線 6 9 および中継接続パッド 7 2 を含む第 1 の上層絶縁膜 6 2 の上面にはビルトアップ材等からなる第 2 の上層絶縁膜 7 4 が設けられている。第 2 の上層絶縁膜 7 4 の上面には下地金属層 7 5 を含む第 2 の上層再配線 7 6 が第 2 の上層絶縁膜 7 4 に形成された開口部 7 7 を介して第 1 の上層再配線 6 4 の接続パッド部に接続されて設けられている。

40

【 0 0 5 0 】

第 2 の上層絶縁膜 7 4 の上面には下地金属層 7 8 を含む上層導電層 7 9 が設けられている。下地金属層 7 8 を含む上層導電層 7 9 の一部は、第 2 の上層絶縁膜 7 4 の上面に設けられた下地金属層 8 0 を含む第 4 の接続配線 8 1 の一端部に接続されている。下地金属層 8 0 を含む第 4 の接続配線 8 1 の他端部は、第 2 の上層絶縁膜 7 4 に設けられた開口部 8 2 を介して中継接続パッド 7 2 に接続されている。

50

## 【0051】

第2の上層再配線76、上層導電層79および第4の接続配線81を含む第2の上層絶縁膜74の上面にはソルダーレジスト等からなるオーバーコート膜83が設けられている。第2の上層再配線76の接続パッド部に対応する部分におけるオーバーコート膜83には開口部84が設けられている。開口部84内およびその上方には半田ボール85が第2の上層再配線76の接続パッド部に接続されて設けられている。

## 【0052】

そして、この半導体装置では、第1の上層絶縁膜62の上面に第1の上層再配線64、下層導電層67、第3の接続配線69および中継接続パッド72が同一の材料によって同時に形成され、第2の上層絶縁膜74の上面に第2の上層再配線76、上層導電層79および第4の接続配線81が同一の材料によって同時に形成されている。したがって、この場合も、製造工程数を増加することなく、一対の導電層67、79を有するコンデンサを形成することができる。

10

## 【0053】

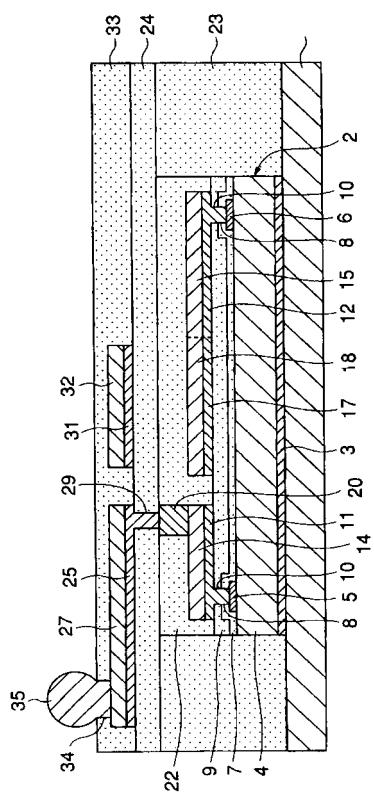

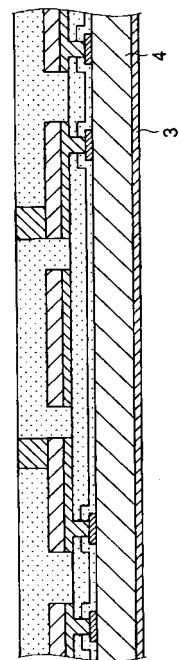

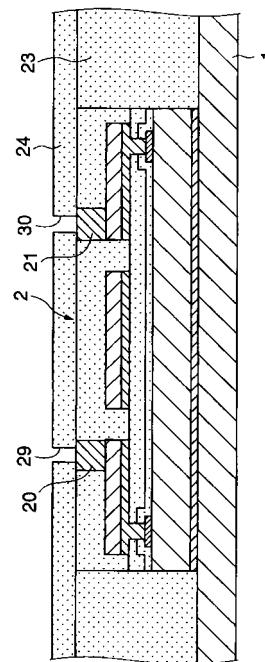

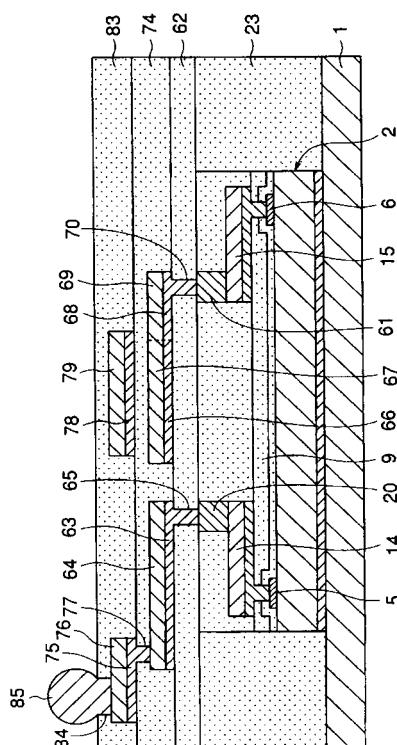

## (第3実施形態)

図20はこの発明の第3実施形態としての半導体装置の一部の平面図を示し、図21は図20のC-C線に沿う断面図を示す。この場合、図20のD-D線に沿う断面図は図3と同じである。この半導体装置において、図1～図3に示す場合と大きく異なる点は、一対の導電層18、32によって逆F形アンテナやパッチアンテナ等の対向導電層回路素子を構成するようにした点である。

20

## 【0054】

このため、第1の接続配線15の途中の接続パッド部上面には柱状電極36が設けられている。そして、上層導電層32の他の一部は、第1の上層絶縁膜24の上面に設けられた下地金属層37を含む第4の接続配線38の一端部に接続されている。下地金属層37を含む第4の接続配線38の他端部は、第1の上層絶縁膜24に設けられた開口部39を介して柱状電極36の上面に接続されている。この場合、第1の接続配線15が接続された一方の接続パッド6は接地用であり、第2の接続配線16が接続された他方の接続パッド6は給電用である。

## 【0055】

そして、この半導体装置では、保護膜9の上面に再配線14、下層導電層18および第1、第2の接続配線15、16が同一の材料によって同時に形成され、再配線14および第1、第2の接続配線15、16の接続パッド部上面に柱状電極20、21、36が同一の材料によって同時に形成され、上層絶縁膜24の上面に上層再配線27、上層導電層32および第3、第4の接続配線28、38が同一の材料によって同時に形成されている。したがって、この場合も、製造工程数を増加することなく、一対の導電層18、32を有するアンテナ素子を形成することができる。

30

## 【0056】

## (その他の実施形態)

なお、対向導電層回路素子は、コンデンサやアンテナに限らず、相対向する一対の導電層を有して構成されるものであれば何でもよい。また、上記各実施形態において、半導体構成体2は、外部接続用電極として、再配線14の接続パッド部上に設けられた柱状電極20を有するものとしたが、これに限定されるものではない。例えば、半導体構成体2は、外部接続用電極としての接続パッド部を有する再配線14のみを有するものであってよい。さらに、ベース板1は、1枚の部材に限らず、絶縁膜および配線が交互に積層された多層印刷回路板としてもよい。

40

## 【符号の説明】

## 【0057】

- 1 ベース板

- 2 半導体構成体

- 3 接着層

50

- 4 シリコン基板

5、6 接続パッド

7 絶縁膜

9 保護膜

1 4 再配線

1 5 第1の接続配線

1 6 第2の接続配線

1 8 下層導電層

2 0、2 1 柱状電極

2 2 封止膜

2 3 絶縁層

2 4 上層絶縁膜

2 7 上層再配線

2 8 第3の接続配線

3 2 上層導電層

3 3 オーバーコート膜

3 5 半田ボール

【 図 1 】

【 図 2 】

〔 図 3 〕

【 図 4 】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【 図 1 9 】

【図20】

## 【 図 2 1 】