(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第3922182号 (P3922182)

(45) 発行日 平成19年5月30日(2007.5.30)

(24) 登録日 平成19年3月2日(2007.3.2)

(51) Int.C1. F 1

HO3F 1/52 (2006.01) HO3F 3/183 (2006.01) HO3F 3/217 (2006.01) HO3F 1/52 HO3F 3/183 HO3F 3/217

請求項の数 3 (全 9 頁)

(21) 出願番号 特願2002-379692 (P2002-379692) (22) 出願日 平成14年12月27日 (2002.12.27)

(65) 公開番号 特開2004-214793 (P2004-214793A)

(43) 公開日 平成16年7月29日 (2004. 7. 29) 審査請求日 平成16年5月21日 (2004. 5. 21) (73)特許権者 000004075

ヤマハ株式会社

Z

静岡県浜松市中沢町10番1号

|(74)代理人 100102635

弁理士 浅見 保男

(74)代理人 100106459

弁理士 高橋 英生

|(74)代理人 100105500

弁理士 武山 吉孝

|(74) 代理人 100103735

弁理士 鈴木 隆盛

(72) 発明者 野呂 正夫

静岡県浜松市中沢町10番1号 ヤマハ株

式会社内

最終頁に続く

(54) 【発明の名称】増幅回路

# (57)【特許請求の範囲】

#### 【請求項1】

入力信号の振幅を制限する電圧リミター回路と、

該電圧リミター回路を介して入力される信号を増幅する増幅器と、

該増幅器から負荷に供給される出力電流に比例する信号を増幅する<u>電流検出アンプであって</u>、<u>負荷インピーダンスが変化しても最大出力がほぼ一定となるように</u>ゲインが大きくされていない電流検出アンプと、

基準電圧から前記電流検出アンプの出力を整流した電圧を減算した電圧を平均化する手段とを有し、

前記電圧リミター回路は、前記入力信号の電圧が前記平均化する手段の出力電圧に対し 所定値以上高い電圧とならないように、前記入力信号の振幅を制限するものであることを 特徴とする増幅回路。

# 【請求項2】

前記電圧リミター回路は、前記基準電圧から前記電流検出アンプの出力を整流した電圧 を減算した電圧の瞬時値が、前記平均化する手段の出力電圧よりもさらに所定値低い電圧 となったときにも、前記入力信号の振幅を制限するように構成されていることを特徴とす る請求項1記載の増幅回路。

#### 【請求項3】

前記増幅器は、デジタルアンプであることを特徴とする請求項1又は2に記載の増幅回路。

#### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、スピーカーなどを駆動する増幅回路に関する。

[0002]

【従来の技術】

スピーカーなどを駆動する増幅回路(パワーアンプ)は基本的に電圧出力であり、負荷に電圧信号を供給する。そのときの電流値は負荷のインピーダンスによって決まるが、スピーカーの場合インピーダンスは機種によって異なり、またインピーダンスは周波数によっても異なる。よって、パワーアンプはかなり広い範囲の負荷インピーダンスに対応する必要がある。

パワーアンプの出力電力は出力電圧と出力電流の積になる。最大出力電圧は電源電圧に依存するが、一般に、電源回路はレギュレーション特性を持っているので、負荷電流(出力電流)が増大すると電源電圧も低下する。よって負荷抵抗が小さくなると負荷電流が増すものの、最大出力電圧は低下するため、最大出力電力は完全には負荷抵抗に反比例しないが、一般的に最大出力電力は増大する方向に向かうため、どこかに出力信号を制限する手段を持たないとアンプが過電流もしくは電力的(熱的)に破壊してしまう。

このような目的で、ほとんどのパワーアンプは保護の目的で何らかのリミター回路(プロテクション回路)を持っている。

[0003]

リミター回路には、(1)出力電圧を制限する電圧リミター、(2)出力電流を制限する電流リミター、(3)アンプの消費電力を制限するPCリミターなどがある。

(1)電圧リミター

アンプの場合、リミター回路がなくても電源電圧でクリップするので、電圧リミターは特に設けなくても問題は無く、実際に無いアンプの方が多い。その場合、出力のクリップ電圧は電源電圧に依存するため、電源電圧が変動するとクリップ電圧も変動する。また、前述したように負荷電流が大きくなると一般的に電源電圧も低下するのでクリップ電圧も低下する。これは、理想アンプという視点からはデメリットに見えるが、現実的にはそうではない。一般的な一定電圧のリミターは、8 負荷と2 負荷の出力差が広がる(見かけ上理想アンプ+理想電源の値に近づく)方向になるため意図的にそういう効果を狙う場合を除き、実用的な効果は少ない。

(2)電流リミター

電流リミターは、負荷ショート時の出力素子保護に不可欠な機能であり、負荷ショート時や低インピーダンス負荷時においてリミット値を越えた出力電流が流れたときに動作する。しかし、電流でクリップさせると信号波形が非常に汚くなる(スピーカーのインピーダンスがリアクタンス成分を含むため)ことと、出力が電流性になりスピーカーのダンピングが効かなくなる、などの問題があって耳につきやすい異音が発生するため、音楽再生中にパワーコントロールの目的で頻繁に動作させるわけにはいかず、あくまでアンプの破壊を防ぐ目的で異常負荷時のプロテクションという意味合いで使われる。

(3) P C リミター

P C リミターは、電流リミターのリミット電流値に出力電圧依存性を持たせたものである。 負荷ショート時の電流リミット値を小さく設定できるので出力素子の負担が少ないというメリットがある。出力素子の保護という目的では、電流リミターより有効であるが、これも電流制限動作なので電流リミターと同様に音楽再生中に動作させると異音が目立つこととなる。

[0004]

また、過大な出力を防止するために電力増幅部の出力電圧と基準電圧とを比較し、出力電圧が基準電圧以上になったときに入力信号レベルを低下させるようにした電力増幅器において、負荷に応じて電力増幅部に供給される電流値に応じて前記基準電圧を複数段階に設定するようにした電力増幅器が提案されている(特許文献1参照)。

20

30

40

#### [0005]

# 【特許文献1】

特開平10-173446号公報

#### [0006]

### 【発明が解決しようとする課題】

理想的電源(完全な定電圧電源)から電流供給を受ける理想アンプが 8 負荷時に 1 0 0 Wの最大出力を持つ場合、 4 負荷で 2 0 0 W、 2 負荷で 4 0 0 Wの最大出力を持つことになる。単純に理想アンプに近い最大出力特性を持つものが良いアンプであるという思想で設計されたアンプも存在しているが、オーディオアンプの場合、実用的には 2 程度の負荷まで対応する必要があるので、この場合アンプとしては、 4 0 0 Wの出力に耐えられる設計にする必要が生じ、非常に大型のアンプになってしまう。しかも、市場で最もポピュラーな 8 のスピーカーを駆動する場合は 1 0 0 Wの出力しか得られないので合理性・実用性という面からみると決して好ましいものではない。

すなわち、アンプの最大出力は、負荷インピーダンスが例えば2 から8 へと変化して も大きく変化しないほうが望ましい。

そこで、本発明は、負荷インピーダンスが変化しても最大出力電力をほぼ一定に制御する ことが可能な増幅回路を提供することを目的としている。

### [0007]

### 【課題を解決するための手段】

上記目的を達成するために、本発明の増幅回路は、入力信号の振幅を制限する電圧リミター回路と、該電圧リミター回路を介して入力される信号を増幅する増幅器と、該増幅器から負荷に供給される出力電流に比例する信号を増幅する<u>電流検出アンプであって</u>、<u>負荷インピーダンスが変化しても最大出力がほぼ一定となるように</u>ゲインが大きくされていない電流検出アンプと、基準電圧から前記電流検出アンプの出力を整流した電圧を減算した電圧を平均化する手段とを有し、前記電圧リミター回路は、前記入力信号の電圧が前記平均化する手段の出力電圧に対し所定値以上高い電圧とならないように、前記入力信号の振幅を制限するものとされているものである。

また、前記電圧リミター回路は、前記基準電圧から前記電流検出アンプの出力を整流した電圧を減算した電圧の瞬時値が、前記平均化する手段の出力電圧よりもさらに所定値低い電圧となったときにも、前記入力信号の振幅を制限するように構成されているものである。

さらに、前記増幅器はデジタルアンプとされているものである。

#### [0009]

## 【発明の実施の形態】

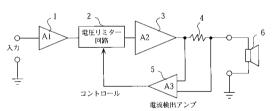

図1は、本発明の増幅回路の第1の実施の形態の概略構成を示すブロック図である。この図において、1は入力信号を電圧増幅する入力アンプ、2は該入力アンプ1の出力信号電圧を電流検出アンプ5の出力に応じて制限する電圧リミター回路、3は該電圧リミター回路2の出力を電力増幅する電力増幅器(パワーアンプ)、4は負荷(スピーカー)6に流れる出力電流(負荷電流)を検出するために電力増幅器3の出力とスピーカー6との間に直列に挿入された抵抗値の小さな抵抗、5は前記抵抗4の両端に発生する電圧を増幅する差動アンプなどにより構成された電流検出アンプ、6はスピーカである。なお、前記パワーアンプ3としてはアナログアンプ又はデジタルアンプのいずれであってもよい。

### [0010]

ここで、前記電流検出アンプ 5 は、入力電圧の平方根にほぼ比例する電圧を出力する入出力電圧特性とされており、また、そのゲインは大きくされていない。さらに、前記電圧リミター回路 2 は、前記電流検出アンプ 5 の出力を積分回路等を用いて平均化した出力に基づいて動作するようになされている。

そして、前記電流検出アンプ5のゲインと前記積分回路等の時定数を、出力電流を増していくとそれに応じて前記電圧リミター回路2のリミット電圧を徐々に下げていくような穏やかな動作(帰還量の少ない動作)となるように設定している。帰還量を非常に多く設定

10

20

30

20

30

50

した場合には出力電流が基準値を超えると急激にクリップさせるというような急峻な動作となるが、本発明の増幅回路においては、意図的に電流検出アンプのゲインを大きくせずに帰還量を少なめに調整し、例えば、スピーカ6のインピーダンスが2 のときには、8 のときよりも大きな電流(約2倍の電流)でクリップするように設定することで、最大出力がほぼ一定となるように制御している。

#### [0011]

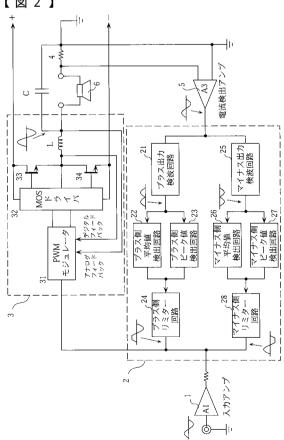

図2は、本発明の増幅回路の第2の実施の形態の構成を示すブロック図である。この図において、入力アンプ1、電圧リミター回路2、パワーアンプ3、抵抗4、電流検出アンプ5及びスピーカ6は前記図1に示したものと同一である。なお、ここでは、パワーアンプ3としてデジタルアンプが用いられている場合を示しており、パワーアンプ3は、PWM変調回路31、ドライバ回路32及び該ドライバ回路32によりスイッチングされるMOSFET33、34からなっており、正負電源により駆動される。また、前記PWM変調回路31には、前記MOSFET33、34の出力からデジタルフィードバックがかけられ、スピーカー6への出力端子からアナログフィードバックがかけられており、高品質の出力を得ることができるようになされている。

#### [0012]

図示するように、この実施の形態における電圧リミター回路 2 は、プラス側とマイナス側 それぞれに、前記電流検出アンプ 5 の出力を検波する検波回路、該検波回路出力のピーク値を検出するピーク値検出回路と平均値を検出する平均値検出回路、及びピーク値検出回路と平均値検出回路の出力に基づいて前記入力アンプ 1 の出力電圧の振幅を制限するリミター回路を設けている。

すなわち、プラス側には、前記電流検出アンプ 5 の出力を両波整流したプラス側の信号を出力するプラス出力検波回路 2 1、該プラス出力検波回路 2 1 の出力の平均値を検出するプラス側平均値検出回路 2 2、前記プラス出力検波回路 2 1 の出力のピーク値を検出するプラス側ピーク値検出回路 2 3、及び、前記プラス側ピーク値検出回路 2 2 の出力と前記プラス側平均値検出回路 2 3 の出力により制御されるプラス側リミター回路 2 4 が設けられており、マイナス側にも同様に、マイナス出力検波回路 2 5、マイナス側平均値検出回路 2 6、マイナス側ピーク値検出回路 2 7 及びマイナス側リミター回路 2 8 が設けられている。

ここで、前記ピーク値検出回路(23,27)は、前記検波回路(21,25)の出力の瞬時値を検出するものであり、前記平均値検出回路(22,26)は前記検波回路(21,25)の出力の平均値又は実効値を検出するものである。

#### [0013]

このように構成された増幅回路において、入力信号は、前記入力アンプ1で電圧増幅されてPWM変調回路31に入力され、ここでパルス幅変調信号に変換される。PWM変調回路31の出力によりドライバ32が駆動され、出力トランジスタ33,34がオンオフ制御されて、インダクタンスLとキャパシタンスCとからなるローパスフィルタを介しスピーカ6が駆動される。このスピーカ6に流れる負荷電流に比例する電圧が前記抵電に出るの両端に発生し、ゲインが大きくされていない電流検出アンプ5により増幅されて、のミター回路2に入力される。電圧リミター回路2のプラス出力検波回路21からはつりに記憶は、プラス側で信号が出力され、プラス側ピーク値を開いる。でで、それぞれそのピーク値と平均値を検出回路23とプラス側平均値検出回路22とで、それぞれそのピーク値と平均値をして、それらがあらかじめ定めたそれぞれの所定の基準値以上のときにプラス側リミター回路24が作動し、入力アンプ1の電圧出力のプラス側の振幅を制限する。同様に、マイナス側では対象により入力アンプ1の出力電圧のマイナス側の振幅が制限される。

## [0014]

このように、この実施の形態においては、前記プラス側平均値検出回路22及びマイナス側平均値検出回路26により、負荷電流の平均値が所定の基準値以上であることを検出し

て入力電圧の振幅を制限するとともに、プラス側ピーク値検出回路 2 3 及びマイナス側ピーク値検出回路 2 7 により負荷電流の瞬時値が所定の基準値以上であるときにも入力電圧の振幅を制限するようにしている。これにより、連続最大出力とダイナミックパワーの両者を独立して制御することができる。

また、プラス側とマイナス側それぞれに検波回路、平均値検出回路、ピーク値検出回路を 設け、それらによりプラス側リミター回路とマイナス側リミター回路を制御するようにし ている。これにより、リミット処理を確実に行うことができる。

### [0015]

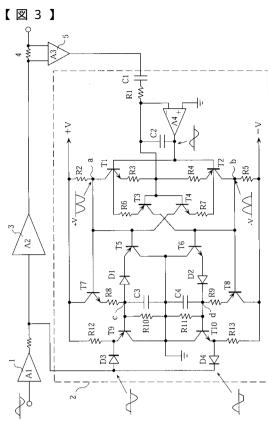

図3は、前記図2における電圧リミター回路の具体的な構成例を示す図である。この図において、入力アンプ1、電圧リミター回路2、パワーアンプ3、抵抗4、電流検出アンプ5は前述のものと同様である。

前記抵抗4の両端に発生する負荷電流に比例する電圧は電流検出アンプ5で増幅され、その交流成分がコンデンサC1と抵抗R1の直列回路を介して増幅器A4の反転入力に供給される。増幅器A4の出力端と前記反転入力との間にコンデンサC2が接続されている。なお、前述のように電流検出アンプ5のゲインは大きくされていない。

正電源 + Vと負電源 - Vとの間に、抵抗R2、npnトランジスタT1のコレクタ、トランジスタT1のエミッタ、抵抗R3、抵抗R4、pnpトランジスタT2のエミッタ、トランジスタT2のコレクタ、抵抗R5が直列に接続されている。前記トランジスタT1のベースとトランジスタT2のベースには前記増幅器A4の出力(コンデンサC2の一端)が接続されており、前記抵抗R3とR4の接続点には前記コンデンサC2の他端が接続されている。

また、前記抵抗R2と前記トランジスタT1のコレクタとの接続点(a点)と前記増幅器A4の出力端との間にnpnトランジスタT4のコレクタ、トランジスタT4のエミッタ、抵抗R7が直列に接続されており、前記抵抗R5と前記トランジスタT2のコレクタとの接続点(b点)と前記増幅器A4の出力端との間にpnpトランジスタT3のコレクタ、トランジスタT3のエミッタ、抵抗R6が直列に接続されている。そして、前記トランジスタT3とT4のベースは相互に接続され、前記コンデンサC2の他端が接続されている。

これらトランジスタT1~T4、抵抗R2~R7の回路により、前記増幅器A4の出力が両波整流される。すなわち、前記増幅器A4の出力が正のとき、前記トランジスタT1が導通し、トランジスタT3も導通する。また、前記増幅器A4の出力が負のとき、前記トランジスタT2が導通し、トランジスタT4も導通する。これにより、a点には正電源から前記増幅器A4の出力を両波整流した出力を減算した電圧(プラス側の検波出力)が生じ、b点には負電源に前記増幅器A4の出力を両波整流した電圧を加算した電圧(マイナス側の検波出力)が生じる。

#### [0016]

前記a点は、コレクタが接地に接続されたpnpトランジスタT5のベースに接続されるとともに、正電源 + Vにコレクタが接続されたnpnトランジスタT7のベースに接続されている。そして、前記npnトランジスタT7のエミッタには抵抗R8の一端が接続されており、該抵抗R8の他端には、カソードが前記pnpトランジスタT5のエミッタに接続されているダイオードD1のアノードが接続されている。前記抵抗R8と前記ダイオードD1のアノードの接続点(c点)と接地との間には、抵抗R10とコンデンサC3が並列に接続されており、また、c点は、エミッタが抵抗R12を介して正電源 + Vに接続され、コレクタが接地に接続されたpnpトランジスタT9のベースに接続されている。そして、pnpトランジスタT9のエミッタには、アノードが前記入力アンプ1の出力に接続されたダイオードD3のカソードが接続されている。

これらにより、前記図 2 に示した電圧リミター回路におけるプラス側平均値検出回路 2 2 、プラス側ピーク値検出回路 2 3 及びプラス側リミター回路 2 4 が実現されている。

# [0017]

一方、前記 b 点は、コレクタが接地に接続された n p n トランジスタT6のベースに接続されるとともに、負電源 - V にコレクタが接続された p n p トランジスタT8のベースに接続されている。そして、前記 p n p トランジスタT8のエミッタには抵抗R9の一端が接続され、該抵抗R9の他端は、アノードが前記 n p n トランジスタT6のエミッタに接続されたダイ

20

10

30

40

オードD2のカソードに接続されている。前記抵抗R9と前記ダイオードD2のカソードとの接続点(d点)と接地との間には抵抗R11とコンデンサC4とが並列に接続されており、d点は、コレクタが接地に接続され、エミッタが抵抗R13を介して負電源 - Vに接続された n p n トランジスタT10のベースに接続されている。そして、前記 n p n トランジスタT10のエミッタには、カソードが前記入力アンプ 1 の出力に接続されたダイオードD4のアノードが接続されている。

これらにより、前記図2におけるマイナス側平均値検出回路26、マイナス側ピーク値検 出回路27及びマイナス側リミター回路28が実現されている。

#### [0018]

このような構成において、前記a点の電圧に応じてトランジスタT7が導通する期間に、正電源 + Vを抵抗R8とR10で分圧した電圧がコンデンサC3にチャージされる。また、トランジスタT7が非導通の期間には該コンデンサC3にチャージされた電圧は抵抗R10を介して放電する。これにより、c点の電圧は、a点に生じたプラス側両波整流電圧の平均値に対応した電圧となる。そして、前記入力アンプ1の出力電圧と前記c点の電圧の差が、(ダイオードD3の順方向電圧降下 + トランジスタT9のエミッタ・ベース間電圧 = 約1.2V)以上であるときに、該ダイオードD3及びトランジスタT9が導通し、入力アンプ1の出力電圧を(c点の電圧 + ダイオードD3の順方向電圧降下 + トランジスタT9のエミッタ・ベース間電圧)より大きくならないように制限する。このようにして出力電流の平均値が、前記抵抗R8、R10及びコンデンサC3により決定される所定の基準値以上となったときに、入力アンプ1の出力のプラス側の振幅を制限することができる。

#### [0019]

また、前記 a 点の電圧が瞬間的に大きく低下し所定の基準値よりも下がったときには、トランジスタT5が導通し、前記入力アンプ 1 の出力電圧が(ダイオードD3の順方向電圧降下+トランジスタT9のエミッタ・ベース間電圧 + ダイオードD1の順方向電圧降下 + トランジスタT5のエミッタ・ベース間電圧 + a 点の電圧)以上とならないように制限する。これにより、瞬時最大電力(ダイナミックパワー)が所定値以上とならないように制御することができる。なお、前記基準値は、前記ダイオードD1の個数により変更することができる。

一方、マイナス側においても、前記トランジスタT6, T8, T10、ダイオードD2, D4、抵抗R9, R11, R13、コンデンサC4からなる回路が、同様に動作して、定格出力(連続最大出力)及び瞬時最大電力(ダイナミックパワー)がそれぞれ設定した値以上にならないように制御することができる。

ここで、前述のように、前記電流検出アンプ5のゲイン(大きくされていない)と、前記抵抗R8,R10,コンデンサC3からなる回路の時定数又は抵抗R9,R11,コンデンサC4からなる回路の時定数を、出力電流が大きくなるに応じてリミット電圧を徐々に下げていく帰還量の少ない動作となるように設定している。

このように、定格出力及びダイナミックパワーを負荷インピーダンスにかかわらずほぼー 定とすることができ、また、それぞれの値を独立に設定することができる。

# [0023]

#### 【発明の効果】

以上説明したように、本発明の増幅回路によれば、例えば、2 から8 までの負荷に対してほとんど同じ最大出力電力にすることが可能になる。これにより、アンプの発熱などの負担が少なくなる。逆に、発熱量を同等にした場合、8 時の最大出力を大きく設定できる。

また、電圧リミター回路を用いて最大出力を制限しているため、通常のアンプの電圧クリップと同様のクリップ波形となる。そして、クリップ時においてもアンプの出力は定電圧特性を保ちクリップ波形がきれいなため音楽再生中にクリップしても通常のアンプのクリップ時と同等の音質となりそれ以上の異音は発生しない。

さらに、連続最大出力とダイナミックパワーを独立してコントロールできるので、アンプの用途に適した設定が可能となる。

20

30

40

10

### 【図面の簡単な説明】

- 【図1】 本発明の増幅回路の第1の実施の形態の構成を示すブロック図である。

- 【図2】 本発明の増幅回路の第2の実施の形態の構成を示すブロック図である。

- 【図3】 本発明の増幅回路における電圧リミター回路の一構成例を示す回路図である。

# 【符号の説明】

1 入力アンプ、2 電圧リミター回路、3 パワーアンプ、4 抵抗、5 電流検出ア ンプ、6 スピーカー、2.1 プラス出力検波回路、2.2 プラス側平均値検出回路、2. 3 プラス側ピーク値検出回路、24 プラス側リミター回路、25 マイナス出力検波 回路、26 マイナス側平均値検出回路、27 マイナス側ピーク値検出回路、28 マ イナス側リミター回路、3.1 PWM変調回路、3.2 ドライバ回路、3.3,3.4 MO SFET

# 【図1】

# 【図2】

# フロントページの続き

# 審査官 野元 久道

(56)参考文献 特表平11-502382(JP,A)

特開昭59-040713(JP,A)

特開平04-079505(JP,A)

特開平08-330874(JP,A)

特開平06-031966(JP,A)

(58)調査した分野(Int.CI., DB名)

H03F 1/52

H03F 3/183

H03F 3/217