(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6067402号

(P6067402)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

F 1

HO2P 6/18 (2016.01)

HO2P 27/08 (2006.01)HO2P 6/18

HO2P 27/08

請求項の数 3 (全 13 頁)

(21) 出願番号 特願2013-25531 (P2013-25531)

(22) 出願日 平成25年2月13日 (2013.2.13)

(65) 公開番号 特開2014-155408 (P2014-155408A)

(43) 公開日 平成26年8月25日 (2014.8.25)

審査請求日 平成27年10月6日 (2015.10.6)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 110000567

特許業務法人 サトー国際特許事務所

(72) 発明者 前川 佐理

東京都港区芝浦一丁目1番1号 株式会社

東芝内

審査官 森山 拓哉

最終頁に続く

(54) 【発明の名称】モータ制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

3相ブリッジ接続された複数のスイッチング素子を所定の PWM 信号パターンに従いオンオフ制御することで、直流を3相交流に変換するインバータ回路を介してモータを駆動するモータ制御装置において、

前記インバータ回路の直流側に接続され、電流値に対応する信号を発生する電流検出素子と、

前記モータの相電流に基づいてロータ位置を決定し、前記ロータ位置に追従するように3相の PWM 信号パターンを生成する PWM 信号生成手段と、

前記電流検出素子に発生した信号と前記 PWM 信号パターンとに基づいて、前記モータの相電流を検出する電流検出手段と、

前記 PWM 信号パターンのデューティを補正するデューティ補正手段とを備え、

前記 PWM 信号生成手段は、前記3相の PWM 信号のうち、デューティが最大となる相については、搬送波周期の任意の位相を基準として遅れ側、進み側の双方向にデューティを増減させ、

デューティが最小となる相については、前記搬送波周期の任意の位相を基準として遅れ側、進み側の一方向にデューティを増減させ、

デューティが前記2相の中間となる相については、前記搬送波周期の任意の位相を基準として前記方向とは逆方向にデューティを増減させることで、前記電流検出手段が、前記 PWM 信号の搬送波周期内で固定された2点のタイミングで2相の電流を検出可能となる

10

20

ように 3 相の PWM 信号パターンを生成し、

前記デューティ補正手段は、前記各相のデューティの増減方向を変化させる切り換えの前後において、デューティを増減して補正することを特徴とするモータ制御装置。

【請求項 2】

前記デューティ補正手段は、デューティの増減方向が、前記双方向から前記進み方向又は遅れ方向に切り換わる相と、前記進み方向又は遅れ方向から前記双方向に切り換わる相を、補正の対象とすることを特徴とする請求項 1 記載のモータ制御装置。

【請求項 3】

前記デューティ補正手段は、前記切り換え後のデューティパルスによるオンタイミングが、切り換え前のデューティパルスのオフタイミングに近付く相については、切り換え後のデューティを減少させ、

前記オンタイミングが前記オフタイミングよりも遠ざかる相については、切り換え前のデューティを増加させることを特徴とする請求項 2 記載のモータ制御装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、インバータ回路の直流部に配置される電流検出素子によって相電流を検出するモータ制御装置に関する。

【背景技術】

【0002】

モータを制御するために U, V, W 各相の電流を検出する場合、インバータ回路の直流部に挿入した 1 つのシャント抵抗を用いて電流検出を行う技術がある。この方式で 3 相の全ての電流を検出するには、PWM (Pulse Width Modulation, パルス幅変調) キャリア (搬送波) の 1 周期内において、2 相以上の電流を検出できるように 3 相の PWM 信号パターンを発生させる必要がある。このような電流の検出を確実に行うため、特許文献 1 に開示されているように、各相の PWM 信号パルスをシフトすることが考えられる。

【0003】

しかし、単純にパルスをシフトするだけでは、シフトパターンが移行するタイミングでモータ電流がステップ状に変化する場合があり、この時の電流変化がトルクの変動を引き起こし、モータの駆動時に発生する騒音のレベルが増大するという問題が生じる。そこで、特許文献 2 には、PWM 信号のシフトパターンが変化しないように PWM 信号パルスの配置を設定することで、電流検出率の向上を図ると共に電流リップル及びそれに付随する騒音の増加を抑制する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特許第 3447366 号公報

【特許文献 2】特開 2012-70591 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献 2 の技術では、騒音の増大を抑制する目的から、電流検出率の向上は変調率が高い領域において一部制限されている。ここで、各 PWM 生成法による電流検出率について比較する。直流電流の検出に必要な最小パルス幅 [s] は、デッドタイム時間、電流検出回路の遅延時間等で決まる。また、最小パルス幅  $D_{min}$  と PWM 周期  $T$  [s] とから、電流検出に必要な最小デューティ  $D_{min}$  [%] は (1) 式で求められる。

$$D_{min} = 2 / T \times 100 \quad \dots (1)$$

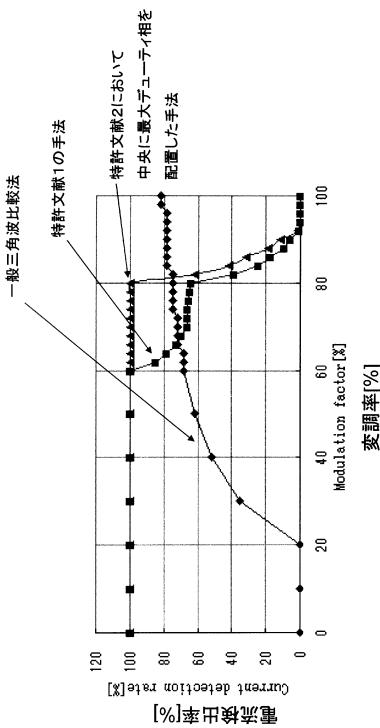

ここで、変調率を直流電源電圧に対するインバータの線間電圧振幅に対する割合と定義し、図 15 には、 $= 10$  [μs], PWM 周期 100 [μs] とした場合、各方式の変調率に応じた電流検出率を示す。電流検出率は電気角 1 周期中に 2 相以上の電流が検出で

10

20

30

40

50

きる区間の割合として算出している。

【0006】

一般的な三角波比較法では、変調率が低い領域で電流検出できない区間が多いが、特許文献1による手法では改善されている。これに対し、固定していたPWM配置を可変とする手法、具体的には特許文献2においてキャリア周期の中央に配置するパルスを3相のうちデューティが最大を示す相となるように配置すると、変調率が高い領域での電流検出率が向上する。しかしながら、この結果、トルクリップルが増加してモータの駆動騒音は悪化してしまう。

【0007】

そこで、単一の電流検出素子によりモータに供給される各相の電流を、変調率が高い領域においても電流検出率を向上させながら駆動騒音を抑制できるモータ制御装置を提供する。

10

【課題を解決するための手段】

【0008】

実施形態のモータ制御装置によれば、PWM信号生成手段は、モータの相電流に基づいてロータ位置を決定すると、ロータ位置に追従するように3相のPWM信号パターンを生成し、電流検出手段は、インバータ回路の直流側に接続される電流検出素子に発生した信号とPWM信号パターンとに基づいてモータの相電流を検出する。PWM信号生成手段は、具体的には、3相のPWM信号のうちデューティが最大となる相は、搬送波周期の任意の位相を基準として遅れ側、進み側の双方向にデューティを増減させ、デューティが最小となる相は、搬送波周期の任意の位相を基準として遅れ側、進み側の一方向にデューティを増減させ、デューティが前記2相の中間となる相は、搬送波周期の任意の位相を基準として前記方向とは逆方向にデューティを増減させる。

20

【0009】

これにより、電流検出手段が、PWM信号の搬送波周期内で固定された2点のタイミングで2相の電流を検出可能となるように3相のPWM信号パターンを生成する。そして、デューティ補正手段は、PWM信号パターンのデューティについて、各相のデューティの増減方向を変化させる切り換えの前後において、デューティを増減して補正する。

【図面の簡単な説明】

【0010】

30

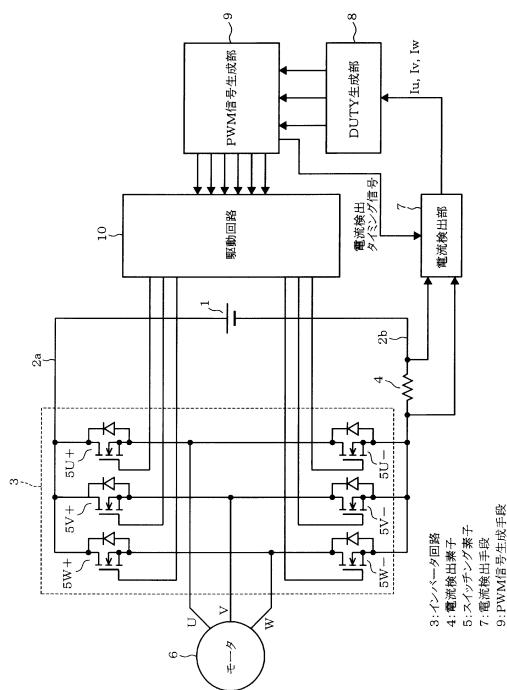

【図1】第1実施形態であり、モータ制御装置の構成を示す機能ブロック図

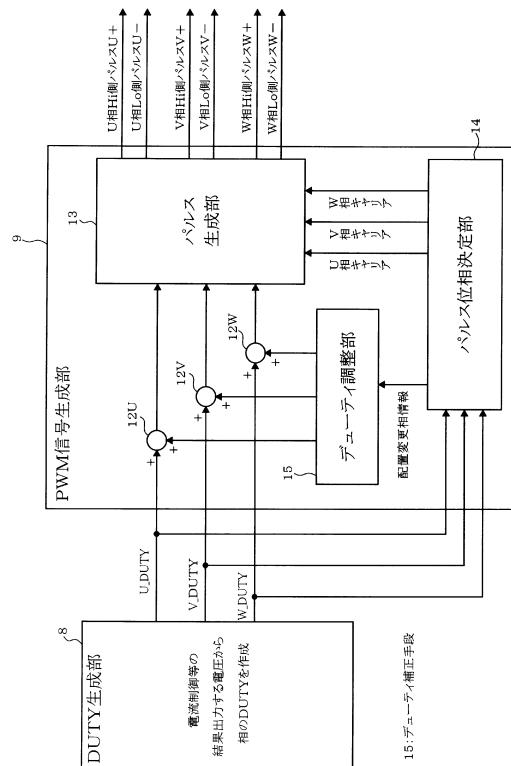

【図2】PWM信号生成部の内部構成を示す機能ブロック図

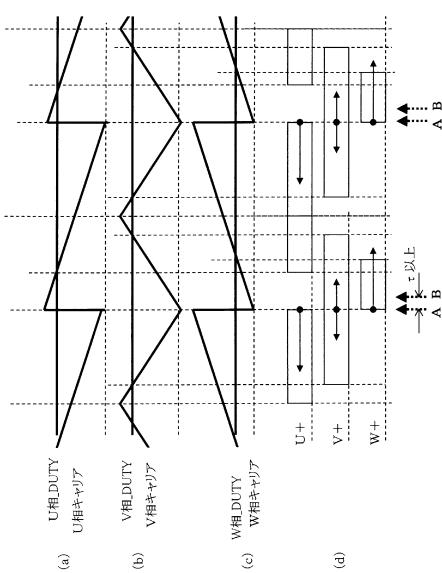

【図3】(a)～(c)は各相のPWMキャリアとデューティ指令、(d)は各相PWM信号パルスの生成状態を示すタイミングチャート

【図4】3相PWMパターンに応じて検出されるモータ電流を示す図

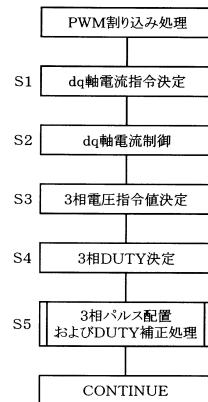

【図5】PWMキャリアの周期毎に発生する割り込み処理を示すフローチャート

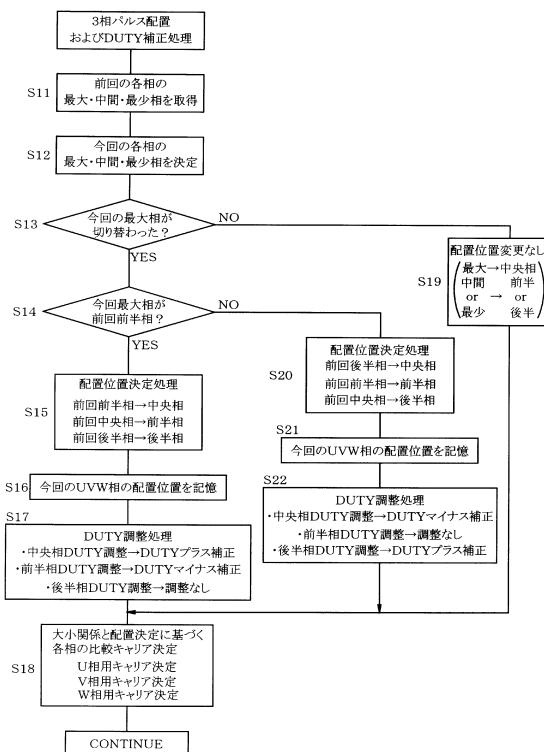

【図6】パルス位相決定部及びデューティ調整部で行われる処理を示すフローチャート

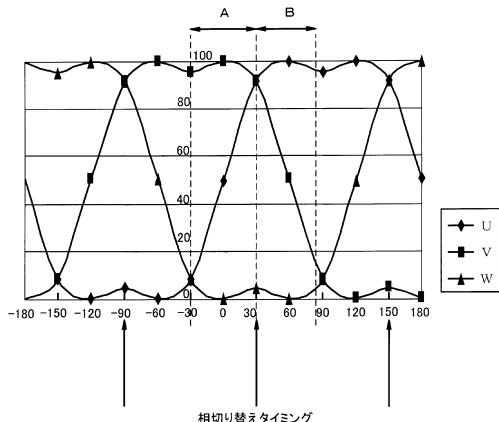

【図7】3相PWMデューティの大小関係が変化するタイミングを示す図

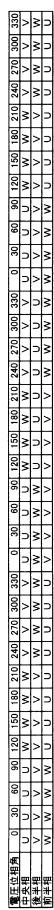

【図8】パルス位置の変更ルールのテーブルを示す図

【図9】(a)、(b)は、パルス位置の切り換え前後でデューティの増減を行った状態を説明する図

40

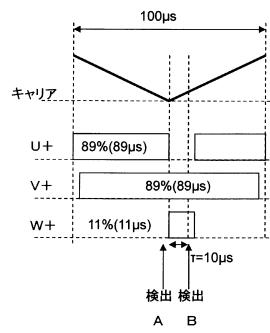

【図10】特許文献2の図9相当図

【図11】特許文献2の手法でW相を中央配置とすることを仮定した場合の図10相当図

【図12】第2実施形態を示す図2相当図

【図13】特許文献2の図16相当図

【図14】特許文献2の図17相当図

【図15】従来技術について電流検出率を説明する図

【発明を実施するための形態】

【0011】

(第1実施形態)

50

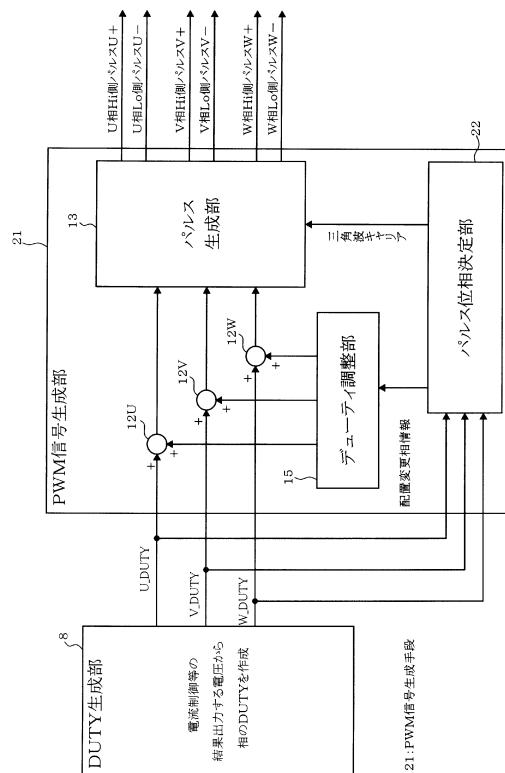

以下、第1実施形態について図1ないし図11を参照して説明する。図1は、モータ制御装置の構成を示す機能ブロック図である。直流電源部1は、直流電源のシンボルで示しているが、商用交流電源から直流電源を生成している場合には、整流回路や平滑コンデンサ等を含んでいる。直流電源部1には、正側母線2a、負側母線2bを介してインバータ回路(直流交流変換器)3が接続されているが、負側母線2b側には電流検出素子であるシャント抵抗4が挿入されている。インバータ回路3は、例えばNチャネル型のパワーMOSFET5(U+, V+, W+, U-, V-, W-)を3相ブリッジ接続して構成されており、各相の出力端子は、例えばブラシレスDCモータからなるモータ6の各相巻線にそれぞれ接続されている。

## 【0012】

10

シャント抵抗4の端子電圧(電流値に対応した信号)は電流検出部7により検出され、電流検出部(電流検出手段)7は、前記端子電圧とインバータ回路3に出力される3相のPWM信号パターンとに基づいてU, V, W各相の電流Iu, Iv, Iwを検出する。電流検出部7が検出した各相電流は、DUTY生成部8に与えられA/D変換されて読み込まれると、モータ6の制御条件等に基づいて演算が行われる。その結果、各相のPWM信号を生成するためのデューティU\_DUTY, V\_DUTY, W\_DUTYが決定される。

## 【0013】

図5は、PWMキャリアの周期毎に発生する割り込み処理を示すフローチャートである。例えばベクトル制御を行う場合であれば、DUTY生成部8には、制御条件を設定するマイクロコンピュータ等からモータ6の回転速度指令refが与えられると、推定したモータ6の実際の回転速度との差分に基づいてトルク電流指令Iqrefが生成される(S1)。また、d軸電流指令値は、全界磁(=0), 強め界磁(+), 弱め界磁運転の何れかを行なうかに応じて、極性及び値が決定される。

20

## 【0014】

モータ6の各相電流Iu, Iv, Iwからはモータ6のロータ位置が決定されると、そのロータ位置を用いるベクトル制御演算によりトルク電流Iq, 励磁電流Idが算出される(S2)。トルク電流指令Iqrefとトルク電流Iqとの差分に対して例えばPI制御演算が行われ、電圧指令Vqが生成される。励磁電流Id側についても同様に処理されて電圧指令Vdが生成され、電圧指令Vq, Vdが上記ロータ位置を用いて三相電圧Vu, Vv, Vwに変換される(S3)。そして、これらの三相電圧Vu, Vv, Vwに基づいて、各相デューティU, V, W\_DUTYが決定される(S4)。続くステップS5で行われる「3相パルス配置及びデューティ補正処理」については、後述する。

30

## 【0015】

各相デューティU, V, W\_DUTYは、PWM信号生成部(PWM信号生成手段)9に与えられ、搬送波とのレベルが比較されることで3相PWM信号が生成される。また、3相PWM信号を反転させた下アーム側の信号も生成されて、必要に応じてデッドタイムが付加された後、それらが駆動回路10に出力される。駆動回路10は、与えられたPWM信号に従い、インバータ回路3を構成する6つのパワーMOSFET5(U+, V+, W+, U-, V-, W-)の各ゲートに、ゲート信号を出力する(上アーム側については、必要なレベルだけ昇圧した電位で出力する)。

40

## 【0016】

次に、PWM信号生成部9が3相PWM信号を生成する方式について説明する。インバータ回路3がPWM変調された3相交流を出力する際には、前述したように、上アーム側のFET5(U+, V+, W+)に対する通電パターンに応じて特定の相の電流を検出できる。以下は、各相上アーム側のゲート信号について述べるが、例えばU相のみがHレベルとなり、V相及びW相が何れもLレベルとなる通電パターンの期間では、シャント抵抗4の両端に発生する電圧はU相電流に対応する。また、U相及びV相の両方がHレベルであり、W相がLレベルとなる区間では、シャント抵抗4の両端電圧の符号を反転したものがW相電流に対応する(図4参照)。

50

## 【0017】

このように、P W M信号の通電パターンに応じて2相分の電流を順次検出して記憶すれば、時分割的ではあるが3相分の電流を検出できる。この場合、各相電流を同時に検出してはいないので実際には誤差を生じるが、特別な厳密さが要求されなければ実用上問題はなく、3相分の電流検出値を用いて回路方程式を解くことで、次の周期の通電パターンを算出できる。

## 【0018】

また、F E T 5のオン、オフ状態が変化した直後は電流波形が安定しないので、シャント抵抗4に発生した電圧信号を安定した状態で読み込むために最小待機時間（安定時間）が必要である（詳細については、特許文献2参照）。また、本実施形態では、基本的に特許文献2に開示されている方式を用いることで、各相のP W M信号パルスの出力位相を各相のデューティの大きさに応じてシフトさせる。10

## 【0019】

図2は、P W M信号生成部9の内部構成を示すもので、図3は、P W M信号生成部9の内部で上アーム側の3相P W M信号（U +, V +, W +）のパルスが生成される状態を示すタイミングチャートであり、これらは特許文献2の図2、図3相当図である。図2では、D U Y T 増減部11に換えて、パルス位相決定部14及びデューティ調整部15が配置されている。D U T Y生成部8より入力された各相デューティU, V, W—D U T Yは、D U Y T調整部15によって調整値が出力された場合に、加算器12U, 12V, 12Wを介してデューティが加算（又は減算）される。そして、加算器12U, 12V, 12Wの出力信号は、パルス生成部13に入力され、U, V, W各相のキャリア（搬送波）とのレベルが比較された結果、各相のP W M信号U ±, V ±, W ±が生成される。20

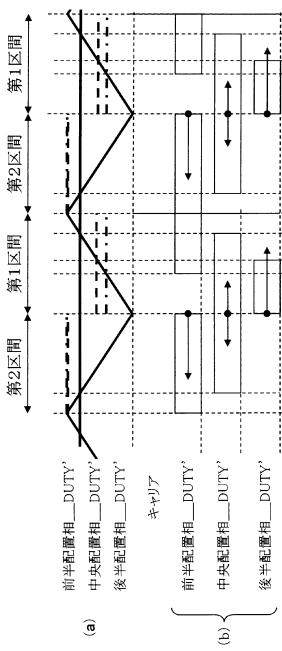

## 【0020】

パルス生成部13に対しては、パルス位相決定部14より選択されて出力される各相毎に異なる波形のキャリアを使用する。図3（a）～（c）に示すように、例えばU相キャリアは鋸歯状波であり、V相キャリアは三角波、W相キャリアはU相に対して逆相となる鋸歯状波である。3相のうち何れの相に対して三角波、上昇鋸波、下降鋸波となる各キャリアを割り当てるかを切り換えるパルス位相決定部14については後述する。キャリア周期は、例えば100 μsecとする。

## 【0021】

パルス生成部13では、各相デューティU, V, W—D U T Yと各相キャリアとのレベルをそれぞれ比較して、（デューティ）>（キャリア）となる期間にハイレベルパルスを出力する。その結果、図3（d）に示すように、V相キャリアの振幅最小位相（三角波の谷）を基準位相とすると、U相のP W M信号パルスU +は、基準位相から遅れ方向側（図中左側；後半）に増減するようにパルス幅が変化し、W相のP W M信号パルスW +は、基準位相から進み方向側（図中右側；前半）に増減するようにパルス幅が変化し、V相のP W M信号パルスV +は、基準位相から遅れ、進みの両方向側（中央）に増減するようにパルス幅が変化する。以上の処理が、図5に示すステップS5の「3相パルス配置」に対応する。30

## 【0022】

また、パルス位相決定部14は、上述のように3種類の波形をそれぞれ何れの割り当たか（すなわち、各相デューティパルスの配置変更情報）を示す情報、すなわち各相デューティパルスの配置変更情報を、デューティ調整部15に出力する。そして、デューティ調整部15は、上記配置変更情報に基づいて対象とする相のデューティパルスを増減させるように調整する。40

## 【0023】

次に、本実施形態の特徴的な作用について図6から図11を参照して説明する。図6は、パルス位相決定部14及びデューティ調整部15によって行われる処理を示すフローチャートである。パルス位相決定部14は、先ず前回の周期で決定されて記憶されているデューティの最大、中間、最小を取得すると（S11）、今回の周期における各相デューテ

10

20

30

40

50

イ U , V , W \_ D U T Y の大小関係を評価して最大 , 中間 , 最小を決定する ( S 1 2 ) 。

**【 0 0 2 4 】**

続くステップ S 1 3 では、ステップ S 1 1 , S 1 2 の処理結果を比較して、今回デューティが最大となる相が前回と切り換わったか否かを判断する。ここで、最大相が切り換わらなければ ( N O ) 、各相のパルス配置位置は従前通りとする ( 変更なし ; S 1 9 ) 。すなわち、デューティが最大の相は中央に、中間又は最小となる相は前半又は後半に配置される。そして、デューティが最大となる相のキャリアを三角波に、中間と最小となる相については、上昇鋸波 , 下降鋸波の何れでも良い ( S 1 8 ) 。但し、ステップ S 1 3 で最大相が切り換わり 「 Y E S 」 と判断した場合は、以下に説明するルールが適用される。

**【 0 0 2 5 】**

10

3 相のデューティは、3 相変調であれば電圧位相角に応じて図 7 に示すように発生するので、各相のデューティの大小関係 ( 最大・中間・最小 ) が変化するタイミングは 6 回ある。また、最大デューティ相が変化するタイミングは 3 回である。例えば、図中 A の区間では、各相のデューティの大小関係とキャリア、及びデューティパルスの発生位置が下記のように規定されているとする。

|                |           |

|----------------|-----------|

| 最大相 U ( 三角波 )  | パルスを中央に配置 |

| 中間相 V ( 上昇鋸波 ) | パルスを後半に配置 |

| 最小相 W ( 下降鋸波 ) | パルスを前半に配置 |

次に、位相角度が進んで区間 B の位置になると、各相デューティの大小関係は U , V , W の順になる。したがって、最大相である U 相は三角波キャリアと比較されることになるが、 V 相と W 相とについては、パルスの配置位置の変化が最も少くなるようにキャリア波形を切り換える。

20

**【 0 0 2 6 】**

例えば、図 7 に示す区間 A から B への移行においては、 W 相は区間 A において下降鋸波をキャリアとしてパルスは前半配置であるが、そこから後半配置に切り換えると変化が大きくなる。そこで、区間 B においても前半配置とする。一方、 V 相は区間 A において三角波キャリアでパルスは中央配置であるが、区間 B においては、上昇鋸波キャリアで後半配置に変更する。

**【 0 0 2 7 】**

30

図 8 は、上述した配置位置変更ルールを電圧位相角全般に亘って示したテーブルである。パルスを中央に配置する相、前半に配置する相、後半に配置する相が切り換わっていくが、同じタイミングで切り換わるのは 2 相に限定され、さらに配置位置の変更は、中央から前半或いは後半となり、 PWM 半周期分に限定される。これにより PWM 配置位置変更により電流リップルの増大と騒音悪化を抑えることができる。尚、図 8 には 3 電気角周期分のパターンを示しているが、パターンの変化は 2 周期分に亘り、 3 周期目では最初のパターンに戻っている。

**【 0 0 2 8 】**

40

そして、図 6 に示すフローチャートのステップ S 1 4 , S 1 5 , S 2 0 は、上記のルールに従ったものである。ステップ S 1 4 では、今回の最大相が前回の前半相であったか否かを判断し、「 Y E S 」 であればステップ S 1 5 に、「 N O 」 であればステップ S 2 0 に移行する。ステップ S 1 5 では、配置位置を以下のように決定する。

|       |     |

|-------|-----|

| 前回前半相 | 中央相 |

| 全回中央相 | 前半相 |

| 前回後半相 | 後半相 |

また、ステップ S 2 0 では、配置位置を以下のように決定する。

|       |     |

|-------|-----|

| 前回後半相 | 中央相 |

| 全回前半相 | 前半相 |

| 前回中央相 | 後半相 |

ステップ S 1 5 , S 2 0 の実行後は、今回の各相パルスの配置位置を記憶する ( S 1 6 , S 2 1 ) 。

50

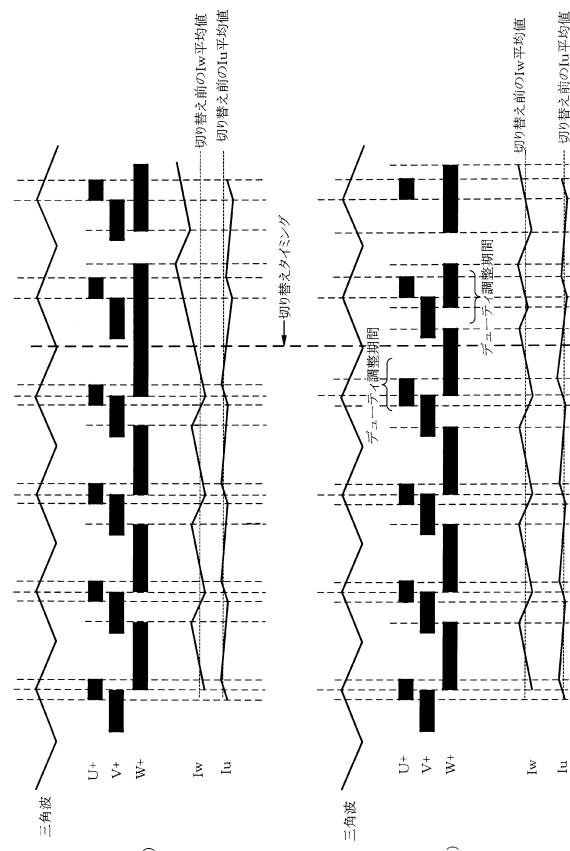

## 【0029】

次に、配置位置変更に伴い、各相のデューティ調整を行うデューティ調整部15について説明する。前述のように各相パルス配置位置を変更しても、PWM周期内における各相の印加電圧の変化は発生してしまう。図9(a)は、W相パルスの配置位置を後半から中央に変化させた場合の各相パルス状態とW相電流を示している。この時、配置変更に伴いW相の正側印加電圧期間が増加するため、W相電流は、配置切り換えのタイミングで正側にリップルを生じてしまう。

## 【0030】

そこで、デューティ調整部15は、配置変化に応じて各相デューティを増減調整することで、上記のようなリップルのレベルを抑制する。パルス位相決定部14による変更ルールにより、パルス位置の前半から後半へ、或いは後半から前半への配置変更は禁止されている。つまり、パルス位置の変更は、中央から前半或いは後半へか、その逆パターンに限定される。デューティ調整部15の調整ルールは、次のように規定される。

(1) 変更によりパルスの発生位置が近付く相は、デューティを減少させる

(2) 変更によりパルスの発生位置が遠ざかる相は、デューティを増加させる。

尚、「発生位置が近付く」とは、より厳密に言えば、前回のパルスのオフタイミング(立下り)と次回のパルスのオンタイミング(立ち上り)との間隔が短くなることであり、「発生位置が遠ざかる」とは、前記オフタイミングと前記オンタイミングとの間隔が長くなることである。

## 【0031】

ここで、図9に示す具体例で説明すると、図9(a)において、W相パルスの配置は、切り換えの前後で後半から中央へ変更されているので、上記のルール(1)に相当する。つまり、後半 中央に切り換わったため、発生位置が近づいている。したがって、図9(b)に示すように、デューティ調整部15はW相パルスのデューティを減少させる。また、U相パルスの配置は中央から後半に変更されているので、上記のルール(2)に相当する。したがって、図9(b)に示すように、デューティ調整部15は、U相パルスのデューティを、切り換えを行う前に増加させる。この結果、図9(b)に示すようにU相、W相の電流は、何れも切り換えの前後における振幅の変化量が小さくなり、リップルが抑制されている。これにより、モータ6の駆動騒音の増加を抑制できる。

## 【0032】

尚、デューティ調整部15で前述のルールに従って調整される増減値は、配置変更が前半(後半) 中央配置の場合は、変更前デューティの1/4程度を目安とし、実験的に騒音が最も軽減できる値を選定することが望ましい。例えば、デッドタイムの設定値が幾つになるかにもよる。

## 【0033】

図6に示すステップS22は、上述した図9のケースに対応したデューティ調整処理である。一方、ステップS17は、ステップS15のように配置変更した場合であるから、今回の中央相には調整ルール(2)が適用され、前半相には調整ルール(1)が適用される。そして、後半相については調整しない。

尚、図9(b)に示すU相パルスのように、パルス配置の変更を行う以前にデューティを調整するには、そのための時間余裕を持たせる必要がある。例えば、

- ・キャリア周期  $100 \mu s$  に対して、デューティの切り換え周期は  $200 \mu s$  にする。

- ・デューティの切り換えはキャリアの谷で行い、デューティ値の更新はキャリアの山で行うようにする。

などの手法を採用すれば良い。

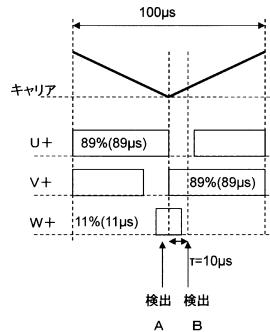

## 【0034】

また図10は、特許文献2の図9相当図であり、電気角が300度で、U、V相のデューティが等しく89%、W相デューティが11%の場合である。このとき、W相は三角波の谷から遅れ側(図中右側)に11%付近までパルスが発生する。この時、デッドタイム =  $10 \mu sec$ に設定されていても、デューティ11%のパルス幅は  $11 \mu sec$  であるため

10

20

30

40

50

、やはり2回の検出タイミングA、Bにおいて、2相の電流が問題なく検出できる。これに対し、特許文献2の手法でW相を中央配置とすることを仮定すると図11のようになり、三角波谷から両側へ5.5μsecずつ延びるパルスが発生するため、時間以下となって、2相の電流が検出できない。

#### 【0035】

尚、図10及び図11では、1回目の電流検出タイミングAを、実際に検出対象となる相を明確にするため、図3等の図示よりも進み側にずらした状態で示している。

以上のように本実施形態によれば、PWM信号生成部9は、モータ6の相電流に基づいてロータ位置を決定すると、ロータ位置に追従するように3相のPWM信号パターンを生成し、電流検出部7は、インバータ回路3の直流側に接続されるシャント抵抗4に発生した信号とPWM信号パターンとに基づいてモータ6の相電流Iu、Iv、Iwを検出する。PWM信号生成部9は、具体的には、3相のPWM信号のうちデューティが最大となる相は、キャリア周期の任意の位相を基準として遅れ側、進み側の双方向にデューティを増減させ、デューティが最小となる相は、キャリア周期の任意の位相を基準として遅れ側、進み側の一方向にデューティを増減させ、デューティが前記2相の中間となる相は、キャリア波周期の任意の位相を基準として前記方向とは逆方向にデューティを増減させる。

#### 【0036】

これにより、電流検出部7が、キャリア周期内で固定された2点のタイミングで2相の電流を検出可能となるように3相のPWM信号パターンを生成する。そして、デューティ調整部15は、PWM信号パターンのデューティについて、各相のデューティの増減方向を変化させる切り換えの前後において、デューティを増減して補正する。

#### 【0037】

具体的には、デューティの増減方向が、双方向から進み方向又は遅れ方向（中央相から前半相又は後半相）に切り換わる相と、進み方向又は遅れ方向から双方向（前半相又は後半相から中央相）に切り換わる相とを補正の対象として、切り換え後のデューティパルスによるオンタイミングが、切り換え前のデューティパルスのオフタイミングに近付く相については切り換え後のデューティを減少させ、前記オンタイミングが前記オフタイミングよりも遠ざかる相については切り換え前のデューティを増加させる。したがって、パルス発生位置の変更による電流リップル及びモータ駆動騒音の増加を抑制しながら、低変調率から高変調率まで電流検出率を向上させることができる。

#### 【0038】

##### （第2実施形態）

図12から図14は第2実施形態であり、第1実施形態と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。図12は図2相当図であり、PWM信号生成部21は、PWM信号生成部9におけるパルス位相決定部14を、パルス位相決定部22に置き換えたものである。第2実施形態は、特許文献2の第4実施形態を適用したものであり、パルス位相決定部22は三角波のキャリアのみをパルス生成部13に出力する。

#### 【0039】

図13及び図14は、特許文献2の図16及び図17相当図である。但し、これらの図では、各相をU、V、Wの具体的な例示ではなく、デューティの大小関係に応じてパルスの配置位置が決められる前半配置相、中央配置相、後半配置相で示している。この様に1種類のキャリアのみを用いてロジックにより各相デューティパルスの配置位置を決定する方式を用いた場合も、第1実施形態と同様の効果が得られる。

#### 【0040】

本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

10

20

30

40

50

電流検出部 7 が、キャリア周期内で 2 相の電流を検出するタイミングは、必ずしもキャリアのレベルが最小又は最大を示す位相を基準とする必要はなく、2 相の電流を検出可能な範囲でキャリアの任意の位相に基づいて設定すれば良い。

#### 【0041】

また、電流を検出するタイミングは、PWM キャリアの周期に一致させる必要はなく、例えばキャリア周期の 2 倍や 4 倍の周期で検出を行っても良い。したがって、電流検出部 7 に入力する電流検出タイミング信号は、キャリアそのものである必要はなく、例えばキャリアに同期して所定の周期を有するパルス信号であっても良い。

シャント抵抗 4 を、正側母線 2a に配置しても良い。また、電流検出素子はシャント抵抗 4 に限ることなく、例えば C T (Current Transformer) 等を設けても良い。

スイッチング素子は N チャネル型の M O S F E T に限ることなく、P チャネル型の M O S F E T や、I G B T , パワートランジスタ等を使用しても良い。

デューティの増減値については、変更前デューティの 1 / 4 程度を目安とするものに限らず、個別の設計に応じて適宜変更すれば良い。

#### 【符号の説明】

#### 【0042】

図面中、3 はインバータ回路、4 はシャント抵抗 (電流検出素子) 、5 はパワー M O S F E T (スイッチング素子) 、6 はモータ、7 は電流検出部 (電流検出手段) 、9 は P W M 信号生成部 (P W M 信号生成手段) 、13 はパルス生成部、14 はパルス位相決定部、15 はデューティ調整部 (デューティ補正手段) 、21 は P W M 信号生成部 (P W M 信号生成手段) 、22 はパルス生成部を示す。

【図 1】

【図 2】

【図3】

【図4】

| U相<br>Hi側FET | V相<br>Hi側FET | W相<br>Hi側FET | 1シャントで検出する<br>モーケ電流 |

|--------------|--------------|--------------|---------------------|

| オン           | オフ           | オフ           | +Iu                 |

| オン           | オン           | オフ           | -Iw                 |

| オフ           | オン           | オフ           | +Iv                 |

| オフ           | オン           | オン           | -Iu                 |

| オフ           | オフ           | オン           | +Iw                 |

| オン           | オフ           | オン           | -Iv                 |

| オフ           | オフ           | オフ           | 検出不可                |

| オン           | オン           | オン           | 検出不可                |

【図5】

【図6】

【図7】

【 四 8 】

【 図 1 0 】

【 図 1 1 】

【 四 9 】

【図12】

【図13】

【図14】

| 第1区間のセット値の変換                           |                                           | 第2区間のセット値の変換                              |                     |

|----------------------------------------|-------------------------------------------|-------------------------------------------|---------------------|

| 前半配置相DUTY'                             | 中央配置相DUTY'                                | 前半配置相DUTY'                                | 中央配置相DUTY'          |

| if 前半配置相DUTY×2 < キャリアMAX値<br>→キャリアMAX値 | if 次半配置相DUTY×2 < キャリアMAX値<br>→2×次半配置相DUTY | if 次半配置相DUTY×2 < キャリアMAX値<br>→2×次半配置相DUTY | else<br>→2×キャリアMAX値 |

【図15】

---

フロントページの続き

(56)参考文献 特開2012-070591(JP,A)

特開2009-118621(JP,A)

特開2009-131065(JP,A)

特開2013-066255(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02P 6/18

H02P 27/08