(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5959551号

(P5959551)

(45) 発行日 平成28年8月2日(2016.8.2)

(24) 登録日 平成28年7月1日(2016.7.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/822 | (2006.01) | HO1L 27/04 | H    |

| HO1L 27/04  | (2006.01) | HO1L 27/06 | 311C |

| HO1L 27/06  | (2006.01) | HO1L 29/72 | P    |

| HO1L 21/331 | (2006.01) | HO1L 29/74 | F    |

| HO1L 29/732 | (2006.01) | HO1L 27/06 | 101B |

請求項の数 33 外国語出願 (全 50 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2014-15212 (P2014-15212)    |

| (22) 出願日     | 平成26年1月30日 (2014.1.30)        |

| (65) 公開番号    | 特開2014-154883 (P2014-154883A) |

| (43) 公開日     | 平成26年8月25日 (2014.8.25)        |

| 審査請求日        | 平成28年2月4日 (2016.2.4)          |

| (31) 優先権主張番号 | 13/766,541                    |

| (32) 優先日     | 平成25年2月13日 (2013.2.13)        |

| (33) 優先権主張国  | 米国(US)                        |

早期審査対象出願

|           |                                    |

|-----------|------------------------------------|

| (73) 特許権者 | 501144003<br>アナログ・デバイシズ・インコーポレーテッド |

| (74) 代理人  | 100078282<br>弁理士 山本 秀策             |

| (74) 代理人  | 100113413<br>弁理士 森下 夏樹             |

| (74) 代理人  | 100181674<br>弁理士 飯田 貴敏             |

| (74) 代理人  | 100181641<br>弁理士 石川 大輔             |

最終頁に続く

(54) 【発明の名称】送受信機信号絶縁および電圧固定法のための装置、および同装置を形成する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

p型基板と、

前記p型基板の中に形成されるNPN双方向性トランジスタを形成するように構成される、第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域と、

前記第1のn型ウェル領域の中に配置される第1のp型活性領域、および前記第2のn型ウェル領域の中に配置される第2のp型活性領域と、

前記NPN双方向性トランジスタを包囲するp型タブであって、前記p型タブは、前記第1のn型ウェル領域、前記第2のn型ウェル領域および前記第1のp型ウェル領域と物理的に接触する、p型タブと、

前記p型タブを包囲するn型タブと、

前記n型タブを包囲するp型エピタキシャル領域と

を備え、

前記第1のn型ウェル領域、前記p型タブ、および前記n型タブは、第1の寄生NPNバイポーラトランジスタを形成するように構成され、

前記p型エピタキシャル領域、前記n型タブ、および前記p型タブは、寄生PNPバイポーラトランジスタを形成するように構成される、

装置。

## 【請求項 2】

前記p型エピタキシャル領域は、前記寄生PNPバイポーラトランジスタのエミッタを

形成するように構成され、前記 n 型タブは、前記寄生 PNP バイポーラトランジスタの基部を形成するように構成される、請求項 1 に記載の装置。

【請求項 3】

前記寄生 PNP バイポーラトランジスタの前記エミッタおよび前記基部は、前記 p 型エピタキシャル領域の中に形成される第 1 の抵抗器を通して接続される、請求項 2 に記載の装置。

【請求項 4】

前記寄生 PNP バイポーラトランジスタの前記 p 型エピタキシャル領域および前記 n 型タブはさらに、前記 p 型基板上に形成される第 2 の抵抗器を通して電気的に接続され、前記第 2 の抵抗器および前記第 1 の抵抗器は、前記寄生 PNP バイポーラトランジスタの前記エミッタと前記基部との間に直列に電気的に接続される、請求項 3 に記載の装置。

10

【請求項 5】

前記 p 型エピタキシャル領域、前記 n 型タブ、前記 p 型タブ、および前記第 1 の n 型ウェル領域は、第 1 の寄生 PNPN シリコン制御整流器を形成するように構成される、請求項 1 に記載の装置。

【請求項 6】

前記 p 型タブは、前記 p 型基板の中に配置される p 型深ウェル層と、前記第 1 の n 型ウェル領域の第 1 の側面に隣接する第 2 の p 型ウェル領域と、前記第 2 の n 型ウェル領域の第 1 の側面に隣接する第 3 の p 型ウェル領域とを備え、前記 p 型深ウェル層、前記第 2 の p 型ウェル領域、および前記第 3 の p 型ウェル領域は、連続して電気的に接続される、請求項 3 に記載の装置。

20

【請求項 7】

前記 p 型タブは、電気的に浮動しているように構成される、請求項 6 に記載の装置。

【請求項 8】

前記第 2 の n 型ウェル領域、前記 p 型タブ、および前記 n 型タブは、第 2 の寄生 NPN バイポーラトランジスタを形成するように構成される、請求項 1 に記載の装置。

【請求項 9】

前記 p 型エピタキシャル領域および前記 n 型タブ、前記 p 型タブ、および前記第 2 の n 型ウェル領域は、第 2 の寄生 PNPN シリコン制御整流器を形成するように構成される、請求項 1 に記載の装置。

30

【請求項 10】

前記 n 型タブは、前記 p 型基板の中に配置される n 型埋め込み層と、前記 p 型タブの第 1 の側面に隣接する第 3 の n 型ウェル領域と、前記 p 型タブの第 2 の側面に隣接する第 4 の n 型ウェル領域とを備える、請求項 3 に記載の装置。

【請求項 11】

前記第 3 の n 型ウェル領域の第 1 の側面に隣接する第 4 の p 型ウェル領域と、前記第 4 の n 型ウェル領域の第 1 の側面に隣接する第 5 の p 型ウェル領域とをさらに備える、請求項 10 に記載の装置。

【請求項 12】

前記第 4 の n 型ウェル領域および前記第 5 の p 型ウェル領域に隣接する前記 p 型基板上に形成される、第 2 の抵抗器をさらに備える、請求項 11 に記載の装置。

40

【請求項 13】

前記第 1 の n 型ウェル領域の中に配置される第 1 の n 型活性領域と、前記第 2 の n 型ウェル領域の中に配置される第 2 の n 型活性領域とをさらに備える、請求項 1 に記載の装置。

【請求項 14】

第 1 のパッドおよび第 2 のパッドをさらに備え、前記第 1 のパッドは、前記第 1 の n 型活性領域および前記第 1 の p 型活性領域に電気的に接続され、前記第 2 のパッドは、前記第 2 の n 型活性領域および前記第 2 の p 型活性領域に電気的に接続される、請求項 13 に記載の装置。

50

## 【請求項 1 5】

基板電位において前記 p 型基板に電気的に接続される第 3 の p 型活性領域の間の第 1 の電気的接続と、前記基板電位における第 1 のまたは第 2 のパッドのうちの 1 つと前記 p 型基板との間の第 2 の電気的接続とをさらに備える、請求項 1 4 に記載の装置。

## 【請求項 1 6】

前記第 1 の電気的接続は、第 1 の抵抗を有し、前記第 2 の電気的接続は、第 2 の抵抗を有し、前記第 1 の抵抗は、前記第 2 の抵抗よりも高い、請求項 1 5 に記載の装置。

## 【請求項 1 7】

前記第 3 の p 型活性領域は、前記寄生 P N P バイポーラトランジスタのエミッタに電気的に接続される、請求項 1 5 に記載の装置。 10

## 【請求項 1 8】

p 型基板と、

前記 p 型基板の中に形成される N P N 双方向性トランジスタを形成するように構成される、第 1 の n 型ウェル領域、第 2 の n 型ウェル領域、および第 1 の p 型ウェル領域と、

前記 N P N 双方向性トランジスタを包囲する p 型タブであって、前記 p 型タブは、前記第 1 の n 型ウェル領域、前記第 2 の n 型ウェル領域および前記第 1 の p 型ウェル領域と物理的に接触する、p 型タブと、

前記 p 型タブを包囲する n 型タブと、

前記 n 型タブを包囲する p 型エピタキシャル領域と

を備え、 20

前記第 1 の n 型ウェル領域、前記 p 型タブ、および前記 n 型タブは、第 1 の寄生 N P N バイポーラトランジスタを形成するように構成され、

前記 p 型エピタキシャル領域、前記 n 型タブ、および前記 p 型タブは、寄生 P N P バイポーラトランジスタを形成するように構成され、

前記 p 型エピタキシャル領域は、前記寄生 P N P バイポーラトランジスタのエミッタを形成するように構成され、前記 n 型タブは、前記寄生 P N P バイポーラトランジスタの基部を形成するように構成され、

前記寄生 P N P バイポーラトランジスタの前記エミッタおよび前記基部は、前記 p 型エピタキシャル領域の中に形成される第 1 の抵抗器を通して接続され、

前記 n 型タブは、前記 p 型基板の中に配置される n 型埋め込み層と、前記 p 型タブの第 1 の側面に隣接する第 3 の n 型ウェル領域と、前記 p 型タブの第 2 の側面に隣接する第 4 の n 型ウェル領域とを備え、 30

前記 N P N 双方向性トランジスタは、環状構成で配列され、前記第 1 の p 型ウェルは、前記第 1 の n 型ウェルを同心円状に包囲し、前記第 2 の n 型ウェルは、前記第 1 の p 型ウェルを同心円状に包囲する、

装置。

## 【請求項 1 9】

前記 p 型タブの第 3 の p 型ウェルは、前記 N P N 双方向性トランジスタを包囲し、前記 n 型タブの前記第 4 の n 型ウェルは、前記第 3 の p 型ウェルを包囲し、前記 p 型エピタキシャル領域は、前記第 4 の n 型ウェルを包囲する、請求項 1 8 に記載の装置。 40

## 【請求項 2 0】

前記 p 型エピタキシャル領域は、前記 p 型基板に電気的に接続される、請求項 1 に記載の装置。

## 【請求項 2 1】

前記第 5 の p 型ウェル領域の第 1 の側面に隣接する第 5 の n 型ウェル領域と、前記第 5 の n 型ウェル領域の第 1 の側面に隣接する第 6 の p 型ウェル領域とをさらに備え、前記 p 型エピタキシャル領域は、前記第 5 の p 型ウェル領域、前記第 5 の n 型ウェル領域、および前記第 6 の p 型ウェル領域のそれぞれより下側に配置される、請求項 1 1 に記載の装置。

## 【請求項 2 2】

10

20

30

40

50

前記第1の抵抗器は、少なくとも部分的に前記p型エピタキシャル領域に由来する、第1の抵抗器の抵抗を有する、請求項21に記載の装置。

【請求項23】

前記第1の抵抗器は、前記第5のp型ウェル領域および前記第6のp型ウェル領域にさらに由来する、第1の抵抗を有する、請求項22に記載の装置。

【請求項24】

p型基板と、

前記p型基板の中の第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域であって、前記第1のn型ウェル領域、前記第2のn型ウェル領域、および前記第1のp型ウェル領域は、前記p型基板の中にNPN双方向性トランジスタを形成するように構成される、第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域と、

前記NPN双方向性トランジスタを包囲するp型タブであって、前記p型タブは、前記第1のn型ウェル領域、前記第2のn型ウェル領域および前記第1のp型ウェル領域と物理的に接觸する、p型タブと、

前記p型タブを包囲するn型タブと、

前記n型タブを包囲するp型エピタキシャル領域と、

前記第1のn型ウェル領域の中に配置される第1のp型活性領域であって、前記第1のp型活性領域、前記第1のn型ウェル領域、および前記p型タブは、第1のPNPバイポーラトランジスタを形成するように構成される、第1のp型活性領域と、

前記第2のn型ウェル領域の中に配置される第2のp型活性領域であって、前記第2のp型活性領域、前記第2のn型ウェル領域、および前記p型タブは、第2のPNPバイポーラトランジスタを形成するように構成される、第2のp型活性領域と

を備え、

前記p型エピタキシャル領域、前記n型タブ、および前記p型タブは、寄生PNPバイポーラトランジスタを形成する、

装置。

【請求項25】

前記p型エピタキシャル領域は、前記p型基板に電気的に接続される、請求項24に記載の装置。

【請求項26】

前記NPN双方向性トランジスタ、前記第1のPNPバイポーラトランジスタ、および前記第2のPNPバイポーラトランジスタは、第1のバイポーラPNPNP双方向性構造を形成する、請求項24に記載の装置。

【請求項27】

前記p型エピタキシャル領域は、前記寄生PNPバイポーラトランジスタのエミッタを形成するように構成され、前記n型タブは、前記寄生PNPバイポーラトランジスタの基部を含むように構成される、請求項24に記載の装置。

【請求項28】

前記寄生PNPバイポーラトランジスタのエミッタおよび基部は、前記p型エピタキシャル領域の第1の抵抗器を通して接続される、請求項24に記載の装置。

【請求項29】

前記寄生PNPバイポーラトランジスタの前記p型エピタキシャル領域および前記n型タブはさらに、前記p型基板上に形成される第2の抵抗器を通して電気的に接続され、前記第2の抵抗器および前記第1の抵抗器は、前記エミッタと前記基部との間で直列に電気的に接続される、請求項28に記載の装置。

【請求項30】

前記p型タブは、電気的に浮動しているように構成される、請求項24に記載の装置。

【請求項31】

前記n型タブは、前記p型基板の中に配置されるn型埋め込み層と、前記p型タブの第

10

20

30

40

50

1の側面に隣接する第3のn型ウェル領域と、前記p型タブの第2の側面に隣接する第4のn型ウェル領域とを備える、請求項24に記載の装置。

【請求項32】

前記NPN双方向性トランジスタは、環状構成で配列され、前記第1のp型ウェルは、前記第1のn型ウェルを同心円状に包囲し、前記第2のn型ウェルは、前記第1のp型ウェルを同心円状に包囲する、請求項24に記載の装置。

【請求項33】

前記p型タブの第3のp型ウェルは、前記NPN双方向性トランジスタを包囲し、前記n型タブの第4のn型ウェルは、前記第3のp型ウェルを包囲し、前記p型エピタキシャル領域は、前記第4のn型ウェルを包囲する、請求項32に記載の装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、電子機器に関し、より具体的には、静電放電からの通信送受信機の保護に関する。

【背景技術】

【0002】

特定の電子システムは、過渡電気的事象または急速に変化する電圧および高温を有する比較的短い持続時間の電気信号に曝露され得る。過渡電気的事象は、例えば、物体または個人から電子システムへの急激な電荷放出から生じる、電気的超過ストレス／静電放電（EOS／ESD）事象を含み得る。

20

【0003】

過渡電気的事象は、過電圧状態および／または比較的小さい区域のICに及ぶ高水準の電力散逸による電子システム内の集積回路（IC）を損傷する可能性がある。高電力の散逸は、IC温度を上昇させ得、ゲートの酸化物パンチスルーや接合部損傷、金属損傷、および表面電荷蓄積等、多くの問題に至る可能性がある。更に、過渡電気的事象は、ラッチアップ（換言すれば、低インピーダンス経路の偶発的発生）を誘発し、それによってICの機能を混乱させ、潜在的にはICの恒久的損傷を引き起こす可能性がある。

【発明の概要】

【課題を解決するための手段】

30

【0004】

一実施形態では、装置が、p型半導体基板上に提供される。本装置は、半導体基板の中に形成されるNPN双方向性トランジスタを形成するように構成される、第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域を含む。本装置はさらに、NPN双方向性トランジスタを包囲するように構成されるp型タブと、p型タブを包囲するように構成されるn型タブと、n型タブを包囲するように構成されるp型エピタキシャル領域とを含み、第1のn型ウェル領域、p型タブ、およびn型タブは、第1のNPNバイポーラトランジスタを形成するように構成され、p型エピタキシャル領域、n型タブ、およびp型タブは、PNPバイポーラトランジスタを形成するように構成される。

【0005】

40

別の実施形態では、装置が、p型半導体基板上に提供される。本装置は、p型基板の第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域を含み、第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域は、p型半導体基板の中にNPN双方向性トランジスタを形成するように構成される。本装置はさらに、NPN双方向性トランジスタを包囲するp型タブと、p型タブを包囲するn型タブとを含む。本装置はさらに、第1のn型ウェル領域の中に配置される第1のp型活性領域を含み、第1のp型活性領域、第1のn型ウェル領域、およびp型タブは、第1のPNPバイポーラトランジスタを形成するように構成される。本装置はさらに、第2のn型ウェル領域の中に配置される第2のp型活性領域を含み、第2のp型活性領域、第2のn型ウェル領域、およびp型タブは、第2のPNPバイポーラトランジスタを形成するように構成され

50

、p型エピタキシャル領域、n型タブ、およびp型タブは、第3の寄生PNPバイポーラトランジスタを形成する。

【0006】

例えば、本願発明は以下の項目を提供する。

(項目1)

p型基板と、

上記p型基板の中に形成されるNPN双方向性トランジスタを形成するように構成される、第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域と、上記NPN双方向性トランジスタを包囲するp型タブと、

上記p型タブを包囲するn型タブと、

上記n型タブを包囲するp型エピタキシャル領域と、

を備え、

上記第1のn型ウェル領域、上記p型タブ、および上記n型タブは、第1の寄生NPNバイポーラトランジスタを形成するように構成され、

上記p型エピタキシャル領域、上記n型タブ、および上記p型タブは、寄生PNPバイポーラトランジスタを形成するように構成される、

装置。

(項目2)

上記p型エピタキシャル領域は、上記寄生PNPバイポーラトランジスタのエミッタを形成するように構成され、上記n型タブは、上記寄生PNPバイポーラトランジスタの基部を形成するように構成される、上記項目に記載の装置。

(項目3)

上記寄生PNPバイポーラトランジスタの上記エミッタおよび上記基部は、上記p型エピタキシャル領域の中に形成される第1の抵抗器を通して接続される、上記項目のいずれか一項に記載の装置。

(項目4)

上記寄生PNPバイポーラトランジスタの上記p型エピタキシャル領域および上記n型タブはさらに、上記p型基板上に形成される第2の抵抗器を通して電気的に接続され、上記第2の抵抗器および上記第1の抵抗器は、上記寄生PNPバイポーラトランジスタの上記エミッタと上記基部との間に直列に電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目5)

上記p型エピタキシャル領域、上記n型タブ、上記p型タブ、および上記第1のn型ウェル領域は、第1の寄生PNPNシリコン制御整流器を形成するように構成される、上記項目のいずれか一項に記載の装置。

(項目6)

上記p型タブは、上記p型基板の中に配置されるp型深ウェル層と、上記第1のn型ウェル領域の第1の側面に隣接する第2のp型ウェル領域と、上記第2のn型ウェル領域の第1の側面に隣接する第3のp型ウェル領域とを備え、上記p型深ウェル層、上記第2のp型ウェル領域、および上記第3のp型ウェル領域は、連続して電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目7)

上記p型タブは、電気的に浮動しているように構成される、上記項目のいずれか一項に記載の装置。

(項目8)

上記第2のn型領域、上記p型タブ、および上記n型タブは、第2の寄生NPNバイポーラトランジスタを形成するように構成される、上記項目のいずれか一項に記載の装置。

(項目9)

上記p型エピタキシャル領域および上記n型タブ、上記p型タブ、および上記第2のn型ウェル領域は、第2の寄生PNPNシリコン制御整流器を形成するように構成される、

10

20

30

40

50

上記項目のいずれか一項に記載の装置。

(項目 1 0)

上記 n 型タブは、上記 p 型基板の中に配置される n 型埋め込み層と、上記 p 型タブの第 1 の側面に隣接する第 3 の n 型ウェル領域と、上記 p 型タブの第 2 の側面に隣接する第 4 の n 型ウェル領域とを備える、上記項目のいずれか一項に記載の装置。

(項目 1 1)

上記第 3 の n 型ウェル領域の第 1 の側面に隣接する第 4 の p 型ウェル領域と、上記第 4 の n 型ウェル領域の第 1 の側面に隣接する第 5 の p 型ウェル領域とをさらに備える、上記項目のいずれか一項に記載の装置。

(項目 1 2) 上記第 4 の n 型ウェル領域および上記第 5 の p 型ウェル領域に隣接する上記 p 型基板上に形成される、第 2 の抵抗器をさらに備える、上記項目のいずれか一項に記載の装置。 10

(項目 1 3)

上記第 1 の n 型ウェル領域の中に配置される第 1 の p 型活性領域と、上記第 2 の n 型ウェル領域の中に配置される第 2 の p 型活性領域とをさらに備える、上記項目のいずれか一項に記載の装置。

(項目 1 4)

上記第 1 の n 型ウェル領域の中に配置される第 1 の n 型活性領域と、上記第 2 の n 型ウェル領域の中に配置される第 2 の n 型活性領域とをさらに備える、上記項目のいずれか一項に記載の装置。 20

(項目 1 5)

第 1 のパッドおよび第 2 のパッドをさらに備え、上記第 1 のパッドは、上記第 1 の n 型活性領域および上記第 1 の p 型活性領域に電気的に接続され、上記第 2 のパッドは、上記第 2 の n 型活性領域および上記第 2 の p 型活性領域に電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目 1 6)

基板電位において上記 p 型基板に電気的に接続される第 3 の p 型活性領域の間の第 1 の電気的接続と、上記基板電位における第 1 のまたは第 2 のパッドのうちの 1 つと上記 p 型基板との間の第 2 の電気的接続とをさらに備える、上記項目のいずれか一項に記載の装置。 30

(項目 1 7)

上記第 1 の電気的接続は、第 1 の抵抗を有し、上記第 2 の電気的接続は、第 2 の抵抗を有し、上記第 1 の抵抗は、上記第 2 の抵抗よりも高い、上記項目のいずれか一項に記載の装置。

(項目 1 8)

上記第 3 の p 型活性領域は、上記寄生 PNP バイポーラトランジスタの上記エミッタに電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目 1 9)

上記 NPN 双方向性トランジスタは、環状構成で配列され、上記 p 型ウェルは、上記第 1 の n 型ウェルを同心円状に包囲し、上記第 2 の n 型ウェルは、上記 p 型ウェルを同心円状に包囲する、上記項目のいずれか一項に記載の装置。 40

(項目 2 0)

上記 p 型タブの上記第 3 の p 型ウェルは、上記 NPN 双方向性トランジスタを包囲し、上記 n 型タブの上記第 4 の n 型ウェルは、上記第 3 の p 型ウェルを包囲し、上記 p 型エピタキシャル領域は、上記第 4 の n 型ウェルを包囲する、上記項目のいずれか一項に記載の装置。

(項目 2 1)

上記 p 型エピタキシャル領域は、上記 p 型基板に電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目 2 2)

50

上記第5のp型ウェル領域の第1の側面に隣接する第5のn型ウェル領域と、上記第5のn型ウェル領域の第1の側面に隣接する第6のp型ウェル領域とをさらに備え、上記p型エピタキシャル領域は、上記第5のp型ウェル領域、上記第5のn型ウェル領域、および上記第6のp型ウェル領域のそれぞれより下側に配置される、上記項目のいずれか一項に記載の装置。

(項目23)

上記第1の抵抗器は、少なくとも部分的に上記p型エピタキシャル領域に由来する、第1の抵抗器の抵抗を有する、上記項目のいずれか一項に記載の装置。

(項目24)

上記第1の抵抗器は、上記第5のp型ウェル領域および上記第6のp型ウェル領域にさらに由来する、第1の抵抗器の抵抗を有する、上記項目のいずれか一項に記載の装置。

(項目25)

p型基板と、

上記p型基板の中の第1のn型ウェル領域、第2のn型ウェル領域、および第1のp型ウェル領域であって、上記第1のn型ウェル領域、上記第2のn型ウェル領域、および上記第1のp型ウェル領域は、上記p型基板の中にNPN双方向性トランジスタを形成するように構成される、ウェル領域と、

上記NPN双方向性トランジスタを包囲するp型タブと、

上記p型タブを包囲するn型タブと、

上記n型タブを包囲するp型エピタキシャル領域と、

上記第1のn型ウェル領域の中に配置される第1のp型活性領域であって、上記第1のp型活性領域、上記第1のn型ウェル領域、および上記p型タブは、第1のPNPバイポーラトランジスタを形成するように構成される、第1のp型活性領域と、

上記第2のn型ウェル領域の中に配置される第2のp型活性領域であって、上記第2のp型活性領域、上記第2のn型ウェル領域、および上記p型タブは、第2のPNPバイポーラトランジスタを形成するように構成される、第2のp型活性領域と、

を備え、上記p型エピタキシャル領域、上記n型タブ、および上記p型タブは、寄生PNPバイポーラトランジスタを形成する、

装置。

(項目26)

上記p型エピタキシャル領域は、上記p型基板に電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目27)

上記NPN双方向性トランジスタ、上記第1のPNPバイポーラトランジスタ、および上記第2のPNPバイポーラトランジスタは、第1のバイポーラPNPNP双方向性構造を形成する、上記項目のいずれか一項に記載の装置。

(項目28)

上記p型エピタキシャル領域は、上記寄生PNPバイポーラトランジスタのエミッタを形成するように構成され、上記n型タブは、上記寄生PNPバイポーラトランジスタの基部を含むように構成される、上記項目のいずれか一項に記載の装置。

(項目29)

上記寄生PNPバイポーラトランジスタの上記エミッタおよび上記基部は、上記p型エピタキシャル領域の第1の抵抗器を通して接続される、上記項目のいずれか一項に記載の装置。

(項目30)

上記寄生PNPバイポーラトランジスタの上記p型エピタキシャル領域および上記n型タブはさらに、上記p型基板上に形成される第2の抵抗器を通して電気的に接続され、上記第2の抵抗器および上記第1の抵抗器は、上記エミッタと上記基部との間で直列に電気的に接続される、上記項目のいずれか一項に記載の装置。

(項目31)

10

20

30

40

50

上記 p 型タブは、電気的に浮動しているように構成される、上記項目のいずれか一項に記載の装置。

(項目 3 2)

上記 n 型タブは、上記 p 型基板の中に配置される n 型埋め込み層と、上記 p 型タブの第 1 の側面に隣接する第 3 の n 型ウェル領域と、上記 p 型タブの第 2 の側面に隣接する第 4 の n 型ウェル領域とを備える、上記項目のいずれか一項に記載の装置。

(項目 3 3)

上記 N P N 双方向性トランジスタは、環状構成で配列され、上記 p 型ウェルは、上記第 1 の n 型ウェルを同心円状に包囲し、上記第 2 の n 型ウェルは、上記 p 型ウェルを同心円状に包囲する、上記項目のいずれか一項に記載の装置。

(項目 3 4)

上記 p 型タブの上記第 3 の p 型ウェルは、上記 N P N 双方向性トランジスタを包囲し、上記 n 型タブの上記第 4 の n 型ウェルは、上記第 3 の p 型ウェルを包囲し、上記 p 型エピタキシャル領域は、上記第 4 の n 型ウェルを包囲する、上記項目のいずれか一項に記載の装置。

【0007】

(摘要)

過渡電気的事象からの送受信機信号絶縁および電圧固定法のための装置は、バイポーラ P N P N P 素子アセンブリと、第 1 の寄生 P N P N 素子アセンブリと、第 2 の寄生 P N P N 素子アセンブリとを備える、双方向性保護装置を含む。バイポーラ P N P N P 素子アセンブリは、N P N 双方向性バイポーラトランジスタと、第 1 の P N P バイポーラトランジスタと、第 2 の P N P バイポーラトランジスタとを含み、第 1 および第 2 のパッドを通して過渡電圧信号を受信するように構成される。第 1 および第 2 のパッドは、第 1 および第 2 の P N P バイポーラトランジスタのエミッタを通して P N P N P 素子アセンブリに電気的に接続される。バイポーラ P N P N P 素子アセンブリは、寄生 P N P バイポーラトランジスタと、第 1 の寄生 N P N バイポーラトランジスタとを備える、第 1 の寄生 P N P N 素子アセンブリに電気的に接続される。バイポーラ P N P N P 素子アセンブリはさらに、寄生 P N P バイポーラトランジスタと、第 2 の寄生 N P N バイポーラトランジスタとを備える、第 2 の寄生 P N P N 素子アセンブリに接続される。寄生 P N P バイポーラトランジスタの基部は、第 1 および第 2 の寄生 P N P N 素子アセンブリのトリガおよび絶縁破壊を防止するように、抵抗器を通して送受信機の基板に接続される。

【図面の簡単な説明】

【0008】

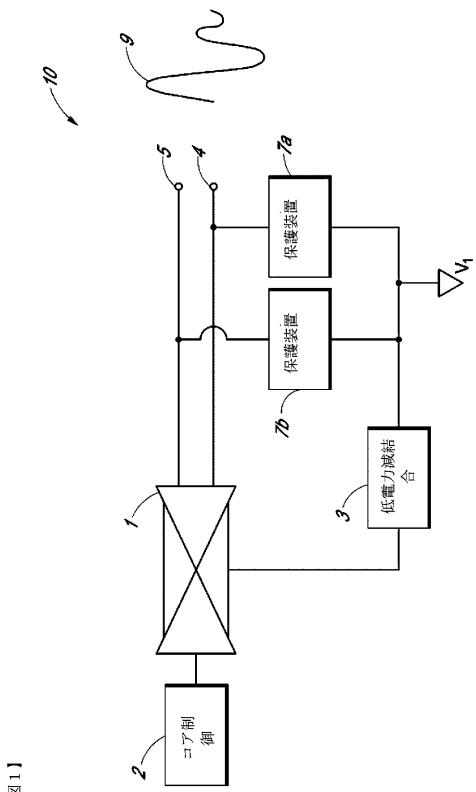

【図 1】図 1 は、送受信機システムの一実施例の概略ブロック図である。

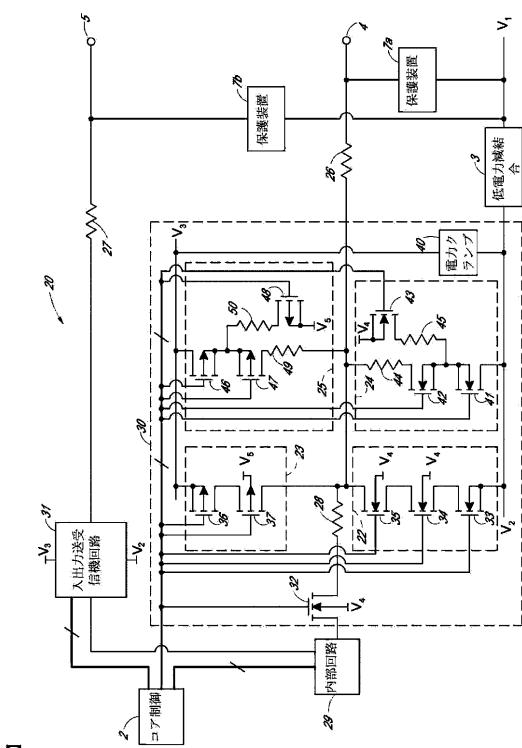

【図 2】図 2 は、一実施形態による、双方向性保護装置の電流と電圧との間の関係を示すグラフである。

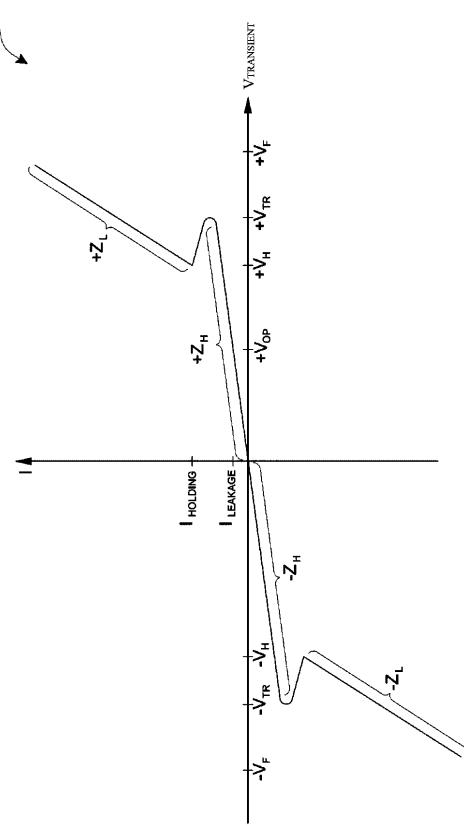

【図 3】図 3 は、送受信機システムインターフェースの一実施例の回路図である。

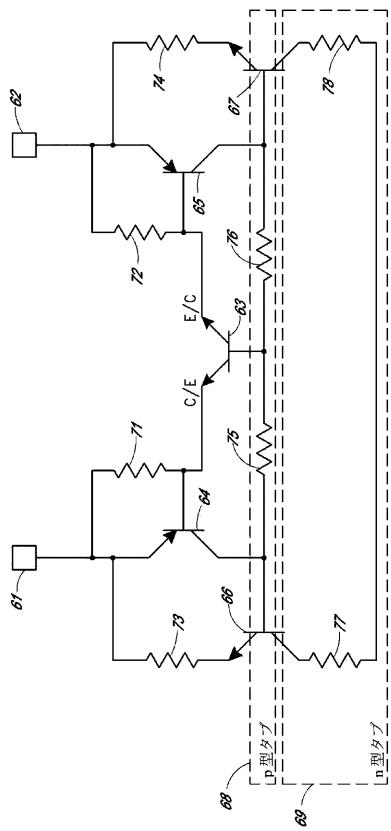

【図 4】図 4 は、一実施形態による、双方向性保護回路を図示する回路図である。

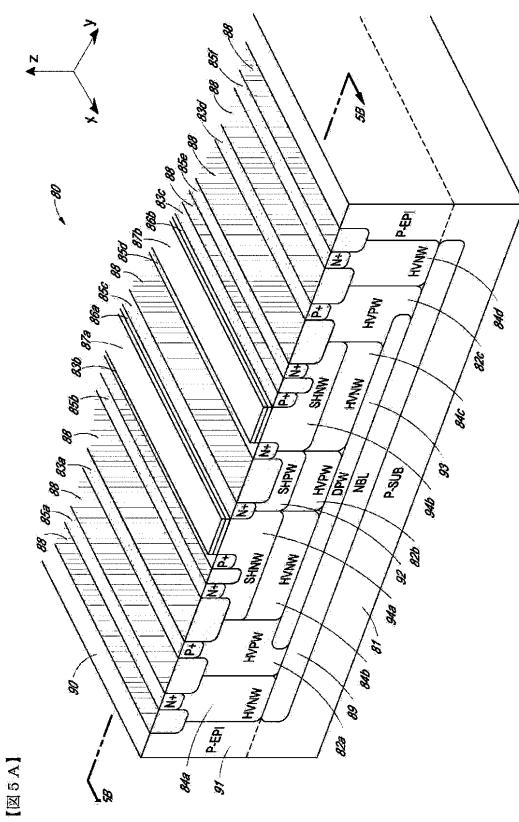

【図 5 A】図 5 A は、一実施形態による、図 4 の保護回路を実装する、二重タブ絶縁双方向性保護装置の概略斜視図である。

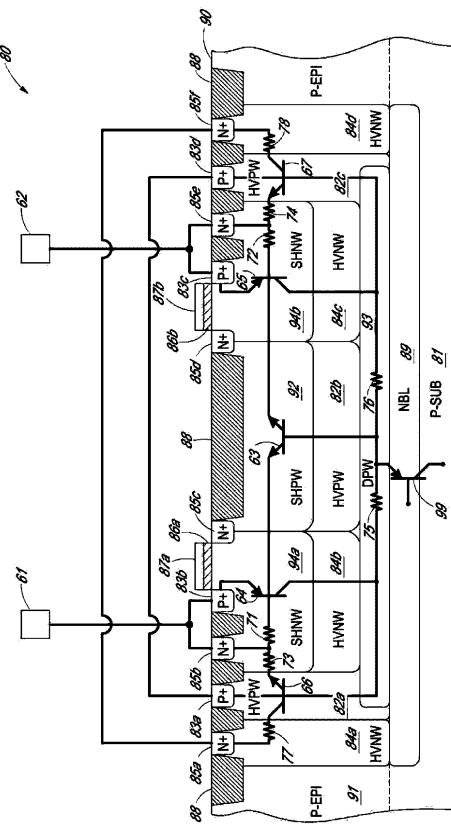

【図 5 B】図 5 B は、線 5 B - 5 B に沿って得られた図 5 A の二重タブ絶縁双方向性保護装置の注釈付き断面図である。

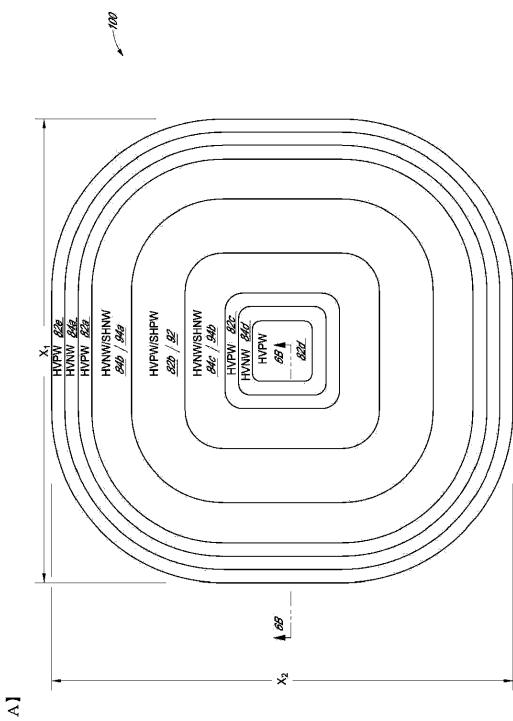

【図 6 A】図 6 A は、一実施形態による、二重タブ絶縁保護装置の概略上面レイアウト図である。

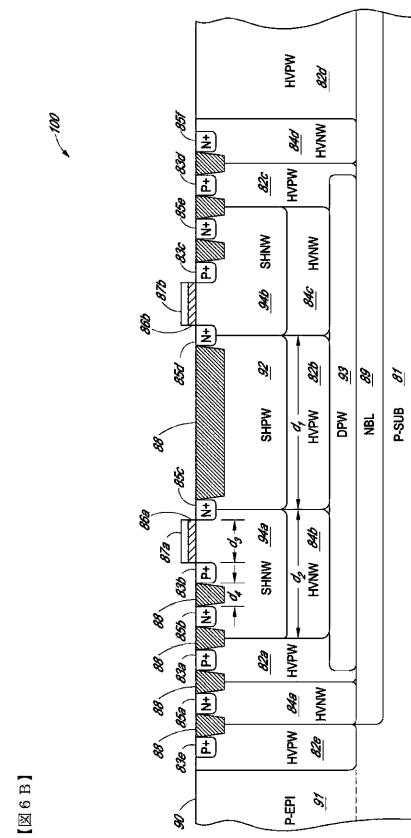

【図 6 B】図 6 B は、線 6 B - 6 B に沿って得られた図 6 A の二重タブ絶縁双方向性保護装置の注釈付き断面図である。

【図 7 A】図 7 A は、別の実施形態による、二重タブ絶縁双方向性保護装置の概略斜視図である。

【図 7 B】図 7 B は、さらに別の実施形態による、二重タブ絶縁双方向性保護装置の概略斜視図である。

10

20

30

40

50

【図8】図8は、別の実施形態による、二重タブ絶縁保護装置の断面図である。

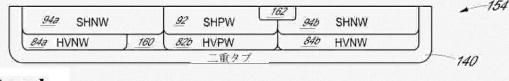

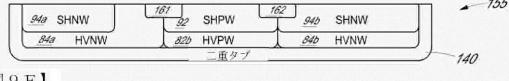

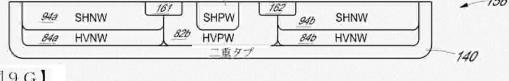

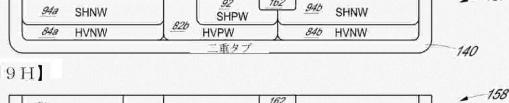

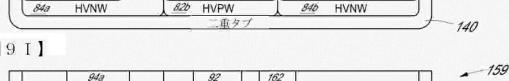

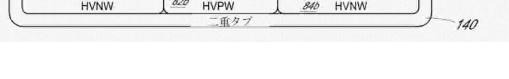

【図9】図9A～9Iは、例えば、精密送受信機の対称および非対称動作を提供するための可変幾何学的特徴を伴う、二重タブ絶縁双方向保護装置の種々の実施形態の部分断面図を図示する。

【図10】図10は、一実施形態による、送受信機信号絶縁および電圧固定法のための双方向性保護回路の概略図である。

【図11A】図11Aは、一実施形態による、送受信機信号絶縁および電圧固定法のための双方向性保護装置の注釈付き断面図である。

【図11B】図11Bは、別の実施形態による、受信機信号絶縁および電圧固定法のための双方向性保護装置の注釈付き断面図である。

【図12A】図12Aは、一実施形態による、送受信機信号絶縁および電圧固定法のための双方向性保護装置の概略上面レイアウト図である。

【図12B】図12Bは、別の実施形態による、送受信機信号絶縁および電圧固定法のための双方向性保護装置の概略上面レイアウト図である。

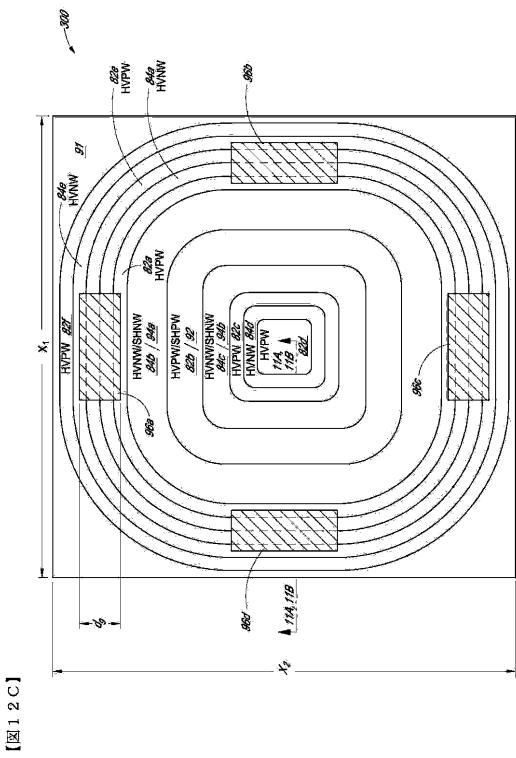

【図12C】図12Cは、さらに別の実施形態による、送受信機信号絶縁および電圧固定法のための双方向性保護装置の概略上面レイアウト図である。

【図12D】図12Dは、図12Cの送受信機信号絶縁および電圧固定法のための双方向性保護装置の概略詳細上面レイアウト図である。

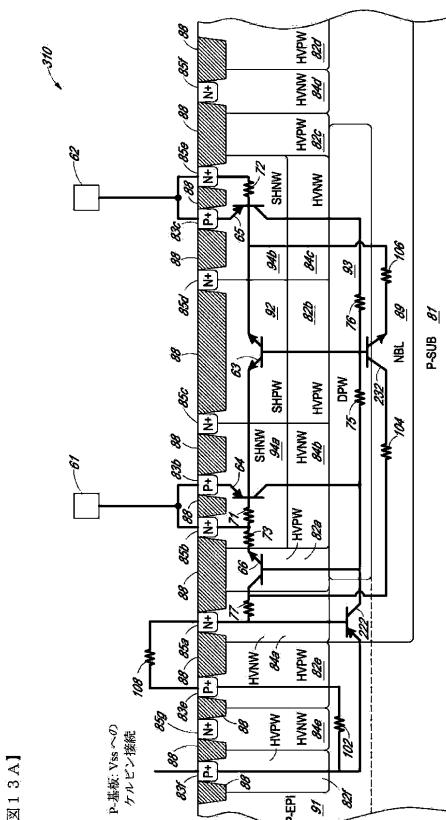

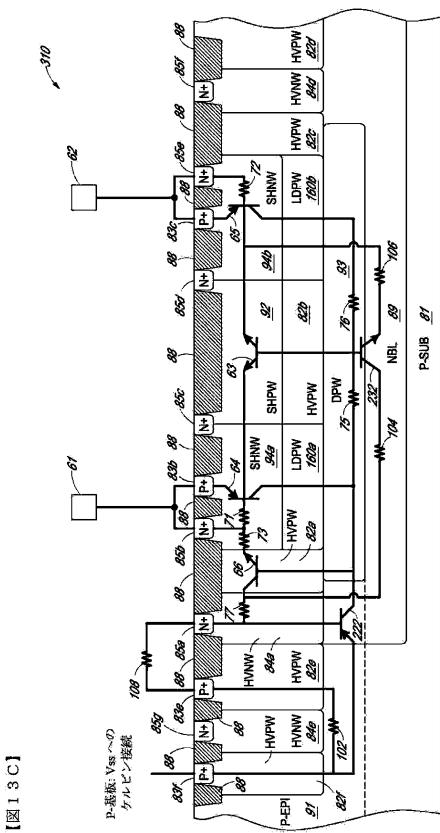

【図13A】図13Aは、図11Bに類似する実施形態による、送受信機信号絶縁のための双方向性保護装置の注釈付き断面図である。

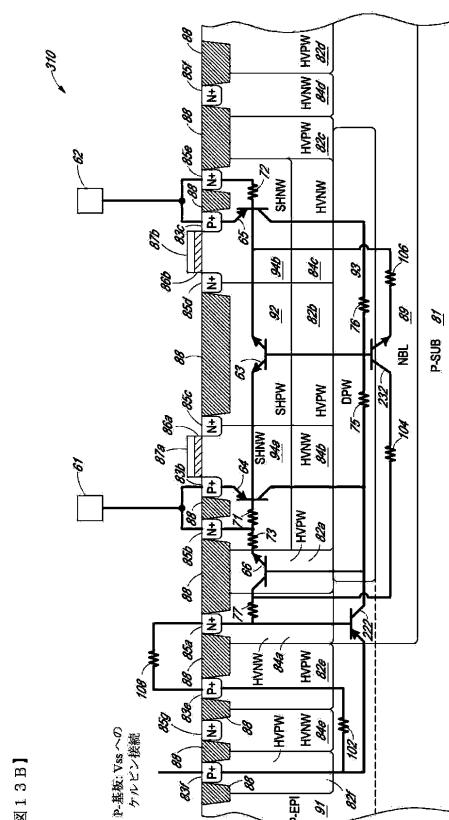

【図13B】図13Bは、図11Bに類似する別の実施形態による、送受信機信号絶縁のための双方向性保護装置の注釈付き断面図である。

【図13C】図13Cは、さらに別の実施形態による、送受信機信号絶縁のための双方向性保護装置の注釈付き断面図である。

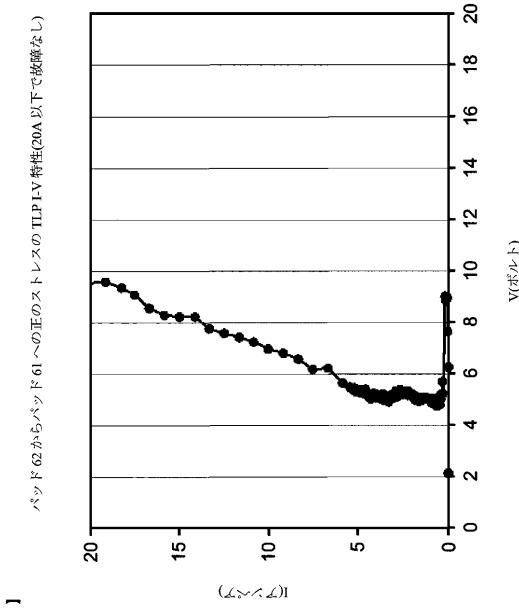

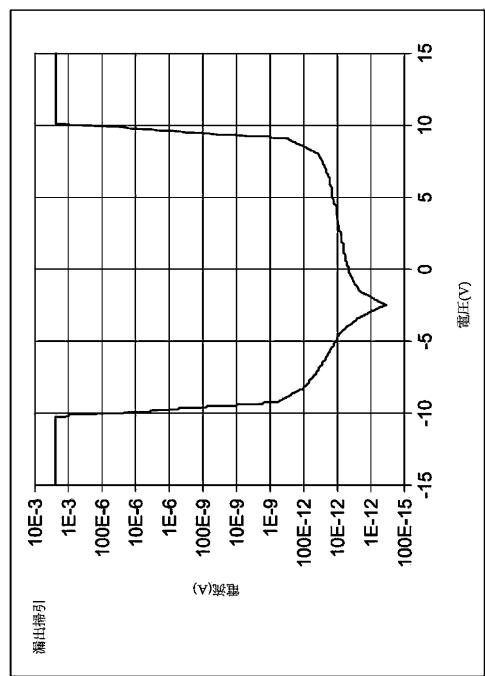

【図14A】図14Aは、一実施形態による、正および負の両方の電圧掃引において高インピーダンス状態にある送受信機信号絶縁のための双方向性保護装置の電流・電圧測定である。

【図14B】図14Bは、一実施形態による、正電圧掃引において高インピーダンス状態から低インピーダンス状態への遷移を図示する、送受信機信号絶縁のための双方向性保護装置の電流・電圧測定である。

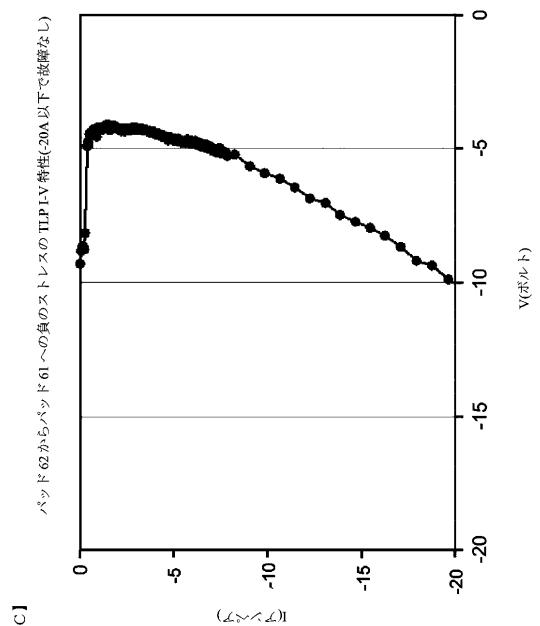

【図14C】図14Cは、一実施形態による、負電圧掃引において高インピーダンス状態から低インピーダンス状態への遷移を図示する、送受信機信号絶縁のための双方向性保護装置の電流・電圧測定である。

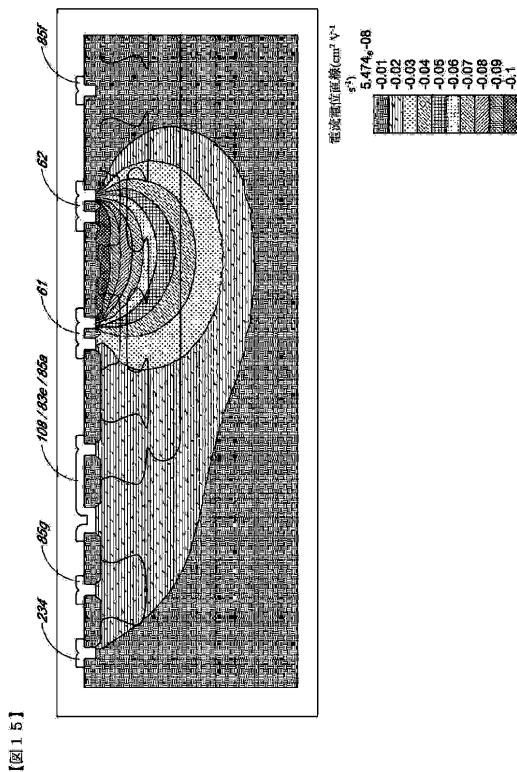

【図15】図15は、一実施形態による、送受信機信号絶縁のための双方向性保護装置のシミュレートした等電流の潜在的等高線の断面図である。

#### 【発明を実施するための形態】

##### 【0009】

特定の実施形態の以下の詳細な説明は、本発明の詳細な実施形態の様々な説明を提示する。しかし、本発明は、特許請求の範囲において定義され、包含される多くの異なる方法で実施され得る。この説明において、図面に参照がなされ、同じ参照の符号が、同一または機能的に類似の要素を示す場合がある。

##### 【0010】

ESD/EOSストレス状態は、厳しい工業および自動車環境下で可変の正および負電圧振幅において動作する精密通信送受信機では、さらに重度である。そのような環境下で動作するロバストな精密通信送受信機を可能にするために、回路が電力供給されたときに共通基板に大電流を注入することなく、高電圧超過ストレスを放出するために、既存の技術では制限に遭遇する。多数キャリア注入と呼ぶことができる、高基板電流注入は、保護装置および基板の端子間に形成されるバイポーラ寄生トランジスタによって引き起こされ得る。例えば、寄生PNPバイポーラトランジスタは、保護装置のp型領域から形成されるエミッタ、保護装置を囲むn型タブから形成される基部、およびp型基板から形成

10

20

30

40

50

されるコレクタを有することができる。バイポーラ寄生トランジスタは、保護装置を伴う共通基板の中に形成される内部回路内で予測不可能なラッチアップ状態につながり得る、正孔を基板に注入し得る。

【0011】

寄生バイポーラ電流注入の影響は、コア回路ブロックと保護装置との間の慎重な間隔により、ラッチアップ経路トリガのリスクを低減させることによって、軽減され得る。しかしながら、そのようなアプローチは、予測不可能な設計反復、過剰なシリコンダイ面積の使用、基板の中への漏出注入による余分なエネルギー消費、および/または付加的な開発費用をもたらし得る。したがって、そのような厳しい過渡電気環境からのオンチップ保護を精密送受信機ICに提供する必要性がある。さらに、接地または低電力基準に対して対称または非対称であるア15V部分範囲内で送受信機の双方向性動作電圧振幅を許可する、保護方式を提供する必要性がある。また、回路の過渡安全動作域内の安全レベルに過渡ストレス電圧を固定する、および電力ストレス状態の間に基板に多数キャリアを注入することなく高ストレス状態を放出する必要性がある。

10

【0012】

(保護装置を含む電子システムの実施例の概観)

図1は、送受信機システム10の一実施例の概略ブロック図である。送受信機システム10は、送受信機回路1と、コア制御回路2と、低電力減結合回路3と、第1の信号ピン4と、第2の信号ピン5と、第1の保護装置7aと、第2の保護装置7bとを含む。

20

【0013】

第1および第2のピン4、5は、低電圧差信号伝達(LVDS)インターフェース用の信号等の差分信号を受信するように構成される。送受信機回路1は、第1および第2のピン4、5に電気的に接続され、差分信号伝達インターフェース上で信号を受信および/伝送するために使用することができる。コア制御回路2は、差分信号伝達インターフェース上で信号伝達の動作を制御するよう、送受信機回路1用の制御信号を生成するように構成される。例えば、コア制御回路2は、第1および第2のピン4、5を使用して全または半二重信号伝達を提供するように、送受信機回路1を制御するために使用することができる。

【0014】

第1の保護装置7aは、第1のピン4のノードと第1または低電力電圧供給部V1との間で電気的に接続され、第2の保護装置7bは、第2のピン5のノードと低電力電圧供給部V1との間で電気的に接続される。低電力電圧供給部V1は、例えば、接地等の低インピーダンス低電力供給であり得、第1および第2の保護装置7a、7bは、それぞれ、過渡電気的事象9から第1および第2のピン4、5を保護するために使用することができる。例えば、過渡電気的事象9が第1のピン4の上で受信されるとき、第1の保護装置7aが、過渡電気的事象9と関連付けられる電流を低電力電圧供給部V1へ迂回させるか、または分路することができる。同様に、過渡電気的事象9が第2のピン5の上で受信されるとき、第2の保護装置7bが、電流を低電力電圧供給部V1へ分路することができる。特定の実装では、低電力電圧供給部V1は、接地ピン等の1つ以上の低電力パッドまたはピンに電気的に接続される。

30

【0015】

過渡電気的事象9は、静電放電(ESD)事象等の急速に変化する高エネルギー信号であり得る。過渡電気的事象9は、ユーザの接触によって引き起こされる過電圧事象と関連付けることができる。他の実装では、過渡電気的事象9は、Joint Electronic Device Engineering Council (JEDEC)、International Electrotechnical Commission (IEC)、およびAutomotive Engineering Council (AEC)等の種々の機関によって設定された標準によって説明することができる、定義されたストレス条件下で、送受信機システム10のロバスト性を試験するように、製造業者によって生成することができる。

40

50

## 【0016】

低電力減結合回路3は、過渡電気的事象9と関連付けられる電流を迂回させるように、第1および第2の保護装置7a、7bによって使用される低電力電圧供給部V1から、送受信機回路1によって使用される低電力電圧供給部を絶縁するために使用することができる。例えば、低電力減結合回路3は、電流が過渡電気的事象9の間に低電力電圧供給部V1を通して送受信機回路1に注入されることを防止するのに役立ち、それにより、送受信機システム10において過電圧状態またはラッチアップを防止するのに役立つことができる。

## 【0017】

第1および第2の保護装置7a、7bは、チップ上で、送受信機回路1、コア制御回路2、および／または低電力減結合回路3と一体化することができる。しかしながら、第1および第2の保護装置7a、7bはまた、別個に包装されたICまたは送受信機回路とともに共通パッケージに封入されたIC等の別個のIC上に配列することもできる。したがって、第1および第2の保護装置7a、7bは、システムオンチップ用途のための共通半導体基板の中の送受信機と一体化する、システムオンパッケージ用途のための共通パッケージの中の別個のICとして提供する、または別個に包装された独立型ICの中に配置することができる。

10

## 【0018】

電子回路の確実性は、保護装置をICのピンまたはパッドに提供することによって強化される。保護装置は、過渡電気的事象の電圧がトリガ電圧に達するときに、高インピーダンス状態から低インピーダンス状態に遷移することによって、所定の安全範囲内でパッドにおける電圧レベルを維持することができる。その後、過渡電気的事象の電圧が、IC損傷のほとんどの一般的の原因のうちの1つにつながり得る、正または負の故障電圧に達する前に、保護装置は、過渡電気的事象と関連付けられる電流の少なくとも一部分を分路することができる。保護装置は、例えば、IC高電力および低電力（例えば、接地）電圧供給部レベルを超える過渡信号に対して内部回路を保護するように構成することができる。保護装置が、異なる電流および電圧（I-V）阻止特性のために構成可能であり、かつ正常動作電圧条件で高速動作性能および低静的電力散逸を伴って正および負の過渡電気的事象に対する保護を与えることができる、望ましくあり得る。

20

## 【0019】

30

図2は、一実施形態による、双方向性保護装置の電流と電圧との間の関係を示す、グラフ19である。図2では、電圧は、水平軸に沿って表され、電流は、垂直軸に沿って表される。図示した実施形態では、保護装置は、対称であるI-V特性を有する。他の実装では、本明細書で説明される保護装置は、非対称I-V特性を有することができる。例えば、保護装置は、グラフ19の正および負の領域中に異なるI-V曲線を伴って、異なるトリガ電圧、保持電圧、および／または故障電圧を有することができる。グラフ19に示されるように、双方向性保護装置は、過渡信号VTRANSIENTの電圧が正のトリガ電圧+VTRに到達するときに、高インピーダンス状態+ZHから低インピーダンス状態+ZLへ遷移することができる。その後、双方向性保護装置は、大量の電流を分路し、過渡信号電圧レベルが正の保持電圧+VH以上にとどまる限り、低インピーダンス状態+ZLにとどまることができる。トリガ電圧+VTRおよび保持電圧+VHを有するように保護装置を構成することによって、保護装置は、意図しない起動に対して強化した安定性を有する一方で、向上した性能を有することができる。

40

## 【0020】

双方向性保護装置はまた、過渡信号VTRANSIENTの電圧が負のトリガ電圧-VTRに達するときに、高インピーダンス状態-ZHから低インピーダンス状態-ZLへ遷移することもできる。双方向性保護装置はまた、負の過渡信号の電圧の大きさが負の保持電圧-VHの電圧の大きさよりも大きい限り、低インピーダンス状態-ZLにとどまることができる。保護装置の双方向性動作は、正および負の過渡電気的事象に対する保護のための別個の構造を使用する設計に対してレイアウト面積の縮小を可能にし、それにより、

50

低電圧動作のためにより拡張性のある設計解決策を可能にすることができます。

【0021】

図2に示されるように、双方向性保護装置は、過渡信号V T R A N S I E N Tの電圧が、別様にI Cに損層を引き起こし得る正の故障電圧+V Fまたは負の故障電圧-V Fのいずれか一方に達する前に、低インピーダンス状態に遷移するように構成することができる。正常動作電圧+V O Pが双方向性保護装置にわたって存在するとき、双方向性保護装置は、比較的少ない漏出電流I L E A K A G Eを伝導し、それにより、静的電力散逸を低減または最小限化し、I Cのエネルギー効率を強化するべきである。

【0022】

双方向保護装置は、正常動作電圧で漏出が非常に低くなり、かつ内部またはコア素子が過電圧状態に達する前に過渡電気的事象の間にトリガするように構成することができる。本明細書で説明される特定の実装では、保護装置は、コア素子にわたる電圧の大きさを約14V未満に制限するよう、約10Vから約12Vの範囲内の大きさを有する順および逆トリガ電圧、ならびに約2.5Vから約5Vの範囲内の大きさを有する順および逆保持電圧を提供するように構成される。しかしながら、例えば、単一モードまたはデュアルモード送受信機インターフェースが、ア3V、ア5Vの範囲内で対称的に、または非対称的に、例えば、約-1.8Vから3.3Vの範囲内で、動作することができる、低雑音精密用途を含む、他の実装が可能である。加えて、トリガ電圧が、送受信機インターフェースを保護するほど十分低い一方で、同時に、絶縁破壊電圧が、動作電圧を超えて少なくとも3Vから4V等、漏出および誤ったトリガのリスクを最小限化するほど十分高いように、絶縁保護装置をコア回路とともに協調設計することができる。

【0023】

図3は、本明細書で説明される1つ以上の保護装置を含むことができる、送受信機システム20または送受信機システムインターフェースの一実施例の回路図である。送受信機システム20は、コア制御回路2と、低電力減結合回路3と、第1および第2のピン4、5と、第1および第2の保護装置7a、7bと、第1および第2の抵抗器26、27と、内部回路29と、第1および第2の入出力送受信機回路30、31とを含む。送受信機システム20は、例えば、第1および第2のピン4、5が、正常動作環境内で、ユーザに直接暴露される、例えば、カーネーブルまたは工業機械硬度に直接接続される、半または全二重通信送受信機I C等のインターフェースI Cであり得る。送受信機システム20は、第1および第2のピン4、5を、自動車用のエンジン制御ユニット(ECU)または工業用プログラマブル論理制御装置(PLC)に接続する、電気ケーブルと関連付けられるインターフェース等のインターフェース上で、データを伝達するために使用することができる。

【0024】

第1および第2の入出力送受信機回路30、31は、それぞれ、第1および第2の抵抗器26、27を通して、第1および第2のピン4、5に電気的に接続される。入出力送受信機回路とピンとの間の信号経路に抵抗器を含むことは、ピンの上で受信される過渡電気的事象と関連付けられる電流が、入出力送受信機回路に注入されることを防止するのに役立つことができる。しかしながら、そのような抵抗器を含むことはまた、入出力送受信機回路を使用して受信または伝送される信号の完全性にも影響を及ぼし得る。特定の実装では、第1および第2の抵抗器26、27は、約0(省略または短絡)から約15の範囲内、例えば、約10であるように選択される抵抗を有する。しかしながら、当業者であれば、信号処理完全性および/または最小雑音制約と関連付けられる抵抗値等の他の好適な抵抗値を容易に解明するであろう。

【0025】

第1および第2の保護装置7a、7bは、第1および第2のピン4、5の上で受信される過渡電気的事象による損傷から、第1および第2の入出力送受信機回路30、31、内部回路29、および/またはコア制御回路2を保護するように提供されている。第1の保護装置7aは、第1のピン4と低電力電圧供給部V1との間で電気的に接続され、第2の

10

20

30

40

50

保護装置 7 b は、第 1 のピン 4 と低電力電圧供給部 V 1 との間で電気的に接続される。第 1 の保護装置 7 a は、第 1 のピン 4 の上の過電圧または不足電圧状態に応答して、高インピーダンス状態から低インピーダンス状態へ遷移し、それにより、第 1 のピン 4 から低電力電圧供給部 V 1 へ電流を分路するように構成することができる。同様に、第 2 の保護装置 7 b は、第 2 のピン 5 の上の過電圧または不足電圧状態に応答して、高インピーダンス状態から低インピーダンス状態へ遷移するように構成することができる。

【 0 0 2 6 】

図示した低電力減結合回路 3 は、第 1 および第 2 の入出力送受信機回路 3 0、3 1 のための電力に使用される、第 1 または低電力電圧供給部 V 1 と第 2 または内部低電力電圧供給部 V 2 との間の電気経路の中に配置される。低電力減結合回路 3 を含むことは、入出力送受信機回路を形成するために使用される基板の中への多数キャリア注入を低減させることによって、過渡電気的事象が第 1 および / または第 2 のピン 4、5 の上で受信されるときに、第 1 および第 2 の入出力送受信機回路 3 0、3 1 のラッチアップを防止するのに役立つことができる。特定の実装では、低電力減結合回路 3 は、逆並列ダイオードおよび / または接合バイポーラトランジスタ構造等の 1 つ以上のクランプ構造と直列に抵抗器を含む。

10

【 0 0 2 7 】

内部回路 2 9 は、第 1 および第 2 の入出力送受信機回路 3 0、3 1 に電気的に連結され、第 1 および第 2 の入出力送受信機回路 3 0、3 1 によって受信される信号を処理するために使用することができる。コア制御回路 2 は、内部回路 2 9、第 1 の入出力送受信機回路 3 0、および第 2 の入出力送受信機回路 3 1 のそれぞれのための制御信号を生成する。

20

【 0 0 2 8 】

第 1 の入出力送受信機回路 3 0 は、第 1 のピン 4 の上で信号を伝送または受信するために好適な回路の一実施例を含むように図示されている。明確にするために図 3 では図示されていないが、第 2 の入出力送受信機回路 3 1 は、類似回路構造を有することができる。図示した第 1 の入出力送受信機回路 3 0 は、第 1 の出力回路 2 2 と、第 2 の出力回路 2 3 と、第 1 の調停回路 2 4 と、第 2 の調停回路 2 5 と、第 3 の抵抗器 2 8 と、第 1 の n 型金属酸化物半導体 (NMOS) トランジスタ 3 2 と、電力クランプ 4 0 とを含む。本明細書で使用されるように、かつ当業者であれば理解するように、MOS トランジスタは、ポリシリコン等の金属ではない材料でできているゲートを有することができ、酸化ケイ素だけでなく、高度な 40 ナノメートル以下のプロセス技術で使用される高 k 誘電体等の他の誘電体を用いて実装される、誘電領域を有することができる。

30

【 0 0 2 9 】

第 1 の出力回路 2 2 および第 2 の出力回路 2 3 は、第 1 のピン 4 の上で信号を電気的に伝送するために使用することができる。例えば、第 1 の出力回路 2 2 は、内部低電力電圧供給部 V 2 と第 1 のピン 4 との間で電気的に接続され、第 1 のピン 4 における電圧を低く駆動するために使用することができる。加えて、第 2 の出力回路 2 3 は、第 3 または高電力電圧供給部 V 3 と第 1 のピン 4 との間で電気的に接続され、第 1 のピン 4 における電圧を高く駆動するために使用することができる。

40

【 0 0 3 0 】

第 1 の出力回路 2 2 は、第 2 から第 4 の NMOS トランジスタ 3 3 ~ 3 5 を含む。第 2 の NMOS トランジスタ 3 3 は、内部低電力電圧供給部 V 2 に電気的に接続されるソースおよび本体と、第 3 の NMOS トランジスタ 3 4 のソースに電気的に接続されるドレインとを含む。第 4 の NMOS トランジスタ 3 5 は、第 3 の NMOS トランジスタ 3 4 のドレインに電気的に接続されるソースと、第 1 の抵抗器 2 6 を通して第 1 のピン 4 に電気的に接続されるドレインとを含む。第 3 の NMOS トランジスタ 3 4 および第 4 の NMOS トランジスタ 3 5 はそれぞれ、第 4 の電圧供給部 V 4 に電気的に接続される本体をさらに含む。特定の実装では、第 4 の電圧供給部 V 4 は、標的信号伝達性能を達成するのに役立つように、内部低電力電圧供給部 V 2 を下回る電圧に選択される。例えば、第 1 のピン 4 の上の信号伝達条件は、正および負の電圧信号伝達レベルを含んでもよく、第 4 の電圧供給

50

部V4は、第1のピン4が比較的低い電圧レベルを有するときに、第3および第4のNMOSトランジスタ34、35の本体が順方向バイアスをかけられることを防止するために使用することができる。第2から第4のNMOSトランジスタ33～35はそれぞれ、コア制御回路2を使用して制御されるように構成されるゲートをさらに含む。特定の実装では、第2のNMOSトランジスタ33のゲートの電圧レベルは、第1の出力回路22の所望のシンク電流を提供するように制御され、第3のNMOSトランジスタ34のゲートの電圧レベルは、第1の出力回路22の出力インピーダンスを調整するための所望の抵抗を提供するように制御され、第4のNMOSトランジスタ35のゲートの電圧レベルは、第1の出力回路22をオンおよびオフにして、第1のピン4の上で信号を生成するように制御される。

10

#### 【0031】

第2の出力回路23は、第1および第2のp型金属酸化物半導体(PMOS)トランジスタ36、37を含む。第1のPMOSトランジスタ36は、高電力電圧供給部V3に電気的に接続されるソースおよび本体と、第2のPMOSトランジスタ37のソースに電気的に接続されるドレインとを含む。第2のPMOSトランジスタ37はさらに、第1の抵抗器26を通して第1のピン4に電気的に接続されるドレインを含む。第2のPMOSトランジスタ37はさらに、第5の電圧供給部V5に電気的に接続される本体を含む。特定の実装では、第5の電圧供給部V5は、第3の電圧供給部V3を上回る電圧に選択され、第1のピン4の電圧が第3の電圧供給部V3を上回るときに、第2のPMOSトランジスタ37の本体が順方向バイアスをかけられることを防止するのに役立つように選択される大きさを有することができる。第1および第2のPMOSトランジスタ36、37はそれぞれ、コア制御回路2を使用して制御することができるゲートを含む。特定の実装では、第1のPMOSトランジスタ36のゲートの電圧レベルは、第2の出力回路23の所望のソース電流を提供するように制御され、第2のPMOSトランジスタ37のゲートの電圧レベルは、第2の出力回路23をオンおよびオフにして、第1のピン4の上で信号を生成するように制御される。

20

#### 【0032】

第1のNMOSトランジスタ32は、第1のピン4の上で受信される信号を内部回路29に渡すために使用することができる。第1のNMOSトランジスタ32は、内部回路29に電気的に接続されるドレインと、第1および第3の抵抗器26、28を通して第1のピン4に電気的に接続されるソースとを含む。コア制御回路2は、第1のNMOSトランジスタ32のゲートの電位を制御し、それにより、内部回路29と第1のピン4との間のインピーダンスを制御し、第1のピン4の上の電圧レベルが内部回路29によって感知されることを可能にすることができます。図2で図示されるように、第1のNMOSトランジスタ32は、第4の電位V4に電気的に接続される本体を含むことができる。

30

#### 【0033】

特定の実装では、第1および第2の調停回路24、25は、それぞれ、第4および第5の電圧供給部V4、V5を生成するように含むことができる。第1の調停回路24は、内部低電力電圧供給部V2および第1のピン4の電圧のうちの小さいほうにほぼ等しくなるように第4の電圧供給部V4の電圧レベルを制御することができる。加えて、第2の調停回路25は、高電力電圧供給部V3および第1のピン4の電圧うちの大きいほうにほぼ等しくなるように第5の電圧供給部V5の電圧レベルを制御することができる。第1および第2の調停回路24、25は、正常信号伝達状態の間に、第1のピン4における電圧が、内部低電力電圧供給部V2を下回ること、および高電力電圧供給部V3を上回ることを可能にすることができます。

40

#### 【0034】

第1の調停回路24は、第5のNMOSトランジスタ41と、第6のNMOSトランジスタ42と、第7のNMOSトランジスタ43と、第5の抵抗器44と、第6の抵抗器45とを含む。第5のNMOSトランジスタ41は、内部低電力電圧供給部V2に電気的に接続されるドレインと、第6のNMOSトランジスタ42のソースおよび本体に、ならび

50

に第 6 の抵抗器 4 5 の第 1 の端部に電気的に接続されるソースおよび本体とを含む。第 6 の抵抗器 4 5 はさらに、第 7 のN M O Sトランジスタ 4 3 のドレインに電気的に接続される第 2 の端部を含む。第 7 のN M O Sトランジスタ 4 3 はさらに、第 4 の電圧供給部 V 4 に電気的に接続されるソースおよび本体を含む。第 5 の抵抗器 4 4 は、第 6 のN M O Sトランジスタ 4 2 のドレインに電気的に接続される第 1 の端部と、第 1 の抵抗器 2 6 を通して第 1 のピン 4 に電気的に接続される第 2 の端部とを含む。第 5 から第 7 のN M O Sトランジスタ 4 1 ~ 4 3 はそれぞれ、コア制御回路 2 を使用して制御されるゲートをさらに含む。第 2 の調停回路 2 5 は、第 3 のP M O Sトランジスタ 4 6 と、第 4 のP M O Sトランジスタ 4 7 と、第 5 のP M O Sトランジスタ 4 8 と、第 7 の抵抗器 4 9 と、第 8 の抵抗器 5 0 とを含む。第 3 のP M O Sトランジスタ 4 6 は、第 3 の電圧供給部 V 3 に電気的に接続されるドレインと、第 4 のP M O Sトランジスタ 4 7 のソースおよび本体に、ならびに第 8 の抵抗器 5 0 の第 1 の端部に電気的に接続されるソースおよび本体とを含む。第 8 の抵抗器 5 0 はさらに、第 5 のP M O Sトランジスタ 4 8 のドレインに電気的に接続される第 2 の端部を含む。第 5 のP M O Sトランジスタ 4 8 はさらに、第 5 の電圧供給部 V 5 に電気的に接続されるソースおよび本体を含む。第 3 から第 5 のP M O Sトランジスタ 4 6 ~ 4 8 はそれぞれ、コア制御回路 2 を使用して制御されるゲートをさらに含む。第 7 の抵抗器 4 9 は、第 4 のP M O Sトランジスタ 4 7 のドレインに電気的に接続される第 1 の端部と、第 1 の抵抗器 2 6 を通して第 1 のピン 4 に電気的に接続される第 2 の端部とを含む。

。

## 【 0 0 3 5 】

過渡電気的事象が第 1 のピン 4 の上で受信されるとき、第 1 のピン 4 の電圧は、第 1 の保護装置 7 a のトリガ電圧に到達するまで増加する(図 2 参照)。しかしながら、特定の実装では、第 1 の保護装置 7 a が起動する前に、第 1 のピン 4 の上の電圧のオーバーシュートがあり得る。一実装形態では、第 1 および第 2 の調停回路 2 4 、 2 5 ならびに第 1 および第 2 の出力回路 2 2 、 2 3 は、第 1 の保護装置 7 a が過渡電気的事象の間に起動する前に、調停回路 2 4 、 2 5 および / または出力回路 2 2 、 2 3 が破壊することを防止するのに役立つために、第 1 の保護装置 7 a のオーバーシュート電圧よりも大きいトリガ電圧を有するように構成される。一実装では、第 1 の保護装置 7 a が過渡電気的事象の間にオフになる前に、第 1 のピン 4 と内部低電力電圧供給部 V 2 との間の寄生経路が起動することを防止するように、少なくとも 2 つの p - n 接合部が、第 1 のピン 4 と内部低電力電圧供給部 V 2 との間の各電気経路の中に配置される。図 3 に示されるように、M O Sトランジスタ素子を連鎖することによって、少なくとも 2 つの p - n 接合部を第 1 のピン 4 と内部低電力電圧供給部 V 2 との間でこれらの回路の中に提供することができる。特定の実装では、電力クランプ 4 0 もまた、含むことができ、オーバーシュートを低減させるのに役立つよう、第 1 の出力回路 2 2 の中で連鎖された素子の数よりも少ない数の素子を連鎖の中に有するように構成することができる。

## 【 0 0 3 6 】

第 5 および第 7 の抵抗器 4 4 、 4 9 は、第 1 および第 2 の調停回路 2 4 、 2 5 を通して第 1 のピン 4 と第 2 の電圧供給部 V 2 との間の寄生電気経路の中のインピーダンスを増加させるように、それぞれ、第 1 および第 2 の調停回路 2 4 、 2 5 の中に含むことができる。一実装では、第 5 および第 7 の抵抗器 4 4 、 4 9 はそれぞれ、約 3 0 オーム ( ) から約 8 5 の範囲内、例えば、約 7 2 であるように選択される抵抗を有する。第 6 および第 8 の抵抗器 4 5 、 5 0 はまた、第 1 および第 2 の調停回路 2 4 、 2 5 を通して第 1 のピン 4 と内部低電力電圧供給部 V 2 との間の寄生経路の中のインピーダンスを増加させることに役立つとともに、それぞれ、第 4 および第 5 の電圧供給部 V 4 、 V 5 を生成することにおいて第 1 および第 2 の調停回路 2 4 、 2 5 を補助することができる。特定の実装では、第 6 および第 8 の抵抗器 4 5 、 5 0 はそれぞれ、約 3 0 から約 8 5 の範囲内、例えば、約 7 5 であるように選択される抵抗を有する。種々の抵抗器値が上記で説明されているが、当業者であれば、他の好適な抵抗値を容易に解明するであろう。

## 【 0 0 3 7 】

10

20

30

40

50

図1の送受信機システム10および図3の送受信機システム20は、本明細書で説明される保護装置とともに使用するために好適な電子システムの2つの実施例を図示する。しかしながら、送受信機システムは、通信プロトコル制約および/または誤った状態の許容値を満たすように他の方法で制御することができる。加えて、保護装置は、送受信機システムとの関連で図示されているが、本明細書で説明される保護装置は、例えば、工業用制御システム、インターフェースシステム、電力管理システム、微小電気機械システム(MEMS)センサシステム、自動車システム、無線インフラストラクチャシステム、および/またはデジタル信号処理(DSP)システムを含む、広範囲のICおよび他の電子機器で使用することができる。加えて、送受信機システムは、2つの信号ピンおよび2つの保護装置を含むものとして図示されているが、システム仕様を満たすように、より多いまたは少ない保護装置およびピンを含むことができる。さらに、保護装置は、ピンと高電力ピンとの間で各保護装置を電気的に接続することによって等、他の方法で配列することができる。

#### 【0038】

##### (二重タブ絶縁双方向性保護装置)

二重タブ絶縁双方向性保護装置および同装置を形成する方法が、本明細書で提供される。特定の実装では、双方向性保護装置は、第1のn-ウェル領域から形成されるエミッタ/コレクタと、p-ウェル領域から形成される基部と、第2のn-ウェル領域から形成されるコレクタ/エミッタとを含む、双方向性NPNバイポーラトランジスタを含む。P型活性領域は、n型絶縁領域またはタブおよびp型絶縁領域またはタブを有する二重タブ絶縁を使用して基板から絶縁される、PNPNP構造を形成するように、第1および第2のn-ウェル領域の中に形成される。二重タブ絶縁は、PNPNP構造と関連付けられるウェルが、過渡電気的事象の間にキャリアを基板に注入すること、ならびに外部構成要素および回路と相互作用することを防止する。例えば、二重タブ絶縁は、PNPNP構造のウェルから形成されるエミッタおよび基板から形成されるコレクタを含む、寄生バイポーラ構造の形成を防止し、それにより、基板からの保護装置の絶縁を増加させ、ICラッチャップ免疫を強化する。ラッチャップはしばしば、ICが電力供給されている間に、大きなストレス状態がICピンにおいて得られたときに、精密送受信機用途で観察される。特定の実装では、PNPNP構造と関連付けられる活性領域およびウェルのサイズ、間隔、およびドーピング濃度は、トリガおよび保持電圧特性の微調整された制御を提供して、低電圧精密インターフェース信号伝達を使用する用途で、双方向性保護装置が実装されることを可能にするように、選択することができる。双方向性保護装置は、大幅に低い費用でシリコンオンインシュレータ(SOI)プロセスと同程度のレベルまで、バルク絶縁バイポーラ相補型金属酸化膜半導体(CMOS)拡散金属酸化物半導体(DMOS)(BCD)プロセスにラッチャッププロバスト性を提供するために使用することができる。

#### 【0039】

図4は、一実施形態による、双方向性保護回路60を図示する回路図である。図示した保護回路60は、第1のピンまたはパッド61と第2のピンまたはパッド62との間で電気的に接続され、低電圧双方向性阻止電圧保護を提供するために使用することができる。双方向性保護回路60は、NPN双方向性バイポーラトランジスタ63と、第1および第2のPNPバイポーラトランジスタ64、65と、第1および第2の寄生NPNバイポーラトランジスタ66、67と、第1から第8の抵抗器71～78とを含む。保護回路60は、例えば、図1および3の保護装置7a、7bのうちのいずれかに役立つように適合することができる。

#### 【0040】

保護回路60は、過電圧または不足電圧状態があるときに、第1および第2のパッド61、62の間に電流分路を提供することができる。例えば、第1のパッド61は、図1および3の第1および第2の信号ピン4、5等のICの信号ピンまたはパッドであり得、第2のパッド62は、図1および3の低電力電圧供給部V1と関連付けられるパッド等の低電力ピンまたはパッドであり得る。特定の実装では、第2のパッド62は、接地パッドま

10

20

30

40

50

たは接地基準に連結されることを目的としているパッドである。

【0041】

第1のPNPバイポーラトランジスタ64は、第1のパッド61に、第1の抵抗器71の第1の端部に、および第3の抵抗器73の第1の端部に電気的に接続される、エミッタを含む。第1のPNPバイポーラトランジスタ64はさらに、NPN双方向性バイポーラトランジスタ63のコレクタ／エミッタC／Eに、および第1の抵抗器71の第2の端部に電気的に接続される、基部を含む。第1のPNPバイポーラトランジスタ64はさらに、第5の抵抗器75の第1の端部に、および第1のNPNバイポーラトランジスタ66の基部に電気的に接続される、コレクタを含む。第1のNPNバイポーラトランジスタ66はさらに、第3の抵抗器73の第2の端部に電気的に接続されるエミッタと、第7の抵抗器77の第1の端部に電気的に接続されるコレクタとを含む。第2のPNPバイポーラトランジスタ65は、第2のパッド62に、第2の抵抗器72の第1の端部に、および第4の抵抗器74の第1の端部に電気的に接続される、エミッタを含む。第2のPNPバイポーラトランジスタ65はさらに、NPN双方向性バイポーラトランジスタ63のエミッタ／コレクタE／Cに、および第2の抵抗器72の第2の端部に電気的に接続される、基部を含む。第2のPNPバイポーラトランジスタ65はさらに、第6の抵抗器76の第1の端部に、および第2のNPNバイポーラトランジスタ67の基部に電気的に接続される、コレクタを含む。第6の抵抗器76はさらに、第5の抵抗器75の第2の端部に、およびNPN双方向性バイポーラトランジスタ63の基部に電気的に接続される、第2の端部を含む。第2のNPNバイポーラトランジスタ67はさらに、第4の抵抗器74の第2の端部に電気的に接続されるエミッタと、第8の抵抗器78の第1の端部に電気的に接続されるコレクタとを含む。第8の抵抗器78はさらに、第7の抵抗器77の第2の端部に電気的に接続される第2の端部を含む。

10

【0042】

NPN双方向性バイポーラトランジスタ63は、双方向性に動作することができ、エミッタおよびコレクタとしてのエミッタ／コレクタE／Cおよびコレクタ／エミッタC／Eの動作は、第1および第2のパッド61、62の電圧条件に依存し得る。例えば、第1のパッド61と第2のパッド62との間の電圧差が保護回路60のほぼ正のトリガ電圧+VTR(図2参照)よりも大きいとき、NPN双方向性バイポーラトランジスタ63のエミッタ／コレクタE／Cは、エミッタとしての機能を果たし、双方向性バイポーラトランジスタのコレクタ／エミッタC／Eは、コレクタとしての機能を果たす。対照的に、第1のパッド61と第2のパッド62との間の電圧差が保護回路60のほぼ負のトリガ電圧-VTR(図2参照)よりも小さいとき、NPN双方向性バイポーラトランジスタ63のエミッタ／コレクタE／Cは、コレクタとしての機能を果たし、NPN双方向性バイポーラトランジスタ63のコレクタ／エミッタC／Eは、エミッタとしての機能を果たす。

20

【0043】

過渡電気的事象が第2のパッド62に対して第1のパッド61の電圧を増加させると、NPN双方向性バイポーラトランジスタ63および第1のPNPバイポーラトランジスタ64は、第1の交差連結バイポーラPNPNまたはシリコン制御整流器(SCR)様構造として動作する。具体的には、NPN双方向性バイポーラトランジスタ63および第1のPNPバイポーラトランジスタ64は、第1のPNPバイポーラトランジスタ64のコレクタ電流の増加が、NPN双方向性バイポーラトランジスタ63の基本電流を増加させ、NPN双方向性バイポーラトランジスタ63のコレクタ電流の増加が、第1のPNPバイポーラトランジスタ64の基本電流を増加させるように、フィードバックで配列される。第1および第2のパッド61、62の間の電圧が、正の過渡電気的事象の間に増加し、保護回路60の順トリガ電圧に達するにつれて、NPN双方向性バイポーラトランジスタ63と第1のPNPバイポーラトランジスタ64との間のフィードバックは、再正式であり、保護回路60を低インピーダンス状態にさせ得る。その後、トランジスタの間のフィードバックは、第1および第2のパッド61、62にわたる電圧が保護回路60の順保持電圧を超える限り、低インピーダンス状態で保護回路60を維持することができる。過渡

40

電気的事象が第2のパッド62に対して第1のパッド61の電圧を減少させるとき、NPN双方向性バイポーラトランジスタ63および第2のPNPバイポーラトランジスタ65は、上記で説明されるものと同様に動作することができる、第2の交差連結バイポーラPNPまたはSCR様構造として動作する。第1および第2の交差連結バイポーラPNP構造がそれぞれ、NPN双方向性バイポーラトランジスタ63を含むため、第1および第2の交差連結バイポーラPNP構造は、本明細書では、集合的にPNPNP構造として動作すると見なすことができる。

#### 【0044】

保護回路60の順トリガおよび保持電圧は、第1のPNPバイポーラトランジスタ64の利得および伝導強度に対してNPN双方向性バイポーラトランジスタ63の利得および伝導強度を制御することによって、ならびに、第1のPNPバイポーラトランジスタ64の基部・エミッタ接合部を横断して配置される、第1の抵抗器71の値を選択することによって、変化させることができ、かつ過渡電気的事象の間に第1のPNPバイポーラトランジスタ64のターンオンを促進することができる。同様に、保護回路60の逆トリガおよび保持電圧は、第2のPNPバイポーラトランジスタ65の利得および伝導強度に対してNPN双方向性バイポーラトランジスタ63の利得および伝導強度を制御することによって、および第2の抵抗器72の値を選択することによって、変化させることができる。NPN双方向性バイポーラトランジスタ63ならびに第1および第2のPNPバイポーラトランジスタ64、65と関連付けられる活性領域およびウェルのサイズ、間隔、およびドーピング濃度は、トリガおよび保持電圧特性の微調整された制御を提供して、低電圧精密インターフェース信号伝達を使用する用途で、保護回路60が実装されることを可能にするように、選択することができる。

#### 【0045】

保護回路60は、保護回路60が、保護回路60を伴う共通基板の中に形成される外部構成要素および回路と相互作用することを防止し、それにより、優れたラッチアップ免疫をICに提供する、二重タブ絶縁を含む。具体的には、図4に示されるように、第1および第2のNPNバイポーラトランジスタ66、67ならびに第5および第6の抵抗器75、76の基部が、p型絶縁領域またはタブ68と関連付けられる一方で、第1および第2のNPNバイポーラトランジスタ66、67ならびに第7および第8の抵抗器77、78のコレクタは、n型絶縁領域またはタブ69と関連付けられる。二重タブ絶縁は、基板への寄生バイポーラ構造の形成を防止し、第1および第2のパッド61、62の間で受信される過渡電気的事象の間に保護回路60が基板に注入する電荷量を低減させる。

#### 【0046】

図5Aは、一実施形態による、図4の保護回路60を実装する、二重タブ絶縁双方向性保護装置80の概略斜視図である。保護装置80は、p型基板(P-SUB)81と、n型埋め込み層(NBL)89と、p型エピタキシャル層(P-EPI)91と、深いp-ウェル(DPW)93と、第1から第4の高電圧n-ウェル(HVNW)84a～84dと、第1から第3の高電圧p-ウェル(HVPW)82a～82cと、第1および第2の浅いn-ウェル(SHNW)94a、94bと、浅いp-ウェル(SHPW)92と、第1から第4のp型活性(P+)領域83a～83dと、第1から第6のn型活性(N+)領域85a～85fと、第1および第2のゲート酸化物層86a、86bと、第1および第2のゲート87a、87bと、酸化物領域88とを含む。図5Bは、線5B-5Bに沿って得られた図5Aの保護装置80の断面図である。図5Bの保護装置80は、図4のNPN双方向性バイポーラトランジスタ63、第1および第2のPNPバイポーラトランジスタ64、65、第1および第2のNPNバイポーラトランジスタ66、67、および第1から第8の抵抗器71～78等の、図示した構造から形成される同等の回路素子を示すように注釈を付けられている。加えて、断面は、第1および第2のパッド61、62、ならびに保護装置80内およびパッドへの電気的接続を示すように注釈を付けられている。

#### 【0047】

NBL89は、P-SUB81の中に形成され、P-EPI91は、P-SUB81を

10

20

30

40

50

覆って形成され、DPW93は、NBL89を覆ってP-EPI91の中に形成される。特定の実装では、P-EPI91は、精密送受信機用途のための混合信号高電圧バイポーラ-CMOS-DMOS(BCD)プロセス技術において、典型的には、最大300Vまでの比較的高い電圧条件で動作を可能にする、低濃度ドープ領域である。第1から第4のHVNW84a～84dおよび第1から第3のHVPW82a～82cは、第1のHVPW82aが第1および第2のHVNW84a、84bの間にあり、第2のHVPW82bが第2および第3のHVNW84b、84cの間にあり、第3のHVPW82cが第3および第4のHVNW84c、84dの間にあるように、P-EPI91の中に形成される。図5Aに示されるように、第1および第3のHVPW82a、82cおよびDPW93は、第2および第3のHVNW84b、84cおよび第2のHVPW82bの底部および側面、ならびにその中に形成された構造および素子を包囲する、p型絶縁領域またはタブを形成する。具体的には、DPW93が、第2および第3のHVNW84b、84cおよび第2のHVPW82bの下に延在する一方で、第1および第3のHVPW82a、82cは、DPW93に接触し、第2および第3のHVNW84b、84cおよび第2のHVPW82bの側面を包囲する。加えて、第1および第4のHVNW84a、84dおよびNBL89は、p型タブを包囲するn型絶縁領域またはタブを形成する。具体的には、NBL89が、DPW93ならびに第1および第3のHVPW82a、82cの下に延在する一方で、第1および第4のHVNW84a、84dは、NBL89に接触し、第1および第3のHVPW82a、82cの側面を包囲する。p型タブおよびn型タブから形成される二重タブ構造は、P-SUB81および/またはP-EPI91の中に形成された他の素子から保護装置80を完全に絶縁することができる。

#### 【0048】

第1のSHNW94aは、第2のHVNW84bの中に形成され、第2のSHNW94bは、第3のHVNW84cの中に形成され、SHPW92は、第2のHVPW82bの中に形成される。第1および第6のN+領域85a、85fは、それぞれ、第1および第4のHVNW84a、84dの中に形成され、第1および第4のP+領域83a、83dは、それぞれ、第1および第3のHVPW82a、82cの中に形成される。第1および第2のゲート酸化物層86a、86bは、それぞれ、第1および第2のSHNW94a、94bを覆ってP-EPI91の表面90の上に形成される。第1および第2のゲート87a、87bは、それぞれ、第1および第2のゲート酸化物層86a、86bを覆って形成され、ポリシリコン層であり得る。ゲート酸化物層86a、86bの各側面では、スペーサ絶縁領域(図示せず)を製造プロセスの一部として形成することができる。第3のN+領域85cが、第1のゲート87aの第1の側面上にあり、SHPW92の中に第1の部分と、第1のSHNW94aの中に第2の部分とを含む。第2のP+領域83bは、第1の側面とは反対側の第1のゲート87aの第2の側面上で第1のSHNW94aの中にあり。第4のN+領域85dは、第2のゲート87bの第1の側面上にあり、SHPW92の中に第1の部分と、第2のSHNW94bの中に第2の部分とを含む。第3のP+領域83cは、第1の側面とは反対側の第2のゲート87bの第2の側面上で第2のSHNW94bの中にあり。第2のN+領域85bは、第1のゲート87aとは反対側の第2のP+領域83bの側面上で第1のSHNW94aの中にあり。第5のN+領域85eは、第2のゲート87bとは反対側の第3のP+領域83cの側面上で第2のSHNW94bの中にあり。

#### 【0049】

図示した保護装置80は、酸化物領域88を含む。絶縁領域の形成は、P-EPI91の中に溝をエッティングすること、二酸化ケイ素(SiO<sub>2</sub>)等の誘電体で溝を充填すること、および化学機械平坦化等の任意の好適な方法を使用して過剰な誘電体を除去することを伴うことができる。特定の実装では、酸化物領域88は、活性領域間に配置される、浅い溝領域またはシリコンの局所酸化(LOCOS)領域であり得る。

#### 【0050】

保護装置80は、任意の好適な製造プロセスを使用して形成することができる。一実施

10

20

30

40

50

形態では、P-SUB81は、NBL89を埋め込むことができ、P-EPI91は、エピタキシャル成長プロセスを使用して、P-SUB81およびNBL89を覆って成長させることができる。その後、DPW93をP-EPI91に埋め込むことができ、HVPW82a-82cおよびHVNW84a-84dをP-EPI91に埋め込むことができる。次に、SHPW92およびSHNW94a、94bを埋め込むことができ、酸化物領域88を上記で以前に説明されたようにP-EPI91の中に形成することができる。その後、P-EPI91の表面90を覆って、ゲート酸化物層86a、86bおよびゲート87a、87bを形成することができ、その後に、N+領域85a-85fおよびP+領域83a-83dの埋め込みが続く。保護装置80の1つの可能な製造プロセスが説明されているが、当業者によって認識されるように、変化例および他の実装が可能である。 10

#### 【0051】

一実施形態では、P+領域83a-83dおよびN+領域85a-85fは、約0.15マイクロメートル(μm)から約0.5μmの範囲内、例えば、約0.2μmのP-EPI91の表面90の中への深度を有し、SHPW92およびSHNW94a、94bは、約0.5μmから約1.5μmの範囲内、例えば、約1.0μmのP-EPI91の中への深度を有し、HVPW82a-82cおよびHVNW84a-84dは、約3.0μmから約4.5μmの範囲内、例えば、約3.5μmのP-EPI91の中への深度を有する。加えて、P-EPI91は、約4μmから約6μmの範囲内、例えば、約4.5μmの厚さを有することができ、NBL89のピークドーピングは、約4.0μmから約5.5μmの範囲内、例えば、約5.0μmのP-SUB81の中への深度を有することができる。図5A-5Bに示されるように、HVPW82a-82cは、DPW93に到達するように十分な深度を有することができ、HVNW84a-84dは、NBL89に到達するように十分な深度を有することができる。DPWドーピングピークの深度は、1.5μmから3μmの範囲内、例えば、2.0μmであり得る。特定の実装では、酸化物領域88は、P+領域83a-83dおよびN+領域85a-85fよりも比較的深くあり得る。深度の種々の実施例が上記で説明されているが、当業者であれば、他の好適な深度値を容易に解明するであろう。 20

#### 【0052】

一実施形態では、P-SUB81は、約0.5ラ1015原子/立方センチメートル(cm-3)から約1.5ラ1015cm-3の範囲内、例えば、約1.0ラ1015cm-3のピークドーピング濃度を有し、P-EPI91は、約1ラ1014cm-3から約8.0ラ1014cm-3の範囲内、例えば、約2.0ラ1014cm-3のピークドーピング濃度を有する。加えて、DPW93は、約8ラ1016cm-3から約2ラ1017cm-3の範囲内、例えば、約1.0ラ1017cm-3のピークドーピング濃度を有し、NBL89は、約0.5ラ1017cm-3から約4ラ1017cm-3の範囲内、例えば、約2.5ラ1017cm-3のピークドーピング濃度を有する。さらに、P+領域83a-83dおよびN+領域85a-85fは、約1ラ1020cm-3から約8ラ1020cm-3の範囲内、例えば、約5ラ1020cm-3のピークドーピング濃度を有し、SHPW92およびSHNW94a、94bは、約2.5ラ1017cm-3から約9.5ラ1017cm-3の範囲内、例えば、約7.0ラ1017cm-3のピークドーピング濃度を有し、HVPW82a-82cおよびHVNW84a-84dは、約1.5ラ1016cm-3から約7.5ラ1016cm-3の範囲内、例えば、約3.0ラ1016cm-3のピークドーピング濃度を有する。したがって、HVPW82a-82cは、SHPW92のピークドーピング濃度よりも小さいピークドーピング濃度を有することができるが、HVPW82a-82cの深度は、SHPW92の深度よりも大きくあり得る。同様に、HVNW84a-84dは、SHNW94a、94bのピークドーピング濃度よりも小さいピークドーピング濃度を有することができるが、HVNW84a-84dの深度は、SHNW94a、94bの深度よりも大きくあり得る。ピークドーピング濃度および深度の種々の範囲が上記で説明されているが、当業者であれば、他の好適なドーピング濃度を容易に解明するであろう。 40 50

## 【0053】

保護装置 80 は、接点を形成する後端処理および金属化を受けることができる。加えて、図 5A ~ 5B では図示されていないが、P-SUB 81 はまた、その中に形成された他の素子または構造を含むこともできる。当業者であれば、明確にするためにこれらの詳細がこの図から省略されていることを理解するであろう。

## 【0054】

ここで図 5B を参照すると、第 1 のパッド 61 は、第 2 の P+ 領域 83b に、および第 2 の N+ 領域 85b に電気的に接続され、第 2 のパッド 62 は、第 3 の P+ 領域 83c に、および第 5 の N+ 領域 85e に電気的に接続される。加えて、第 1 の N+ 領域 85a は、第 6 の N+ 領域 85f に電気的に接続され、第 1 の P+ 領域 83a は、第 4 の P+ 領域 83d に電気的に接続される。NPN 双方向性バイポーラトランジスタ 63 は、第 1 の SHNW94a および第 2 の HVNW84b を含む第 1 の n- ウェル領域から形成されるコレクタ / エミッタ C/E と、SHPW92 および HV PW82b を含む p- ウェル領域から形成される基部と、第 2 の SHNW94b および第 3 の HVNW84c を含む第 2 の n- ウェル領域から形成されるエミッタ / コレクタ E/C とを含む。第 1 の PNP バイポーラトランジスタ 64 は、第 2 の P+ 領域 83b から形成されるエミッタと、第 1 の SHNW94a および第 2 の HVNW84b から形成される基部と、DPW93 から形成されるコレクタとを含む。第 2 の PNP バイポーラトランジスタ 65 は、第 3 の P+ 領域 83c から形成されるエミッタと、第 2 の SHNW94b および第 3 の HVNW84c から形成される基部と、DPW93 から形成されるコレクタとを含む。第 1 の NPN バイポーラトランジスタ 66 は、第 1 の SHNW94a から形成されるエミッタと、第 1 の HV PW82a から形成される基部と、第 1 の HVNW84a から形成されるコレクタとを含む。第 2 の NPN バイポーラトランジスタ 67 は、第 2 の SHNW94b から形成されるエミッタと、第 3 の HV PW82c から形成される基部と、第 4 の HVNW84d から形成されるコレクタとを含む。第 1 および第 3 の抵抗器 71、73 は、第 1 の SHNW94a の抵抗から形成され、第 2 および第 4 の抵抗器 72、74 は、第 2 の SHNW94b の抵抗から形成される。第 5 および第 6 の抵抗器 75、76 は、DPW93 の抵抗から形成され、第 7 および第 8 の抵抗器 77、78 は、それぞれ、第 1 および第 4 の HVNW84a、84d の抵抗から形成される。

## 【0055】

図 5B に示されるように、NBL89 ならびに第 1 および第 4 の HVNW84a、84d から形成される n 型タブは、電気的に浮動することができる。加えて、DPW93 ならびに第 1 および第 3 の HV PW82a、82c から形成される p 型タブは、電気的に浮動することができる。このようにして p 型タブおよび n 型タブを構成することにより、p 型タブおよび / または n 型タブが固定電位に電気的にバイアスをかけられている構成に対して、第 1 および第 2 のパッド 61、62 上の最大許容電圧振幅を増加させることができる。しかしながら、低漏出実装等のいくつかの構成では、p 型タブおよび / または n 型タブを、電圧供給部に電気的に接続することができる。例えば、p 型タブは、1 メガオーム (M-ohm) の範囲内の高インピーダンスを介して、第 1 および第 2 のパッド 61、62 の最小動作電圧以下の低電力電圧供給部に電気的に接続することができ、n 型タブは、第 1 および第 2 のパッド 61、62 の最大動作電圧以上の高電力電圧供給部に電気的に接続することができる。一実施形態では、n 型タブが、基板からの保護装置のより強い絶縁を提供するように、第 1 および第 2 のパッド 61、62 の最大動作電圧以上の高電力電圧供給部に電気的に接続される一方で、p 型タブは、第 1 および第 2 のパッド 61、62 の間で最大双方向性電圧振幅を提供するように電気的に浮動しているように構成される。

## 【0056】

上記で説明されるものと同様に、保護装置 80 と関連付けられる PNPNP 構造を制御することによって、保護装置 80 の保護特性を変化させることができる。例えば、NPN 双方向性バイポーラトランジスタ 63 および第 1 の PNP バイポーラトランジスタ 64 と関連付けられる第 1 の PNP 構造の抵抗および相対素子強度を制御することによって、

10

20

30

40

50

保護装置 80 の順トリガおよび保持電圧を変化させることができ、NPN 双方向性バイポーラトランジスタ 63 および第 2 の PNP バイポーラトランジスタ 65 から形成される第 2 の PNPN 構造の抵抗および相対素子強度を制御することによって、保護装置 80 の逆トリガおよび保持電圧を変化させることができる。第 1 および第 2 の PNPN 構造は、集合的に PNPNP 構造として動作する。図示した構成では、本装置の表面付近で絶縁破壊を制御するように、SHPW92 ならびに第 1 および第 2 の SHNW94a、94b が、保護装置 80 の中に含まれている。本装置の保護特性をさらに制御するために、第 3 および第 4 の N+ 領域 85c、85d が、SHPW92 と第 1 および第 2 の SHNW94a、94b との間の境界線に沿って含まれている。第 3 および第 4 の N+ 領域 85c、85d は、第 1 および第 2 の SHNW94a、94b よりも高いドーピング濃度を有し、したがって、NPN 双方向性バイポーラトランジスタ 63 の絶縁破壊電圧を制御し、過渡電気的事象の間に PNPNP 構造内のフィードバックを強化するために使用することができる。10

#### 【0057】

加えて、異なるドーピング極性の活性領域が、第 1 および第 2 のゲート 87a、87b のそれぞれの反対側に埋め込まれているため、保護装置 80 は、従来の金属酸化膜半導体 (MOS) ドーピングを含まない、第 1 および第 2 のゲート 87a、87b を含む。しかしながら、第 2 のパッド 62 の電圧に対して第 1 のパッド 61 の電圧を増加させる過渡電気的事象の間に、電流は、第 1 のパッド 61 から第 1 のゲート 87a までのさらなる横方向均一性をさらに付け加え、それにより、キャリアが第 3 の N+ 領域 85c に到達して絶縁破壊を促すことができる、伝導経路を第 1 のゲート 87a の下に提供することができる。同様に、第 1 のパッド 61 の電圧に対して第 2 のパッド 62 の電圧を増加させる過渡電気的事象の間に、電流は、第 2 のパッド 62 から第 2 のゲート 87b までのさらなる横方向均一性をさらに付け加え、それにより、キャリアが第 4 の N+ 領域 85d に到達することができる、伝導経路を第 2 のゲート 87b の下に提供することができる。しかしながら、正常動作条件の間に、比較的高い準静的電圧でさえも、第 1 および第 2 のパッド 61、62 と第 3 および第 4 の N+ 活性領域 85c、85d との間のインピーダンスは、比較的高く、それにより、保護装置 80 の意図しない起動に対する強化した保護を提供し、常時漏出電流を最小限化することができる。20

#### 【0058】

保護装置 80 で使用される二重タブ絶縁は、P-SUB81 への寄生バイポーラ構造の形成を防止し、それにより、保護装置 80 の絶縁を強化する。例えば、保護装置 80 は、DPW93 から形成されるエミッタと、NBL89 から形成される基部と、P-SUB81 から形成されるコレクタとを含む、寄生 PNP バイポーラトランジスタ 99 を示すように注釈を付けられている。図 5B に示されるように、寄生 PNP バイポーラトランジスタ 99 は、SHNW94a、94b および SHPW92 等の PNP 双方向性バイポーラトランジスタ 63 を形成するために使用されるウェルからよりもむしろ、p 型タブおよび n 型タブから形成されるエミッタおよび基部を含む。この寄生 PNP バイポーラの n 型タブ基部は、高電力電圧でバイアスをかけることができ、さらに、電力上昇条件中に双方向性素子と機能的に相互作用することなく、基板への任意の電流経路を排除するとともに、保護クランプから同一の基板の中の他の構成要素までの任意の潜在的なラッチアップ経路を排除する。30

#### 【0059】

保護装置 80 は、図 4 の保護回路 60 の 1 つの実装を図示するが、保護回路 60 は、他の方法で実装することができる。例えば、基板から保護装置を絶縁するために使用される p 型および n 型タブは、他の方法で実装することができる。本明細書で使用されるようになつて理解されるように、「n 型タブ」という用語は、例えば、埋め込み n- 層技術または深 n- ウェル技術で使用されるものを含む、任意の好適な n 型タブを指す。同様に、「p 型タブ」という用語は、任意の好適な p 型タブを指す。40

#### 【0060】

図 6A は、一実施形態によれば、二重タブ絶縁双方向性保護装置 100 の概略上面レイ

50

アウト図である。図 6 B は、線 6 B - 6 B に沿って得られた図 6 A の保護装置 100 の注釈付き断面図である。保護装置 100 は、p 型基板 (P - S U B) 81 と、n 型埋め込み層 (N B L) 89 と、p 型エピタキシャル層 (P - E P I) 91 と、第 1 から第 4 の高電圧 n - ウェル (H V N W) 84a ~ 84d と、第 1 から第 5 の高電圧 p - ウェル (H V P W) 82a ~ 82e と、第 1 および第 2 の浅い n - ウェル (S H N W) 94a、94b と、浅い p - ウェル (S H P W) 92 と、第 1 から第 5 の p 型活性 (P+) 領域 83a ~ 83e と、第 1 から第 6 の n 型活性 (N+) 領域 85a ~ 85f と、第 1 および第 2 のゲート酸化物層 86a、86b、第 1 および第 2 のゲート 87a、87b と、酸化物領域 88 とを含む。明確にする目的で、H V N W および H V P W のみが図 6 A の上面レイアウト図で図示されている。このレイアウト上面図はまた、面積効率的な保護の形成を可能にし、ダイの周辺でパッケージ接着適合性を促進する、埋め込み接着パッド (図示せず) を含むこともできる。

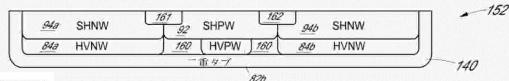

#### 【0061】

保護装置 100 は、図 5 A ~ 5 B の保護装置 80 の環状実装の一実施例を図示する。図 6 A ~ 6 B の保護装置 100 は、保護装置 100 がさらに、第 4 および第 5 の H V P W 82d、82e および第 5 の P+ 領域 83e を含むことを除いて、図 5 A ~ 5 B の保護装置 80 に類似する。加えて、保護装置 100 は、第 4 の H V N W 84d が第 4 の H V P W 82d を包囲する第 1 のリングであり、第 3 の H V P W 82c が第 4 の H V N W 84d を包囲する第 2 のリングであり、第 3 の H V N W 84c が第 3 の H V P W 82c を包囲する第 3 のリングであり、第 2 の H V P W 82b が第 3 の H V N W 84c を包囲する第 4 のリングであり、第 2 の H V N W 84b が第 2 の H V P W 82b を包囲する第 5 のリングであり、第 1 の H V P W 82a が第 2 の H V N W 84b を包囲する第 6 のリングであり、第 1 の H V N W 84a が第 1 の H V P W 82a を包囲する第 7 のリングであり、第 5 の H V P W 82e が第 1 の H V N W 84a を包囲する第 8 のリングであるように、アニュラリングとして構成される。リングとしてウェルを構成することにより、電流処理能力を向上させ、および / または保護装置の設置面積を縮小するのに役立つことができる。

#### 【0062】

図 6 A ~ 6 B は、本装置の中心が第 4 の H V P W 82d を含む構成を図示するが、特定の実装では、p 型ウェル領域よりもむしろ H V N W 等の n 型ウェル領域を本装置の中心で使用することができる。加えて、特定の構成では、第 4 の H V N W 84d および第 4 の H V P W 82d を省略することができ、第 3 の H V P W 82c は、保護装置の中心として動作するように構成することができる。

#### 【0063】

第 5 の H V P W 82e は、その中に形成された第 5 の P+ 領域 83e を含み、保護装置 100 の周囲のガードリングとして使用することができる。ガードリングは、過渡電気的事象の間に P - E P I 91 および / または P - S U B 81 に注入される電荷量をさらに低減するために使用することができる。特定の実装では、ガードリングを低電力電圧供給部に接続することができる。

#### 【0064】

一実施形態では、信号パッドは、第 2 の P+ 領域 83b に、および第 2 の N+ 領域 85b に電気的に接続され、低電力パッドは、第 3 の P+ 領域 83c に、および第 5 の N+ 領域 85e に電気的に接続される。

#### 【0065】

図 6 B は、保護装置 100 について上記で説明されるウェル、領域、および層の種々の寸法を示すように注釈を付けられている。例えば、保護装置 100 は、H V P W 82b の幅に対応する第 1 の寸法 d1、H V N W 84b の幅に対応する第 2 の寸法 d2、第 2 の P+ 領域 83b と第 3 の N+ 領域 85c との間の間隔に対応する第 3 の寸法 d3、および第 2 の N+ 領域 85b と第 2 の P+ 領域 83b との間の間隔に対応する第 4 の寸法 d4 を示すように注釈を付けられている。寸法は、本装置の左半分に関して示されているが、本装置の右半分は、類似寸法を有するように構成することができる。

10

20

30

40

50

## 【0066】

一実施形態では、第1の寸法d1は、約2.5μmから約8μmの範囲内、例えば、4μmであるように選択されるサイズを有し、第2の寸法d2は、約4μmから約8μmの範囲内、例えば、6.5μmであるように選択されるサイズを有し、第3の寸法d3は、約0.25μmから約2μmの範囲内、例えば、1μmであるように選択されるサイズを有し、第4の寸法d4は、約0μm(隣接)から約2μmの範囲内、例えば、0.6μmであるように選択されるサイズを有する。しかしながら、他の寸法が当業者によって容易に判定されるであろう。

## 【0067】

一実施形態では、保護装置100の設置面積は、約220μmから約170μmの範囲内、例えば、約200μmの幅×1を有し、保護装置100は、8kV IEC-61000-4-2ESD口バスト性レベルのために、約220μmから約170μmの範囲内、例えば、約200μmの高さ×2を有する。しかしながら、他の寸法が当業者によって容易に判定されるであろう。

10

## 【0068】

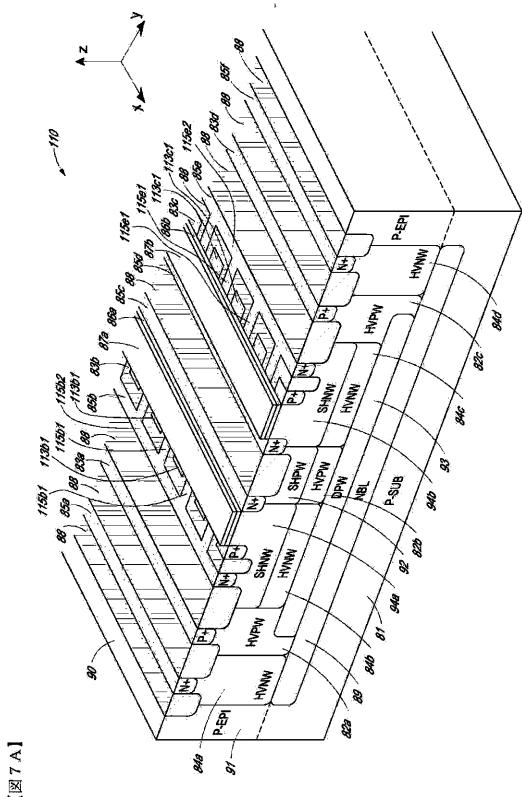

図7Aは、別の実施形態による、二重タブ絶縁双方向性保護装置110の概略斜視図である。保護装置110は、保護装置110が、第2および第3のP+領域83b、83c、ならびに第2および第5のN+領域85b、85eの異なる構成を含むことを除いて、図5A～5Bを参照して上記で説明される保護装置80に類似する。具体的には、図7Aの保護装置110では、第2のP+領域83bは、x方向に沿って配置される複数の島領域113b1を含み、第2のN+領域85bは、突出領域115b1のそれぞれが島領域113b1のうちの2つの間に延在するように、x方向に沿って配置される細長い領域115b2と、y方向に延在する突出領域115b1とを含む。同様に、第3のP+領域83cは、x方向に沿って配置される複数の島領域113c1を含み、第5のN+領域85eは、突出領域115e1のそれぞれが島領域113c1のうちの2つの間に延在するように、x方向に沿って配置される細長い領域115e2と、y方向に延在する突出領域115e1とを含む。

20

## 【0069】

このようにして保護装置110を構成することは、類似絶縁破壊電圧を維持しながら、図5A～5Bの保護装置80に対して図7Aの保護装置110の保持電圧を増加させるために使用することができる。保持電圧の増加は、図5BのPNPバイポーラトランジスタ64、65の利得および伝導強度に対して図5BのNPN双方向性バイポーラトランジスタ63の利得および伝導強度を強化するように、P+領域83b、83cのサイズに対してN+領域85b、85eのサイズを増加させることによって達成することができる。

30

## 【0070】

図7Bは、さらに別の実施形態による、二重タブ絶縁双方向性保護装置120の概略斜視図である。保護装置120は、保護装置120が、第2および第3のP+領域83b、83c、ならびに第2および第5のN+領域85b、85eの異なる構成を含むことを除いて、図5A～5Bを参照して上記で説明される保護装置80に類似する。具体的には、図7Bの保護装置120では、第2のN+領域85bは、x方向に沿って配置される複数の島領域125b1を含み、第2のN+領域83bは、突出領域123b1のそれぞれが島領域125b1のうちの2つの間に延在するように、x方向に沿って配置される細長い領域123b2と、y方向に延在する突出領域123b1とを含む。同様に、第5のN+領域85eは、x方向に沿って配置される複数の島領域125e1を含み、第3のP+領域83cは、突出領域123c1のそれぞれが島領域125e1のうちの2つの間に延在するように、x方向に沿って配置される細長い領域123c2と、y方向に延在する突出領域123c1とを含む。

40

## 【0071】

このようにして保護装置120を構成することはさらに、類似絶縁破壊電圧を維持しながら、図5A～5Bの保護装置80に対して図7Bの保護装置120の保持電圧を増加さ

50

するために使用することができる。保持電圧の増加は、図 5 B の N P N 双方向性バイポーラトランジスタ 6 3 の利得および伝導強度に対して図 5 B の P N P バイポーラトランジスタ 6 4、6 5 の利得および伝導強度を強化するように、N + 領域 8 5 b、8 5 e のサイズに対して P + 領域 8 3 b、8 3 c のサイズを増加させることによって達成することができる。

#### 【0072】

図 8 は、別の実施形態による、二重タブ絶縁保護装置 130 の断面図である。保護装置 130 は、本装置の各側面における阻止電圧接合部をカスタマイズするために、図 5 B の第 3 および第 4 の N + 領域 8 5 c、8 5 d が、それぞれ、第 1 および第 2 の P + 領域 133 a、133 b と置換されている構成を、保護装置 130 が図示することを除いて、図 5 A ~ 5 B を参照して上記で説明される保護装置 80 に類似する。第 1 および第 2 のゲート 87 a、87 b の各側面上の反対ドーピング極性の活性区域を維持し、常時漏出電流を最小限化するために、保護装置 130 はさらに、SH NW 9 4 a の中に配置される第 1 の N + 領域 135 a と、SH NW 9 4 b の中に配置される第 2 の N + 領域 135 b とを含む。P + 領域 133 a、133 b は、SH PW 9 2 よりも高いドーピング濃度を有し、したがって、過渡電気的事象の間に図 5 B の N P N 双方向性バイポーラトランジスタ 6 3 の絶縁破壊電圧を制御するために使用することができる。

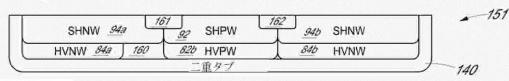

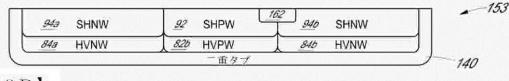

#### 【0073】

図 9 A ~ 9 I は、カスタム双方向性動作特性を提供するために使用することができる、二重タブ絶縁双方向性保護装置の種々の実施形態の部分断面図を図示する。図 9 A ~ 9 I は、SH PW 9 2、SH NW 9 4 a、9 4 b、HV NW 8 4 a、8 4 b、および HV PW 8 2 b 等の、その中に含有された特定の構造とともに、二重タブ絶縁構造 140 の断面を示す。二重タブ絶縁構造 140 は、前述の通りであり得る、p 型タブおよび n 型タブを含む。種々のウェルおよび活性領域が図 9 A ~ 9 I の断面図で図示されるが、N + 領域および P + 領域等の付加的な構造を、図示したウェルの中に形成することができるが、明確にするために図 9 A ~ 9 I から省略されている。例えば、図 5 A ~ 5 B の N + 領域 8 5 b および P + 領域 8 3 b を SH NW 9 4 a の中に形成することができ、図 5 A ~ 5 B の N + 領域 8 5 e および P + 領域 8 3 c を SH NW 9 4 b の中に形成することができる。

#### 【0074】

図示した断面は、順方向および逆方向の両方で保護装置のトリガおよび保持電圧特性の微調整された制御を提供するために使用することができる、図 5 A ~ 5 B の保護装置 80 の変形例を示す。図 9 A ~ 9 I では、順動作のための阻止電圧特性（左から右の正の過電圧）を制御するために使用される、変形例の実施例を識別するように、保護装置の左側が図 5 A ~ 5 B の保護装置 80 に対して変更される、構造が非対称的に形成されることが示されている。例えば、40 ~ 60 V 動作 B C D プロセスを使用する一実装では、図 9 A ~ 9 B の保護装置は、約 15 V 未満の順トリガ電圧（中ドーピングレベルから高ドーピングレベルの絶縁破壊）を提供することができ、図 9 C ~ 9 D の保護装置は、約 15 V から約 30 V の間の順トリガ電圧（中ドーピングレベルから中ドーピングレベルの絶縁破壊）を提供することができ、図 9 E ~ 9 F の保護装置は、約 15 V から約 30 V の間の順トリガ電圧（高ドーピングレベルから低ドーピングレベル絶縁破壊）を提供することができ、図 9 G および 9 H の保護装置は、約 30 V から約 40 V の間の順トリガ電圧（中ドーピングレベルから低ドーピングレベル絶縁破壊）を提供することができ、図 9 I の保護装置は、約 40 V よりも大きい順トリガ電圧（低ドーピングレベルから低ドーピングレベル絶縁破壊）を提供することができる。順トリガ電圧は、特定の処理技術を用いて増減または変化することができるが、図 9 A ~ 9 I の断面図は、特定の用途に所望される保護特性を達成するために使用することができる、保護装置の種々の構成を図示する。

#### 【0075】

図 9 A は、低濃度ドープの p 型領域 160 が HV NW 8 4 a と HV PW 8 2 b との間に形成されるように、HV NW 8 4 a が SH NW 9 4 a よりも小さい幅を有する、非対称保護装置 151 を図示する。p 型領域 160 は、p 型領域 160 が形成されるエピタキシャル

10

20

30

40

50

ル層のドーピング濃度等の背景ドーピング濃度に類似するドーピング濃度を有することができる。p型領域160を含むことにより、図5BのPNPバイポーラトランジスタ64の基本抵抗を増加させることができ、それは、過渡応答時間を向上させ、保護装置のトリガ電圧を減少させることができる。保護装置151はさらに、SHNW94aとSHPW92との間の境界線に沿って配置される第1の活性領域161と、第2の活性領域162とを含む。第1および第2の活性領域161、162は、n型またはp型ドーピング導電型のいずれか一方であり得る。

【0076】

図9Bは、p型領域160がHVPW82bとHVNW84a、84bのそれぞれとの間に形成されるように、HVPW82bがSHPW92の幅よりも小さい幅を有するように構成される、保護装置152を示す。このようにして保護装置152を構成することにより、代わりに、図5BのNPN双方向性バイポーラトランジスタ63の基本抵抗を増加させ、それは、保護装置のトリガ電圧を減少させ、より速い応答時間を提供することができる。図9Cは、保護装置の順トリガ電圧を増加させることができる、第1の活性領域161が省略されている保護装置153を図示する。図9Dは、第1の活性領域161が省略されており、図9Aと関連して論議されたように、p型領域160がHVNW84aとHVPW82bとの間に形成されるように、HVNW84aがSHNW94aよりも小さい幅を有する、保護装置154の構成要素を示す。

【0077】

図9Eは、SHNW94aがHVNW84aの幅よりも小さい幅を有する、保護装置155を示す。このようにして保護装置155を構成することは、阻止電圧を増加させることによって保護装置の順トリガ電圧を増加させることができる。加えて、このようにして本装置を構成することはまた、PNP基本抵抗、および図5BのNPN双方向性バイポーラトランジスタ63のコレクタ／エミッタに入る抵抗も増加させる。図9Fは、SHNW94a/HVNW84aおよび活性領域161領域からHVPW82bへの阻止電圧を増加させることによって保護装置の順トリガ電圧を増加させることができる、HVPW82bがSHPW92を包囲するように、SHPW92がHVPW82bの幅よりも小さい幅を有する、保護装置156を図示する。加えて、このようにして本装置を構成することはまた、図5BのNPN双方向性バイポーラトランジスタ63の基本抵抗も増加させる。図9Gは、HVPW82bがSHPW92の1つの側面を包囲するように、SHPW92がHVPW82bの幅よりも小さい幅を有する、保護装置157を示す。加えて、図9Gは、第1の活性領域161が省略されており、それにより、図9Fに示される構成に対して順トリガ電圧をさらに増加させる、実装を示す。保護装置157が、SHNW94aおよびHVPW82bによって形成される接合部によって定義される阻止電圧を有することができる一方で、接合部からSHPW92までの間隔は、パンチスルーエミッタ型阻止電圧の微調整を得るように調整することができる。図9Hは、SHNW94aの幅がHVNW84aの幅よりも小さく、第1の活性領域161が省略されている、保護装置158の構成を示す。図9Iは、HVNW84aがSHNW94aを包囲するように、SHNW94aの幅がHVNW84aの幅よりも小さい、保護装置159を図示する。加えて、図9Iでは、第1の活性領域161が省略されており、HVPW82bがSHPW92を包囲するように、SHPW92の幅がHVPW82bの幅よりも小さい。図9Iの保護装置159は、阻止電圧およびウェル抵抗を最適化するようにSHPW92およびSHNW94a、94bを維持しながら、比較的低いドーピング濃度を伴う2つの領域の間で阻止接合部形成を画定することによって、対応するプロセス技術のための最大阻止電圧条件を達成することができる。

【0078】

上記で説明される実施形態では、保護装置は、n型またはp型ドーパントを有する、層、領域、および／またはウェルを含むことができる。他の実施形態では、保護装置の全ての層、領域、およびウェルのドーピング型は、上記の実施形態で説明され、示されるものと反対であり得、同一の原理および利点が、他の実施形態に依然として該当することができる。

10

20

30

40

50

きる。例えば、n型基板およびn型エピタキシャル層を使用し、かつその中に形成されたウェル、活性領域、および埋め込み層のドーピング極性を逆転させることによって、図5 A～5 Bの保護装置の相補的バージョンを形成することができる。同様に、図6 A～9 Iに示される保護装置の相補的バージョンはまた、上記で説明される同一の原理の下でも可能である。

#### 【0079】

本明細書で使用されるような、上回る、下回る、以上等の用語は、図に示されるように配向される素子を指し、それに従って解釈されるべきである。また、半導体素子（トランジスタ等）内の領域が、異なる不純物または異なる不純物の濃度で半導体材料の異なる部分をドープすることによって画定されるため、異なる領域間の離散した物理的境界線は、完成した素子の中で実際に存在しなくてもよいが、代わりに、領域は1つのものから別のものへ遷移してもよいことも理解されたい。添付図に示されるようないくつかの境界線は、この種類であり、読者の支援のために急な構造として図示されるにすぎない。上記で説明される実施形態では、p型領域は、ドーパントとしてホウ素等のp型半導体材料を含むことができる。さらに、n型領域は、ドーパントとしてリン等のn型半導体材料を含むことができる。当業者であれば、上記で説明される領域の中の種々のドーパントの濃度を理解するであろう。

#### 【0080】

（ラッチャップ防止寄生PNPN素子を伴う送受信機信号絶縁装置）

図4で図示される保護回路60等の双方向性保護回路は、第1および第2のパッド61および62の間のトリガ電圧を超える電圧差を誘発する過渡電気的事象に応答して、大量の電流を放出するように電流分路を提供する。高電流路が、シリコン制御整流器（SCR）構成で構成される、第1のPNPバイポーラトランジスタ64、NPN双方向性バイポーラトランジスタ63、および第2のPNPバイポーラトランジスタ65によって可能にされる。加えて、高度にドープされたp型タブ68と、高度にドープされたn型タブ69とを備える、二重タブ絶縁が、主要送受信機回路の他の構成要素との相互作用を最小限化しながら、保護回路60の最大電圧処理能力を可能にしてもよい。

#### 【0081】

ある実装下では、図4の保護回路60等の双方向性保護回路を製造する結果として形成する、寄生素子があってもよい。寄生素子は、保護回路60のコア領域を形成する、特定の領域を共有してもよい。例えば、成長したままのp型エピタキシャル領域もまた、保護回路60の二重タブ絶縁を形成するp型タブ68およびn型タブ69とともに、寄生PNPバイポーラトランジスタを形成してもよい。そのような寄生素子は、第1および第2のPNPバイポーラトランジスタ64および65ならびにNPN双方向性バイポーラトランジスタ63を通して接続される、第1および第2のパッド61および62の間の主要電流路の代わりに、それを通して過渡電気的事象が放し得る、代替的な電流路を提供してもよい。そのような経路を通る電流の流れは、そのような事象のために設計されていない送受信機回路の部分を通して大量の電流の放出をもたらし、回路への望ましくない損傷および信頼性の問題をもたらし得るため、望ましくない場合がある。したがって、寄生素子を通る高電流の流れを防止する必要がある。

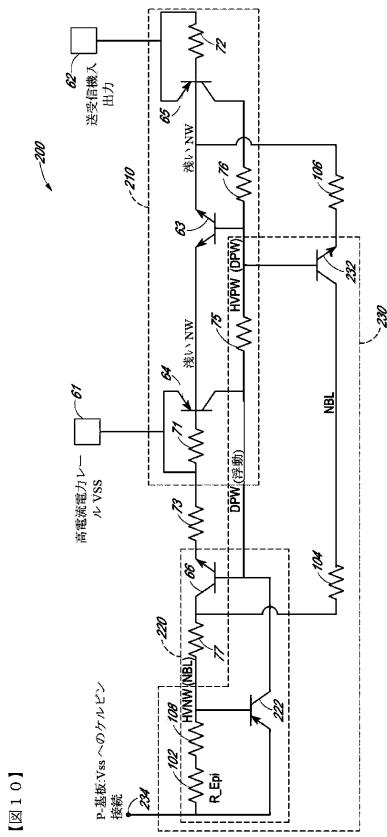

#### 【0082】

図10は、一実施形態による、概略的な双方向性保護回路200を図示する。双方向性保護回路200は、バイポーラPNPNP素子アセンブリ210と、第1の寄生PNPN素子アセンブリ220と、第2の寄生PNPN素子アセンブリ230とを含む。保護回路200は、特定の臨界値を超える第1および第2のパッド61および62の間の電圧差を誘発する、外部過渡電気的事象に応答して、バイポーラPNPNP素子アセンブリ210を通る電流分路を提供するように構成することができる。例えば、第2のパッド62は、図1および3の第1および第2の信号ピン4、5等のICの信号ピンまたはパッドであり得、第1のパッド61は、図1および3の低電力電圧供給部V1と関連付けられるパッド等の低電力ピンまたはパッドであり得る。

10

20

30

40

50

## 【0083】

一実施形態では、第2のパッド62は、送受信機I/Oパッドとして構成されてもよい。第1のパッド61は、VSSまたは接地であり得る、図1の送受信機回路1等の送受信機回路の基板に接続されるように構成することができる。第1のパッド61と送受信機回路基板との間の接続は、高電流電力レールを通して行うことができる。高電流電力レールは、典型的には、比較的低い抵抗を有し、過渡電気的事象に応答して、比較的大量の電流を処理するように設計されている。保護回路200はさらに、同様にVSSまたは接地であり得る、図1に示される送受信機回路1の基板に接続することができる。送受信機回路1の基板と保護回路200の基板との間の接続は、ケルビン接続234を通して行われてもよい。第1のパッド61および送受信機回路基板を接続し得る、比較的高い電流の電力レール接続と比較して、ケルビン接続234は、抵抗が比較的高くあり得るが、高電流電力レールを通過するように比較的大量の電流をトリガすることができる、同一の過渡電気的事象に応答して流れる、比較的少量の電流を通過させる。第1のパッド61およびケルビン接続234の両方が、VSSまたは接地であり得る、送受信機回路1の基板に接続し、平衡条件下では、双方向性保護回路200と送受信機回路1の基板との間に感知可能な電流がないため、第1のパッド61およびケルビン接続234における電圧電位は、ほぼ同一である。しかしながら、過渡電気的事象の間に、比較的大量の電流が、高電流電力レールを介して双方向性保護回路200と送受信機回路1の基板との間を流れるため、たとえそれが送受信機回路1の基板に接続しても、第1のパッド61とケルビン接続234との間に電位の差があり得るように、高電流電力レールに沿って比較的大きい電圧降下がある。

## 【0084】

双方向性保護回路200は、バイポーラPNPNP素子アセンブリ210を含む。バイポーラPNPNP素子アセンブリ210は、図4において上記で説明されるのと同様に配列される、NPN双方向性バイポーラトランジスタ63と、第1のPNPバイポーラトランジスタ64と、第2のPNPバイポーラトランジスタ65と、第1および第2の抵抗器71および72と、第5および第6の抵抗器75および76とを含む。具体的には、第1のパッド61は、第1の抵抗器71および第1のPNPバイポーラトランジスタ64のエミッタを通してPNPNP素子アセンブリ210に電気的に接続される。第1のPNPバイポーラトランジスタ64は、第1のパッド61に電気的に接続されるエミッタと、第1の寄生NPNバイポーラトランジスタ66の基部に電気的に接続されるコレクタとを含む。第1のPNPバイポーラトランジスタ64はさらに、NPN双方向性バイポーラトランジスタ63のコレクタ/エミッタC/Eに、および第1の抵抗器71に電気的に接続される、基部を含む。第2のパッド62は、第2の抵抗器72および第2のバイポーラトランジスタ65のエミッタを通してPNPNP素子アセンブリ210に電気的に接続される。第2のPNPバイポーラトランジスタ65は、第2のパッド62に電気的に接続されるエミッタと、第6の抵抗器76を通して第2の寄生NPNバイポーラトランジスタ232の基部に電気的に接続されるコレクタとを含む。第2のPNPバイポーラトランジスタ65はさらに、NPN双方向性バイポーラトランジスタ63のエミッタ/コレクタE/Cに、および第2の抵抗器72に電気的に接続される、基部を含む。NPN双方向性バイポーラトランジスタ63は、第1のPNPバイポーラトランジスタ64の基部に電気的に接続されるコレクタ/エミッタC/Eと、第2のPNPバイポーラトランジスタ65の基部に電気的に接続されるエミッタ/コレクタE/Cとを含む。NPN双方向性トランジスタはさらに、第5の抵抗器75を通して第1のPNPバイポーラトランジスタ64のコレクタに接続され、さらに第6の抵抗器76を通して第2のPNPバイポーラトランジスタ65コレクタに接続される、基部を含む。

## 【0085】

双方向性保護回路200は、加えて、第1の寄生PNPNN素子アセンブリ220を含む。第1の寄生PNPNN素子アセンブリ220は、寄生PNPバイポーラトランジスタ222と、第1の寄生NPNバイポーラトランジスタ66と、第7の抵抗器77と、第9の抵

10

20

30

40

50

抗器 102 と、第 12 の抵抗器 108 とを含む。寄生 PNPバイポーラトランジスタ 222 は、送受信機回路 1 の p - 基板に、および第 9 の抵抗器 102 に電気的に接続される、エミッタを含む。寄生 PNPバイポーラトランジスタ 222 はさらに、直列に接続された第 9 の抵抗器 102 および第 12 の抵抗器 108 を通してエミッタに接続される基部を含む。寄生 PNPバイポーラトランジスタ 222 の基部はさらに、第 7 の抵抗器 77 を通して寄生 NPNバイポーラトランジスタ 66 のコレクタに接続される。寄生 PNPバイポーラトランジスタ 222 はさらに、第 1 の寄生 NPNバイポーラトランジスタ 66 の基部に接続されるコレクタを含む。第 1 の寄生 NPNバイポーラトランジスタ 66 は、第 3 の抵抗器 73 に電気的に接続されるエミッタと、寄生 PNPバイポーラトランジスタ 222 のコレクタに電気的に接続される基部とを含む。第 1 の寄生 NPNバイポーラトランジスタ 66 はさらに、第 7 の抵抗器 77 を通して寄生バイポーラ PNPトランジスタ 222 の基部に電気的に接続されるコレクタを含む。

10

#### 【 0086 】

双方向性保護回路 200 はさらに、第 2 の寄生 PNPN 素子アセンブリ 230 を含む。第 2 の寄生 PNPN 素子アセンブリ 230 は、寄生 PNPバイポーラトランジスタ 222 と、第 2 の寄生 NPNバイポーラトランジスタ 232 と、第 5 の抵抗器 75 と、第 7 の抵抗器 77 と、第 9 の抵抗器 102 と、第 10 の抵抗器 104 と、第 12 の抵抗器 108 とを含む。寄生 PNPバイポーラトランジスタ 222 は、送受信機回路 1 の p - 基板に、および第 9 の抵抗器 102 に電気的に接続される、エミッタを含む。寄生 PNPバイポーラトランジスタ 222 はさらに、第 9 の抵抗器 102 および第 12 の抵抗器 108 を通してエミッタに接続される基部を含む。寄生 PNPバイポーラトランジスタ 222 の基部はさらに、直列に接続された第 7 の抵抗器 77 および第 10 の抵抗器 104 を通して第 2 の寄生 NPNバイポーラトランジスタ 232 のコレクタに接続される。寄生 PNPバイポーラトランジスタ 222 はさらに、第 5 の抵抗器 75 を通して第 2 の寄生 NPNバイポーラトランジスタ 232 の基部に接続されるコレクタを含む。第 2 の寄生 NPNバイポーラトランジスタ 232 は、第 11 の抵抗器 106 に接続されるエミッタと、第 5 の抵抗器 75 を通して寄生 PNPバイポーラトランジスタ 222 のコレクタに接続される基部とを含む。第 2 の寄生 NPNバイポーラトランジスタ 232 はさらに、第 10 の抵抗器 104 および第 7 の抵抗器 77 を通して寄生 PNPバイポーラトランジスタ 222 の基部に電気的に接続されるコレクタを含む。

20

#### 【 0087 】

バイポーラ PNPNP 素子アセンブリ 210 の動作は、図 4 に関連して説明されるものに類似する。具体的には、過渡電気的事象が第 1 のパッド 61 と第 2 のパッド 62 との間の絶対電圧差を増加させると、NPN 双方向性バイポーラトランジスタ 63 および第 1 の PNPバイポーラトランジスタ 64 または第 2 の PNPバイポーラトランジスタ 65 のうちの 1 つは、上記で説明されるようなシリコン制御整流器 (SCR) 構成で第 1 の交差連結バイポーラ PNPNバイポーラトランジスタとして動作する。例えば、過渡電気的事象が、第 2 のパッド 62 の電圧を超えるように第 1 のパッド 61 の電圧を誘導するとき（または代替として、第 2 のパッド 62 の電圧が第 1 のパッド 61 の電圧を下回る）、PNPバイポーラトランジスタ 64 のエミッタ・基部接合部およびコレクタ・基部接合部は、それぞれ、順方向バイアスおよび逆方向バイアスをかけられる。この状況下で、NPN 双方向性バイポーラトランジスタ 63 のエミッタ / コレクタ E / C は、エミッタとしての機能を果たし、NPN 双方向性バイポーラトランジスタ 63 のコレクタ / エミッタ C / E は、コレクタとしての機能を果たす。いったん第 1 のパッド 61 と第 2 のパッド 62 との間の正の電圧差がトリガ電圧 + VTR を超えるとき、PNPNP 素子アセンブリ 210 は、図 2 に関連して説明される低インピーダンスモードになる。低インピーダンスモードは、第 1 または第 2 の PNPバイポーラトランジスタ 64 および 65 のうちの 1 つと NPN 双方向性バイポーラトランジスタ 63 との間に形成される、フィードバックループによってトリガされる。フィードバックループは、以下のように動作する。第 1 または第 2 の PNPバイポーラトランジスタ 64 または 65 のコレクタ電流の増加が、NPN 双方向性バイポ

30

ーラトランジスタ 6 3 の基本電流を増加させ、N P N 双方向性バイポーラトランジスタ 6 3 のコレクタ電流の増加が、第 1 または第 2 の P N P バイポーラトランジスタ 6 4 または 6 5 の基本電流を増加させる。フィードバックループは、個々のバイポーラトランジスタの利得により、再正式であり、P N P N P 素子アセンブリ 2 1 0 を低インピーダンス状態にさせ得る。いったん低インピーダンス状態になると、P N P N P 素子アセンブリ 2 1 0 は、第 1 および第 2 のピン 6 1 および 6 2 にわたる電圧が保持電圧 + V H を下回る、または電流が + I H を下回る、または両方となるまで、低インピーダンス状態にとどまるであろう。過渡電気的事象が、第 1 のパッド 6 1 の電圧を超えるように第 2 のパッド 6 2 の電圧を誘導するとき（または代替として、第 1 のパッド 6 の電圧が第 2 のパッド 6 2 の電圧を下回る）に、類似する状況が発生する。この状況下で、P N P バイポーラトランジスタ 6 5 のエミッタ・基部接合部およびコレクタ・基部接合部は、それぞれ、順方向バイアスおよび逆方向バイアスをかけられる。この状況下で、N P N 双方向性バイポーラトランジスタ 6 3 のコレクタ / エミッタ C / E は、エミッタとしての機能を果たし、双方向性バイポーラトランジスタのエミッタ / コレクタ E / C は、コレクタとしての機能を果たす。いったん第 1 のパッド 6 1 と第 2 のパッド 6 2 との間の負の電圧差が絶対値でトリガ電圧 - V T R を超えると、P N P N P 素子アセンブリは、図 2 に関連して説明される低インピーダンスモードになる。いったん低インピーダンス状態になると、P N P N P 素子は、第 1 および第 2 のピン 6 1 および 6 2 にわたる電圧が絶対値で - V H を下回る、または電流が絶対値で - I H を下回る、または両方となるまで、低インピーダンス状態にとどまるであろう。

10

20

#### 【 0 0 8 8 】

保護回路 2 0 0 は、P N P N P 素子アセンブリ 2 1 0 と、保護回路 2 0 0 を伴う共通基板の中に形成される外部構成要素および回路との間の相互作用を低減させる、図 4 の保護回路 6 0 に類似する二重タブ絶縁を含む。しかしながら、上記で論議されるように、特定の実装下で、P N P N P 素子アセンブリ 2 1 0 および二重タブ絶縁を作成するように形成される種々の領域に起因し得る、寄生素子アセンブリがあってもよい。これらの寄生素子は、望ましくない信頼性故障を引き起こし得る、代替または付加的な電流路を提供してもよい。

#### 【 0 0 8 9 】

具体的には、図 1 0 の図示した実施形態では、第 1 の寄生 P N P N 素子アセンブリ 2 2 0 は、過渡電気的事象に応答して、代替的な電流路を提供してもよい。図 1 0 に図示されるように、第 1 の寄生 P N P N 素子アセンブリ 2 2 0 は、シリコン制御整流器（S C R）構成で配列される、寄生 P N P バイポーラトランジスタ 2 2 2 および第 1 の寄生 N P N バイポーラトランジスタ 6 6 を含む。具体的には、寄生 P N P バイポーラトランジスタ 2 2 2 のコレクタは、第 1 の寄生 N P N バイポーラトランジスタ 6 6 の基部に接続され、第 1 の寄生 N P N バイポーラトランジスタ 6 6 のコレクタは、寄生 P N P バイポーラトランジスタ 2 2 2 の基部に接続される。バイポーラ P N P N P 素子アセンブリ 2 1 0 と同様に、第 1 の寄生バイポーラトランジスタ 6 6 に連結された寄生 P N P バイポーラトランジスタ 2 2 2 は、第 1 の P N P N 素子アセンブリ 2 2 0 にわたる電圧が特定の値を超えるときに、再正フィードバックループに入ってもよい。具体的には、いったんケルビン接続 2 3 4 と第 1 のパッド 6 1 との間の正の電圧差が第 1 の寄生 P N P N 素子アセンブリ 2 2 0 のトリガ電圧 + V T R を超えるとき、第 1 の P N P N 素子アセンブリ 2 2 0 は、フィードバックループにより P N P N P 素子アセンブリ 2 1 0 で起こるものに類似する、低インピーダンスモードになってもよい。フィードバックループは、第 1 の寄生 N P N バイポーラトランジスタ 6 6 の基本電流を増加させる、寄生 P N P バイポーラトランジスタ 2 2 2 のコレクタ電流の増加、および寄生 P N P バイポーラトランジスタ 2 2 2 の基本電流を増加させる、第 1 の寄生 N P N バイポーラトランジスタ 6 6 のコレクタ電流の増加といったように、動作する。P N P N P 素子アセンブリ 2 1 0 の場合のように、いったん低インピーダンス状態になると、第 1 の寄生 P N P N 素子アセンブリ 2 2 0 は、ケルビン接続 2 3 4 と第 1 のパッド 6 1 との間の正の電圧差が + V H を下回る、または電流が + I H を下回る、ま

30

40

50

たは両方となるまで、低インピーダンス状態にとどまるであろう。

【0090】

図10の図示した実施形態は、加えて、過渡電気的事象に応答して別の代替的な電流路を提供し得る、第2の寄生P N P N素子アセンブリ230を含む。第2の寄生P N P N素子アセンブリ230は、シリコン制御整流器（SCR）構成で配列される、寄生P N Pバイポーラトランジスタ222および第2の寄生N P Nバイポーラトランジスタ232を含む。具体的には、寄生P N Pバイポーラトランジスタ222のコレクタは、第2の寄生N P Nバイポーラトランジスタ232の基部に接続され、第2の寄生N P Nバイポーラトランジスタ232のコレクタは、寄生P N Pバイポーラトランジスタ222の基部に接続される。P N P N P素子アセンブリ210と同様に、第2の寄生P N Pバイポーラトランジスタ232に連結された寄生P N Pバイポーラトランジスタ222は、第2の寄生P N P N素子アセンブリ230のトリガ電圧+VTRを超えるケルビン接続234と第2のパッド62との間の正の電圧差に応答して、低インピーダンスマードになってもよい。トリガ機構、ならびに第2のP N P N素子アセンブリ230が低インピーダンス状態にとどまる条件は、第1の寄生P N P N素子アセンブリ220について上記で説明されるものに類似する。

【0091】

第1および第2の寄生P N P N素子アセンブリ220および230が、バイポーラP N P N P素子アセンブリ210と同様にトリガされ得るため、第1および第2の寄生P N P N素子アセンブリ220および230が、P N P N P素子アセンブリ210のトリガ電圧値よりも大きいトリガ電圧値を有するように、双方向性保護回路200を設計することが望ましくあり得る。第1および第2の寄生P N P N素子アセンブリ220および230のトリガ電圧値を制御する、多くの要因があつてもよい。一般に、キャリア寿命の比、ドーピングの比、およびエミッタと基部との間の拡散距離の比が、概して、所与のバイポーラトランジスタの利得を決定する。概して、第1および第2の寄生P N P N素子アセンブリ220および230内の個々のバイポーラトランジスタのより高い利得が、ひいては、より低いトリガ電圧をもたらす。例えば、基部の中のより長い小数キャリア寿命、基部の中のより低いドーピング濃度、およびより小さい物理的な基部幅が、寄生P N Pバイポーラトランジスタ222のより高い利得をもたらし得る。寄生P N Pバイポーラトランジスタ222のより高い利得が、ひいては、第1および第2の寄生P N P N素子アセンブリ220および230のより低いトリガ電圧をもたらすことができる。同様に、第1および第2の寄生N P Nバイポーラトランジスタ66および232のより高い利得もまた、それぞれ、第1および第2の寄生P N P N素子アセンブリ220および230のより低いトリガ電圧をもたらすことができる。

【0092】

第1および第2の寄生P N P N素子アセンブリ220および230のより高いトリガ電圧を有することが、概して望ましくあり得る一方で、当業者であれば、双方向性保護回路200の全体的な回路を設計するときに、他の要因も考慮することが重要であり得ることを理解するであろう。特定の実装では、バイポーラP N P N P素子アセンブリ210のトリガ前インピーダンス値に対して有意に高い、寄生P N P N素子アセンブリ220および230のトリガ前インピーダンス値を有することが望ましくない場合がある。これらの状況下で、より高い電圧が、バイポーラP N P N P素子アセンブリ210と比較して、第1のおよび/または第2の寄生P N P N素子アセンブリ220および230にわたって低下し、優先的に寄生P N P N素子アセンブリをトリガさせ得る。これらの状況下で、トリガ前インピーダンスとトリガ電圧との間にトレードオフがあつてもよい。例えば、より高い寄生P N P Nトリガ前インピーダンスを有する設計が、より低いP N P Nトリガ電圧につながり、その逆も同様であり得る。したがって、均衡のとれたトリガ前インピーダンス値およびトリガ電圧を有することが、望ましくあり得る。

【0093】

また、P N P N P素子アセンブリ210の素子パラメータに行われる変更が、第1のお

10

20

30

40

50

および/または第2の寄生PNPN素子アセンブリ220および230の素子パラメータに影響を及ぼさないように、バイポーラPNPNP素子アセンブリ210の素子性質に影響を及ぼす設計要因から独立している、第1および第2の寄生PNPN素子アセンブリ220および230の設計要因を有することが望ましくあり得る。

【0094】

図10で図示されるような一実施形態では、直列の第9および第12の抵抗器102、108を通して寄生PNPバイポーラトランジスタ222の基部およびエミッタを接続すること、および2つの抵抗器の複合抵抗値を制御することを通して、第1および第2の寄生PNPN素子アセンブリ220および230の適正に最適化された漏出およびトリガ特性が達成されてもよい。第9および第12の抵抗器102および108の複合抵抗の相対値に応じて、寄生PNPバイポーラトランジスタ222の構成は、BVCES状態（エミッタ・基部が短絡したコレクタ・エミッタ絶縁破壊電圧）、BVCEO状態（基部が開いているコレクタ・エミッタ絶縁破壊電圧）、およびBVCER状態（エミッタ・基部が抵抗によって接続されているコレクタ・エミッタ絶縁破壊）として知られている、3つのモードのうちの1つであってもよい。

【0095】

具体的には、一実装では、第9および第12の抵抗器102および108の複合抵抗の値がほぼゼロである（すなわち、短絡した）か、または非常に低いとき、寄生PNPバイポーラトランジスタ222は、BVCES状態（エミッタ・基部が短絡した絶縁破壊）と呼ばれる状態であるように構成される。これらのモードの間で、BVCES状態は、概して、寄生PNPバイポーラトランジスタ222の逆バイアス基部・コレクタ接合部の最高絶縁破壊電圧をもたらし、それがひいては、第1および第2の寄生PNPN素子アセンブリ220および230のより高いトリガ電圧をもたらし得る。同時に、BVCES状態は、概して、最低トリガ前インピーダンス、したがって、第1および第2の寄生PNPN素子アセンブリ220および230を通る最高漏出電流をもたらす。

【0096】

別の実装下で、第9および第12の抵抗器102および108の複合抵抗の値が非常に高い（すなわち、開回路）とき、寄生PNPバイポーラトランジスタ222は、BVCEO状態（エミッタ・基部が開いている絶縁破壊）と呼ばれる状態であるように構成される。これらのモードの間で、BVCEO状態は、概して、寄生PNPバイポーラトランジスタ222の逆バイアス基部・コレクタ接合部の可能な限り低い絶縁破壊電圧をもたらし、それがひいては、第1および第2の寄生PNPN素子アセンブリ220および230のより低いトリガ電圧をもたらし得る。同時に、BVCEO状態は、概して、最高トリガ前インピーダンス、したがって、第1および第2の寄生PNPN素子アセンブリ220および230を通る最低漏出電流をもたらす。

【0097】

さらに別の好ましい実装下で、第9および第12の抵抗器102および108の複合抵抗の値は、中間値であってもよく、寄生PNPバイポーラトランジスタ222は、BVCER状態（エミッタ・基部が抵抗器によって接続されている絶縁破壊）と呼ばれる状態であるように構成される。これらのモードの間で、BVCER状態は、概して、寄生PNPバイポーラトランジスタ222の逆バイアス基部・コレクタ接合部の中間絶縁破壊電圧をもたらし、それがひいては、第1および第2の寄生PNPN素子アセンブリ220および230の中間トリガ電圧をもたらし得る。同様に、BVCER状態は、概して、中間トリガ前インピーダンス、したがって、第1および第2の寄生PNPN素子アセンブリ220および230を通る中間漏出電流をもたらす。BVCER状態の寄生PNPバイポーラトランジスタ222は、第1および第2の寄生PNPN素子アセンブリ220および230のトリガ前インピーダンスとトリガ電圧との間の適正な均衡を可能にしてもよい。また、以下で論議されるように、第9および第12の抵抗器102および108の抵抗値は、バイポーラPNPNP素子アセンブリ210に影響を及ぼすプロセスパラメータとは大部分が無関係であるプロセスを通して制御される。

10

20

30

40

50

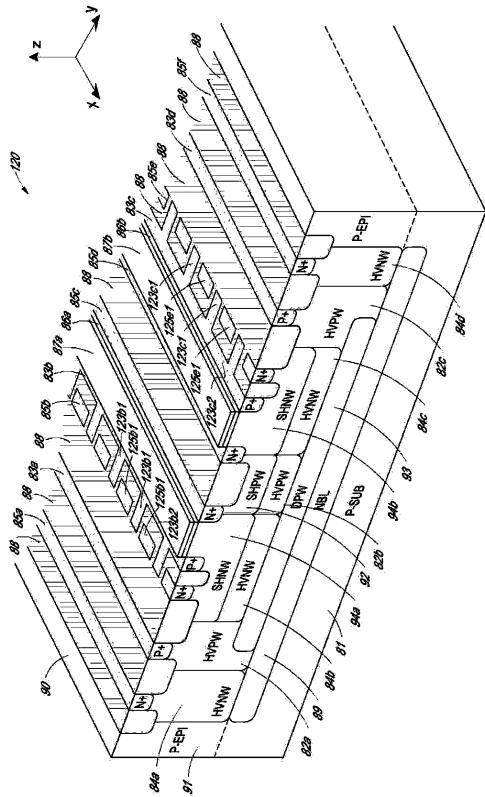

## 【0098】

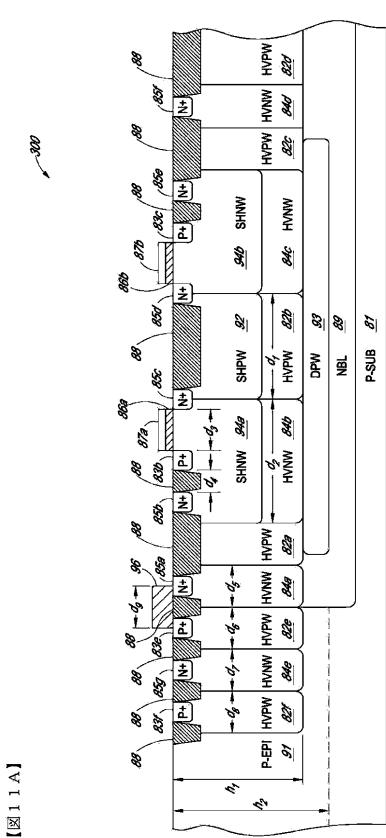

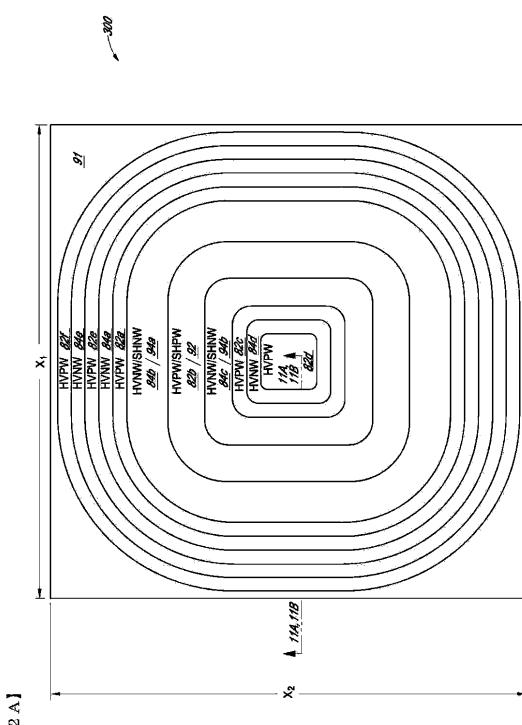

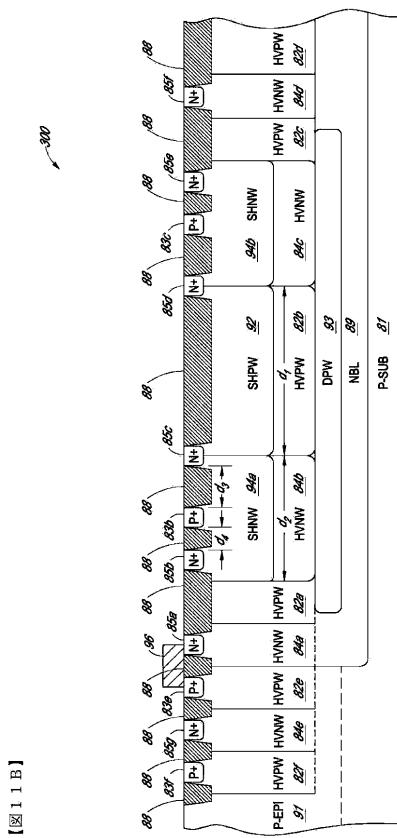

図11Aは、上面図が図12Aで図示される、一実施形態による、双方向性保護装置300の環状実装の断面図である。具体的には、図11Aは、図12Aの断面11A-11Aを通した図を表す。明確にするために、図12Aは、活性領域より下側の（最初に第7のN+領域85a～85g、そして第2、第3、第5および第6のP+領域83b、83c、83e、83fを通る）種々のウェル領域、および酸化物領域88のみを示す。図11Aおよび12Aを参照すると、双方向性保護装置300は、図6Aおよび6Bの保護装置100の環状実装に類似する。図示した実施形態の対称性により、（図に示される）本装置の一方の半分に関して以下で論議される特徴はまた、本装置の他方の半分（図示せず）にも適用可能であり得る。図11Aおよび12Aの双方向性保護装置300の中心位置は、第4の高電圧p-ウェル（HVPW）82dを備え、その周囲で、第4の高電圧n-ウェル（HVNW）84dが第1のリングを形成し、第3の高電圧p-ウェル（HVPW）82cが第2のリングを形成し、第2の浅いn-ウェル（SHNW）94b／第3の高電圧n-ウェル（HVNW）84cが第3のリングを形成し、浅いp-ウェル（SHPW）92／第2の高電圧p-ウェル（HVPW）82bが第4のリングを形成し、第1の浅いn-ウェル（SHNW）94a／第2の高電圧n-ウェル（HVNW）84bが第5のリングを形成し、第5の高電圧p-ウェル（HVPW）82aが第6のリングを形成し、第1の高電圧n-ウェル（HVNW）84aが第7のリングを形成し、第5の高電圧p-ウェル（HVPW）82eが第8のリングを形成し、各リングは、前のリングを包囲し、第1から第8のリングのそれぞれは、連続同心円状リングを形成するように第4のHVPW82dを包囲し、第4の高電圧p-ウェル（HVPW）82dは、双方向性保護装置300の中心位置を形成する。10

## 【0099】

加えて、双方向性保護装置300はさらに、第5の高電圧p-ウェル（HVPW）82eを包囲する第5の高電圧n-ウェル（HVNW）84eによって形成される第9のリングと、第5の高電圧n-ウェル（HVNW）84eを包囲する第6の高電圧p-ウェル（HVPW）82fによって形成される第10のリングとを含む。双方向性保護装置300はさらに、第6の高電圧p-ウェル（HVPW）によって形成される第10のリングを包囲する、p型エピタキシャル層（P-EPI）91を含む。20

## 【0100】

明確にする目的で、HVNWおよびHVPWのみが、図12Aの上面レイアウト図で図示されている。図6Bで図示される保護装置と同様に、図11Aの双方向性保護装置300は、第2、第3、第5、および第6の活性（P+）領域83b、83c、83e、83fと、第1から第6のn型活性（N+）領域85a～85fと、第1および第2のゲート酸化物層86a、86bと、第1および第2のゲート87a、87bと、酸化物領域88とを含む。加えて、双方向性保護装置300は、第5のHVNW84eの中に形成される第7のn型活性（N+）領域と、第6のHVPW82fの中に形成される第6のp型活性（P+）領域83fとを含む。加えて、酸化物領域88は、第5のP+領域83eと第7のN+領域85gとの間、第7のN+領域85gと第6のP+領域83fとの間、および第6のP+領域83fとP-EPI91との間に配置される。30

## 【0101】

また、図6Bの保護装置100と同様に、双方向性保護装置300の深いp-ウェル（DPW）93は、第4の高電圧p-ウェル（HVPW）82dを備える双方向性保護装置300の中心位置を包囲する、アニュラリングを形成するように、第2および第3の高電圧n-ウェル（HVNW）84bおよび84c、第1から第3の高電圧p-ウェル（HVPW）82a～82c、第1および第2の浅いn-ウェル（SHNW）94aおよび94b、ならびに浅いp-ウェル（SHPW）92より下側に配置される。また、図6Bの保護装置100と同様に、n型埋め込み層（NBL）89は、DPW93を包囲するように、HVNW84a、HVNW84d、HVPW82d、およびDPW93より下側に配置される。40

## 【0102】

双方向性保護装置300の第1から第5のHVNW84a～84eおよび第1から第6のHVPW82a～82fは、p型基板(P-SUB81)の中への第1の深度h1を有する。双方向性保護装置300はさらに、P-EPI91が第1の深度h1よりも深く延在する第2の深度h2を有することを除いて、図6Bの保護装置100に類似するp型エピタキシャル層(P-EPI)91を含む。結果として、P-EPI91は、第6のHVPW82fを水平に包囲する第1のp型エピタキシャル領域と、DPW93を水平に包囲するように第1のp型エピタキシャル領域、第6のHVPW82f、第5のHVNW84e、および第5のHVPW82eよりも下側に配置される、第2のp型エピタキシャル領域とを含む。加えて、双方向性保護装置300はまた、NBL89およびP-EPI91より下側に配置されるp型基板(P-SUB)81も含む。10

## 【0103】

図示した実施形態の双方向性保護装置300は、シリコン基板より上側に配置され、第5のP+領域83eの少なくとも一部分を覆って、第1のN+領域85aの少なくとも一部分を覆って、かつP+領域83eとN+領域85aとの間の酸化物領域88を覆って形成される、直列抵抗器96を含む。実施形態では、直列抵抗器96は、第5のP+領域83eの一部分および第1のN+領域85aの一部分に重複するように基板の表面と平行な半径方向に延在する。別の実施形態では、直列抵抗器96は、基板の表面と平行な半径方向に第5のP+領域83e全体および第1のN+領域85a全体に重複するように延在する。20

## 【0104】

実施形態では、直列抵抗器96は、n型ポリシリコンを含む。別の実施形態では、直列抵抗器96は、p型ポリシリコンを含む。さらに別の実施形態では、直列抵抗器96は、金属または金属窒化物を含む。

## 【0105】

図11Aの図示した実施形態はさらに、第1および第2のゲート酸化物層86aおよび86bと、第1および第2のゲート87aおよび87bとを含む。図6Bで説明されるその機能と同様に、第1のパッド61と第2のパッド62との間の電圧差を増加させる過渡電気的事象の間に、第1および第2のゲート87aおよび87bは、電流が、それぞれ、第1のパッド61から第1のゲート87aまで、および第2のパッド62から第2のゲート87bまでのさらなる横方向均一性をさらに付け加えることを可能にする。図11Bで図示される別の実施形態では、第1および第2のゲート87aおよび87bは、それぞれ、P+領域83cとN+領域85dとの間、およびN+領域85cとP+領域83bとの間に配置される、酸化物領域88と置換されてもよい。30

## 【0106】

図11Aは、双方向性保護装置300について上記で説明されるウェル、領域、および層の種々の寸法を示すように注釈が付けられている。図6Bの保護装置100と同様に、第1から第4の寸法d1からd4は、HVPW82b、HVNW84b、第3のN+領域85cと第2のP+領域83bとの間の間隔、および第2のP+領域83bと第2のN+領域85bとの間の間隔の幅に対応する。加えて、第5から第9の寸法d5からd9は、HVNW84a、HVPW82e、HVNW84e、HVPW82f、および直列抵抗器96の幅に対応する。40

## 【0107】

一実施形態では、第1から第4の寸法d1からd4は、図6Bの保護装置100に関連して説明されるものに類似する。加えて、第5の寸法d5は、約3.5μmから約5μmの範囲内、例えば、4μmであるように選択されるサイズを有し、第6の寸法d6は、約4μmから約5μmの範囲内、例えば、4μmであるように選択されるサイズを有し、第7の寸法d7は、約3.0μmから約6.0μmの範囲内、例えば、4.0μmであるように選択されるサイズを有し、第8の寸法d8は、約3.5μmから約8μmの範囲内、例えば、5μmであるように選択されるサイズを有し、第9の寸法d9は、約1.5μm50

から約  $2 \mu m$  の範囲内、例えば、 $1.8 \mu m$  であるように選択されるサイズを有する。しかしながら、他の寸法が当業者によって容易に判定されるであろう。

#### 【0108】

一実施形態では、P-SUB81、P-EPI91、DPW93、NBL89、P+領域83a～83dおよびN+領域85a～85f、SHPW92およびSHNW94a、94b、ならびにHVPW82a～82cおよびHVNW84a～84dのピークドーピング濃度は、図5Aの保護装置80の値に類似するピークドーピング濃度を有する。加えて、P+領域83eおよび83fならびにN+領域85gは、約1ラ1020cm-3から約8ラ1020cm-3の範囲内、例えば、約2ラ1020cm-3のピークドーピング濃度を有する。加えて、HVPW82d～82fならびにHVNW84eは、約1.5ラ1016cm-3から約7.5ラ1016cm-3の範囲内、例えば、約5.0ラ1016cm-3のピークドーピング濃度を有する。ピークドーピング濃度および深度の種々の範囲が上記で説明されているが、当業者であれば、他の好適なドーピング濃度を容易に解説するであろう。

#### 【0109】

図12Bは、別の実施形態による、双方向性保護装置300の概略上面図を図示する。明確にするために、図12Bは、直列抵抗器96と活性領域より下側の（最初に第7のN+領域85a～85g、そして第2、第3、第5および第6のP+領域83b、83c、83e、83fを通る）種々のウェル領域との間の重複領域、および酸化物領域88のみを示す。図示した実施形態の対称性により、（図に示される）本装置の半分に関して以下で論議される特徴はまた、本装置の他方の半分（図示せず）にも適用可能であり得る。

#### 【0110】

図12Bの11A～11Aを通る断面図は、図12Bの直列抵抗器96が図11Aと比較してより広い水平領域に重複することを除いて、図11Aに類似する。具体的には、図12Bの実施形態は、HVPW82dを備える中心区域を包囲するリングを形成し、HVPW82eおよびHVNW84aならびにHVPW82aおよびHVNW84eの一部分に水平に重複する、直列抵抗器96を図示する。直列抵抗器96の内縁は、HVPW82a内に配置され、直列抵抗器96の外縁は、HVNW84e内に配置される。明確にするために示されていないが、直列抵抗器96の内縁は、N+領域85aとN+領域85bとの間の酸化物領域88内に配置され、直列抵抗器96の外縁は、N+領域85gとP+領域83eとの間の酸化物領域88内に配置される。

#### 【0111】

直列抵抗器96が、HVPW82aおよびHVNW84eの一部分を実質的に重複することなく、HVPW82eおよびHVNW84aの実質的に全体に水平に重複するようにリングを形成する、他の実施例が可能である。明確にするために示されていないが、この実施形態では、直列抵抗器96の内縁は、N+領域85aとN+領域85bとの間の酸化物領域88との間の境界線付近に配置することができ、直列抵抗器96の外縁は、P+領域83eと、N+領域85gとP+領域83eとの間の酸化物領域88との間の境界線付近に配置されるであろう。

#### 【0112】

直列抵抗器96が、HVPW82aおよびHVNW84eの一部分に重複することなく、HVPW82eおよびHVNW84aの一部分に水平に重複するようにリングを形成する、図11Aに示されるもの等のさらに他の実施形態が可能である。明確にするために示されていないが、この実施形態では、直列抵抗器96の内縁は、N+領域85a内に配置することができ、直列抵抗器96の外縁は、P+領域83e内に配置することができる。

#### 【0113】

直列抵抗器96と酸化物領域88との間の重複の区域が、直列抵抗器と対応するN+およびP+領域との間の接触抵抗に影響を及ぼさないため、内および外縁が酸化物領域88内に入るように直列抵抗器マスクを設計することは、直列抵抗器96の電気的統制に実質的に影響を及ぼすことなく、第1および第2の縁が酸化物領域88内のどこかに入ること

10

20

30

40

50

ができるという利点を有することができる。

【0114】

直列抵抗器の縁が種々の領域内に入るよう、直列抵抗器マスクを設計することは、当業者が選択するための設計考慮事項である。一実装では、直列抵抗器96の内および外縁が、電気的短絡を引き起こすことなく酸化物領域88内のどこかに入り得るため、上記で説明されるように、直列抵抗器96の内および外縁が酸化物領域88内に入るよう、直列抵抗器マスクを設計することは、例えば、リソグラフィの利点を提供してもよい。加えて、そのような設計はまた、直列抵抗器96（例えば、ポリシリコン）と酸化物領域88内の絶縁材料（例えば、SiO<sub>2</sub>）との間のより高いエッチング選択性により、エッチング処理における利点を提供してもよい。電気的トレードオフの観点では、設計は、基板表面と平行な半径方向での増加した長さにより、直列抵抗器96の増加した抵抗値をもたらし得る。直列抵抗器96とN+領域85aおよびP+領域83eとの間の重複の区域が、絶縁領域内で直列抵抗器96の第1および第2の縁の位置とは無関係のままであるため、直列抵抗器96と活性領域との間の接点と関連付けられる接触抵抗は、比較的不变のままであってもよい。

【0115】

別の実装では、例えば、直列抵抗器96の内および外縁が、活性領域内のどこかに入り、依然として電気的に接触し得る一方で、抵抗器96と活性領域との間にそれほどエッチング選択性がなくなり得るため、直列抵抗器96の内および外縁がN+領域85aおよびP+領域83e内に入るよう、直列抵抗器マスクを設計することは、それほど処理利点を提供しなくなり得る。電気的トレードオフの観点では、設計は、基板表面と平行な半径方向での直列抵抗器の短縮した長さにより、直列抵抗器96の低減した抵抗値を提供し得る。直列抵抗器96と活性領域との間の接点と関連付けられる接触抵抗は、直列抵抗器96とN+領域85aおよびP+領域83eとの間の減少した重複の区域により、増加し得る。

【0116】

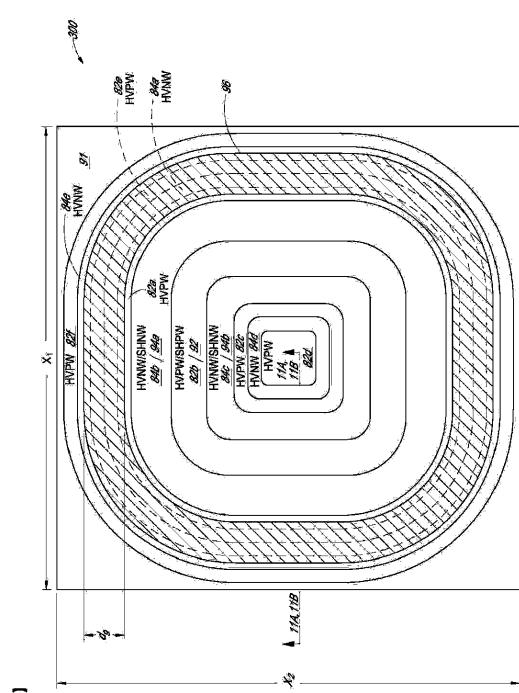

図12Cは、さらに別の実施形態による、双方向性保護装置300の概略上面図を図示する。明確にするために、図12Cは、第1から第4の抵抗器セグメント96a～96dと活性領域より下側の（最初に第7のN+領域85a～85g、そして第2、第3、第5および第6のP+領域83b、83c、83e、83fを通る）種々のウェル領域との間の重複領域、および酸化物領域88のみを示す。図示した実施形態の対称性により、（図に示される）本装置の半分に関して以下で論議される特徴はまた、本装置の他方の半分（図示せず）にも適用可能であり得る。図12Cの実施形態は、単一のリングを形成する直列抵抗器96の代わりに、実施形態が第1から第4の抵抗器セグメント96a～96dを含むことを除いて、図12Bの実施形態に類似する。第1から第4の抵抗器セグメント96a～96dのそれぞれは、第1から第4の内縁長を伴う第1から第4の内縁セグメントと、基板表面と平行な各抵抗器セグメントの接線方向に沿って延在する第1から第4の外縁を有する第1から第4の外縁セグメントとを有する、部分リングを形成する。加えて、第1から第4の抵抗器セグメント96a～96dのそれぞれは、基板表面と平行な双方向性保護装置300の各部分リングセグメントの半径方向に延在する、セグメント幅を有する。

【0117】

基板表面と平行な半径方向での各抵抗器セグメントの第1および第2の縁の終端の場所を含む、図12Bに関連して上記で論議される設計考慮事項の全てが、この実施形態で適用可能である。加えて、実施形態は、抵抗器セグメントの複合抵抗、例えば、抵抗器セグメントの数を制御することにおいて、付加的な自由度を提供してもよい。図12Cの実施形態は、第1から第4の抵抗器セグメント96a～96dを示すが、各セグメントの好適な抵抗値、および電気的に並列に配列されたセグメントからの全抵抗の好適な抵抗値をもたらすように、抵抗器セグメントの数が任意の好適な数であり得る、他の実施形態が可能である。加えて、抵抗器セグメントのそれぞれの長さは、抵抗器セグメントの複合抵抗を

制御することにおいて、別の自由度を提供してもよい。各セグメントの好適な抵抗値、および電気的に並列に配列されたセグメントからの全抵抗の好適な抵抗値をもたらすように、基板表面と平行な接線方向での第1から第4の抵抗器セグメント96a～96dの任意の好適な長さが選択されてもよい。

#### 【0118】

一実施形態では、図12A～12Cの双方向性保護装置300の設置面積は、約220μmから約170μmの範囲内、例えば、約200μmの幅×1を有し、保護装置100は、8kV IEC-61000-4-2 ESD口バスト性レベルのために、約220μmから約170μmの範囲内、例えば、約200μmの高さ×2を有する。しかしながら、他の寸法が当業者によって容易に判定されるであろう。

10

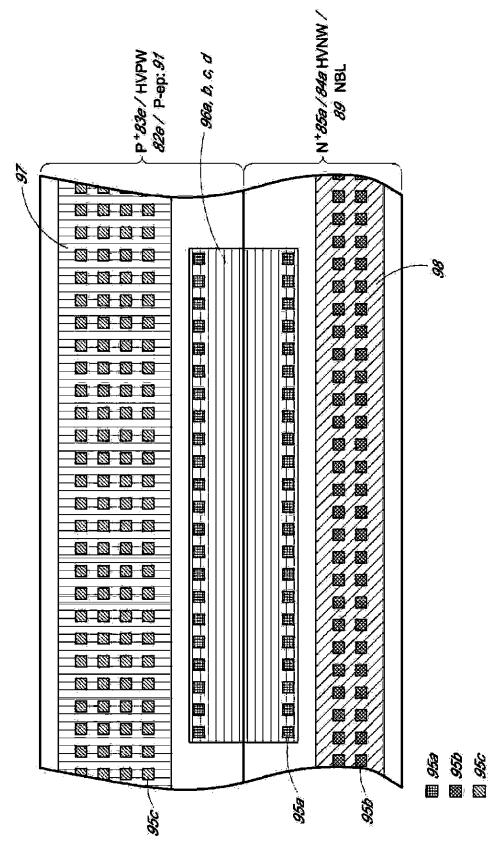

#### 【0119】

図12Dは、第1から第4の直列抵抗器セグメント96a～96dのうちのいずれかの一実施形態を示す。具体的には、実施形態は、半径方向での抵抗器セグメントの各端部が、どのようにして、それぞれ、P+領域83eおよびN+領域85aを通してHVPW82eおよびHVNW84aに接続され得るかに関する。図示した実施形態では、第1の抵抗器セグメント96aのみが明確にするために示されている。第1の抵抗器セグメント96aは、HVPWライン97とHVNWライン98との間で水平に配置される。HVPWライン97は、接点95cを介してP+領域83eに接続され、HVNWライン98は、接点95bを介してN+領域85aに接続される。図示した実施形態は、第1の抵抗器セグメント96aが（または同様に第2から第4の抵抗器セグメント96b～96dのうちのいずれか1つが）、HVPW82aおよびHVNW84eの一部分に重複することなく、P+領域83e/HVPW82eおよびN+領域85a/HVNW84aの一部分に水平に重複するように、部分リングを形成する場合に対応する。抵抗器セグメント96aは、N+領域85a/HVNW84aにより近い側面上で第1の内縁セグメントと、P+領域83e/HVPW82eにより近い側面上で第1の外縁セグメントとを有する。第1の抵抗器セグメント96aはさらに、第1の抵抗器セグメント96aがN+領域85a/HVNW84aに水平に重複する内側重複領域と、第1の抵抗器セグメント96aがP+領域83e/HVPW82eに水平に重複する外側重複領域とを含む。内側および外側重複領域内で水平に配置され、第1の抵抗器セグメント96aとN+領域85aおよびP+領域83eとの間で垂直に配置されるのは、接点95aを介した複数の直列抵抗器である。接点95aを介した直列抵抗器は、例えば、図10の第12の抵抗器を提供するように、P+領域83e/HVPW82eおよびN+領域85a/HVNW84aを電気的に接続する。

20

#### 【0120】

図12Dの実施形態は、P+領域83eおよびN+領域85aを通して、図12Cの第1から第4の直列抵抗器セグメント96a～96dをHVPW82eおよびHVNW84aに接続するための接続方法を図示するが、他の実施形態も可能である。例えば、類似接続方法が、図12Bの直列抵抗器96、または上記で論議される抵抗器リングおよびセグメント構成の他の配列のうちのいずれかを接続するために使用されてもよい。

30

#### 【0121】

種々の実施形態下で採用され得る、接点95aを介した直列抵抗器の単位面積あたりの密度および横寸法は、状況に依存し、当業者による設計選択によって左右される。例えば、当業者は、直列抵抗器96の抵抗値または第1から第4の直列抵抗器セグメント96a～96dの抵抗値を標的にするために、接点95aを介した直列抵抗器の任意の好適な数の密度および任意の好適な寸法を使用してもよい。

40

#### 【0122】

図13Aおよび13Bは、関連回路要素とともに注釈が付けられた、それぞれ、図11Bおよび11Aの双方向性保護回路300に類似する双方向性保護回路310の代替実施形態を示す。図13Aの双方向性保護回路310は、図13Aでは、第1および第2のゲート87aおよび87bが、それぞれ、第3のP+領域83cと第4のN+領域85dと

50

の間、および第3のN+領域85cと第2のP+領域83bとの間に配置される、酸化物領域88と置換されていることを除いて、図13Bに類似する。2つの実施形態の間の第1および第2のゲート87aおよび87bに関する動作の違いが、図11Aおよび11Bを参照して上記で論議される。

【0123】

第1のパッド61および第2のパッド62に対する接続は、図5Bの対応する特徴に類似する。加えて、NPN双向性バイポーラトランジスタ63、第1のPNPバイポーラトランジスタ64、第2のPNPバイポーラトランジスタ65、第1から第3の抵抗器71～73、第5の抵抗器75、および第6の抵抗器76の種々の物理的領域に対する電気的構成は、図5Bの対応する特徴に類似する。結果として、NPN双向性バイポーラトランジスタ63、第1のPNPバイポーラトランジスタ64、および第2のPNPバイポーラトランジスタ65を含む、バイポーラPNPNPN素子アセンブリの素子応答は、図5Bに関連して上記で説明されるものに類似する。加えて、第1および第2の寄生PNPN素子アセンブリ220および230の素子応答は、図10に関連して上記で説明されるものに類似する。

【0124】

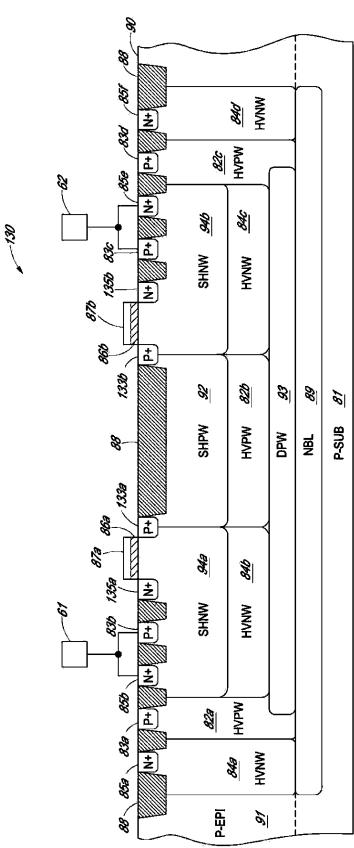

図5Bとは対照的に、図13Aおよび13Bの実施形態では、NBL89ならびに第1および第4のHVNW84a、84dから形成されるn型タブは、浮動していない。代わりに、n型タブは、HVPW82f、HVNW84e、およびHVNW82eより下側に配置されたP-EPI91の抵抗から形成された第9の抵抗器102に直列に接続された、直列抵抗器96の抵抗から形成された第12の抵抗器108を通して、送受信機回路1のp-基板(VSSへのケルビン接続)に電気的に接続される。図5Bと同様に、DPW93ならびに第1および第3のHVPW82a、82cから形成されるp型タブは、電気的に浮動することができる。

【0125】

加えて、図13Aの実施形態は、寄生PNPバイポーラトランジスタ222、第1の寄生NPNバイポーラトランジスタ66、第7の抵抗器77、第9の抵抗器102、および第12の抵抗器108を含む、図10で説明される第1の寄生PNPN素子アセンブリ220に類似する第1の寄生PNPN素子アセンブリを示す。寄生PNPバイポーラトランジスタ222は、P-EPI91から形成されるエミッタと、NBL89から形成される基部と、DPW93から形成されるコレクタとを含む。寄生PNPバイポーラトランジスタ222のエミッタは、送受信機回路1のp-基板(VSSへのケルビン接続)に、およびP-EPI91内の抵抗から形成される第9の抵抗器102に電気的に接続される。寄生PNPバイポーラトランジスタ222はさらに、第9の抵抗器102、および第9の抵抗器102と電気的に直列に接続された図11Aおよび11Bの抵抗器96の抵抗から形成される第12の抵抗器108を通して、エミッタに接続される基部を含む。寄生PNPバイポーラトランジスタ222の基部はさらに、第7の抵抗器77を通して第1の寄生NPNバイポーラトランジスタ66のコレクタに接続される。第1の寄生NPNバイポーラトランジスタ66は、SHNW94a/HVNW84bから形成されるエミッタと、HVPW82aから形成される基部と、NBL89から形成されるコレクタとを含む。第7の抵抗器77は、HVNW84a内の抵抗から形成される。寄生PNPバイポーラトランジスタ222はさらに、第1の寄生NPNバイポーラトランジスタ66の基部に接続されるコレクタを含む。第1の寄生NPNバイポーラトランジスタ66は、SHNW94aの抵抗から形成される第3の抵抗器73に電気的に接続されるエミッタと、寄生PNPバイポーラトランジスタ222のコレクタに電気的に接続される基部とを含む。第1の寄生NPNバイポーラトランジスタ66はさらに、第7の抵抗器77を通して寄生バイポーラPNPトランジスタ222の基部に電気的に接続されるコレクタを含む。

【0126】

図13Aはさらに、寄生PNPバイポーラトランジスタ222、第2の寄生NPNバイポーラトランジスタ232、第5の抵抗器75、第7の抵抗器77、第9の抵抗器102

10

20

30

40

50

、第10の抵抗器104、および第12の抵抗器108を含む、図10で説明される第2の寄生PNPN素子アセンブリ230に類似する第2の寄生PNPN素子アセンブリを示す。寄生PNPバイポーラトランジスタ222は、P-EPI91から形成されるエミッタと、NBL89から形成される基部と、DPW93から形成されるコレクタとを含む。寄生PNPバイポーラトランジスタ222は、p-基板(VSSへのケルビン接続)に、およびP-EPI91内の抵抗から形成される第9の抵抗器102に電気的に接続される、エミッタを含む。寄生PNPバイポーラトランジスタ222はさらに、第9の抵抗器102、および第9の抵抗器102と電気的に直列に接続された図11Aおよび11Bの抵抗器96の抵抗から形成される第12の抵抗器108を通して、エミッタに接続される基部を含む。第1の寄生PNPバイポーラトランジスタ220の基部はさらに、直列に接続された第7の抵抗器77および第10の抵抗器104を通して第2の寄生PNPバイポーラトランジスタ232のコレクタに接続される。第2の寄生PNPバイポーラトランジスタ232は、SHNW94b/HVNW84cから形成されるエミッタと、DPW93から形成される基部と、NBL89から形成されるコレクタとを含む。第7の抵抗器77は、HVNW84aの抵抗から形成され、第10の抵抗器104は、NBL89の中の抵抗から形成される。寄生PNPバイポーラトランジスタ222はさらに、DPW93の中の抵抗から形成される第5の抵抗器75を通して、第2の寄生PNPバイポーラトランジスタ232は、SHNW94b/HVNW84cの中の抵抗から形成される第11の抵抗器106に接続されるエミッタと、第5の抵抗器75を通して寄生PNPバイポーラトランジスタ222のコレクタに電気的に接続される基部とを含む。第2の寄生PNPバイポーラトランジスタ232はさらに、第10の抵抗器104および第7の抵抗器77を通して、寄生PNPバイポーラトランジスタ222の基部に電気的に接続されるコレクタを含む。

10

20

#### 【0127】

図13Cは、さらに別の代替実施形態を示す。図13Cの双方向性保護装置310の実施形態は、HVNW84bおよびHVNW84cが、それぞれ、低濃度ドープのp-ウェル領域LDPW160aおよびLDPW160bと置換されてもよいことを除いて、図13Aに示されるものに類似する。p型領域160は、P-EPI91のドーピング濃度等の背景ドーピング濃度に類似するドーピング濃度を有することができる。LD PW160aおよびLD PW160bは、図9Aおよび9Cで図示される素子挙動への類似微調整影響を提供してもよい。具体的には、LD PW160aおよびLD PW160bを含むことにより、図13Aの第1および第2のPNPバイポーラトランジスタ64および65の基本的抵抗を増加させることができる。結果として、過渡応答時間が向上してもよく、双方向性PNPNP素子アセンブリ210のトリガ電圧もまた、第1および第2のPNPバイポーラトランジスタ64および65の増加した利得により減少してもよい。双方向性PNPNP素子アセンブリ210のトリガ電圧を非対称的に変化させるように、領域LD PW160aおよびLD PW160bが異なるレベルまでドープされる、他の実施形態が可能である。

30

#### 【0128】

上記で論議されるように、寄生PNPバイポーラトランジスタ222がBVCE(R(エミッタ・基部が抵抗器によって接続されている絶縁破壊)であるように構成される場合に、第9および第12の抵抗器102および108の複合抵抗の値を中間値にさせることが望ましくあり得る。一実施形態では、第9の抵抗器102の値は、約200ミリオーム(mオーム)から約5オームの範囲内、例えば、約500mオームの値を有するように設計されている。そのような値は、例えば、P-EPI91の中の活性化ドーパントのレベルを制御することによって得られてもよい。別の実施形態では、第12の抵抗器108の値は、約200mオームから20オームの範囲内、例えば、2オームの値を有するように設計されてもよい。そのような値は、図12Bの直列抵抗器96の中、または図12Cの直列抵抗器セグメント96a～96dの中の活性化ドーパントのレベルを制御することによって得られてもよい。

40

50

## 【0129】

図14Aは、高インピーダンス状態（すなわち、トリガ前）の図10の双方向性保護回路200に類似する、双方向性保護回路の一実施形態の第1および第2のパッド61および62にわたって行われた電流・電圧（IV）掃引を図示する。x軸は、ボルト（V）単位で第1および第2のパッド61および62の間の電圧差を表し、y軸は、アンペア（A）単位で測定された電流の対応する絶対値を表す。図示した実施形態では、絶対値での電流は、第1および第2のパッド61および62の間の正および負の5Vで約2ラ10-11Aを超えない。加えて、最大でおよそ正および負の10Vでは、図10で説明されるSCR素子ペアのうちのいずれも、それらのトリガ電圧を超えていない。具体的には、+/-10Vでは、第1および第2のパッド61および62にわたる電圧は、図2で概略的に示されるように起こり得る、電流スナップバック事象の不足によって示されるように、NPN双方向性バイポーラトランジスタ63と、第1のPNPバイポーラトランジスタ64と、第2のPNPバイポーラトランジスタ65とを含む、バイポーラPNPNNP素子アセンブリ210の+/-VTRを超えていない。加えて、第1および第2のパッド61および62にわたる+/-10Vでは、寄生PNPバイポーラトランジスタ222と、第1の寄生NPNバイポーラトランジスタ66とを含む、第1の寄生PNPNN素子アセンブリ220のトリガ電圧を超えていない。同様に、1および第2のパッド61および62にわたる+/-10Vでは、寄生PNPバイポーラトランジスタ222と、第2の寄生NPNバイポーラトランジスタ232とを含む、第2の寄生PNPNN素子アセンブリ230のトリガ電圧を超えていない。10 20

## 【0130】

図14Bおよび14Cは、図10の双方向性保護回路200に類似する、双方向性保護回路の一実施形態の第1および第2のパッド61および62にわたって行われた電流・電圧（IV）掃引を図示する。これらの実施形態では、掃引は、トリガ事象を通して低い正のインピーダンス状態（すなわち、トリガ後）に行われている。図14Bおよび図14CのX軸は、ボルト（V）単位で第1および第2のパッド61および62の間の電圧差を表す。図14Bおよび図14CのY軸は、それぞれ、正および負のアンペア（A）単位で測定される電流の値を表す。図示した実施形態では、図14Bの約+9Vで、または図14Cの約-9Vでは、第1および第2のパッド61および62にわたる絶対電圧は、電流スナップバック事象によって示されるように、NPN双方向性バイポーラトランジスタ63と、第1のPNPバイポーラトランジスタ64と、第2のPNPバイポーラトランジスタ65とを含む、バイポーラPNPNNP素子アセンブリ210の+/-VTRを超えていない。トリガした後、双方向性保護回路200は、低インピーダンス状態になり、PNPNNP素子アセンブリ210にわたる絶対電圧は、+/-VHに戻る。絶対値での電流は後に、+/-VHを超える第1および第2のパッド61および62にわたる絶対値での電圧で、再び増加する。図示した実施例では、本素子は、顕著な素子劣化を伴わずに+/-20Aに耐える。加えて、二次スナップバック事象の欠如によって示されるように、高インピーダンス状態から低インピーダンス状態へ、後にトリガした後の第1および第2のパッド61および62にわたる約+/-9Vへ、バイポーラPNPNNP素子アセンブリ210の遷移の全体を通して、第1および第2の寄生PNPNN素子アセンブリ220および230のトリガ電圧を超えていない。30 40

## 【0131】

図15は、図13Aの双方向性保護装置310に類似する双方向性保護装置の一実施形態の模擬電流等高線図を示す。この実施形態では、図13Aのように、P+領域83eおよびN+領域85aは、第12の抵抗器108を通して電気的に接続される。N+領域85fは、電気的に浮動しており、N+領域85gは、5Vに接続される。等高線図は、第1のパッド61およびP+領域83fが両方とも接地電位で基板に接続されている間に、負の電圧掃引が第2のパッド62上で行われるときの空間電流密度の断面図を表す。図10に関連して論議されるように、実施形態では、HVPW82fは、ケルビン接続234を通して、接地電位で送受信機の基板に接続されてもよく、第1のパッド61は、高電流50

レールを通して、接地電位で送受信機の基板に接続されてもよい。等高線図は、NPN双向性バイポーラトランジスタ63と、第1のPNPバイポーラトランジスタ64と、第2のPNPバイポーラトランジスタ65とを含む、PNPNP素子アセンブリに対応する、表面領域付近の第1および第2のパッド61および62の間で0.1にて最高レベルの電流電位を示す。対照的に、等高線図は、接地電位で基板に接続される第2のパッド62とP+領域83fとの間の10-9未満の電流電位を示す。それは、電流伝導がパッド61および62の間で大幅により大きく優勢であることを示す。

#### 【0132】

##### (用途)

上記の保護方式を採用するデバイスは、種々の電子デバイスおよびインターフェース用途に実装することができる。電子デバイスの実施例は、消費者電子製品、消費者電子製品の部品、電子試験機器、高ロバスト性の工業および自動車用途等を含むことができるが、それらに限定されない。電子デバイスの実施例はまた、光学ネットワークまたは他の通信ネットワークの回路を含むこともできる。消費者電子製品は、携帯電話、電話、テレビ、コンピュータモニタ、コンピュータ、手持ち式コンピュータ、携帯情報端末(PDA)、自動車、自動車エンジン管理コントローラ、変速機コントローラ、シートベルトコントローラ、アンチロックブレーキシステムコントローラ、カムコーダ、カメラ、デジタルカメラ、携帯用メモリチップ、洗濯機、乾燥機、洗濯/乾燥機、コピー機、ファクシミリ機、スキャナ、多機能周辺デバイス等を含むことができるが、それらに限定されない。さらに、電子デバイスは、工業、医療、および自動車用途のためのものを含む、未完成製品を含むことができる。

10

#### 【0133】