(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6134537号

(P6134537)

(45) 発行日 平成29年5月24日(2017.5.24)

(24) 登録日 平成29年4月28日(2017.4.28)

|              |           |                 |

|--------------|-----------|-----------------|

| (51) Int.Cl. | F 1       |                 |

| HO1L 29/786  | (2006.01) | HO1L 29/78 616V |

| HO1L 21/336  | (2006.01) | HO1L 29/78 618B |

| HO1L 27/115  | (2017.01) | HO1L 29/78 619A |

| HO1L 21/8242 | (2006.01) | HO1L 29/78 616L |

| HO1L 27/108  | (2006.01) | HO1L 27/10 434  |

請求項の数 5 (全 39 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2013-38115 (P2013-38115)    | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成25年2月28日(2013.2.28)         | (74) 代理人  | 100119301<br>弁理士 蟹田 昌之                         |

| (65) 公開番号    | 特開2013-211543 (P2013-211543A) | (72) 発明者  | 大野 普司<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成25年10月10日(2013.10.10)       | (72) 発明者  | 渡邊 裕一<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日        | 平成27年12月24日(2015.12.24)       | (72) 発明者  | 楠本 直人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2012-40837 (P2012-40837)    |           |                                                |

| (32) 優先日     | 平成24年2月28日(2012.2.28)         |           |                                                |

| (33) 優先権主張国  | 日本国(JP)                       |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

ソース領域、ドレイン領域、及びチャネル形成領域を有する酸化物半導体層と、

前記酸化物半導体層上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記チャネル形成領域と重なる領域を有するゲート電極と、

前記ソース領域と接する領域を有するソース電極と、

前記ドレイン領域と接する領域を有するドレイン電極と、を有し、

前記ソース領域及び前記ドレイン領域は、前記チャネル形成領域よりも酸素濃度が高い

領域を有し、

前記ソース領域または前記ドレイン領域から前記チャネル形成領域に対し、常温において酸素が拡散されることを特徴とする半導体装置。

## 【請求項2】

ソース領域、ドレイン領域、及びチャネル形成領域を有する酸化物半導体層と、

前記酸化物半導体層上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記チャネル形成領域と重なる領域を有するゲート電極と、

前記ソース領域と接する領域を有するソース電極と、

前記ドレイン領域と接する領域を有するドレイン電極と、を有し、

前記ソース領域及び前記ドレイン領域は、前記チャネル形成領域よりも酸素濃度が高い

領域を有し、

前記チャネル形成領域は、前記酸化物半導体層の表面の法線ベクトルと平行な方向に c

10

20

軸が配向した結晶を含み、

前記ソース領域または前記ドレイン領域から前記チャネル形成領域に対し、常温において酸素が拡散されることを特徴とする半導体装置。

**【請求項 3】**

請求項 1 または請求項 2 において、

前記ゲート絶縁膜及び前記ゲート電極上に設けられた、酸化アルミニウムを含む絶縁膜を有することを特徴とする半導体装置。

**【請求項 4】**

前記チャネル形成領域下に前記チャネル形成領域に接する下地絶縁膜を有し、

前記下地絶縁膜は酸素を含む絶縁膜からなることを特徴とする請求項 1 から 3 のいずれか 1 項に記載の半導体装置。

10

**【請求項 5】**

前記ソース領域または前記ドレイン領域に不純物（酸素を除く。）が添加されていることを特徴とする請求項 1 から 4 のいずれか 1 項に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置、およびその作製方法に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

20

**【背景技術】**

**【0003】**

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（薄膜トランジスタ（TFT）ともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

**【0004】**

例えば、トランジスタの活性層として、インジウム（In）、ガリウム（Ga）、および亜鉛（Zn）を含む非晶質酸化物半導体を用いたトランジスタが開示されている（特許文献 1 参照）。

30

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献 1】特開 2006 - 165528 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

酸化物半導体における酸素欠損や、不純物として含まれる水素はドナーとなることが知られており、トランジスタのチャネル形成領域に酸化物半導体を用いる場合は、酸素欠損、水素、および水分等の極力少ない酸化物半導体層を用いることが好ましい。しかしながら、酸化物半導体層や該酸化物半導体層に接する絶縁膜などの脱水、脱水素化処理として行う熱処理では、酸化物半導体層から酸素も同時に脱離してしまう。

40

**【0007】**

酸化物半導体層からの酸素脱離はトランジスタの電気特性変動の要因となるため、酸化物半導体層から脱離した酸素を補う必要がある。そのため、酸化物半導体層への酸素供給能力の高い方法の開発が望まれている。

**【0008】**

したがって、本発明の一態様は、トランジスタのチャネル形成領域への酸素供給能力が高

50

く、電気特性の優れたトランジスタを提供することを目的の一つとする。また、該トランジスタの作製方法を提供することを目的の一つとする。

【課題を解決するための手段】

【0009】

本明細書に開示する本発明の一態様は、ソース領域およびドレイン領域の酸素濃度が、チャネル形成領域よりも高いトランジスタ、およびその作製方法に関する。

【0010】

本明細書に開示する本発明の一態様は、絶縁表面上に形成された、ソース領域、ドレイン領域、およびチャネル形成領域を有する酸化物半導体層と、酸化物半導体層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、チャネル形成領域と重畳するゲート電極と、ソース領域と接するソース電極と、ドレイン領域と接するドレイン電極と、を有し、ソース領域およびドレイン領域は、チャネル形成領域よりも酸素濃度が高い部位を有することを特徴とする半導体装置である。10

【0011】

上記酸化物半導体層において、チャネル形成領域は、c軸に配向した結晶を含み、ソース領域およびドレイン領域における、チャネル形成領域よりも酸素濃度が高い部位は、非晶質であることが好ましい。

【0012】

また、ソース領域およびドレイン領域における、チャネル形成領域よりも酸素濃度が高い部位には、酸化物半導体層の導電率を高める不純物が添加されていることが好ましい。20

【0013】

また、ゲート電極、ソース電極、およびドレイン電極の少なくとも一つは、上記酸化物半導体層とは異なる禁制帯幅を持つ半導体層を有する半導体装置と電気的に接続されていてもよい。

【0014】

また、ゲート絶縁膜上およびゲート電極上には、酸化アルミニウムを含む絶縁膜が形成されていることが好ましい。

【0015】

また、本明細書に開示する本発明の他の一態様は、絶縁表面を有する基板を準備する工程と、絶縁表面上に酸化物半導体層を形成する工程と、酸化物半導体層上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に酸化物半導体層と重畳するようにゲート電極を形成する工程と、酸化物半導体層において、ゲート電極と重畳しない領域に酸素を添加する工程と、酸化物半導体層において、ゲート電極と重畳しない領域に不純物を添加し、ソース領域、ドレイン領域、およびチャネル形成領域を形成する工程と、ゲート絶縁膜、およびゲート電極上に絶縁膜を形成する工程と、酸化物半導体層を加熱処理する工程と、ソース領域と接するソース電極、およびドレイン領域と接するドレイン電極を形成する工程と、を上記順序で行うことを特徴とする半導体装置の作製方法である。30

【0016】

また、本明細書に開示する本発明の他の一態様は、絶縁表面を有する基板を準備する工程と、絶縁表面上に酸化物半導体層を形成する工程と、酸化物半導体層と接するソース電極およびドレイン電極を形成する工程と、酸化物半導体層、ソース電極、およびドレイン電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に酸化物半導体層と重畳するようにゲート電極を形成する工程と、酸化物半導体層において、ゲート電極、ソース電極、およびドレイン電極と重畳しない領域に酸素を添加する工程と、酸化物半導体層において、ゲート電極、ソース電極、およびドレイン電極と重畳しない領域に不純物を添加し、ソース領域、ドレイン領域、およびチャネル形成領域を形成する工程と、ゲート絶縁膜、およびゲート電極上に絶縁膜を形成する工程と、酸化物半導体層を加熱処理する工程と、を上記順序で行うことを特徴とする半導体装置の作製方法である。40

【0017】

なお、上記二つの半導体装置の作製方法において、酸化物半導体層への不純物の添加は、50

酸化物半導体層への酸素の添加前、絶縁膜の形成後、または、酸化物半導体層の加熱処理後であってもよい。

**【0018】**

また、本明細書に開示する本発明の他の一態様は、絶縁表面を有する基板を準備する工程と、絶縁表面上にソース電極およびドレイン電極を形成する工程と、ソース電極およびドレイン電極と接する酸化物半導体層を形成する工程と、ソース電極、ドレイン電極、および酸化物半導体層上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にソース電極、ドレイン電極、および酸化物半導体層のそれぞれの一部と重畳するゲート電極を形成する工程と、酸化物半導体層において、ゲート電極と重畳しない領域に酸素を添加する工程と、ゲート絶縁膜、およびゲート電極上に絶縁膜を形成する工程と、酸化物半導体層を加熱処理する工程と、を有することを特徴とする半導体装置の作製方法である。 10

**【0019】**

上記半導体装置の作製方法において、絶縁膜は、酸化アルミニウムを含む絶縁膜であることが好ましい。

**【発明の効果】**

**【0020】**

本発明の一態様を用いることにより、チャネル形成領域への酸素供給能力が高く、電気特性の優れたトランジスタを提供することができる。

**【図面の簡単な説明】**

**【0021】**

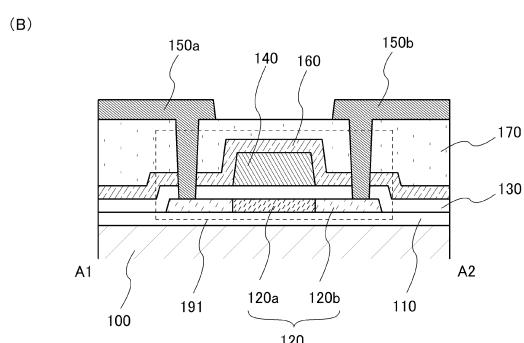

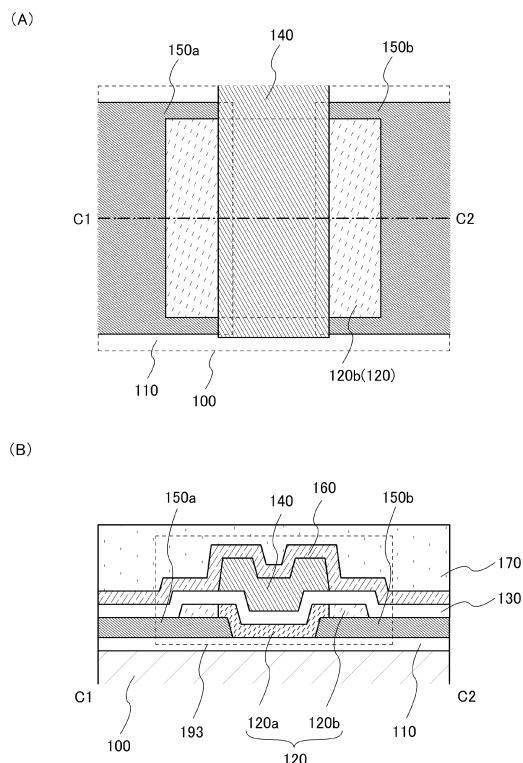

【図1】本発明の一態様の半導体装置を示す上面図および断面図。

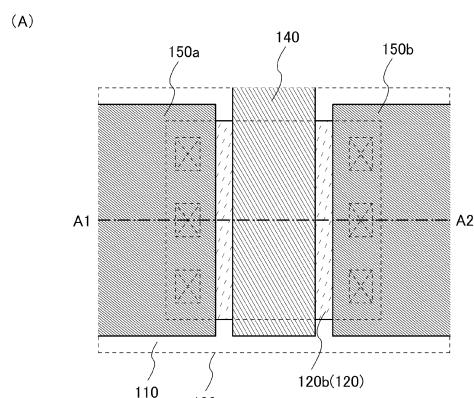

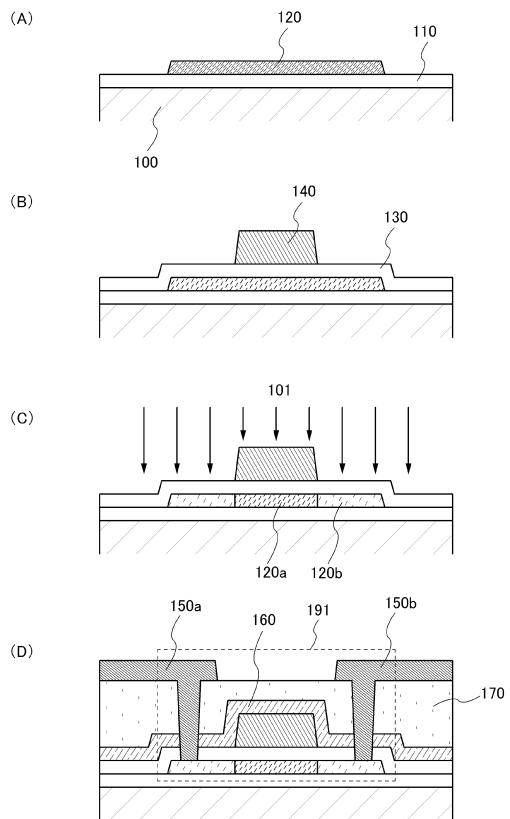

【図2】本発明の一態様の半導体装置を示す上面図および断面図。

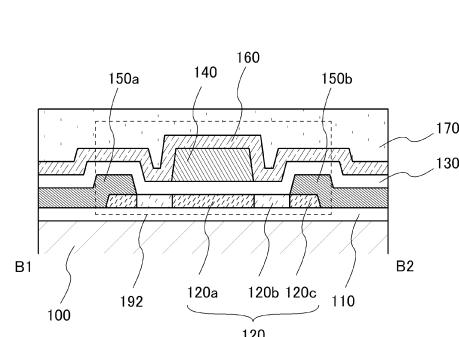

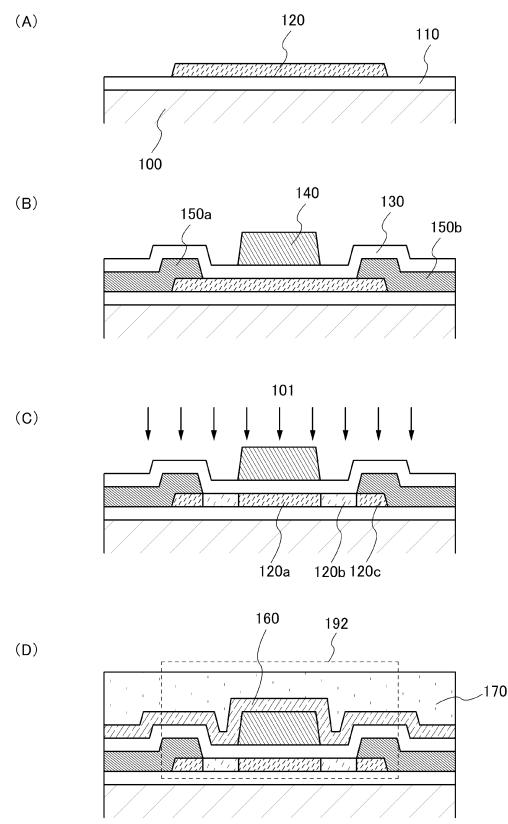

【図3】本発明の一態様の半導体装置を示す上面図および断面図。

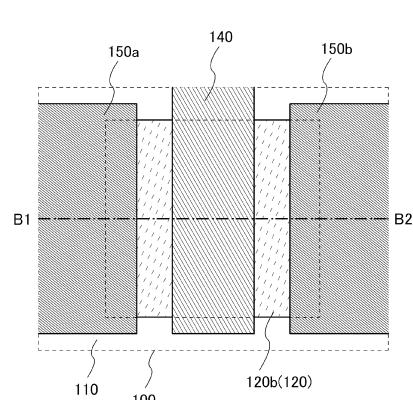

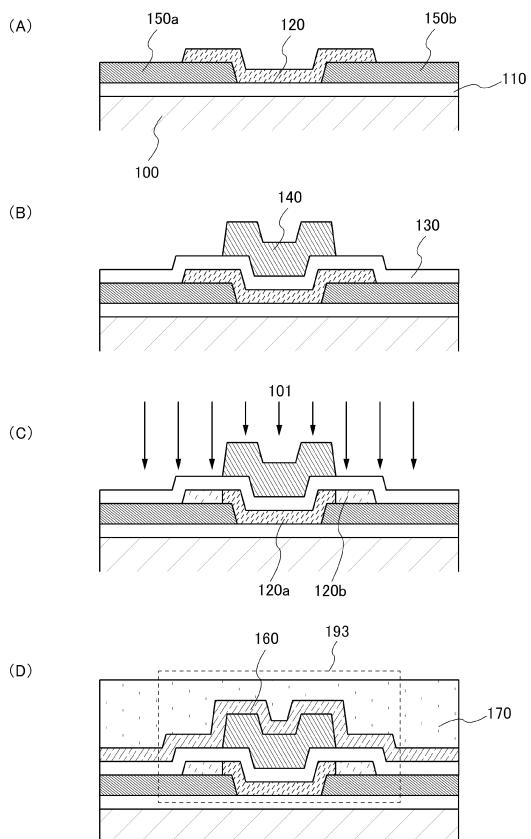

【図4】本発明の一態様の半導体装置の作製方法を説明する図。

【図5】本発明の一態様の半導体装置の作製方法を説明する図。

【図6】本発明の一態様の半導体装置の作製方法を説明する図。

【図7】半導体装置の一態様を示す断面図および回路図。

【図8】半導体装置の一態様を示す回路図および斜視図。

【図9】CPUの構成例を示すブロック図およびその一部の回路の構成例を示す図。

【図10】電子機器を示す図。

30

【図11】電子機器を示す図。

【図12】電子機器を示す図。

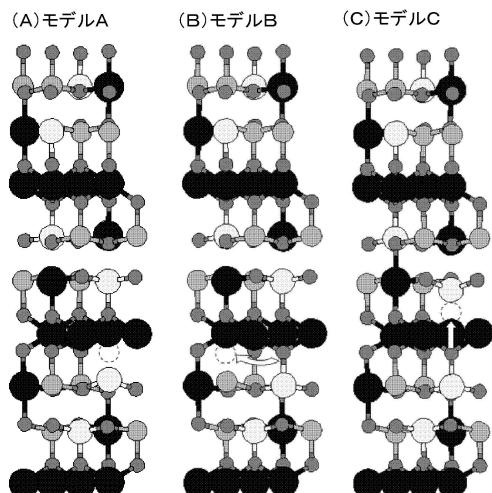

【図13】過剰酸素の移動の計算に用いたモデル図。

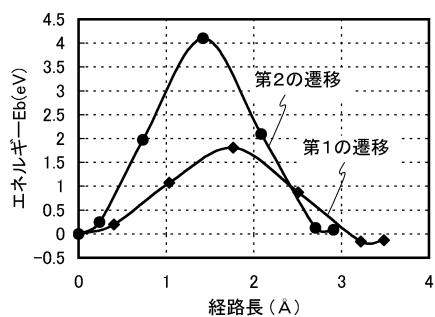

【図14】図13のモデル図の計算結果。

【図15】酸素欠損の移動の計算に用いたモデル図。

【図16】図15のモデル図の計算結果。

**【発明を実施するための形態】**

**【0022】**

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。 40

**【0023】**

(実施の形態1)

本実施の形態では、本発明の一態様における半導体装置、およびその作製方法を説明する。

**【0024】**

図1(A)は、本発明の一態様におけるトランジスタの上面図であり、図1(B)は、図 50

1 ( A ) に示す線分 A 1 - A 2 における断面図である。なお、図 1 ( A ) では明瞭化のため、一部の構成要素を省いて図示してある。

#### 【 0 0 2 5 】

図 1 ( A )、( B ) に示すトランジスタ 191 は、基板 100 上に形成された下地絶縁膜 110、該下地絶縁膜上に形成された酸化物半導体層 120、該酸化物半導体層上に形成されたゲート絶縁膜 130、該ゲート絶縁膜上に形成されたゲート電極 140、該ゲート絶縁膜および該ゲート電極上に形成された保護膜 160、該保護膜上に形成された平坦化膜 170、該保護膜および該平坦化膜に形成されたコンタクトホールを通じて該酸化物半導体層と接するソース電極 150a、ドレイン電極 150b を有する。なお、保護膜 160 および平坦化膜 170 は必要に応じて設ければよい。

10

#### 【 0 0 2 6 】

また、図 1 ( A )、( B ) は本発明の一態様に用いることのできる自己整合型のトップゲート型トランジスタの一例を示すものであり、各構成要素の種類、形状、および位置関係を限定するものではない。

#### 【 0 0 2 7 】

また、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合には入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

#### 【 0 0 2 8 】

基板 100 は、単なる支持材料に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ 191 のゲート電極 140、ソース電極 150a、およびドレイン電極 150b の少なくとも一つは、他のデバイスと電気的に接続されていてもよい。

20

#### 【 0 0 2 9 】

下地絶縁膜 110 は、基板 100 からの不純物の拡散を防止する役割を有するほか、酸化物半導体層 120 に酸素を供給する役割を担うことができるため、酸素を含む絶縁膜であることが好ましい。また、上述のように基板 100 が他のデバイスが形成された基板である場合、下地絶縁膜 110 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように CMP ( C hemical M echanical P olishing ) 法等で平坦化処理を行うことが好ましい。

30

#### 【 0 0 3 0 】

酸化物半導体層 120 は島状に加工されており、ゲート絶縁膜 130 を介してゲート電極 140 と重畠している。酸化物半導体層 120 において、ゲート電極 140 と重畠した領域はチャネル形成領域 120a となり、ゲート電極 140 と重畠しない領域はソース領域またはドレイン領域 120b となる。

#### 【 0 0 3 1 】

チャネル形成領域 120a は、c 軸に配向した結晶を含む酸化物半導体で形成する。ここで、c 軸に配向した結晶とは、結晶軸の c 軸が膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃った結晶のことをいう。

40

#### 【 0 0 3 2 】

それに対し、ソース領域またはドレイン領域 120b は非晶質とする。非晶質であるソース領域またはドレイン領域 120b はゲッタリングサイトとなる欠陥等を多く含むため、チャネル形成領域 120a、下地絶縁膜 110、およびゲート絶縁膜 130 に含まれる水素や水分などをゲッタリングすることができる。また、非晶質であるソース領域またはドレイン領域 120b では、トランジスタの製造工程や動作環境においてチャネル形成領域 120a に混入しようとする水素や水分などをゲッタリングすることもできる。

#### 【 0 0 3 3 】

ここで、ソース領域またはドレイン領域 120b は、チャネル形成領域 120a よりも多くの酸素を含んで形成されている。このソース領域またはドレイン領域 120b に含まれ

50

る過剰の酸素をチャネル形成領域 120a に拡散させることで、トランジスタの作製工程における加熱工程などで発生したチャネル形成領域 120a の酸素欠損などを補填することができる。また、トランジスタの長期動作や動作環境に起因して発生するチャネル形成領域 120a の酸素欠損なども補填することもできる。

#### 【0034】

c 軸に配向した結晶を含む酸化物半導体で形成されたチャネル形成領域 120a は、横方向 (c 軸とは略垂直方向) に酸素原子が移動しやすい特徴を有するため、ソース領域またはドレイン領域 120b の方向から効率よくチャネル形成領域 120a に酸素を拡散させることができる。なお、チャネル形成領域 120a は、化学量論組成よりも多くの酸素を含む、酸素過剰な状態であることが好ましい。

10

#### 【0035】

また、ソース領域またはドレイン領域 120b には、酸化物半導体層の導電率を高める不純物が添加されていることが好ましい。該不純物には、例えは、リン (P)、砒素 (As)、アンチモン (Sb)、ホウ素 (B)、アルミニウム (Al)、窒素 (N)、アルゴン (Ar)、ヘリウム (He)、ネオン (Ne)、インジウム (In)、フッ素 (F)、塩素 (Cl)、チタン (Ti)、亜鉛 (Zn)、炭素 (C) のいずれかから選択される一つ以上を用いることができる。

#### 【0036】

ゲート絶縁膜 130 およびゲート電極 140 上には、保護膜 160 として酸化アルミニウムを含む絶縁膜が形成されていることが好ましい。酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果 (ブロック効果) が高い。したがって、酸化アルミニウム膜は、作製工程中および作製後において、トランジスタの電気特性の変動要因となる水素、水分などの不純物の酸化物半導体層 120 への混入、および酸化物半導体層 120 を構成する主成分材料である酸素の酸化物半導体層からの放出を防止する保護膜として用いることに適している。なお、ゲート絶縁膜 130 およびゲート電極 140 と、保護膜 160 との間に他の絶縁膜が形成されていてもよい。

20

#### 【0037】

なお、本発明の一態様に用いることのできるトランジスタは、図 2 (A)、(B) に示す構造であってもよい。

#### 【0038】

30

図 2 (A) は、トランジスタの上面図であり、図 2 (B) は、図 2 (A) に示す線分 B1 - B2 における断面図である。なお、図 2 (A) では明瞭化のため、一部の構成要素を省いて図示してある。

#### 【0039】

図 2 (A)、(B) に示すトランジスタ 192 は、基板 100 上に形成された下地絶縁膜 110、該下地絶縁膜上に形成された酸化物半導体層 120、該酸化物半導体層に接して形成されたソース電極 150a およびドレイン電極 150b、該酸化物半導体層、該ソース電極および該ドレイン電極上に形成されたゲート絶縁膜 130、該ゲート絶縁膜上に形成されたゲート電極 140、該ゲート絶縁膜および該ゲート電極上に形成された保護膜 160、該保護膜上に形成された平坦化膜 170 を有する。なお、保護膜 160 および平坦化膜 170 は必要に応じて設ければよい。

40

#### 【0040】

トランジスタ 192 は、ソース電極 150a およびドレイン電極 150b の位置がトランジスタ 191 とは異なる。またそれに伴い、酸化物半導体層 120 にはチャネル形成領域 120a、ソース領域またはドレイン領域 120b に加え、領域 120c が形成される。

#### 【0041】

ソース領域またはドレイン領域 120b は、ゲート電極 140 を形成後に酸素や、導電率を高める不純物をイオン注入法等で添加することにより形成する。トランジスタ 191 では、ゲート電極 140 がマスクとなり、酸化物半導体層 120 のゲート電極 140 と重畠しない領域には全て酸素や、導電率を高める不純物が添加され、ソース領域またはドレイ

50

ン領域 120b が形成される。一方、トランジスタ 192 では、ソース電極 150a およびドレイン電極 150b もマスクとなるため、酸化物半導体層 120 には領域 120c が形成される。

#### 【0042】

領域 120c は、チャネル形成領域 120a と同様に導電率を高める不純物が添加されない領域であるが、ソース電極 150a およびドレイン電極 150b である金属材料が接する領域であり、その抵抗は無視することができる。したがって、領域 120c はソース領域またはドレイン領域の一部であるということができる。

#### 【0043】

また、本発明の一態様に用いることのできるトランジスタは、図 3 (A)、(B) に示す構造であってもよい。10

#### 【0044】

図 3 (A) は、トランジスタの上面図であり、図 3 (B) は、図 3 (A) に示す線分 C1-C2 における断面図である。なお、図 3 (A) では明瞭化のため、一部の構成要素を省いて図示してある。

#### 【0045】

図 3 (A)、(B) に示すトランジスタ 193 は、基板 100 上に形成された下地絶縁膜 110、該下地絶縁膜上に形成されたソース電極 150a およびドレイン電極 150b、該ソース電極およびドレイン電極に接して形成された酸化物半導体層 120、該ソース電極、ドレイン電極および酸化物半導体層 120 上に形成されたゲート絶縁膜 130、該ゲート絶縁膜上に形成されたゲート電極 140、該ゲート絶縁膜および該ゲート電極上に形成された保護膜 160、該保護膜上に形成された平坦化膜 170 を有する。なお、保護膜 160 および平坦化膜 170 は必要に応じて設ければよい。20

#### 【0046】

トランジスタ 193 は、トランジスタ 191 およびトランジスタ 192 とは異なり、ソース電極 150a およびドレイン電極 150b の一部とゲート電極 140 の一部とが重畠する構造である。したがって、チャネル形成領域 120a と、ソース電極 150a またはドレイン電極 150b とが接した状態となるため、ソース領域またはドレイン領域 120b に不純物を添加して低抵抗化する工程を省くこともできる。

#### 【0047】

次に、図 1 (A)、(B) に示すトランジスタ 191 の作製方法について、図 4 を用いて説明する。30

#### 【0048】

まず、基板 100 上に下地絶縁膜 110 を形成する。基板 100 の材料は限定されず、後の加熱工程などに耐えうる材質であればよい。例えば、ガラス基板などの絶縁基板やシリコンウェハーなどの半導体基板などを用いることができる。また、前述したように、他のデバイスが形成された基板であってもよい。

#### 【0049】

下地絶縁膜 110 は、プラズマ CVD 法またはスパッタ法等により、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウムなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いて形成することができる。また、上記材料の積層であってもよく、少なくとも酸化物半導体層 120 と接する上層は、酸化物半導体層 120 への酸素の供給源となりえる酸素を含む材料で形成することが好ましい。40

#### 【0050】

次に、下地絶縁膜 110 上に酸化物半導体膜を成膜し、フォトリソグラフィ法およびエッチング法を用いて島状に加工して酸化物半導体層 120 を形成する（図 4 (A) 参照）。

#### 【0051】

酸化物半導体膜は成膜後に、該酸化物半導体膜に含まれる過剰な水素（水や水酸基を含む50

)を低減または除去(脱水化または脱水素化)するための熱処理を行うことが好ましい。熱処理の温度は、300以上700以下、または基板にガラス基板などを用いている場合は、基板の歪み点未満とする。熱処理は、減圧下、窒素や希ガスなどの不活性雰囲気下、または酸素を含む雰囲気下で行うことが好ましい。

#### 【0052】

この熱処理によって、n型の導電性を付与する不純物である水素を酸化物半導体膜から低減または除去することができる。また、下地絶縁膜110として酸素を含む絶縁層を適用した場合、この熱処理によって下地絶縁膜110に含まれる酸素が酸化物半導体膜へと供給されうる。酸素を下地絶縁膜110から供給することによって、脱水化または脱水素化処理によって増加した酸化物半導体膜の酸素欠損を補填することが可能である。

10

#### 【0053】

なお、脱水化または脱水素化のための熱処理は、島状の酸化物半導体層120の形成後に行ってもよい。また、トランジスタの作製工程の他の加熱処理と兼ねてもよい。

#### 【0054】

上記熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガス、酸素等に、水分、水素などが含まれないことが好ましい。または、上記ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0055】

また、熱処理で酸化物半導体膜を加熱した後、加熱温度を維持、またはその加熱温度から徐冷しながら同じ炉に高純度の酸素ガス、高純度の一酸化二窒素ガス、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気)を導入してもよい。酸素ガスまたは一酸化二窒素ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する酸素ガスまたは一酸化二窒素ガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたは一酸化二窒素ガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガスまたは一酸化二窒素ガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって増加した酸素欠損を補填するため酸素を供給することによって、酸化物半導体膜を高純度化およびi型(真性)化することができる。

20

#### 【0056】

また、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などによって、酸化物半導体膜に酸素を供給する方法を用いてもよい。この場合は、酸化物半導体膜に直接酸素を供給する他、後に形成されるゲート絶縁膜130を介して酸素を供給してもよい。

#### 【0057】

酸化物半導体膜への酸素の導入は、脱水化または脱水素化処理を行った後であれば工程順は限定されない。また、上記脱水化または脱水素化処理を行った酸化物半導体膜への酸素の導入は複数回行ってもよい。

#### 【0058】

酸化物半導体膜は、非晶質であってもよいし、結晶成分を有していてもよい。非晶質の酸化物半導体膜を用いる場合には、後の作製工程において、酸化物半導体膜に熱処理を行うことによって、結晶性酸化物半導体膜としてもよい。非晶質酸化物半導体膜を結晶化させる熱処理の温度は、250以上700以下、好ましくは、400以上、より好ましくは500以上、さらに好ましくは550以上とする。なお、当該熱処理は、作製工程における他の熱処理を兼ねることも可能である。

30

#### 【0059】

酸化物半導体膜の成膜方法は、スパッタ法、MBE(Molecular Beam Epitaxy)法、CVD法、パルスレーザ堆積法、ALD(Atomic Layer Deposition)法等を適宜用いることができる。また、酸化物半導体膜は、ス

40

パッタターゲット表面に対し、略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

#### 【0060】

酸化物半導体膜を成膜する際、できる限り酸化物半導体膜に含まれる水素濃度を低減させることができが好ましい。水素濃度を低減させるには、例えば、スパッタ法を用いて成膜を行う場合には、スパッタ装置の成膜室内に供給する雰囲気ガスとして、水素、水、水酸基または水素化物などの不純物が除去された高純度の希ガス（代表的にはアルゴン）、酸素、および希ガスと酸素との混合ガスを適宜用いる。

#### 【0061】

また、成膜室内の残留水分を除去しつつ水素および水分が除去されたスパッタガスを導入して成膜を行うことで、成膜された酸化物半導体膜の水素濃度を低減させることができる。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることができる。また、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプは、例えば、水素分子、水（H<sub>2</sub>O）など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等の排気能力が高いため、クライオポンプを用いて排気した成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0062】

また、酸化物半導体膜をスパッタ法で成膜する場合、成膜に用いる金属酸化物ターゲットの相対密度（充填率）は90%以上、好ましくは95%以上とする。相対密度の高い金属酸化物ターゲットを用いることにより、緻密な酸化物半導体膜を成膜することができる。

#### 【0063】

また、基板を高温に保持した状態で酸化物半導体膜を形成することも、酸化物半導体膜中に含まれる不純物濃度を低減するのに有効である。基板を加熱する温度としては、150以上450以下とすればよく、好ましくは基板温度が200以上350以下とすればよい。また、成膜時に基板を高温で加熱することで、結晶性酸化物半導体層を形成することができる。

#### 【0064】

上記酸化物半導体膜に用いる酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。特にInとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。また、スタビライザーとしてジルコニウム（Zr）を有することが好ましい。

#### 【0065】

また、他のスタビライザーとして、ランタノイドである、ランタン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種あるいは複数種を有してもよい。

#### 【0066】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物（IGZOとも表記する）、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸

10

20

30

40

50

化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

#### 【0067】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

10

#### 【0068】

また、酸化物半導体として、 $InMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、MnおよびCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

#### 【0069】

なお、酸化物半導体膜の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。特に、成膜時に発生するゴミを低減でき、かつ膜厚分布も均一とすることからDCスパッタ法を用いることが好ましい。

20

#### 【0070】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1 / 3 : 1 / 3 : 1 / 3$ )、 $In : Ga : Zn = 2 : 2 : 1$  ( $= 2 / 5 : 2 / 5 : 1 / 5$ )、あるいは $In : Ga : Zn = 3 : 1 : 2$  ( $= 1 / 2 : 1 / 6 : 1 / 3$ ) の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1 / 3 : 1 / 3 : 1 / 3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1 / 3 : 1 / 6 : 1 / 2$ ) あるいは $In : Sn : Zn = 2 : 1 : 5$  ( $= 1 / 4 : 1 / 8 : 5 / 8$ ) の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0071】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

30

#### 【0072】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低くすることにより移動度を上げることができる。

#### 【0073】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ ) である酸化物の組成が、原子数比が $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ ) の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$ が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことをいい、 $r$ は、例えば、0.05とすればよい。他の酸化物でも同様である。

40

#### 【0074】

また酸化物半導体膜を成膜する際に用いるスパッタガスは、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

#### 【0075】

また、初期の酸化物半導体層120は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態を有する膜を用いることができる。好ましくは、酸化物半導体層は、CAAC-OS(C Axis Aligned Crystalline Oxid

50

e Semiconductor) 膜とすることが好ましい。

**【0076】**

C AAC - OS 膜で構成された酸化物半導体膜は、スパッタ法によつても作製することができる。スパッタ法によつて C AAC - OS 膜を得るには酸化物半導体膜の堆積初期段階において六方晶の結晶が形成されるようにすることと、当該結晶を種として結晶が成長されるようにすることが肝要である。そのためには、ターゲットと基板の距離を広くとり(例えば、150 mm ~ 200 mm 程度)、基板加熱温度を 100 ~ 500 、好適には 200 ~ 400 、さらに好適には 250 ~ 300 にすると好ましい。また、これに加えて、成膜時の基板加熱温度よりも高い温度で、堆積された酸化物半導体膜を熱処理することで膜中に含まれるミクロな欠陥や、積層界面の欠陥を修復することができる。

10

**【0077】**

C AAC - OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。C AAC - OS 膜は、非晶質相に結晶部および非晶質部を有する結晶 - 非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が 100 nm 未満の立方体内に收まる大きさが多い。また、透過型電子顕微鏡 (TEM: Transmission Electron Microscope) による観察像では、C AAC - OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって C AAC - OS 膜には粒界 (グレインバウンダリーともいう) は確認できない。そのため、C AAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。

**【0078】**

20

C AAC - OS 膜に含まれる結晶部は、c 軸が C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85° 以上 95° 以下の範囲も含まれることとする。また、単に平行と記載する場合、-5° 以上 5° 以下の範囲も含まれることとする。

**【0079】**

なお、C AAC - OS 膜において、結晶部の分布が一様でなくてもよい。例えば、C AAC - OS 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、C AAC - OS 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

30

**【0080】**

C AAC - OS 膜に含まれる結晶部の c 軸は、C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、C AAC - OS 膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、C AAC - OS 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

40

**【0081】**

C AAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

**【0082】**

また、C AAC - OS 膜を成膜するために、以下の条件を適用することが好ましい。

**【0083】**

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物を低減すればよい。具体的には、露点が -80 以下、好ましくは -100 以下である成膜ガスを用いる。

50

## 【0084】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタ粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタ粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタ粒子の平らな面が基板に付着する。

## 【0085】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

10

## 【0086】

また、酸化物半導体層120は、複数の酸化物半導体層が積層された構造でもよい。例えば、酸化物半導体層120を第1の酸化物半導体層と第2の酸化物半導体層の積層として、第1の酸化物半導体層と第2の酸化物半導体層に、異なる組成の金属酸化物を用いてもよい。

## 【0087】

また、第1の酸化物半導体層と第2の酸化物半導体層の構成元素を同一とし、両者の組成を異ならせててもよい。例えば、第1の酸化物半導体層の原子数比をIn:Ga:Zn=1:1:1とし、第2の酸化物半導体層の原子数比をIn:Ga:Zn=3:1:2としてもよい。また、第1の酸化物半導体層の原子数比をIn:Ga:Zn=1:3:2とし、第2の酸化物半導体層の原子数比をIn:Ga:Zn=2:1:3としてもよい。

20

## 【0088】

この時、第1の酸化物半導体層と第2の酸化物半導体層のうち、ゲート電極に近い側(チャネル側)の酸化物半導体層のInとGaの含有率をIn>Gaとするよ。またゲート電極から遠い側(バックチャネル側)の酸化物半導体層のInとGaの含有率をIn Ga(Gaの含有率はInの含有率以上)とするよ。

## 【0089】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることによりs軌道のオーバーラップが多くなる傾向があるため、In>Gaの組成となる酸化物はIn-Gaの組成となる酸化物と比較して高い移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、In-Gaの組成となる酸化物はIn>Gaの組成となる酸化物と比較して安定した特性を備える。

30

## 【0090】

チャネル側にIn>Gaの組成となる酸化物半導体を適用し、バックチャネル側にIn Gaの組成となる酸化物半導体を適用することで、トランジスタの移動度および信頼性をさらに高めることが可能となる。

## 【0091】

また、第1の酸化物半導体層と第2の酸化物半導体層に、結晶性の異なる酸化物半導体を適用してもよい。すなわち、単結晶酸化物半導体膜、多結晶酸化物半導体膜、非晶質酸化物半導体膜、またはCAAC-OS膜を適宜組み合わせた構成としてもよい。また、第1の酸化物半導体層と第2の酸化物半導体層の少なくともどちらか一方に非晶質酸化物半導体膜を適用すると、酸化物半導体層120の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、また、トランジスタの信頼性をさらに高めることが可能となる。

40

## 【0092】

一方で、非晶質酸化物半導体膜は水素などのドナーとなる不純物を吸収しやすく、また、酸素欠損が生じやすいためn型化されやすい。このため、チャネル側の酸化物半導体層は、CAAC-OSなどの結晶性を有する酸化物半導体を適用することが好ましい。

## 【0093】

50

また、酸化物半導体層 120 を 3 層以上の積層構造とし、複数層の結晶性を有する酸化物半導体層で非晶質酸化物半導体層を挟む構造としてもよい。また、結晶性を有する酸化物半導体層と非晶質酸化物半導体層を交互に積層する構造としてもよい。

#### 【0094】

また、酸化物半導体層 120 を複数層の積層構造とする場合の上記構成は、それぞれを適宜組み合わせて用いることができる。

#### 【0095】

また、酸化物半導体層 120 を複数層の積層構造とし、各酸化物半導体層の形成後に酸素を導入してもよい。酸素の導入は、酸素雰囲気下による熱処理や、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、酸素を含む雰囲気下で行うプラズマ処理などを用いることができる。10

#### 【0096】

各酸化物半導体層の形成毎に酸素を導入することで、酸化物半導体内の酸素欠損を低減する効果を高めることができる。

#### 【0097】

本実施の形態においては、CAC - OS 膜を初期の酸化物半導体層 120 に用いる例として説明する。

#### 【0098】

次に、酸化物半導体層 120 上にゲート絶縁膜 130 を plasma CVD 法またはスパッタ法等により形成する。ゲート絶縁膜 130 には、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いることができる。20

#### 【0099】

また、ゲート絶縁膜 130 の材料として酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート、ハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、酸化ランタンなどの high - k 材料を用いることでゲートリーク電流を低減することができる。また、ゲート絶縁膜 130 は、上記材料の単層構造に限らず、積層構造であってもよい。

#### 【0100】

なお、ゲート絶縁膜 130 は、酸化物半導体層 120 と接する絶縁膜であるため、酸素を含む絶縁膜とすることが好ましく、可能な限り水、水素などの不純物が含まれないことが好ましい。しかしながら、 plasma CVD 法では原料ガスに水素が含まれるため、スパッタ法と比較して膜中の水素濃度を低減させることが困難である。したがって、 plasma CVD 法でゲート絶縁膜 130 を形成する場合は、成膜後に水素の低減、または除去を目的とした熱処理（脱水化または脱水素化処理）を行うことが好ましい。30

#### 【0101】

熱処理の温度は、250 以上 650 以下、好ましくは 450 以上 600 以下、またはガラス基板を用いている場合は、ガラス基板の歪み点未満とする。例えば、加熱処理装置の一つである電気炉に基板を導入し、ゲート絶縁膜 130 に対して真空（減圧）雰囲気下 650 において 1 時間の加熱処理を行う。40

#### 【0102】

なお、熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等の RTA (Rapid Thermal Anneal) 装置を用いることができる。LRTA 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA 装置は、高温のガスを用いて熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気50

体が用いられる。なお、熱処理装置としてG R T A 装置を用いる場合には、その処理時間が短いため、650 ~ 700 の高温に加熱した不活性ガス中で基板を加熱してもよい。

#### 【 0 1 0 3 】

熱処理は、窒素、酸素、超乾燥空気（水の含有量が20 ppm以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥空気、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、加熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上（即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。10

#### 【 0 1 0 4 】

熱処理によって、ゲート絶縁膜130の脱水化または脱水素化を行うことができ、トランジスタの特性変動を引き起こす水素、または水などの不純物が排除されたゲート絶縁膜130を形成することができる。

#### 【 0 1 0 5 】

脱水化または脱水素化処理を行う熱処理においては、ゲート絶縁膜130表面は水素または水分等の放出を妨害するような状態（例えば、水素または水分等を通過させない膜などを設けるなど）とせず、ゲート絶縁膜130は表面を露出した状態とすることが好ましい。20

#### 【 0 1 0 6 】

また、脱水化または脱水素化のための熱処理は、複数回行ってもよく、他の熱処理と兼ねてもよい。

#### 【 0 1 0 7 】

また、脱水化または脱水素化されたゲート絶縁膜130に対して加酸素化処理を行ってもよい。例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などによって、ゲート絶縁膜130に酸素を供給することができる。この処理において、同時に酸化物半導体層120に酸素を供給してもよい。30

#### 【 0 1 0 8 】

次に、ゲート絶縁膜130上にスパッタ法等で導電膜を形成し、フォトリソグラフィ法およびエッチング法を用いて、ゲート電極140を形成する（図4（B）参照）。

#### 【 0 1 0 9 】

ゲート電極140となる導電膜には、モリブデン、チタン、タンタル、タンクステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いることができる。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極140は、単層構造としてもよいし、積層構造としてもよい。

#### 【 0 1 1 0 】

また、ゲート電極140の材料は、酸化インジウム酸化スズ、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を用いることができる。また、上記導電性材料と、前述した金属材料の積層構造とすることもできる。40

#### 【 0 1 1 1 】

また、ゲート電極140として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Zn-O膜や、窒素を含むIn-Sn-O膜や、窒素を含むIn-Ga-O膜や、窒素を含むIn-Zn-O膜や、窒素を含むSn-O膜や、窒素を含むIn-O膜や、金属窒化膜（InN、SnNなど）を用いることができる。これらの膜は5eV（電子ボルト）以上、好ましくは5.5eV以上の仕事関数を有し、ゲート電極として用いた場合、50

トランジスタのしきい値電圧をプラスにすることができ、所謂ノーマリオフのスイッチング素子を実現できる。

#### 【0112】

例えば、中間層に銅、上層または下層の一方に銅の拡散を防止する窒化タンゲステン、他方に窒化タンタルを形成した三層構造の導電層をゲート電極140として用いることができる。なお、上記電極構造では、銅を封じ込めるためにフォトリソグラフィ工程およびエッチング工程が増加してしまうが、銅の拡散を抑制する効果は非常に高く、トランジスタの信頼性を高めることができる。

#### 【0113】

また、ゲート電極140、およびそれらと同時に形成することのできる他の電極や配線は、端部をテーパー形状にすることが好ましい。電極や配線の端部をテーパー形状することで、それらの上部に形成される絶縁膜等の被覆性を向上させることができ、該被覆性の不良にともなう電気特性の低下および信頼性の低下を抑えることができる。なお、電極や配線の端部のテーパー角は40°～80°とすることがより好ましい。

#### 【0114】

ゲート電極140形成後には熱処理を行ってもよい。例えば、G R T A装置により、650、1分～5分間、熱処理を行えばよい。また、電気炉により、500、30分～1時間、熱処理を行ってもよい。

#### 【0115】

次に、ゲート電極140をマスクとして、酸素101を酸化物半導体層120に添加し、チャネル形成領域120a、およびソース領域またはドレイン領域120bを形成する（図4（C）参照）。例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などによって、ゲート絶縁膜130を介して酸化物半導体層120に酸素を供給することができる。この処理において、同時にゲート絶縁膜130に酸素を供給してもよい。

#### 【0116】

本実施の形態では、イオン注入法を用いて、ソース領域またはドレイン領域120bとなる領域に酸素101を注入する。例えば、酸化物半導体層120の膜厚が30nm、ゲート絶縁膜130の膜厚が20nmの場合、加速電圧を5～30kVとし、ドーズ量 $1 \times 10^{15} / cm^2$ ～ $5 \times 10^{16} / cm^2$ のO<sup>+</sup>を注入すればよい。または、加速電圧を10～60kVとし、ドーズ量 $5 \times 10^{14} / cm^2$ ～ $2.5 \times 10^{16} / cm^2$ のO<sub>2</sub><sup>+</sup>を注入すればよい。

#### 【0117】

ここで、初期の酸化物半導体層120はCAC-O<sub>x</sub>膜であり、チャネル形成領域はその形態を維持するが、ソース領域またはドレイン領域120bとなる領域は、注入された酸素原子によるダメージなどによって結晶成分を構成する原子の秩序性が崩れ、非晶質化する。

#### 【0118】

次に、酸化物半導体層120において、ソース領域またはドレイン領域120bとなる領域を低抵抗化するため、該領域に不純物を添加し、ソース領域またはドレイン領域120bを形成する。該不純物の添加方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

#### 【0119】

酸化物半導体層120の導電率を高める不純物としては、例えば、リン(P)、砒素(A<sub>s</sub>)、アンチモン(Sb)、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Ar)、ヘリウム(He)、ネオン(Ne)、インジウム(In)、フッ素(F)、塩素(Cl)、チタン(Ti)、亜鉛(Zn)、および炭素(C)のいずれかから選択される一つ以上を用いることができる。

#### 【0120】

該不純物の添加工程は、加速電圧、ドーズ量などの注入条件、また、通過させる膜の膜厚

10

20

30

40

50

を適宜設定して制御すればよい。例えば、ソース領域またはドレイン領域 120b となる領域に添加される不純物としてリンを用いる場合、不純物が添加される領域の不純物濃度を  $5 \times 10^{-8} / \text{cm}^3$  以上  $1 \times 10^{-2} / \text{cm}^3$  以下とすることが好ましい。

#### 【0121】

なお、上記イオン注入工程において、CO<sup>+</sup> または CO<sub>2</sub><sup>+</sup> を注入することで、ソース領域またはドレイン領域 120b に酸素と炭素を同時に添加することができ、イオン注入工程を 1 回とすることができます。また、CO<sub>2</sub><sup>+</sup> では O<sub>2</sub><sup>+</sup> より質量が大きいため、注入プロファイルのピーク位置をより浅くすることができ、薄膜への注入に適しているということができる。

#### 【0122】

なお、不純物の添加は、基板を加熱しながら行ってもよい。また、酸化物半導体層 120 への不純物添加処理は、複数回行ってもよく、不純物の種類も複数種用いてもよい。また、不純物の添加は、ソース領域またはドレイン領域 120b となる領域に酸素を添加する前、保護膜 160 の形成後、または酸化物半導体層 120 の熱処理後に行ってもよい。

#### 【0123】

次に、ゲート絶縁膜 130 およびゲート電極 140 上に保護膜 160 を形成することが好ましい。保護膜 160 としては、例えば、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜などの絶縁膜を用いることができる。

#### 【0124】

なお、保護膜 160 としては、酸化アルミニウム膜を用いることがより好ましい。酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果（ブロック効果）が高い。

#### 【0125】

なお、酸化アルミニウム膜は、酸化アルミニウム膜をスパッタ法などで直接成膜する、またはアルミニウム（Al）膜をスパッタ法等で成膜後に、酸素プラズマ処理、酸素のイオン注入、酸素のイオンドーピングなどを行うことによって形成することができる。

#### 【0126】

また、保護膜 160 は、酸化シリコン膜、酸化ガリウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜のいずれか一つ以上の絶縁膜と、酸化アルミニウム膜との積層であってもよい。

#### 【0127】

また、保護膜 160 に対して加酸素化処理を行ってもよい。例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などによって、保護膜 160 に酸素を供給することができる。

#### 【0128】

次に、酸化物半導体層 120 の熱処理を行うことによりソース領域またはドレイン領域 120b に添加されている酸素の横方向への拡散を助長させ、先のゲート絶縁膜 130 の脱水、脱水素化のための熱処理などによりチャネル形成領域 120a に形成された酸素欠損を補填する。酸化物半導体層 120 の熱処理は、ゲート絶縁膜 130 の脱水、脱水素化のための熱処理と同様の方法を用いることができる。なお、この熱処理は、ソース領域またはドレイン領域 120b となる領域に酸素を添加する工程以降のいずれの段階で行ってもよいが、保護膜 160 の形成後に行なうことがより好ましい。保護膜 160 によって該保護膜より外側に酸素が放出されることを防ぐことができ、ソース領域またはドレイン領域 120b に添加されている酸素を効率よくチャネル形成領域 120a に拡散させることができる。

#### 【0129】

なお、ソース領域またはドレイン領域 120b からチャネル形成領域 120a に拡散する酸素は、ソース領域またはドレイン領域 120b に添加されている酸素の一部であり、ソース領域またはドレイン領域 120b に含まれる酸素がチャネル形成領域 120a よりも

10

20

30

40

50

多い状態は保持される。したがって、ソース領域またはドレイン領域 120b は、常にチャネル形成領域 120a に対する酸素供給源とすることができる、トランジスタの長期動作や動作環境に起因して発生するチャネル形成領域 120a の酸素欠損なども補填することができる。なお、ソース領域またはドレイン領域 120b に含まれる過剰の酸素は、常温においてもチャネル形成領域 120a に拡散させることができる。

#### 【0130】

次に、必要に応じて、保護膜 160 上に平坦化膜 170 を形成する。該平坦化膜としては、保護膜 160 として用いることのできる絶縁膜の他、ポリイミド系樹脂、アクリル系樹脂、ポリイミドアミド系樹脂、ベンゾシクロブテン系樹脂、ポリアミド系樹脂、エポキシ系樹脂等の耐熱性を有する有機材料を用いることができる。また、上記有機材料の他に、低誘電率材料 (low-k 材料)、シロキサン系樹脂、PSG (リンガラス)、BPSG (リンボロンガラス) 等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで平坦化膜を形成してもよい。また、CMP 法等によって形成した膜の表面を平坦化処理してもよい。

10

#### 【0131】

例えば、平坦化膜 170 として、膜厚 1500 nm のアクリル樹脂膜を形成すればよい。アクリル樹脂膜は塗布法による塗布後、焼成 (例えば、窒素雰囲気下、250°、1 時間) して形成することができる。

#### 【0132】

次に、フォトリソグラフィ法およびエッティング法を用いて平坦化膜 170、保護膜 160、およびゲート絶縁膜 130 にコンタクトホールを形成する。そして、該コンタクトホールを充填する導電膜をスパッタ法などを用いて平坦化膜 170 上に形成し、フォトリソグラフィ法およびエッティング法を用いてソース電極 150a およびドレイン電極 150b を形成する (図 4 (D) 参照)。

20

#### 【0133】

なお、上記導電膜としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステン等から選ばれた元素、または上述した元素を成分とする合金、または上述した元素を組み合わせた合金などを用いることができる。また、該導電膜は単層でも 2 層以上の積層としてもよい。例えば、アルミニウムや銅などの金属膜の下側、または上側、若しくはその両方にクロム、タンタル、チタン、モリブデン、タングステン等の高融点金属膜やそれらの導電性窒化膜を積層する構成とすることもできる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

30

#### 【0134】

以上により、図 1 (A)、(B) に示したトランジスタ 191 を作製することができる。

#### 【0135】

また、図 2 (A)、(B) に示したトランジスタ 192 の作製方法は次の通りである。

#### 【0136】

まず、基板 100 上に形成した下地絶縁膜 110 上に酸化物半導体層 120 を形成する (図 5 (A) 参照)。

40

#### 【0137】

次に、該酸化物半導体層の一部と接するソース電極 150a およびドレイン電極 150b を形成し、該酸化物半導体層および該ソース電極およびドレイン電極上にゲート絶縁膜 130 を形成する (図 5 (B) 参照)。

#### 【0138】

次に、イオン注入法等によりゲート電極 140、ソース電極 150a、およびドレイン電極 150b をマスクとして、酸化物半導体層 120 に酸素および導電率を高める不純物を添加し、チャネル形成領域 120a、ソース領域またはドレイン領域 120b、および領域 120c を形成する (図 5 (C) 参照)。

#### 【0139】

50

次に、保護膜 160 形成後に熱処理を行い、ソース領域またはドレイン領域 120b からチャネル形成領域 120a に酸素を拡散させる。

【0140】

そして、必要に応じて平坦化膜 170 を形成する（図 5（D）参照）。

【0141】

以上により、図 2（A）、（B）に示したトランジスタ 192 を作製することができる。なお、トランジスタ 192 はトランジスタ 191 と同様の材料を用いて形成することができ、その詳細はトランジスタ 191 の作製方法を参照することができる。

【0142】

また、図 3（A）、（B）に示したトランジスタ 193 の作製方法は次の通りである。

10

【0143】

まず、基板 100 上に形成した下地絶縁膜 110 上にソース電極 150a およびドレイン電極 150b を形成する。

【0144】

次に、ソース電極 150a およびドレイン電極 150b の一部と接するように酸化物半導体層 120 を形成する（図 6（A）参照）。

【0145】

次に、ソース電極 150a、ドレイン電極 150b、および酸化物半導体層 120 上にゲート絶縁膜 130 を形成し、該ゲート絶縁膜上にゲート電極 140 を形成する（図 6（B）参照）。

20

【0146】

次に、イオン注入法等によりゲート電極 140 をマスクとして酸化物半導体層 120 に酸素を添加し、チャネル形成領域 120a、ソース領域またはドレイン領域 120b を形成する（図 6（C）参照）。なお、ソース領域またはドレイン領域 120b には、導電率を高める不純物を添加してもよい。

【0147】

次に、保護膜 160 形成後に熱処理を行い、ソース領域またはドレイン領域 120b からチャネル形成領域 120a に酸素を拡散させる。

【0148】

そして、必要に応じて平坦化膜 170 を形成する（図 6（D）参照）。

30

【0149】

以上により、図 3（A）、（B）に示したトランジスタ 193 を作製することができる。なお、トランジスタ 193 はトランジスタ 191 と同様の材料を用いて形成することができ、その詳細はトランジスタ 191 の作製方法を参照することができる。

【0150】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0151】

（実施の形態 2）

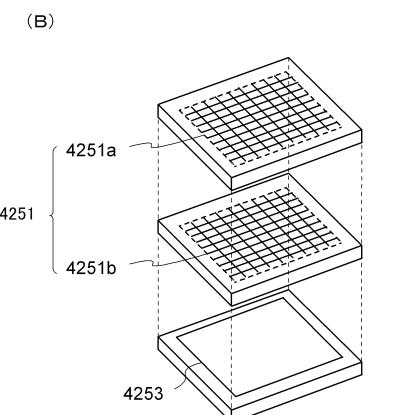

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置（記憶装置）の一例を、図面を用いて説明する。

40

【0152】

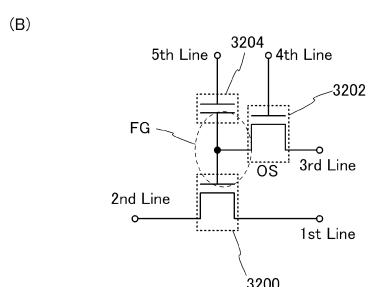

図 7 は、半導体装置の構成の一例である。図 7（A）に、半導体装置の断面図を、図 7（B）に半導体装置の回路図をそれぞれ示す。

【0153】

図 7（A）および図 7（B）に示す半導体装置は、下部に第 1 の半導体材料を用いたトランジスタ 3200 を有し、上部に第 2 の半導体材料を用いたトランジスタ 3202 および容量素子 3204 を有している。なお、トランジスタ 3202 としては、実施の形態 1 の図 1 に示すトランジスタを適用する例を示している。また、容量素子 3204 は、一方の

50

電極をトランジスタ3202のゲート電極、他方の電極をトランジスタ3202のソース電極またはドレイン電極、誘電体をトランジスタ3202の保護膜および平坦化膜と同じ材料を用いる構造とすることで、トランジスタ3202と同時に形成することができる。

#### 【0154】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料（シリコンなど）とし、第2の半導体材料を酸化物半導体とすることができます。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

#### 【0155】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのではない。また、情報を保持するために酸化物半導体を用いた実施の形態1に示すようなトランジスタを用いる他は、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

#### 【0156】

図7(A)におけるトランジスタ3200は、半導体材料（例えば、結晶性シリコンなど）を含む基板3000に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、不純物領域に接する金属間化合物領域と、チャネル形成領域上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を有する。なお、図において、明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極やドレイン電極と表現することがある。つまり、本明細書において、ソース電極との記載には、ソース領域が含まれうる。

#### 【0157】

基板3000上にはトランジスタ3200を囲むように素子分離絶縁層3106が設けられており、トランジスタ3200を覆うように絶縁層3220が設けられている。なお、素子分離絶縁層3106は、LOCOS (Local Oxidation of Silicon) や、STI (Shallow Trench Isolation) などの素子分離技術を用いて形成することができる。

#### 【0158】

例えば、結晶性シリコン基板を用いたトランジスタ3200は、高速動作が可能である。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。トランジスタ3202および容量素子3204の形成前の処理として、トランジスタ3200を覆う絶縁層3220にCMP処理を施して、絶縁層3220を平坦化すると同時にトランジスタ3200のゲート電極の上面を露出させる。

#### 【0159】

トランジスタ3200のゲート電極上には、該ゲート電極と電気的に接続する接続配線3210が設けられている。また、絶縁層3220上にはトランジスタ3202が設けられ、そのソース電極またはドレイン電極の一方と接続配線3210は電気的に接続される。また、接続配線3210は容量素子3204の一方の電極としても作用する。

#### 【0160】

図7(A)に示すトランジスタ3202は、酸化物半導体層にチャネルが形成されるトップゲート型トランジスタである。トランジスタ3202は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

#### 【0161】

10

20

30

40

50

図7(A)に示すように、トランジスタ3200と容量素子3204は重畠するように形成することができるため、その占有面積を低減することができる。したがって、半導体装置の集積度を高めることができる。

#### 【0162】

次に、図7(A)に対応する回路構成の一例を図7(B)に示す。

#### 【0163】

図7(B)において、第1の配線(1st Line)とトランジスタ3200のソース電極とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ3200のドレイン電極とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ3202のソース電極またはドレイン電極の一方とは、電気的に接続され

10、第4の配線(4th Line)と、トランジスタ3202のゲート電極とは、電気的に接続されている。そして、トランジスタ3200のゲート電極と、トランジスタ3202のソース電極またはドレイン電極の他方は、容量素子3204の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子3204の電極の他方は電気的に接続されている。

#### 【0164】

図7(B)に示す半導体装置では、トランジスタ3200のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

。

#### 【0165】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ3202がオン状態となる電位にして、トランジスタ3202をオン状態とする。これにより、第3の配線の電位が、トランジスタ3200のゲート電極、および容量素子3204に与えられる。すなわち、トランジスタ3200のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ3202がオフ状態となる電位にして、トランジスタ3202をオフ状態とすることにより、トランジスタ3200のゲート電極に与えられた電荷が保持される(保持)。

20

#### 【0166】

トランジスタ3202のオフ電流は極めて小さいため、トランジスタ3200のゲート電極の電荷は長時間にわたって保持される。

30

#### 【0167】

次に情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ3200のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極にHighレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_H}$ は、トランジスタ3200のゲート電極にLowレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$ ( $> V_{th\_H}$ )となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$ ( $< V_{th\_L}$ )となっても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線の電位を判別することで、保持されている情報を読み出すことができる。

40

#### 【0168】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み

50

出せることが必要になる。このように情報を読み出さないメモリセルにおいては、ゲート電極の状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{t\ h\_H}$ より小さい電位を第5の配線に与えればよい。または、ゲート電極の状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{t\ h\_L}$ より大きい電位を第5の配線に与えればよい。

#### 【0169】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。10

#### 【0170】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フロー・ティング・ゲートへの電子の注入や、フロー・ティング・ゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁膜の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限ではなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。20

#### 【0171】

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置、および該半導体装置の作製方法を提供することができる。

#### 【0172】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0173】

##### （実施の形態3）

本実施の形態では、実施の形態1に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態2に示した構成と異なる半導体装置の説明を行う。30

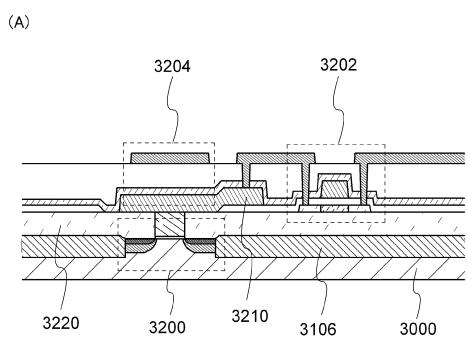

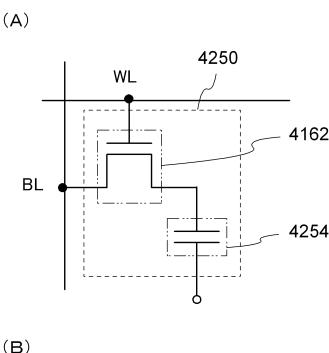

#### 【0174】

図8(A)は、半導体装置の回路構成の一例を示し、図8(B)は半導体装置の一例を示す概念図である。なお、当該半導体装置に含まれるトランジスタ4162としては、実施の形態1で説明したトランジスタを用いることができる。また、容量素子4254は、実施の形態2で説明した容量素子3204と同様に、トランジスタ4162の作製工程にて同時に作製することができる。

#### 【0175】

図8(A)に示す半導体装置において、ビット線BLとトランジスタ4162のソース電極とは電気的に接続され、ワード線WLとトランジスタ4162のゲート電極とは電気的に接続され、トランジスタ4162のドレイン電極と容量素子4254の第1の端子とは電気的に接続されている。40

#### 【0176】

次に、図8(A)に示す半導体装置(メモリセル4250)に、情報の書き込みおよび保持を行う場合について説明する。

#### 【0177】

まず、ワード線WLの電位を、トランジスタ4162がオン状態となる電位として、トランジスタ4162をオン状態とする。これにより、ビット線BLの電位が、容量素子4254の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ4162がオフ状態となる電位として、トランジスタ4162をオフ状態とすること50

により、容量素子 4254 の第 1 の端子の電位が保持される（保持）。

【0178】

酸化物半導体を用いたトランジスタ 4162 は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ 4162 をオフ状態とすることで、容量素子 4254 の第 1 の端子の電位（あるいは、容量素子 4254 に蓄積された電荷）を極めて長時間にわたって保持することが可能である。

【0179】

次に、情報の読み出しについて説明する。トランジスタ 4162 がオン状態となると、浮遊状態であるビット線 BL と容量素子 4254 とが導通し、ビット線 BL と容量素子 4254 の間で電荷が再分配される。その結果、ビット線 BL の電位が変化する。ビット線 BL の電位の変化量は、容量素子 4254 の第 1 の端子の電位（あるいは容量素子 4254 に蓄積された電荷）によって、異なる値をとる。

10

【0180】

例えば、容量素子 4254 の第 1 の端子の電位を V、容量素子 4254 の容量を C、ビット線 BL が有する容量成分（以下、ビット線容量とも呼ぶ）を CB、電荷が再分配される前のビット線 BL の電位を V<sub>B0</sub> とすると、電荷が再分配された後のビット線 BL の電位は、 $(CB \times V_{B0} + C \times V) / (CB + C)$  となる。したがって、メモリセル 4250 の状態として、容量素子 4254 の第 1 の端子の電位が V<sub>1</sub> と V<sub>0</sub> ( $V_1 > V_0$ ) の 2 状態をとるとすると、電位 V<sub>1</sub> を保持している場合のビット線 BL の電位 (=  $(CB \times V_{B0} + C \times V_1) / (CB + C)$ ) は、電位 V<sub>0</sub> を保持している場合のビット線 BL の電位 (=  $(CB \times V_{B0} + C \times V_0) / (CB + C)$ ) よりも高くなることがわかる。

20

【0181】

そして、ビット線 BL の電位を所定の電位と比較することで、情報を読み出すことができる。

【0182】

このように、図 8 (A) に示す半導体装置は、トランジスタ 4162 のオフ電流が極めて小さいという特徴から、容量素子 4254 に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。

30

【0183】

次に、図 8 (B) に示す半導体装置について、説明を行う。

【0184】

図 8 (B) に示す半導体装置は、上部に記憶回路として図 8 (A) に示したメモリセル 4250 を複数有するメモリセルアレイ 4251 (メモリセルアレイ 4251a および 4251b) を有し、下部に、メモリセルアレイ 4251 を動作させるために必要な周辺回路 4253 を有する。なお、周辺回路 4253 は、メモリセルアレイ 4251 と電気的に接続されている。

40

【0185】

図 8 (B) に示した構成とすることにより、周辺回路 4253 をメモリセルアレイ 4251 の直下に設けることができるため半導体装置の小型化を図ることができる。

【0186】

周辺回路 4253 に設けられるトランジスタは、トランジスタ 4162 とは異なる半導体材料を用いることが好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることがより好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、該トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。

50

**【 0 1 8 7 】**

なお、図8（B）に示した半導体装置では、メモリセルアレイ4251がメモリセルアレイ4251aとメモリセルアレイ4251bの積層である構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としても良いし、単層であってもよい。

**【 0 1 8 8 】**

トランジスタ4162は、酸化物半導体を用いて形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

10

**【 0 1 8 9 】**

また、酸化物半導体以外の材料を用いたトランジスタ（換言すると、十分な高速動作が可能なトランジスタ）を用いた周辺回路と、酸化物半導体を用いたトランジスタ（より広義には、十分にオフ電流が小さいトランジスタ）を用いた記憶回路とを一体に備えることでの、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

**【 0 1 9 0 】**

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置を提供することができる。

**【 0 1 9 1 】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

20

**【 0 1 9 2 】****（実施の形態4）**

本実施の形態では、上記実施の形態に開示したトランジスタを少なくとも一部に用いて構成されるCPU（Central Processing Unit）について説明する。

**【 0 1 9 3 】**

図9（A）は、CPUの具体的な構成を示すブロック図である。図9（A）に示すCPUは、基板1190上に、演算回路（ALU：Arithmetic logic unit）1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェイス（Bus I/F）1198、書き換え可能なROM1199、およびROMインターフェイス（ROM I/F）1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROM I/F1189は、別チップに設けてもよい。もちろん、図9（A）に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

30

**【 0 1 9 4 】**

バスインターフェイス1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

40

**【 0 1 9 5 】**

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアド

50

レスを生成し、C P Uの状態に応じてレジスタ1196の読み出しや書き込みを行う。

#### 【0196】

また、タイミングコントローラ1195は、A L U 1 1 9 1、A L Uコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号C L K 1を元に、内部クロック信号C L K 2を生成する内部クロック生成部を備えており、内部クロック信号C L K 2を上記各種回路に供給する。

#### 【0197】

図9(A)に示すC P Uでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルには、上記実施の形態に記載されているメモリセルを用いることができる。

#### 【0198】

図9(A)に示すC P Uにおいて、レジスタコントローラ1197は、A L U 1 1 9 1からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、論理反転素子によるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。論理反転素子によるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

10

20

#### 【0199】

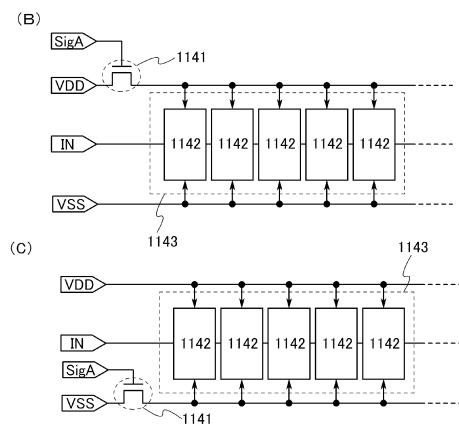

電源停止に関しては、図9(B)または図9(C)に示すように、メモリセル群と、電源電位V D Dまたは電源電位V S Sの与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図9(B)および図9(C)の回路の説明を行う。

#### 【0200】

図9(B)および図9(C)では、メモリセルへの電源電位の供給を制御するスイッチング素子に、上記実施の形態に開示したトランジスタを含む記憶回路の構成の一例を示す。

#### 【0201】

図9(B)に示す記憶装置は、スイッチング素子1141と、メモリセル1142を複数有するメモリセル群1143とを有している。具体的には、各メモリセル1142には、上記実施の形態に記載されているメモリセルを用いることができる。メモリセル群1143が有する各メモリセル1142には、スイッチング素子1141を介して、ハイレベルの電源電位V D Dが供給されている。さらに、メモリセル群1143が有する各メモリセル1142には、信号I Nの電位と、ローレベルの電源電位V S Sの電位が与えられている。

30

#### 【0202】

図9(B)では、スイッチング素子1141として、上記実施の形態に開示したトランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号S i g Aによりスイッチングが制御される。

40

#### 【0203】

なお、図9(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、特に限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

#### 【0204】

また、図9(B)では、スイッチング素子1141により、メモリセル群1143が有する各メモリセル1142への、ハイレベルの電源電位V D Dの供給が制御されているが、スイッチング素子1141により、ローレベルの電源電位V S Sの供給が制御されていて

50

もよい。

**【0205】**

また、図9(C)には、メモリセル群1143が有する各メモリセル1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、メモリセル群1143が有する各メモリセル1142への、ローレベルの電源電位VSSの供給を制御することができる。

**【0206】**

上記実施の形態に記載されているメモリセルにおいては、電源電圧の供給を停止した場合においてもデータを保持することが可能である。よって、メモリセル群1143を含むCPU全体に対する電源電圧の供給が適宜停止される場合であっても、当該CPUの動作が遅延することはない。具体的には、当該メモリセル群1143においては、電源電圧の供給が停止される期間に渡って所望のデータが保持される。そして、当該CPUは、電源電圧の供給が再開される際に当該保持されているデータを用いて即座に動作することが可能である。また、このようにCPUに対する電源電圧の供給を適宜停止することによって、消費電力の低減を図ることが可能である。

**【0207】**

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

**【0208】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

**【0209】**

(実施の形態5)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、デスクトップ型或いはノート型のパソコンコンピュータ、ワードプロセッサ、光ディスクなどの記録媒体に静止画または動画を記録、または再生する装置、オーディオプレイヤー、ラジオ、ステレオ、電話機、トランシーバ、携帯無線機、携帯電話、ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアーコンディショナーなどの空調設備、食器洗浄器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、煙感知器、放射線測定器、透析装置等の医療機器、などが挙げられる。さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレーター、産業用ロボット、電力貯蔵システム等の産業機器も挙げられる。また、内燃機関や電力を用いる電動機により推進する移動体なども、電子制御されるものは電子機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車(EV)、内燃機関と電動機を併せ持ったハイブリッド車(HEV)、プラグインハイブリッド車(PHEV)、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型または大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器の具体例の一部を図10乃至図12に示す。

**【0210】**

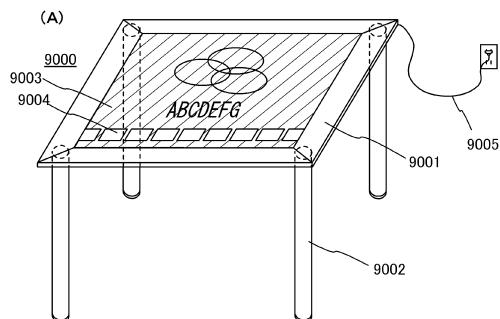

図10(A)は、表示部を有するテーブルを示している。テーブル9000は、筐体9001に表示部9003が組み込まれており、表示部9003により映像を表示することができる。なお、4本の脚部9002により筐体9001を支持した構成を示している。また、電力供給のための電源コード9005を筐体9001に有している。

**【0211】**

実施の形態1に示すトランジスタは、表示部9003に用いることが可能であり、電子機

10

20

30

40

50

器に高い信頼性を付与することができる。

**【0212】**

表示部9003は、タッチ入力機能を有しており、テーブル9000の表示部9003に表示された表示ボタン9004を指などで触れることで、画面操作や、情報を入力することができ、また他の家電製品との通信を可能とする、または制御を可能とすることで、画面操作により他の家電製品をコントロールする制御装置としてもよい。例えば、イメージセンサ機能を有する半導体装置を用いれば、表示部9003にタッチ入力機能を持たせることができる。

**【0213】**

また、筐体9001に設けられたヒンジによって、表示部9003の画面を床に対して垂直に立てる ALSO 10 こともでき、テレビジョン装置としても利用できる。狭い部屋においては、大きな画面のテレビジョン装置は設置すると自由な空間が狭くなってしまうが、テーブルに表示部が内蔵されれば、部屋の空間を有效地に利用することができる。

**【0214】**

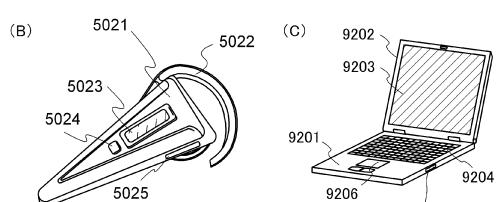

図10(B)は、オーディオプレイヤーであり、本体5021には表示部5023と、耳に装着するための固定部5022と、スピーカ、操作ボタン5024、外部メモリスロット5025等が設けられている。実施の形態1のトランジスタ、または実施の形態2に示したメモリを本体5021に内蔵されているメモリやCPUなどに適用することにより、より省電力化されたオーディオプレイヤーとすることができます。

**【0215】**

さらに、図10(B)に示すオーディオプレイヤーにアンテナやマイク機能や無線機能を持たせ、携帯電話と連携させれば、乗用車などを運転しながらワイヤレスによるハンズフリーでの会話も可能である。

**【0216】**

図10(C)はコンピュータであり、CPUを含む本体9201、筐体9202、表示部9203、キーボード9204、外部接続ポート9205、ポインティングデバイス9206等を含む。コンピュータは、その表示部9203に実施の形態1のトランジスタを用いることができる。また、実施の形態4に示したCPUを利用すれば、省電力化されたコンピュータとすることが可能となる。

**【0217】**

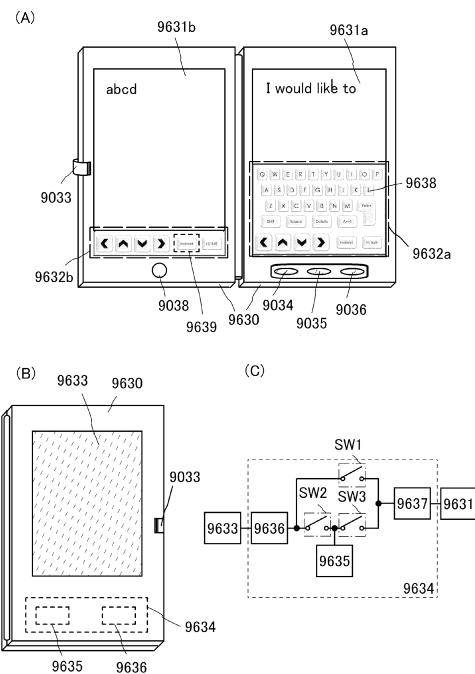

図11(A)および図11(B)は2つ折り可能なタブレット型端末である。図11(A)は、開いた状態であり、タブレット型端末は、筐体9630、表示部9631a、表示部9631b、表示モード切り替えスイッチ9034、電源スイッチ9035、省電力モード切り替えスイッチ9036、留め具9033、操作スイッチ9038、を有する。

**【0218】**

図11(A)および図11(B)に示すような携帯機器においては、画像データの一時記憶などにメモリが使用されている。例えば、実施の形態2、または実施の形態3に説明した半導体装置をメモリとして使用することができる。先の実施の形態で説明した半導体装置をメモリに採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

**【0219】**

また、表示部9631aは、一部をタッチパネルの領域9632aとすることができる、表示された操作キー9638にふれることでデータ入力をすることができる。なお、表示部9631aにおいては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが該構成に限定されない。表示部9631aの全ての領域がタッチパネルの機能を有する構成としても良い。例えば、表示部9631aの全面をキーボードボタン表示させてタッチパネルとし、表示部9631bを表示画面として用いることができる。

**【0220】**

また、表示部9631bにおいても表示部9631aと同様に、表示部9631bの一部

10

20

30

40

50

をタッチパネルの領域 9 6 3 2 b とすることができる。また、タッチパネルのキーボード表示切り替えボタン 9 6 3 9 が表示されている位置に指やスタイラスなどでふれることで表示部 9 6 3 1 b にキーボードボタン表示することができる。

#### 【 0 2 2 1 】

また、タッチパネルの領域 9 6 3 2 a とタッチパネルの領域 9 6 3 2 b に対して同時にタッチ入力することもできる。

#### 【 0 2 2 2 】

また、表示モード切り替えスイッチ 9 0 3 4 は、縦表示または横表示などの表示の向きの切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ 9 0 3 6 は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができます。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。10

#### 【 0 2 2 3 】

また、図 1 1 ( A ) では表示部 9 6 3 1 b と表示部 9 6 3 1 a の表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

#### 【 0 2 2 4 】

図 1 1 ( B ) は、閉じた状態であり、タブレット型端末は、筐体 9 6 3 0 、太陽電池 9 6 3 3 、充放電制御回路 9 6 3 4 、バッテリー 9 6 3 5 、D C D C コンバータ 9 6 3 6 を有する。なお、図 1 1 ( B ) では充放電制御回路 9 6 3 4 の一例としてバッテリー 9 6 3 5 、D C D C コンバータ 9 6 3 6 を有する構成について示している。20

#### 【 0 2 2 5 】

なお、タブレット型端末は 2 つ折り可能なため、未使用時に筐体 9 6 3 0 を閉じた状態にすることができる。したがって、表示部 9 6 3 1 a 、表示部 9 6 3 1 b を保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

#### 【 0 2 2 6 】

また、この他にも図 1 1 ( A ) および図 1 1 ( B ) に示したタブレット型端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作または編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。30

#### 【 0 2 2 7 】

タブレット型端末の表面に装着された太陽電池 9 6 3 3 によって、電力をタッチパネル、表示部、または映像信号処理部等に供給することができる。なお、太陽電池 9 6 3 3 は、筐体 9 6 3 0 の片面又は両面に設けることができ、バッテリー 9 6 3 5 の充電を効率的に行う構成とすることができます。なおバッテリー 9 6 3 5 としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

#### 【 0 2 2 8 】

また、図 1 1 ( B ) に示す充放電制御回路 9 6 3 4 の構成、および動作について図 1 1 ( C ) にブロック図を示し説明する。図 1 1 ( C ) には、太陽電池 9 6 3 3 、バッテリー 9 6 3 5 、D C D C コンバータ 9 6 3 6 、コンバータ 9 6 3 7 、スイッチ SW 1 乃至 SW 3 、表示部 9 6 3 1 について示しており、バッテリー 9 6 3 5 、D C D C コンバータ 9 6 3 6 、コンバータ 9 6 3 7 、スイッチ SW 1 乃至 SW 3 が、図 1 1 ( B ) に示す充放電制御回路 9 6 3 4 に対応する箇所となる。40

#### 【 0 2 2 9 】

まず外光により太陽電池 9 6 3 3 により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー 9 6 3 5 を充電するための電圧となるよう D C D C コンバータ 9 6 3 6 で昇圧または降圧がなされる。そして、表示部 9 6 3 1 の動作に太50

陽電池 9 6 3 3 からの電力が用いられる際にはスイッチ SW1 をオンにし、コンバータ 9 6 3 7 で表示部 9 6 3 1 に必要な電圧に昇圧または降圧をすることとなる。また、表示部 9 6 3 1 での表示を行わない際には、SW1 をオフにし、SW2 をオンにしてバッテリー 9 6 3 5 の充電を行う構成とすればよい。

#### 【 0 2 3 0 】

なお、太陽電池 9 6 3 3 については、発電手段の一例として示したが、特に限定されず、圧電素子（ピエゾ素子）や熱電変換素子（ペルティエ素子）などの他の発電手段によるバッテリー 9 6 3 5 の充電を行う構成であってもよい。例えば、無線（非接触）で電力を送受信して充電する無接点電力伝送モジュールや、また他の充電手段を組み合わせて行う構成としてもよい。

10

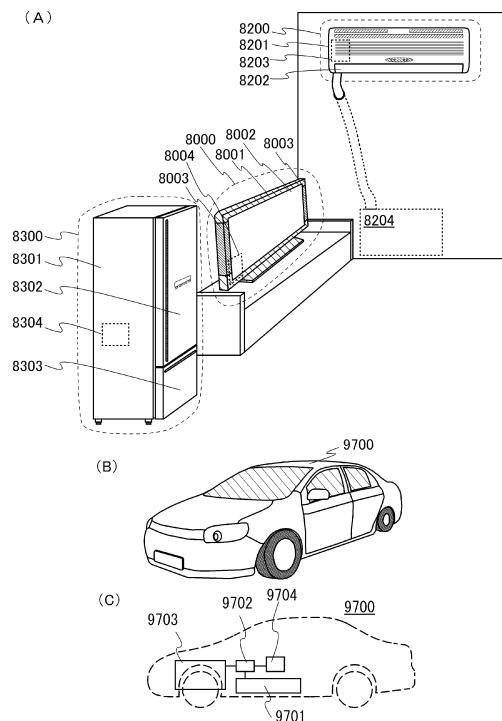

#### 【 0 2 3 1 】

図 12 ( A )において、テレビジョン装置 8 0 0 0 は、筐体 8 0 0 1 に表示部 8 0 0 2 が組み込まれており、表示部 8 0 0 2 により映像を表示し、スピーカ部 8 0 0 3 から音声を出力することが可能である。実施の形態 1 に示すトランジスタを用いて表示部 8 0 0 2 に用いることが可能である。

#### 【 0 2 3 2 】

表示部 8 0 0 2 は、液晶表示装置、有機 EL 素子などの発光素子を各画素に備えた発光装置、電気泳動表示装置、D M D ( D i g i t a l M i c r o m i r r o r D e v i c e ) 、P D P ( P l a s m a D i s p l a y P a n e l ) などの、半導体表示装置を用いることができる。

20

#### 【 0 2 3 3 】

テレビジョン装置 8 0 0 0 は、受信機やモデムなどを備えていてもよい。テレビジョン装置 8 0 0 0 は、受信機により一般的なテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

#### 【 0 2 3 4 】

また、テレビジョン装置 8 0 0 0 は、情報通信を行うための C P U や、メモリを備えていてもよい。テレビジョン装置 8 0 0 0 は、実施の形態 2 乃至 5 のいずれかに示すメモリや C P U を用いることが可能である。

30

#### 【 0 2 3 5 】

図 12 ( A )において、室内機 8 2 0 0 および室外機 8 2 0 4 を有するエアーコンディショナーは、実施の形態 4 の C P U を用いた電子機器の一例である。具体的に、室内機 8 2 0 0 は、筐体 8 2 0 1 、送風口 8 2 0 2 、C P U 8 2 0 3 等を有する。図 12 ( A )において、C P U 8 2 0 3 が、室内機 8 2 0 0 に設けられている場合を例示しているが、C P U 8 2 0 3 は室外機 8 2 0 4 に設けられていてもよい。或いは、室内機 8 2 0 0 と室外機 8 2 0 4 の両方に、C P U 8 2 0 3 が設けられていてもよい。実施の形態 4 に示した C P U は、酸化物半導体を用いた C P U であるため、耐熱性に優れており、信頼性の高いエアーコンディショナーを実現できる。

#### 【 0 2 3 6 】

図 12 ( A )において、電気冷凍冷蔵庫 8 3 0 0 は、酸化物半導体を用いた C P U を備える電子機器の一例である。具体的に、電気冷凍冷蔵庫 8 3 0 0 は、筐体 8 3 0 1 、冷蔵室用扉 8 3 0 2 、冷凍室用扉 8 3 0 3 、C P U 8 3 0 4 等を有する。図 12 ( A )では、C P U 8 3 0 4 が、筐体 8 3 0 1 の内部に設けられている。実施の形態 4 に示した C P U を電気冷凍冷蔵庫 8 3 0 0 の C P U 8 3 0 4 に用いることによって省電力化が図れる。

40

#### 【 0 2 3 7 】

図 12 ( B )において、電子機器の一例である電気自動車の例を示す。図 12 ( C )は、該電気自動車の内部に関する図である。電気自動車 9 7 0 0 には、二次電池 9 7 0 1 が搭載されている。二次電池 9 7 0 1 の電力は、制御回路 9 7 0 2 により出力が調整されて、駆動装置 9 7 0 3 に供給される。制御回路 9 7 0 2 は、図示しない R O M 、R A M 、C P

50

U等を有する処理装置9704によって制御される。実施の形態2乃至5のいずれかに示すメモリやCPUを電気自動車9700に用いることによって省電力化が図れる。

#### 【0238】

駆動装置9703は、直流電動機若しくは交流電動機単体、または電動機と内燃機関と、を組み合わせて構成される。処理装置9704は、電気自動車9700の運転者の操作情報（加速、減速、停止など）や走行時の情報（上り坂や下り坂等の情報、駆動輪にかかる負荷情報など）の入力情報に基づき、制御回路9702に制御信号を出力する。制御回路9702は、処理装置9704の制御信号により、二次電池9701から供給される電気エネルギーを調整して駆動装置9703の出力を制御する。交流電動機を搭載している場合は、図示していないが、直流を交流に変換するインバータも内蔵される。

10

#### 【0239】

なお、上記に例示した電子機器は、太陽電池、圧電素子、熱電変換素子、および／または無接点電力伝送モジュールなどの電力供給手段により、直接電力が供給される構成を有していてもよい。また、蓄電装置を介して電力が供給される構成を有していてもよい。

#### 【0240】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0241】

<参考例1>

本明細書で開示されるトランジスタの構造は、チャネル形成領域がC A A C - O S 膜で形成されるトランジスタの構造として有用である。以下、C A A C - O S 膜では、横方向に酸素が拡散しやすい点について詳述する。

20

#### 【0242】

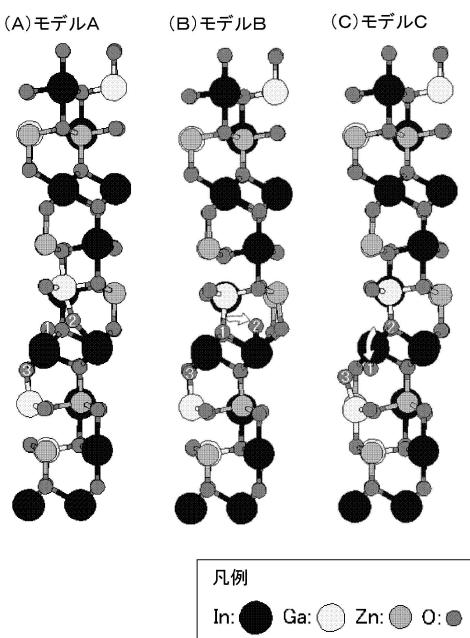

ここでは、酸化物半導体膜の一例として、In-Ga-Zn系酸化物（以下、IGZOと呼ぶ。）膜における、過剰酸素（化学量論比を越えて存在している酸素原子）および酸素欠損の動きやすさについて、科学技術計算結果を参照して説明する。

#### 【0243】

なお、計算は、原子数比がIn:Ga:Zn = 3:1:2となるIGZOのIn-O面に過剰酸素または酸素欠損が一つ存在するモデルを構造最適化によって作成（図13（A）乃至（C）および図15（A）乃至（C）を参照）し、NEB（N u d g e d E l a s t i c B a n d）法を用いて最小エネルギー経路に沿った中間構造に対するエネルギーをそれぞれ算出した。

30

#### 【0244】

計算は、密度汎関数理論（DFT）に基づく計算プログラムソフト「OpenMX」を用いて行った。パラメータについて以下に説明する。

#### 【0245】

基底関数には、擬原子局在基底関数を用いた。この基底関数は、分極基底系S T O（S later Type Orbital）に分類される。

#### 【0246】

汎関数には、GGA/PBE（Generalized-Gradient-Approximation/Perdew-Burke-Ernzerhof）を用いた。

40

#### 【0247】

カットオフエネルギーは200 Ryとした。

#### 【0248】

サンプリングk点は、 $5 \times 5 \times 3$ とした。

#### 【0249】

過剰酸素の動きやすさについての計算では、計算モデル内に存在する原子の数を85個とし、酸素欠損の動きやすさについての計算では、計算モデル内に存在する原子の数を83個とした。

#### 【0250】

50

過剰酸素または酸素欠損の動きやすさは、過剰酸素または酸素欠損が各々のサイトへ移動する際に越えることを要するエネルギーbarriaの高さ  $E_b$  を計算することにより評価する。すなわち、移動に際して越えるエネルギーbarriaの高さ  $E_b$  が高ければ移動しにくく、エネルギーbarriaの高さ  $E_b$  が低ければ移動しやすい。

#### 【0251】

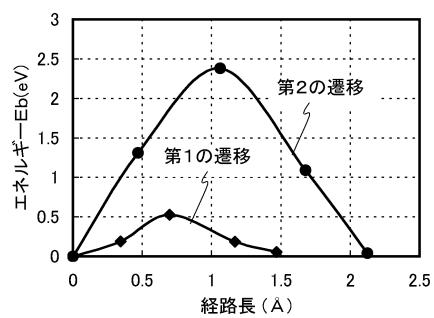

まず、過剰酸素の移動について説明する。過剰酸素の移動の計算に用いたモデルを図13に示す。なお、モデルの縦方向が結晶軸のc軸である。計算は、以下の2つの遷移形態について行った。計算結果は、図14に示す。図14では、横軸を（過剰酸素の移動の）経路長とし、縦軸を図13(A)のモデルAの状態のエネルギーに対する（移動に要する）エネルギーとしている。

10

#### 【0252】

過剰酸素の移動について、上記2つの遷移形態のうち、第1の遷移は、モデルAからモデルBへの遷移である。第2の遷移は、モデルAからモデルCへの遷移である。

#### 【0253】

なお、図13(A)乃至(C)中の”1”と表記されている酸素原子をモデルAの第1の酸素原子と呼ぶ。図13(A)乃至(C)中の”2”と表記されている酸素原子をモデルAの第2の酸素原子と呼ぶ。図13(A)乃至(C)中の”3”と表記されている酸素原子をモデルAの第3の酸素原子と呼ぶ。

#### 【0254】

図14から明らかなように、第1の遷移のエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) は、0.53eVであり、第2の遷移のエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) は、2.38eVである。そのため、第1の遷移では第2の遷移よりもエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) が低い。そのため、第1の遷移に要するエネルギーは第2の遷移に要するエネルギーよりも小さく、第1の遷移のほうが第2の遷移よりも起こりやすいといえる。

20

#### 【0255】

すなわち、モデルAの第1の酸素原子の移動は、モデルAの第3の酸素原子を押し出す方向よりも、モデルAの第2の酸素原子を押し出す方向に移動しやすいといえる。したがって、酸素原子はインジウム原子の層を横断して移動するよりもインジウム原子の層に沿つて移動しやすいといえる。

30

#### 【0256】

次に、酸素欠損の移動について説明する。酸素欠損の移動の計算に用いたモデルを図15に示す。計算は、以下の2つの遷移形態について行った。計算結果は、図16に示す。図16では、横軸を（酸素欠損の移動の）経路長とし、縦軸を図15(A)のモデルAの状態のエネルギーに対する（移動に要する）エネルギーとしている。

#### 【0257】

酸素欠損の移動について、上記2つの遷移形態のうち、第1の遷移は、モデルAからモデルBへの遷移である。第2の遷移は、モデルAからモデルCへの遷移である。

#### 【0258】

なお、図15(A)乃至(C)中の点線で描画している丸は、酸素欠損を表している。

40

#### 【0259】

図16から明らかなように、第1の遷移のエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) は、1.81eVであり、第2の遷移のエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) は、4.10eVである。そのため、第1の遷移では第2の遷移よりもエネルギーbarriaの高さ  $E_b$  の最大値 ( $E_{b_{max}}$ ) が低い。そのため、第1の遷移に要するエネルギーは第2の遷移に要するエネルギーよりも小さく、第1の遷移のほうが第2の遷移よりも起こりやすいといえる。

#### 【0260】

すなわち、モデルAの酸素欠損はモデルCの酸素欠損の位置よりも、モデルBの酸素欠損の位置のほうが移動しやすいといえる。したがって、酸素欠損もインジウム原子の層を横

50

断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。

#### 【0261】

次に、前述した4つの遷移形態の起こりやすさを別の側面から比較するために、これらの遷移の温度依存性について説明する。前述した4つの遷移形態は、(1)過剰酸素の第1の遷移 (2)過剰酸素の第2の遷移 (3)酸素欠損の第1の遷移 (4)酸素欠損の第2の遷移の4つである。

#### 【0262】

これらの遷移の温度依存性は、単位時間あたりの移動頻度により比較する。ここで、ある温度T(K)における移動頻度Z( /秒)は、化学的に安定な位置における酸素原子の振動数Z<sub>0</sub>( /秒)を用いると、以下の式(1)で表される。

#### 【0263】

##### 【数1】

$$Z = Z_0 \cdot \exp\left(-\frac{E b_{\max}}{kT}\right) \quad (1)$$

#### 【0264】

なお、式(1)において、E b<sub>m a x</sub>は各遷移におけるエネルギー障壁の高さE bの最大値であり、kはボルツマン定数である。また、Z<sub>0</sub> = 1.0 × 10<sup>-3</sup>( /秒)を計算に用いる。

#### 【0265】

過剰酸素または酸素欠損が1秒間あたりに1度だけエネルギー障壁の高さE bの最大値(E b<sub>m a x</sub>)を越えて移動する場合(Z = 1( /秒)の場合)、Tについて式(1)を解くと以下の通りである。

- |                |                             |

|----------------|-----------------------------|

| (1) 過剰酸素の第1の遷移 | Z = 1において T = 206 K (-67)   |

| (2) 過剰酸素の第2の遷移 | Z = 1において T = 923 K (650)   |

| (3) 酸素欠損の第1の遷移 | Z = 1において T = 701 K (428)   |

| (4) 酸素欠損の第2の遷移 | Z = 1において T = 1590 K (1317) |

#### 【0266】

一方、T = 300 K (27)の場合のZは、以下の通りである。

- |                |                                                  |

|----------------|--------------------------------------------------|

| (1) 過剰酸素の第1の遷移 | T = 300 Kにおいて Z = 1.2 × 10 <sup>-4</sup> ( /秒)   |

| (2) 過剰酸素の第2の遷移 | T = 300 Kにおいて Z = 1.0 × 10 <sup>-2.7</sup> ( /秒) |

| (3) 酸素欠損の第1の遷移 | T = 300 Kにおいて Z = 4.3 × 10 <sup>-1.8</sup> ( /秒) |

| (4) 酸素欠損の第2の遷移 | T = 300 Kにおいて Z = 1.4 × 10 <sup>-5.6</sup> ( /秒) |

#### 【0267】

また、T = 723 K (450)の場合のZは、以下の通りである。

- |                |                                                  |

|----------------|--------------------------------------------------|

| (1) 過剰酸素の第1の遷移 | T = 723 Kにおいて Z = 2.0 × 10 <sup>-9</sup> ( /秒)   |

| (2) 過剰酸素の第2の遷移 | T = 723 Kにおいて Z = 2.5 × 10 <sup>-4</sup> ( /秒)   |

| (3) 酸素欠損の第1の遷移 | T = 723 Kにおいて Z = 2.5( /秒)                       |

| (4) 酸素欠損の第2の遷移 | T = 723 Kにおいて Z = 2.5 × 10 <sup>-1.6</sup> ( /秒) |

#### 【0268】

上記計算結果に鑑みると、過剰酸素は、T = 300 KにおいてもT = 723 Kにおいても、インジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。また、酸素欠損も、T = 300 KにおいてもT = 723 Kにおいても、インジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。

#### 【0269】

また、T = 300 Kにおいて、インジウム原子の層に沿った過剰酸素の移動は非常に起こりやすいが、他の遷移形態は起こりにくい。T = 723 Kにおいては、インジウム原子の層に沿う過剰酸素の移動のみならず、インジウム原子の層に沿う酸素欠損の移動も起こりやすいが、過剰酸素についても酸素欠損についてもインジウム原子の層を横断する移動は

困難である。

【0270】

したがって、例えば C A A C - O S 膜のように、インジウム原子の層が当該膜の被形成面または表面に平行な面上に存在する場合には、過剰酸素および酸素欠損のいずれも当該膜の被形成面または表面に沿って移動しやすいといえる。

【0271】

以上説明したように、C A A C - O S 膜では当該膜の被形成面または表面に沿って過剰酸素は移動しやすい。したがって、トランジスタのチャネル形成領域が C A A C - O S 膜である場合、チャネル形成領域に対して縦方向（下地絶縁膜およびゲート絶縁膜）からよりも、横方向（ソース領域およびドレイン領域）からの方が酸素が拡散しやすいといえる。

10

【0272】

なお、上述した説明では過剰酸素または酸素欠損がインジウム原子の層を横断する場合について説明したが、酸化物半導体膜に含まれるインジウム以外の金属についても同様である。

【符号の説明】

【0273】

|       |                |    |

|-------|----------------|----|

| 100   | 基板             | 20 |

| 101   | 酸素             |    |

| 110   | 下地絶縁膜          |    |

| 120   | 酸化物半導体層        |    |

| 120 a | チャネル形成領域       |    |

| 120 b | ソース領域またはドレイン領域 |    |

| 120 c | 領域             |    |

| 130   | ゲート絶縁膜         |    |

| 140   | ゲート電極          |    |

| 150 a | ソース電極          |    |

| 150 b | ドレイン電極         |    |

| 160   | 保護膜            |    |

| 170   | 平坦化膜           |    |

| 191   | トランジスタ         | 30 |

| 192   | トランジスタ         |    |

| 193   | トランジスタ         |    |

| 114 1 | スイッチング素子       |    |

| 114 2 | メモリセル          |    |

| 114 3 | メモリセル群         |    |

| 118 9 | R O M インターフェイス |    |

| 119 0 | 基板             |    |

| 119 1 | A L U          |    |

| 119 2 | A L U コントローラ   | 40 |

| 119 3 | インストラクションデコーダ  |    |

| 119 4 | インターフラプトコントローラ |    |

| 119 5 | タイミングコントローラ    |    |

| 119 6 | レジスタ           |    |

| 119 7 | レジスタコントローラ     |    |

| 119 8 | バスインターフェイス     |    |

| 119 9 | R O M          |    |

| 300 0 | 基板             |    |

| 310 6 | 素子分離絶縁層        |    |

| 320 0 | トランジスタ         |    |

| 320 2 | トランジスタ         | 50 |

|           |             |    |

|-----------|-------------|----|

| 3 2 0 4   | 容量素子        |    |

| 3 2 1 0   | 接続配線        |    |

| 3 2 2 0   | 絶縁層         |    |

| 4 1 6 2   | トランジスタ      |    |

| 4 2 5 0   | メモリセル       |    |

| 4 2 5 1   | メモリセルアレイ    |    |

| 4 2 5 1 a | メモリセルアレイ    |    |

| 4 2 5 1 b | メモリセルアレイ    |    |

| 4 2 5 3   | 周辺回路        |    |

| 4 2 5 4   | 容量素子        | 10 |

| 5 0 2 1   | 本体          |    |

| 5 0 2 2   | 固定部         |    |

| 5 0 2 3   | 表示部         |    |

| 5 0 2 4   | 操作ボタン       |    |

| 5 0 2 5   | 外部メモリスロット   |    |

| 8 0 0 0   | テレビジョン装置    |    |

| 8 0 0 1   | 筐体          |    |

| 8 0 0 2   | 表示部         |    |

| 8 0 0 3   | スピーカ部       |    |

| 8 2 0 0   | 室内機         | 20 |

| 8 2 0 1   | 筐体          |    |

| 8 2 0 2   | 送風口         |    |

| 8 2 0 3   | C P U       |    |

| 8 2 0 4   | 室外機         |    |

| 8 3 0 0   | 電気冷凍冷蔵庫     |    |

| 8 3 0 1   | 筐体          |    |

| 8 3 0 2   | 冷蔵室用扉       |    |

| 8 3 0 3   | 冷凍室用扉       |    |

| 8 3 0 4   | C P U       |    |

| 9 0 0 0   | テーブル        | 30 |

| 9 0 0 1   | 筐体          |    |

| 9 0 0 2   | 脚部          |    |

| 9 0 0 3   | 表示部         |    |

| 9 0 0 4   | 表示ボタン       |    |

| 9 0 0 5   | 電源コード       |    |

| 9 0 3 3   | 留め具         |    |

| 9 0 3 4   | スイッチ        |    |

| 9 0 3 5   | 電源スイッチ      |    |

| 9 0 3 6   | スイッチ        |    |

| 9 0 3 8   | 操作スイッチ      | 40 |

| 9 2 0 1   | 本体          |    |

| 9 2 0 2   | 筐体          |    |

| 9 2 0 3   | 表示部         |    |

| 9 2 0 4   | キーボード       |    |

| 9 2 0 5   | 外部接続ポート     |    |

| 9 2 0 6   | ポインティングデバイス |    |

| 9 6 3 0   | 筐体          |    |

| 9 6 3 1   | 表示部         |    |

| 9 6 3 1 a | 表示部         |    |

| 9 6 3 1 b | 表示部         | 50 |

|           |               |

|-----------|---------------|

| 9 6 3 2 a | 領域            |

| 9 6 3 2 b | 領域            |

| 9 6 3 3   | 太陽電池          |

| 9 6 3 4   | 充放電制御回路       |

| 9 6 3 5   | バッテリー         |

| 9 6 3 6   | D C D C コンバータ |

| 9 6 3 7   | コンバータ         |

| 9 6 3 8   | 操作キー          |

| 9 6 3 9   | ボタン           |

| 9 7 0 0   | 電気自動車         |

| 9 7 0 1   | 二次電池          |

| 9 7 0 2   | 制御回路          |

| 9 7 0 3   | 駆動装置          |

| 9 7 0 4   | 処理装置          |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【図15】

|     |   |     |   |

|-----|---|-----|---|

| 凡例  |   |     |   |

| In: | ● | Ga: | ○ |

| Zn: | ● | O:  | ● |

【図16】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 27/105 (2006.01) | H 01 L 27/10 3 2 1   |

| H 01 L 29/788 (2006.01) | H 01 L 27/10 4 4 1   |

| H 01 L 29/792 (2006.01) | H 01 L 27/10 6 7 1 Z |

|                         | H 01 L 29/78 3 7 1   |

審査官 市川 武宜

(56)参考文献 特表2009-528670 (JP, A)

特開2007-073705 (JP, A)

特開2007-220816 (JP, A)

特開2011-159697 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

H 01 L 21 / 336

H 01 L 21 / 8242

H 01 L 27 / 105

H 01 L 27 / 108

H 01 L 27 / 115

H 01 L 29 / 788

H 01 L 29 / 792