(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7529897号**

**(P7529897)**

(45)発行日 令和6年8月6日(2024.8.6)

(24)登録日 令和6年7月29日(2024.7.29)

(51)国際特許分類

**G 0 5 B 19/05 (2006.01)**

F I

G 0 5 B

19/05

L

請求項の数 7 (全12頁)

|                   |                             |          |                                                          |

|-------------------|-----------------------------|----------|----------------------------------------------------------|

| (21)出願番号          | 特願2023-509008(P2023-509008) | (73)特許権者 | 390008235<br>ファナック株式会社<br>山梨県南都留郡忍野村忍草字古馬場 3 5<br>8 0 番地 |

| (86)(22)出願日       | 令和4年3月11日(2022.3.11)        | (74)代理人  | 110003683<br>弁理士法人桐朋                                     |

| (86)国際出願番号        | PCT/JP2022/010775           | (72)発明者  | 佐伯 正博<br>山梨県南都留郡忍野村忍草字古馬場 3 5<br>8 0 番地 ファナック株式会社内       |

| (87)国際公開番号        | WO2022/202388               | (72)発明者  | 桑畠 真一<br>山梨県南都留郡忍野村忍草字古馬場 3 5<br>8 0 番地 ファナック株式会社内       |

| (87)国際公開日         | 令和4年9月29日(2022.9.29)        | (72)発明者  | 前田 翌檜<br>山梨県南都留郡忍野村忍草字古馬場 3 5<br>8 0 番地 ファナック株式会社内       |

| 審査請求日             | 令和5年10月10日(2023.10.10)      |          |                                                          |

| (31)優先権主張番号       | 特願2021-50003(P2021-50003)   |          |                                                          |

| (32)優先日           | 令和3年3月24日(2021.3.24)        |          |                                                          |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |          |                                                          |

最終頁に続く

(54)【発明の名称】 I / O ユニット、マスターユニットおよび通信システム

**(57)【特許請求の範囲】****【請求項 1】**

マスターユニット(12、14)と機器(104)とを接続し、前記マスターユニットと前記機器との間で信号を伝送するI / O ユニット(16)であって、

前段に設けられるマスターユニットまたは前段に設けられる他のI / O ユニットと接続するための前段側本流端子(34)および前段側支流端子(36)と、

前記前段側支流端子に接続され、後段に設けられる他のI / O ユニット(16)と接続するための後段側支流端子(38)と、

前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路(30)と、

前記前段側本流端子に接続され、後段に設けられる他の前記I / O ユニット、または後段に設けられる前記マスターユニットと接続するための後段側本流端子(40)と、

を備える、I / O ユニット。

**【請求項 2】**

請求項1に記載のI / O ユニットであって、

前記後段側支流端子が後段に設けられる他の前記I / O ユニットの前記前段側支流端子と接続されることで、複数の前記スレーブ処理回路をデイジーチェーン接続する、I / O ユニット。

**【請求項 3】**

請求項1または2に記載のI / O ユニットであって、

前記前段側本流端子が前段側に設けられた前記マスターユニットのマスター処理回路(18)に接続され、前記後段側本流端子が後段側に設けられたマスターユニット(14)のマスター処理回路(18)に接続されることで、複数の前記マスター処理回路をデイジーチェーン接続する、I/Oユニット。

#### 【請求項4】

請求項1～3のいずれか1項に記載のI/Oユニットであって、前記スレーブ処理回路と前記機器とを接続し、前記スレーブ処理回路が前記機器と信号の入出力を行うためのインターフェース(32)をさらに備える、I/Oユニット。

#### 【請求項5】

マスター処理回路(18)を有し、I/Oユニット(16)を介して、前記I/Oユニットに接続された機器(104)と信号を伝送するマスターユニット(14)であって、

前記マスター処理回路と、前段に設けられる前記I/Oユニットを介して前段側に位置するマスター処理回路とを接続するための第1本流端子(44)と、

前記マスター処理回路と、後段に設けられるI/Oユニットを介して後段側に位置するマスター処理回路とを接続するための第2本流端子(24)と、

後段に設けられた前記I/Oユニットと接続するための支流端子(26)と、を備える、マスターユニット。

#### 【請求項6】

マスターユニット(12、14)と、前記マスターユニットと機器(104)との間で信号を伝送するI/Oユニット(16)とを有する通信システム(10)であって、

前記I/Oユニットは、

前段に設けられる前記マスターユニットまたは前段に設けられる他のI/Oユニット(16)と接続するための前段側本流端子(34)および前段側支流端子(36)と、

前記前段側支流端子に接続され、後段に設けられる他のI/Oユニット(16)と接続するための後段側支流端子(38)と、

前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路(30)と、

前記前段側本流端子に接続され、後段に設けられる他の前記I/Oユニット、または後段に設けられるマスターユニット(14)と接続するための後段側本流端子(40)と、

を備え、

前記マスターユニットは、

前段に設けられた前記I/Oユニットの前記後段側本流端子に接続される第1本流端子(44)と、

後段に設けられる前記I/Oユニットの前記前段側本流端子に接続される第2本流端子(24)と、

後段に設けられる前記I/Oユニットの前記前段側支流端子に接続される支流端子(26)と、

前記第1本流端子、前記第2本流端子および前記支流端子に接続され、信号処理を行うマスター処理回路(18)と、

を備える、通信システム。

#### 【請求項7】

請求項6に記載の通信システムであって、

前記I/Oユニットは、前記スレーブ処理回路と前記機器とを接続し、前記スレーブ処理回路が前記機器と信号の入出力を行うためのインターフェース(32)をさらに備える、通信システム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、I/Oユニットと、I/Oユニットを介して機器と信号を伝送するマスターユニットと、そのI/Oユニットとマスターユニットとを有する通信システムとに関する。

10

20

30

40

50

**【背景技術】****【0002】**

特開2016-110460号公報には、プログラマブル・ロジック・コントローラシステムが開示されている。このプログラマブル・ロジック・コントローラシステムは、基本ユニット（マスター）と、複数の拡張ユニット（スレーブ）とを有する。基本ユニットと、複数の拡張ユニットとは、マスターユニットを先頭にして、デイジーチェーン接続される。複数の拡張ユニットの各々は、例えばI/Oユニットである。基本ユニットは、複数の拡張ユニットを介して、被制御装置に信号を送受信する。被制御装置は、例えばセンサ、またはアクチュエータである。

**【発明の概要】****【0003】**

マスターユニットと複数のI/Oユニットとは、マスターユニットを先頭にして所定の設置方向に沿って並べられる。隣り合うマスターユニットの端子と、I/Oユニットの端子とが接続される。また、隣り合うI/Oユニット同士の端子が互いに接続される。これにより、ケーブル等を別途必要とすることなく、マスターユニットと、複数のI/Oユニットとは、通信可能に接続される。以下において、通信可能に接続されたマスターユニットと複数のI/Oユニットとからなる塊は、「ステーション」とも記載される。

**【0004】**

1つのマスターユニットの後段に接続可能（通信可能）なI/Oユニットの台数には、制限がある。したがって、オペレータは、制限台数を超えた台数のI/Oユニットを使用したい場合には、ステーションを別途用意し、ケーブル等を用いて、各ステーションのマスターユニットを接続しなければならない。

**【0005】**

したがって、従来は、制限台数を超えた台数のI/Oユニットを1つのステーションにすることが困難であった。

**【0006】**

本発明は、上述した課題を解決することを目的とする。

**【0007】**

本発明の第1の態様は、マスターユニットと機器とを接続し、前記マスターユニットと前記機器との間で信号を伝送するI/Oユニットであって、前段に設けられるマスターユニットまたは前段に設けられる他のI/Oユニットと接続するための前段側本流端子および前段側支流端子と、前記前段側支流端子に接続され、後段に設けられる他のI/Oユニットと接続するための後段側支流端子と、前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路と、前記前段側本流端子に接続され、後段に設けられる他の前記I/Oユニット、または後段に設けられるマスターユニットと接続するための後段側本流端子と、を備える。

**【0008】**

本発明の第2の態様は、マスター処理回路を有し、I/Oユニットを介して、前記I/Oユニットに接続された機器と信号を伝送するマスターユニットであって、前記マスター処理回路と、前段に設けられる前記I/Oユニットを介して前段側に位置するマスター処理回路とを接続するための第1本流端子と、前記マスター処理回路と、後段に設けられるI/Oユニットを介して後段側に位置するマスター処理回路とを接続するための第2本流端子と、後段に設けられた前記I/Oユニットと接続するための支流端子と、を備える。

**【0009】**

本発明の第3の態様は、マスターユニットと、前記マスターユニットと機器との間で信号を伝送するI/Oユニットとを有する通信システムであって、前記I/Oユニットは、前段に設けられる前記マスターユニットまたは前段に設けられる他のI/Oユニットと接続するための前段側本流端子および前段側支流端子と、前記前段側支流端子に接続され、後段に設けられる他のI/Oユニットと接続するための後段側支流端子と、前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路と、前記前

10

20

30

40

50

段側本流端子に接続され、後段に設けられる他の前記 I / O ユニット、または後段に設けられるマスターユニットと接続するための後段側本流端子と、を備え、前記マスターユニットは、前段に設けられた前記 I / O ユニットの前記後段側本流端子に接続される第 1 本流端子と、後段に設けられる前記 I / O ユニットの前記前段側本流端子に接続される第 2 本流端子と、後段に設けられる前記 I / O ユニットの前記前段側支流端子に接続される支流端子と、前記第 1 本流端子、前記第 2 本流端子および前記支流端子に接続され、信号処理を行うマスター処理回路と、を備える。

#### 【 0 0 1 0 】

本発明の態様によれば、1つのステーション内で増設が可能な I / O ユニットが提供される。また、1つのステーション内での I / O ユニットの増設を可能にするマスターユニットが提供される。さらに、これらの I / O ユニットとマスターユニットとを有する通信システムが提供される。10

#### 【 図面の簡単な説明 】

#### 【 0 0 1 1 】

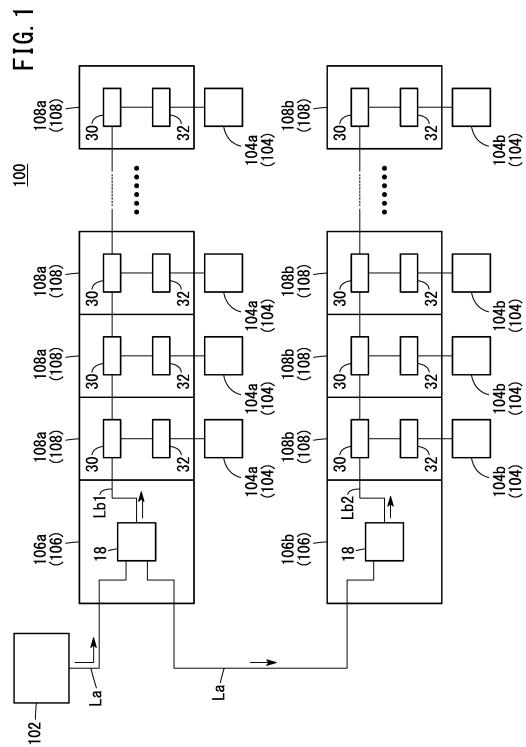

【図 1】図 1 は、本発明の参考例に係る通信システムを表す図である。

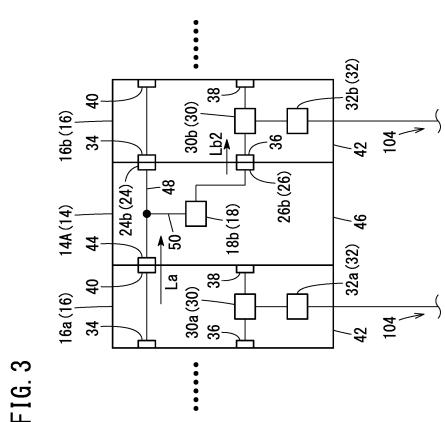

【図 2】図 2 は、本発明の実施形態に係る通信システムを表す図である。

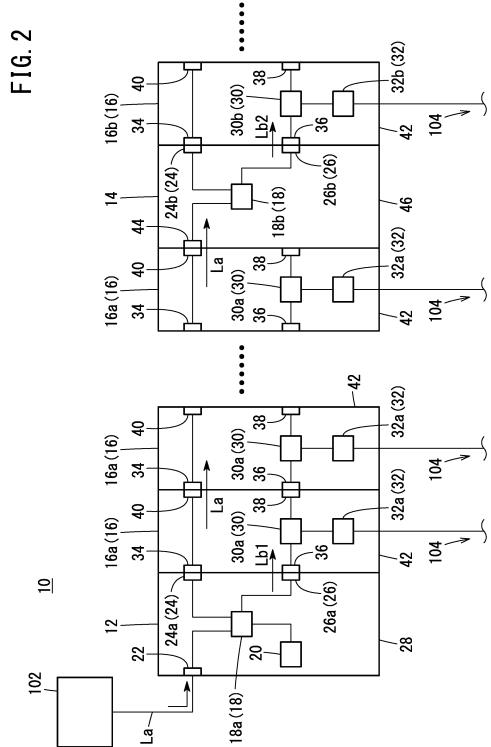

【図 3】図 3 は、変形例 1 に係るインターフェースユニットを表す図である。

#### 【 発明を実施するための形態 】

#### 【 0 0 1 2 】

本発明の I / O ユニットと、マスターユニットと、通信システムとについて、好適な実施の形態を掲げ、添付の図面を参照しながら以下、詳細に説明する。20

#### 【 0 0 1 3 】

##### [ 実施の形態 ]

図 1 は、本発明の参考例に係る通信システム 1 0 0 を表す図である。

#### 【 0 0 1 4 】

通信システム 1 0 0 は、制御装置 1 0 2 と機器 1 0 4 との間で信号を伝送するシステムである。機器 1 0 4 は、機械装置に設けられる。機械装置は、例えば工作機械、またはロボットである。機器 1 0 4 は、出力機器 1 0 4 a と、入力機器 1 0 4 b とを含む。出力機器 1 0 4 a は、例えば、スイッチ等のアクチュエータである。制御装置 1 0 2 は、出力機器 1 0 4 a を駆動させる場合は、通信システム 1 0 0 を介して、出力機器 1 0 4 a に制御信号を送る。入力機器 1 0 4 b は、例えば押圧、電圧、または電流等を検出するセンサである。制御装置 1 0 2 は、入力機器 1 0 4 b からの検出信号を、通信システム 1 0 0 を介して取得する。30

#### 【 0 0 1 5 】

通信システム 1 0 0 は、複数の通信カプラユニット 1 0 6 ( 1 0 6 a, 1 0 6 b ) と、複数の I / O ユニット 1 0 8 とを有する。複数の I / O ユニット 1 0 8 は、複数の I / O ユニット 1 0 8 a と、複数の I / O ユニット 1 0 8 b とからなる。

#### 【 0 0 1 6 】

制御装置 1 0 2 と、通信カプラユニット 1 0 6 a と、通信カプラユニット 1 0 6 b とは、この順序で順次接続される。これにより、制御装置 1 0 2 と、通信カプラユニット 1 0 6 a と、通信カプラユニット 1 0 6 b とをこの順序で辿る通信路（本流線 L a ）が構成される。制御装置 1 0 2 と通信カプラユニット 1 0 6 a との接続は、ケーブルを用いて行われる。また、通信カプラユニット 1 0 6 a と通信カプラユニット 1 0 6 b との接続は、別のケーブルを用いて行われる。ケーブルは、オペレータが用意する。40

#### 【 0 0 1 7 】

複数の I / O ユニット 1 0 8 a は、通信カプラユニット 1 0 6 a の後段に順次接続される。これにより、通信カプラユニット 1 0 6 a と、複数の I / O ユニット 1 0 8 a とは、1つのステーションを構成する。また、通信カプラユニット 1 0 6 a と、複数の I / O ユニット 1 0 8 a とを順に辿る通信路（支流線 L b 1 ）が構成される。

#### 【 0 0 1 8 】

複数の I / O ユニット 108b は、通信カプラユニット 106b の後段に順次接続される。これにより、通信カプラユニット 106b と、複数の I / O ユニット 108b とは、1 つのステーションを構成する。また、通信カプラユニット 106b と、複数の I / O ユニット 108b とを順に辿る通信路（支流線 Lb2）が構成される。

#### 【0019】

複数の I / O ユニット 108 は、複数の機器 104 と接続される。図 1 の複数の I / O ユニット 108 は、互いに異なる機器 104 と接続される。ただし、1 つの I / O ユニット 108 に、複数の機器 104 が接続されてもよい。

#### 【0020】

通信カプラユニット 106a と、通信カプラユニット 106b との各々は、マスター処理回路 18 を有する。I / O ユニット 108a と、I / O ユニット 108b との各々は、スレーブ処理回路 30 と、インターフェース 32 とを有する。スレーブ処理回路 30 は、マスター処理回路 18 と信号の入出力を行う回路である。マスター処理回路 18 とスレーブ処理回路 30 との各々は、例えば CPU（中央処理装置）を含む。ただし、マスター処理回路 18 とスレーブ処理回路 30 との各々は、例えば ASIC（特定用途向け集積回路）、PLD（プログラマブルロジックデバイス）、または、FPGA（フィールドプログラマブルロジックゲートアレー）等を含んでもよい。インターフェース 32 は、スレーブ処理回路 30 と機器 104 との間で信号を伝送するハードウェア（回路、電子部品群）である。インターフェース 32 は、スレーブ処理回路 30 と機器 104 とを接続し、スレーブ処理回路 30 が機器 104 と信号の入出力を行う。なお、インターフェース 32 の具体的な構成は、機器 104 の種類に応じて異なる。

10

20

#### 【0021】

通信カプラユニット 106a のマスター処理回路 18 と、通信カプラユニット 106b のマスター処理回路 18 とは、本流線 La によって、制御装置 102 を先頭にしてデイジーチェーン接続される。また、複数の I / O ユニット 108a のスレーブ処理回路 30 は、支流線 Lb1 によって、通信カプラユニット 106a のマスター処理回路 18 を先頭にしてデイジーチェーン接続される。さらに、複数の I / O ユニット 108b のスレーブ処理回路 30 は、支流線 Lb2 によって、通信カプラユニット 106b のマスター処理回路 18 を先頭にしてデイジーチェーン接続される。

#### 【0022】

30

制御装置 102 が機器 104 に制御信号を送る場合、制御装置 102 は、自分から見て初段（1 番目）に接続された通信カプラユニット 106a に制御信号を出力する。この制御信号は、送り先の機器 104 が接続された I / O ユニット 108 のアドレス情報等を含む。通信カプラユニット 106a のマスター処理回路 18 は、制御信号に含まれるアドレス情報が、複数の I / O ユニット 108a のいずれかを示しているかを判断する。アドレス情報が複数の I / O ユニット 108a のいずれかを示さない場合、通信カプラユニット 106a のマスター処理回路 18 は、通信カプラユニット 106b のマスター処理回路 18 に制御信号を出力する。アドレス情報が複数の I / O ユニット 108a のいずれかを示す場合、通信カプラユニット 106a のマスター処理回路 18 は、自身の後段の I / O ユニット 108a に制御信号を出力する。前段から制御信号を入力された I / O ユニット 108a のスレーブ処理回路 30 は、入力された制御信号に含まれるアドレス情報が自身を示すかを判断する。ここで、I / O ユニット 108a のスレーブ処理回路 30 は、アドレス情報が自身を示す場合、自身に接続された機器 104 に制御信号を出力する。これにより、機器 104 が動作する。その一方で、I / O ユニット 108a は、入力された制御信号に含まれるアドレス情報が自身を示さない場合は、自身の後段の I / O ユニット 108a に制御信号を出力する。なお、I / O ユニット 108 は、制御信号に含まれるアドレス情報が自身を示す場合において、後段側の I / O ユニット 108 に制御信号を出力してもよい。また、通信カプラユニット 106 は、制御信号に含まれるアドレス情報が自身に接続された I / O ユニット 108 を示す場合において、後段側の通信カプラユニット 106 に制御信号を出力してもよい。

40

50

**【 0 0 2 3 】**

機器 104 が制御装置 102 に向けて信号を出力する場合がある。この場合、機器 104 の信号は、機器 104 が接続された I/O ユニット 108 のスレーブ処理回路 30 に入力される。スレーブ処理回路 30 は、自身に接続された機器 104 から入力された信号を、制御装置 102 に送る。この場合、スレーブ処理回路 30 は、自身の前段に接続された I/O ユニット 108、または通信カプラユニット 106 に信号を出力する。ここで、スレーブ処理回路 30 は、機器 104 が出力した内容と、信号を出力した I/O ユニット 108 のアドレス情報を出力信号に含める。通信カプラユニット 106 と I/O ユニット 108 との間の信号の入出力は周知技術なので、これ以上の説明は省略する。

**【 0 0 2 4 】**

ところで、参考例では、上記の通り、通信カプラユニット 106 a を先頭にしたステーションと、通信カプラユニット 106 b を先頭にしたステーションとが構成されている。オペレータにしてみると、必要な通信カプラユニット 106 と、必要な I/O ユニット 108 との全てを、1つのステーションにまとめて設置したい場合がある。

**【 0 0 2 5 】**

しかしながら、既に説明したように、1つの通信カプラユニット 106 が並行して通信可能な I/O ユニット（スレーブ処理回路 30）108 の数には、制限台数が決められている。この制限台数は、より詳しくはマスター処理回路 18 に関して、その性能を加味しつつ、設計者が許容する通信の品質に基づいて決められる。オペレータは、少なくとも I/O ユニット 108 の数がマスター処理回路 18 の制限台数を超える場合には、オペレータは複数のステーションを設置せざるを得ない。

**【 0 0 2 6 】**

以上を踏まえ、以下において、実施の形態が説明される。なお、参考例で説明された構成要素と同様の構成要素には、同一の参照符号を付してその説明を省略し、参考例とは異なる部分を主に説明する。

**【 0 0 2 7 】**

図 2 は、本発明の実施形態に係る通信システム 10 を表す図である。図 2 において、スレーブ処理回路 30 は、スレーブ処理回路 30 が支流線 L b 1 と支流線 L b 2 とのいずれに属するかに応じて、スレーブ処理回路 30 a またはスレーブ処理回路 30 b とも記載される。同様に、インターフェース 32 は、インターフェース 32 が支流線 L b 1 と支流線 L b 2 とのいずれに属するかに応じて、インターフェース 32 a またはインターフェース 32 b とも記載される。

**【 0 0 2 8 】**

図 2 に示すように、通信システム 10 は、複数のマスターユニットと、複数のマスターユニットのスレーブである複数のスレーブユニットとを有するシステムである。より具体的に、通信システム 10 は、通信カプラユニット 12 と、インターフェースユニット 14 と、複数の I/O ユニット 16 とを有する。

**【 0 0 2 9 】**

通信カプラユニット 12 と、インターフェースユニット 14 との各々は、通信システム 10 におけるマスターユニットである。一方、複数の I/O ユニット 16 の各々は、通信システム 10 におけるスレーブユニットである。図 2 において、通信カプラユニット 12 のスレーブユニットとなる I/O ユニット 16 は、I/O ユニット 16 a である。また、図 2 において、インターフェースユニット 14 のスレーブユニットとなる I/O ユニット 16 は、I/O ユニット 16 b である。

**【 0 0 3 0 】**

通信カプラユニット 12 は、マスター処理回路 18 (18 a) と、電源 20 と、コネクタ 22 と、端子 24 (24 a) と、端子 26 (26 a) と、筐体 28 とを有する。マスター処理回路 18 a と、電源 20 と、コネクタ 22 と、端子 24 a と、端子 26 a とは、筐体 28 に収容される。

**【 0 0 3 1 】**

10

20

30

40

50

電源 20 は、マスター処理回路 18a に電力を供給する。ただし、電源 20 は、通信力プラユニット 12 の後段側に接続されたインターフェースユニット 14 または I/O ユニット 16 に電力を供給してもよい。

#### 【0032】

コネクタ 22 は、制御装置 102、他の通信力プラユニット 12、または通信力プラユニット 106（図 1）と接続するためのコネクタである。図 2 の例では、コネクタ 22 は制御装置 102 に接続される。コネクタ 22 は、マスター処理回路 18a に接続されている。したがって、図 2 の例では、マスター処理回路 18a はコネクタ 22 を通じて制御装置 102 に接続される。

#### 【0033】

端子 24a と、端子（支流端子）26aとの各々は、後段に設けられる I/O ユニット 16 と接続するための端子である。端子 24a と、端子 26a との各々は、マスター処理回路 18a に接続される。したがって、コネクタ 22 と端子 24a との間にはマスター処理回路 18a が介在する。同様に、コネクタ 22 と端子 26a との間にはマスター処理回路 18a が介在する。

10

#### 【0034】

インターフェースユニット 14 は、マスター処理回路 18（18b）と、端子 24（24b）と、端子 26（26b）と、端子 44 と、筐体 46 を有する。マスター処理回路 18b と、端子 24b と、端子 26b と、端子 44 とは、筐体 46 に収容される。

#### 【0035】

端子 24b と、端子 26b との各々は、後段に設けられた I/O ユニット 16 と接続するための端子である。端子 44 は、インターフェースユニット 14 の前段に設けられた I/O ユニット 16 と接続するための端子である。端子 24b と、端子 26b との各々は、マスター処理回路 18b に接続される。また、端子（第 1 本流端子）44 は、マスター処理回路 18b に接続される。したがって、端子 44 と端子 24b との間には、マスター処理回路 18b が介在する。同様に、端子 44 と端子 26b との間には、マスター処理回路 18b が介在する。

20

#### 【0036】

I/O ユニット 16 は、スレーブ処理回路 30 と、インターフェース 32 と、端子（前段側本流端子）34 と、端子（前段側支流端子）36 と、端子（後段側支流端子）38 と、端子（後段側本流端子）40 と、筐体 42 を有する。スレーブ処理回路 30 と、インターフェース 32 と、端子（前段側本流端子）34 と、端子（前段側支流端子）36 と、端子（後段側支流端子）38 と、端子（後段側本流端子）40 とは、筐体 42 に収容される。

30

#### 【0037】

端子 34 と、端子 36 との各々は、前段に設けられた通信力プラユニット 12、前段に設けられたインターフェースユニット 14、または前段に設けられた別の I/O ユニット 16 と接続するための端子である。なお、端子 36 は、スレーブ処理回路 30 に接続されている。

#### 【0038】

I/O ユニット 16 が通信力プラユニット 12 の後段に設けられる場合、I/O ユニット 16（16a）の端子 34 と通信力プラユニット 12 の端子 24a とが接続されると共に、端子 36 と端子 26a とが接続される。ここで、通信力プラユニット 12 のマスター処理回路 18a と、I/O ユニット 16a のスレーブ処理回路 30 とは、端子 26a と、端子 36 とを通じて接続される。I/O ユニット 16 がインターフェースユニット 14 の後段に設けられる場合、I/O ユニット 16（16b）の端子 34 とインターフェースユニット 14 の端子 24b とが接続されると共に、端子 36 と端子 26b とが接続される。ここで、インターフェースユニット 14 のマスター処理回路 18b と、I/O ユニット 16b のスレーブ処理回路 30 とは、端子 26b と、端子 36 とを通じて接続される。

40

#### 【0039】

50

端子 3 8 は、後段に設けられる別の I / O ユニット 1 6 と接続するための端子である。端子 3 8 は、スレーブ処理回路 3 0 を介して端子 3 6 に接続される。

#### 【 0 0 4 0 】

端子 4 0 は、後段に設けられる別の I / O ユニット 1 6 、または後段に設けられるインターフェースユニット 1 4 と接続するための端子である。端子 4 0 は、端子 3 4 に接続される。ここで、端子 3 4 と端子 4 0 とは、スレーブ処理回路 3 0 を介さずに接続される。つまり、端子 3 4 と端子 4 0 とは、スレーブ処理回路 3 0 と電気的に断線した状態で、互いに接続される。

#### 【 0 0 4 1 】

I / O ユニット 1 6 ( 前段 I / O ) の後段に別の I / O ユニット 1 6 ( 後段 I / O ) が設けられる場合、前段 I / O の端子 3 8 と、後段 I / O の端子 3 6 とが接続される。また、前段 I / O の端子 4 0 と、後段 I / O の端子 3 4 とが接続される。ここで、前段 I / O のスレーブ処理回路 3 0 と、後段 I / O のスレーブ処理回路 3 0 とは、前段 I / O の端子 3 8 と後段 I / O の端子 3 6 を通じて、接続される。

10

#### 【 0 0 4 2 】

また、図 2 に示すように、I / O ユニット 1 6 a の後段にインターフェースユニット 1 4 が設けられる場合、I / O ユニット 1 6 a の端子 4 0 とインターフェースユニット 1 4 の端子 4 4 とが接続される。ここで、端子 4 4 は、I / O ユニット 1 6 a ( 複数の I / O ユニット 1 6 a ) を通じて、通信カプラユニット 1 2 の端子 2 4 a に接続される。前述の通り、端子 4 4 はマスター処理回路 1 8 b と接続されている。また、端子 2 4 a は、マスター処理回路 1 8 a と接続されている。したがって、マスター処理回路 1 8 b は、マスター処理回路 1 8 a と接続 ( デイジーチェーン接続 ) される。マスター処理回路 1 8 b とマスター処理回路 1 8 a との間にスレーブ処理回路 3 0 は介在しない。

20

#### 【 0 0 4 3 】

このように、本実施の形態によれば、仮に通信カプラユニット 1 2 ( マスター処理回路 1 8 a ) の台数制限を超える数の I / O ユニット 1 6 が用いられるとしても、オペレータは、超過分の I / O ユニット 1 6 b をインターフェースユニット 1 4 に接続できる。通信カプラユニット 1 2 のマスター処理回路 1 8 a とインターフェースユニット 1 4 のマスター処理回路 1 8 b との接続は、I / O ユニット 1 6 a ( 複数の I / O ユニット 1 6 a ) を通じて、1 つのステーション内で行われる。オペレータは、インターフェースユニット 1 4 を必要に応じて設けることにより、必要な I / O ユニット 1 6 の全てを1 つのステーションにまとめて設置することができる。

30

#### 【 0 0 4 4 】

なお、インターフェースユニット 1 4 の後段に設けた I / O ユニット 1 6 のさらに後段に、別のインターフェースユニット 1 4 と、I / O ユニット 1 6 とが順次接続されてもよい。つまり、インターフェースユニット 1 4 のマスター処理回路 1 8 b は、1 以上の I / O ユニット 1 6 の端子 3 4 と、端子 4 0 とを通じて、さらに後段側のマスター処理回路 1 8 に接続されてもよい。

#### 【 0 0 4 5 】

##### [ 変形例 ]

以上、本発明の一例として実施の形態が説明された。上記実施の形態には、多様な変更または改良を加えることが可能である。また、その様な変更または改良を加えた形態が本発明の技術的範囲に含まれ得ることは、請求の範囲の記載から明らかである。

40

#### 【 0 0 4 6 】

以下には、上記実施形態に係る変形例が記載される。ただし、上記実施形態と重複する説明は、以下の説明では可能な限り省略される。上記実施形態で説明済みの構成要素には、特に断らない限り、上記実施形態と同一の参照符号が付される。

#### 【 0 0 4 7 】

##### ( 変形例 1 )

実施の形態では、インターフェースユニット 1 4 の端子 2 4 b と端子 4 4 とはマスター

50

処理回路 18 b を介して接続された。しかしながら、インターフェースユニット 14 の構成はこれに限定されない。

#### 【0048】

図 3 は、変形例 1 に係るインターフェースユニット 14 A (14) を表す図である。図 3 には、インターフェースユニット 14 A のほか、その前段側の I/O ユニット 16 a と、後段側の I/O ユニット 16 b とが含まれる。

#### 【0049】

インターフェースユニット 14 A の端子 24 b と端子 44 とは、第 1 信号線 48 によって接続されてもよい。また、インターフェースユニット 14 A の第 1 信号線 48 とマスター処理回路 18 b とは、第 2 信号線 50 によって接続されてもよい。

10

#### 【0050】

##### (変形例 2)

端子 38 はスレーブ処理回路 30 と接続され、且つ、端子 36 はスレーブ処理回路 30 と接続される。ただし、端子 38 と端子 36 とは、スレーブ処理回路 30 を介さず接続されてもよい。例えば、端子 38 と端子 36 とが信号線によって結ばれ、且つ、該信号線とスレーブ処理回路 30 とが別の信号線によって結ばれてもよい。

#### 【0051】

##### [実施の形態から得られる発明]

上記実施の形態および変形例から把握しうる発明について、以下に記載する。

20

#### 【0052】

##### <第 1 の発明>

第 1 の発明は、マスターユニット (12、14) と機器 (104) とを接続し、前記マスターユニット (14) と前記機器との間で信号を伝送する I/O ユニット (16) であって、前段に設けられるマスターユニット (12、14) または前段に設けられる他の I/O ユニット (16) と接続するための前段側本流端子 (34) および前段側支流端子 (36) と、前記前段側支流端子に接続され、後段に設けられる他の I/O ユニット (16) と接続するための後段側支流端子 (38) と、前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路 (30) と、前記前段側本流端子に接続され、後段に設けられる他の前記 I/O ユニット、または後段に設けられる前記マスターユニット (14) と接続するための後段側本流端子 (40) と、を備える。

30

#### 【0053】

これにより、1つのステーション内で増設可能な I/O ユニットが提供される。

#### 【0054】

前記後段側支流端子が後段に設けられる他の前記 I/O ユニットの前記前段側支流端子と接続されることで、複数の前記スレーブ処理回路をデイジーチェーン接続してもよい。

#### 【0055】

第 1 の発明は、前記前段側本流端子が前段側に設けられた前記マスターユニットのマスター処理回路 (18) に接続され、前記後段側本流端子が後段側に設けられたマスターユニット (14) のマスター処理回路 (18) に接続されることで、複数の前記マスター処理回路をデイジーチェーン接続してもよい。

40

#### 【0056】

前記 I/O ユニットは、前記スレーブ処理回路と前記機器とを接続し、前記スレーブ処理回路が前記機器と信号の入出力を行うためのインターフェース (32) をさらに備えてよい。

#### 【0057】

##### <第 2 の発明>

第 2 の発明は、マスター処理回路 (18) を有し、I/O ユニット (16) を介して、前記 I/O ユニットに接続された機器 (104) と信号を伝送するマスターユニット (14) であって、前記マスター処理回路と、前段に設けられる前記 I/O ユニットを介して前段側に位置するマスター処理回路 (18) とを接続するための第 1 本流端子 (44) と

50

、前記マスター処理回路と、後段に設けられるI/Oユニット(16)を介して後段側に位置するマスター処理回路(18)とを接続するための第2本流端子(24)と、後段に設けられた前記I/Oユニットと接続するための支流端子(26)と、を備える。

【0058】

これにより、1つのステーション内でのI/Oユニットの増設を可能にするマスターユニットが提供される。

【0059】

<第3の発明>

第3の発明は、マスターユニット(12、14)と、前記マスターユニットと機器(104)との間で信号を伝送するI/Oユニット(16)とを有する通信システム(10)であって、前記I/Oユニットは、前段に設けられる前記マスターユニットまたは前段に設けられる他のI/Oユニット(16)と接続するための前段側本流端子(34)および前段側支流端子(36)と、前記前段側支流端子に接続され、後段に設けられる他のI/Oユニット(16)と接続するための後段側支流端子(38)と、前記前段側支流端子と前記後段側支流端子とに接続され、信号処理を行うスレーブ処理回路(30)と、前記前段側本流端子に接続され、後段に設けられる他の前記I/Oユニット、または後段に設けられるマスターユニット(14)と接続するための後段側本流端子(40)と、を備え、前記マスターユニット(14)は、前段に設けられた前記I/Oユニットの前記後段側本流端子に接続される第1本流端子(44)と、後段に設けられる前記I/Oユニットの前記前段側本流端子に接続される第2本流端子(24)と、後段に設けられる前記I/Oユニットの前記前段側支流端子に接続される支流端子(26)と、前記第1本流端子、前記第2本流端子および前記支流端子に接続され、信号処理を行うマスター処理回路(18)と、を備える。

【0060】

これにより、1つのステーション内でより多くのI/Oユニットの増設が可能な通信システムが提供される。

【0061】

前記I/Oユニットは、前記スレーブ処理回路と前記機器とを接続し、前記スレーブ処理回路が前記機器と信号の入出力を行うためのインターフェース(32)をさらに備えてよい。

10

20

30

40

50

## 【図面】 【図 1】

【図3】

FIG. 3

【図2】

FIG. 2

10

20

30

40

50

---

フロントページの続き

審査官 田中 友章

- (56)参考文献

- 特開2018-157456 (JP, A)

- 特開平9-244772 (JP, A)

- 特開2016-110460 (JP, A)

- 特開2019-114085 (JP, A)

- 米国特許出願公開第2020/0333758 (US, A1)

- 米国特許出願公開第2019/0243793 (US, A1)

- 米国特許出願公開第2013/0297829 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

- G 05 B 19 / 05

- G 06 F 3 / 00

- G 06 F 13 / 00