(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5280309号

(P5280309)

(45) 発行日 平成25年9月4日(2013.9.4)

(24) 登録日 平成25年5月31日(2013.5.31)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

N

請求項の数 9 (全 20 頁)

(21) 出願番号 特願2009-168596 (P2009-168596)

(22) 出願日 平成21年7月17日 (2009.7.17)

(65) 公開番号 特開2011-23626 (P2011-23626A)

(43) 公開日 平成23年2月3日 (2011.2.3)

審査請求日 平成24年5月23日 (2012.5.23)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 堀内 道夫

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 德武 安衛

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 松田 勇一

長野県長野市小島田町80番地 新光電氣

工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

一方の面から他方の面に貫通する複数の線状導体を有する基板と、

前記基板に設けられた半導体素子収納孔内に固着された半導体素子と、

前記基板の前記一方の面及び前記半導体素子の表面側に形成された第1絶縁層と、

前記第1絶縁層上に形成され、かつ、前記第1絶縁層に設けられた貫通孔を介して前記

基板の前記一方の面から前記貫通孔内に露出する複数の線状導体及び前記半導体素子と電

気的に接続された第1配線層と、

前記基板の前記他方の面及び前記半導体素子の背面側に形成された第2絶縁層と、

前記第2絶縁層上に形成され、かつ、前記第2絶縁層に設けられた貫通孔を介して前記

基板の前記他方の面から前記貫通孔内に露出する前記複数の線状導体と電気的に接続され

た第2配線層と、を有し、

前記線状導体は、隣接する前記線状導体間の距離が、前記線状導体の径よりも小さくな

るように配置されている半導体装置。

## 【請求項 2】

前記線状導体は、電気的に接続されていない孤立した線状導体を含む請求項1記載の半

導体装置。

## 【請求項 3】

前記線状導体は、信号配線と接続されている線状導体と、前記信号配線と接続されてい

る線状導体の周囲に位置する線状導体と、を有し、

前記周囲に位置する線状導体は、グランド配線と接続されている請求項 1 又は 2 記載の半導体装置。

【請求項 4】

前記信号配線と接続されている線状導体と前記周囲に位置する線状導体との間には、電気的に接続されていない孤立した線状導体が配置されている請求項 3 記載の半導体装置。

【請求項 5】

前記半導体素子を複数個有する請求項 1 乃至 4 の何れか一項記載の半導体装置。

【請求項 6】

前記基板には複数の貫通孔が形成され、一部の貫通孔は前記半導体素子が固着されている前記半導体素子収納孔であり、他の貫通孔は受動部品が固着されている受動部品収納孔である請求項 1 乃至 5 の何れか一項記載の半導体装置。 10

【請求項 7】

前記線状導体の径は、30 nm ~ 2000 nm である請求項 1 乃至 6 の何れか一項記載の半導体装置。

【請求項 8】

請求項 1 乃至 7 の何れか一項記載の半導体装置を複数個積層した積層型半導体装置。

【請求項 9】

一方の面から他方の面に貫通する複数の線状導体を有する基板を準備する第 1 工程と、前記基板に半導体素子収納孔を形成する第 2 工程と、

前記基板の前記一方の面に、前記半導体素子収納孔の一端を塞ぐように、第 1 絶縁層を形成する第 3 工程と、 20

前記半導体素子収納孔内に、表面側が前記第 1 絶縁層に接するように、半導体素子を固着する第 4 工程と、

前記第 1 絶縁層上に、前記第 1 絶縁層に設けられた貫通孔を介して前記基板の前記一方の面から前記貫通孔内に露出する複数の線状導体及び前記半導体素子と電気的に接続された第 1 配線層を形成する第 5 工程と、

前記基板の前記他方の面に、前記貫通孔の他端を塞ぐように、第 2 絶縁層を形成する第 6 工程と、

前記第 2 絶縁層上に、前記第 2 絶縁層に設けられた貫通孔を介して前記基板の前記他方の面から前記貫通孔内に露出する前記複数の線状導体と電気的に接続された第 2 配線層を形成する第 7 工程と、を有する半導体装置の製造方法。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子と基板とを含んで構成された半導体装置及びその製造方法に関する。

【背景技術】

【0002】

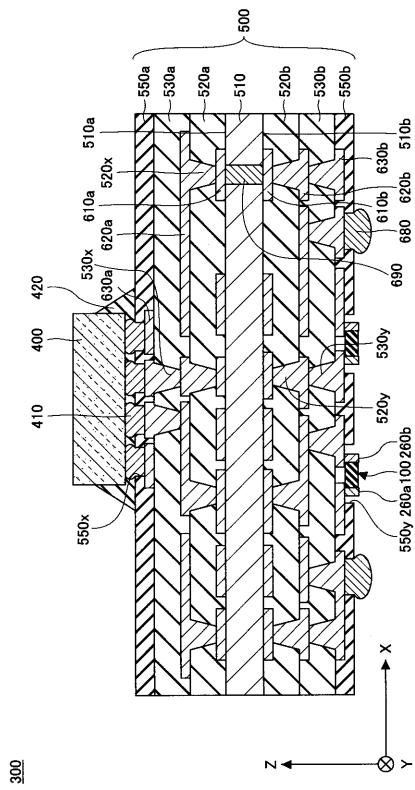

従来から、基板上に半導体素子を実装した半導体装置が知られている。以下、図 1 を参照しながら、基板上に半導体素子を実装した従来の半導体装置について説明する。図 1 は、基板上に半導体素子を実装した従来の半導体装置を例示する断面図である。図 1 を参照するに、半導体装置 300 は、多層基板 500 と、半導体素子 400 と、はんだバンプ 410 と、アンダーフィル樹脂層 420 とを有する。多層基板 500 の中心部には、支持体 510 が設けられている。 40

【0003】

支持体 510 の第 1 主面 510a 上には、第 1 配線層 610a が形成されている。又、支持体 510 には、第 1 主面 510a から第 2 主面 510b に貫通するスルーピア 690 が形成されている。第 1 配線層 610a は、スルーピア 690 を介して後述する第 4 配線層 610b と電気的に接続されている。更に、第 1 配線層 610a を覆うように第 1 絶縁層 520a が形成されており、第 1 絶縁層 520a 上には、第 2 配線層 620a が形成さ 50

れている。第1配線層610aと第2配線層620aとは、第1絶縁層520aを貫通するビアホール520xを介して電気的に接続されている。

#### 【0004】

更に、第2配線層620aを覆うように第2絶縁層530aが形成されている。第2絶縁層530a上には、第3配線層630aが形成されている。第2配線層620aと第3配線層630aとは、第2絶縁層530aを貫通するビアホール530xを介して電気的に接続されている。

#### 【0005】

更に、第3配線層630aを覆うように、開口部550xを有するソルダーレジスト膜550aが形成されている。第3配線層630aのソルダーレジスト膜550aの開口部550xから露出する部分は、電極パッドとして機能する（以降、第3配線層630aのソルダーレジスト膜550aの開口部550xから露出する部分を電極パッド630aという場合がある）。以降、電極パッド630aが形成されている面を、多層基板500の第1主面という場合がある。

#### 【0006】

支持体510の第2主面510b上には、第4配線層610bが形成され、更に、第4配線層610bを覆うように第3絶縁層520bが形成されている。第3絶縁層520b上には、第5配線層620bが形成されている。第4配線層610bと第5配線層620bとは、第3絶縁層520bを貫通するビアホール520yを介して電気的に接続されている。

#### 【0007】

更に、第5配線層620bを覆うように第4絶縁層530bが形成されている。第4絶縁層530b上には、第6配線層630bが形成されている。第5配線層620bと第6配線層630bとは、第4絶縁層530bを貫通するビアホール530yを介して電気的に接続されている。

#### 【0008】

更に、第6配線層630bを覆うように、開口部550yを有するソルダーレジスト膜550bが形成されている。第6配線層630bのソルダーレジスト膜550bの開口部550yから露出する部分は、電極パッドとして機能する（以降、第6配線層630bのソルダーレジスト膜550bの開口部550yから露出する部分を電極パッド630bという場合がある）。以降、電極パッド630bが形成されている面を、多層基板500の第2主面という場合がある。

#### 【0009】

一部の電極パッド630b上には、はんだバンプ680が形成されている。はんだバンプ680は、半導体装置300を回路基板（図示せず）に実装する際に、回路基板の対応する端子と電気的に接続される外部接続端子として機能する。又、一部の電極パッド630b上には、チップコンデンサ100が実装されている。電極パッド630bとチップコンデンサ100の外部電極260a及び260bとは電気的に接続されている。

#### 【0010】

多層基板500の第1主面上には半導体素子400が実装されている。半導体素子400は、シリコン等からなる薄板化された半導体基板（図示せず）上に半導体集積回路（図示せず）や電極パッド（図示せず）が形成されたものである。半導体素子400の電極パッド（図示せず）上には、はんだバンプ410が形成されている。

#### 【0011】

半導体素子400の電極パッド（図示せず）は、はんだバンプ410により、多層基板500の対応する電極パッド630aと電気的に接続されている。はんだバンプ410の材料としては、例えばSnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。半導体素子400と多層基板500のソルダーレジスト膜550aとの間には、アンダーフィル樹脂層420が充填されている。

#### 【0012】

10

20

30

40

50

又、従来から、基板に半導体素子を内蔵した半導体装置が知られている。以下、図2を参照しながら、基板に半導体素子を内蔵した従来の半導体装置について説明する。図2は、基板に半導体素子を内蔵した従来の半導体装置を例示する断面図である。図2を参照するに、半導体装置700は、多層基板800と、半導体素子450とを有する。半導体素子450は、樹脂810に埋め込まれている。半導体素子450及び樹脂810の一方の面には第1絶縁層820が形成されており、第1絶縁層820上には、第1配線層910が形成されている。第1配線層910と半導体素子450の電極パッド(図示せず)とは、第1絶縁層820を貫通するビアホール820xを介して電気的に接続されている。すなわち、半導体素子450と多層基板800との電気的接続にバンプを用いていない。

## 【0013】

10

更に、第1配線層910を覆うように第2絶縁層830が形成されており、第2絶縁層830上には、第2配線層920が形成されている。第1配線層910と第2配線層920とは、第2絶縁層830を貫通するビアホール830xを介して電気的に接続されている。

## 【0014】

更に、第2配線層920を覆うように第3絶縁層840が形成されている。第3絶縁層840上には、第3配線層930が形成されている。第2配線層920と第3配線層930とは、第3絶縁層840を貫通するビアホール840xを介して電気的に接続されている。

## 【0015】

20

更に、第3配線層930を覆うように、開口部850xを有するソルダーレジスト膜850が形成されている。第3配線層930のソルダーレジスト膜850の開口部850xから露出する部分は、電極パッドとして機能する(以降、第3配線層930のソルダーレジスト膜850の開口部850xから露出する部分を電極パッド930という場合がある)。電極パッド930上には、はんだバンプ980が形成されている。はんだバンプ980は、半導体装置700を回路基板(図示せず)に実装する際に、回路基板の対応する端子と電気的に接続される外部接続端子として機能する。

## 【先行技術文献】

## 【特許文献】

## 【0016】

30

## 【特許文献1】特開平10-308565号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0017】

しかしながら、基板上に半導体素子を実装した従来の半導体装置300では、半導体素子400と多層基板500との接続性が低いという問題があった。具体的には、半導体素子400と多層基板500との熱膨脹係数の違いに起因する応力破壊や、エレクトロマイグレーションに起因する断線等である。

## 【0018】

40

又、基板に半導体素子を内蔵した従来の半導体装置700では、半導体素子450と多層基板800との接続にバンプを用いていないため、半導体装置300に比べて半導体素子450と多層基板800との接続信頼性を向上することができる。しかしながら、半導体装置700では、半導体素子450を樹脂810に埋め込んでから樹脂810の表面に第1配線層910等を形成するため、相互に接続された配線層を半導体素子450の表裏両面に形成することができず、高密度実装化が困難であった。

## 【0019】

上記の点に鑑みて、半導体素子と基板との接続信頼性が高く、高密度実装化が可能な半導体装置及びその製造方法を提供することを課題とする。

## 【課題を解決するための手段】

## 【0020】

50

本半導体装置は、一方の面から他方の面に貫通する複数の線状導体を有する基板と、前記基板に設けられた半導体素子収納孔内に固着された半導体素子と、前記基板の前記一方の面及び前記半導体素子の表面側に形成された第1絶縁層と、前記第1絶縁層上に形成され、かつ、前記第1絶縁層に設けられた貫通孔を介して前記基板の前記一方の面から前記貫通孔内に露出する複数の線状導体及び前記半導体素子と電気的に接続された第1配線層と、前記基板の前記他方の面及び前記半導体素子の背面側に形成された第2絶縁層と、前記第2絶縁層上に形成され、かつ、前記第2絶縁層に設けられた貫通孔を介して前記基板の前記他方の面から前記貫通孔内に露出する前記複数の線状導体と電気的に接続された第2配線層と、を有し、前記線状導体は、隣接する前記線状導体間の距離が、前記線状導体の径よりも小さくなるように配置されていることを要件とする。

10

### 【0021】

本半導体装置の製造方法は、一方の面から他方の面に貫通する複数の線状導体を有する基板を準備する第1工程と、前記基板に半導体素子収納孔を形成する第2工程と、前記基板の前記一方の面上に、前記半導体素子収納孔の一端を塞ぐように、第1絶縁層を形成する第3工程と、前記半導体素子収納孔内に、表面側が前記第1絶縁層に接するように、半導体素子を固着する第4工程と、前記第1絶縁層上に、前記第1絶縁層に設けられた貫通孔を介して前記基板の前記一方の面から前記貫通孔内に露出する複数の線状導体及び前記半導体素子と電気的に接続された第1配線層を形成する第5工程と、前記基板の前記他方の面上に、前記貫通孔の他端を塞ぐように、第2絶縁層を形成する第6工程と、前記第2絶縁層上に、前記第2絶縁層に設けられた貫通孔を介して前記基板の前記他方の面から前記貫通孔内に露出する前記複数の線状導体と電気的に接続された第2配線層を形成する第7工程と、を有することを要件とする。

20

### 【発明の効果】

### 【0022】

開示の技術によれば、半導体素子と基板との接続信頼性が高く、高密度実装化が可能な半導体装置及びその製造方法を提供することができる。

### 【図面の簡単な説明】

### 【0023】

【図1】基板上に半導体素子を実装した従来の半導体装置を例示する断面図である。

30

【図2】基板に半導体素子を内蔵した従来の半導体装置を例示する断面図である。

【図3】第1の実施の形態に係る半導体装置を例示する断面図である。

【図4】図3のA部を拡大して例示する斜視透視図である。

【図5】第1の実施の形態に係る半導体装置の製造工程を例示する図（その1）である。

【図6】第1の実施の形態に係る半導体装置の製造工程を例示する図（その2）である。

【図7】第1の実施の形態に係る半導体装置の製造工程を例示する図（その3）である。

【図8】第1の実施の形態に係る半導体装置の製造工程を例示する図（その4）である。

【図9】第1の実施の形態に係る半導体装置の製造工程を例示する図（その5）である。

【図10】第1の実施の形態に係る半導体装置の製造工程を例示する図（その6）である

。

【図11】第1の実施の形態に係る半導体装置の製造工程を例示する図（その7）である

。

【図12】第1の実施の形態に係る半導体装置の製造工程を例示する図（その8）である

。

【図13】第1の実施の形態に係る半導体装置の製造工程を例示する図（その9）である

。

【図14】第1の実施の形態に係る半導体装置の製造工程を例示する図（その10）である。

【図15】第1の実施の形態に係る半導体装置の製造工程を例示する図（その11）である。

40

50

【図16】第1の実施の形態の変形例に係る半導体装置の一部を例示する図である。

【図17】第2の実施の形態に係る半導体装置を例示する断面図である。

【図18】第3の実施の形態に係る半導体装置を例示する断面図である。

【図19】第4の実施の形態に係る積層型半導体装置を例示する断面図である。

【発明を実施するための形態】

【0024】

以下、図面を参照して、実施の形態の説明を行う。

【0025】

### 第1の実施の形態

[第1の実施の形態に係る半導体装置の構造]

10

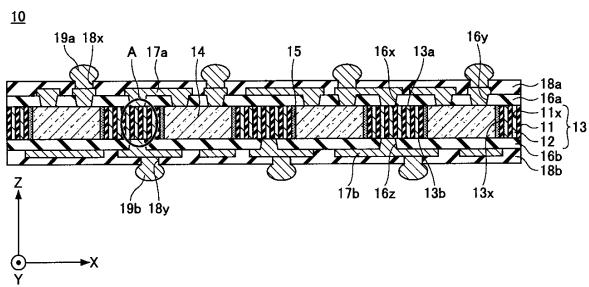

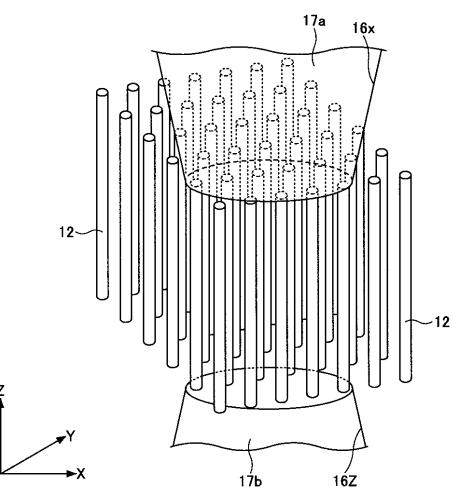

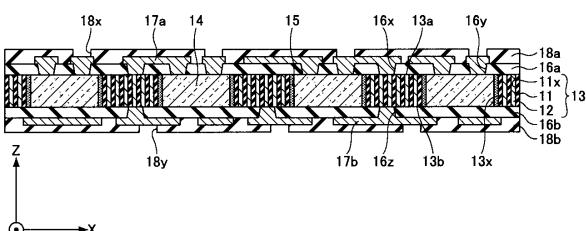

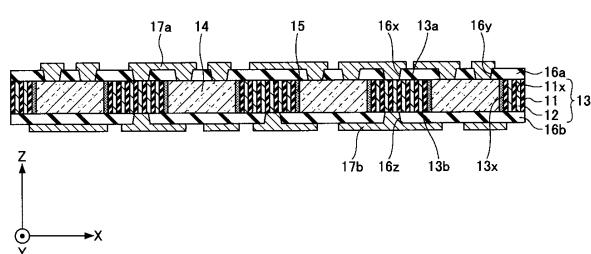

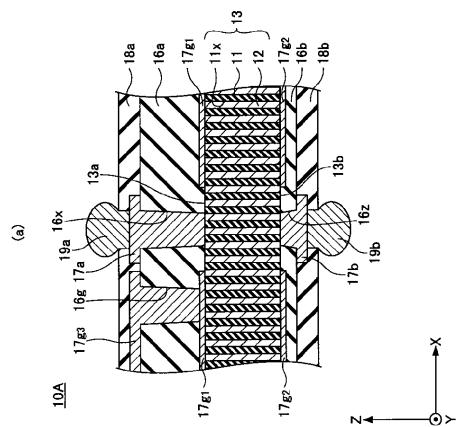

始めに、第1の実施の形態に係る半導体装置の構造について説明する。図3は、第1の実施の形態に係る半導体装置を例示する断面図である。図4は、図3のA部を拡大して例示する斜視透視図である。ただし、図4において、一部の構成要素は省略されている。図3及び図4において、X方向は後述する基板13の一方の面13aと平行な方向、Y方向はX方向に垂直な方向(紙面奥行き方向)、Z方向はX方向及びY方向に垂直な方向(基板13の厚さ方向)をそれぞれ示している。

【0026】

図3及び図4を参照するに、第1の実施の形態に係る半導体装置10は、基板13と、半導体素子14と、絶縁性樹脂15と、第1絶縁層16aと、第2絶縁層16bと、第1配線層17aと、第2配線層17bと、第1ソルダーレジスト層18aと、第2ソルダーレジスト層18bと、第1はんだバンプ19aと、第2はんだバンプ19bとを有する。

20

【0027】

半導体装置10において、基板13は、例えば厚さ70～100μm程度、大きさ10×10mm程度の基板であり、絶縁性基材11全体に亘りそのZ方向(厚さ方向)に形成された多数の貫通孔11xに金属材料を充填して線状導体(ビア)12が形成された基板である。絶縁性基材11としては、例えばアルミナ(酸化アルミニウム)、ムライト、窒化アルミニウム、ガラスセラミックス(ガラスとセラミックスの複合材料)等を用いることができる。又、絶縁性基材11の材料として、有機系の樹脂等(エポキシ系樹脂、ポリイミド系樹脂等)を用いても構わない。

【0028】

30

基板13に内蔵される半導体素子14が例えばシリコンである場合、その熱膨張係数(CTE)は3ppm/程度である。又、基板13に形成される第1配線層17aや第2配線層17bが例えば銅(Cu)である場合、その熱膨張係数(CTE)は16～17ppm/程度である。絶縁性基材11の材料として例えば熱膨張係数(CTE)が6～7ppm/程度のアルミナや熱膨張係数(CTE)が4.5ppm/程度のムライト等の半導体素子14の熱膨張係数(CTE)と第1配線層17aや第2配線層17bの熱膨張係数(CTE)との中間的な値の熱膨張係数(CTE)を有するセラミックス等を用いることにより、半導体素子14と第1配線層17aや第2配線層17bとの熱膨張係数(CTE)の差に起因する応力を緩和することができる。

【0029】

40

絶縁性基材11の材料として有機系の樹脂等(エポキシ系樹脂、ポリイミド系樹脂等)を用いる場合には、シリカ等の無機フィラーを高密度に混合させることにより、その熱膨張係数(CTE)を半導体素子14の熱膨張係数(CTE)と第1配線層17aや第2配線層17bの熱膨張係数(CTE)との中間的な値にすることが可能となり、半導体素子14と第1配線層17aや第2配線層17bとの熱膨張係数(CTE)の差に起因する応力を緩和することができる。

【0030】

線状導体12は、その一端面が基板13の一方の面13aから露出しており、その他端面が基板13の他方の面13bから露出している。線状導体12は、例えば平面視円形に形成されており、その直径は例えば30nm～2000nmとすることができる。なお、

50

平面視とは、対象物を図3のZ方向から見た場合を指す。又、線状導体12は、隣接する線状導体12の間隔が線状導体12の直径よりも小さくなる程度に密に形成されていることが好ましい。ただし、線状導体12の配置形態については、特に限定されず、例えばヘキサゴナル状に配置されていてもよいし、グリッド状に配置されていてもよい。

#### 【0031】

各線状導体12は、基板13の一方の面13aに形成された導体と他方の面13bに形成された導体とを接続するビアとしての機能を有する。ただし、線状導体12の一部は導体には接続されず、電気的に孤立（フローティング）した状態であっても構わない。線状導体（ビア）12を形成する金属材料としては、例えば銀（Ag）、銅（Cu）、ニッケル（Ni）等を用いることができる。10

#### 【0032】

半導体素子14は、基板13に形成された貫通孔13x（半導体素子14を実装するための半導体素子収納孔）内に絶縁性樹脂15により固着されている。半導体素子14は、シリコン等からなる薄板化された半導体基板（図示せず）上に半導体集積回路（図示せず）や電極パッド（図示せず）が形成されたものである。半導体素子14の厚さは、例えば10～50μmとすることができます。絶縁性樹脂15の材料としては、エポキシ系樹脂、ポリイミド系樹脂等を用いることができる。なお、半導体素子14は、半導体集積回路（図示せず）や電極パッド（図示せず）が上側（第1絶縁層16aと接する側）に来るよう配置されている。20

#### 【0033】

第1絶縁層16aは、半導体素子14の表面（電極パッド（図示せず）が形成されている面）及び基板13の一方の面13aに形成されている。第1絶縁層16aの材料としては、エポキシ系樹脂、ポリイミド系樹脂などの樹脂材を用いることができる。20

#### 【0034】

第1配線層17aは、第1絶縁層16a上に形成されている。第1ビアホール16x内の第1配線層17aは、第1ビアホール16x内に露出した多数の線状導体12の端面と電気的に接続されている。例えば第1ビアホール16xの底部の直径を100μm程度に選定すると、第1配線層17aは数千本の線状導体12の端面と電気的に接続されることになる。第2ビアホール16y内の第1配線層17aは、第2ビアホール16y内に露出した半導体素子14の電極パッド（図示せず）と電気的に接続されている。第1配線層17aの材料としては、例えば銅（Cu）等を用いることができる。30

#### 【0035】

第1ソルダーレジスト層18aは、第1配線層17aを覆うように第1絶縁層16a上に形成されている。第1ソルダーレジスト層18aは開口部18xを有し、開口部18x内には第1配線層17aの一部が露出している。

#### 【0036】

第1はんだバンプ19aは、第1ソルダーレジスト層18aの開口部18x内に露出する第1配線層17a上に形成されている。第1はんだバンプ19aの材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。第1はんだバンプ19aは、例えばマザーボード等と接続される外部接続端子として機能する。40

#### 【0037】

なお、外部接続端子として、第1はんだバンプ19aに代えて金属ピン等を用いても構わない。又、第1はんだバンプ19aや金属ピン等の外部接続端子は、設けなくても構わない。この場合には、必要なときに開口部18x内に露出する第1配線層17a上に外部接続端子を形成すればよい。

#### 【0038】

第2絶縁層16bは、半導体素子14の背面（電極パッド（図示せず）が形成されていない面）及び基板13の他方の面13bに形成されている。第2絶縁層16bの材料としては、エポキシ系樹脂、ポリイミド系樹脂などの樹脂材を用いることができる。50

## 【0039】

第2配線層17bは、第2絶縁層16b上に形成されている。第3ビアホール16z内の第2配線層17bは、第3ビアホール16z内に露出した多数の線状導体12の端面と電気的に接続されている。すなわち、第2配線層17bは、多数の線状導体12により第1配線層17aと電気的に接続されている。例えば第3ビアホール16zの底部の直径を100μm程度に選定すると、第2配線層17bは数千本の線状導体12の端面と電気的に接続されることになる。この場合、第2配線層17bは、数千本の線状導体12により第1配線層17aと電気的に接続される。第2配線層17bの材料としては、例えば銅(Cu)等を用いることができる。

## 【0040】

第2ソルダーレジスト層18bは、第2配線層17bを覆うように第2絶縁層16b上に形成されている。第2ソルダーレジスト層18bは開口部18yを有し、開口部18y内には第2配線層17bの一部が露出している。

## 【0041】

第2はんだバンプ19bは、第2ソルダーレジスト層18bの開口部18y内に露出する第2配線層17b上に形成されている。第2はんだバンプ19bの材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。第2はんだバンプ19bは、例えばマザーボード等と接続される外部接続端子として機能する。

## 【0042】

なお、外部接続端子として、第2はんだバンプ19bに代えて金属ピン等を用いても構わない。又、第2はんだバンプ19bや金属ピン等の外部接続端子は、設けなくても構わない。この場合には、必要なときに開口部18y内に露出する第2配線層17b上に外部接続端子を形成すればよい。以上が、第1の実施の形態に係る半導体装置の構造である。

## 【0043】

## [第1の実施の形態に係る半導体装置の製造方法]

続いて、第1の実施の形態に係る半導体装置の製造方法について説明する。図5～図15は、第1の実施の形態に係る半導体装置の製造工程を例示する図である。図5～図15において、図3に示す半導体装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

## 【0044】

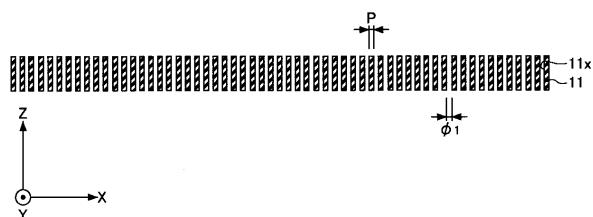

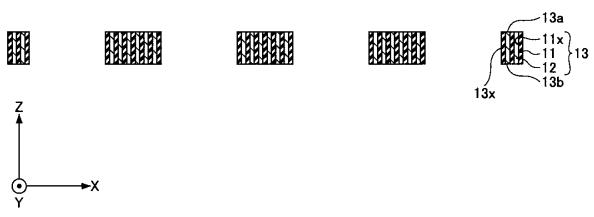

始めに、図5に示す工程では、絶縁性基材11を準備し、準備した絶縁性基材11全体に亘りその厚さ方向に、多数の貫通孔11xを形成する。絶縁性基材11としては、例えば厚さ70～100μm程度、大きさ10×10mm程度のアルミナ(酸化アルミニウム)のグリーンシート等を用いることができる。貫通孔11xは、例えば平面視円形とすることができ、その場合の直径<sub>1</sub>は例えば30nm～2000nmとすることができる。又、貫通孔11xは、隣接する貫通孔11xの間隔Pが貫通孔11xの直径<sub>1</sub>よりも小さくなる程度に密に形成することが好ましい。ただし、貫通孔11xの配置形態については、特に限定されず、例えばヘキサゴナル状に配置してもよいし、グリッド状に配置してもよい。

## 【0045】

貫通孔11xの形成方法の一例を以下に示す。貫通孔11xは、例えば陽極酸化法を用いて形成することができる。具体的には、例えばアルミニウム(A1)の基板の一方の面を絶縁被膜したA1基板、又はガラス基板上にスパッタリング等によりアルミニウム(A1)の電極層を形成したA1電極層を用意し、用意したA1基板又はA1電極層の表面を洗浄後、電解液(好適には硫酸水溶液)中に浸漬し、浸漬したA1基板又はA1電極層を陽極とし、これに対向配置される白金(Pd)電極を陰極として通電(パルス電圧を印加)することで、A1基板又はA1電極層の表面に多孔質金属酸化膜(微小径の孔が規則正しく形成された酸化アルミニウムの膜)を形成することができる。

## 【0046】

10

20

30

40

50

この後、陽極酸化とは逆電位の電圧を各電極に印加（A1基板又はA1電極層を陰極とし、白金（Pd）電極を陽極として通電）することで、多孔質金属酸化膜をA1基板又はA1電極層から分離する。これによって、所望の微小径（例えば30nm～2000nm）の貫通孔11xが高密度に形成された絶縁性基材11が得られる。

#### 【0047】

なお、絶縁性基材11の材料としては、アルミナ（酸化アルミニウム）以外に、ムライト、窒化アルミニウム、ガラスセラミックス（ガラスとセラミックスの複合材料）等を用いてもよい。又、絶縁性基材11の材料はセラミックス（無機材料）には限定されず、有機系の樹脂等（エポキシ系樹脂、ポリイミド系樹脂等）を用いても構わない。

#### 【0048】

ただし、有機系の樹脂（エポキシ系樹脂、ポリイミド系樹脂等）を用いる場合、シリカ等の無機フィラーを高密度に混合させたものを使用することが望ましい。第1絶縁層16aや第2絶縁層16bも同等の樹脂を使用し、熱膨張係数（CTE）も近似しているため、シリカ等の無機フィラーを高密度に混合させることにより絶縁性基材11に使用する樹脂の熱膨張係数（CTE）を下げる、半導体素子14の熱膨張係数（CTE）と第1配線層17aや第2配線層17bの熱膨張係数（CTE）との中間的な値の熱膨張係数（CTE）を確保するためである。

#### 【0049】

絶縁性基材11に有機系の樹脂（エポキシ系樹脂、ポリイミド系樹脂等）を用いる場合、貫通孔11xは炭酸ガスレーザ、エキシマレーザ等を用いた穴明け加工により形成することができる。

#### 【0050】

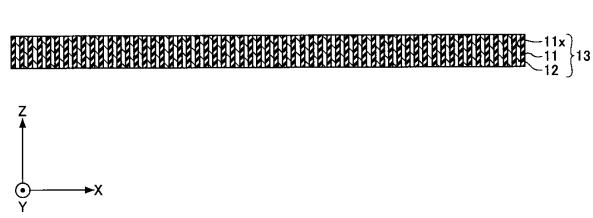

次いで、図6に示す工程で、絶縁性基材11に形成された貫通孔11xに金属材料を充填して線状導体（ピア）12を形成する。以降、線状導体12を有する絶縁性基材11を基板13と称する場合がある。線状導体12は、例えばスクリーン印刷法やインクジェット法等を用いて、例えば銀（Ag）や銅（Cu）等の導電性ペーストを貫通孔11xに充填することにより形成することができる。又、絶縁性基材11として有機系の樹脂等（エポキシ系樹脂、ポリイミド系樹脂等）を用いた場合には、めっき法を用いて貫通孔11xに銅（Cu）やニッケル（Ni）等の金属材料を充填することができる。

#### 【0051】

例えば金属材料として銅（Cu）を用いる場合には、絶縁性基材11の表面（貫通孔11xの内壁面を含む）に、無電解銅（Cu）めっき法によりシード層を形成し、形成したシード層を給電層として利用した電解銅（Cu）めっき法により、貫通孔11xに銅（Cu）を充填することができる。又、無電解銅（Cu）めっき法のみにより、銅（Cu）を貫通孔11xに充填しても構わない。

#### 【0052】

更に、必要に応じて機械研磨、化学機械研磨（CMP）等により両面を研磨して平坦化し、線状導体12の両端を絶縁性基材11の両面に露出させることができる。このようにして、絶縁性基材11に、絶縁性基材11の厚さ方向に貫通する微小径の線状導体12が高密度に設けられた構造体（図6参照）を形成することができる。

#### 【0053】

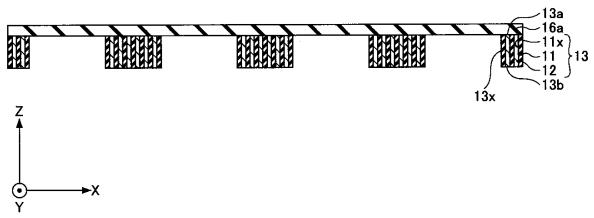

次いで、図7に示す工程では、図6において形成した基板13に、複数の貫通孔13xを形成する。貫通孔13xは、後述する図9に示す工程において、半導体素子14を実装するための半導体素子収納孔である。従って、貫通孔13xの形状は、半導体素子14の形状に対応させて適宜決定すればよいが、例えば直方体状の孔とすることができる。貫通孔13xは、例えばレーザ加工法やウェットエッチング法等を用いて形成することができる。

#### 【0054】

次いで、図8に示す工程では、基板13の一方の面13aに、貫通孔13xの一端を塞ぐように、第1絶縁層16aを形成する。第1絶縁層16aの材料としては、エポキシ系

10

20

30

40

50

樹脂、ポリイミド系樹脂などの樹脂材を用いることができる。ただし、第1絶縁層16aの材料としては、例えばフィラーが含有された厚さの均一性や加工性に優れた樹脂材を用いることが好ましい。第1絶縁層16aは、一例として、基板13の一方の面13aに、貫通孔13xの一端を塞ぐように樹脂フィルムをラミネートした後、樹脂フィルムをプレス(押圧)し、その後、190程度の温度で熱処理して硬化させることにより形成することができる。

#### 【0055】

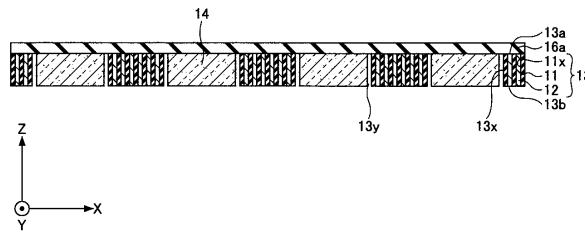

次いで、図9に示す工程では、複数の貫通孔13x内に半導体素子14を1つずつ配置する。本実施例では、半導体素子14を、半導体素子14の表面(電極パッド(図示せず)が形成されている面)が、第1絶縁層16aに接するように配置する。又、半導体素子14を、半導体素子14の側面と複数の貫通孔13xの内壁面との間に間隙13yが形成されるように配置する。半導体素子14の厚さは、例えば10~50μmとすることができる。ただし、半導体素子14の厚さは、基板13の厚さ(例えば70~100μm程度)と同程度又は多少厚くても構わない。なお、半導体素子14は、シリコン等からなる薄板化された半導体基板(図示せず)上に半導体集積回路(図示せず)や電極パッド(図示せず)が形成されたものである。

#### 【0056】

次いで、図10に示す工程では、間隙13y及び基板13の他方の面13bに絶縁性樹脂15(エポキシ系樹脂、ポリイミド系樹脂等)を塗布し、硬化させて半導体素子14を貫通孔13x内の第1絶縁層16a上に固着する。なお、絶縁性樹脂15の材料としては、厚さの均一性や加工性よりも空間充填性に優れた樹脂材を用いることが好ましい。

#### 【0057】

次いで、図11に示す工程では、基板13の他方の面13bに形成された絶縁性樹脂15を機械研磨、化学機械研磨(CMP)等により除去し、基板13の他方の面13bを露出させる。なお、半導体素子14の厚さが基板13の厚さよりも薄い場合には、半導体素子14の背面(第1絶縁層16aに接しない側)に絶縁性樹脂15が形成されたままで構わない。

#### 【0058】

次いで、図12に示す工程では、基板13の他方の面13b及び半導体素子14の背面(又は半導体素子14の背面に形成された絶縁性樹脂15上)に第2絶縁層16bを形成する。すなわち、貫通孔13xの他端を塞ぐように、第2絶縁層16bを形成する。第2絶縁層16bの材料としては、エポキシ系樹脂、ポリイミド系樹脂などの樹脂材を用いることができる。ただし、第2絶縁層16bの材料としては、例えばフィラーが含有された厚さの均一性や加工性に優れた樹脂材を用いることが好ましい。又、第2絶縁層16bの材料は、電気特性設計上、第1絶縁層16aの材料と同じものを用いることが好ましい。第2絶縁層16bは、一例として、半導体素子14の背面(又は半導体素子14の背面に形成された絶縁性樹脂15)及び基板13の他方の面13bに樹脂フィルムをラミネートした後、樹脂フィルムをプレス(押圧)し、その後、190程度の温度で熱処理して硬化させることにより形成することができる。

#### 【0059】

次いで、図13に示す工程では、第1絶縁層16aに、レーザ加工法等を用いて、基板13の一方の面13aが露出するように第1絶縁層16aを貫通する第1ビアホール16xを形成し、半導体素子14の電極パッド(図示せず)が露出するように第1絶縁層16aを貫通する第2ビアホール16yを形成する。又、第2絶縁層16bに、レーザ加工法等を用いて、基板13の他方の面13bが露出するように第2絶縁層16bを貫通する第3ビアホール16zを形成する。第1ビアホール16x内及び第3ビアホール16z内には、多数の線状導体12の端面が露出する(前述の図4参照)。

#### 【0060】

なお、第1絶縁層16a及び第2絶縁層16bとして感光性樹脂膜を用い、フォトリソグラフィによりパターニングして第1ビアホール16x等を形成する方法を用いてもよい

10

20

30

40

50

し、スクリーン印刷により開口部が設けられた樹脂膜をパターニングして第1ビアホール $16\times$ 等を形成する方法を用いてもよい。

#### 【0061】

次いで、図14に示す工程では、第1絶縁層16a上に、第1ビアホール $16\times$ 内に露出した多数の線状導体12の端面、及び第2ビアホール $16y$ 内に露出した半導体素子14の電極パッド（図示せず）と電気的に接続される第1配線層17aを形成する。又、第2絶縁層16b上に、第3ビアホール $16z$ 内に露出した多数の線状導体12の端面と電気的に接続される第2配線層17bを形成する。これにより、第1配線層17aと第2配線層17bとは、多数の線状導体12により電気的に接続される。第1配線層17a及び第2配線層17bの材料としては、例えば銅（Cu）等を用いることができる。第1配線層17a及び第2配線層17bは、例えばセミアディティブ法により形成される。10

#### 【0062】

第1配線層17aを、セミアディティブ法により形成する例を、より詳しく説明すると、先ず、無電解めっき法又はスパッタ法により、第1ビアホール $16\times$ 内、第2ビアホール $16y$ 内、基板13の一方の面13a、及び半導体素子14の電極パッド（図示せず）上に銅（Cu）シード層（図示せず）を形成した後に、第1配線層17aに対応する開口部を備えたレジスト層（図示せず）を形成する。次いで、銅（Cu）シード層をめっき給電層に利用した電解めっき法により、レジスト層の開口部に銅（Cu）層パターン（図示せず）を形成する。

#### 【0063】

続いて、レジスト層を除去した後に、銅（Cu）層パターンをマスクにして銅（Cu）シード層をエッチングすることにより、第1配線層17aを得ることができる。なお、第1配線層17aの形成方法としては、上述したセミアディティブ法の他にサブトラクティブ法などの各種の配線形成方法を用いることができる。第2配線層17bも同様の方法により形成することができる。20

#### 【0064】

なお、上記と同様な工程を繰り返すことにより、第1配線層17a及び第2配線層17b上に絶縁層及び配線層を積層し、n層（nは1以上の整数）のビルトアップ配線層を形成してもよい。

#### 【0065】

次いで、図15に示す工程では、第1配線層17aを被覆するように第1絶縁層16a上に開口部 $18\times$ を有する第1ソルダーレジスト層18aを形成する。又、第2配線層17bを被覆するように第2絶縁層16b上に開口部 $18y$ を有する第2ソルダーレジスト層18bを形成する。開口部 $18\times$ を有する第1ソルダーレジスト層18aは、例えば第1配線層17aを被覆するようにソルダーレジスト液を塗布し、塗布したソルダーレジスト液を露光、現像することで形成することができる。開口部 $18y$ を有する第2ソルダーレジスト層18bも同様の方法により形成することができる。第1ソルダーレジスト層18a及び第2ソルダーレジスト層18bの材料としては、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。30

#### 【0066】

第1配線層17aの一部は、第1ソルダーレジスト層18aの開口部 $18\times$ 内に露出する。又、第2配線層17bの一部は、第2ソルダーレジスト層18bの開口部 $18y$ 内に露出する。第1ソルダーレジスト層18aの開口部 $18\times$ 内に露出する第1配線層17a上、及び第2ソルダーレジスト層18bの開口部 $18y$ 内に露出する第2配線層17b上に、例えば無電解めっき法により金属層（図示せず）を形成しても構わない。40

#### 【0067】

金属層（図示せず）の例としては、Au層、Ni層/Au層をこの順番で積層したNi/Au層や、Ni層/Pd層/Au層をこの順番で積層したNi/Pd/Au層等を挙げることができる。又、金属層（図示せず）に代えて、第1ソルダーレジスト層18aの開口部 $18\times$ 内に露出する第1配線層17a上、及び第2ソルダーレジスト層18bの開口50

部 18 y 内に露出する第 2 配線層 17 b 上に OSP (Organic Solderability Preservative) 处理を施しても構わない。

#### 【0068】

次いで、第 1 ソルダーレジスト層 18 a の開口部 18 x 内に露出する第 1 配線層 17 a 上、及び第 2 ソルダーレジスト層 18 b の開口部 18 y 内に露出する第 2 配線層 17 b 上に、第 1 はんだバンプ 19 a 及び第 2 はんだバンプ 19 b を形成することにより、図 3 に示す半導体装置 10 が製造される。第 1 はんだバンプ 19 a は、例えば第 1 ソルダーレジスト層 18 a の開口部 18 x 内に露出する第 1 配線層 17 a を覆うように、はんだペーストを印刷し、リフローすることにより形成することができる。第 2 はんだバンプ 19 b も同様の方法により形成することができる。第 1 はんだバンプ 19 a 及び第 2 はんだバンプ 19 b の材料としては、例えば Pb を含む合金、Sn と Cu の合金、Sn と Ag の合金、Sn と Ag と Cu の合金等を用いることができる。第 1 はんだバンプ 19 a 及び第 2 はんだバンプ 19 b は、例えばマザーボード等と接続される外部接続端子として機能する。

10

#### 【0069】

なお、外部接続端子として、第 1 はんだバンプ 19 a 及び / 又は第 2 はんだバンプ 19 b に代えて金属ピン等を用いても構わない。又、第 1 はんだバンプ 19 a 及び / 又は第 2 はんだバンプ 19 b や金属ピン等の外部接続端子は、設けなくても構わない。この場合には、必要なとき（例えば半導体装置 10 の出荷時等）に、開口部 18 x 内に露出する第 1 配線層 17 a 上、及び / 又は第 2 ソルダーレジスト層 18 b の開口部 18 y 内に露出する第 2 配線層 17 b 上に外部接続端子を形成すればよい。以上が、第 1 の実施の形態に係る半導体装置の製造方法である。

20

#### 【0070】

なお、第 1 の実施の形態では、複数の半導体素子を内蔵する半導体装置を例示したが、半導体装置に内蔵される半導体素子は 1 つであっても構わない。

#### 【0071】

このように、第 1 の実施の形態によれば、貫通孔を有する基板（線状導体を有する絶縁性基材）の貫通孔内に半導体素子を固着する。そして、基板（線状導体を有する絶縁性基材）の一方の面及び半導体素子の表面側に第 1 絶縁層を形成し、第 1 絶縁層上に、第 1 絶縁層に設けられた貫通孔（ビアホール）を介して基板の一方の面から露出する複数の線状導体の一部及び半導体素子の電極パッドと電気的に接続された第 1 配線層を形成する。又、基板（線状導体を有する絶縁性基材）の他方の面及び半導体素子の背面側に第 2 絶縁層を形成し、第 2 絶縁層上に、第 2 絶縁層に設けられた貫通孔（ビアホール）を介して基板の他方の面から露出する複数の線状導体の一部と電気的に接続された第 2 配線層を形成する。

30

#### 【0072】

その結果、基板（線状導体を有する絶縁性基材）の一方の面上に形成された第 1 配線層と、基板（線状導体を有する絶縁性基材）の他方の面上に形成された第 2 配線層とを、線状導体により電気的に接続することができる。

#### 【0073】

すなわち、第 1 の実施の形態に係る半導体装置では、相互に接続された配線層（第 1 配線層及び第 2 配線層）を半導体素子の表裏両面に形成することができるため、実装密度を高めることができる。

40

#### 【0074】

又、第 1 の実施の形態に係る半導体装置では、半導体素子と配線層（第 1 配線層及び第 2 配線層）との電気的接続にバンプを用いていないため、半導体素子と配線層（第 1 配線層及び第 2 配線層）との熱膨脹係数の違いに起因する応力破壊や、エレクトロマイグレーションに起因する断線等の発生を防止することが可能となり、半導体素子と配線層（第 1 配線層及び第 2 配線層）との接続信頼性を向上することができる。

#### 【0075】

第 1 の実施の形態の変形例

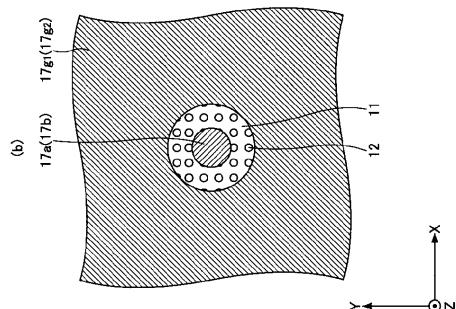

図16は、第1の実施の形態の変形例に係る半導体装置の一部を例示する図である。図16(a)は断面図であり、図16(b)は基板13の一方の面13a(基板13の他方の面13b)に接する導体を模式的に示す平面図である。図16において、図3に示す半導体装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。図16において、X方向は基板13の一方の面13aと平行な方向、Y方向はX方向に垂直な方向(紙面奥行き方向)、Z方向はX方向及びY方向に垂直な方向(基板13の厚さ方向)をそれぞれ示している。

#### 【0076】

図16を参照するに、第1の実施の形態の変形例に係る半導体装置10Aは、基板13の一方の面13a及び他方の面13bに、対向配置された一対のGNDパターン17g<sub>1</sub>及び17g<sub>2</sub>が設けられている点、並びに、GNDパターン17g<sub>1</sub>が第4ビアホール16gを介して第1絶縁層16a上に形成されたGNDパターン17g<sub>3</sub>と接続されている点、を除いて第1の実施の形態に係る半導体装置10と同一構造である。以下、半導体装置10Aについて、半導体装置10と同一構造の部分についてはその説明を省略し、半導体装置10と異なる部分を中心に説明する。

#### 【0077】

半導体装置10Aにおいて、第1ビアホール16x内の第1配線層17a、第3ビアホール16z内の第2配線層17b、及びそれらを接続する複数の線状導体12には、所定の信号電流が流れる。又、図16(b)に示すように、GNDパターン17g<sub>1</sub>及び17g<sub>2</sub>は、第1ビアホール16x内の第1配線層17a、及び第3ビアホール16z内の第2配線層17bが基板13の一方の面13a及び他方の面13bに接する部分の周囲に、所定の間隔を空けて形成されている。又、GNDパターン17g<sub>1</sub>と17g<sub>2</sub>とは、複数の線状導体12を介して電気的に接続されている。

#### 【0078】

GNDパターン17g<sub>1</sub>は、第4ビアホール16gを介して第1絶縁層16a上に形成されたGNDパターン17g<sub>3</sub>と接続されている。すなわち、GNDパターン17g<sub>1</sub>～17g<sub>3</sub>は、何れもGND(基準電位)に接続されたパターンである。なお、GNDパターン17g<sub>1</sub>は、第1配線層17aの一部である。

#### 【0079】

GNDパターン17g<sub>1</sub>及び17g<sub>2</sub>は、例えばスパッタ法やめっき法により、基板13の一方の面13a及び他方の面13bに形成することができる。GNDパターン17g<sub>1</sub>及び17g<sub>2</sub>の材料としては、例えば銅(Cu)等を用いることができる。

#### 【0080】

このように、基板13において、信号電流が流れる複数の線状導体12の周囲には、所定の間隔を空けてGNDに接続された複数の線状導体12が配置されている。この構造は、同軸線路と同等の構造であるため、シールド(遮蔽)効果を奏することができる。又、隣接して配置される信号電流が流れる複数の線状導体間には、GNDに接続された複数の線状導体が配置されることになるため、隣接して配置される信号電流が流れる複数の線状導体間に生じる電気的結合(容量結合)を低減することが可能となり、信号電流が流れる複数の線状導体自体がノイズ源となることを防止することができる。

#### 【0081】

なお、第1絶縁層16aの第1ビアホール16xの周囲、及び第2絶縁層16bの第3ビアホール16zの周囲に、円環状の貫通孔を形成して導体を充填し、GNDパターン17g<sub>1</sub>～17g<sub>3</sub>と接続しても構わない。これにより、第1絶縁層16a及び第2絶縁層16bにも、基板13に形成した同軸線路と同等の構造が形成されるため、同等の効果を得られる。

#### 【0082】

このように、第1の実施の形態の変形例によれば、第1の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。

#### 【0083】

10

20

30

40

50

すなわち、第1の実施の形態の変形例に係る半導体装置では、基板内に同軸線路と同等の構造を形成することにより、シールド(遮蔽)効果を奏することができる。又、隣接して配置される信号電流が流れる複数の線状導体との間に生じる電気的結合(容量結合)を低減することが可能となり、信号電流が流れる複数の線状導体自体がノイズ源となることを防止することができる。

#### 【0084】

##### 第2の実施の形態

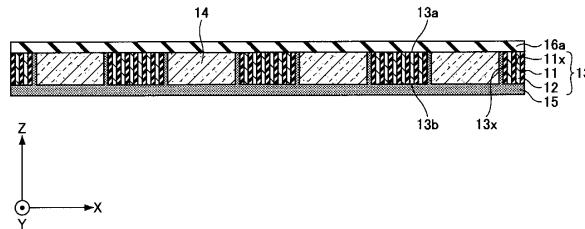

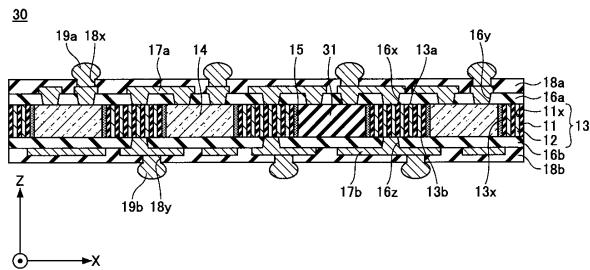

図17は、第2の実施の形態に係る半導体装置を例示する断面図である。図17において、図3に示す半導体装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。図17において、X方向は基板13の一方の面13aと平行な方向、Y方向はX方向に垂直な方向(紙面奥行き方向)、Z方向はX方向及びY方向に垂直な方向(基板13の厚さ方向)をそれぞれ示している。10

#### 【0085】

図17を参照するに、第2の実施の形態に係る半導体装置30は、複数の半導体素子14のうちの一部が受動部品31に置換された点を除いて第1の実施の形態に係る半導体装置10と同一構造である。以下、半導体装置30について、半導体装置10と同一構造の部分についてはその説明を省略し、半導体装置10と異なる部分を中心に説明する。

#### 【0086】

半導体装置30において、受動部品31は、コンデンサ、抵抗、インダクタ等である。又、異なる貫通孔13x内に、異なる受動部品(例えばコンデンサと抵抗等)を内蔵しても構わない。このように、本発明に係る半導体装置は、半導体素子と受動部品とを有していても構わない。20

#### 【0087】

なお、第2の実施の形態に係る半導体装置30の製造方法は、第1の実施の形態に係る半導体装置10の製造方法と同一である。受動部品31は、図9に示す工程において、貫通孔13x内に配置することができる。

#### 【0088】

このように、第2の実施の形態によれば、第1の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。

#### 【0089】

すなわち、第2の実施の形態に係る半導体装置では、半導体素子及び受動部品を内蔵するため、高機能化を図ることができる。30

#### 【0090】

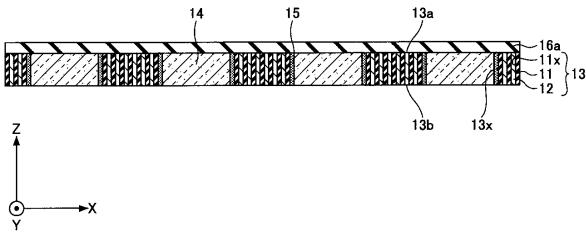

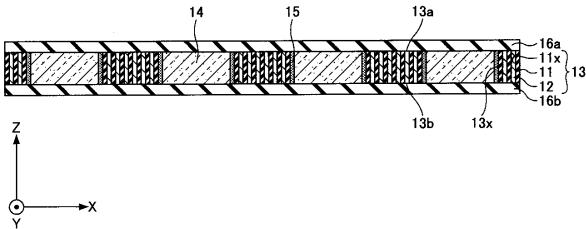

##### 第3の実施の形態

図18は、第3の実施の形態に係る半導体装置を例示する断面図である。図18において、図3に示す半導体装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。図18において、X方向は基板13の一方の面13aと平行な方向、Y方向はX方向に垂直な方向(紙面奥行き方向)、Z方向はX方向及びY方向に垂直な方向(基板13の厚さ方向)をそれぞれ示している。40

#### 【0091】

図18を参照するに、第3の実施の形態に係る半導体装置40は、1つの貫通孔13x内に複数の半導体素子14が配置された点を除いて第1の実施の形態に係る半導体装置10と同一構造である。以下、半導体装置40について、半導体装置10と同一構造の部分についてはその説明を省略し、半導体装置10と異なる部分を中心に説明する。

#### 【0092】

半導体装置40において、1つの貫通孔13x内の複数の半導体素子14は、何れも半導体素子14の表面(電極パッド(図示せず)が形成されている面)が、第1絶縁層16aに接するように配置されており、絶縁性樹脂15により固着されている。このように、本発明に係る半導体装置は、1つの貫通孔内に複数の半導体素子を有していても構わない。

**【0093】**

なお、第3の実施の形態に係る半導体装置40の製造方法は、第1の実施の形態に係る半導体装置10の製造方法と同一である。複数の半導体素子14は、図9に示す工程において、1つの貫通孔13x内に配置することができる。

**【0094】**

このように、第3の実施の形態によれば、第1の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。

**【0095】**

すなわち、第3の実施の形態に係る半導体装置では、複数の半導体素子を内蔵するため、実装密度を更に高めることができる。

10

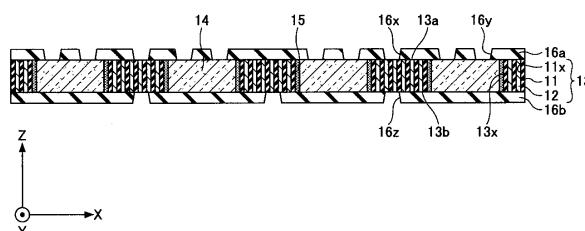

**【0096】****第4の実施の形態**

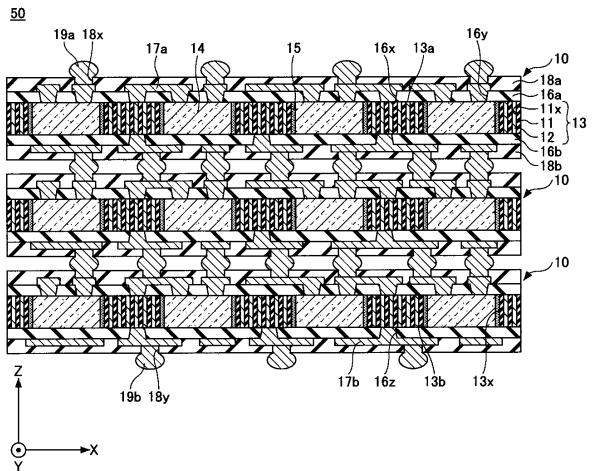

図19は、第4の実施の形態に係る積層型半導体装置を例示する断面図である。図19において、図3に示す半導体装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。図19において、X方向は基板13の一方の面13aと平行な方向、Y方向はX方向に垂直な方向（紙面奥行き方向）、Z方向はX方向及びY方向に垂直な方向（基板13の厚さ方向）をそれぞれ示している。

**【0097】**

図19を参照するに、第4の実施の形態に係る積層型半導体装置50は、本発明に係る半導体装置10が複数個積層された構造である。以下、積層型半導体装置50について、半導体装置10と同一構造の部分についてはその説明を省略し、半導体装置10と異なる部分を中心に説明する。

20

**【0098】**

積層型半導体装置50において、本発明に係る半導体装置10が3個積層されており、各半導体装置10は、第1はんだバンプ19a又は第2はんだバンプ19bで接続されている。ただし、積層する半導体装置10の数は3個には限定されず、2個又は4個以上であってもよい。このように、本発明に係る半導体装置を複数個積層して積層型半導体装置を実現することができる。

**【0099】**

なお、第4の実施の形態に係る積層型半導体装置50の製造方法は、第1の実施の形態に係る半導体装置10の製造方法に、更に半導体装置10を積層する工程を追加することにより実現できる。なお、半導体装置10の積層は、周知の方法により実現することができる。

30

**【0100】**

このように、第4の実施の形態によれば、第1の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。

**【0101】**

すなわち、第4の実施の形態に係る積層型半導体装置では、本発明に係る半導体装置を複数個積層するため、垂直方向にも実装密度を高めることができる。

40

**【0102】**

以上、好ましい実施の形態について詳説したが、上述した実施の形態に制限されることはなく、特許請求の範囲に記載された範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

**【0103】**

例えば、第2～第4の実施の形態に、第1の実施の形態の変形例と同様の変形を加えても構わない。

**【符号の説明】****【0104】**

10、20、30、40 半導体装置

11 絶縁性基材

50

- 1 1 x、1 3 x 貫通孔

1 2 線状導体

1 3 基板

1 3 a 基板 1 3 の一方の面

1 3 b 基板 1 3 の他方の面

1 4 半導体素子

1 5 絶縁性樹脂

1 6 a 第 1 絶縁層

1 6 b 第 2 絶縁層

1 6 x 第 1 ピアホール 10

1 6 y 第 2 ピアホール

1 6 z 第 3 ピアホール

1 7 a 第 1 配線層

1 7 b 第 2 配線層

1 7 g<sub>1</sub>、1 7 g<sub>2</sub>、1 7 g<sub>3</sub> GND パターン

1 8 a 第 1 ソルダーレジスト層

1 8 b 第 2 ソルダーレジスト層

1 8 x、1 8 y 開口部

1 9 a 第 1 はんだバンプ

1 9 b 第 2 はんだバンプ 20

3 1 受動部品

5 0 積層型半導体装置

P 間隔

1 直径

【図 1】

基板上に半導体素子を実装した従来の半導体装置を例示する断面図

【図3】

第1の実施の形態に係る半導体装置を例示する断面図

【図4】

図3のA部を拡大して例示する斜視透視図

【図5】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その1)

【図7】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その3)

【図6】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その2)

【図8】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その4)

【図9】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その5)

【図10】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その6)

【図11】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その7)

【図12】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その8)

【図13】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その9)

【図15】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その11)

【図14】

第1の実施の形態に係る半導体装置の製造工程を例示する図(その10)

【図16】

## 第1の実施の形態の変形例に係る半導体装置の一部を例示する図

【図17】

## 第2の実施の形態に係る半導体装置を例示する断面図

【 図 1 8 】

### 第3の実施の形態に係る半導体装置を例示する断面図

This cross-sectional diagram illustrates a memory device structure. The top layer features several cylindrical structures labeled 19a, 18x, 17a, 14, 15, 13a, 16x, and 16y. Below this is a layer with diagonal hatching. The central part of the diagram shows a vertical stack of layers labeled 13b, 16z, 17b, and 13x. To the right, there is a vertical stack of layers labeled 18a, 16a, 11a, 11b, 12, 16b, and 18b. A coordinate system at the bottom left indicates the X, Y, and Z axes.

【図19】

#### 第4の実施の形態に係る積層型半導体装置を例示する断面図

---

フロントページの続き

(72)発明者 山崎 智生

長野県長野市小島田町80番地 新光電気工業株式会社内

(72)発明者 坂口 勇太

長野県長野市小島田町80番地 新光電気工業株式会社内

審査官 坂本 薫昭

(56)参考文献 特開平10-041435(JP,A)

特開平10-256698(JP,A)

特開2005-135995(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12-23/15

H01L 23/34-23/473

H01L 25/00-25/18

H05K 1/00- 1/02