(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4104746号

(P4104746)

(45) 発行日 平成20年6月18日(2008.6.18)

(24) 登録日 平成20年4月4日(2008.4.4)

(51) Int.Cl.

G06F 13/14 (2006.01)

G06F 13/36 (2006.01)

F 1

G06F 13/14 320E

G06F 13/36 320A

請求項の数 3 (全 42 頁)

(21) 出願番号 特願平10-278559

(22) 出願日 平成10年9月30日(1998.9.30)

(65) 公開番号 特開平11-175454

(43) 公開日 平成11年7月2日(1999.7.2)

審査請求日 平成17年8月9日(2005.8.9)

(31) 優先権主張番号 940367

(32) 優先日 平成9年9月30日(1997.9.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 591030868

コンパック・コンピューター・コーポレーション

COMPAQ COMPUTER CORPORATION

アメリカ合衆国テキサス州77070, ヒューストン, ステイト・ハイウェイ 249, 20555

20555 State Highway 249, Houston, Texas 77070, United States of America

(74) 代理人 100089705

弁理士 社本 一夫

最終頁に続く

(54) 【発明の名称】自動直接メモリ・アクセス機能を備えたコンピュータ・システム

## (57) 【特許請求の範囲】

## 【請求項 1】

自動直接メモリ・アクセス機能を備えたコンピュータ・システムにおいて、

ホスト・バスと、

ホスト・バスに接続され、パケットの少なくとも1つのプールを記憶する主メモリであつて、各プールはパケットのリンク・リストで構成され、各パケットは、リンク・リストを構成するために次のパケットの物理アドレスを含んでいる物理アドレス・フィールドを備えたヘッダを備えている、主メモリと、

ホスト・バスに接続されたプロセッサと、

ローカル・バスと、

ローカル・バスに接続された大容量記憶サブシステムと、

ホスト・バスとローカル・バスとの間に接続され、大容量記憶サブシステムと主メモリとの間でパケットを通信するための分散型バースト・エンジンを含んでいるホスト/ローカル・バス・ブリッジと

からなり、分散型バースト・エンジンは、

リンク・リストの次のパケットの物理アドレスを保持する要求ヘッド・レジスタと、

リンク・リストの最後のパケットの物理アドレスを保持するフリー・キュー・レジスタと、

パケットを保持するための要求キューであって、パケットが保持されているときにキューの充ち具合を示す指示を提供する要求キューと、

10

20

処理すべき次のパケットが存在することを表す指示をホストから受け取る要求ドアベル・レジスタと、

完了リストの物理アドレスを保持する完了ヘッド・レジスタと、

パケットを保持する完了キューと、

完了キューが既に提供されかつプロセッサがパケットを受信する準備が完了していることを表す指示をプロセッサから受け取る完了ドアベル・レジスタと、

要求キューに接続され、要求ドアベル・レジスタの出力に応答して、要求ドアベル・レジスタが駆動された時に、要求ヘッド・レジスタに記憶された物理アドレスに応じて、主メモリからパケットを読み出して、要求キューに該パケットを記憶する第1のフロント・エンド・コントローラと、

10

要求キュー及び完了キューに接続され、キューの充ち具合を示す指示に応答して、要求キューが空ではないことを示しているときに、要求キューからパケットを読み出して大容量記憶サブシステムに提供し、また、大容量記憶サブシステムがパケットの処理を完了したときに、パケットを完了キューに供給する第1バック・エンド・コントローラと、

完了キューに接続され、完了ドアベル・レジスタ及び完了ヘッド・レジスタの出力に応答して、完了キューからのパケットを主メモリに戻す完了コントローラとを含んでいることを特徴とするコンピュータ・システム。

#### 【請求項2】

請求項1記載のコンピュータ・システムにおいて、分散型バースト・エンジンは、

リンク・リスト中の次のパケットの物理アドレスを保持するポステド・ヘッド・レジスタと、

20

プロセッサの請求に基づくことなくデータをプロセッサに転送する際に大容量記憶サブシステムにより使用されるパケットを保持するポステド・キューと、

主メモリ中の次のパケットが大容量記憶サブシステムのために取得できることを表すプロセッサからの指示を受け取るポステド・ドアベル・レジスタと、

ポステド・キューに接続され、ポステド・ドアベル・レジスタの出力に応答して、主メモリからポステド・パケットを受け取ってポステド・キューに書き込む第2フロント・エンド・コントローラと、

ポステド・キュー及び完了キューに接続され、かつ大容量記憶サブシステムの出力に応答し、ポステド・キューが空ではないときにポステド・キューからパケットを受け取って該パケットを大容量記憶サブシステムに提供し、大容量記憶サブシステムがパケットの処理を完了したときに、完了キューに該パケットを供給する第2バック・エンド・コントローラと

30

を備えていることを特徴とするコンピュータ・システム。

#### 【請求項3】

請求項2記載のコンピュータ・システムにおいて、第2バック・エンド・コントローラはさらに、プロセッサがポステド・ドアベル・レジスタを駆動した場合に、主メモリからパケットを取得することを特徴とするコンピュータ・システム。

#### 【発明の詳細な説明】

#### 【発明の属する技術分野】

40

#### 【0001】

本発明は、インテリジェント入出力デバイスと通信する方法、及び入出力デバイスとホストとの間で自動的にデータ転送を行なう装置に関するものである。

#### 【0002】

#### 【従来の技術】

コンピュータ・システムが発展するに連れて、その都度一層強力かつ先進の特徴が取り入れられている。PCIバス、即ち、周辺要素相互接続バスのような多くの新しい進んだバス構造が開発され、コンピュータ・システムの性能向上をもたらした。加えて、近年のパソコン・コンピュータが接続及びマルチメディア指向システム(connected and multimedia oriented system)の色合いを強めるに連れて、ユニバーサル・シリアル・バス及びフ

50

アイアウエア(Firewire)としても知られている I . E . E . 1 3 9 4 (電気電子学会)のような新たなシリアル通信バスが開発されている。しかしながら、これらの投入は、その度毎に、プロセッサに対するデータの管理及び移動の要求を増々増大させることになる。

今日のオペレーティング・システムは、真のマルチタスク・オペレーティング・システムであり、所与のタイム・スライス間で多数のタスクのバランスを保つ役割を担っている。プロセッサに対して入出力動作を処理する要求が増大するに連れて、各タスクに適当なプロセッサ時間量を与えるようにタスクのバランスを適正に保つことが一層難しくなる。更に、割り込みが問題を複雑にする。何故なら、割り込みは予測不可能であり、通常素早くそれに対応しなければならないからである。

10

### 【0003】

#### 【発明が解決しようとする課題】

過去において、ある種の処理をコプロセッサに割り振る(load off)ことによって、プロセッサの負荷配分(loadering)の問題を解決しようとする試みがなされている。算術演算用コプロセッサ(math co-processor)又はダイレクト・メモリ・アクセス・コントローラ(DMA)が、よく知られている例である。しかしながら、算術演算用コプロセッサは、企業に固有のインターフェース及び命令によってプロセッサに強く結び付けられているので、汎用の入出力への応用には適していない。DMAは、一旦そのコンフィギュレーションが設定されたならば、データの移動には好適であるが、各データ・ブロック毎にコンフィギュレーションを必要とする。したがって、DMAコントローラは、単一のデータ・ブロックを超えて独立して機能することができない(そのコンフィギュレーションをデマンド・モード用に設定するのでない場合)。更に、DMAコントローラは、ハードウェアのレベルで機能する。DMAコントローラは、処理(service)対照のデータ型又はデバイス型についての理解(comprehension)を有していない。したがって、プロセッサが常に関与している。過去において、DMAコントローラは、データをあるアドレスから他のアドレスに移動させるには格段に効率的であったが、しかしながら、今日のプロセッサはそれよりもはるかに効率的であるので、そのリード/ライト・サイクル・タイムはDMAコントローラのそれに近づきつつある。したがって、DMAコントローラの利点は、時とともに減少している。更に、高性能DMAコントローラによって与えられるいすれの価値(gain)も、典型的に、次世代プロセッサによって相殺されてしまっている。

20

他にも、インテリジェント入出力(I<sub>2</sub>O)処理を開発する試みがなされたが、これらは、Intel i960RPプロセッサのような埋め込み型プロセッサを対象としたものであった。これらの解決策はプロセッサの独立を達成するが、それを行なうためのコストは非常に高い。したがって、インテリジェント入出力処理に対する安価な解決策が必要とされている。

30

### 【0004】

#### 【課題を解決するための手段】

本発明は、ホスト・プロセッサ、メモリ、及び1つ以上の入出力(I/O)デバイスを含む。ホスト・プロセッサはパケットを発生し、I/Oデバイスが後に使用するために、これらをメモリに提出する(submit)。パケットは、アドレス及びその他の情報を収容するためのヘッダ部分と、データ又はメッセージを搬送するためのペイロード部分とを含む。パケットは、リスト内において互いにリンクされ、パケット・プールを形成する。パケット・ヘッダは、物理アドレス・フィールド、次パケット物理アドレス・フィールド、仮想アドレス・フィールド、及び次パケット仮想アドレス・フィールドを含む。したがって、一旦パケットが読み込まれたなら、パケットの仮想及び物理アドレス、ならびに次のパケットの仮想及び物理アドレスは知られることになる。第1パケットが、次のパケットの物理アドレス及び仮想アドレスを収容し、リンク・リスト(linked list)を形成する。一旦リンクが確立されたなら、仮想アドレス上又は物理アドレス上のいずれかにおいて、それ以上のアドレス変換を必要とすることなく、パケット・プールを処理することができる。仮想及び物理アドレス・フィールドは、ヘッダの予め規定された位置にあるので、インデックス機能(indexing)を用いて必要なアドレスを読み出すことができる。

40

50

## 【0005】

パケットの移動を容易に行なうために、分散型バースト・エンジン（D B E : distributed burst engine）を開示する。これは、1つ以上の入出力（I / O）デバイスと主メモリとを結合するものである。分散型バースト・エンジンは、単一のI / Oデバイスのバス・インターフェース、ブリッジ・デバイス、又はメモリ・コントローラのいずれにも位置することができる汎用性のある構成物であり、これによって多数のI / Oデバイスに結合する。

分散型バースト・エンジン・アーキテクチャは、キュー・スキームを定義し、プロセッサにパケットの物理アドレスをデバイス・レジスタに書き込ませることなく、プロセッサが連続的にパケットをI / Oデバイスに整列（キュー：queue）することを可能にする。パケットが互いにリンクされているので、D B Eは常に、次のパケットがどこで得られるかについて知っている。これにより、D B Eがプロセッサの介入を受けずに、メモリからのデータをバーストすることを可能にする。10

## 【0006】

D B Eは、フロント・エンドとバック・エンドとの間に、パケットを保持するための3つのデータ・バッファ、即ち、先入れ先出しメモリ（F I F O）を含む。それらは、要求バッファ、ポステッド・バッファ（posted buffer）、及び完了バッファである。D B Eのフロント・エンドは、全体的に、メモリからパケットを引き出し、要求バッファ及びポステッド・バッファを満杯に保持しつつ、パケットをメモリに押し出して、完了バッファを空の状態に保つ役割を担っている。D B Eのバック・エンドは、1つ以上のI / Oデバイスと双方向処理を行い、パケットからのコマンド、制御、アドレス、及びデータ情報をI / Oデバイスに提示する。20

リンク・リストにおける加入及び削除に対するパケットの移動を容易に行なうために、D B E及びプロセッサによって、ヘッド・レジスタ及びテール・レジスタが保持されている。また、D B Eは、新たな要求パケットが要求キューにリンクされたというような、イベントが発生したことの指示をプロセッサから受け取るためのドアベル・レジスタ（doorbell register）も含む。例えば、プロセッサが要求パケットを要求キューに整列した後、プロセッサは要求ドアベルを鳴らす。パケットはリンクされており、D B Eは次のパケットの位置を保持しているので、D B Eは、これに応答して、単にメモリからパケットを引き出し、それをI / Oデバイスに提示する。コマンド又はデータは、パケット内に収容されている。30

## 【0007】

単一のI / Oデバイスが多数の機能を提供することができるので、多数の要求チャネルが利用可能となり、各要求チャネル毎に、要求バッファ、要求ドアベル、ならびに対応するヘッド・レジスタ及びテール・レジスタを有する。

パケットは、当該パケットに関する情報を搬送するためのヘッダを含む。パケットは、非同期、割り込み又はポール・パケット（polled packet）として指定することができる。非同期パケットは、当該パケットが完了したことの通知を必要としない要求に有用である。割り込みパケットは、完了の通知を必要とする要求パケットに有用である。非請求（unolicited）パケットも、割り込みパケットとして指定される。割り込みパケットが完了した場合、D B Eによってプロセッサに割り込みを発生する。ポール・パケットは、完了の通知を必要とするが、ハードウェア割り込みの形態ではない通知でよい要求に有用である。この形式のパケットは、ハードウェアの割り込みに伴うオーバーヘッドを回避するのに役立つ。40

パケット・ヘッダ内に、ポール・パケットが完了したか否かを示すビットが1つある。したがって、プロセッサは、連続的にこのアドレス上で読み出し即ち「スピン（spin）」を行い、通知を受け取らなければならない。プロセッサがパケットをポールしている間メモリ・バス帯域を占領することを防止するために、パケット・ヘッダは、都合よくプロセッサのキャッシュライン内に位置するように設計されている。したがって、プロセッサは、D B Eが前述のビットを変化させたときに、キャッシュ・ミスが発生するまで、そのキャッシュ

シュー上でポールする。

#### 【0008】

##### 【発明の実施の形態】

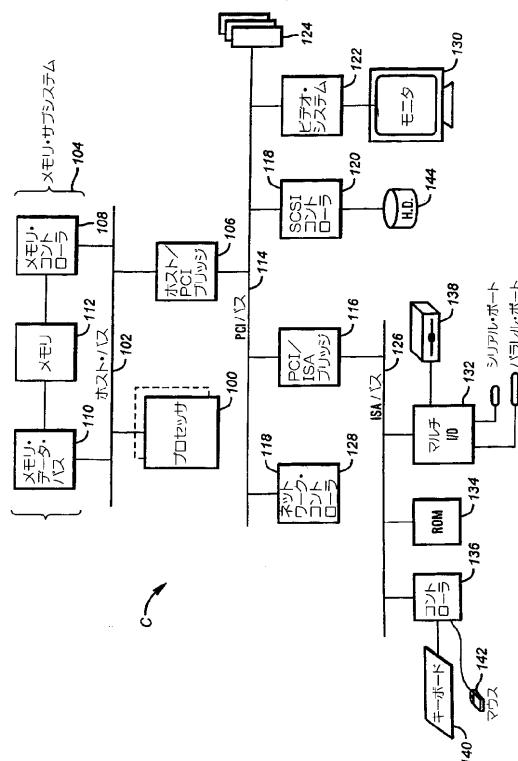

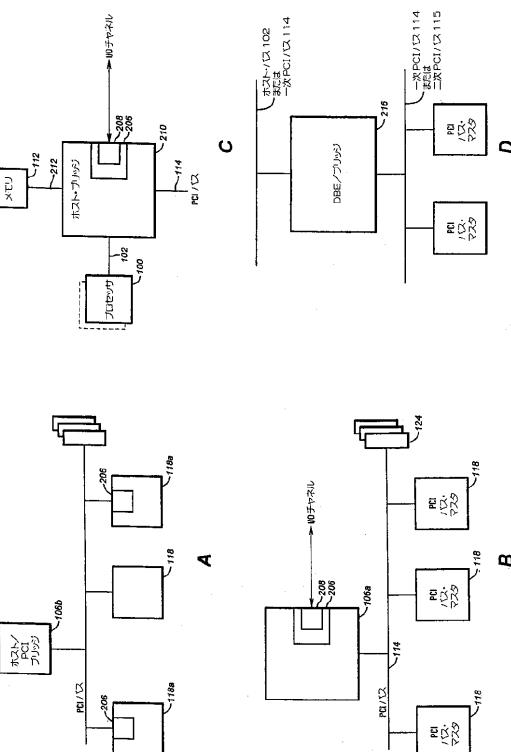

図1は、本発明の好適な実施形態によるコンピュータ・システムCを示している。コンピュータ・システムCは、インテル社のペンティウム・プロ・プロセッサ(Intel Pentium Pro processor)等のような、1つ以上のプロセッサ100を含む。1つのプロセッサ100のみを示すが、本発明は單一プロセッサ・コンピュータに限定される訳ではない。プロセッサ100は、ホスト・バス102に結合されている。

ホスト・バス102には、メモリ・サブシステム104、及びIntel 82454KX等のような、ホスト・PCI間のブリッジ・デバイス106が結合されている。ホスト・PCIブリッジ・デバイスは、プロセッサ・サイクルをPCIサイクルに、及びその逆に変換し、PCIバス114に接続する。メモリ・サブシステム104は、それ自体、Intel 82453KX等のようなメモリ・コントローラ108、Intel 82452KX等のようなメモリ・データ・バス・デバイス、及び主メモリ・アレイ112からなる。メモリ・コントローラ108は、主メモリ112にアドレス信号及び制御信号を供給する。主メモリ112は、複数のダイナミック・ランダム・アクセス・メモリ(DRAM)デバイス(具体的には示さない)で構成されている。メモリ・データ・バス・デバイス110は、メモリ・コントローラ108と共に動作し、ホスト・バス102のデータ部分と複数のDRAMとの間のバッファ動作(buffering)を行なう。勿論、他の公知の様々なメモリ・サブシステムを利用することも可能である。20

#### 【0009】

また、PCIバス114には、PCI/ISA(業界標準アーキテクチャ)ブリッジ116、小型コンピュータ・システム・インターフェース(SCSI)コントローラ120のような1つ以上のPCIバス・マスタ118、及びネットワーク・インターフェース・コントローラ128も接続されている。更に、PCIバス114には、ビデオ・システム122及び1つ以上のPCIスロット124が接続されている。PCI/ISAブリッジ116は、PCIサイクルをISAバス・サイクルに、及びその逆に変換し、ISAバス126に接続する。また、PCI/ISAブリッジ116は、強化したダイレクト・メモリ・アクセス(DMA)コントローラ、割り込みコントローラ、タイマ/カウンタ、及びノンマスクブル割り込みロジック(non-maskable interrupt logic)ならびに種々の周辺デバイス用デコード・ロジックを統合する。SCSIコントローラ120は、ハード・ディスク144、テープ・ドライブ、及びCD-ROMのようなSCSI周辺機器に接続可能である。ビデオ・システム122は、ビデオ・コントローラ、フレーム・バッファ、及びモニタ130に接続するための種々のロジックを含む。ネットワーク・インターフェース・コントローラ128は、イーサネット・ネットワークに接続するための種々のインターフェース回路、又は代わりにトーケン・リング・ネットワークを含む。SCSIコントローラ120及びネットワーク・コントローラ128は、バス・マスタの多くの例の内の2つに過ぎず、これらを総称してPCIバス・マスタ118と呼ぶことにする。尚、ここに開示する原理は、PCIバス114以外にも、ISA又はEISAのようなバス・マスタリング(bus mastering)に対応するその他のバスにも適用可能である。30

ISAバス126は、更に、マルチI/Oデバイス132、リード・オンリ・メモリ(ROM)134、及びキーボード・コントローラ136にも接続する。マルチI/Oデバイスは、フロッピ・ディスク・ドライブ138に接続するためのフロッピ・ディスク・コントローラを含む。また、マルチI/Oデバイス内には、多数のシリアル・ポート回路及びパラレル・ポート回路が収容されている。ROMは、電力投入時にハードウェアを起動するための低レベル・コードを与える。キーボード・コントローラは、キーボード140及びマウス142との通信を扱う。40

#### 【0010】

##### システム・アーキテクチャ

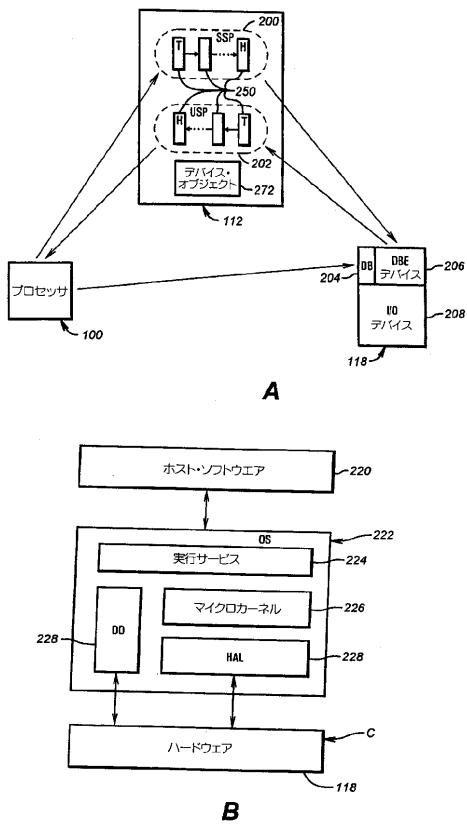

次に、図2のAのブロック図を参照する。本発明で特に興味深いのは、プロセッサ100

10

20

30

40

50

が PCI バス・マスタ 118 と、及びその逆方向に、通信する方法である。各 PCI バス・マスタ 118 毎に、主メモリ 112 において初期化時に、請求パケット・プール(solicited packet pool) 200 及び非請求パケット・プール(unolicited packet pool) 202 が形成される。パケット・プールを収容するメモリ 112 のエリアは、プロセッサ 100 と PCI バス・マスタ 118 との間で共有される。請求パケット・プール 200 は、1 つ以上のパケット 250 を収容し、これらは、プロセッサ 100 によって、目標の PCI バス・マスタ 118 へのデータを請求する際に用いられる。非請求パケット・プール 202 は、2 つ以上のパケット 250 を収容し、これらは、PCI バス・マスタ 118 によって、非請求データ(unsolicited data)をプロセッサ 100 に伝達する際に用いられる。非請求データとは、マウス 142 又はネットワーク・コントローラ 128 によって受け取られたデータのように、PCI バス・マスタ 118 によって、非同期データ源から自発的に受け取られたデータのことである。10

パケット・プールを構成するパケット 250 は、初期化時にリンクされ、リストを形成する。各リストは、ヘッド H ポインタとテール T ポインタとを有し、これらに他のパケット 250 をリンクすることができる。請求パケット・プール 200 内に位置するパケット 250 は、好ましくは同一の長さで、共に仮想アドレスによってリンクされている。非請求パケット・プール 202 内に位置するパケット 250 は、好ましくは同一の長さで、共に物理アドレスによってリンクされている。

#### 【0011】

メモリ 112 と PCI バス・マスタ 118 との間のパケットの移動を容易に行なうために、各 PCI バス・マスタ 118 は、分散型バースト・エンジン(DBE) 206 を含むことが好ましい。DBE 206 は、本質的に、I/O デバイス 208 のためのインテリジェント・ダイレクト・メモリ・アクセス(DMA) コントローラである。DBE の機能は、プロセッサ 100 からの介入なく、パケット 250 を読み出し、送ることである。I/O デバイス 208 は、本質的に、SCSI コントローラのように、DBE 206 と通信するように構成された従来からの I/O コントローラである。20

各 DBE 206 は、1 つ以上のドアベル・レジスタ(doorbell register) 204 を含む。ドアベル 204 は、プロセッサ 100 が「鳴らして(ring)」、メモリ 112 において 1 つ以上のパケット 250 の準備が完了しており、使用可能であることを、目標 I/O デバイス 208 に通知する。その後、I/O デバイス 208 は、DBE 206 を介して、パケットをメモリ 112 から引き出し、即ち、読み出し、パケット 250 の内容に応じてそれらを処理する。30

#### 【0012】

I/O デバイス 208 が外部ソースからデータを受け取った場合、DBE 206 によって非請求パケットが準備され、メモリ 112 内に格納される。DBE 206 が未請求データ・パケットをメモリ 112 内に格納した後、プロセッサ 100 に割り込みをかけ、パケットが処理可能であることをプロセッサ 100 に通知する。

1 つ以上の論理通信チャネル 214 が、プロセッサ 100 と I/O デバイス 208 との間に存在する可能性がある。例えば、I/O デバイス 208 は、入来データ専用に 1 つのチャネル 214、出立データに別のチャネル 214、ならびにコマンド及び制御のために第 3 のチャネル 214 を有することができる。40

したがって、プロセッサ 100 と PCI バス・マスタ 118 との間の直接通信は、このコマンド・パケット・アーキテクチャによって減少即ち制限される。このプロセッサ 100 及び PCI バス・マスタ 118 間の、コマンド・パケット・アーキテクチャによる切り離しの結果、多数の利点が得られる。その利点の中には、ハードウェア割り込みの減少、グラフィックスやオーディオのようなプロセッサ 100 の集約的アプリケーション(intensive application)に対する処理能力向上、及びプロセッサ 100 の目標 I/O デバイス 208 から読み出し不要が含まれる。

#### 【0013】

次に図 2 の B を参照すると、本発明のデバイス・ドライバがどのようにしてメモリ 112

10

20

30

40

50

と通信するかについて示されている。従来技術では、プロセッサ100は、デバイス・ドライバを介してI/Oデバイスと直接通信し、デバイス・ドライバが、I/Oデバイス上のメモリ・マップI/Oレジスタ(memory mapped I/O register)のコンフィギュレーション(環境設定)を行い、I/Oデバイスに処理を行なわせていた。その処理が完了した後、I/Oデバイスはプロセッサ100に割り込みをかけ、一方プロセッサ100は、割り込み源に関して、I/Oデバイス上のステータス・レジスタをプロセッサ100にチェックさせる。

本発明の好適な実施形態によれば、要求は、ホスト・ソフトウェア・アプリケーション220から、Windows NTのようなオペレーティング・システム(OS)222に発生する。OS222は、全体として、ある実行サービス224、マイクロカーネル226、ハードウェア抽象レイヤ(HAL: hardware abstraction layer)228、及び1つ以上のデバイス・ドライバ230を有するI/Oシステムを含むカーネルで構成されている。デバイス・ドライバ230は、メモリ112やPCIバス・マスター118のようなハードウェアCと直接通信することを許可されている。各PCIバス・マスター118毎に、少なくとも1つのデバイス・ドライバ230があることは理解されよう。DBEデバイス206に対するデバイス・ドライバ230は、いずれかのプロセッサ100の特権レベル(インテル社のプロセッサ上における「リング」レベル)で実行するためには不要である。ドライバ230は、カーネル・モード又はユーザ・モードで実行することができる。

#### 【0014】

デバイス・ドライバ230とは、ここでは、Windows、Windows NT、OS/2等のようなオペレーティング・システムに関する技術分野では公知のデバイス・ドライバのクラスを意味する。しかしながら、本発明にしたがって記載されるデバイス・ドライバ230は、当技術分野では新規なものであることは理解されよう。ここの開示は、本発明にしたがってデバイス・ドライバを開発するための十分な手引きを当業者に提供する。

デバイス・ドライバ230は、DBEデバイス206及びホスト・ソフトウェア220との双方向処理に関して、6つの主要な機能を有するものと見ることができる。これらの機能は、初期化/初期化解除(initialization/deinitialization)、パケット提出(packet submission)、パケット完了(packet completion)、同期ダイレクト・アクセス、パケット取り消し、パケット・プールの増減である。

ドライバ230は、システムの初期化中に、DBEデバイス206及びI/Oデバイス208を初期化しなければならない。一旦DBEデバイス206及びI/Oデバイス208が初期化され、要求を受け入れ可能となったなら、ドライバ230は、デバイス要求を開始することができ、DBEデバイス206はデータ転送を開始することができる。次いで、デバイス・ドライバ230は、パケットに対して適切な完了シーケンスを実行することができる。これらの詳細については、以下で論ずる。

尚、デバイス・ドライバ230はプロセッサ100上で実行することが好みないので、オペレーティング・システム222によって実行されるパケット処理に言及する場合、用語は相互交換可能に用いることができることを注記しておく。加えて、「ホスト」という用語は、ときとして、プロセッサ100、ホスト・ソフトウェア220、及びデバイス・ドライバ230全体に論理的に言及するために用いることもある。このような場合、番号指定はプロセッサ100と同一とする。即ち、ホスト100とする。

#### 【0015】

##### パケット

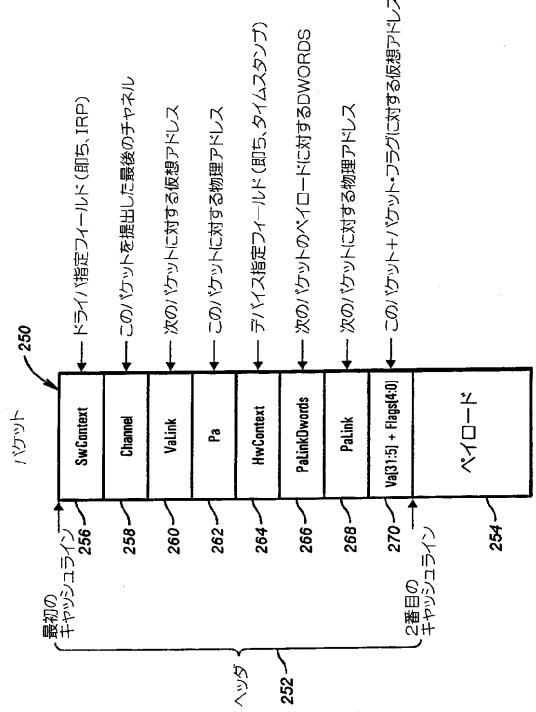

DBE206の更なる詳細に進む前に、パケット250について更に詳しく理解する必要がある。ここで図3を参照すると、好適な実施形態によるパケット250が示されている。パケット250は、2つの主要部分、即ち、32バイトのヘッダ252及び可変サイズのペイロード254からなる。各パケットは、64バイトの境界、即ち、Pentiumのキャッシュラインに整合されている。このようにすれば、最初のキャッシュラインがヘッダ252を収容し、後続のキャッシュラインはペイロード254を収容することができる。ペイロード254は、デバイスに特定のデータを保持し、4バイト刻みで4~256バイト

10

20

30

40

50

の範囲を取ることができる。

ヘッダ252は、8つの32ビット・フィールドで構成され、ソフトウェア・コンテクスト(SwContext)フィールド256、チャネル・フィールド258、仮想アドレス・リンク(Palink)フィールド260、物理アドレス(Pa)フィールド262、ハードウェア・コンテクスト(HwContext)フィールド264、物理アドレス・リンクDword(PaLinkDwords)フィールド266、物理アドレス・リンク(PaLink)フィールド268、及び仮想アドレス(Va)フィールド270を含む。リンク・フィールドは、パケットのリンク・リスト形成を可能にする。

#### 【0016】

SwContextフィールド256は、ホスト・ソフトウェア220が、適切と見なすいすれかの方法で使用するために予約されている32ビット・フィールドである。ソフトウェアは、このフィールドを用いて、このパケット250に関連するOSに特定の情報を埋め込むことができる。その一例をあげるとすれば、パケット250内のI/O要求と関連するI/O要求パケット(IRP)の仮想アドレスを置くことであろう。これによって、デバイス・ドライバ230は、I/O完了の間に、I/O要求パケットを直接復元することができ、未決要求のリストを管理する必要がなくなる。

チャネル・フィールド258は、パケットが関連した最後のチャネル214の番号を収容する32ビット・フィールドである。チャネル214は、論理通信リンクである。各I/Oデバイス208は、2つ以上のチャネル214を有する場合がある。一方、1つ以上のI/Oデバイスに対応するDBE206は、2つ以上のチャネル214を有する場合がある。例えば、1つのチャネル214をデータ転送のために割り当て、他方のチャネル214をコマンド及びステータスのために割り当てる場合もある。このフィールドは、非請求パケット・プール202内のパケットに対しては、「0」を収容する。

#### 【0017】

Vaフィールド270、Valinkフィールド260、Paフィールド262、及びPaLinkフィールド268は、パケット・ヘッダ252内に収容され、物理メモリ及び仮想メモリ間の多数のアドレス変換を不要とする。物理メモリはメモリ112である。Pentium及び同等のプロセッサ100は、物理メモリ112を効率的に使用するために、ハードウェア・メモリ管理機構を採用している。典型的に、プロセッサ100上で実行するプログラムは直接物理メモリ112にアドレス指定するのではなく、代わりに、仮想アドレスを用いてメモリ112にアクセスする。各パケット250内に仮想アドレス・フィールド及び物理アドレス・フィールドの双方を備えることにより、パケット250を初期化するときに、変換を1回だけ行えば済むようになる。このように、デバイス・ドライバは仮想アドレスを用いて動作することができ、一方DBE206は物理アドレスを用いて動作することができ、各々同じパケット250を用いて通信する。

#### 【0018】

Vaフィールド270は、以下のフィールドで構成された32ビット・フィールドである。

#### 【表1】

表 1

| ビット  | 説明                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | デバイス・ドライバが見る場合のこのパケットに対する仮想アドレスを収容する。                                                                                                                                          |

| 5    | 予約                                                                                                                                                                             |

| 4    | 0 - プロセス・パケット<br>1 - キャンセル・パケット<br>取り消しビット。パケットの処理状態を表す。デバイス・ドライバはこのビットをセットして、パケット 250 を処理せず、直ちに完了しなければならないことを、DBE デバイス 206 に示す。                                               |

| 3    | 0 - 通常の提出<br>1 - ダイレクト・アクセスの開始<br>ダイレクト・アクセス・ビット。ドライバは、このパケットの完了後ダイレクト・アクセスを行うことを、DBE デバイス 206 に示す。受け取られた場合、DBE 206 は、ダイレクト・アクセスが終了するまで、それ以上のデータを引き出さない。「1」の場合、このパケットを直ちに完了する。 |

| 2:1  | 00 - ヌル提出状態<br>01 - 非同期パケット<br>10 - ポール・パケット<br>11 - 割り込みパケット<br>提出型ビット。このパケットがどのように DBE デバイスに提出されたかを表す値を収容する。未請求ポール内のパケットは、このフィールドには全て 0 を有する。                                |

| 0    | 0 - 未請求パケット・プール<br>1 - 請求パケット・プール<br>パケット型ビット。どのプールにパケットが属するかを示す。                                                                                                              |

10

20

30

## 【0019】

VaLink フィールドは、リスト内の次のパケットの仮想アドレスを収容する 32 ビット・フィールドである。このフィールドは、リンクされているパケットがない場合、ヌルとなる。このフィールドは、DBE デバイス 206 が完了したときに、空きパケットを再び請求パケット・プール 200 にリンクする際に DBE デバイス 206 によって用いられる。空きパケット(free packet)とは、既に完了し、現在は再び「自由に」使用できるパケットのことである。DBE 206 デバイスは必ずしも仮想アドレス処理を理解している訳ではないが、単純にパケット 250 内に収容されている仮想アドレスのリード及びライトを行うことによって、仮想アドレスを用いてパケット 250 をリンクすることができる。

Pa フィールド 262 は、パケット 250 の物理アドレスを収容する 32 ビット・フィールドである。これは、DBE デバイス 206 が見て使用するアドレスである。

PaLink フィールド 268 は、リスト内の次のパケット 250 の物理アドレスを収容する 32 ビット・フィールドである。

HwContext フィールド 264 は、DBE デバイス 206 が適切とみなすいずれかの方法で、その特定の実装によって用いるために予約されている 32 ビット・フィールドである。例えば、これを用いて、キャッシュされていないメモリ範囲へのアドレスを埋め込むことにより、ペイロード 254 なしでパケット 250 を作成することが可能となる。

PaLinkDwords フィールド 262 は、次のパケットのペイロード 254 のサイズを収容する 32 ビット・フィールドである。そのサイズは、連続する 4 バイトのチャンク(chunk)の数として表現することが好ましい。

40

50

**【 0 0 2 0 】**

このように、パケット構造及びプロトコルが定義され、これによって、デバイス・ドライバ230は、I/Oデバイス208とパケットを通信することが可能となる。デバイスの初期化時に、プロセッサ100は、I/Oデバイス208に対して、特定数のパケットを形成する。次に、デバイス・ドライバ230は、I/Oデバイス208と通信する際、メモリ112に格納されているパケット250にコマンド及びデータを書き込み、パケット250を処理する準備ができていることをDBE206に通知する。DBE206は、メモリ112からパケット250を読み出し、それを解析してドライバ230が要求した処理を判定する。どのようにパケット250をDBE206に発行したかに応じて、DBEデバイスがどのように処理を完了し、ドライバ230のためにパケット250をメモリ112に戻すのかが決定される。10

パケット250は、Vaフィールド270に示される3つの方法、即ち、非同期、ポール、又は割り込みの内の1つで提出することができる。デバイス・ドライバ230は、完了通知を必要としない又は望まない場合に、非同期パケットを提出する。グラフィックス・コントローラ122のビット・ブリット(BLT:bit-blit)処理が、その一例である。

**【 0 0 2 1 】**

デバイス・ドライバ230は、完了通知を必要とする場合、I/Oデバイス118によってアサートされたハードウェア割り込みによって、割り込みパケットを提出する。

デバイス・ドライバ230は、ホスト・ソフトウェア220がポーリングを要求するような状況に対して、ポール・パケットを提出する。場合によって、ポール・パケットの方が効率的な手段完了通知(means completion notification)となることもある。例えば、SCIコントローラ120に対する典型的な要求は、「セクタ・リード」と「セクタ・ライト」動作である。従来技術のオペレーティング・システムは、その殆どが、デバイス・ドライバに要求を完了するのを「待つ」ように要求するセクタ・データのリード及びライトを行うためのコール側アプリケーションの目標バッファを表す、物理ページのリストを備えている。要求の完了を示すディスク・デバイスによる通知の際に、ドライバは、コール側のアプリケーションの目標バッファのために、メモリを解放することができる。目標デバイスに基づいて、ドライバにとっては、ハードウェア割り込みの結果としてコンテクストの切り替えを誘発するよりはむしろ、特定の処理上で「ポール」することによって、完了通知を「待つ」方が一層効率的な場合がある。したがって、本発明は、デバイス・ドライバ230が、DBEデバイス206に要求を提出し、I/Oデバイス208がその要求を終了するまで、パケット250上でポールするための方法を提供する。2030

**【 0 0 2 2 】****パケット・キュー**

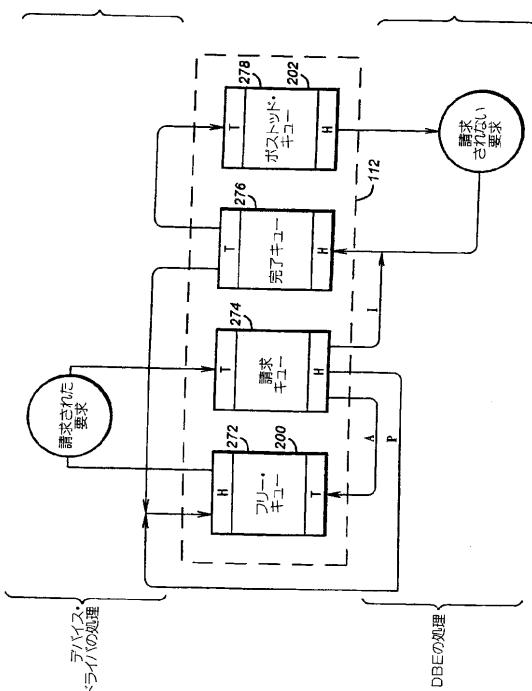

初期化時に、デバイス・ドライバ230は、請求パケット・プール200及び非請求パケット・プール202を形成する。図4には、これらのパケットのリンク・リストの形成に関して更に詳細に示されている。デバイス・ドライバ230及びメモリ112間ならびにDBEデバイス206及びメモリ112間双方におけるパケットのフローを管理するために、4つのキュー272～278が形成される。即ち、フリー・キュー(FQ: free queue)272、要求キュー(RQ: request queue)274、完了キュー(CQ: completion queue)276、及びポステッド・キュー(PQ: posted queue)278である。フリー・キュー272は、請求パケット・プール200と同一であり、ポステッド・キュー278は非請求パケット・プール202と同一である。これら4つのキュー272～278の各々は、ヘッドHポインタ及びテールTポインタを有する。40

デバイス・ドライバ230は、フリー・キュー272のヘッドH及び残りの3つのキュー274～278のテールTを保持する。DBEデバイス206は、フリー・キュー272のテールT及び残りの3つのキュー274～278のヘッドHを保持する。

**【 0 0 2 3 】**

フリー・キュー272は、デバイス・ドライバ230がDBEデバイス206との通信に使用する際に利用可能なパケット250を収容する。ホスト・ソフトウェア220から50

要求が出されると、デバイス・ドライバ230は、フリー・キュー272のヘッドHからパケット250のリンクを解除し、パケットのペイロード254を満たし、パケット250を要求キュー272のテールTにリンクする。パケット250は、非同期的(A)、ポール(P)又は割り込み(I)のいずれかによって提出することができる。

D B E デバイス206は、受け取った要求を処理する際に、パケット250のリンクを要求キュー274から解除し、ペイロード254をI/Oデバイス208に受け渡し、それらの提出方法にしたがってパケット250を完了する。更に具体的には、非同期パケットAの完了は、デバイス・ドライバ230に通知せずに行い、フリー・キュー272のテールTで完了する。ポール・パケットPは、デバイス・ドライバ230によって、フリー・キュー272のヘッドHに戻され、割り込みパケットIの完了は、完了キュー276を通じて行う。

#### 【0024】

割り込みパケットについては、D B E デバイス206が割り込みパケットIを完了キューのヘッドHにリンクした後、ハードウェア割り込みを発生すればよい。完了キュー276が空の場合、パケット250をリンクするときに割り込みを発生する。完了キュー276が空でない場合、続いてリンクされるパケットは割り込みを発生しない。デバイス・ドライバ230は、完了キュー276からのパケット250のリンクを解除し、ペイロード254を除去し、Vaフィールド270のビット0に基づいて、パケットをフリー・キュー272又はポステッド・キュー278のいずれかに戻す。

ポステッド・キュー278は、ホスト側の請求に基づくことなくホスト側にデータを転送することを要求する非請求要求のためにパケット250を保持する。非請求要求が発生した場合、D B E デバイス206は、ポステッド・キュー278からのパケット250のリンクを解除し、ペイロード254をデータで満たし、パケット250を完了キュー276にリンクする。パケットのリストが未だ完了キュー276上にない場合、ハードウェア割り込みを発生する。

#### 【0025】

##### D B E に対するソフトウェア・インターフェース

D B E デバイス206は、D B E デバイス・オブジェクト272(図2のA)を通じて、デバイス・ドライバ230に対して抽象化される。D B E デバイス・オブジェクト272は、関連するデータ構造、及びドライバ230とD B E デバイス206との間でパケット・プロトコルを管理するために必要なリソースを収容する。D B E デバイス・オブジェクト272は、メモリ112に格納され、D B E デバイス・ドライバ230によって管理される。

D B E デバイス・オブジェクト272は、コンピュータ・システムC内の特定のD B E デバイス206に対応する。D B E デバイス206は、このデータ構造の概念を有していない。オブジェクト272は、目標D B E デバイス206のリソースを管理するために、デバイス・ドライバ230のみによって作成され使用される。D B E デバイス・オブジェクトのメモリ・フォーマットを変更しても、新たなファンクショナリティがデバイスによって要求されなければ、デバイスには影響を与えない。D B E オブジェクト272をPentiumのキャッシュ・ラインの境界と整合させ、頻繁に参照される隣接するデータ項目上でキャッシュ・ラインが満杯になる回数を減少させる。D B E デバイス・オブジェクト272は、表2に示したデータ構造からなる。

#### 【0026】

##### 【表2】

10

20

30

40

表 2

| パラメータ              | 説明                                                                                                                                                                                                                                                                                                                                     |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DeviceID           | このD B Eオブジェクトの一意のデバイスIDとして使用される32ビット・フィールド。                                                                                                                                                                                                                                                                                            |

| FreeQueue          | ヘッド・パケットに対するアドレスを含む、フリー・キューを管理するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                              |

| CompletionQueue    | テール・パケットに対するアドレスを含む、完了キューを管理するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                |

| RequestQueue       | テール・パケットに対するアドレスを含む、要求キューを管理するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                |

| PostedQueue        | ポスティッド・パケットに対するアドレスを含む、フリー・キューを管理するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                           |

| RegistersVa        | D B Eデバイス206のレジスタの仮想アドレスを保持するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                 |

| RegisterPa         | D B Eデバイス206のレジスタの物理アドレスを保持するためのフィールドを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                 |

| MmioAddressRange   | D B Eデバイスのレジスタをマップするために必要なバイトの範囲を収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                      |

| RequestPacketCount | 請求パケット・プールに割り当てられるパケット数を収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                               |

| RequestPacketSize  | 請求パケット・プールの各パケット毎にDeviceContextフィールドのDwordサイズを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                         |

| PostedPacketCount  | 非請求パケット・プールに割り当てられるパケット数を収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                              |

| PostedPacketSize   | 非請求パケット・プールの各パケット毎にDeviceContextフィールドのDwordサイズを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                        |

| DbeFlink           | この1つ前のD B Eデバイス・オブジェクトへのポインタを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                          |

| Dbeblink           | この1つ後ろのD B Eデバイス・オブジェクトへのポインタを収容する32ビット・メモリ位置。                                                                                                                                                                                                                                                                                         |

| DummyPacket        | このフィールドは、デバイス・ドライバが、要求キューのテール上有るパケットがそれ自体を参照しないことを保証するするために用いられるダミー・コマンド・パケットを示す。この状態は、最後に提出したパケットが、別のパケットを割り当ててデバイスに提出する前に、フリー・キューに戻ってきた場合に発生する可能性がある。<br>DBE_AllocatePacket ルーチンが、パケット・アドレスをコール元に戻す前に、この状態をチェックする。フリー・キューから除去されたパケットが偶然D B Eデバイスに提出された最後のパケットであった場合、DBE_AllocatePacket ルーチンは、除去されたパケット・アドレスを DummyPacket のアドレスと交換する。 |

## 【 0 0 2 7 】

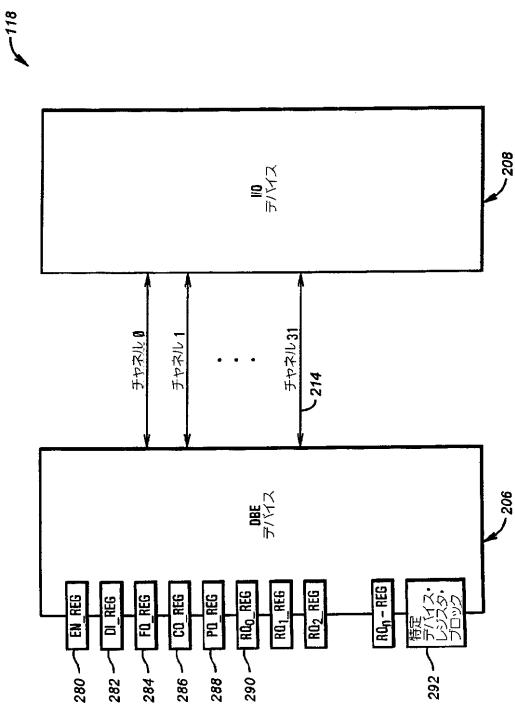

D B Eデバイス・インターフェース

次にD B Eデバイス206に言及するために、図5に注意を向けると、D B Eデバイス206のレジスタ・インターフェースが示されている。D B Eデバイス206は、1組のメモリ・マップI/Oレジスタ280～292を含み、D B Eプロトコルに便宜を図っている。D B Eドライバ206に対応するデバイス・ドライバ230は、システムの初期化中に、コンフィギュレーション情報をレジスタ280～292に書き込む。レジスタ280～292は、プロセッサ100(デバイス・ドライバ)及びD B Eデバイス206双方にアクセス可能である。これらのレジスタは、イベント・イネーブル・レジスタ(EN\_REG)280、イベント・ディスエーブル・レジスタ(D I\_REG)282、フリー・キュー・テール

10

20

30

40

50

- レジスタ(FQ\_REG) 284、完了キュー・ヘッド・レジスタ(CQ\_REG) 286、ポステッド

- バッファ・キュー・ヘッド・レジスタ(PQ\_REG) 288、及び1つ以上の要求キュー・ヘッド・レジスタ(RQ<sub>n</sub>\_REG) 290を含む。

イベント・イネーブル・レジスタ(EN\_REG) 280は、実装に特定の情報を収容するための32ビット・レジスタである。ビット31:2は、カスタム化(customization)のために使用可能である。ビット1:0については、以下で定義する。このレジスタは、32ビット、リード/ライト、ビット・マップ、及びメモリ・マップI/Oレジスタであることの属性を有する。ビットの定義は以下の通りである。

【0028】

【表3】

10

表 3

| EN_REG |            |                                                                   |

|--------|------------|-------------------------------------------------------------------|

| ビット    | プロセッサ・サイクル | 説明                                                                |

| 0      | W          | 0 - このビットに影響なし<br>1 - DBEデバイスを RESET に置く                          |

| 0      | R          | 0 - DBEデバイスは RESET にない<br>1 - DBEデバイスは RESET にある                  |

| 1      | W          | 0 - このビットに影響なし<br>1 - ホスト・プロセッサへのDBE<br>デバイス割り込みをイネーブルする          |

| 1      | R          | 0 - DBEデバイス割り込みはイネー<br>ブルされていない<br>1 - DBEデバイス割り込みはイネー<br>ブルされている |

| 31:2   | R/W        | これらのビットはカスタム使用のため<br>に定義される                                       |

20

【0029】

30

イベント・ディスエーブル・レジスタ(DI\_REG) 282は、デバイス・ドライバ230が、EN\_REG 280によってイネーブルされたイベントをディスエーブルする際に用いられる。EN\_REG 280 及びDI\_REG 282 レジスタは、同一レジスタに対するセット/クリア動作に

対して、個々のビット位置を自動的に反映させる(affect)ために通常必要なリード/修正

/ライト動作を不要とするために実装する。このレジスタは、32ビット、リード/ライト、

ビット・マップ及びメモリ・マップI/Oレジスタであることの属性を有する。ビット定義は以下の通りである。

【表4】

表 4

| DI_REG |            |                                                         |

|--------|------------|---------------------------------------------------------|

| ビット    | プロセッサ・サイクル | 説明                                                      |

| 0      | W          | 0 - このビットに影響なし。<br>1 - DBEデバイスを RESET から取りだす。           |

| 0      | R          | 0 - DBEデバイスは未だ RESET にある。<br>1 - DBEデバイスは RESET 外にある。   |

| 1      | W          | 0 - このビットに影響なし<br>1 - ホスト・プロセッサへのDBEデバイス割り込みをディスエーブルする。 |

| 1      | R          | 0 - DBEデバイス割り込みをイネーブルする。<br>1 - DBEデバイス割り込みをディスエーブルする。  |

| 31:2   | R/W        | これらのビットはカスタム使用のために定義される。                                |

10

20

30

## 【0030】

フリー・キュー・テール・レジスタ(FQ\_REG)284は、請求パケット・プール200上の最後のパケット250、即ち、テール・パケットTの物理アドレスを格納するための32ビット・レジスタである。このレジスタは、システムの初期化中に、デバイス・ドライバ230によって初期化される。その後、このレジスタは、DBEデバイス206によって維持される。この手順を実装するために、DBEデバイス206は、DBEデバイス206がRESETモードにある場合(EN\_REG[0] = "1")、このレジスタのビット[31:5]へのプロセッサ100のライトをラッチする。DBEデバイス206は、物理アドレスのビット[4:0]が"0"を含むことを想定する。

DBEデバイス206は、デバイス・ドライバ230に通知を返送することなく、請求パケット・プール200のテールTへの非同期パケット(以下で論ずる)を完了する。デバイス・ドライバ230は、DBEデバイス206が、完了した非同期パケット250にリンクするための場所を有するために、請求パケット・プール200上に少なくとも1つのフリー・パケット250を保持しなければならない。このレジスタは、32ビット、リード/ライト、ビット・マップ及びメモリ・マップI/Oレジスタであることの属性を有する。ビット定義は以下の通りである。

【表5】

40

表 5

| FQ_REG |            |                                                                                            |

|--------|------------|--------------------------------------------------------------------------------------------|

| ビット    | プロセッサ・サイクル | 説明                                                                                         |

| 31:5   | W          | Pentium キャッシュラインに整合した請求パケット・プールのテール上のパケットの物理アドレス。ライトは、RESET モードにある D B E デバイスによってのみラッチされる。 |

| 4:0    | W          | D B E デバイスは常に無視する。                                                                         |

| 31:0   | R          | 請求パケット・プール上の最後のパケットの物理アドレスを生成する。                                                           |

10

## 【 0 0 3 1 】

完了キュー・レジスタ(CQ\_REG) 2 8 6 は、メモリ 1 1 2 内に位置する完了リスト・ヘッドの物理アドレスを格納するための 3 2 ビット・レジスタである。CQ\_REG 2 8 6 は、D B E デバイス 2 0 6 によって構築された完了リストのヘッドを置く位置の 4 ビット整合物理アドレスを用いて、デバイス・ドライバ 2 3 0 によって初期化される。その後、CQ\_REG 2 8 6 は、D B E デバイス 2 0 6 によって維持される。この手順を実装するために、D B E デバイス 2 0 6 は、D B E デバイス 2 0 6 が RESET モードにある場合(EN\_REG[0] = "1")、このレジスタのビット[31:2]へのプロセッサ 1 0 0 の書き込みをラッチする。D B E デバイス 2 0 6 は、物理アドレスのビット[1:0]が"0"を含むことを想定する。

20

## 【 表 6 】

表 6

| CQ_REG |            |                                                                        |

|--------|------------|------------------------------------------------------------------------|

| ビット    | プロセッサ・サイクル | 説明                                                                     |

| 31:2   | W          | DWORD に整合した、完了キュー・ヘッドの物理アドレス。ライトは RESET モードにある D B E デバイスによってのみラッチされる。 |

| 1      | W          | 0 - D B E デバイスは常に無視する。                                                 |

| 0      | W          | 0 - このビット位置には影響なし。<br>1 - D B E デバイスが RESET モード以外の場合にのみ、CQ ドアベルをセットする。 |

| 31:0   | R          | このレジスタの現内容を生成する。                                                       |

30

## 【 0 0 3 2 】

ポステッド・キュー・レジスタ(PQ\_REG) 2 8 8 は、非請求パケット・プール 2 0 2 内の最初のパケット 2 5 0 の 3 2 ビット整合物理アドレスを格納するための 3 2 ビット・レジスタである。PQ\_REG 2 8 8 は、システムの初期化中に、デバイス・ドライバ 2 3 0 によって初期化される。その後、PQ\_REG 2 8 8 は、D B E デバイス 2 0 6 によって維持される。この手順を実装するために、D B E デバイス 2 0 6 は、D B E デバイス 2 0 6 が RESET モードにある場合(EN\_REG[0] = "1")、このレジスタのビット[31:5]へのプロセッサ 1 0 0 のライトをラッチする。D B E デバイス 2 0 6 は、物理アドレスのビット[4:0]が"0"を含むこ

50

とを想定する。D B E デバイスはこのレジスタを読み取り、非請求データをメモリ 112 のどこに書き込むかの決定を行う。

【表 7】

図 7

| PQ_REG |            |                                                                                            |

|--------|------------|--------------------------------------------------------------------------------------------|

| ビット    | プロセッサ・サイクル | 説明                                                                                         |

| 31:5   | W          | Pentium キャッシュラインに整合した非請求パケット・プール内の最初のパケットの物理アドレス。ライトは、RESET モードにある D B E デバイスによってのみラッチされる。 |

| 4:1    | W          | 0 0 0 0 - D B E デバイスは常に無視する。                                                               |

| 0      | W          | 0 - このビット位置には影響なし。<br>1 - D B E デバイスが RESET モード以外の場合にのみ、CQ ドアベルをセットする。                     |

| 31:0   | R          | このレジスタの現内容を生成する。                                                                           |

10

20

## 【0033】

要求キュー・ヘッド・レジスタ( $RQ_n\_REG$ ) 290 は、次の要求パケット 250 がデバイス・ドライバ 230 によってどこに置かれたかの、32 ビット整合物理アドレスを格納するための 32 ビット・レジスタである。各( $RQ_n\_REG$ ) 290 は、システムの初期化中に、チャネル  $n$  に対応する「ダミー」パケット 250 の物理アドレスを用いて、デバイス・ドライバ 230 によって初期化される。その後、 $RQ_n\_REG$  290 は、D B E デバイス 206 によって維持される。この手順を実装するために、D B E デバイス 206 は、D B E デバイス 206 がRESET モードにある場合( $EN\_REG[0] = "1"$ )、このレジスタのビット[31:5]へのプロセッサ 100 のライトをラッチする。D B E デバイス 206 は、物理アドレスのビット[4:0]が"0"を含むことを想定する。D B E デバイス 206 は、このレジスタを用いてパケット 250 をフェッチする。

30

【表 8】

表 8

| RQn_REG |            |                                                                                                               |

|---------|------------|---------------------------------------------------------------------------------------------------------------|

| ビット     | プロセッサ・サイクル | 説明                                                                                                            |

| 31:5    | W          | Pentium キャッシュラインに整合したチャネル <sub>n</sub> に対する「ダミー」パケットの物理アドレス。ライトは、RESET モードにある D B E デバイスによってラッチされる。           |

| 31:5    | R          | D B E デバイスによって処理された最後の要求パケットの物理アドレスのビット[31:5]を生成する。                                                           |

| 4:2     | W          | 0 0 0 0 - D B E デバイスは常に無視する。                                                                                  |

| 4:2     | R          | 常に 0 0 0 を返す。                                                                                                 |

| 1       | W          | 0 - このビットには影響なし。<br>1 - D B E デバイスが RESET モード以外にある場合のみ、D B E デバイスにおけるチャネル <sub>n</sub> に対する同期ダイレクト・アクセスを終了する。 |

| 0       | R          | 0 - ダイレクト・アクセスのためにチャネル <sub>n</sub> を同期させる。<br>1 - チャネル <sub>n</sub> はパケット処理中である。                             |

| 0       | W          | RQ_DOORBELL<br>0 - このビット位置に影響なし。<br>1 - デバイスが RESET モード以外にある場合のみ、RQ <sub>n</sub> ドアベルをセットする。                  |

| 0       | R          | RQ_DOORBELL<br>0 - D B E デバイスによるドアベル・イベントのクリア。<br>1 - D B E デバイスにおいて保留中のドアベル・イベント。                            |

## 【 0 0 3 4 】

ソフトウェア・アーキテクチャ

D B E プロトコルの機構を隠すように、1組のルーチンがホスト・ソフトウェア 2 2 0 に使用可能である。各ルーチンは、ホスト・ソフトウェア 2 2 0 によってコールされるためのエントリポイントを含む。以下に各エントリポイントを説明する。

DBE\_AcknowledgeInterrupt

このルーチンは、完了したパケット 2 5 0 のリストを返し、目標 D B E デバイス 2 0 6 における割り込みを承認する。このルーチンは、デバイス・ドライバの割り込みサービス・ルーチン ( I R S : Interrupt Service Routine ) 又は遅延プロシージャ・コール ( D P C : Deferred Procedure Call ) によってコールすることができる。このルーチンをコールして、D B E デバイス・オブジェクト・ハンドル内に位置する完了キュー・ヘッドから、完了リストを除去する。コール元は、同期を与える必要はない。

DBE\_AllocatePacket

このルーチンは、請求パケット・プール 2 0 0 のヘッド H から最初のパケット 2 5 0 を原子的に除去する。このルーチンは、ドライバ 2 3 0 がある処理を目標 D B E デバイス 2 0 6 に請求したい場合に、当該ドライバによってコールされる。ドライバ 2 3 0 は、パケット 2 5 0 を割り当て、指定された請求要求のためにそれを満たし、D B E 提出ルーチンの 1 つを用いてそれを目標 D B E デバイス 2 0 6 に発行する。このルーチンは、ドライバ

10

20

30

40

50

230による同期を必要としない。

#### 【0035】

##### DBE\_BeginDirectAccess

このルーチンは、DBEデバイス206に対するダイレクト・アクセスを、チャネル・パラメータによって指定された請求要求チャネルに以前に提出されたパケット250と同期させる。同期を取るには、ドライバ230が指定されたチャネル214に対するDBE\_EndDirectAccessをコールするまで、指定されたチャネル214に対するDBEデバイス206上での入力処理を停止する。通常、ドライバのダイレクト・アクセスは、DBEデバイス230において保留となっている請求パケットとの同期は必要としない。ドライバ230は、そのダイレクト・アクセスが、指定された請求要求チャネル214に以前に提出された未決のパケットの完了に依存する場合に、このルーチンをコールする。このルーチンは、他のスレッドが、指定された請求要求チャネル214に要求を提出するのを禁止する。

10

##### DBE\_CancelPacket

このルーチンは、指定されたパケットに、取り消しのためのマークを付ける。このルーチンは、以前に提出したパケットが目標DBEデバイスによって処理されるべきでない場合に、ドライバによってコールされる。次に、DBEドライバ206は、パケットのペイロード254をバースト・ダウンする(burst down)ことなく、取り消されたパケットを完了する。パケットの完了は、パケット250がドライバ230によってどのように提出されたかによって判定される。ドライバ230は、IO取り消しプロトコルを実装するために、DBEデバイス206において保留となっているパケット250を追跡する役割を担う。このルーチンは、IO完了のためのマークを、指定されたパケットに付ける方法を与えるに過ぎない。

20

#### 【0036】

##### DBE\_CompletionListIsReady

このルーチンは、完了リストのために、完了キュー・ヘッドを「のぞき見る」。このルーチンは、完了リスト・キューから完了リストを除去することはない。このルーチンは、ドライバ230が、DBEデバイス・オブジェクト272内の完了リスト・キュー上の完了リストをチェックするためにコールされる。ドライバ230が完了キューから完了リストを除去したい場合、DBE\_AcknowledgeInterruptルーチンをコールしなければならない。

30

##### DBE\_DecreasePool

このルーチンは、指定されたパケット・プールからパケットを除去する。DBEプロトコルは、2つのパケット・プールを定義する。1つのプールは、DBEデバイスに対する請求要求のためのものであり、他方のプールは、DBEデバイスから受け取った非請求データのためのものである。

##### DBE\_Deinitialize

このルーチンは、目標デバイスのためにDBE\_Initializeによって作成された、全ての割り当てリソースを削除する。

##### DBE\_FreePacket

このルーチンは、指定されたパケットを、請求パケット・プールのヘッド上に置く。

40

#### 【0037】

##### DBE\_EndDirectAccess

このルーチンは、チャネル214によって指定された請求要求チャネル214に対して、DBE状態機械(マシン)を起動する。

##### DBE\_GetDevice

このルーチンは、システム内の全てのDBEデバイスのマスター・リストを走査し、指定されたデバイスIDに対する一致を調べる。このルーチンは、指定されたデバイスIDを有するDBEデバイスを作成するのではない。代わりに、このルーチンは、DBE\_Initializeルーチンによって既に作成されている、指定されたデバイスIDを有するDBEデバイスを検索する。このルーチンは、マルチスレッド及びマルチプロセッサ・セーフ(multith

50

read and multiprocessor safe)である。

#### DBE\_GetHwContext

このルーチンは、D B E パケット・ヘッダ内の、特定ハードウェア・データ・フィールドの 32 ビットの内容を返す。

#### DBE\_GetNextPacketToComplete

このルーチンは、完了したパケットのリストにおいて、次のパケットを読み出し、現パケットを適切なパケット・プール上に返す。このルーチンは、DBE\_AcknowledgeInterrupt ルーチンによって既に除去されている、完了リスト上の次のパケットの仮想アドレスを返す。このルーチンは、マルチスレッド及びマルチプロセッサ・セーフである。DBE\_AcknowledgeInterrupt によって完了リストを除去した各実行コンテクスト(execution context) 10 は、当該リストの独占所有権を有する。

#### 【 0 0 3 8 】

#### DBE\_GetSwContext

このルーチンは、D B E パケット・ヘッダ内の特定ソフトウェア・データ・フィールドの 32 ビットの内容を返す。

#### DBE\_IncreasePool

このルーチンは、パケットを、指定されたパケット・プールに追加する。D B E プロトコルは 2 つのパケット・プールを定義する。一方のプールは、D B E デバイスに対する請求要求のためのものであり、他方のプールは、D B E デバイスから受け取った非請求データのためのものである。

#### DBE\_Initialize

このルーチンは、D B E デバイス・オブジェクトを作成する。このルーチンは、ドライバが D B E デバイス・オブジェクトを作成し初期化するためにコールされる。このルーチンは、DeviceID によって指定された同一デバイス ID を有する別の D B E デバイスが既に存在する場合は、実行されない(succeed)。

#### DBE\_PacketIsBusy

このルーチンは、指定されたパケットが目標 D B E デバイスにおいて保留となっているか否かについて判定を行う。このルーチンは、パケット・ヘッダ内のVaLinkフィールド 260 のビット 2 の検査を行うのみである。何故なら、ドライバの完了及び承認を必要とするのは、ポール・パケット及び割り込みパケットだけであるからである。このルーチンは、非同期パケットとして提出されたパケット 250 にはNULL(ヌル)を返す。

#### 【 0 0 3 9 】

#### DBE\_SetHwContext

このルーチンは、D B E パケット・ヘッダ 252 内の特定ハードウェア・データ・フィールドの 32 ビットの内容をセットする。

#### DBE\_SetSwContext

このルーチンは、D B E パケット・ヘッダ 252 内の特定ソフトウェア・データ・フィールドの 32 ビットの内容をセットする。

#### DBE\_SubmitPacketA

このルーチンは、請求パケットを目標 D B E デバイス 206 に発行する。このパケットは、D B E デバイス 206 が当該処理を完了したときに、D B E デバイス 206 によって自動的に請求パケット・プール 200 のテール T に再循環される。このルーチンは、プロセッサ割り込みをディスエーブルせず、目標請求要求キューに対するアクセスの同期を取るために、「スピル」ループを必要としない。

#### DBE\_SubmitPacketI

このルーチンは、請求パケットを目標 D B E デバイスに発行する。このパケットを発行して、目標 D B E デバイスからのハードウェア割り込みに、このパケットの完了を承認するように要求する。このルーチンは、この要求を発行後直ちに、コール元に戻る。ドライバは、目標オペレーティング・システム環境によって定義された標準的な割り込み処理を通じて、このパケットの完了を承認しなければならない。このルーチンは、プロセッサ割り 50

込みをディスエーブルせず、目標請求要求キューに対するアクセスの同期を取るために、「スピン」ループを必要としない。このルーチンは、マルチスレッド及びマルチプロセッサ・セーフである。

#### 【 0 0 4 0 】

##### DBE\_SubmitPacketP

このルーチンは、請求パケットを目標D B E デバイスに発行する。このパケットは、目標D B E デバイスに対する「ポール」要求として発行される。このルーチンは、この要求を発行後直ちにコール元に戻る。ドライバは、DBE\_PacketIsBusyルーチンを用いて、このパケットの完了を承認しなければならない。ドライバは、何らかのI O完了処理をパケット上で実行した後、DBE\_FreePacketを用いて、当該パケットを解放しなければならない。このルーチンは、プロセッサ割り込みをディスエーブルせず、目標請求要求キューに対するアクセスの同期を取るために、「スピン」ループを必要としない。

##### DBE\_SubmitPacketPdeferred

このルーチンは、請求パケットを、目標D B E デバイスにポール・パケットとして発行する。このルーチンは、直ちにコール元に戻り、D B E デバイスとプロセッサとの間の処理の重複を最大化する。このルーチンは、目標D B E デバイスによるこのパケットの提出後直ちにコール元に戻る。D B E デバイスは、パケット2 5 0 のVaLinkフィールド内の「提出」ビット(ビット[2:1])をクリアすることによって、完了を指示する。ドライバは、何らかのI O完了をパケット上で実行した後は、DBE\_FreePacketを用いて当該パケットを解放しなければならない。このルーチンは、プロセッサ割り込みをディスエーブルせず、目標請求要求キューに対するアクセスの同期を取るために、「スピン」ループを必要としない。

上述のエントリポイントは、概略的に、以下のカテゴリの1つに該当する。即ち、初期化 / 初期化解除、パケット提出、パケット完了、同期ダイレクト・アクセス、パケット取り消し、及びパケット・プール増減である。

#### 【 0 0 4 1 】

##### 初期化 / 初期化解除

初期化 / 初期化解除ルーチンは、ホスト・ソフトウェアが、D B E ハードウェア及びソフトウェア・リソースの初期化及び初期化解除を実行する際に用いられる。このカテゴリは、DBE\_Initialize, DBE\_Deinitialize及びDBE\_GetDeviceという3つのルーチンを含む。ホスト・ソフトウェアは、その初期化フェーズ中にDBE\_Initializeをコールし、D B E デバイス・オブジェクト2 7 2 のハンドルを作成し、適切なアドレス情報を用いてD B E ハードウェア・レジスタ2 8 0 ~ 2 9 2 を設定し、自動化D M A を容易にする。

ホスト・ソフトウェア2 2 0 が、システムのリブート又はO S 2 2 2 による動的アンローディング(dynamic unloading)によって再初期化される場合、DBE\_Initializeルーチンを再度コールし、目標D B E デバイス2 0 6 に対する新たな接続を作成し、新たなアドレス情報を用いて、D B E ハードウェア・レジスタ2 8 0 ~ 2 9 2 を再初期化しなければならない。

DBE\_Deinitializeルーチンは、ホスト・ソフトウェア2 2 0 が、目標D B E デバイス2 0 6 のために割り当てられたメモリ・リソースを一掃し、目標D B E デバイス2 0 6 をRESETモードに設定する際に用いられる。

DBEソフトウェア・アーキテクチャは、システム全体で作成されたD B E デバイス・オブジェクト2 7 2 全てを追跡する。ホスト・ソフトウェア2 2 0 は、DBE\_GetDeviceをコールすることによって、他のソフトウェア・エンティティが既に初期化したD B E デバイス2 0 6 に対する接続を確立することができる。ホスト・ソフトウェア2 2 0 は、その初期化コンテクスト内からのこのルーチンのコールに限定されるのではない。DBE\_GetDeviceは、いずれの実行コンテクスト内からでもコールすることができる。

#### 【 0 0 4 2 】

##### パケット提出

パケット提出ルーチンは、ホスト・ソフトウェアが、請求パケットの割り当て、及びD B

10

20

30

40

50

E デバイス 2 0 6 への提出を実行する際に用いられる。このカテゴリは、DBE\_AllocatePacket, DBE\_SubmitPacketA, DBE\_SubmitPacketP, DBE\_SubmitPacketPdeferred、及びDBE\_SubmitPacketI の 5 つのルーチンを含む。

ホスト・ソフトウェア 2 2 0 が、請求要求を D B E デバイス 2 0 6 に提出可能となる前に、請求パケット・プール 2 0 0 から請求パケット 2 5 0 を割り当てなければならない。ホスト・ソフトウェア 2 2 0 は、DBE\_AllocatePacket をコールし、使用可能なパケット 2 5 0 を請求パケット・プール 2 0 0 から除去する。ソフトウェアは、パケット 2 5 0 が使用可能となるまで、リトライ・カウントを指定するか、あるいはいつまでも待つことができる。DBE\_AllocatePacket ルーチンは、アプリケーション / デバイスが定義するいずれの方法でも使用可能な、空パケットのペイロード・データ・エリアへのポインタを返す。

一旦空パケット 2 5 0 が割り当てられたなら、ホスト・ソフトウェア 2 2 0 は、指定された請求要求チャネル 2 1 4 への請求トランザクション(solicited transaction)を実行するためには必要な関連情報で、パケットのペイロード・データ・エリア 2 5 4 を満たす。ホスト・ソフトウェア 2 2 0 は、非同期、ポール、又は割り込みの 3 つの方法の内の 1 つで、パケット 2 5 0 を D B E デバイス 2 0 6 に発行する。

#### 【 0 0 4 3 】

非同期パケットは、D B E デバイス 2 0 6 からの完了通知を必要としない。ホスト・ソフトウェア 2 2 0 は、ソフトウェアが特定の処理に対して完了通知を必要としない場合、即ち、グラフィック処理が要求されたような場合に、非同期パケット 2 5 0 を提出する。D B E デバイス 2 0 6 は、パケットの完了時に、請求パケット・プール 2 0 0 のテールに、自動的に非同期パケットを置く。ホスト・ソフトウェア 2 2 0 は、DBE\_SubmitPacketA ルーチンを用いて、非同期パケットを発行する。典型的な非同期処理は、グラフィックス・デバイス 1 2 2 によって実行される、スクリーン - スクリーン間 B L T (screen- screen-BLT) である。ポール要求は、ドライバ 2 3 0 が I / O デバイス 1 1 8 に処理の完了を指示するように要求したときに、デバイス・ドライバ 2 3 0 によって発行されるが、ハードウェア割り込みの形態ではない。デバイス・ドライバ 2 3 0 は、パケット・ヘッダ 2 5 2 内のキャッシュに基づくフィールドにポールすることによって、I / O デバイス 1 1 8 が処理を完了するのを待つ。ポール・パケットは、パケット・ヘッダ 2 5 2 内のビットをクリアすることによって、D B E デバイス 2 0 6 からの完了通知を要求する。ホスト・ソフトウェア 2 2 0 は、パケット 2 5 0 の完了時に D B E デバイス 2 0 6 が提出ビット (Va +Flags フィールドのビット [2:1]) のビット位置に "00" を書き込むまで、パケット・ヘッダ 2 5 2 内の提出ビット上で「スピン」即ちポールする。ドライバ 2 3 0 は、修正されたデータによる「無効化」サイクルがキャッシュ・ラインを更新するまで、そのキャッシュ内においてスピンを行う。これによって、I / O デバイス 1 1 8 に直接ポールし、プロセッサ 1 0 0 をホスト・バス 1 0 2 から分離しておく必要性がなくなる。

#### 【 0 0 4 4 】

ホスト・ソフトウェア 2 2 0 は、DBE\_SubmitPacketP 及び DBE\_SubmitPacketPdeferred ルーチンを用いて、ポール・パケットを発行する。DBE\_SubmitPacketP ルーチンは、D B E デバイス 2 0 6 がパケット・ヘッダ 2 5 2 内の提出ビットをクリアするまで、そのビット上の「スピン」動作を与える。DBE\_SubmitPacketPdeferred ルーチンは、要求を D B E デバイス 2 0 6 に提出した後直ちに戻る。ホスト・ソフトウェア 2 2 0 は、パケット 2 5 0 が D B E デバイス 2 0 6 によって処理されている間、他のタスクの処理を続けることができる。

割り込み要求は、ホスト・ソフトウェア 2 2 0 がハードウェア割り込みによる完了通知を要求するときに、デバイス・ドライバ 2 3 0 によって発行される。これは、より古典的なドライバ 2 3 0 とその目標 P C I バス・マスター 1 1 8 との間の通信方法である。D B E デバイス 2 0 6 は、割り込み要求を完了する際、完了したパケットの仮想アドレスを、システム・メモリ内の中の既知のメモリ・キューに書き込み、ハードウェア割り込みをアサートする。D B E デバイス 2 0 6 は、ドライバ 2 3 0 が未だ直前の完了に対応していない場合、要求を完了し続けることができる。この場合、D B E デバイス 2 0 6 は、システム・メ

10

20

30

40

50

モリ内に完了パケットのリストを構築し、完了キューが他の完了リストを受け取る準備ができることを I/O デバイス 118 が示すまで、他のハードウェア割り込みをアサートしない。ホスト・ソフトウェア 220 は、DBE\_SubmitPacket ルーチンをコールすることによって、割り込みパケットを発行する。このルーチンは、パケット 250 の提出時に、直ちにコール元に戻る。ホスト・ソフトウェア 220 は、要求された割り込みイベントの到着まで、実行コンテクストの「ポスティング(posting)」を扱う。

#### 【0045】

##### パケット完了

パケット完了ルーチンは、ホスト・ソフトウェアが、DBE デバイス 206 に提出されたパケット 250 上で完了処理を実行する際に用いられる。このカテゴリは、DBE\_PacketIsBusy, DBE\_FreePacket, DBE\_CompletionListIsReady, DBE\_AcknowledgeInterrupt, 及び DBE\_GetNextPacketToComplete という 5 つのルーチンを含む。10

非同期で提出された請求パケット 250 は、ホスト・ソフトウェア 220 による完了処理を要求しない。DBE デバイス 206 は、完了した非同期パケット 250 を自動的に「解放」し、請求パケット・プール 200 のテーブル T に配する。

ポール・パケット 250 は、何らかの完了処理がホスト・ソフトウェア 220 によって実行された後、請求パケット・プール 200 上に返されなければならない。ソフトウェア 220 は、DBE\_FreePacket をコールし、完了したパケット 250 を、請求パケット・プール 200 のヘッド上に置く。

DBE\_SubmitPacketPdeferrred ルーチンによって発行されたパケット 250 は、DBE\_FreePacket を用いて請求パケット・プール 200 のヘッド上にパケット 250 を置く前に、最初に DBD\_PacketIsBusy ルーチンをコールしなければならない。20

#### 【0046】

DBE デバイス 206 は、割り込みパケット 250 を完了する際に、パケット完了リストを構築し、このリストの先頭を、DBE デバイス・オブジェクト 272 内に位置する完了キュー・ヘッド内に置く。DBE デバイス 206 は、完了リストを完了キュー・ヘッド内に置いた後、プロセッサ 100 へのハードウェア割り込みをアサートして、ホスト・プロセッサにリストを通知する。

ホスト・ソフトウェアは、完了キュー・ホストを「覗いて」、DBE\_CompletionListIsReady をコールすることにより、完了キュー・ヘッドからリストを実際に除去することなく、DBE デバイス 206 が実際にその割り込みをアサートしているか否か確認することができる。DBE\_AcknowledgeInterrupt ルーチンは、ソフトウェア 220 が、完了キュー・ヘッドから完了リストを除去し、DBE デバイス 割り込みを承認する際にコールされる。一旦このリストが除去されると、完了リストの終端に到達するまで、後続の DBE\_GetNextPacketToComplete へのコールによって、「検索(walk)」することができる。DBE\_GetNextPacketToComplete は、次のパケットを抽出しそれから完了させた後、直ちに、現パケットを請求パケット・プールのヘッド上に置くことによって、それを「解放」することができる。30

#### 【0047】

##### 同期ダイレクト・アクセス

同期ダイレクト・アクセスは、プロセッサ 100 が共有 DBE ハードウェア・リソースに対するダイレクト・アクセスを要求する場合に有用である。ホスト・ソフトウェア 220 は、DBE\_BeginDirectAccess をコールして、ポール・パケット 250 を提出し、指定されたチャネル(群)に対する DBE デバイス 206 に、後続のパケット 250 の処理を停止させる。これによって、以前に提出されたパケットの処理とダイレクト・アクセス処理との間の接続がなくとも、ホスト・ソフトウェア 220 の目標デバイスのハードウェア・リソースに対するダイレクト・アクセスが可能となる。ホスト・ソフトウェア 220 は、DBE\_EndDirectAccess ルーチンをコールすることによって、指定されたチャネル(群)に対する同期ダイレクト・アクセスを終了する。40

#### 【0048】

##### パケット取り消し

D B E デバイス 2 0 6 に発行され、D B E デバイス 2 0 6 による完了が未だ保留中のパケット 2 5 0 は、ホスト・ソフトウェアがDBE\_CancelPacketをコールすることによって取り消すことができる。D B E デバイス 2 0 6 は、パケット 2 5 0 がVaフィールド 2 7 0 においてI O取り消しのためのマークが付けられている場合、パケットのペイロード 2 5 4 をバーストしてはならない。取り消されたパケット 2 5 0 は、当該パケット 2 5 0 がどのように提出されたかに応じて、直ちにD B E デバイス 2 0 6 によって完了される。

#### 【 0 0 4 9 】

##### パケット・プールの増減

ホスト・ソフトウェア 2 2 0 は、より多くのパケット 2 5 0 を請求パケット・プール 2 0 0 及び非請求パケット・プール 2 0 2 に追加することによって、それ自体と目標 D B E デバイス 2 0 6 との間の切り離し(decoupling)量を増加させることができる。ソフトウェア 2 2 0 は、DBE\_IncreasePoolをコールし、指定されたプールにパケット 2 5 0 を更に追加する。ソフトウェア 2 2 0 が、パケット・プール上に過剰に多いパケット 2 5 0 があり、いくつかのパケット 2 5 0 をO S のメモリ・マネージャに戻せることを発見した場合、ホスト・ソフトウェア 2 2 0 はDBE\_DecreasePoolをコールし、指定されたパケット・プールからパケット 2 5 0 を除去することができる。

#### 【 0 0 5 0 】

##### D B E アーキテクチャ

図 6 の A 及び図 6 の B を参照すると、分散型バースト・エンジン ( D B E ) 2 0 6 に対する少なくとも 2 つの選択可能な位置が示されている。図 6 の A では、多数の P C I バス・マスター 1 1 8 が D B E インターフェース 2 0 6 を含み、P C I バス・マスター 1 1 8 とメモリ 1 1 2 との間で効率的にパケットをバーストする。図 6 の B では、ホスト - P C I 間ブリッジ 1 0 6 a が D B E 2 0 6 を含み、ユニバーサル・シリアル・バスのホスト・コントローラ又はファイアウエア・コントローラのような I / O デバイス 2 0 8 とメモリ 1 1 2 との間で、パケット・アドレスを受け渡しを行う。

図 6 の B の更に別の変形として、図 6 の C は、ホスト・ブリッジ 2 1 0 が、1 つ以上のプロセッサ 1 0 0 と通信するためのホスト・バス 1 0 2 , メモリ 1 1 2 と通信するためのメモリ・バス 2 1 2 、及び周辺機器と通信するための P C I バス 1 1 4 に取り付けられた、コンピュータ・システムを示す。ホスト・ブリッジ 2 1 0 内には、ユニバーサル・シリアル・バス ( U S B ) 、ファイアウエアとしても知られている I . E . E . E . ( 電気電子学会 ) 1 3 9 4 、又は小型コンピュータ・システム・インターフェース ( S C S I ) というような、I / O チャネル 2 0 8 がある。I / O チャネル 2 0 8 は、分散型バースト・エンジン 2 0 6 に接続されている。この実施形態は、図 6 の A 及び図 6 の B の実施形態とは異なる。何故なら、D B E 2 0 6 は一層緊密にメモリ 1 1 2 に結合されているからである。これによって、D B E は、I / O デバイス 2 0 8 に対してパケットをバーストする代わりに、パケット・アドレスをI / O デバイス 2 0 8 に渡すことが可能となる。このようにして、I / O デバイス 2 0 8 は、直接メモリ 1 1 2 からのパケット上で処理を行うことができる。P C I バス 1 1 4 を通じてパケットをバーストする際に伴うレイテンシイが排除されるので、これは図 6 の A 及び図 6 の B の結合が緩い D B E に対する利点である。このように、D B E デバイス 2 0 6 は、種々の状況に対する適合性が非常に高い。

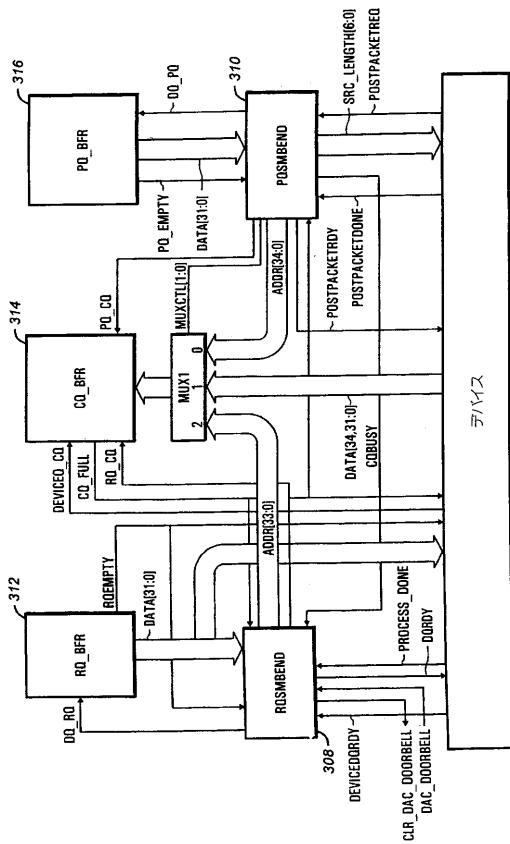

#### 【 0 0 5 1 】

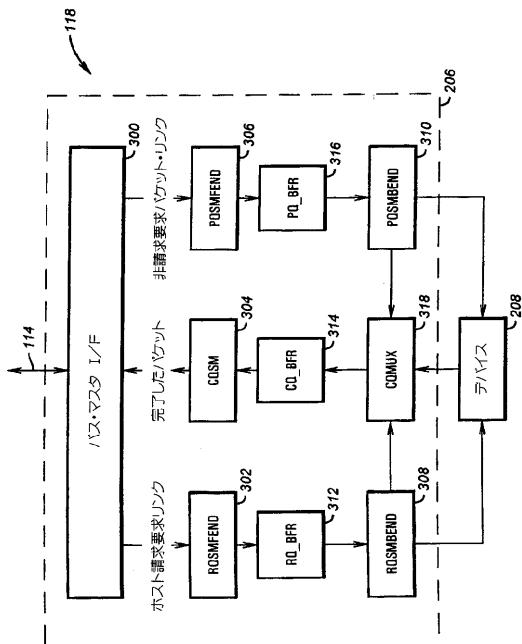

##### 分散型バースト・エンジン ( D B E )

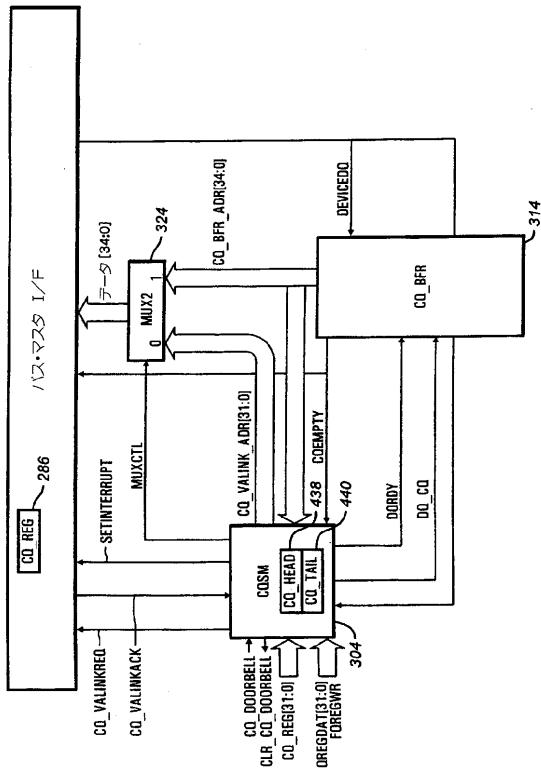

図 7 を参照すると、D B E デバイス 2 0 6 及び I / O デバイス 2 0 8 を含む、P C I バス・マスター 1 1 8 のブロック図が示されている。D B E デバイス 2 0 6 は、D B E デバイス 2 0 6 とメモリ 1 1 2 との間で P C I バス 1 1 4 を通じてデータ・パケット 2 5 0 を交換するための、バス・マスター・インターフェース ( I / F ) 3 0 0 を含む。あるいは、D B E 2 0 6 は、E I S A バス又は他のいずれかの所望のバスに対するバス・マスター・インターフェースを有することも可能である。また、D B E デバイス 2 0 6 は、あるフロント・エンド状態機械 3 0 2 ~ 3 0 6 とあるバック・エンド状態機械 3 0 8 ~ 3 1 0 との間に結合された 3 つのバッファ 3 1 2 ~ 3 1 6 も含む。これら 3 つのバッファは、要求キュー・

10

20

30

40

50

バッファ(RQ<sub>n</sub>\_BFR)312、完了キュー・バッファ(CQ\_BRF)314、及びポステッド・キュー・バッファ(PQ\_BFR)316である。フロント・エンドの目的は、要求キュー・バッファ312及びポステッド・キュー・バッファ316を満杯に保持し、完了キュー・バッファ314を空に保持することである。バック・エンドの目的は、要求キュー・バッファ312及びポステッド・キュー・バッファ316からパケット・アドレス及びデータ情報を引き出し、パケットを処理し、完了したパケットをプロセッサ100に戻すことである。

#### 【0052】

要求キュー・バッファ312は、ホスト側から出された要求を整列するための先入れ先出し(FIFO)バッファである。供給キュー・バッファ312は、I/Oデバイス208が対応するチャネル数214に応じた、並列なn個のバッファからなる。好ましくは、要求キュー・フロント・エンド状態機械302及び要求キュー・バック・エンド状態機械308は、要求キュー・バッファ312全ての管理を担うが、状態機械の別個の集合を、各要求キュー・バッファ312毎に用いることも可能であると考えられる。簡略化のために、要求キュー・バッファ312は、ここでは単一のバッファとして扱う。

完了キュー・バッファ314は、完了したパケットを整列するためのFIFOである。ポステッド・キュー・バッファ316は、ホスト側の請求に基づくことなくホスト側にデータを転送することを要求する非請求要求を整列するためのFIFOである。バッファ312～316は、キューのデータ全体(キュー274～278)の一部分のみを収容する場合もあるので、バッファ312～316はそれらの各キュー274～278のサブセットと見なされる。バッファ312～316は、典型的にバス調定の結果として起こるPCIバス114のレイテンシイから、I/Oデバイス208を切り離す。この結果、以前に得られたものよりも、I/O性能が向上する。

#### 【0053】

ここで、図示するDBEデバイス206は、单一ストリームDBEデバイスであることを注記しておく。DBEデバイス206が多機能周辺機器に対応することを要求される場合、多数の状態機械の集合を並列に実装し、单一のI/Oデバイス内に結合されている各機能毎に対応することができる。単一の状態機械の集合が、対応するI/Oデバイス208に対する全てのチャネル214を処理する。

フロント・エンド状態機械は、要求キュー・フロント・エンド状態機械(RQSMFEND)302、ポステッド・キュー・フロント・エンド状態機械(PQSMFEND)306、及び完了キュー・フロント・エンド状態機械(CQSM)304を含む。要求キュー・フロント・エンド状態機械302は、デバイス・ドライバ230によって要求キュー274上に置かれたパケット250を処理し、要求キュー・バッファ312に供給する役割を担う。ポステッド・キュー・フロント・エンド状態機械306は、メモリ112からポステッド・パケット・アドレスを引き出し、それらをポステッド・キュー・バッファ316内に置く役割を担う。

#### 【0054】

バック・エンド状態機械308～310は、要求キュー・バック・エンド状態機械(RQSMBEND)308及びポステッド・キュー・バック・エンド状態機械(PQSMBEND)310を含む。要求キュー・バック・エンド状態機械308は、要求キュー・バッファ312からパケット情報を引き出し、それをI/Oデバイス208に供給する役割を担う。ポステッド・キュー・バック・エンド状態機械310は、ポステッド・キュー・バッファ316から非請求パケット・アドレスを引き出し、それらをI/Oデバイス208に提示する役割を担う。

完了キュー状態機械(CQSM)304は、フロント・エンド及びバック・エンドと協同してパケットを完了し、完了キュー276及びフリー・キュー272のリンクを維持する役割を担う。また、DBEデバイス206には、多数のソース、即ち、I/Oデバイス208、要求キュー・バック・エンド状態機械308、及びポステッド・キュー・バック・エンド状態機械310から、データのフローを完了キュー・バッファ314に方向付けるための、完了キュー・マルチプレクサ(CQMUX)318も含まれる。完了キュー・マルチプレクサ318は、ポステッド・キュー・バック・エンド状態機械310によって制御される。

10

20

30

40

50

## 【0055】

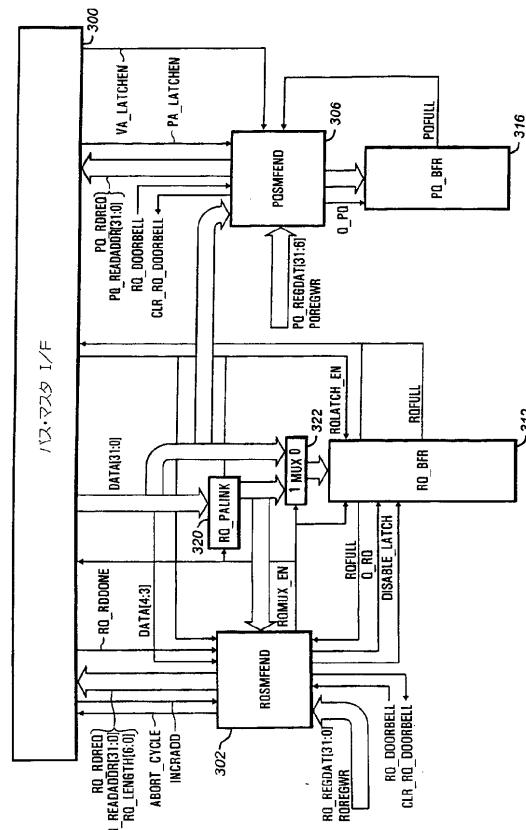

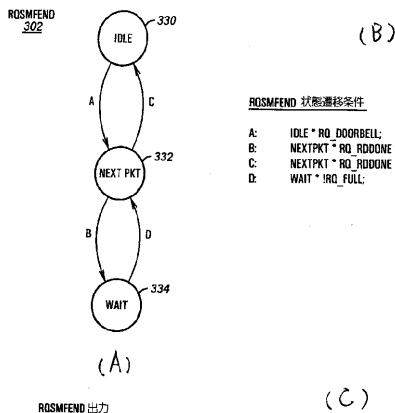

次に図8を参照すると、要求キュー・フロント・エンド状態機械302及びポステッド・キュー・フロント・エンド状態機械306のフロント・エンドの更に詳細なブロック図が示されている。要求キュー・フロント・エンド状態機械302について最初に説明する。図9のA、図9のB及び図9のCは、要求キュー・フロント・エンド状態機械302のフロー・チャート、状態遷移図、及び出力を示す。要求キュー・フロント・エンド状態機械302の出力は、図9のCに示されている。他に特に示さない限り、出力は、それに割り当てられた論理レベルから不变のままであるとする。

要求キュー・フロント・エンド状態機械302は、プロセッサ100によって要求キュー274上に置かれたパケットを処理する役割を担う。要求キュー・フロント・エンド状態機械302は、Rq<sub>n</sub>\_REG290を用いて、プロセッサ100が次のパケット・アドレスを置くメモリ・アドレスを得る。プロセッサ100は、システムの初期化中に1回Rq<sub>n</sub>\_REG290に書き込み、再度それに書き込むことは決してない。要求キュー・フロント・エンド状態機械302は、要求キュー・フロント・エンド状態機械302が処理した最後のパケットの物理アドレスを用いて、Rq<sub>n</sub>\_REG290の内容を実行時間中保持する。要求キュー・フロント・エンド状態機械302は、要求キュー・バッファ312を満杯に維持し、要求キュー・バック・エンド状態機械308をバス・マスターI/F300から切り離そうとする。

## 【0056】

要求キュー・フロント・エンド状態機械302は、PA\_LINKフィールド268を保持するために、要求キューPA\_LINKレジスタ(RQ\_PALINK)320を制御する。要求キュー・フロント・エンド状態機械302内部には、要求キュー・ヘッド・レジスタ(RQ\_REG)290、現パケットのPALINKDWORDフィールドを保持するためのパケット長レジスタ(RQ\_LENGTH)、及び次のパケットのPaLinkDWORDを保持するための次パケット長レジスタ(RQ\_NXPLENGTH)がある。RQ\_LENGTHレジスタの出力は、バス・マスターI/F300に供給されるので、パケット250の中を適正に読み取ることができる。以下の検討は単一のチャネル要求キューについてのみ言及するが、多数のチャネルが使用可能であることは理解されよう。

パケット250が互いにリンクされていることを思い出すのは重要である。したがって、リンク・リスト内のどのパケット250を状態機械が処理しているのかを明確にするために、以下の規則を用いる。「現パケット」とは、現在処理又は転送されている最中のパケットを意味する。「前パケット」とは、現パケットに先立ってリンクされ、現パケットよりも前に処理されたパケットを意味する。「次パケット」とは、現パケットの後にリンクされ、現パケットよりも後に処理されるパケットを意味する。したがって、前パケットのPaLinkフィールド268は現パケットを示し、現パケットのPaLinkDWORDフィールド266は、次パケットに対するDWORDの数を示す。これは全てのパケット型に対して一貫している。

## 【0057】

要求キュー・フロント・エンド状態機械302は、システム・リセットからIDLE状態に初期化する。RESETモードにある間、デバイス・ドライバ230は、請求パケット・プール200（又はフリー・キュー272）上の最後のパケット250の物理アドレスを用いて、RQ\_REG290を初期化する。フリー・キュー272は、DBEデバイス206が完了した非同期パケットを整列する場所を有するために、請求パケット・プール200上に少なくとも1つの空きパケット250を維持する必要がある。

IDLE状態330において、要求キュー・フロント・エンド状態機械302は、RQ\_DOORBELLが鳴らされるのを待つ。RQ\_DOORBELLを待っている間、要求キュー・フロント・エンド状態機械302は、RQ\_REG290からの値（通常、DBEによって処理された最後の要求パケットの物理アドレス）を用いて、要求キュー・リード・アドレス・レジスタ(RQ\_READADR\_DR\_B)を初期化し、RQ\_LENGTHレジスタは2hに初期化される。DBE206が丁度デバイス・ドライバ230によって初期化されたばかりである場合、RQ\_READADDR\_Bは、デバイス・ドライバ230によってRQ\_REG290に書き込まれた値によって初期化される。RQ\_D

10

20

30

40

50

DOORBELL信号がアサートされると、要求キュー・フロント・エンド状態機械302は、クリア要求キュー・ドアベル(CLR\_RQ\_DOORBELL)信号をアサートし、NEXTPKT状態332に遷移する。

#### 【0058】

NEXTPKT状態332において、RQ\_DOORBELLがクリアされ、パケット250がメモリ112から読み出され、要求キュー・バッファ312に書き込まれる。バス・マスター/F300は、PaLinkDWORDフィールド266を用いてパケット情報を供給し始め、ペイロードの終端に到達するまで続ける。PaLinkDWORDフィールド266の前のフィールド(図3参照)は、要求キュー・フロント・エンド状態機械302には必要ではない。

現パケット250が書き込まれると、前パケットからの値が要求キュー・バッファ312上に押し出される。現パケットのPaLinkDWORDフィールド値266がRQ\_NXPLENGTHレジスタにラッチされると、RQ\_LENGTHレジスタに現在保持されているPaLinkDWORDフィールド値266は、要求キュー・バッファ312上に押し出される。マルチプレクサ(MUX)322は0入力から1入力に切り替えられるので、現在RQ\_PALINKレジスタ320に保持されているPaLinkフィールド値268は、現パケットのPaLinkフィールド値268がRQ\_PALINKレジスタ320にラッチされると、要求キュー・バッファ312上に押し出される。その後、マルチプレクサ322は、0入力からのデータを受け取るように、再度切り替えられる。

#### 【0059】

現パケットのVa+Flagsフィールド値270は、現パケットの残りのペイロード254であるので、要求キュー・バッファ312上に押し出される。現パケット250が要求キュー・バッファ312に書き込まれる際、Va+Flagsフィールド270をチェックし、I/O取り消しか又はダイレクト・アクセスかを調べる。Va+Flagsフィールド270のビット3又はビット4のいずれかがセットされている場合、ペイロードを読み出す前にパケット転送サイクルを中断する。パケット250の各DWORDを読み出すに連れて、RQ\_READADDR\_Bレジスタをそれに応じて増分する。

ペイロード254が転送されたとき、RQ\_RDDONE信号がバス・マスター/F300から受け取られる。RQ\_RDDONE信号が受け取られ、RQ\_PALINKレジスタが0値を収容している場合、要求キュー・フロント・エンド状態機械はIDLE状態330に戻り、別のRQ\_DOORBELLを待つ。

#### 【0060】

RQ\_RDDONE信号が受け取られ、更にRQ\_PALINKレジスタが0値を収容している場合、別のパケット転送サイクルが必要となる。この場合、状態機械302は、RQ\_NXPLENGTH内の次パケット長値を、3hだけ増分し、この値をRQ\_LENGTHレジスタにラッチし、RQ\_PALINKレジスタからの値をPQ\_READADDR\_Bレジスタにラッチする。

RQ\_RDDONE信号が受け取られ、RQ\_PALINKレジスタが0ではないが、要求キュー・バッファ312が満杯である場合(RQFULL)、要求キュー・フロント・エンド状態機械302はWAIT状態に遷移する。状態機械302は、要求キュー・バッファ312が満杯でない場合、再びWAIT状態からNEXTPKT状態に遷移する。RQFULL信号は、要求キュー・バッファ312によって供給される。いずれの状態においても、要求キュー・バッファ312が満杯でない場合、RQ\_PALINKレジスタ内に格納されている値がRQ\_REGにラッチされる。RQ\_LENGTH, RQ\_READADDR\_B, 及びRQ\_REGレジスタにロードされた後、別のパケット転送サイクルが始まる。

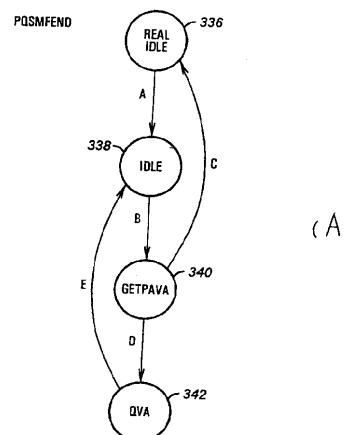

#### 【0061】

次に、図8及び図10を参照して、ポステッド・キュー・フロント・エンド状態機械306を更に詳細に説明する。図10のA及びBは、ポステッド・キュー・フロント・エンド状態機械306のフロー・チャート及び状態遷移条件を示す。ポステッド・キュー・フロント・エンド状態機械306の出力を図10のCに示す。他に特に示していない限り、出力は不变のままとする。

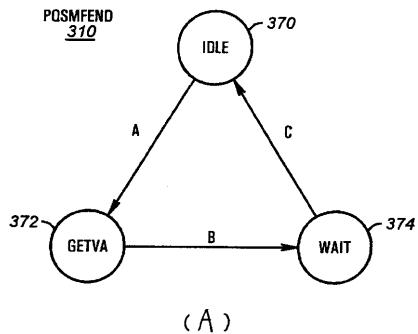

ポステッド・キュー・フロント・エンド状態機械(PQSMFEND)306は、メモリ112から

10

20

30

40

50

ポステッド・パケット・アドレスを引き出し、それらをポステッド・キュー・バッファ316内に置く役割を担う。ポステッド・キュー・フロント・エンド状態機械306は、常に、3つのDWORD(現パケット250に対してPALINKDWORDS, PA\_LINK及びVA+FLAGS)を初期リード上で要求し、2つのDWO RD(PA\_LINK及びVA+FLAGS)を後続の全てのリード上で要求する。プロセッサ100は、システムの初期化中にポステッド・パケット250のリストを構築し、次に、ポステッド・キュー278内の最初のパケット250の物理アドレスをPQ\_REG288に書き込む。ポステッド・キュー・フロント・エンド状態機械306は、ポステッド・パケット250のリストを見渡し、パケット・アドレスをプリフェッチする。アドレス(PA\_LINK及びVA)は、バッファ316が満杯になるまで、又はメモリ112内の非請求パケット・プール202上にもはやポステッド・パケット250がなくなるまで、ポステッド・キュー・バッファ316内に置かれる。リスト上に残っているパケット250が1つのみの場合、非請求パケット・プール202は、空と見なされる。

10

#### 【0062】

ポステッド・キュー・フロント・エンド状態機械306は、ポステッド・キュー・レジスタ(PQ\_REG)288、ならびに次のパケットのペイロードのPA\_LINK及び長さ(PQ\_PALINK及びPQ\_LENGTH)を保持するための他のレジスタを内蔵する。

ポステッド・キュー・フロント・エンド状態機械306は、システム・リセットからREAL IDLE状態336に初期化する。RESETモードにある間、デバイス・ドライバ230は、非請求パケット・プール202内の最初のパケットの物理アドレスを用いて、PQ\_REG288を初期化する。その後、ポステッド・キュー・フロント・エンド状態機械は、非請求パケット・プール202のヘッドの物理アドレスを、PQ\_REG288に保持する。

20

REAL IDLE状態336では、ポステッド・キュー・フロント・エンド状態機械306は、PQ\_DOORBELLが鳴らされるのを待つ。デバイス・ドライバ230がPQ\_DOORBELLを鳴らすのは、パケット250がDBE206に使用可能となったときである。これは、DBE\_FreePacket又はDBE\_GetNextPacketToCompleteが非請求パケットによってコールされる毎に発生する。PQ\_DOORBELLビットがセットされると、ポステッド・キュー・フロント・エンド状態機械306は、IDLE状態338に遷移する。

#### 【0063】

IDLE状態338では、PQ\_DOORBELLがクリアされ、ポステッド・キュー・リード要求信号(PQ\_RDREQ)がアサートされる。ポステッド・キュー・フロント・エンド状態機械306は自動的にIDLE状態338からGETPAVA状態340に遷移する。

30

GETPAVA状態340における第1リード・サイクルにおいて、PA\_LINKフィールド値268はポステッド・キューPaLinkレジスタ(PQ\_PALINK)にラッチされ、PaLinkDWORDフィールド値266はポステッド・キュー長レジスタ(PQ\_LENGTH)にラッチされ、Va+Flagsフィールド値270はラッチされる。後続のリード・サイクルでは、PA\_LINK及びVA+FLAGSフィールドのみが読み取られる。何故なら、ペイロード254のサイズが既にわかっているからである。各リード・サイクル毎に、PA\_LINKフィールド及びVA+FLAGSフィールドは、ポステッド・キュー・バッファ316に押し出される。現パケット250のPA\_LINKフィールドが0に等しい場合、ポステッド・キュー・フロント・エンド状態機械306は、再びREAL IDLE状態に遷移し、PQ\_DOORBELLビットが再度セットされるのを待つ。

40

現パケット250のPA\_LINKフィールドが0に等しくない場合、現パケットには追加のパケット250がリンクされていることになる。この場合、ポステッド・キュー・フロント・エンド状態機械306は、QVA状態342に遷移し、更にIDEL状態338に戻り、次パケット250をフェッチする。ポステッド・キュー・バッファ316が満杯となっている場合(PWFULL信号)、パケットのフェッチは抑制される。

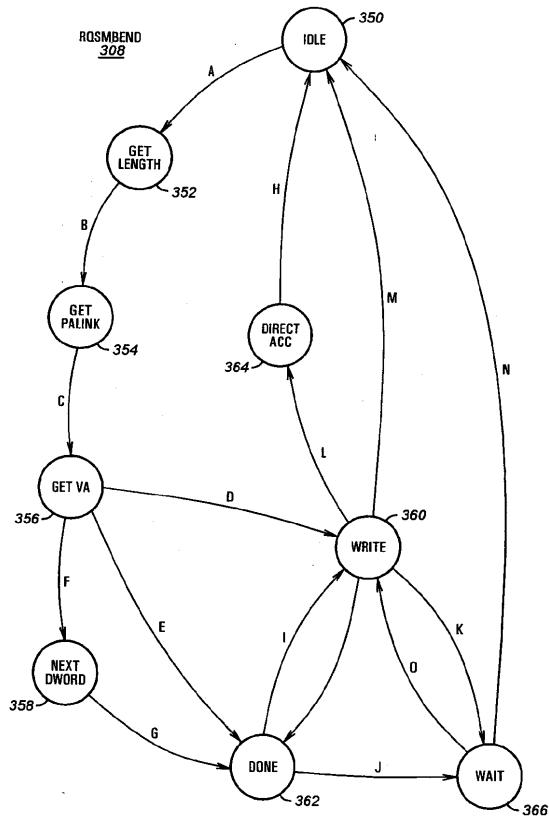

#### 【0064】

次に図11を参照すると、要求キュー・バック・エンド状態機械(RQSMBEND)308及びポステッド・キュー・バック・エンド状態機械(PQSM BEND)310の更に詳細なブロック図が示されている。要求キュー・バック・エンド状態機械308について最初に説明する。図12及び図13は、要求キュー・バック・エンド状態機械308のフロー・チャート及

50

び状態遷移条件を示す。要求キュー・バック・エンド状態機械308の出力を、図14に示す。他に特に示されていない限り、出力は、それらに予め割り当てられた論理値から不变のままとする。

要求キュー・バック・エンド状態機械308は、要求キュー・バッファ312の1つからパケット情報を引き出す役割を担う。要求キュー・バック・エンド状態機械308は、要求キュー・バッファ312から物理アドレス及び仮想アドレスを引き出し、I/Oデバイス208にデータ254を引き出させる。パケット250が既にI/Oデバイス208によって処理されている場合、I/Oデバイス208は、要求キュー・バック・エンド状態機械308に通知し、パケット250を完了する。パケット250には、割り込み、ポール、又は非同期完了とマークが付けられる。要求キュー・バック・エンド状態機械308は、完了の間、プロセッサ100のDBEデバイス206へのダイレクト・アクセスをパケット250と同期させる役割も担っている。

10

#### 【0065】

要求キュー・バック・エンド状態機械308は、システム・リセット又はRESETモードからIDLE状態350に初期化し、要求キュー・バッファ312からの!RQEMPTY信号が、要求キュー・バッファ312が空でないことを示すのを待つ。空でない場合、要求キュー・バック・エンド状態機械308はGETLENGTH状態352に遷移し、要求キュー(dq\_RQ)信号をアサートし、最初のDWORDを要求キュー・バッファ312からポップする(pop)。

GETLENGTH状態352において、状態機械308は最初のDWORDを長さレジスタ(RQB\_LENGTH)に書き込む。最初のDWORDは、現パケット250のPALINKDWORDフィールド値266である。要求キュー・バッファ312が空でない場合、要求キュー・バック・エンド状態機械308はGETPALINK状態354に遷移し、要求キュー(dq\_RQ)信号をアサートし、他のDWORDを要求キュー・バッファ312からポップする。要求キュー・バッファ312が空の場合、要求キュー・バック・エンド状態機械308は、要求キュー・バッファ312が空でなくなるまで、GETLENGTH状態352に止まる。

20

#### 【0066】

GETPALINK状態354において、状態機械308は2番目のDWORDを要求キューPA\_LINKレジスタ(RQB\_PALINK)に書き込む。2番目のDWORDは、現パケット250のPA\_LINKフィールド値268である。要求キュー・バッファ312が未だ空でない場合、要求キュー・バック・エンド状態機械308はGETVA状態356に遷移し、要求キュー(dq\_RQ)信号をアサートし、別のDWORDを要求キュー・バッファ312からポップする。要求キュー・バッファ312が空になった場合、要求キュー・バック・エンド状態機械308は、GETPALINK状態354に止まる。

30

GETVA状態356において、状態機械308は3番目のDWORDを要求キューVA+FLAGSレジスタ(RQB\_VA+FLAGS)に書き込む。3番目のDWORDは、現パケット250のVA+FLAGSフィールド値270である。VA+FLAGSフィールド値270を書き込む間、状態機械308は、ビット4でI/O取り消しをチェックし、更にビット3でダイレクト・アクセスをチェックする。ビット3は、RQB\_LENGTH=0の場合にのみチェックするように制限が設けられる。いずれかのビットがセットされている場合、状態機械308はWRITE状態360(以下で論ずる)に遷移し、パケットはI/Oデバイス208に提出されない。ビット3及び4がセットされていないが、RQB\_LENGTH=0である場合、状態機械308は、DONE状態362(以下で論ずる)に遷移する。その他の場合、状態機械308はNEXTDWORD状態358に遷移し、DQRDY信号をアサートして、I/Oデバイス208にデータが準備できていることを示す。

40

#### 【0067】

NEXTDWORD状態358において、DQ\_RQ信号をアサートし、DWORDを要求キュー・バッファ312からポップする。DWORDがI/Oデバイス208によって読み込まれる毎に、デバイス・レディ(DEVICEDQRDY)信号がI/Oデバイス208から受け取られ、LENGTHレジスタを1だけ減分する。LENGTH値が1hに達したとき、DQRDY信号をディアサートし、状態機械308はDONE状態362に遷移する。

50

DONE状態362において、状態機械308は、非同期、割り込み、又はポールの内どの型のパケットが完了したかについて判定を行なう。DQ\_RQ信号をディアサートし、パケット情報をキューから取り出す(dequeue)のを停止する。パケット型を判定するために、状態機械308はRQB\_VALINKレジスタ内に格納されているVALINKフィールド値270のビット1及び2を検査する。ビット2 : 1 = 1 h (DBE\_PKT\_SUBMIT\_A)の場合、状態機械308はWRITE状態360に遷移する。ビット2 : 1 = 2 h (DBE\_PKT\_SUBMIT\_P)又は2 : 1 = 3 h (DBE\_PKT\_SUBMIT\_I)の場合、状態機械308はWAIT状態366に遷移し、I/Oデバイス208へのDONE信号をアサートし、パケット250が処理されたことの承認を要求する。

## 【0068】

10

WAIT状態366において、状態機械308はI/Oデバイス208からの完了通知を待つ。PROCESS\_DONE信号がI/Oデバイス208から受け取られ、パケットが非同期パケットであった場合、DONE信号はディアサートされ、状態機械308は再びIDLE状態350に遷移する。PROCESS\_DONE信号がI/Oデバイス208から受け取られ、パケットが非同期パケットでなかった場合、DONE信号はディアサートされ、状態機械308はWRITE状態360に遷移する。PROCESS\_DONE信号が受け取られない場合、状態機械はWAIT状態366において待機する。

WRITE状態360において、現パケット250のPA\_LINK268及びVA+FLAGS270フィールドの値を、完了キュー276に書き込む。パケットの型もキュー上でマークするので、フロント・エンドは、それが処理しようとするパケットの型がわかる。

20

## 【0069】

状態機械308は、完了キュー276が満杯でなく(CQFULL)、ポステッド・キュー・バック・エンド状態機械310が使用中でない(CQBUSY)場合、AGAIN信号に基づいて、WRITE状態360を通じて2回のバスを行なう。その他の場合、状態機械308は、完了キュー276が満杯でなくなり、使用可能となるまで待機する。AGAINは最初にセットされるので、最初のバスではAGAINはセットされず、2回目のバスでセットされる。

最初のバスでは、現パケットの物理アドレス(PA)が、完了キュー276に書き込まれる。2回目のバスは、パケット型によって異なる。

パケット型が非同期の場合、現パケット250の仮想アドレスが完了キュー276に書き込まれ、ビット33 : 34に2hが書き込まれ、非同期パケットであることを意味する。

30

状態機械308は、パケット250にI/O取り消しのマークが付けられている場合、又はダイレクト・アクセスのマークが付けられていない場合、WAIT状態366に遷移する。その他の場合(パケット250に、I/O取り消しのマークが付けられていなかつたが、ダイレクト・アクセスのマークが付けられていた場合)、状態機械308はDIRECTACC状態364に遷移し、対応する要求レジスタ(Rq<sub>n</sub>\_REG)内のダイレクト・アクセス・ビットをクリアし、チャネルが使用可能であることあるいは同期されていることを、デバイス・ドライバ230に示す。

## 【0070】

パケット型がポールの場合、現パケット250の仮想アドレスが完了キュー276に書き込まれ、ビット33 : 34に1hが書き込まれ、ポール・パケットであることを意味する。状態機械308は、パケット250にI/O取り消しのマークが付けられていたか、あるいはダイレクト・アクセスのマークが付けられていなかつた場合、IDLE状態350に遷移する。その他の場合(パケット250にはI/O取り消しのマークが付けられていなかつたが、ダイレクト・アクセスのマークが付けられていた場合)状態機械308はDIRECTACC状態364に遷移し、対応する要求レジスタ(Rq<sub>n</sub>\_REG)内のダイレクト・アクセス・ビットをクリアし、デバイス・ドライバ230に、チャネルが使用可能であることあるいは同期されていることを示す。

40

パケット型が割り込みの場合、現パケット250の仮想アドレスが完了キュー276に書き込まれ、ビット33 : 34に3hが書き込まれ、割り込みパケットであることを意味する。状態機械308は、パケット250にI/O取り消しのマークが付けられていた場合

50

、IDLE状態350に遷移する。パケット250にダイレクト・アクセスのマークが付けられていた場合、状態機械308はDIRECTACC状態350に遷移し、対応する要求レジスタ(Rq<sub>n</sub>\_REG)内のダイレクト・アクセス・ビットをクリアし、デバイス・ドライバ230に、チャネルが使用可能であることあるいは同期されていることを示す。その他の場合、状態機械308はWAIT状態350に遷移する。

DIRECTACC状態364において、状態機械308は、デバイス・ドライバ230がダイレクト・アクセス動作を完了するのを待つ。状態機械308は、デバイス・ドライバ230が要求レジスタ(Rq<sub>n</sub>\_REG)内の終了ダイレクト・アクセス・ビット(ビット3)をセットするまで、要求キュー・バッファ312からいかなる追加データも引き出さない。

#### 【0071】

10

図15A、及びBには、図11のポステッド・キュー・バック・エンド状態機械(PQSMBEND)310の対応するフロー・チャート、及び状態遷移条件が示されている。ポステッド・キュー・バック・エンド状態機械310の出力を図15のCに示す。他に特に示されていない限り、出力は、それらに予め割り当てられた論理値から不变のままである。

ポステッド・キュー・バック・エンド状態機械310は、ポステッド・キュー・バッファ316から非請求パケットのアドレスを引き出し、それらをI/Oデバイス208に提示する役割を担う。I/Oデバイス208は、これらのアドレスをメモリ112内の位置として用い、非請求データを「ダンプ」する。ポステッド・キュー・バック・エンド状態機械310は、常に、2つのDWORD(PALINK及びVA+FLAGS)をポステッド・キュー・バッファ316から除去する。DBEデバイス206によって受け取られた非請求データは、ポステッド・キュー・フロント・エンド状態機械306によって供給された物理アドレス及び仮想アドレスを用いて、メモリ112に書き込まれる。

20

#### 【0072】

20

ポステッド・キュー・バック・エンド状態機械310は、非請求パケットの物理ペイロード・アドレスを完了キュー・バッファ314に書き込む。次いで、ポステッド・キュー・バック・エンド状態機械310は、I/Oデバイス208に、その非請求データを、現パケット250のための非請求パケットのペイロード・データ・エリアの長さだけ、完了キュー・バッファ314に「ダンプ」するよう要求する。一方、I/Oデバイス208は、データの「ダンプ」を完了したときに、ポステッド・キュー・バック・エンド状態機械310に通知する。次に、ポステッド・キュー・バック・エンド状態機械310は、非請求パケットの仮想及び物理アドレス・ヘッダ情報を、完了キュー・バッファ314内に置く。完了キュー状態機械304は、このパケットを割り込み型パケット250として完了する。

30

ポステッド・キュー・バック・エンド状態機械310は、システム・リセット又はRESETモードからIDLE状態370に初期化し、I/Oデバイス208からのポステッド・パケット要求(POSTPACKETREQ)信号を待つ。POSTPACKETREQ信号がアサートされ、ポステッド・キュー・バッファ310が空いておらず(PQEMPTY)、更にマルチプレクサ制御信号(MUXVA)がアサートされていない場合、完了キュー・ビジー(CQBUSY)信号がセットされ、現パケットの物理アドレスがポステッド・キュー・バッファ310から除去されてラッチされ、ペイロードの物理アドレスが完了キュー上に置かれ、マルチプレクサ制御信号がセットされ(1)、I/Oデバイス208からデータを受け取り、状態機械310はGETVA状態372に遷移する。

40

#### 【0073】

GETVA状態372において、ポステッド・キュー・バッファ316が空でない場合(PQEMPTY)、状態機械は、I/Oデバイス208に、ポステッド・パケット250が準備できている(POSTPACKETRDY)ことを通知し、データを完了キュー・バッファ314に「ダンプ」し、WAIT状態374に遷移する。

WAIT状態374において、ポステッド・パケット終了(POSTPACKETDONE)信号がI/Oデバイス208から受け取られた場合、マルチプレクサ制御信号を再度セットし(0)、ポステッド・キュー・バック・エンド状態機械310からパケット仮想アドレス(VA+FLAGS)を

50

受け取る。POSTPACKETDONE信号が受け取られ、完了キュー・バッファ314は満杯ではなく、POSTPACKETRDY信号がアサートされた場合、状態機械310はPOSTPACKETRDY信号をディアサートし、現パケットの物理アドレス(PA\_LINK)を完了キュー・バッファ314上に押し出す。完了キュー・バッファ314が満杯でなく、POSTPACKETRDY信号がディアサートされた場合、仮想アドレス(VA+FLAGS)を完了キュー276上に置く。

#### 【0074】

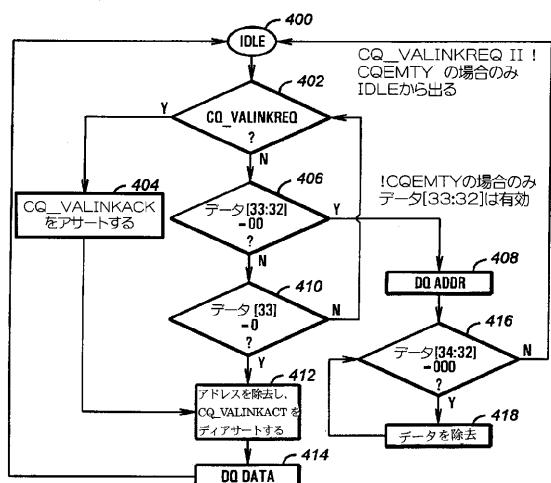

次に、図16～図19を参照すると、完了キュー状態機械304を更に詳細に説明する。図17は、バス・マスター/F300の制御のフロー・チャートである。完了キュー状態機械304は、バス・マスター/F300が完了キュー・バッファ314からアドレス及びデータを引き出す際、マルチプレクサ(MUX2)324を通じて、データのフローを制御する。

図17を参照する。バス・マスター/F300は、IDLE状態400において待機している。ステップ400において、完了キューVAリンク要求(CQ\_VALINKREQ)信号が受け取られたか、あるいは完了キュー・バッファ314が空でない場合、バス・マスター/F300はステップ402に遷移し、CQ\_VALINKREQ信号を検査する。CQ\_VALINKREQが完了キュー状態機械304によってアサートされている場合、バス・マスター/F300はステップ404に進む。CQ\_VALINKREQがない場合、バス・マスター/F300はステップ406に進み、完了キュー・バッファ314の出力のビット33：32を検査する。ビット33：32が0に等しい場合、バス・マスター/F300はステップ408に進む。ビット33：32が0でない場合、バス・マスター/F300はステップ410に進み、ビット33を検査する。ステップ410において、ビット33が0に等しくない場合、バス・マスター/F300はステップ402に戻る。ステップ410において、ビット33が0に等しい場合、バス・マスター/F300はステップ412に進み、パケット・アドレス情報を除去する。ステップ412から、バス・マスター/F300はステップ414に進み、完了キュー・バッファ314からパケット・データを除去する。ステップ414から、制御はIDLE状態400に戻る。

#### 【0075】

ステップ404において、バス・マスター/F300は、完了キューVAリンク承認(CQ\_VALINKACK)信号をアサートする。ステップ404から、制御はステップ412に進み、パケット・アドレス情報を除去し、CQ\_VALINKACK信号をディアサートする。

ステップ408において、バス・マスター/F300は、パケット・アドレス情報を除去する。ステップ408から、制御はステップ416に進み、除去したパケット・アドレスのビット34：32を検査する。ビット34：32が0に等しい場合、制御はステップ418に進み、完了キュー・バッファ314からパケット・データを除去する。ステップ416, 418は、ビット34：32がもはや0に等しくなくなる(パケット・データを除去する)まで繰り返される。ステップ416において、ビット34：32が0に等しくない場合、制御はIDLE状態400に戻る。

完了キュー状態機械(CQSM)304は、完了及びフリー・キュー・リンクを維持する役割を担う。また、完了リンク・リストをCQ\_REG286に提示し、CQ\_REG286のライト完了時に、バス・マスター/F300に割り込みをセットすることを通知する役割も担う(ボスティッド・パケット及び割り込みパケットのみ)。完了キュー状態機械304は、請求及び非請求イベントから完了パケットを受け取る。要求キュー274に発行された割り込みパケット、及びI/Oデバイス208によって非請求データで満たされた非請求パケット・プール202から発した全てのパケットには、完了が要求される。

#### 【0076】

プロセッサ100は、完了キューが処理され(service)、プロセッサ100が他の完了パケットのリストの準備ができたときに、CQ\_REG286のCQ\_DOORBELLビットを鳴らす(ring)。メモリ112内の完了キュー276がプロセッサ100によって処理されていない場合、完了キュー状態機械304は、現完了パケットの仮想アドレスを、直前に完了したパケット250のVAフィールド270に書き込む。完了キュー状態機械304は、次回パケ

10

20

30

40

50

ットが完了を要求するときのために、現パケット250の物理アドレスをテールTとしてセーブする。

メモリ112内の完了キュー276が完了パケット250のリストを受け入れる準備ができる場合、完了パケットのリストにおける最初のパケット250の仮想アドレスVAが、メモリ112の完了キュー276に書き込まれる。完了キュー276のヘッドの物理アドレスは、CQ\_REG286内に位置付けられる。その後、完了キュー状態機械204の内部ヘッド／テール・レジスタは消去(null)され、新たな完了リストを開始する。

完了キュー状態機械304は、ドライバによって非同期要求として提出されたパケット250も完了させる。非同期パケット250内に指定されている処理が終了したなら、完了キュー状態機械304は、パケット250の仮想アドレスVAを請求パケット・プール200のテールT上に置く。請求パケット・プール200のテールTは、FQ\_REG284を通じて、DBEデバイス206によって維持される。パケットの仮想アドレスVAが直前のパケットのVALINKフィールド260に書き込まれた後、完了キュー状態機械304は、パケットの物理アドレスPAをFQ\_REG284内に置く。

10

#### 【0077】

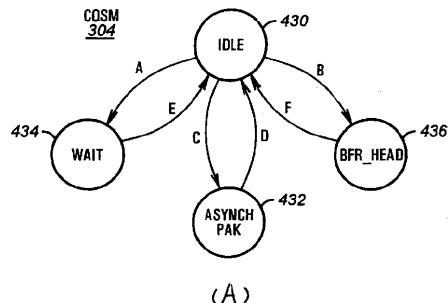

図18及び図19を参照し、完了キュー状態機械の動作について説明する。完了キュー状態機械304は、システム・リセット時又はRESETモード時に、IDLE状態430に初期化する。完了キュー状態機械304は、次の3つのイベントの1つが発生するまで、IDLE状態で待機する。1) 完了キュー・ドアベル(CQ\_DOORBELL)が鳴らされ、完了キュー・バッファ314がヌルでない。2) 完了した割り込みパケット20を、完了キュー276のテールにリンクする必要がない。又は3) 完了した非同期パケットが、完了キュー276のテールTにリンクする必要がある。

20

完了キュー・ドアベル(CQ\_DOORBELL)が鳴らされ、完了キュー・ヘッド・レジスタ(CQ\_HEAD)438がヌルでない場合、完了キュー状態機械304は、CQ\_VALINKREG信号及びバス・マスターI/F300へのセット割り込み(SETINTERRUPT)信号をアサートし、バス・マスターI/F300が割り込みの準備ができているか否か調べる。CQ\_HEAD438は、状態機械304によって維持され、完了リストを追跡する。バス・マスターI/F300は、CQ\_VALINKACK信号によって応答し、状態機械304は、MUX2に、CQ\_REG内の物理アドレスを通過させ、次いで、CQ\_HEAD内に位置する完了リストのヘッドの仮想アドレスをバス・マスターI/F300に受け渡す。次に、CQ\_HEAD及び完了キュー・ドアベル・ビット(CQ\_DOORBELL)をクリアし、状態機械304はWAIT状態434に遷移する。

30

#### 【0078】

CQ\_DOORBE LLがセットされていないか、あるいはCQ\_HEADが0に等しい場合で、かつバス・マスターI/F300からのレディ信号(GO)がセットされている場合、状態機械304は、完了キュー276から最初のDWORDを引き出し(現パケットの物理アドレス)、それを完了キュー・テール・レジスタCQ\_TAIL440に書き込む。このDWORDは、完了キュー276上の最後のパケットの物理アドレスである。次に、状態機械304は、BFR\_HEAD状態436に遷移する。

BFR\_HEAD状態において、現パケットの仮想アドレスを格納する。完了キュー・ヘッド・レジスタが0に等しくなく、CQ\_DOORBELLがセットされていない場合、状態機械304はCQ\_VALINKREQ信号をアサートし、直前のパケットの物理アドレス(CQ\_TAIL)をバス・マスターI/F300に受け渡す。バス・マスターI/F300がCQ\_VALINKACK信号で応答すると、完了キュー・バッファ314の最初のDWORDがCQ\_TAILレジスタ440に書き込まれ、状態機械304はASYNCHPAK状態432に遷移する。(現パケットの仮想アドレスは、直前のパケットの物理アドレス(CQ\_TAIL)に書き込まれる。)

40

#### 【0079】

CQ\_DOORBELLがセットされていないか、あるいはCQ\_HEADが0に等しい場合で、かつバス・マスターI/F300からのレディ信号(GO)がセットされ、現パケットが非同期パケットであることをビット34:33が示す場合、状態機械304はCQ\_VALINKREQ信号をアサートし、次のパケットの仮想アドレスをバス・マスターI/F300に受け渡す。バス・マスター

50

I / F 3 0 0 がCQ\_VALINKACK信号で応答すると、FQ\_REG 2 8 4 の内容がバス・マスター / F 3 0 0 に受け渡され、完了キュー・バッファ 3 1 4 からの最初のDWORDがFQ\_REG 2 8 4 に書き込まれ、完了キュー・バッファ 3 1 4 からの仮想アドレスがFQ\_REG 2 8 4 の直前の内容に書き込まれ、状態機械 3 0 4 はASYNCHPAK状態 4 3 2 に遷移する。

ASYNCHPAK状態 4 3 2 において、状態機械 3 0 4 は、GO信号がディアサートされ、IDLE状態 4 3 0 に遷移するのを待つ。デバイス・ディキュー(DEVICEDQ)信号が受け取られ、AGAIN信号がアサートされていない場合、MUX2がセットされ、完了キュー・バッファ 3 1 4 からのアドレスを受け取る。DEVICEDQ信号は、バス・マスター / F 3 0 0 によって供給され、完了キュー・バッファ 3 1 4 からデータを引き出す。AGAIN信号は、状態機械 3 0 4 をASYNCHPAK状態 4 3 2 に止めておく。MUX2は、本質的に、完了キュー・バッファ 3 1 4 とFQ\_REG 2 8 4との間の切り替えを制御する。GO信号がディアサートされると、状態機械はIDLE状態 4 3 0 に再び遷移する。

10

WAIT状態 4 3 4 において、状態機械 3 0 4 はIDLE状態 4 3 0 に戻る前に、割り込みが発生したことの確認を待つ。IN TROUTB信号をバス・マスター / F 3 0 0 から受け取った場合、CQ\_HEADを消去し、状態機械はIDLE状態 4 3 0 に戻る。

BRF\_HEAD状態 4 3 6 では、完了中の現パケットの仮想アドレスを、完了した直前のパケットのVALINKフィールド 2 6 0 に書き込む。

#### 【 0 0 8 0 】

##### D B E / ブリッジ

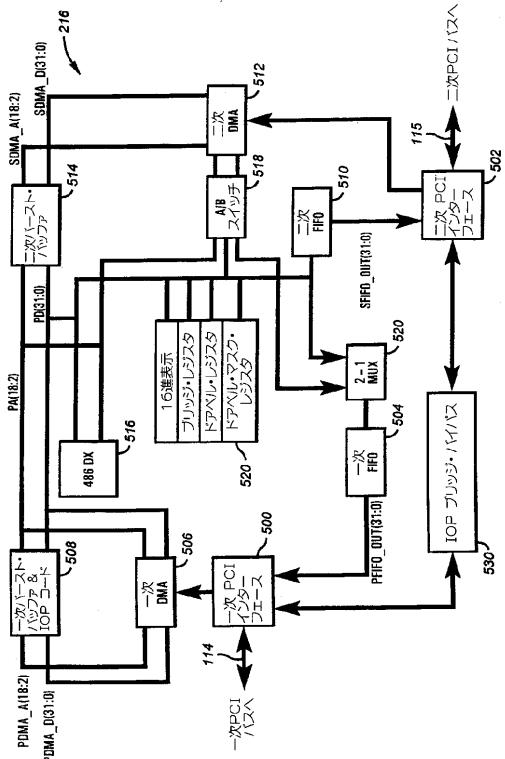

次に図 2 0 を参照すると、図 6 の D の D B E / ブリッジ 2 1 6 の更に詳細なブロック図が示されている。これは、一次 PCI バス I / F コントローラ 5 0 0 及び二次 PCI バス I / F コントローラ 5 0 2 と共に示されているが、代わりに、ホスト・バス 1 0 2 を含むその他のバスに、これらのインターフェースを適合化させることも可能である。各 PCI コントローラ 5 0 0 , 5 0 2 は、マスター及びスレーブ I / F を内蔵する。上述した同じパケット・アーキテクチャ及びプロトコルが図 1 1 のハードウェアに適用されるので、ここでは繰り返さないことにする。

20

D B E / ブリッジ 2 1 6 は、2つの機能的半部分において見ることができる。即ち、一方の半部分は一次 PCI バス 1 1 4 と通信し、他方の半部分は二次 PCI バス 1 1 5 と通信する。一次 PCI バス半部分は、一次 PCI バス I / F コントローラ 5 0 0 , 一次 F I F O 5 0 4 , 一次ダイレクト・メモリ・アクセス(DMA)コントローラ 5 0 6 、及び一次バースト・バッファ(PBB) 5 0 8 を内蔵する。二次 PCI バス半部分は、二次 PCI バス I / F コントローラ 5 0 2 、二次 F I F O 5 1 0 、二次 DMA コントローラ 5 1 2 、及び二次バースト・バッファ(SBB) 5 1 4 を内蔵する。バースト・バッファ 5 0 8 , 5 1 4 は、好ましくは、デュアル・ポート型とし、I / O プロセッサ 5 1 6 及び DMA エンジン(5 0 6 又は 5 1 2 )又は PCI I / F (5 0 0 又は 5 1 2 )のいずれか双方の同時アクセスを可能とすることによって、PCI デバイス 1 1 8 、I / O プロセッサ 5 1 6 、及びプロセッサ 1 0 0 間の潜在的なボトルネックを全て解消する。しかしながら、従来の DRAM 又は SRAM のような他の形式のメモリも、バースト・バッファ 5 0 8 , 5 1 4 を形成するために使用可能である。

30

#### 【 0 0 8 1 】

また、D B E / ブリッジ 2 1 6 には、埋め込み I / O プロセッサ 5 1 6 も含まれており、プロセッサ 1 0 0 からの介入を受けずに、データを転送するために必要なインテリジェンス(intelligence)を与える。これは、D B E / ブリッジ 2 1 6 に接続されている PCI デバイス 1 1 8 を効果的にプロセッサ 1 0 0 から切り離し、プロセッサ 1 0 0 、D B E / ブリッジ 2 1 6 、及び PCI デバイス 1 1 8 間の同時性及び負荷均衡配分を最大に高める。I / O プロセッサ 5 1 6 は、好ましくは、Advanced Micro Devices486 プロセッサであるが、いずれの形式のプロセッサでも使用可能である。データ・キャッシュは、I / O プロセッサ 5 1 6 においてはディスエーブルされる。メモリ・コントローラを含ませ、データ・キャッシュのコヒーレンシを確保することも可能である。

一次バースト・バッファ 5 0 8 の一部は、I / O プロセッサ 5 1 6 のためのコードを格納

40

50

するために割り当てられる。あるいは、別個のリード・オンリ・メモリ(ROM)を用いて、コード又はコンフィギュレーション情報を格納することも可能である。メモリ・コントローラは、I/Oプロセッサ516に結合され、プロセッサ・サイクルを、以下の分類にデコードする。ROMリード/ライト、バースト・バッファ(ローカル・メモリ)ヒット、FIFOリード/ライト、DMAコントローラ・コンフィギュレーション、ローカル・レジスタ・リード/ライト、16進ステータス・ディスプレイ・ライト、PCIコンフィギュレーション、及びその他(PCISイクル)である。あるサイクルがローカル・アドレス空間に該当しない場合、このサイクルをPCIサイクルに変換する。

#### 【0082】

異なるPCIデバイス118と通信するときに、種々のステータス及びコマンド・フォームマットを、デバイス・ドライバ230が理解することのできるパケット250にカプセル化するのは、I/Oプロセッサ516の役割である。10

PCIバスの最大速度でのバースト処理を容易に行うために、一次(PBB)及び二次(SBB)バースト・バッファ504, 506が設けられており、これらは、一次及び二次ダイレクト・メモリ・アクセス(DMA)コントローラ508, 510によってそれぞれ制御される。一次DMAコントローラ508は、一次バースト・バッファ504と一次PCIバス114との間でデータを転送する役割を担う。二次DMAコントローラ510は、二次バースト・バッファ506と二次PCIバス115との間でデータを転送する役割を担う。

一次及び二次FIFO504, 510は、DMAコントローラ506, 512に転送を行わせることに加えて、そしてそれに代わる更に効率的な代替案として、データを転送するために設けられている。DMAコントローラ506又は512の一方によってデータが転送される場合、一次及び二次PCIバス114, 115双方を利用する。例えば、二次DMAコントローラ512がデータを二次バースト・バッファ514からメモリ112に転送しようとした場合、二次PCIバス115だけでなく、一次PCIバス114も使用不可能となる。データは、一次及び二次バースト・バッファ508, 514において、主にDBE/ブリッジ216内に受け取られる。したがって、DMAコントローラ506, 512にデータを一次及び二次バースト・バッファ508, 514からDBE/ブリッジ216外部に移動させる代わりに、DMAコントローラ506, 512は、データをFIFO504, 510内に移動させることができる。その後、PCIバス114, 115双方に影響を与えることなく、FIFO504, 510の一方からデータを移動させることができる。例えば、PCIデバイス118がデータを二次バースト・バッファ514に書き込む場合、二次DMAコントローラ512は、データを一次FIFO504に移動させることができる。一旦これが行われたなら、二次PCI-I/F502が他のデータ・ブロックを受け取っている間、一次PCI-I/F500からデータを転送することができる。2030

#### 【0083】

このバースト・バッファ508, 514と一次及び二次FIFO間のデータの移動を容易に行うために、スイッチ518及びマルチブレクサ520を設け、図20に示すようにデータを通過させ、データの経路を決定する。加えて、DBE/ブリッジ216は、ドアベル・レジスタ520を含む多数のレジスタを備えている。40

また、一次PCIバス114と二次PCIバス115との間に接続されているI/Oプロセッサ・ブリッジ・バイパス回路(IOPブリッジ・バイパス)530も示されている。好ましくは、これは、IBM 82352PCI-PCIブリッジのような、従来からのPCI-PCI間ブリッジ・デバイスである。バイパス・ブリッジ530は、二次PCIバス115に対する調停を行い、二次PCIバス115及びそれに関連する割り込みを、一次PCIバス114から効果的に分離する。

#### 【0084】

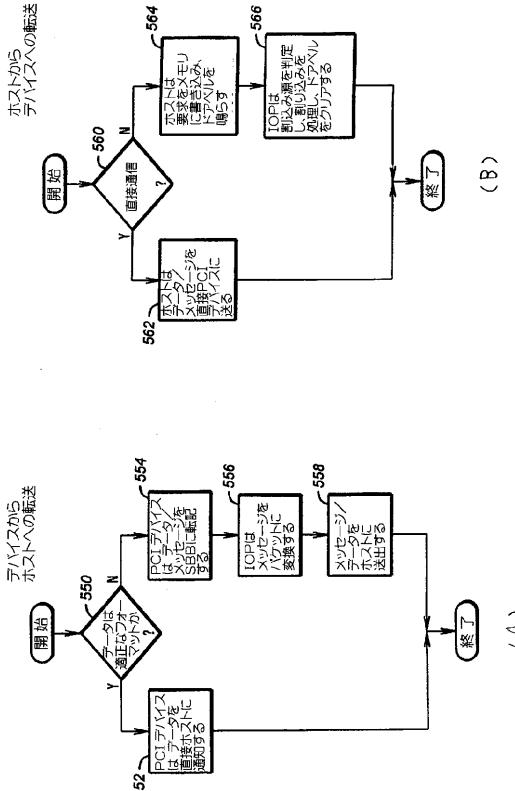

図21のAは、PCIデバイス118及びホスト100間の転送を示すフロー・チャートである。このプロセスは、典型的に、PCIデバイス118がメッセージ/データを二次バースト・バッファ514に転記(post)したときに開始する。あるいは、PCIデバイス50

118がD B Eプロトコルに準拠する場合、PCIデバイス118はデータを直接メモリ112に転記することができる。ステップ550において、PCIデバイス118が適正なフォーマットでデータを供給可能か否かについて判定を行う。可能であれば、処理はステップ552に進み、PCIデバイス118は、適正にフォーマットされたデータ／メッセージを直接メモリ112に転記する。この場合、I/Oプロセッサ516は、PCIデバイス118に対してアドミニストレータ(administrator)となり、バイパス・ブリッジ530を用いて、データ／メッセージをホスト100に移動させる。可能でない場合、処理はステップ554に進み、PCIデバイス118はデータ／メッセージを二次バースト・バッファ514に転記する。ステップ556において、I/Oプロセッサ516は、このデータ／メッセージをD B Eと互換性のあるプロトコルに変換し、データ／メッセージをパケット250にカプセル化する。データ／メッセージをフォーマットした後、ステップ558において、データ／メッセージは、DMA転送によってホスト100に送出するか、あるいは一次FIFO554に転記することができる。データ／メッセージを一次FIFO554に転記することによって、データの連続的な順序が保証される。

10

#### 【0085】

図21の(B)に示すホスト-PCIデバイス118間の転送では、データ／メッセージをPCIデバイス118に送るプロセスは、PCIデバイス-ホスト間転送(図21のA)と同様である。ステップ560において、ホスト100がPCIデバイス118と直接通信可能か否かについて判定を行う。可能であれば、ステップ562において、ホストはデータ／メッセージを直接バイパス・ブリッジ530を通じてPCIデバイス118に送る。可能でない場合、ステップ564において、ホスト100は要求をメモリ112に書き込み、対応するドアベル520を鳴らす。ドアベル520は、I/Oプロセッサ516に割り込みを発生させる。ドアベルが鳴らされた場合、ステップ566においてI/Oプロセッサ516は、割り込み源を判定し、その割り込みを処理し、ドアベルをクリアする。I/Oプロセッサは、請求パケット及び非請求パケットを、D B Eデバイス206と同様に取り扱う。

20

以上、ホスト100とI/Oデバイス208との間でパケット250を移動するためのパケット・プロトコル及び複数の選択可能なハードウェア・エンジンを説明した。

#### 【0086】

本発明の上述の開示及び説明は、本発明の例示及び説明のためのものであり、サイズ、形状、材料、構成部品、回路素子、配線接続及びコンタクト、ならびに図示の回路及び構造や、動作方法の詳細において、本発明の精神から逸脱することなく、様々な変更が可能である。

30

#### 【図面の簡単な説明】

【図1】本発明によるコンピュータ・システムCのブロック図である。

【図2】Aは、好適な実施形態による本発明のシステム・アーキテクチャを示すブロック図である。

Bは、好適な実施形態による本発明のソフトウェア・システム・アーキテクチャを示すブロック図である。

【図3】好適な実施形態によるパケット・アーキテクチャを示すブロック図である。

40

【図4】好適な実施形態によるパケット・キューを示すブロック図である。

【図5】好適な実施形態によるD B Eデバイスのハードウェア・レジスタを示すブロック図である。

【図6】Aは、PCIバスに沿ったD B Eデバイスの第1の配置を示すブロック図である。

Bは、図1のホスト/PCIブリッジにおけるD B Eデバイスの第2の実施形態を示すブロック図である。

Cは、ブリッジ/メモリ・コントローラ・デバイスにおけるD B Eデバイスの第3の実施形態を示すブロック図である。

Dは、PCI/PCIブリッジにおけるD B Eデバイスの第4の実施形態を示すブロック図である。

50

【図 7】好適な実施形態による D B E デバイスの更なる詳細を示すブロック図である。

【図 8】好適な実施形態による D B E デバイスの要求キュー・フロント・エンド状態機械及びポステッド・キュー・フロント・エンド状態機械のブロック図である。

【図 9】要求キュー・フロント・エンド状態機械の状態遷移図、状態遷移条件、及び出力を示す図である。

【図 10】ポステド・キュー・フロント・エンド状態機械の状態遷移図、状態遷移条件、及び出力を示す図である。

【図 11】好適な実施形態による D B E デバイスの要求キュー・バック・エンド状態機械及びポステッド・キュー・バック・エンド状態機械のブロック図である。

【図 12】要求キュー・フロント・エンド状態機械の状態遷移図である。 10

【図 13】要求キュー・フロント・エンド状態機械の状態遷移条件、及び出力を示す図である。

【図 14】要求キュー・フロント・エンド状態機械の出力を示す図である。

【図 15】ポステド・キュー・フロント・エンド状態機械の状態遷移図、状態遷移条件、及び出力を示す図である。

【図 16】好適な実施形態による D B E デバイスの完了キュー状態機械のブロック図である。

【図 17】好適な実施形態による図 7 のバス・マスタ・インターフェースのプロセスを示すフロー・チャートである。

【図 18】完了キュー状態機械の状態遷移図、及び状態遷移条件を示す図である。 20

【図 19】完了キュー状態機械の出力を示す図である。

【図 20】D B E デバイスの代替実施例を示すブロック図である。

【図 21】デバイス - ホスト間転送及びホスト - デバイス間転送を示すフロー・チャートである。

【図 1】

【図 2】

【 四 3 】

【図4】

【 四 5 】

【 四 6 】

【図7】

【四 8】

【図9】

【図10】

```

ABORT_CYCLE - 1#  NEXTPKT* ROTLATCH_EN ~ CHECKVA ~ RDDATA[4] + RDDATA[3];

ABORT_CYCLE - 0#  NEXTPKT* RD_RODUNE;

CLR_RX_DODBELL - 1#  ~IDLE ~ RD_DODBELL;

DISABLE_LATCH - 1#  IDLE +;

DISABLE_LATCH - 0#  NEXTPKT* ROTLATCH_EN ~ CHECKVA ~ RDDATA[4](INCLUDING rddata4 + RDDATA[3]);

DISABLE_LATCH - 0#  RD - 0#  IDLE + WAIT;

RD - 0#  IDLE + WAIT;

RD_RX - 1#  NEXTPKT* ROTLATCH_EN ~ DISABLE_LATCH;

RD_LEN - 1#  2h IF IDLE;

RD_LEN[0:0] - NEXTPKT* RD_RODUNE + RD_PALINK[31:5] - 0#;

RD_MUX - 0#  NEXTPKT* ROTLATCH_EN ~ ROMUX_EN;

RD_RQED - 1#  (IDLE ~ RD_DODBELL) +

(WAIT ~ IRQFULL);

RD_RQED - 1#  NEXTPKT* RD_RODUNE ~ RD_PALINK[31:5] - 0# ~ IRQFULL;

RD_RQED - 0#  NEXTPKT* ROTLATCH_EN ~ ROMUX_EN;

RD_RQED - 0#  NEXTPKT* ROTLATCH_EN ~ ROMUX_EN;

RD_READADOR_B31:5 - <- RD_REG[31:5] - IDLE;

RD_READADOR_B31:5 - <- RD_REG[31:5] + 4h IF NEXTPKT * INCRAOD;

RD_READADOR_B31:5 - <- RD_PALINK[31:5] ~ NEXTPKT * RD_RODUNE ~ RD_PALINK[31:5] - 0#;

RD_READADOR_B31:5 - <- RD_PALINK[31:5] ~ NEXTPKT * RD_RODUNE;

RD_REG[31:5] - <- RD_PALINK[31:5] + IDLE ~ REGVERG;

RD_REG[31:5] - <- RD_PALINK[31:5] + WAIT ~ IRQFULL;

RD_REG[31:5] - <- RD_PALINK[31:5] ~ NEXTPKT * RD_RODUNE ~ RD_PALINK[31:5] - 0# ~ IRQFULL;

RD_REG[31:5] - <- RD_PALINK[31:5] ~ NEXTPKT * RD_PALINK[31:5] ~ NEXTPKT * ROTLATCH_EN ~ ROMUX_EN;

```

【图 11】

【 図 1 2 】

【 図 1 3 】

```

RSMBEND 指標變量多條件

A: IDLE * !RD_RQEMPTY;

B: GETLENGTH * !RD_RQEMPTY;

C: GETPALINK * !RD_RQEMPTY;

D: GETVA * !RD_BFR[4] + !RD_BFR[3] * LENGTH[9:0] - 0h;

E: GETVA * LENGTH[9:0] * !RD_BFR[4] + !RD_BFR[3] * LENGTH[9:0] - 0h;

F: GETVA * !RD_BFR[4] + !RD_BFR[3] * LENGTH[9:0] - 0h;

G: NEXTWORD * DEVICEORDIR * LENGTH[9:0];

H: DIRECTACC * DAC_DoorBell * CLR_DAC_DOORBELL;

I: DONE * !RD_VALINK[2:1] - 1h;

J: IDONE * !RD_VALINK[2:1] - 1h;

K: IWRITE * !ICFULL * !ICBUSY * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * !RD_VALINK[4] + !RD_VALINK[3];

L: IWRITE * !ICFULL * !ICBUSY * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * !RD_VALINK[4] + !RD_VALINK[3];

M: IWRITE * !ICFULL * !ICBUSY * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * !RD_VALINK[4] + !RD_VALINK[3];

N: IWRITE * !ICFULL * !ICBUSY * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * !RD_VALINK[4] + !RD_VALINK[3];

O: IWRITE * !ICFULL * !ICBUSY * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * !RD_VALINK[4];

P: WAIT PROCESS_DONE * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A;

Q: WAIT PROCESS_DONE * !RD_VALINK[2:1]-DBE_PKT_SUBMIT_A;

```

【 図 1 4 】

```

ROSMBEND(07)

CLR_DAC_DOORBELL < -0 if

CLR_DAC_DOORBELL < -1 if

IDLE + DIRECTACC;

[WRITE * ICODEFULL & ICODEBUSY * RD_VALINK[2:1]-DBE_PKT_SUBMIT_A * AGAIN * IRO_VALINK[4] +

IRO_VALINK[3][1] +

[WRITE * ICODEFULL & ICODEBUSY * RD_VALINK[2:1]-DBE_PKT_SUBMIT_P * AGAIN * IRO_VALINK[4] +

IRO_VALINK[3][1] +

[WRITE * ICODEFULL & ICODEBUSY * RD_VALINK[2:1]-DBE_PKT_SUBMIT_I * AGAIN * IRO_VALINK[4] +

IRO_VALINK[3][1];

DO_RQ < -1 if

IDLE * IROEMPTY +

GETPALINK * IROEMPTY +

GETLENGTH * IROEMPTY;

otherwise DO_RQ < -0;

DORDY < -1 if

DORDY < -0 if

NEXTWORD * DEVIEDORDY * LENGTH[8:0]-0h;

WRITE * ICODEFULL * ICODEBUSY;

RO_CO < -1 if

RO_CO < -0 if

IDLE + DIRECTACC + WAIT;

```

【図15】

POSMFEND 状態遷移条件

A: IDLE \* COBUSY;

B: GETVA \* !POEMPTY;

C: WAIT \* !COFULL \* !POSTPACKETRDY;

POSMFEND 出力

COBUSY < -0 if WAIT \* !COFULL \* !POSTPACKETRDY;

COBUSY < -1 if IDLE \* POSTPACKETREQ \* !POEMPTY \* !MUXVA;

DO\_CQ < -1 if IDLE \* COBUSY +

(WAIT \* POSTPACKETDONE \* !COFULL \* POSTPACKETRDY) +

(WAIT \* !COFULL \* !POSTPACKETRDY);

DO\_CQ < -0 if IDLE \* !COBUSY + GETVA + WAIT;

DO\_PQ < -1 if IDLE \* (MUXVA + COBUSY);

otherwise DO\_PQ = 0;

POSTPACKETRDY < -0 if WAIT \* POSTPACKETDONE \* !COFULL \* POSTPACKETRDY;

POSTPACKETRDY < -1 if GETVA \* !POEMPTY;

【図16】

【図17】

【図18】

COSM 状態遷移条件

A: IDLE \* CO\_DORBL \* (CQ\_HEAD[31:2] != 0h) \* CQ\_VALINKACK;

B: IDLE \* !(CO\_DORBL \* (CQ\_HEAD[31:2] != 0h)) \* GO \* !CQ\_BFR\_ADR[34] \*

(CQ\_BFR\_ADR[33:32]-3h) \* (CQ\_HEAD[31:2]-0);

C: IDLE \* !(CO\_DORBL \* (CQ\_HEAD[31:2] != 0h)) \* GO \* !CQ\_BFR\_ADR[34] \*

(CQ\_BFR\_ADR[33:32]-3h) \* !(CQ\_HEAD[31:2]-0) \* CQ\_VALINKACK +

(IDLE \* !CO\_DORBL \* (CQ\_HEAD[31:2] != 0h)) \* GO \* !CQ\_BFR\_ADR[34] \*

(CQ\_BFR\_ADR[33:32]-2h) \* CQ\_VALINKACK;

D: ASYNCH \* GO;

E: WAIT \* INTROUTB;

F: don't care;

(B)

【図19】

```

CSM出力

CLR_CQ_DOORBELL <- 1 if IDLE * CQ_DOORBELL * [CQ_HEAD(31:2)-0h] * CQ_VALINKACK;

CLR_CQ_DOORBELL <- 0 if WAIT * INTROUTB;

CQ_HEAD(31:2) <- CQ_BFR_ADR(1:2) if BFR_HEAD;

CQ_HEAD(31:2) <- 0 if WAIT * INTROUTB;

CQ_TAIL(31:2) <- CQ_BFR_ADR(31:2);

(IDLE * [CQ_DOORBELL * [CQ_HEAD(31:2)-0h]] * GO * [CQ_BFR_ADR(34)] *

IDLE * [CQ_DOORBELL * [CQ_HEAD(33:32)-3h] * [CQ_HEAD(31:2)-0h] +

[CQ_BFR_ADR(33:32)-3h]] * GO * [CQ_BFR_ADR(34)] * [CQ_VALINKACK];