【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成18年9月21日(2006.9.21)

【公表番号】特表2006-511955(P2006-511955A)

【公表日】平成18年4月6日(2006.4.6)

【年通号数】公開・登録公報2006-014

【出願番号】特願2004-564756(P2004-564756)

【国際特許分類】

|               |                |           |

|---------------|----------------|-----------|

| <i>H 01 L</i> | <i>23/52</i>   | (2006.01) |

| <i>H 01 L</i> | <i>21/3205</i> | (2006.01) |

| <i>H 01 L</i> | <i>21/288</i>  | (2006.01) |

| <i>H 01 L</i> | <i>23/522</i>  | (2006.01) |

| <i>H 01 L</i> | <i>21/768</i>  | (2006.01) |

| <i>H 01 L</i> | <i>21/82</i>   | (2006.01) |

【F I】

|               |               |   |

|---------------|---------------|---|

| <i>H 01 L</i> | <i>21/88</i>  | R |

| <i>H 01 L</i> | <i>21/288</i> | E |

| <i>H 01 L</i> | <i>21/90</i>  | N |

| <i>H 01 L</i> | <i>21/82</i>  | W |

| <i>H 01 L</i> | <i>21/88</i>  | S |

【手続補正書】

【提出日】平成18年8月4日(2006.8.4)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

半導体装置(10)を形成する方法であって、

半導体基板(12)を提供すること、

第1の誘電体層(34または36)を形成すること、

前記第1の誘電体層をパターニングして第1の開口部を形成すること、

前記第1の開口部内に導電性領域(30または44)を形成すること、

前記導電性領域上にパッシベーション膜(32または54)を無電解めっきすること、

を含む方法。

【請求項2】

前記パッシベーション膜(32)上に第2の誘電体層(36)を形成すること、前記第2の誘電体層に空隙(66または68)を形成することをさらに含む、請求項1記載の方法。

【請求項3】

半導体装置(10)を形成する方法であって、

半導体基板(12)を提供すること、

第1の誘電体層(36)を形成すること、

前記第1の誘電体層をパターニングして、互いに隣接しているが互いに分離された第1の開口部および第2の開口部を形成すること、

前記第1の開口部内に第1の導電領域(44、48a、または48b)を形成すること、

前記第2の開口部内に第2の導電領域(48a、48b、または44)を形成すること、

前記第1の開口部および前記第2の開口部上に第2の導電層(54)をめっきして、物理的に互いに分離された第1のキャップ(54)および第2のキャップ(54)を形成すること、

を含む方法。

【請求項4】

半導体装置(10)を形成する方法(300)であって、

半導体基板(12)を提供すること、

前記半導体基板上に第1の誘電体層を形成すること、

前記第1の誘電体層内に導電領域を形成すること、

前記導電領域をエッチングして、前記導電領域に窪みを形成すること(302)、

前記導電領域上に触媒溶液を加えて、前記導電領域を触媒活性にすること(304)、

キレート剤溶液を加えて、前記触媒溶液の一部分を除去すること(306)、

前記導電領域上にパッシベーション膜を無電解めっきすること(308)、

を含む方法。

【請求項5】

半導体装置(10)であって、

半導体基板(12)と、

前記半導体基板上の第1の誘電体層(36)と、

前記第1の誘電体層内の第1の導電領域(44, 48a, または48)と、

前記第1の誘電体層内の、前記第1の導電領域とは互いに分離された第2の導電領域(44, 48a, または48)と、

前記第1の導電領域上の、無電解めっきされた第1のパッシベーション膜(54)と、

前記第2の導電領域上にあって、前記無電解めっきされた第1のパッシベーション膜とは物理的に分離され、無電解めっきされた第2のパッシベーション膜(54)と、

前記無電解めっきされた第1のパッシベーション膜および前記無電解めっきされた第2のパッシベーション膜上に形成された、第2の誘電体層(72)と、

を含む半導体装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0018

【補正方法】変更

【補正の内容】

【0018】

第1のパッシベーション膜32の形成後、一実施形態では、第1のパッシベーション膜32および第2の誘電体層34上に、エッチング停止層(図示せず)が任意に形成される。エッチング停止層は、炭化ケイ素、有機材料、またはCVD、PVD、SOD(スピンドル法)等、またはそれらの組合せによってエッチング停止層上に続いて形成される第3の誘電体層36(層間誘電体層)とは異なるエッチング速度を有する任意の他の材料であつてもよい。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0020

【補正方法】変更

【補正の内容】

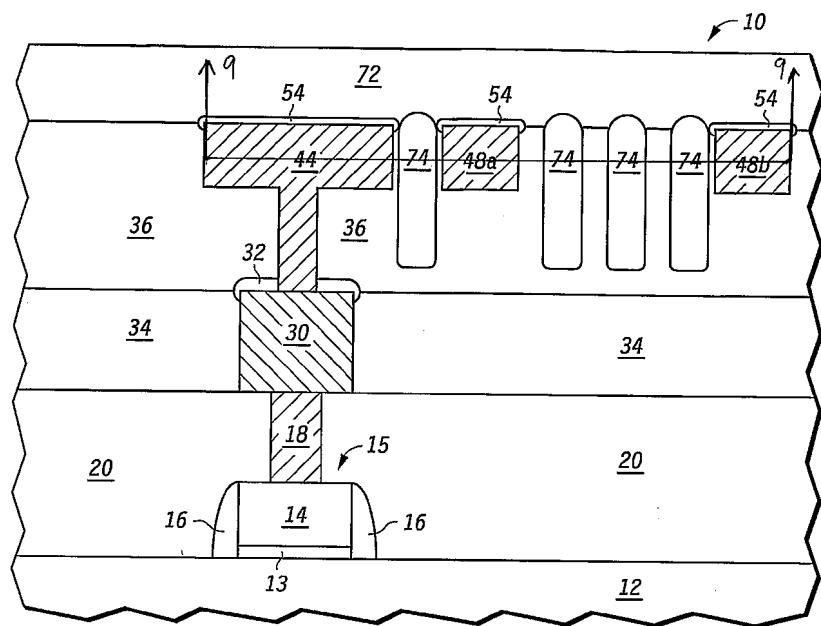

【0020】

次に、CVD、PVD、ALD等、またはそれらの組合せを使用して、導電性材料を配線開口部および導電性ダミーフィーチャ開口部内に蒸着してこれらを充填するとともに、第3の誘電体層36上にも蒸着する。一実施形態では、化学機械研磨(CMP)プロセスが実行され、余分な導電性材料(すなわち、配線開口部および導電性ダミーフィーチャ開口部内に無い導電性材料)が除去され、図3に示すように、第2の導電領域30と電気的

に接続される導電領域 4 4、第 1 の導電性ダミーフィーチャ 4 8 a、および第 2 の導電性ダミーフィーチャ 4 8 b が形成される。他の実施形態では、エッチバックプロセスを使用して、余分な導電性材料を除去することができる。図示した実施形態では、第 1 の導電性ダミーフィーチャ 4 8 a は、空隙の間隔より小さいかそれに等しい幅を有する第 1 の絶縁領域 3 7 によって導電領域 4 4 から分離されており、第 2 の導電性ダミーフィーチャ 4 8 b は、空隙の間隔より大きい幅を有する第 2 の絶縁領域 3 9 によって第 1 のダミーフィーチャ 4 8 a から離間している。

#### 【手続補正 4】

【補正対象書類名】明細書

【補正対象項目名】0 0 2 1

【補正方法】変更

【補正の内容】

【0 0 2 1】

図 4 に示すように、第 2 のパッシベーション膜（キップ）5 4 が、導電領域 4 4、第 1 の導電性ダミーフィーチャ 4 8 a、および第 2 の導電性ダミーフィーチャ 4 8 b 上に形成される。第 2 のパッシベーション膜 5 4 は、第 1 のパッシベーション膜 3 2 の形成に関して説明したような無電解めっきを使用して形成されるのが好ましい。したがって、第 2 のパッシベーション膜 5 4 は導電領域 4 4 ならびに導電性ダミーフィーチャ 4 8 a、および 4 8 b 各々より外に延在し、第 3 の誘電体層 3 6 上を覆う。同じ材料および加工フローを利用することができるが、第 1 のパッシベーション膜 3 2 および第 2 のパッシベーション膜 5 4 は、必ずしも同じ材料または同一のプロセスを使用して形成されなくてもよい。代わりに、第 1 のパッシベーション膜 3 2 の形成について説明したいずれかの方法を使用してもよい。

#### 【手続補正 5】

【補正対象書類名】明細書

【補正対象項目名】0 0 2 2

【補正方法】変更

【補正の内容】

【0 0 2 2】

図 5 に示すように、半導体装置 1 0 上に（フォト）レジスト層 5 8 が蒸着され、パターニングされて第 1 の開口部 6 0 が形成され、第 1 の絶縁領域 3 7、ならびに導電領域 4 4 および第 1 の導電性ダミーフィーチャ 4 8 a 上に形成された第 2 のパッシベーション膜 5 4 が露出される。さらに、フォトレジスト層 5 8 がパターニングされ、第 2 の絶縁領域 3 9 および第 2 の導電性ダミーフィーチャ 4 8 b 部上に多くのダミー開口部 6 2 が形成される。以下により詳細に説明するように、導電領域 4 4 と第 1 の導電性ダミーフィーチャ 4 8 a 間の第 1 の絶縁領域 3 7 は続いてエッチングされるが、第 2 のパッシベーション膜 5 4 が存在するため、導電領域 4 4 または第 1 の導電性ダミーフィーチャ 4 8 a が損傷またはエッチングされることはない。したがって、第 1 の開口部 6 0 の幅を変えることができ、また絶縁領域 3 7 の幅程度に小さいか、または導電領域 4 4 および第 1 の導電性ダミーフィーチャ 4 8 a の上に延在することができる。すなわち、第 1 の開口部 6 0 は、エッチングされる第 3 の誘電体層 3 6 の任意の部分と第 2 のパッシベーション膜 5 4 部を露出する。したがって、第 1 の開口部 6 0 は、続いてエッチングされる領域（すなわち、第 1 の絶縁領域 3 7）より大きくてもよい。

#### 【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0 0 2 5

【補正方法】変更

【補正の内容】

【0 0 2 5】

絶縁性ダミースペース 6 8 が存在することにより第 1 の絶縁性ダミーフィーチャ 6 4 が

形成されるが、以下の説明でさらに理解されるように、これらはまたエアギャップ形成プロセスの一部としても形成される。第2の絶縁性ダミーフィーチャ65aおよび65bは、図6に示す実施形態では、第1の導電性ダミーフィーチャ48aおよび第2の導電性ダミーフィーチャ48bに隣接し、かつこれらと物理的に接触している第3の誘電体層36の一部を構成しているが、配線または導電性ダミーフィーチャと物理的に接触することもできる。第2の絶縁性ダミーフィーチャ65aおよび65bは、一実施形態では、第1の導電性ダミーフィーチャ48aおよび第2の導電性ダミーフィーチャ48bを絶縁するために形成されるのであって、すべての実施形態において必要なわけではない。図6に示すように、第2の絶縁性ダミーフィーチャ65aは、第2のパッシベーション膜54を越えて横方向に延在し、一方第2の絶縁性ダミーフィーチャ65b（および第3の絶縁性ダミーフィーチャ67）は、パッシベーション膜54が覆い被さっている量にほぼ等しい幅を有している。各絶縁性ダミーフィーチャは、特にそれらが半導体装置10において、静電容量に対する異なる感度または要件を有する異なる領域に位置する場合、互いに同じ幅を持つ必要はない。パッシベーション膜54が覆い被さっているため、第3の誘電体層36部は、導電性領域44, 48a, および48bと隣接したままであり、導電領域44, 48a, または48bを保護する第2の絶縁性ダミーフィーチャ65bおよび第3の絶縁性ダミーフィーチャ67を形成している。第2のパッシベーション膜54は、上記のごとく、第3の誘電体層36をエッチングする際に除去されないので、第3の誘電体層36をエッチングするのに使用されるマスクパターンおよびフォトレジストパターンは、第2のパッシベーション膜54を露出する開口部を有することができる。したがって、マスクパターンおよびフォトレジストパターンの開口部の許容誤差は重要ではなく、加工が容易になる。

#### 【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0028

【補正方法】変更

【補正の内容】

【0028】

図7に示す実施形態では、エアギャップ74は第3の誘電体層36内のみに形成されるので、第3の誘電体層36の底面までまたはそこを越えるところまでは延在しない。すなわち、エアギャップ74は、1つの配線層内に形成される。図8に示す代替の実施形態では、エアギャップ106は、第3の誘電体層（ILD）104および第2の誘電体層94を通じて、第1の誘電体層89内まで延在している。したがって、エアギャップ106は、複数の配線層内に形成される。図8のエアギャップ105は、1つの配線レベルを通じて延在しているため、図7のエアギャップ74に類似している。エアギャップ105はまた、第2の導電領域92上に形成されたパッシベーション膜96の上で止まっている。

#### 【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正の内容】

【0029】

図8に示す半導体装置80は、2つの主要な点で図7に示す半導体装置10と異なっている。すなわち、（1）（図7に示す1つのみのトランジスタと対照的に）図8では第1のトランジスタ85および第2のトランジスタ87が存在している点、（2）図8では、エアギャップ105および106が第3の誘電体層36を越えて延在している（すなわち、エアギャップ105および106が、半導体装置80の多層に存在している）点である。半導体基板81上に形成される第1のトランジスタ85は、第1のゲート誘電体83、第1のゲート電極84および第1の側壁スペーサ86を有している。第2のトランジスタ87は、第2のゲート誘電体82、第2のゲート電極107および第2の側壁スペーサ9

1を有している。第1および第2のトランジスタ85および87に対して、ソース領域およびドレイン領域(図示せず)が、半導体基板81内の第1の側壁スペーサ86および第2の側壁スペーサ91の下に、それぞれ存在している。

#### 【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0031

【補正方法】変更

【補正の内容】

#### 【0031】

図7の導電領域44と類似の第3の導電領域98は、第1の導電領域88と電気的に接続され、また導電性ダミーフィーチャ100は、図7の導電性ダミーフィーチャ48aおよび48bと類似の形態である。図7に示した実施形態における第1のパッシベーション膜32と類似した第2のパッシベーション膜102が、第3の導電領域98および導電性ダミーフィーチャ100の上に形成される。図8における半導体装置80の要素に使用されるプロセスおよび材料は、図1および図3から図7における半導体装置10の同じ要素について上で説明した同じプロセスおよび材料であってもよい。

#### 【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0036

【補正方法】変更

【補正の内容】

#### 【0036】

図10に示した他の実施形態では、エアギャップ74を形成したのと同じ方法で形成されたエアギャップ290は、正方形または長方形等の所定の形状で、所定の行数および所定の列数のパターンまたは配列である。エアギャップ290は、配線または導電性ダミーフィーチャであってもよい第1の導電性領域294と、第1の導電性領域294と同じまたは異なる機構であってもよい第2の導電性領域292との間にある。さらに、第1の導電性領域294または第2の導電性領域292が導電性ダミーフィーチャである場合、それらはまた、長方形または正方形等所定の形状の繰返しパターンであってもよい。したがって、一実施形態では、エアギャップ290は導電性領域(配線または導電性ダミーフィーチャ)より実質的に短い長さを持つが、他の実施形態では、エアギャップ290と導電性ダミーフィーチャは同じ長さであり、それは配線の長さよりも短い。他の実施形態では、エアギャップを導電性領域より大きくしてフリンギング電界効果を低減している。1つまたは複数の大きいダミーフィーチャではなく、多数の小さいダミーフィーチャを使用することによって、誘電体層部をダミーフィーチャ間に残し、次に実行される研磨プロセスおよび実装における機械的な堅牢性を向上させることもできる。

#### 【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0040

【補正方法】変更

【補正の内容】

#### 【0040】

第2の領域420および第3の領域422は、各々第2の主要回路402bと第3の主要回路402cとを含んでいる。主要回路402a, 402b, および402cは、異なる静電容量の要件を有するという点ですべて互いに異なっている。第1の領域418では、ダミーフィーチャ406は、第1の形状、密度、大きさ、間隔、およびパターンを有して形成される。ダミーフィーチャ406に対して選択される形状、大きさ、密度、間隔およびパターンならびに材料は、第1の主要回路402a間の所望の静電容量結合に基づいて決定される。第2の領域420および第3の領域422は、ダミーフィーチャ408および410を各々有し、これらは、主要回路402aから402c間の静電容量結合の条

件が異なるため、形状、大きさ、密度、間隔およびパターンが各領域において異なり、またダミーフィーチャ406とも異なっている。第1の領域418および第2の領域420は、ダミーフィーチャ406および408が、それらと主要回路402aと402bとの間の異なる間隔を有するという点で互いに異なっている。したがって、有効な誘電率が異なっているので、主要回路402aと402b間の静電容量結合は異なる。有効な誘電率が異なるのは、斜線の領域425と426として示したエアギャップの異なる領域が、ダミーフィーチャ406および408自体と主要回路402aと402bとの間に形成されるためである。402aと402bは主要回路であるため、それらの間の結合を最小化し、それによりダミーフィーチャ406同士間、およびダミーフィーチャ406と主要回路402間にエアギャップを形成することが望ましい。したがって、ダミーフィーチャ406および408同士間の間隔、ならびにダミーフィーチャ406および408と主要回路402aと402b間の間隔は、半導体チップ400の他の領域にある同様の機構間の間隔よりは大きいが、それらの間にエアギャップを形成するのには十分に小さすぎる。エアギャップの面積は、第2の領域420よりも第1の領域418において大きいため、(ダミーフィーチャ406および408が同じ材料であるとすれば)第1の領域418の静電容量結合の方が小さい。絶縁性の場合と比較して、ダミーフィーチャが導電性の場合には、静電容量結合は実際に増加することができるため、ダミーフィーチャ406および408に選択される材料は、静電容量結合に影響がある。その理由は、デバイス性能によって第2の領域420よりも第1の領域418における静電容量結合が最小化されることが望ましいからである。

#### 【手続補正12】

【補正対象書類名】明細書

【補正対象項目名】0041

【補正方法】変更

【補正の内容】

#### 【0041】

第2の領域420および第3の領域422におけるダミーフィーチャのパターンは、互いに同じ間隔を有しているが、ダミーフィーチャ408および410の大きさは異なっている。図11に示すように、ダミーフィーチャ410部の幅はダミーフィーチャ408の幅より大きいため、ダミーフィーチャ410はダミーフィーチャ408より大きく、それによって主要回路402bおよび402cの間の機械的安定性および静電容量結合を変えることができる。図11に示すように、エアギャップ426および427を形成できる面積がより小さいため、(ダミーフィーチャ410および406が同じ材料であるとすれば)第3の領域422間の静電容量結合は、第2の領域420よりも大きい。この静電容量結合の違いは、デバイス性能によって促進される。さらに、第3の領域422内のすべてのダミーフィーチャ410の面積は第2の領域420のそれよりも大きいため、ダミーフィーチャ408および410に使用される材料に関わらず、第3の領域は、第2の領域420よりも大きい機械的安定性を有している。

#### 【手続補正13】

【補正対象書類名】図面

【補正対象項目名】図7

【補正方法】変更

【補正の内容】

【図7】