(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3549364号

(P3549364)

(45) 発行日 平成16年8月4日(2004.8.4)

(24) 登録日 平成16年4月30日(2004.4.30)

(51) Int.C1.<sup>7</sup>

F 1

H01L 21/8247

H01L 29/78 371

H01L 27/115

H01L 27/10 434

H01L 29/788

H01L 29/792

請求項の数 1 (全 16 頁)

(21) 出願番号

特願平9-142031

(22) 出願日

平成9年5月30日(1997.5.30)

(65) 公開番号

特開平10-84054

(43) 公開日

平成10年3月31日(1998.3.31)

審査請求日

平成9年9月30日(1997.9.30)

審判番号

不服2001-6434(P2001-6434/J1)

審判請求日

平成13年4月23日(2001.4.23)

(31) 優先権主張番号

60/018694

(32) 優先日

平成8年5月30日(1996.5.30)

(33) 優先権主張国

米国(US)

(31) 優先権主張番号

08/863917

(32) 優先日

平成9年5月27日(1997.5.27)

(33) 優先権主張国

米国(US)

(31) 優先権主張番号

08/863918

(32) 優先日

平成9年5月27日(1997.5.27)

(33) 優先権主張国

米国(US)

(73) 特許権者 593205691

ヒュンダイ エレクトロニクス アメリカ

アメリカ合衆国 カリフォルニア州 95

134 サン ホセ ノース ファースト

ストリート 3101

(74) 代理人 100059959

弁理士 中村 稔

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100065189

弁理士 宍戸 嘉一

(74) 代理人 100096194

弁理士 竹内 英人

最終頁に続く

(54) 【発明の名称】三重ウェルを有するフラッシュ・メモリ・セルの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表面を有する第1導電型の半導体基板内に、第1導電型の導電性とは反対の第2導電型の、周辺を有する第1ウェル領域を形成するステップと、第1ウェル領域の周辺内に、かつ表面の近傍に第1導電型の第2ウェル領域を形成するステップと、これも第1ウェル領域の周辺内に、第2ウェル領域から間隔を隔てて第2導電型であって、第1ウェルよりも導電率が高い第1接点領域を形成するステップと、を有する三重ウェル・フラッシュ・メモリ・セルを含む集積回路メモリの製造方法において、

基板表面上に第1の厚さの第1の絶縁層を配設し、

前記第2ウェル領域上の上記第1の絶縁層の第1の部分をエッチングし、

前記第2ウェル領域の前記エッチングされた第1の部分に第1の厚さと異なる第2の厚さの第2の絶縁層を配設し、

フローティングゲートを設けるために前記第2の絶縁層上に第1導電層を堆積し、かつ周辺回路の第1のトランジスタのゲートを設けるために第1の絶縁層上に第1導電層を堆積して、前記フローティングゲート及び前記周辺回路内の第1のトランジスタのゲートが基板表面上に配置され、かつ電気的に該表面から絶縁されるようにし、

前記第1導電層の表面上に第4の絶縁層を配設し、

前記第1ウェル領域上の前記第1の絶縁層の第2の部分をエッチングし、

前記エッチングされた第2の部分に第1及び第2の厚さと異なる第3の厚さの第3の絶縁層を配設し、

10

20

周辺回路の第2のトランジスタのゲートを設けるために前記第3の絶縁層上に第2導電層を堆積し、そして、

前記フローティングゲートの上方に、前記フローティングゲートから電気的に絶縁された制御ゲートを設けるために、前記第4の絶縁層上に第3導電層を堆積するステップからなることを特徴とする製造方法。

【発明の詳細な説明】

【0002】

【発明の属する技術分野】

本発明は集積回路不揮発性メモリに関し、特にフラッシュ・メモリに関する。フラッシュ・メモリとは一度の操作でセル群を消去できる電気的消去可能な不揮発性メモリのことである。

10

【0003】

【従来の技術】

現在、多くの種類の集積回路メモリが、その製造工程とともに公知である。集積回路メモリの特定の一つの種類が不揮発性メモリである。不揮発性メモリがそう呼ばれるのは、メモリから電力を遮断してもメモリ内に記憶された情報が失われないからである。不揮発性メモリは給電が遮断されることがある製品に多くの用途を持っている。例えば、フラッシュ・メモリを使用している公知の製品の一つはP C M C I A、もしくはP C カードである。P C カードは内部にコンピュータ・プログラムまたはその他の情報が記憶されている不揮発性メモリを収納した小型のクレジットカードのサイズのパッケージである。このようなデバイスによって、ユーザーはメモリ・カード内に記憶されたプログラムを失うことなくメモリ・カードをコンピュータ、またはその他の電子機器に接続したり、遮断したりすることができる。

20

【0004】

不揮発性メモリ・デバイスには読み出し専用メモリ(ROM)、プログラムできる読み出し専用メモリ(PROM)、電気的消去可能な読み出し専用メモリ(EEPROM)、並びにその他の種類がある。電気的消去可能なプログラムできるメモリの分野の中で、ある分類のデバイスはフラッシュ・メモリ、またはフラッシュEEPROMとして知られている。このようなメモリは選択的にプログラム可能、および消去可能であり、代表的にはセル群を一度の操作で消去できる。

30

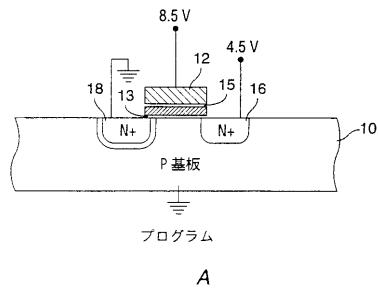

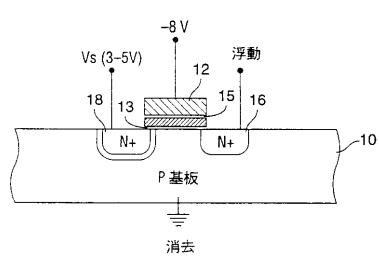

従来形のフラッシュ・メモリでは、各メモリ・セルはソース、ドレン、制御ゲートおよびフローティングゲートを有するトランジスタから構成されている。フローティングゲートは制御ゲートと基板との間に形成されている。フローティングゲート上に捕捉された電荷の有無は、メモリ・セルの内容を表示するために利用できる。フローティングゲートに捕捉された電荷によってトランジスタのしきい値電圧が変化し、その2進状態を検知することが可能になる。図1Aおよび図1Bは従来形の代表的なフラッシュ・メモリ・セルを示している。

【0005】

ほとんどのフラッシュ・メモリでは、内容を読み出すための通常の動作状態以外の状態でメモリを動作することによって、電荷がフローティングゲートに印加され、またはそこから除去される。例えば、ゲートとソース、ドレンまたはチャネル領域の間の相対電位を調整することによって、電子の形態の電荷をフローティングゲートへと注入し、またはフローティングゲートから除去することができる。

40

既成のフラッシュ・メモリの残念な欠点は、フローティングゲートをプログラムするために制御ゲートに高電位を印加しなければならないことにある。例えば、制御ゲートに8.5ボルトのような高い正電圧を印加し、ソース領域をアースすることによって、電子はソースからフローティングゲートへと引き寄せられ、そこで捕捉される。そこで、メモリ・セル内に“1”または“0”が存在することを表示するため、フローティングゲートの負の電荷を利用できる。プログラミング(または消去)のためにこのような高電位を使用する必要があることの残念な結果は、周辺回路をそのような高電位を処理できるように設計

50

しなければならないことである。言い換えると、8.5ボルトが印加されるトランジスタとアクセス回路の全てが、それ自体で8.5ボルトの電位を処理できなければならない。更に高電位によって漏れ電流が生じ、ホットホール劣化を引き起こす。このような代表的な従来形のNOR負・セルの一つは米国特許明細書第5,077,691号「負のゲート電圧消去機能を伴うフラッシュ EEPROMアレイ」に記載されている。

### 【0006】

#### 【発明が解決しようとする課題】

従って、より低い電位で動作し、上記の不都合な作用を最小限にし、性能が向上するフラッシュ・メモリを提供することが望ましく、そのための好適な集積回路メモリの製造方法が必要とされている。

10

### 【0007】

#### 【課題を解決するための手段】

本発明は上述した先行技術のフラッシュ・メモリ・セルと比較して利点を有するフラッシュ・メモリ・セルを、関連する周辺回路とともに製造する集積回路メモリの新規且つ好適な製造方法を提供するものである。

本発明によって得られる三重ウェル・フラッシュ・メモリ・セルは、メモリ・セルが基板から電気的に絶縁され、上述した先行技術のフラッシュ・メモリ・セルで使用されるよりも大幅に低い電圧を利用してプログラムおよび消去が可能である。それによって、同じ集積回路チップ上にある周辺回路をより低い電圧を処理するように設計できるという利点が得られると共に、より小型のトランジスタを使用でき、その結果、収率が高まり、信頼性が高まり、コストが低下する。

20

### 【0008】

本発明によると、表面を有する第1導電型の半導体基板内に、第1導電型の導電性とは反対の第2導電型の、周辺を有する第1ウェル領域を形成するステップと、第1ウェル領域の周辺内に、かつ表面の近傍に第1導電型の第2ウェル領域を形成するステップと、これも第1ウェル領域の周辺内に、第2ウェル領域から間隔を隔てて第2導電型であって、第1ウェルよりも導電率が高い第1接点領域を形成するステップと、を有する三重ウェル・フラッシュ・メモリ・セルを含む集積回路メモリの製造方法において、基板表面上に第1の厚さの第1の絶縁層を配設し、前記第2ウェル領域上の上記第1の絶縁層の第1の部分をエッチングし、前記第2ウェル領域の前記エッチングされた第1の部分に第1の厚さと異なる第2の厚さの第2の絶縁層を配設し、フローティングゲートを設けるために前記第2の絶縁層上に第1導電層を堆積し、かつ周辺回路の第1のトランジスタのゲートを設けるために第1の絶縁層上に第1導電層を堆積して、前記フローティングゲート及び前記周辺回路内の第1のトランジスタのゲートが基板表面上に配置され、かつ電気的に該表面から絶縁されるようにし、前記第1導電層の表面上に第4の絶縁層を配設し、前記第1ウェル領域上の前記第1の絶縁層の第2の部分をエッチングし、前記エッチングされた第2の部分に第1及び第2の厚さと異なる第3の厚さの第3の絶縁層を配設し、周辺回路の第2のトランジスタのゲートを設けるために前記第3の絶縁層上に第2導電層を堆積し、そして、前記フローティングゲートの上方に、前記フローティングゲートから電気的に絶縁された制御ゲートを設けるために、前記第4の絶縁層上に第3導電層を堆積するステップからなることを特徴とする製造方法が提供される

30

### 【0012】

#### 【実施例】

図1はプログラム・モード(図1A)と消去モード(図1B)の従来のフラッシュ・メモリ・セルを示している。図示されたフラッシュ・メモリ・セルは代表的には単結晶シリコンである基板10と、二重拡散されたソース領域18と、ドレン領域18とを含んでいる。基板の上方に薄い絶縁層13によって間隔を隔てられてフローティングゲート15が配置されている。フローティングゲートの上方には、フローティングゲートから電気的に絶縁されて制御ゲート12が配置されている。代表的には、図示したフラッシュ・メモリ・セルは著しく大規模なメモリ、たとえば100万ビットオーダのフラッシュ・メモリを備

40

50

えた集積回路チップに单一のビットを付与するものである。集積回路上の個々のトランジスタは直交して配列されたビット線と語線とのマトリクスに構成されている。代表的には、ドレン領域16はビット線に接続され、一方、制御ゲート12は語線に接続される。このようにしてマトリクスのアドレス指定がなされる。

#### 【0013】

図1Aおよび図1Bに示したフラッシュ・メモリ・セルは幾つかの異なるモード、すなわちプログラム、消去、および読み出しモードで動作することができる。それぞれのモードの動作状態は後述する。

従来形のデバイスのプログラム・モードでは、好ましくは+8.5ボルトの高電圧が選択されたワード線用の制御ゲート12に印加される。選択されない語線はアース電位のままに留まる。選択されたビット線は約+4.5ボルトに設定され、このビット線はドレン16と結合される。ソース領域18はアースされる。このような条件の結果、チャネル電流によってホット電子が生成され、制御ゲート上の+8.5ボルトの電位によって誘引され、フローティングゲート15とチャネル領域18の間の酸化物薄層をトンネリングする。フローティングゲートに到達すると、上記の電子は捕捉され、フローティングゲートに負の電荷を荷電する。負の電荷はトランジスタのしきい電圧を変化させる。このようにしてメモリ・セルがプログラムされる。

#### 【0014】

従来形のメモリ・セルを読み出すには、代表的には約+5ボルトのVccである電位が選択された語線に印加され、一方、約1ボルトが選択されたビット線に印加される。フローティングゲート上に電子が存在するか、しないかによってトランジスタはターンオンし難くなったり、し易くなったりする。ビット線が電位を変化させたか否かを検出することによって、フローティングゲートの状態を検知することができる。

図1Bに示した消去モードでは、通常は-8.5ボルトである大きい負電圧が、消去されるべく選択されたデバイス群の制御ゲートに印加される。ビット線の電位は浮動することができ、一方ソースは例えば3から5ボルトである中間的な正の電位に保持される。制御ゲート上の負の電位とソース上の正の電位の組合せが電子をフローティングゲートから遊離させて、ソース領域を経て基板へと戻すことによってフローティングゲートを放電し、セルを消去する。

#### 【0015】

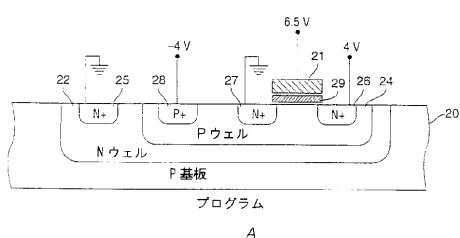

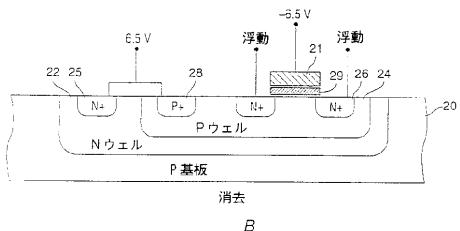

図2Aおよび図2Bは本発明の実施例に基づくフラッシュ・メモリ・セルの断面図を示している。同じセルが図2Aと図2Bに示されているが、図2Aはプログラミング用の状態を示し、図2Bは消去用の状態を示している。図2Aでは、フラッシュ・メモリ・セルは好適にシリコン基板20内に製造されている。基板はP導電型のシリコンであり、P型基板20内にはN導電型のシリコン・ウェル22が形成されている。（図2Aおよび図2Bに示した構造の製造工程は後述する。）Nウェル22は図示したフラッシュ・メモリ・セルを含み、代表的には百または千オーダーのセルを含むだけの充分な規模である。通常は、少なくともブロック消去動作に必要な数のセルがNウェル22に形成される。Nウェル22内には、P導電型のウェル24が形成される。Pウェル24と電気的に接触させるため、ソース27とドレン26が付加的にドーピングされた領域28とともにPウェル内に形成される。フローティングゲート29と制御ゲート21も示されている。Nウェル22のバイアスを可能にするためNウェルへの接点25が設けられている。

#### 【0016】

セルをプログラムするには、好適な実施例では制御ゲート21が最高+9.0ボルト、好ましくは+6.5ボルトの電位に保たれ、一方、ドレン26は+5ボルト、またはそれ未満、好ましくは+4ボルトの正の供給電圧に接続される。ソース27はNウェル接点25と同様にアースされている。PウェルへのP接点28は代表的には-4ボルトである負の電位に保たれる。

図示した状態によって電界エンハンスメント型チャネルのホット電子効果が生じ、それによって、Pウェル上の負の電圧と、制御ゲート上の正の電圧により電子はチャネル上方の

10

20

30

40

50

ゲート酸化物を経てフローティングゲート 29 上へとトンネリングする。それによってフローティングゲートに負の電荷が荷電される。第1図に示した従来形の回路と比較して、大幅に低いプログラミング電位しか必要ないことに留意されたい。それによってより高い容量の周辺回路の必要が縮減され、動作電位が低下し、電力消費が節減される。

#### 【0017】

プログラミングの後、図2Aに示したセルは代表的にはVcc、すなわち+5ボルトの正の電位を制御ゲート21に印加し、1ボルト信号をビット線26に印加することによって読み出しができる。選択されないワード線はアース電位に保持され、一方、選択されないビット線の電位は浮動状態のままであることができる。フローティングゲート29上に電子が存在するか否かによってトランジスタはターンオンし難くなったり、し易くなったりし、この状態はドレン26に接続されたビット線によって検知される。トランジスタがターンオンすると、ビット線はアースへと放電される。そこでビット線は“1”または“0”として読み取られる。

図示したデバイスは図2Bに示した状態を利用して消去できる。図示のように、セルを消去するには制御ゲートは最高-9.0ボルト、好ましくは-6.5ボルトのより低い電位に設定され、一方、Pウェル24とNウェル22は最高+8ボルトであるが、+6.5ボルトであることが好ましい正の電位にされる。ウェル上の正の電位は、制御ゲート上の負の電位と結合されてフローティングゲート上の電子をゲート酸化物を経て再び基板内に戻るように誘引させ、それによってデバイスを消去する。図2Bに示したデバイスには図1Bに示したデバイスに対してより大幅に低い電位が印加されることに再度留意されたい。10

#### 【0018】

下記の表1は図2Aおよび図2Bに示した3重ウェルを有するセルの読み出し、消去、およびプログラミング状態を要約したものである。プログラム確認、消去2、およびプログラム2モードも示されている。これらについては後述するが、基本的に消去2およびプログラム2モードがソース側の消去とプログラム機能を果たし、一方、前述の消去およびプログラム機能はチャネルの消去とプログラム機能を果たす。20

#### 【0019】

##### 【表1】

## 代表的な動作電位(ボルト)

表 1

|       | 読み出し   | 消去         | プログラム      | プログラム | 消去2        | プログラム2 |    |

|-------|--------|------------|------------|-------|------------|--------|----|

|       |        |            |            | 確認    |            |        |    |

| ワード線  | Vee    | -3.0~-9.0  | +5.0 ~+9.5 | +5.0  | -5.0 ~-9.0 | +5.0   | 10 |

| (選択)  | (+5)   | (-6.5)     | (+6.5)     |       | (-6.5)     |        |    |

| ワード線  | 0      | 0          | 0          | 0     | 0          | 0      |    |

| (非選択) |        |            |            |       |            |        |    |

| ピット線  | (+1.0) | F          | +3.0 ~+5.0 | +1.0  | F          | +1.0   |    |

| (選択)  |        |            | (+4.0)     |       |            |        |    |

| ピット線  | F      | F          | F          | F     | F          | F      | 20 |

| (非選択) |        |            |            |       |            |        |    |

| ソース   | 0      | F          | 0          | 0     | +3.0 ~+6.5 | -4.0   |    |

| N-ウェル | 0      | +3.0 ~+9.0 | 0          | 0     | +2.0 ~+6.0 | 0      |    |

|       |        | (-6.5)     |            |       |            |        |    |

| P-ウェル | 0      | +3.0 ~+9.0 | -2.0 ~-4.0 | 0     | +2.0 ~+6.0 | F      |    |

|       |        | (-6.5)     | (-4.0)     |       |            |        |    |

注：上記の表で、好ましい動作条件を括弧内に示してある。

【0020】

本発明の別の実施例では、フローティングゲート29とPウェル30との間の一定電界は、ゲートまたはPウェルのいずれか一方、または双方に傾斜して変化する電圧、もしくは段階的に変化する電圧を印加することによって消去中に保持される。例えばPウェル電圧は+3から+7ボルトまで傾斜して、もしくは段階的に変換することができ、および（または）ゲート上の電圧を-5ボルトから-9ボルトまで傾斜して変化することができる。このような技術は、低速消去ピット(slow-to-erase-bit)をより高速な消去ピットと同時に消去させることができるという利点を有している。これは消去時間の配分をより厳格なものとし、同時に漏れ電流の誘発の原因となる消去時の応力を軽減するのに役立つ。更にこれは、必要であった消去確認動作が不要になるという利点を有している。

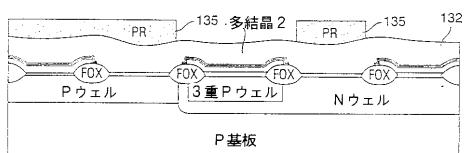

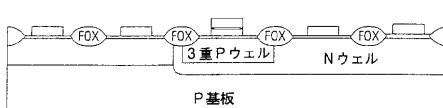

ここでは“消去2”と呼ばれる補足的な消去動作によって、バンド間のトンネリング電流を抑止するためにPウェル電圧によるソース・エッジ消去が可能になる。それによって更にウインドウの閉鎖が軽減される。このような消去動作によって消去中の電力消費が節減され、ソース・ゲート領域のエッジ部に発生するホット・ホールが縮減することによってデバイスの耐性が高まる。同様のプログラミング動作は“プログラム2”と呼ばれる。図3乃至31は本発明に基づくフラッシュ・メモリの製造工程の実施例を示している。本発明を充分に明確にするため、図示し、後述する工程は異なる種類の5個のトランジスタを形成するステップを含んでいる。図3、および同様にそれ以降の図面の上部には本発明

の工程によって形成される異なる種類のトランジスタが示されている。すなわち、本発明の工程によってPチャネル型とNチャネル型の双方の種類のフラッシュ・メモリ・セルを周辺CMOS回路とともに製造することができる。勿論、特定のフラッシュ・メモリ製品の実施に際しては、P型とN型の双方のトランジスタを備える必要はないが、完全を期すために図面には双方の種類を示してある。

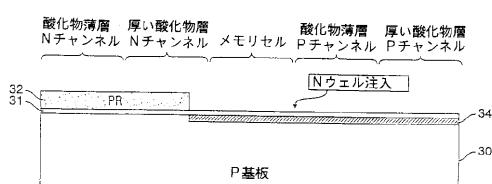

### 【0021】

図3の上部に示すように、図3乃至31のそれぞれの左部分では酸化物薄層のNチャネル・トランジスタを形成するのに必要な工程が説明される。この一つのトランジスタのようなNチャネル・トランジスタは+5ボルト程度の電圧で動作する。酸化物薄層のNチャネル製造工程のすぐ近傍では、厚い酸化物層のNチャネル・デバイスの製造工程が説明されている。厚い酸化物層のNチャネル・デバイスはより高い電圧の印加用に周辺回路で使用される。例えば、このようなデバイスは代表的には、およそ+9ボルトに及ぶ程度の電位が印加されるプログラミングおよび消去モードを処理するために使用される。

各図面の中央部では、フラッシュ・メモリ・セルを形成する工程が説明されている。前述のように、このフラッシュ・メモリ・セルは、NウェルがP基板内に形成され、全体がNウェル内にあるPウェル内でメモリ・セルが形成される3重ウェル構造で形成される。勿論、必要ならば、ただし図面の断面図には図示されていないが、Nチャネル・デバイスもPウェル内に形成することもできる。これらのNチャネル・デバイスはメモリ・セルとは異なりフローティングゲートを含まない。

### 【0022】

図面のメモリ・セルのすぐ近傍では酸化物薄層のPチャネル・トランジスタを形成する工程が説明されている。このようなデバイスは、例えば約+5ボルトまでのより低い電位を処理するための周辺回路で使用される。図面のその近傍には、厚い酸化物層のPチャネル・トランジスタを形成する工程が説明されている。これらのトランジスタは近傍に形成されたより薄い酸化物層のPチャネル・デバイスよりも高い電位で動作する。厚い酸化物層のNチャネル・デバイスの場合と同様に、厚い酸化物層のPチャネル・デバイスはフラッシュ・メモリ・セルのプログラミングと消去に必要なより高い電位を発生し、配分するための回路に使用される。

図3では、好ましくは抵抗率が8-10オーム・センチメートルで、水晶配向100のP導電型のシリコン基板が設けられている。従来の工程を利用して、シリコン酸化物の薄層31を得るために基板が酸化される。二酸化シリコン31の上表面上には、好ましくはフォトレジストのマスク32が形成される。公知の技術を利用して、Nウェル22(図2Aを参照)が必要な領域からマスクを除去するためにマスクは露出され、現像される。次に、再び公知の技術を利用して、Nウェルをドーピングするために例ええば燐であるN導電型の不純物がシリコン表面内に注入される。注入は $2.2 \text{ mev}$ のエネルギーと、 $6 \times 10^{12} \text{ cm}^{-2}$ の不純物濃度で行われることが好ましい。注入の終了時の構造の外見は図3に示すとおりである。図3には、周辺回路トランジスタとメモリ・セル(フラッシュ)とが形成される基本位置を表記した標識が付されている。ほとんどの集積回路では、表面の大部分がメモリ・セルからなっている。

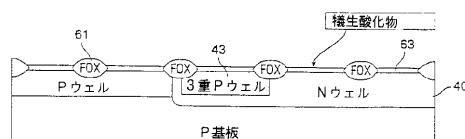

### 【0023】

次に、図4に示すように、フォトレジスト32が除去され、Nウェル・ドープ剤を駆使して、Nウェル40を生成するためにアニーリング工程が実施される。新たなフォトレジスト層41が集積回路の上表面に被覆され、次にPウェルが必要な領域を露出するためにマスキングと現像が行われる。次に、例えば濃度が $1.5 \times 10^{13} \text{ cm}^{-2}$ で、エネルギーが100keVでボロンまたはその他のP導電型の不純物を用いてPウェル注入が行われる。Nウェルはチップのメモリ・セル領域を含んでいる。これは個数が所望のとおりの少なさまたは多さのメモリ・セルを含むことができ、別のメモリ・セル群は別のNウェル内に形成される。Nウェルを使用することによって小ブロック、例えば単一の語線の消去が可能であり、消去ブロックのブロック・サイズを任意に選択できる。これは3重ウェル工程に必要な電位が従来形のソース側消去と比較して低いことの結果である。従来形のデバイス

10

20

30

40

50

では消去ブロックのサイズは電流の制限によって規定されていた。使用される高電力を処理するために大型のデコーディング・トランジスタが必要であり、それによってチップ面積が過剰なものになっていた。本発明では、Nウェルを用いることで大型のデコーディング・トランジスタを使用する必要がなくなり、任意のセル群を同時に消去することが可能になる。更に、前述のように、チャネル消去を利用することによって消去をより均一にすることができる。図4はP型不純物の注入後の構造の外見を示している。

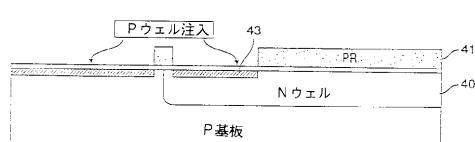

#### 【0024】

フォトレジスト41は除去され、図5に示すように、Pウェル・ドープ剤が熱アニーリング工程の際に駆使される。上表面上の全ての二酸化シリコンは、例えば酸浸漬、またはプラズマ・エッティング工程を利用して剥離される。次に、例えば熱処理を利用して200オングストロームの二酸化シリコンを生成するため、集積回路の上表面に新たな二酸化シリコン層51が形成される。二酸化シリコン51の上正面上には、例えば化学蒸着のような公知の技術を用いて、好ましくは厚さ約400オングストロームの多結晶シリコン層53が形成される。多結晶シリコン層53の機能は応力除去層として役立つことである。多結晶シリコン層53の上面にはこの場合も化学蒸着を利用して、代表的には約2000オングストロームの厚さに窒化シリコン層54が蒸着される。窒化シリコン54の上面には、別のフォトレジスト層55が蒸着される。その後、層55はこの場合も公知の技術を利用して露出され、現像される。次にフォトレジスト55のアイランドの間に露出した窒化シリコン領域54を除去するためにプラズマ、もしくは反応性イオン・エッティングが施される。このようなエッティングはこの分野では公知である。工程のこの段階での構造の外見は図5に示されている。10

#### 【0025】

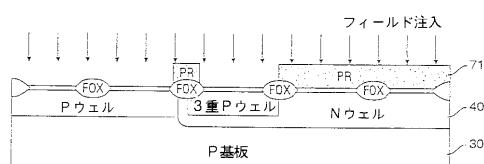

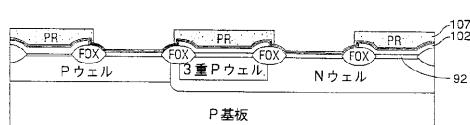

工程の次の段階を図6を参照しつつ説明する。図示のとおり、フォトレジストは構造の上表面から除去され、図ではFOXと記されている電界酸化領域61を生成するために、代表的には高温での酸化が行われる。電界酸化領域61は集積回路の種々の部分を互いに電気的に絶縁する機能を果たす。好適な実施例では、電界酸化物の厚さは0.5ミクロンであり、基板を1150の温度に300分間加熱することによって形成される。領域61のような電界酸化領域はこの分野では公知である。20

電界酸化領域の形成の後、例えば熱したH<sub>2</sub>PO<sub>4</sub>溶液(磷酸)への浸漬によって窒化物層が構造の表面から剥離される。次に、下層の多結晶シリコン、並びに多結晶シリコンの下の二酸化シリコン層51が除去される。次に、好ましくはシリコンを加熱することによって構造の上表面に新たな二酸化シリコン層63が形成される。酸化物層63は後に除去されるので犠牲酸化物と呼ばれる。犠牲酸化物63を除去した後の構造の外見が図6に示されている。30

#### 【0026】

次に構造の上表面にフォトレジスト層71が形成され、その後、電界注入が必要な領域を露出するためにマスキングと現像が行われる。電界注入はP型領域内に導入される。このNチャネル電界注入は、後に能動Nチャネル・デバイスが形成される領域での深注入である。これは図7に示されている。Nチャネル注入は165keVのエネルギーと、濃度が5E12cm<sup>-2</sup>のボロン不純物を使用して導入されることが好ましい。40

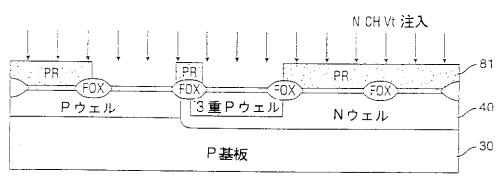

図8は工程の次の段階を示している。図示のように、この場合も公知のフォトリトグラフ技術を利用して修正回路の表面の所望の領域に新たなフォトレジスト・マスキング層81が形成される。フォトレジストは、少なくとも後にメモリ・セルが形成される領域から除去され、次にこれらの領域内でしきい電圧調整用の注入が行われる。

#### 【0027】

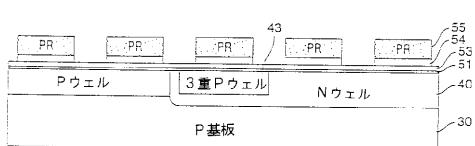

図9に示すように、新たなマスク83が形成され、これらの周辺トランジスタを調整するためにPチャネルしきい電圧注入が行われる。次にフォトレジストが除去され、集積回路の露出部分の表面から犠牲酸化物を除去するためにエッティング動作が施される。

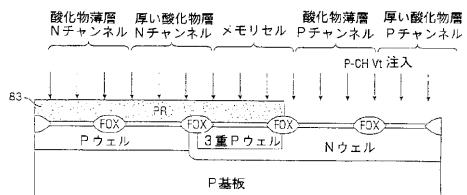

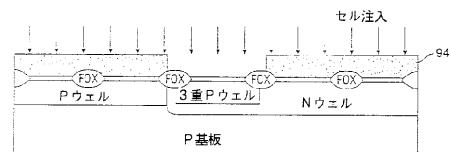

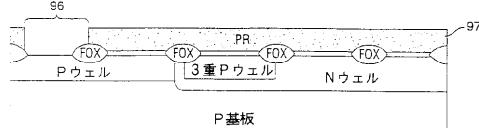

図10に示すように、構造上に新たな二酸化シリコン層92が形成される。この新たな層によって周辺回路内の厚い酸化物層のPおよびnチャネル・トランジスタ用の厚い酸化物50

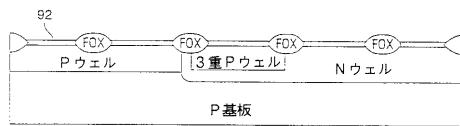

ゲートが備えられる。図11に示すように、メモリ・セルへのしきい電圧注入が行われる領域96を露出するために新たなフォトレジスト・マスク94が施される。セル注入、すなわちボロンであることが好ましいP型不純物が $3 \times 10^3 \text{ cm}^{-2}$ の投与量と、40keVのエネルギーで導入される。セル注入の後、厚いゲート酸化物層92を除去するために同じマスク94が使用される。次に、露出された二酸化シリコンがエッティング処理され(図12を参照)、この場合も公知の技術を用いて新たなゲート酸化物層98が形成される。この新たな層98によって、メモリ・セルのプログラミングと消去の間に電子がそこを通ってトンネリングするトンネル酸化物層が得られる。トンネリング酸化物層98は厚さが85オングストロームであることが好ましく、構造を850の温度に45分間だけ蒸気中で加熱し、N<sub>2</sub>内で30分間900でアニーリングすることによって形成される。

10

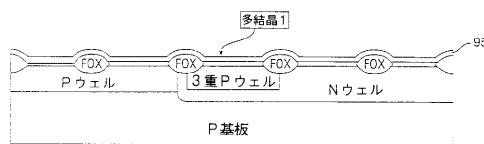

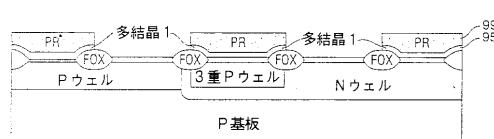

### 【0028】

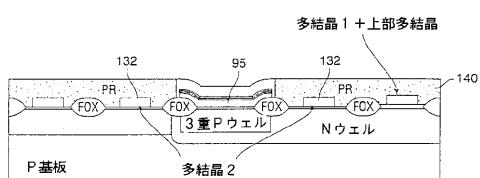

酸化物層98の形成後、多結晶シリコン層95が、例えば化学蒸着によって構造の上表面上に蒸着されて、厚さ約1000オングストロームの層が形成される。次にこの層には燐不純物がドーピングされて、導電性にされる。多結晶シリコン層95によってメモリ・セル用のフローティングゲートと、周辺回路内のトランジスタ用の制御セルとが備えられる。図14に示すように、構造上に残されることになる多結晶シリコン95の所望の領域をマスキングするために、好ましくはフォトレジストである別のマスク99が形成される。それによって露出された多結晶シリコン95が、例えば公知のプラズマ・エッティング、または異方性エッティング工程を用いて構造の表面からエッティングされる。エッティングの完了後の構造の外見は図14に示されている。

20

### 【0029】

図15は製造工程の次の段階を示している。フォトレジスト層99が剥離され、次に二酸化シリコン、窒化シリコン、および二酸化シリコンの蒸着が順次行われて、“ONOサンディッチ”状の複合絶縁層102が形成される。この層は、多結晶シリコン層95が形成された領域では多結晶シリコン95の上表面上にあり、回路の別の領域では厚いゲート酸化物層92の上表面上にある。ONO層は化学蒸着を用いて蒸着することが好ましい。しかし、別の公知の技術を用いてもよい。ONO層は厚さ50オングストロームの下部の二酸化シリコン層、厚さ60オングストロームの中間の窒化シリコン層、および厚さ50オングストロームの上部の二酸化シリコン層から構成されることが好ましい。ONO層の形成後、新たなマスキング層107が蒸着され、多結晶シリコン層95が残される領域を保護するように形成される。

30

### 【0030】

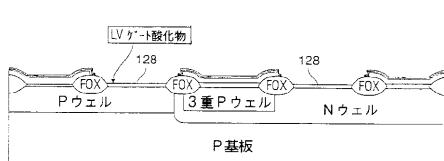

マスク107の形成後、図16に示すように、従来のエッティング手順を用いてONOサイドィッチ構造の露出領域が除去される。この段階では、ONO複合層が除去され、かつ露出領域内の厚いゲート酸化物層92も除去される。次にフォトレジストが剥離される。新たなゲート酸化物層128が形成される。この新たなゲート酸化物層はより薄く(約110オングストローム)、電力がより低いPおよびNチャネル・トランジスタを形成するべき位置に形成される。

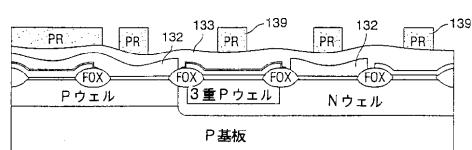

次に、図17に示すように、多結晶シリコンの第2層132が構造の表面に蒸着される。多結晶シリコン132の厚さは1000オングストロームであることが好ましく、従来の化学蒸着工程の技術を用いて蒸着される。多結晶シリコン132の蒸着に引き続き、この層にはPOCl<sub>3</sub>工程を用いて燐不純物がドーピングされる。この“多結晶2”層によって回路内の相互接続が形成される。第2多結晶シリコン層は回路の周辺領域内の第1多結晶シリコン層への相互接続用に利用できる。これによって更にコンデンサが備えられ、またはメモリ・セル領域内の別の接続用に利用できる。次に第2多結晶層を選択的に防護するためマスク135が形成される。図18に示すように、次に多結晶シリコン132は構造上の不要な位置からこれを除去するためにエッティング処理される。次に珪化タンゲステン層133が多結晶シリコン132の上表面上に蒸着される。珪化タンゲステンの上正面上には、反射防止コーティング(図示せず)が蒸着され、珪化タンゲステンの上表面からの反

40

50

射を最小限に抑止することによってマスキング公差をより精密にすることが可能になる。最後に、第2多結晶シリコン層が残されるべき構造の領域を更に規定するために、構造の上表面にマスク139が形成される。図面中の断面図では、ゲート電極が必要な領域がある。マスク139を利用して、第2多結晶シリコン層132がエッティング処理される。次に、構造の一部を保護し、多結晶第1層95(図19を参照)内に制御およびフローティングゲートを形成するために新たなマスク140(図19を参照)が形成される。

#### 【0031】

図20に示すように、次にこれも従来の処理技術を利用して第2多結晶シリコン層132がエッティングされる。第2多結晶シリコン層132のエッティング後、第2多結晶シリコン層132はONOサンドイッチ層の露出領域を除去できるようにするマスクとして利用される。次にONOサンドイッチは多結晶シリコン層95の第1レベルをエッティングするためのマスクとして機能する。このようにして、メモリ・セル・ゲートが形成される。エッティング後、それによって露出したシリコン領域上に再び防護用の酸化物層を形成するため、構造は再加熱される。メモリ・セル・トランジスタはフローティングゲートと制御ゲートを含み、一方、周辺回路で使用するように意図された別のトランジスタはこれらのゲートを含んでいないことに留意されたい。

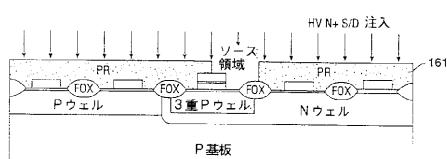

#### 【0032】

図21は製造工程の次の段階を示している。メモリ・セル・トランジスタのソース領域以外の領域を保護するため、構造の表面にマスク161が形成される。次に二重注入が行われ、N形不純物の第1次注入は比較的少ない $3 \times 10^{-14} \text{ cm}^{-2}$ の投与量と、50keVのエネルギーで行われる。第1次注入後に、濃度がより高い第2次注入が行われる。これらの注入によってメモリ・セルの二重拡散ソース領域濃度が規定される。

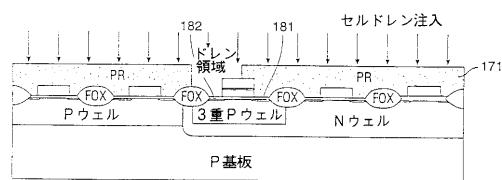

図22に示すように、全てのフォトレジストが除去され、メモリ・セルのドレン領域だけを露出させる新たなマスク171が形成される。別の注入が行われ、この場合は $3.5 \times 10^{-15} \text{ cm}^{-2}$ の濃度量と、50keVのエネルギーでヒ素不純物が注入される。図22はその結果生じた注入済のドレン領域を示している。

#### 【0033】

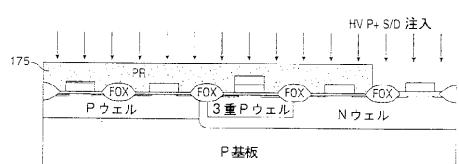

図23は別のトランジスタ用のソースおよびドレン領域を形成するためのマスク175を介した同様の注入を示している。フォトレジストが除去され、次にソース・ドレン注入をアニーリングするため $900^{\circ}\text{C}$ の温度で25分間だけ加熱される。その結果、ソースおよびドレン領域181と182が形成される。このアニーリング動作によって更に多結晶シリコン上に二酸化シリコン層184が形成される。次にプラチナケット・エッティングを利用してこの層のほとんどが除去される。全ての酸化物が除去される前にエッティングを停止することによって、多結晶シリコン・ゲートの側壁にスペーサ領域184が残される。それによって軽くドーピングされたドレン構造の形成が可能である。次により高度にドーピングされたソース/ドレンが必要な位置で周辺トランジスタを露出させるために新たなマスク175が形成される。次に、図23に示すように $3.5 \times 10^{-15} \text{ cm}^{-2}$ の注入が行われる。

#### 【0034】

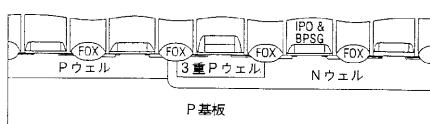

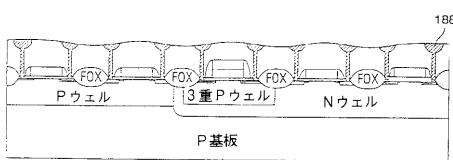

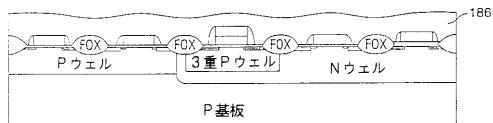

図26に示すように、アニーリングの後、構造の上表面に二酸化シリコン層が蒸着され、その後でBPSG層(リン化ホウケイ酸塩ガラス)が蒸着される。次に構造はBPSG186層をほぼ平坦化するために加熱される。

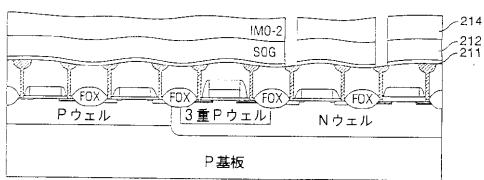

BPSGの上表面にマスク(図示せず)が形成され、BPSGは図27に示すようにエッティング処理されて構造の表面並びに別の領域への接触位置が形成される。次に図28で例えばチタン/窒化チタンのような障壁用金属がBPSG層186の開口部内に蒸着され、その後で所望の第1金属化層が蒸着される。第1金属層はアルミニウムであることが好ましい。アルミニウムの表面上には、反射防止コーティングを施すために窒化チタン層が蒸着される。次に第1金属層がマスキングおよびエッティングされ、フォトレジストが剥離される。残された帰属接点188が図28に示されている。BPSG186と金属接点188の上表面に、化学蒸着法を利用して例えば二酸化シリコン材料の金属間酸化物が蒸着

10

20

20

30

40

50

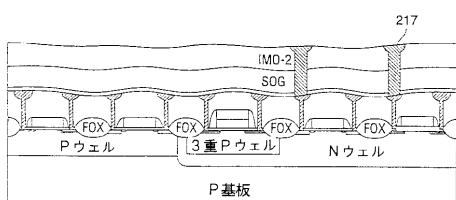

される。第29図にはIMO層211が示されている。IMO層の頂部には、スピニ・オン・ガラス212が蒸着され、その上表面上には別の金属間酸化物214が蒸着される。層211の厚さは約1000オングストロームであり、一方層214の厚さは約2000オクロンであることが好ましい。次にマスク(図示せず)が第2金属間酸化物の上表面に形成される。このマスクは層212および214のエッティングのための開口部を形成するために露出され、現像される。次にこれらの層は、第1金属層への経路217用の開口部を形成するため、好ましくはプラズマを利用してエッティングされる。フォトレジストが除去され、構造の外見は図21に示されている。

#### 【0035】

図30に示すように、経路用開口部217を充填し、第2金属層を備えるために例えばアルミニウムである別の金属層がチップの上表面に蒸着される。その上表面上に反射防止用の窒化チタン・コーティングが蒸着され、次に第2金属層がマスキングおよびエッティングされ、かつフォトレジストが剥離されて、第30図に示した構造が製造される。

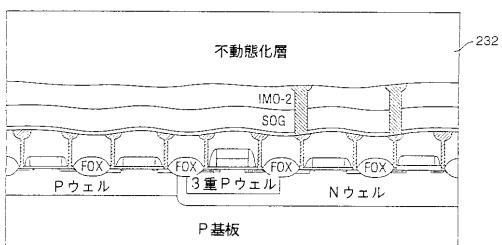

図31は第2金属層221の上表面上に不動態化層232を付加した後の完成した構造を示している。不動態化層はマスキング、およびエッティングされ、フォトレジストが剥離され、次にウェーハ内に完成した集積回路を製造するために構造は窒素内でアニーリングされる。

この段階に続いて、公知の半導体製造工程を利用して、製造された製品はテストされ、パッケージ内に収納され、パッケージと相互接続され、かつカプセルに封入される。

#### 【0036】

これまで本発明のフラッシュ・メモリ・セルおよびその製造工程を説明してきた。多くの特定の時間、温度およびその他の工程上の細部を提示してきたが、当業者には本発明の範囲を離れることなく、多くの変化形が可能であることが理解されよう。本発明の範囲は特許請求の範囲によって規定されるものである。

#### 【0037】

##### 【発明の効果】

以上説明してきたように、ウェルを3重構造にすることによって、動作用の電位を著しく低下させることができ、かつメモリ・セルを均一に消去できる。

##### 【図面の簡単な説明】

【図1】図1A及び1Bは、従来形のフラッシュ・メモリ・セルを示す。

【図2】図2A及び2Bは、本発明のフラッシュ・メモリ・セルの好適な実施例を示す。

【図3】図3乃至31は、本発明のフラッシュ・メモリ・セルの製造方法の好適な実施例を示し、本図は、nウェルの注入後の構造を示す。

【図4】Pウェルの注入後の構造を示す。

【図5】PおよびNウェルのアニーリングとマスクの形成後の構造を示す。

【図6】フィールド酸化物領域の形成後の構造を示す。

【図7】Nチャネルフィルドの注入後の構造を示す。

【図8】Pチャネルしきい電圧注入後の構造を示す。

【図9】Nチャネルしきい電圧注入後の構造を示す。

【図10】ゲート酸化物の形成後の構造を示す。

【図11】セル注入後の構造を示す。

【図12】選択された領域内でゲート酸化物層を除去した後の構造を示す。

【図13】多結晶シリコンの第1層の形成後の構造を示す。

【図14】多結晶シリコンの第1層のマスキングとエッティング後の構造を示す。

【図15】ONO絶縁層の形成後の構造を示す。

【図16】選択された位置に新たなゲート酸化物を形成した後の構造を示す。

【図17】多結晶シリコンの第2層の形成後の構造を示す。

【図18】マスクの形成後の構造を示す。

【図19】多結晶シリコンの第2層のエッティングおよび新たなマスクの形成後の構造を示す。

10

20

30

40

50

- 【図 2 0】更なるエッティングの完了後の構造を示す。

【図 2 1】メモリ・セルのソース領域注入後の構造を示す。

【図 2 2】メモリ・セルのドレン領域注入後の構造を示す。

【図 2 3】幾つかの周辺トランジスタのP型ドレン注入後の構造を示す。

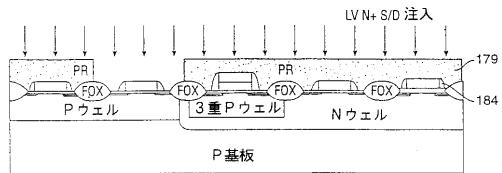

【図 2 4】別の周辺トランジスタのN型ドレン注入後の構造を示す。

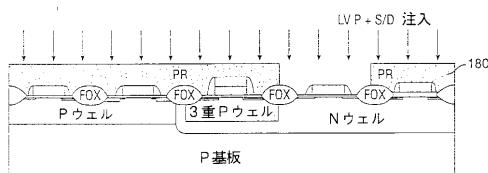

【図 2 5】更に別の周辺トランジスタのP型ソース・ドレン注入後の構造を示す。

【図 2 6】B P S G のアニーリングと蒸着後の構造を示す。

【図 2 7】接点マスクの形成後の構造を示す。

【図 2 8】第1金属層の蒸着後の構造を示す。

【図 2 9】第2接点層の形成後の構造を示す。

【図 3 0】第2金属層の蒸着後の構造を示す。

【図 3 1】不動態化層の蒸着後の構造を示す。

## 【符号の説明】

|     |            |

|-----|------------|

| 1 0 | 基板         |

| 1 2 | 制御ゲート      |

| 1 3 | 絶縁薄層       |

| 1 5 | フローティングゲート |

| 1 6 | ドレン領域      |

| 1 8 | ソース領域      |

| 2 0 | 基板         |

| 2 2 | N ウエル      |

| 2 4 | P ウエル      |

| 2 6 | ドレン        |

| 2 7 | ソース        |

| 2 8 | P 接点       |

| 2 9 | フローティングゲート |

10

20

【図1】

A

【図2】

A

B

B

【図3】

【図6】

【図4】

【図7】

【図8】

【図5】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 18】

【図 16】

【図 19】

【図 17】

【図 20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図27】

【図28】

【図29】

【図26】

【図30】

【図31】

---

フロントページの続き

(31) 優先権主張番号 08/863919

(32) 優先日 平成9年5月27日(1997.5.27)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 08/863920

(32) 優先日 平成9年5月27日(1997.5.27)

(33) 優先権主張国 米国(US)

(74) 代理人 100074228

弁理士 今城 俊夫

(74) 代理人 100084009

弁理士 小川 信夫

(74) 代理人 100082821

弁理士 村社 厚夫

(72) 発明者 アーサー ワン シングヤ

アメリカ合衆国 カリフォルニア州 95070 サラトガ ダグマー ドライヴ 19071

(72) 発明者 イエイン チェン ヨウン

アメリカ合衆国 カリフォルニア州 95035 ミルピタス メドーランド ドライヴ 193

(72) 発明者 クワン ミン サン

アメリカ合衆国 カリフォルニア州 94577 サン リンドロー マグノリア コート 9

45

(72) 発明者 イーコン チョイ

大韓民国 ソウル ソングパ-ク バンギ-ドン (番地なし) アパートメント 5-605

## 合議体

審判長 松本 邦夫

審判官 恩田 春香

審判官 橋本 武

(56) 参考文献 特開平8-63985(JP,A)

特開平5-259413(JP,A)