(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5801030号

(P5801030)

(45) 発行日 平成27年10月28日(2015.10.28)

(24) 登録日 平成27年9月4日(2015.9.4)

(51) Int.Cl.

F 1

**H01L 21/336 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

**H01L 21/8247 (2006.01)**

**H01L 27/115 (2006.01)**

H01L 29/78 371

H01L 27/10 434

請求項の数 3 (全 13 頁)

(21) 出願番号 特願2009-516566 (P2009-516566)

(86) (22) 出願日 平成19年6月20日 (2007.6.20)

(65) 公表番号 特表2009-541999 (P2009-541999A)

(43) 公表日 平成21年11月26日 (2009.11.26)

(86) 國際出願番号 PCT/US2007/014431

(87) 國際公開番号 WO2007/149515

(87) 國際公開日 平成19年12月27日 (2007.12.27)

審査請求日 平成22年3月3日 (2010.3.3)

審判番号 不服2014-12969 (P2014-12969/J1)

審判請求日 平成26年7月4日 (2014.7.4)

(31) 優先権主張番号 11/471,772

(32) 優先日 平成18年6月21日 (2006.6.21)

(33) 優先権主張国 米国(US)

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ボイズ, サウス フェデ

ラル ウエイ 8000

(74) 代理人 100106851

弁理士 野村 泰久

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 有留 誠一

アメリカ合衆国, アイダホ州 83706

, ボイズ, サウス スワロー・テイル レー

ン 2222

最終頁に続く

(54) 【発明の名称】浮遊ゲートメモリデバイスと製造

## (57) 【特許請求の範囲】

## 【請求項1】

基板の上にゲート酸化物層を配置するステップと、

前記ゲート酸化物層の上に浮遊ゲート層を配置するステップと、

前記浮遊ゲート層の上にゲート間誘電層を配置するステップと、

複数の分離されているゲート間誘電領域を形成するために、前記ゲート間誘電層、前記

浮遊ゲート層、前記ゲート酸化物層、および前記基板の各々を通して、複数の実質的に平

行なトレンチを同じ処理段階でエッチングするステップと、

前記複数のトレンチの各々を絶縁酸化物で充填するステップと、

前記絶縁酸化物と前記複数の分離されているゲート間誘電領域とを平坦化するステップ

と、

平坦化された前記ゲート間誘電領域の各々の上に制御ゲートを堆積するステップと、

を含む、浮遊ゲートメモリアレイを製造する方法。

## 【請求項2】

エッチングするステップが、前記ゲート間誘電層と、前記浮遊ゲート層の各々を单一の

処理段階でエッチングするステップを含む、請求項1に記載の方法。

## 【請求項3】

前記絶縁酸化物と前記複数の分離されているゲート間誘電領域とを平坦化する前記ステ

ップは、前記浮遊ゲート層の絶縁領域によって分離される絶縁酸化物領域を作るために、

前記複数のトレンチの各々を絶縁酸化物で充填するステップの後、前記絶縁酸化物と前記

複数の分離されているゲート間誘電領域とを平坦化するステップを含む、請求項\_1に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、概してメモリデバイスに関し、より具体的には、隣接する浮遊ゲート間の干渉が少ない浮遊ゲートメモリデバイスに関する。

【背景技術】

【0002】

この節は、下記に記載および／または請求される本発明の様々な態様に関連し得る技術の様々な態様を読者に紹介することを意図する。この考察は、本発明の様々な態様の理解を深めるために、読者に予備知識を提供する上で役立つと考えられる。従って、これらの記述はこの観点から読まれるものであり、先行技術を認めるものではないということが理解されるべきである。

【0003】

コンピュータなどのプロセッサベースのシステムは、典型的に、システムに保存能力を与えるために一つ以上のメモリデバイスを含む。システムメモリは、一般に、一つ以上の集積回路チップもしくはデバイスの形で提供され、一般に、ランダムアクセスメモリ (RAM) とリードオンリーメモリ (ROM) の両方を含む。システムRAMは、通常は大きく揮発性で、システムのメインメモリを提供する。スタッフィックRAMとダイナミックRAMは、一般に利用される種類のランダムアクセスメモリである。対照的に、システムROMは一般に小さく、初期設定ルーチンと識別情報を保存するための不揮発性メモリを含む。電気的消去可能なリードオンリーメモリ (EEPROM) は、一般に利用される種類のリードオンリーメモリであり、メモリでデータをプログラムおよび／または消去するために電荷が使用され得る。

【0004】

特定用途の不揮発性メモリの一つの種類はフラッシュメモリである。フラッシュメモリは、ブロック単位で消去と再プログラムが可能なEEPROMの種類である。フラッシュメモリは、基本入出力システム (BIOS) プログラムを容易にアップデートできるように保存するために、パーソナルコンピュータシステムでしばしば利用される。フラッシュメモリは、製造業者が、新たな通信プロトコルが標準化される際にそれをサポートし、デバイスに拡張機能を遠隔でアップグレードする能力を与えることを可能にするので、無線電子機器でも利用される。

【0005】

典型的なフラッシュメモリは、行と列に配列された多数のメモリセルを持つメモリアレイを含む。メモリセルは一般にブロックにグループ化され、セルのグループを同時にプログラムしたり消去したりできるようになっている。メモリセルの各々は、電荷を保持することができる浮遊ゲート電界効果トランジスタを含む。浮遊ゲートメモリセルは、標準制御ゲートに加えて、“浮遊ゲート”と呼ばれる電気的に絶縁されたゲートを含む点で、標準MOSFET設計とは異なる。浮遊ゲートは、通常はチャネルの上に形成され、ゲート酸化物によってチャネルから分離される。制御ゲートは浮遊ゲートの真上に形成され、別の薄い酸化物層によって浮遊ゲートから分離される。浮遊ゲートメモリセルは、浮遊ゲート内に電荷を保持することによって情報を記憶する。浮遊ゲートから電荷を加えたり除去したりすることによって、セルの閾値電圧が変化し、それによって、このメモリセルがプログラムされたか消去されたかどうかを決定する。

【0006】

NANDフラッシュメモリデバイスは、中に基本メモリセル構成が配列される、いわゆる論理形式用の一般的な種類のフラッシュメモリデバイスである。典型的には、NANDフラッシュメモリデバイスのメモリセルのアレイは、アレイの行の各メモリセルの制御ゲートがワード選択線に接続されるように配列される。アレイの列は、選択線のペア（ソース選択線とドレイン選択線）の間で、ソースからドレインへ直列につながれたメモリセルのストリ

10

20

30

40

50

ング（しばしばNANDストリングと呼ばれる）を含む。ソース選択線は、NANDストリングとソース選択線との間の各交点においてソース選択ゲートを含み、ドレイン選択線は、NANDストリングとドレイン選択線との間の各交点においてドレイン選択ゲートを含む。選択ゲートは通常は電界効果トランジスタである。各ソース選択ゲートはソース線に接続され、一方各ドレイン選択ゲートは列ビット線に接続される。

#### 【0007】

メモリアレイは、メモリセルの制御ゲートに接続されたワード選択線を選択することにより、メモリセルの行を活性化する行デコーダによってアクセスされる。加えて、各ストリングの選択されないメモリセルの制御ゲートに接続されたワード選択線は、その蓄積されたデータ値によって制限されないやり方で電流を通すように、各ストリングの選択されないメモリセルをバストランジスタとして操作するように駆動される。その後電流は、各ストリングの選択されたメモリセルのみによって制限されて、対応する選択ゲートを介して、各NANDストリングを通してソース線から列ビット線へと流れる。こうして、選択されたメモリセルの行の、電流でコード化されたデータ値が、列ビット線に置かれる。

10

#### 【0008】

今日の減少し続けるデバイス形状では、メモリデバイスの超高密度化は、多くの構成要素間の相互作用を引き起こす可能性があり、これは好ましくない。例えば、隣接するメモリセル間の干渉は、メモリセルのサイズが減少するにつれてますます懸念を高める。特に浮遊ゲートメモリセルでは、隣接する浮遊ゲート間の干渉は一般に好ましくない。

20

#### 【発明の概要】

#### 【0009】

本発明の実施形態は、上述の問題の一つ以上に向けられ得る。

#### 【図面の簡単な説明】

#### 【0010】

本発明の効果は、以下の詳細な説明を読み、図面を参照することで明らかとなり得る。

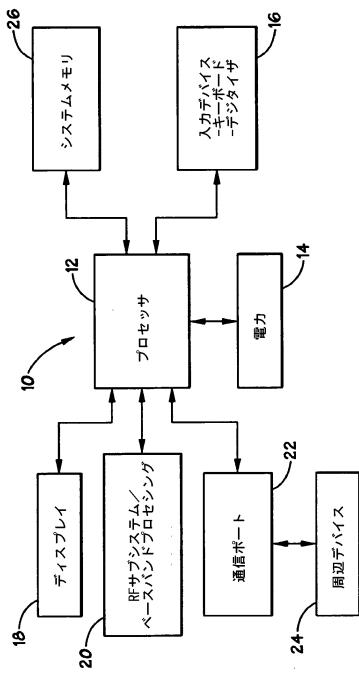

【図1】本発明の実施形態に従って製造されるメモリデバイスを含むメモリを持つ、例示的なプロセッサベースのデバイスのブロック図を図示する。

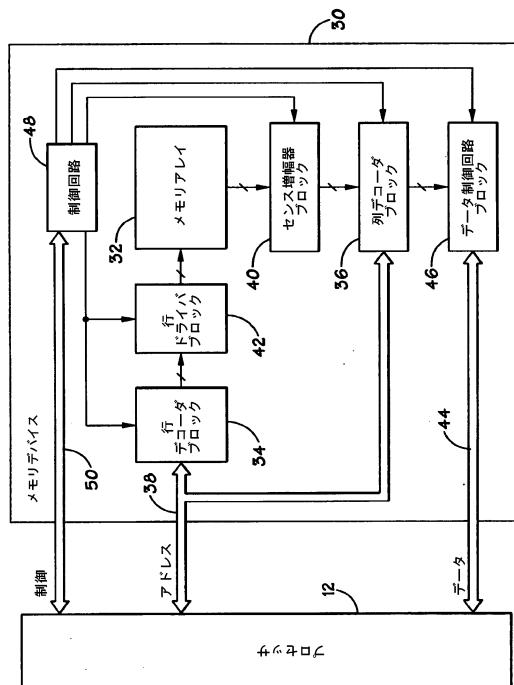

【図2】本発明の実施形態に従って製造されるメモリアレイを持つ例示的なメモリデバイスのブロック図を図示する。

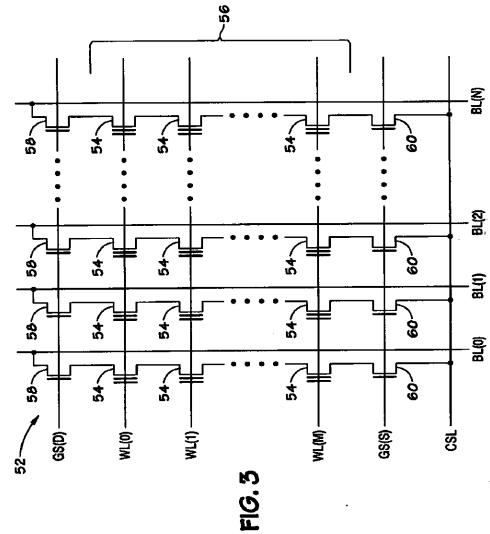

【図3】本発明の実施形態に従って製造されるメモリセルを持つ例示的なNANDフラッシュメモリアレイの概略図である。

30

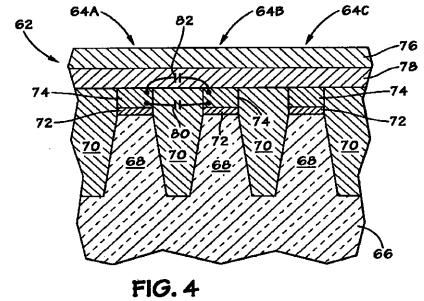

【図4】従来の浮遊ゲートメモリデバイスの断面図を図示する。

【図5】従来の浮遊ゲートメモリデバイスの断面図を図示する。

【図6】本発明の実施形態に従う、浮遊ゲートメモリデバイスを製造するための例示的な技法を図示するフローチャートである。

【図7】本発明の実施形態に従う、図6のフローチャートに対応する浮遊ゲートメモリセルの製造を図示する断面図である。

【図8】本発明の実施形態に従う、図6のフローチャートに対応する浮遊ゲートメモリセルの製造を図示する断面図である。

【図9】本発明の実施形態に従う、図6のフローチャートに対応する浮遊ゲートメモリセルの製造を図示する断面図である。

40

【図10】本発明の実施形態に従う、図6のフローチャートに対応する浮遊ゲートメモリセルの製造を図示する断面図である。

【図11】本発明の実施形態に従う、図6のフローチャートに対応する浮遊ゲートメモリセルの製造を図示する断面図である。

【図12】本発明のさらなる実施形態に従う、浮遊ゲートメモリセルを製造する代わりの方法を図示するフローチャートである。

#### 【発明を実施するための形態】

#### 【0011】

本発明の一つ以上の特定の実施形態が下記に記載される。これらの実施形態の簡潔な記

50

載を提供するために、実際の実装の全ての特徴が明細書に記載されるわけではない。当然のことながら、任意のそのような実際の実装の開発にあたっては、任意のエンジニアリングもしくは設計計画におけるように、実装毎に異なり得る、システム関連およびビジネス関連の制約の順守など、開発者の特定の目標を達成するために、数多くの実装特有の決定がなされなければならない。さらに、当然のことながら、そのような開発努力は複雑で時間のかかるものとなり得るが、それでもやはり、本開示の利益を有する当業者にとっては、設計、組立、および製造の日常業務となる。

#### 【0012】

次に図面を参照し、最初に図1を参照すると、概して参考数字10であらわされた例示的なプロセッサベースのシステムを示すブロック図が図示される。システム10は、コンピュータ、ポケベル、携帯電話、電子手帳、制御回路などの、様々な種類のいずれであってもよい。典型的なプロセッサベースのデバイスでは、マイクロプロセッサなどのプロセッサ12が、システム10においてシステムの機能と要求の処理を制御する。さらに、プロセッサ12はシステム制御を分担する複数のプロセッサを含んでもよい。

10

#### 【0013】

システム10は典型的には電源14を含む。例えば、システム10が携帯用システムである場合、電源14は、永久電池、交換式電池、および／または充電式電池を有利に含んでもよい。また、電源14は、例えばシステム10を壁コンセントに差しめるように、ACアダプタを含んでもよい。また、電源14は、例えばシステム10を車両のシガレットライターに差しめるように、DCアダプタを含んでもよい。

20

#### 【0014】

システム10が行う機能に応じて、様々な他のデバイスがプロセッサ12に結合されてもよい。例えば、ユーザーインターフェース16がプロセッサ12に結合されてもよい。ユーザーインターフェース16は、例えばボタン、スイッチ、キーボード、ライトペン、マウス、および／または音声認識システムを含んでもよい。また、ディスプレイ18がプロセッサ12に結合されてもよい。ディスプレイ18は、例えばLCDディスプレイ、CRT、LED、および／またはオーディオディスプレイを含んでもよい。

#### 【0015】

さらに、RFサブシステム／ベースバンドプロセッサ20がプロセッサ12に結合されてもよい。RFサブシステム／ベースバンドプロセッサ20は、RF受信機とRF送信機（図示せず）に結合されるアンテナを含んでもよい。また、通信ポート22がプロセッサ12に結合されてもよい。通信ポート22は、例えば、モデム、プリンタ、コンピュータなどの一つ以上の周辺デバイス24や、または、ローカルエリアネットワーク、リモートエリアネットワーク、インターネット、もしくはインターネットなどのネットワークに結合されるように構成されてもよい。

30

#### 【0016】

プロセッサ12は、ソフトウェアプログラムを実行することによってシステム10の機能を制御するので、プロセッサ12を有効にするためにメモリが使用される。一般にメモリは、様々なプログラムの実行を保存し、容易にするためにプロセッサ12に結合される。例えば、プロセッサ12はシステムメモリ26に結合されてもよく、システムメモリ26は、ダイナミックランダムアクセスメモリ（DRAM）および／または静态ランダムアクセスメモリ（SRAM）などの揮発性メモリを含んでもよい。また、システムメモリ26は、揮発性メモリと併用される、リードオンリーメモリ（ROM）、EEPROM、および／またはフラッシュメモリなどの不揮発性メモリ28も含んでもよい。以下にさらに説明されるように、システムメモリ26は、本発明の実施形態に従って製造される浮遊ゲートメモリアレイを含み得る、フラッシュメモリデバイスなどの一つ以上のメモリデバイスを含んでもよい。

40

#### 【0017】

図2は、図1のシステムメモリ26の一部として含まれ得るフラッシュメモリデバイス30を図示するブロック図である。図3に関して以下にさらに説明されるように、フラッシュメモリデバイス30はNANDフラッシュメモリデバイスであってもよい。フラッシュメモリデ

50

バイス30は、一般にメモリアレイ32を含む。メモリアレイ32は、一般に、多数のメモリセルを形成するために、グリッドパターンに配列された多くの導電トレースの行と列を含む。メモリアレイ32を構成する行もしくは“行の線”は、一般的に“ワード線”と呼ばれる。列もしくは“列の線”は、一般的に“ピット線”もしくは“ディジット線”と呼ばれる。メモリアレイ32のサイズ(すなわちメモリセルの数)は、フラッシュメモリデバイス30のサイズに応じて異なる。

#### 【0018】

メモリアレイ32にアクセスするために、行デコーダブロック34および列デコーダブロック36が提供され、メモリアレイ32内の特定のメモリセルにアクセスするために、アドレスバス38を介してプロセッサ12からのアドレス情報を受信し変換するように構成される。また、メモリセルに蓄積される個々の値を感知し増幅するために、複数のセンス増幅器を持つセンス増幅器ブロック40が列デコーダ36とメモリアレイ32の間に提供される。さらに、与えられた行アドレスに従ってメモリアレイ内の選択されたワード線を活性化するために、行ドライバブロック42が行デコーダブロック34とメモリアレイ32の間に提供される。

10

#### 【0019】

読み書き動作の最中に、データはデータバス44を介してフラッシュメモリデバイス30に出し入れされ得る。データとアドレス情報の調整は、データ制御回路ブロック46を通して行われ得る。最後に、フラッシュメモリデバイス30は、制御バス50を介してプロセッサ12から制御信号を受信するように構成される制御回路48を含んでもよい。制御回路48は、行デコーダブロック34、列デコーダブロック36、センス増幅器ブロック40、行ドライバブロック42、およびデータ制御回路ブロック46の各々に結合され、一般に、フラッシュメモリデバイス30内の様々な回路間でタイミングと制御を調整するように構成される。

20

#### 【0020】

図3は、図2のメモリアレイ32の実施形態例を図示する。本実施形態例では、メモリアレイ32はNANDメモリアレイ52を含む。NANDメモリアレイ52は、ワード線WL(0)-WL(M)と、交差するローカルピット線BL(0)-BL(M)を含む。理解されるように、デジタル環境でのアドレス指定を容易にするために、ワード線WLの数とピット線BLの数は各々2のべき乗である(例えば256のワード線WL × 4,096のピット線BL)。ローカルピット線BLは多対一の関係でグローバルピット線(図示せず)に結合される。

30

#### 【0021】

NANDメモリアレイ52は、ワード線WLとローカルピット線BLの各交点にある浮遊ゲートトランジスタ54を含む。浮遊ゲートトランジスタ54は、前述のようにNANDメモリアレイ52にデータを記憶するための不揮発性メモリセルとして機能する。理解されるように、各浮遊ゲートトランジスタは、ソース、ドレイン、浮遊ゲート、および制御ゲートを含む。各浮遊ゲートトランジスタ54の制御ゲートは、それぞれのワード線WLに結合される。浮遊ゲートトランジスタ54は、ゲート選択線間に形成されるNANDストリング56を形成するために、ソースからドレインに直列に接続される。具体的には、NANDストリング56はドレイン選択線GS(D)とソース選択線GS(S)の間に形成される。ドレイン選択線GS(D)は、それぞれのドレイン選択ゲート58を通して各NANDストリング56に結合される。同様に、ソース選択線GS(S)はそれぞれのソース選択ゲート60を通して各NANDストリング56に結合される。ドレイン選択ゲート58とソース選択ゲート60は、例えば電界効果トランジスタ(FET)をそれぞれ含んでもよい。メモリアレイ52の列は、NANDストリング56と、それに接続されるソース選択ゲート60およびドレイン選択ゲート58とを含む。浮遊ゲートトランジスタ52の行は、与えられたワード線WLに共通に結合されるトランジスタである。

40

#### 【0022】

各ソース選択ゲート60のソースは、共通ソース線CSLに接続される。各ソース選択ゲートのドレインは、それぞれのNANDストリング56内の浮遊ゲートトランジスタ54のドレインに結合される。各ソース選択ゲート60のゲートは、ソース選択線GS(S)に結合される。

#### 【0023】

各ドレイン選択ゲート58のドレインは、対応するNANDストリング56のためのそれぞれの

50

ローカルピット線BLに接続される。各ドレイン選択ゲート58のソースは、それぞれのNANDストリング56の浮遊ゲートトランジスタ54のドレインに接続される。従って、図3に図示される通り、各NANDストリング56はそれぞれのドレイン選択ゲート58とソース選択ゲート60の間に結合される。各ドレイン選択ゲート58のゲートは、ドレイン選択線GS(D)に結合される。

#### 【0024】

NANDメモリアレイ52の動作中、個々のメモリセル(浮遊ゲートトランジスタ54)の極めて接近した物理的構造は、隣接するメモリセル間の干渉を引き起こす可能性がある。例えば、読み取り動作中、ソース選択線GS(S)とドレイン選択線GS(D)が有効化される。ソース選択線GS(S)とドレイン選択線GS(D)は、例えば4.5Vの電圧にバイアスされ得る。ソース選択線GS(S)とドレイン選択線GS(D)のバイアスは、それぞれのソース選択ゲート60とドレイン選択ゲート58をオンにする。動作中、隣接する浮遊ゲート間の容量性の干渉(“FG-FG干渉”もしくは“FG-FG静電容量”)は、NANDメモリアレイ52の動作に悪影響を及ぼす可能性がある。多くの従来の浮遊メモリセルのFG-FG干渉は、図4と5に関して下記に簡潔に記載され、説明される。10

#### 【0025】

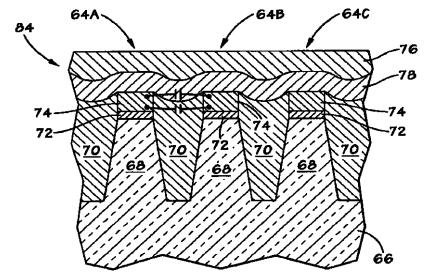

簡潔に図4を参照すると、NANDメモリアレイなどの従来の浮遊ゲートメモリアレイの一部の断面図が図示され、概して参考数字62であらわされる。構造62は、浮遊ゲートメモリアレイのワード線WLに沿った三つの浮遊ゲートトランジスタ64A-64Cの断面図を図示する。構造62は、例えばケイ素であり得る基板66を含む。ワード線WLに沿った浮遊ゲートトランジスタ64A-64Cの各々の間を絶縁するために、シャロウトレチが基板66に形成され、酸化物などの誘電材料で充填され、シャロウトレチアイソレーション(STI)酸化物領域70によって分離された垂直支柱68を作り出す。理解されるように、支柱68はアレイのピット線BLに沿ってページの中にのびる。浮遊ゲートトランジスタ64A-64Cの各々のソースおよびドレインを提供するために、ドープ領域(図示された図では見えない)が支柱68の上部に形成される。20

#### 【0026】

各浮遊ゲートトランジスタ64A-64Cは、一般に、二酸化ケイ素( $\text{SiO}_2$ )などのゲート酸化物72を含む。各浮遊ゲートトランジスタ64A-64Cは、絶縁浮遊ゲート74も含む。浮遊ゲート74は、例えばポリシリコンを含んでもよい。前述の通り、各浮遊ゲートトランジスタ64A-64Cは、さらに制御ゲートも含み、これはポリシリコンなどの単一の導電層から形成されてもよく、概して参考数字76であらわされる。アレイの構成と動作のために、一つのワード線WL内の浮遊ゲートトランジスタ64A-64Cの各々は、図4に図示されるように共通制御ゲート76を共有し得る。浮遊ゲート74と制御ゲート76は、ゲート間誘電層78によって互いに電気的に絶縁される。ゲート間誘電層は例えば $\text{SiO}_2$ もしくは $\text{SiN}_x$ を含んでもよい。しかしながら、ゲート間誘電体は、以下にさらに説明されるように、典型的には、例えば $\text{SiO}_2$ もしくは $\text{SiN}_x$ よりも高い誘電率( $k$ )を持つ材料である。30

#### 【0027】

前述のように、隣接する浮遊ゲート74間の小さなピッチはFG-FG干渉の増加を引き起こす可能性がある。例えば、FG-FG干渉は、キャパシタ80によって図示されるようにSTI酸化物を通して起こる可能性がある。このわずかなFG-FG干渉は許容できる可能性があるが、キャパシタ82によってあらわされるゲート間誘電層78を通るFG-FG干渉は、あまり許容できない可能性がある。これは、特に高誘電率の誘電材料(例えば $k>10$ )に当てはまる。理解されるように、静電容量80と82は、一般に次の式によって決定される。40

#### 【0028】

$$C = k_0 A / t$$

ここでAは容量面積であり、 $k_0$ は自由空間の誘電率であり、kは材料の誘電率であり、tは材料の厚みである。

#### 【0029】

理解されるように、高誘電率の材料は、浮遊ゲート74と制御ゲート76からのトンネル電50

流と外方拡散を軽減するためにしばしば利用される。しかしながら、高誘電率の材料は、ゲート間誘電層78を通るFG-FG静電容量82を増加するという悪影響も有する。従って、より高誘電率の材料がゲート間誘電層78として利用されるにつれ、FG-FG静電容量82が増加する。本発明の実施形態は、図6-12に関して以下にさらに説明されるように、ゲート間誘電層78を通る浮遊ゲート74間の容量性の経路を除去することによって、ゲート間誘電層78を通るFG-FG静電容量82を削減し得る。

### 【0030】

次に図5を参照すると、構造84が図示される。構造84は、ゲート間誘電層78が、浮遊ゲート74の間でSTI酸化物70領域に落ち込んでいる点を除いて、図4の構造62と同一である。浮遊ゲートトランジスタ64A-64Cを製造するための特定のプロセスでは、ゲート間誘電体78が配置される際に、浮遊ゲート74の間に落ち込み、浮遊ゲート74の間により直接的な干渉の経路を作るよう、STI酸化物70が過剰にエッチングされることもある。理解されるように、図5の従来の構造84は、ゲート間誘電層78が隣接する浮遊ゲート74間により短い容量性の経路を作るので、好ましくないFG-FG静電容量82をさらにいっそう受けやすい可能性がある。本発明の実施形態は、図6-12に関して以下にさらに説明されるように、ゲート間誘電層78を通る浮遊ゲート74の間の容量性の経路を除去することによって、ゲート間誘電層78を通るFG-FG静電容量82を削減し得る。

### 【0031】

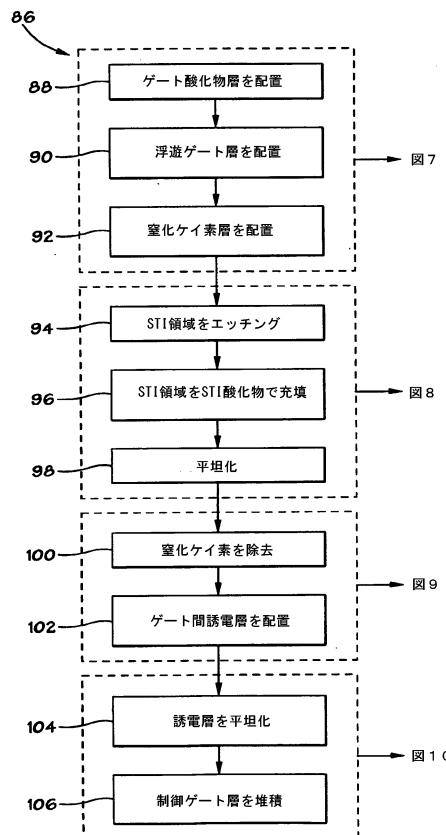

図6では、本発明の一実施形態に従う例示的なプロセス86が図示される。図7-11は、例示的なプロセス86に従って製造される浮遊ゲートメモリアレイの一部分の断面図を図示する。従って、図6は図7-11に図示された断面図と併せて説明される。

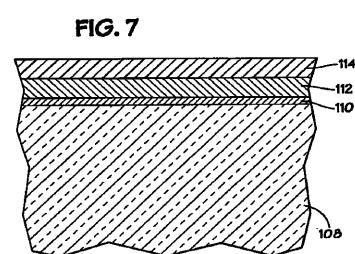

### 【0032】

最初に図6と併せて図7を参照すると、図6のブロック88で示されるように、ゲート酸化物層110が基板108の上に配置もしくは成長される。基板108は、例えばケイ素もしくはヒ化ガリウムを含んでもよい。ゲート酸化物層110は、例えば二酸化ケイ素(SiO<sub>2</sub>)を含んでもよい。ゲート酸化物層110を配置した後、ブロック90で示されるように浮遊ゲート材料112が配置される。浮遊ゲート層112は、例えばポリシリコン材料を含んでもよい。浮遊ゲート層112は、以下にさらに説明されるように、個々のトランジスタの浮遊ゲートを形成するために使用される。浮遊ゲート層112の堆積後、ブロック92で示されるように、窒化ケイ素(SiN<sub>2</sub>)層114などの誘電層が配置される。以下にさらに説明されるように、窒化ケイ素層114は、製造中に利用される犠牲層であり、浮遊ゲートトランジスタが形成される前に除去される。図9を参照して以下にさらに説明される理由から、窒化ケイ素層114はおよそ400よりも大きい厚みで配置される。ある実施形態では、窒化ケイ素層114は400~700の範囲の厚みで堆積される。

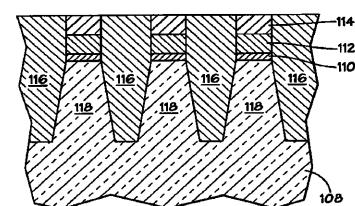

### 【0033】

次に図6と併せて図8を参照すると、ゲート酸化物層110、浮遊ゲート材料112、および窒化ケイ素層114の堆積後、ブロック94で示されるように、シャロウトレントアイソレーション(STI)領域が形成されるように、堆積された層と基板108の各々を通してシャロウトレントチがエッチングされる。次に、ブロック96で示されるように、STI酸化物領域116を形成するために、酸化物などの誘電材料がトレントチの各々に堆積される。前述の通り、STI酸化物領域116は、基板108内に形成され、最終的に浮遊ゲートメモリアレイとなるもののビット線BLに沿ってページの中に向かってのびる、垂直支柱118を画定する。また、STI酸化物領域116は、基板108内に形成された垂直支柱118の各々の上端の上に、ゲート酸化物層110、浮遊ゲート層112、および窒化ケイ素層114の絶縁領域も提供する。また、理解されるように、STI酸化物領域116を提供する酸化物材料の堆積中に、一般的に酸化物が窒化ケイ素層114を含む全構造の上に堆積される。従って、図8に図示された構造を完成させるために、ブロック98で示されるように、窒化ケイ素層114の上端から酸化物が除去されるように、酸化物の表面が平坦化され得る。平坦化は、例えば化学機械平坦化(CMP)プロセスによってなされてもよい。図8に図示される通り、平坦化ステップは、窒化ケイ素層114が支柱118の各々の上の個々の領域に分離されるまで行われ得る。

10

20

30

40

50

## 【0034】

STI酸化物領域116を作るために酸化物を平坦化した後、図6のブロック100で示されるように窒化ケイ素114が除去される。窒化ケイ素114は、例えば沸騰H<sub>3</sub>PO<sub>4</sub>などの標準的な窒化ケイ素エッチャントを用いて除去されてもよい。理解されるように、窒化ケイ素に選択的な他のエッチャントが利用されてもよい。理解されるように、窒化ケイ素エッチングは基本的には窒化ケイ素に選択的なエッチャントの使用によって行われるが、全エッチングプロセスは、窒化ケイ素エッチャントの利用の前および/または後に図8の構造をフッ化水素(HF)酸で処理するなど、窒化ケイ素エッチングの前および後のステップを含んでもよい。例えば、平坦化(図6のステップ98)の後、窒化ケイ素114に残った残存酸化物を除去するために、窒化ケイ素エッチングの前に希釈HF溶液で構造を処理してもよい。窒化ケイ素エッチングの前のHF処理は、窒化ケイ素114の全表面がその後窒化ケイ素エッチャントに晒されることを確実にする。同様に、窒化ケイ素エッチングの後、窒化ケイ素エッチングによる窒化ケイ素114の除去後に残った開口部内の自然酸化物や残存酸化物を除去するために、希釈HF溶液を用いる別のウェット処理が利用されてもよい。HF溶液処理は好ましくない酸化物をいくらか除去する上で有利であるが、HF溶液はSTI酸化物116の表面の部分もエッチングしてしまう可能性がある。本発明の実施形態に従って、一旦窒化ケイ素エッチングとHF溶液処理のステップが行われたら、以下にさらに説明されるように、ゲート間誘電層の堆積のためのシャロウトレンチを作るために、STI酸化物116の一部分を浮遊ゲート層112の平面よりも上におよぶように保持することが好ましい。

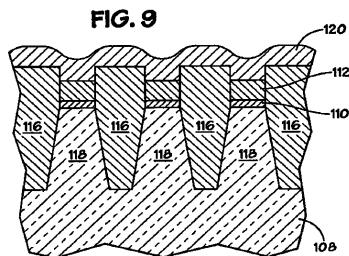

## 【0035】

次に図6と併せて図9を参照すると、ブロック102で示される通り、窒化ケイ素層114の除去後、ゲート間誘電層120が堆積され得る。本明細書で使用される“ゲート間誘電層”とは、浮遊ゲートトランジスタの浮遊ゲートと制御ゲートとの間に存在する誘電層をあらわす。図9は、窒化ケイ素層114の除去後、かつゲート間誘電層120の堆積後のこの構造を図示する。前述の通り、窒化ケイ素エッチングとHF処理の後、シャロウトレンチがSTI酸化物領域116の各々の間に残り、図9に図示される通り、ゲート間誘電層120が、浮遊ゲート層112の上端、かつSTI酸化物領域116の部分の間に配置され得るようになっている。STI酸化物領域の一部分が浮遊ゲート層112の平面よりも上におよぶことを確実にするために、HFエッチングステップの後にも、最終的にゲート間誘電層120の堆積のための開口部を画定する犠牲窒化ケイ素層114が、およそ400より大きい厚みで配置される。特定の実施形態では、窒化ケイ素層114は400~700の範囲の厚みで堆積される。理解されるように、窒化ケイ素層114の少なくとも400の初期厚さは、窒化ケイ素の除去およびHF処理の後、STI酸化物領域116間に形成される所望のトレンチをもたらす。つまり、ゲート間誘電体120が中に配置され得る空洞もしくはトレンチを画定するために、十分なSTI酸化物領域116が、依然として浮遊ゲート層112の平面よりも上に存在することになる。浮遊ゲート層112の上の空洞もしくはトレンチの深さは、50~500の範囲となり得る。窒化ケイ素層114の厚みと、利用される平坦化技術(図6のステップ98および104)は、理解されるように、ゲート間誘電層の所望の厚みを持つ浮遊ゲートトランジスタを作るために調節され得る。

## 【0036】

図9では、浮遊ゲート層112の上のトレンチは、浮遊ゲート層112の端と垂直に並んでいるように図示されるが、HF溶液処理は、STI酸化物領域116の中へ、トレンチの側壁を横方向にエッチングしてもよいことにも注目すべきである。従って、ある実施形態では、浮遊ゲート層112の上に作られるトレンチの側壁は、下にある浮遊ゲート層112よりも広いトレンチ(および最終的にゲート間誘電層)を画定してもよい。いずれにせよ、以下にさらに説明されるように、本発明の実施形態に従って、各浮遊ゲートトランジスタに対し分離されたゲート間誘電領域(図10の120A-120C)を最終的に画定するトレンチの各々の間には、いくらかの量のSTI酸化物領域116が存在することになる。

## 【0037】

前述の通り、ゲート間誘電層120は、高誘電率(k)を持つ材料を有利に含んでもよい。

10

20

30

40

50

本明細書で使用される“高誘電率”誘電材料は、一般的に、10以上( $k > 10$ )の誘電率を持つ材料をあらわす。ゲート間誘電層120のために利用され得る適切な高誘電率材料は、 $\text{Al}_2\text{O}_3$ 、 $\text{Gd}_2\text{O}_3$ 、 $\text{Yb}_2\text{O}_3$ 、 $\text{Dy}_2\text{O}_3$ 、 $\text{Nb}_2\text{O}_5$ 、 $\text{Y}_2\text{O}_3$ 、 $\text{La}_2\text{O}_3$ 、 $\text{ZrO}_2$ 、 $\text{HfO}_2$ 、 $\text{TiO}_2$ 、 $\text{Ta}_2\text{O}_5$ 、 $\text{SrTiO}_3$ 、 $\text{Ba}_x\text{Sr}_{1-x}\text{TiO}_3$ 、 $\text{Zr}_x\text{Si}_{1-x}\text{O}_y$ 、 $\text{Hf}_x\text{Si}_{1-x}\text{O}_y$ 、もしくは $\text{Al}_x\text{Zr}_{1-x}\text{O}_2$ 、あるいはそれらの組み合わせを含むが限定はされない。前述の通り、高誘電率誘電材料を利用することで、浮遊ゲートトランジスタ内のゲート間誘電体の厚みが非常に薄い場合でさえも、トランジスタ性能を維持しながらゲートリークを削減する。

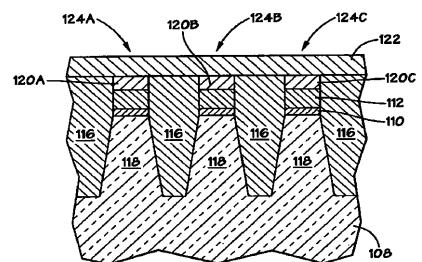

#### 【0038】

浮遊ゲートトランジスタの形成を完了するために、図6のブロック104で示される通り、ゲート間誘電層120がSTI酸化物領域116の上面と平坦になり、その結果、隣接するゲート間誘電領域から電気的に絶縁されるように、ゲート間誘電層120が平坦化される。従って、図10に最もよく示される通り、ゲート間誘電層120の平坦化の後(図6のブロック104)、個々に分離されたゲート間誘電領域120A-120Cが残る。理解されるように、浮遊ゲート112の各々の上に連続する誘電層を利用するよりも、各トランジスタ毎に電気的に絶縁されたゲート間酸化物領域120A-120Cを作ることによって、ゲート間誘電層を通る容量性の経路が除去され、その結果、図4および5を参照して前述したようなFG-FG干渉を有利に削減する。各ゲート間誘電領域120A-120Cの厚みは、およそ50-500 nmの範囲である。最終的に、本発明の実施形態に従って浮遊ゲートトランジスタ124A-124Cを完成させるために、図10に図示され、図6のブロック106で示される通り、制御ゲート層122が堆積される。

#### 【0039】

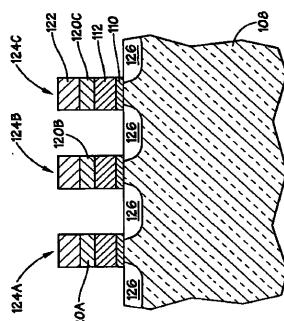

次に図11を参照すると、図10に図示された最終構造の別の図が示される。図11は、ワード線WLではなくビット線BLに沿って図10の構造を図示する。つまり、図11に示された図では、ワード線WLがページの中へのびる。図11に図示される通り、各浮遊ゲートトランジスタ124A-124Cに対する浮遊ゲート112、ゲート間誘電領域120A-120C、および制御ゲート122は、ビット線BLに沿って隣接デバイスから電気的に絶縁される。また、当業者に理解されるように、基板108の支柱118内に形成されたソースおよびドレイン拡散領域126も、図11に図示される。

#### 【0040】

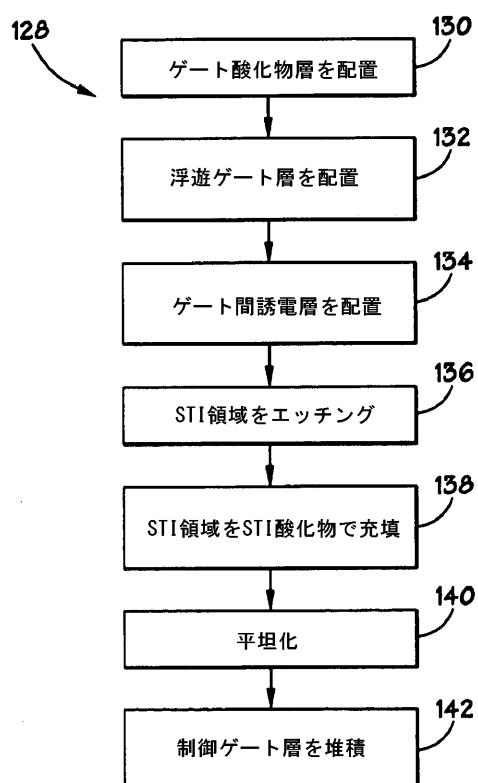

次に図12を参照すると、本発明のさらなる実施形態に従って、分離されたゲート間誘電領域を持つ浮遊ゲートトランジスタを製造するための別のプロセス128が図示される。プロセス128では、犠牲窒化ケイ素層は利用されない。その代わり、前述のように、および図12のブロック130と132で示される通り、ゲート酸化物層と浮遊ゲート層が基板の上に配置される。前述のように、浮遊ゲート層の上端の上に窒化ケイ素層を堆積するのではなく、ブロック134で示される通り、ゲート間誘電層が浮遊ゲート層の上に直接堆積される。ゲート間誘電層の堆積後、ブロック136で示される通り、ゲート間誘電層、浮遊ゲート層、ゲート酸化物層、および下にある基板は、STI領域を形成するためにエッチングされる。ゲート間誘電層の堆積後にSTI領域を形成することで、トレンチによって画定される各支柱の上端の上に分離されたゲート間誘電領域を作る。次に、ブロック138で示される通り、STI酸化物がSTI領域に配置される。次に、ブロック140で示される通り、分離されたSTI酸化物領域を形成するために構造が平坦化される。平坦化の後、ブロック142で示される通り、制御ゲートが堆積される。

#### 【0041】

図6および12に関して記載されたプロセスと同様の別のプロセスも利用されてもよい。この例示的なプロセスは、ゲート間誘電層の堆積後(ブロック134)、かつSTI領域がエッチングされる前(ブロック136)に、ポリシリコン層がゲート間誘電層の上に堆積され、窒化ケイ素層がポリシリコン層の上に堆積されることを除いて、図12に関して記載されたプロセスと同様である。ポリシリコン層と窒化ケイ素層の堆積後、STI領域がエッチングされ得る(ブロック138)。STI領域がSTI酸化物で充填され(ブロック138)、表面が平坦化された(ブロック140)後、窒化ケイ素層が除去される。窒化ケイ素層の除去後、

10

20

30

40

50

堆積されたポリシリコン層の絶縁領域がゲート間誘電層の上に残る。次に、この構造の上に制御ゲート層が堆積される（ブロック142）。理解されるように、制御ゲート層は、分離されたポリシリコン領域と直接的に接触するように配置される。ポリシリコン領域は導電性であり、それぞれの下にある浮遊ゲート領域に向かって下にのびる、制御ゲート層の垂直伸長部分を形成する。

【 0 0 4 2 】

本発明の実施形態は、様々な変更と代わりの形態を許容し得るが、特定の実施形態が一例として図面に示され、本明細書に詳細に記載されている。しかしながら、本発明は開示された特定の形態に限定されることを意図しないことを理解すべきである。むしろ、本発明の実施形態は、以下の添付の請求項によって規定される通り、これらの実施形態の精神と範囲の内にある全ての変更、均等物、および代わりのものを包含するものである。

10

( 1 )

( 2 )

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

---

フロントページの続き

合議体

審判長 小野田 誠

審判官 鈴木 匡明

審判官 飯田 清司

(56)参考文献 特開平10-340964(JP,A)

特開2005-026591(JP,A)

特開2004-179624(JP,A)

特開2005-150676(JP,A)

特開2002-076272(JP,A)

特開2000-174242(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792