## (12) UK Patent Application (19) GB (11) 2488496

(43) Date of Reproduction by UK Office

29.08.2012

(21) Application No: 1210769.4

19.11.2010 (22) Date of Filing:

Date Lodged: 18.06.2012

(30) Priority Data:

(31) 12646836 (32) 23.12.2009 (33) US

(86) International Application Data: PCT/US2010/057436 En 19.11.2010

(87) International Publication Data: WO2011/087573 En 21.07.2011

(71) Applicant(s):

Intel Corporation (Incorporated in USA - Delaware) 2200 Mission College Boulevard, SC4-202, Santa Clara, CA 95052, United States of America

(72) Inventor(s):

Mihir K Roy Islam Salama Charavana K Gurmurthy Robert L Sankman

(74) Agent and/or Address for Service:

**RGC Jenkins & Co** 26 Caxton Street, London, SW1H 0RJ, **United Kingdom**

(51) INT CL:

H01L 21/48 (2006.01) H01L 23/498 (2006.01)

(56) Documents Cited by ISA:

US 20080003764 A1 US 20070175025 A1 US 20070082501 A1 US 20040140551 A1

US 20040089470 A1

(58) Field of Search by ISA:

INT CL H01L, H05K

Other: Korean & Japanese utility models and appliactions,eKOMPASS(KIPO internal) & keywords

- (54) Title of the Invention: Through mold via polymer block package Abstract Title: Through mold via polymer block package

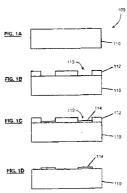

- (57) Methods for forming an integrated circuit chip package having through mold vias in a polymer block, and such packages are described. For example, a first interconnect layer may be formed on a molded polymer block, wherein the first interconnect layer comprises first interconnects through a first polymer layer and to the block. Then, at least one second interconnect layer may be formed on the first interconnect layer, wherein the second interconnect layer comprises second interconnects through a second polymer layer and to the first interconnects of the first interconnect layer. Through mold FIG. 15 vias may then be formed through the block, into the first interconnect layer, and to the first interconnects. The through mold vias may be filled with solder to form bumps contacting the first interconnects and extending above the block. Other embodiments are also described and claimed.