**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

H03M 7/02

(45) 공고일자 2005년11월16일

(11) 등록번호 10-0528891

(24) 등록일자 2005년11월09일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2000-7009781   | (65) 공개번호   | 10-2001-0041589 |

| (22) 출원일자   | 2000년09월04일       | (43) 공개일자   | 2001년05월25일     |

| 번역문 제출일자    | 2000년09월04일       |             |                 |

| (86) 국제출원번호 | PCT/US1999/005301 | (87) 국제공개번호 | WO 1999/46861   |

| 국제출원일자      | 1999년03월11일       | 국제공개일자      | 1999년09월16일     |

## (81) 지정국

국내특허 : 알바니아, 아르메니아, 오스트리아, 오스트레일리아, 아제르바이잔, 보스니아 헤르체고비나, 바르바도스, 불가리아, 브라질, 벨라루스, 캐나다, 스위스, 리히텐슈타인, 중국, 쿠바, 체코, 독일, 덴마크, 에스토니아, 스페인, 핀란드, 영국, 그루지야, 헝가리, 이스라엘, 아이슬랜드, 일본, 캐냐, 키르키즈스탄, 북한, 대한민국, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트비아, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 노르웨이, 뉴질랜드, 슬로베니아, 슬로바키아, 타지키스탄, 투르크멘, 터키, 트리니다드토바고, 우크라이나, 우간다, 미국, 우즈베키스탄, 베트남, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 싱가포르, 아랍에미리트, 안티구와바부다, 코스타리카, 도미니카, 알제리, 모로코, 탄자니아, 남아프리카, 벨리제, 모잠비크,

AP ARIPO특허 : 캐냐, 레소토, 말라위, 수단, 스와질랜드, 우간다, 시에라리온, 가나, 감비아, 짐바브웨,

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크멘,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 리히텐슈타인, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 말리, 모리타니, 니제르, 세네갈, 차드, 토고, 기니 비사우,

(30) 우선권주장 60/077,537 1998년03월11일 미국(US)

(73) 특허권자 톰슨 라이센싱 소시에떼 아노님

프랑스 세데 볼로뉴 깨아 르 갈로 46

(72) 발명자 모한, 찬드라

미국, 인디애나주46032, 카멜, 플리트우드드라이브노쓰12970

라이들, 월 헬름, 언스트

미국, 인디애나주46250, 인디애나폴리스, 프린비아테라쓰8837

즈항, 즈히밍

미국, 인디애나주46280, 인디애나폴리스, 벨레르드라이브10854

(74) 대리인

문경진

조현석

심사관 : 송병준

**(54) 코딩된 출력 신호를 생성하는 방법 및 디코딩된 데이터스트림을 생성하는 방법****요약**

화산 스펙트럼 시스템에서 사용하기에 적합한 가변 애피쳐 코딩/디코딩 시스템은 입력 NRZ 비트스트림의 다중 위상 코딩을 제공한다. 코딩된 출력 신호의 각 비트는 입력 신호의 논리 레벨에 따라 사전 결정된 다른 수의 클럭 주기를 포함하기 위해 코딩된다. 코딩된 비트는, 입력 신호가 논리 레벨 천이를 나타내지 않을 때, 일예로 9와 같이 사전 결정된 클럭 주기에 대한 기준 수을 나타낸다. 입력 신호가 논리 레벨 "0"에서 "1"로의 위상 변화를 나타낼 때, 관련된 코딩 비트 폭은 1 클럭 주기가 증가되어 10 클럭 주기가 된다. 입력 신호가 논리 레벨 "1"에서 "0"으로의 위상 변화를 나타낼 때, 관련된 코딩 비트의 비트 폭은 1 클럭 주기가 감소되어 8클럭 주기가 된다. 따라서, 코딩된 출력 신호는 사전 결정된 인자(N)에 비례하는 비트 폭 변화에 의해 표시되는 3 가지 타입의 정보를 보유할 수 있다.

**대표도**

도 6

**명세서****기술분야**

본 발명은 특별히 화산 스펙트럼 응용에 적합한 디지털 신호 위상 변조에 관한 것이다.

**배경기술**

무선 주파수(RF) 대역폭 압축(즉, 스펙트럼 효율을 증대시키기 위함)에 대해 널리 공지된 두 가지 변조 기술에는 직교 진폭변조(QAM)와 직교위상 편이변조(QPSK)가 있다. 이러한 두 방법은 변조 레벨을 증가시키고 대역폭 압축을 수반함으로서 신호 전력의 손실을 갖는다. 또한, 이러한 방법은 낮은 신호 대 잡음비(SNR)로 인해 에러가 발생하기 쉽다. 이러한 에러를 보상하기 위해, 대역폭 압축 증가분의 자승에 거의 동일한 전력 증가가 필요하다. 예를 들어, 10 배의 대역폭 압축을 위해서는 100 배의 전력 증가가 필요하다.

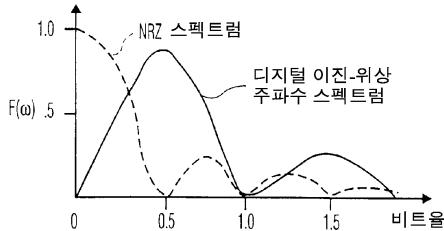

주파수 편이변조(FSK), 최소 주파수 편이변조(MFSK), GMSK, 및 QAM과 같이 일부 일반적으로 사용되는 변조 기술은 반송파 주위로 대역폭을 집중시키는 비 제로 복귀(NRZ:non-return to zero) 라인 코딩된 데이터를 송신한다. 이진-위상 코딩{예를 들어, 공지된 것과 같은 맨체스터(Manchester) 및 밀러(Miller) 코딩}은 정보 측파대가 반송파에 근접하지 못하도록 한다. 도 1은 QPSK, BPSK, QAM 등과 같은 디지털 이진-위상 신호의 스펙트럼 특성을 도시한다. 라인 코딩된 신호의 스펙트럼은 기저대역 주위에 집중하고, 반면에 디지털 이진-위상 신호에 대해서 상기 스펙트럼은 원래의 지점에서 송신된 비트율의 거의 반이 되는 지점으로 물러난다. 송신 대역폭에서 상당한 절약을 획득하기 위해서, 하나의 측파대만이 송신될 필요가 있다. 이진-위상 신호는 시간에 가변적이기 때문에 시간에 따라 변하는 제로 교차점을 갖지 않는다. 이진-위상 코드는 극성은 갖고 DC 성분은 거의 갖지 않는다.

다른 변조 방법인 펄스 폭 변조는 스펙트럼 엔코딩을 위해 기저대역에서 사용되고 클럭 주기의 정수배인 출력 펄스를 생성한다. 이 방법을 통해, 데이터 비트의 종단 또는 중심으로의 위상 지연(phase delay)은 "1" 또는 "0"의 논리 레벨로 각각 구별된다. 밀러 엔코딩은 이러한 타입의 변조에 대한 한 예이다. 이러한 타입의 변조를 통해 RF 반송파를 변조시키는 것은 대역폭을 보존하지 않는다.

H.R. 워커(H.R. Walker)에 허여된 미국 특허(제 4,742,532호)에서는 가변 위상 편이변조(VPSK)로 언급되는 변조 방법을 기술하고 있다. VPSK 변조는 이진 비 제로 복귀 데이터 신호의 "1"과 "0" 논리 상태 사이에서의 변화를 엔코딩한다. 상기 엔코딩은 사전 결정된 코딩 규칙(coding rule) 세트에 따라 비트 구간의 4/4, 5/4, 및 6/4 배인 가변 구간을 갖는 필스 신호를 생성한다. 코딩 규칙에 따라, 데이터 극성에서의 무변화는 4/4 비트 폭으로 코딩되고, 데이터 극성에서의 변화는 5/4 비트 폭으로 코딩되며, 마지막 비트에 대한 조건부적인 경우의 코딩은 코딩/디코딩 시스템의 필요한 리셋을 나타내기 위해 6/4 비트 폭 구간으로 코딩된다. 이 방법은 이론적으로 Hz-대역폭 당 7.2 비트의 나이키스트 인자(Nyquist factor)를 생성할 수 있다.

H.R. 워커에 허여된 미국 특허(제 5,185,765호)에서는 VPSK 변조의 개선된 방법이 설명되어 있다. 이 방법을 통해, 각각의 입력 데이터 비트는 M개의 클럭 주기로 구성된 비트 구간을 갖는다. 데이터 비트 극성 변화는 M/M, M+1/M, 및 M+2/M개의 비트 구간의 과형 폭으로 코딩된 위상 편이변조이고, 여기서 M은 3보다 큰 짝수 정수이다. 코딩 규칙에 따라, 데이터 극성에서의 무변화(no change)는 M개의 클럭 주기로 코딩되고, 데이터 극성에서의 변화는 M+1/M개의 클럭 주기로 코딩되며, M-1 데이터 비트 극성의 변화에서 발생하는 리셋을 나타내기 위해 구간에 대한 최종 엔코딩 비트는 M+2/M개의 클럭 주기로 코딩된다. 이 방법은 이론적으로 신호 스펙트럼을 기저대역 NRZ 등가 신호 대역폭의 1/6으로 맞춤으로서, 나이키스트 효율이 10 변조 레벨에 대해서 Hz-대역폭 당 15.3 비트까지 되도록 한다. 이러한 가변적인 위상 편이는 코딩/디코딩 시스템으로 하여금 각 비트 구간의 처음부분과 동기를 이루지 못하도록 야기한다. 이러한 문제를 극복하기 위해서, 리셋 비트가 모든 비트 구간에 대해 데이터에 삽입되어야 한다.

개시된 코딩/디코딩 방법은 워커에 의해 설명된 시스템과 비교해서 동작에 관련한 장점을 보인다. 특히, 개시된 가변 애퍼처(aperture) 코딩 방법은 워커의 미국 특허(제 5,185,765호)에 설명된 방법의 효율보다 두 배의 효율을 제공하고, 하드웨어 및 소프트웨어의 필요성에 있어서 더욱 경제적이다.

### 발명의 상세한 설명

본 발명의 원리에 따른 가변 애퍼처 코딩 시스템은 입력 NRZ 비트스트림을 엔코딩하기 위해서 다음의 알고리즘을 사용한다.

만약 비트스트림이 논리 "0"에서 논리 "1"로의 위상 변화를 나타낸다면, 관련된 코딩 데이터 비트가 사전 결정된 인자(N)에 비례하는 제 1 방향(예를 들어, 증가하는 방향)으로의 비트 폭 변화를 나타낸다.

만약 비트스트림 논리 레벨이 불변한 채로 있다면, 관련된 코딩 비트의 비트 폭은 사전 결정된 원래의 비트 폭으로 유지된다.

만약 비트스트림이 논리 "1"에서 논리 "0"로의 위상 변화를 나타낸다면, 관련된 코딩 비트가 사전 결정된 인자(N)에 비례하는 다른 제 2 방향(예를 들어, 감소하는 방향)으로의 비트 폭 변화를 나타낸다.

### 도면의 간단한 설명

도 1은 NRZ 및 이진-위상 신호에 대한 주파수 스펙트럼을 나타내는 도면.

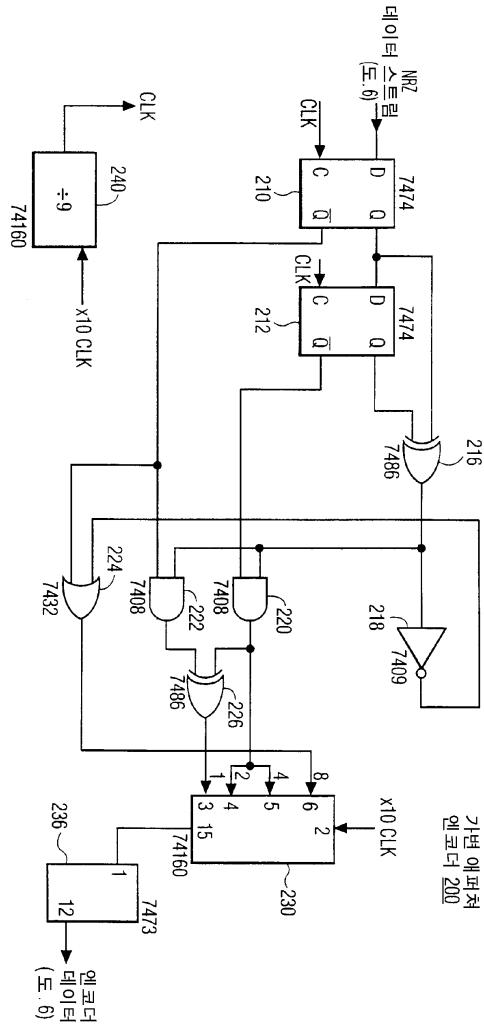

도 2는 본 발명의 원리에 따른 엔코더 네트워크를 나타내는 도면.

도 3은 도 2의 엔코더에 사용되는 엔코더 논리 표를 나타내는 도면.

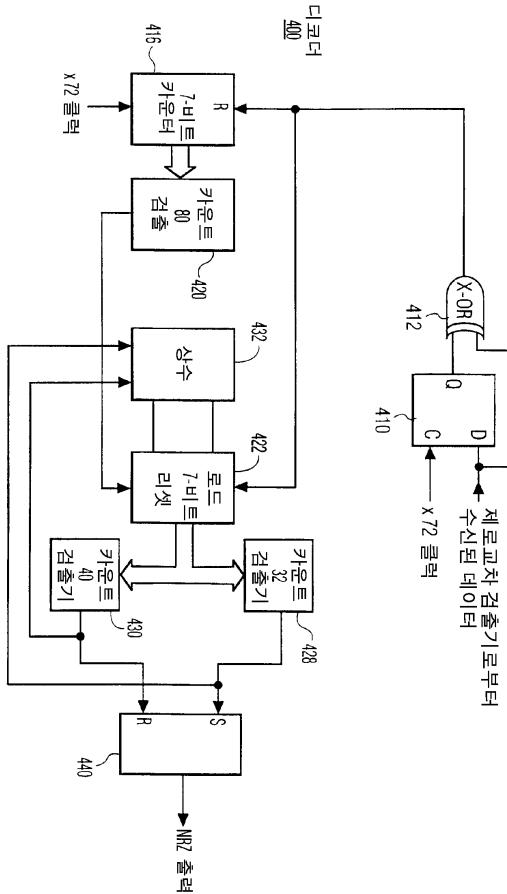

도 4는 본 발명의 원리에 따른 디코더 네트워크를 나타내는 도면.

도 5 및 도 6은 본 발명의 원리를 도시하는 과정을 나타내는 도면.

도 7은 본 발명에 따른 엔코더를 포함하는 송신기 시스템을 나타내는 도면.

도 8은 본 발명에 따른 디코더를 포함하는 수신기를 나타내는 도면.

### 실시예

개시된 신호 코딩 방법은 가변 애피처 코딩(Variable Aperture Coding), 즉 VAC로 언급된다. 상기 개시된 방법은 변조 레벨을 증가시키거나 대역폭 압축을 수반함으로서 신호 전력의 손실을 갖는 QAM 및 QPSK 시스템의 이전에 언급된 문제를 극복한다. 개시된 VAC 방법은 9:1의 인자만큼 정보 대역폭을 압축시키기 위해 단일 측파대 방법을 사용하고, 반송파에 대한 직접적인 주파수 변조를 통해 구현될 수 있다. 개시된 VAC 대역폭 압축 방법은, 반송파에 대해 VAC 코딩된 데이터가 송신되는 동안에, 상기 반송파에 대한 BPSK 타입의 변조를 수행하는 확산 코드를 갖는 직접 시퀀스 확산 스펙트럼 시스템을 구현하는데 매우 유용하다.

개시된 장치는 처리이득에 있어 상당한 개선을 보인다. 정의상으로는, 임의의 직접 시퀀스 확산 스펙트럼 시스템에 대해서, 처리이득은  $10 \log[\text{확산 스펙트럼 대역폭}/\text{정보 대역폭}]$ 으로 정의된다. 더 높은 처리이득이란 통신 시스템을 방해하기 위해서는 간섭 신호로부터 더 많은 전력이 필요할 것이라는 것을 의미한다. 일반적인 디지털 구현에 있어서, 다음의 시스템 파라미터가 적용될 수 있다:

- 확산 대역폭 : 2 MHz

- 버스트(burst) 데이터 송신속도 : 80 Kbps(시분할 이중송신 링크를 통해 송신되는 40 Kbps는 원래의 송신속도의 두 배로 버스트 출력되어야 할 것이다)

- 버스트 데이터 대역폭 : BT=1에서 80 Khz(최소의 필터링을 가정한 경우)

이러한 조건하에서 처리이득은 13.97 dB임을 알 수 있다.

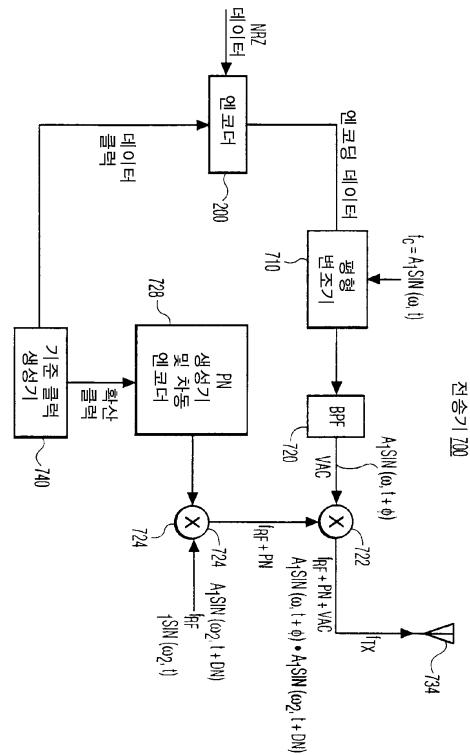

개시된 시스템에서는 다음의 파라미터가 적용된다:

- 확산 대역폭 : 2 MHz

- 정보 대역폭 : 4.44 Khz(9:1의 압축에서 40 Kbps). 이 경우에, 처리이득은 26.57 dB임을 알 수 있다. 따라서, 간섭 신호는 종래의 디지털 시스템에 비해서 12.6 dB의 차이가 나는 개시된 시스템을 방해하기 위해서 20배 더 강력하게 될 필요가 있다. 이는 더 많은 양의 데이터 송신이 다른 소스로부터 동일한 주파수로 송신되는 간섭으로부터 이뮤니티(immunity)를 갖도록 한다. 이러한 장점은 도 7 및 도 8에 도시된 장치를 통해 달성된다. 더 높은 처리이득이 디지털 정보 비트를 아날로그 도메인으로 변환함으로써 달성된다. 이러한 더 높은 처리이득의 달성을 엔코더나 이진위상 변조기 블록(710)없이는 불가능하다. 수신기 측에서, 블록(832) 이후에, 위상 편이 검출기와 제로 교차 검출기가 검출 처리를 완료한다. 다음으로 검출된 데이터는 유닛(836)에 의해 디코딩된다.

개시된 VAC 코딩은 개선된 간섭 저지를 용이하게 하고, 상당히 감소된 비용과 복잡도로 다양한 응용에 사용될 수 있다. 이러한 응용은 일례로 전력선 음성 및 데이터 통신(power line voice and data communications), 대역내 디지털 오디오 방송(in-band digital audio broadcast), 케이블 모뎀, 다중선 비즈니스 전화(multiple line business telephone), 및 BPSK 코딩을 사용한 디지털 방송 위성 시스템을 포함한다. 개시된 변조 시스템은 50 Khz 이상의 반송파 주파수로 가정내 유선(예를 들어, 전용 케이블, 전용 4-선 전력선) 또는 무선 응용을 효과적으로 지원할 것이다.

아래에 설명되는 바와 같이, 본 발명에 따른 시스템은 입력 NRZ 비트스트림을 사전 결정된 인자(N)의 함수에 따라 엔코딩하기 위해 다음의 알고리즘을 이용한다. N이 9일 때, 예를 들어, 만약 비트스트림이 논리 레벨 "0"에서 "1"로의 위상 변화를 나타낸다면, 코딩된 비트스트림에서 관련 비트의 비트 폭은 1 클럭 주기 증가되어, 이 예에서는 10 클럭 주기로 된다. 만약 입력 NRZ 데이터스트림 논리 레벨이 불변한 상태로 있다면, 코딩된 비트스트림에서 관련 비트의 비트 폭은 사전 결정된 폭에서 불변한 상태로 존재하고, 이 예에서는 9 클럭 주기를 유지한다. 만약 비트스트림이 논리 레벨 "1"에서 "0"으로의 위상 변화를 나타낸다면, 코딩된 비트스트림에서 관련 비트의 비트 폭은 1 클럭 주기 감소되어, 이 예에서는 8 클럭 주기로 된다. 설명된 9 클럭 주기으로부터 1 주기 비트 폭의 증가 및 감소는 한 예이다. 다른 비트 폭의 변동이 가능하다. 현행 기술에서는, NRZ 주기의 최대 1/15의 비트 폭 변동이 심각한 신호 열화 없이 생성될 수 있다. 그러한 경우에, 거의 30:1의 RF 대역폭 압축이 달성될 수 있다. 또한, 비트 폭은 거꾸로 조정될 수 있다. 즉 "0"에서 "1" 및 "1"에서 "0"으로의 논리 레벨 변화에 대해서 각각 감소 또는 증가될 수 있다.

개시된 시스템은, "하이(high)"에서 "로우(low)"로의 천이 및 "로우"에서 "하이"로의 천이로 인한 위상 편이(phase excursion)가 동일하기 때문에, 누적 위상 증가(cumulative phase build up)를 나타내지 않는다. 또한, 개시된 시스템에서, 데이터 엔코딩은 별도의 9X 클럭을 통해 수행되고, Fc를 생성하기 위해 사용되지 않는다. 수신기는 제로 교차를 검출

하고 9X 디코딩 클럭의 시간을 정한다. 이는 RF가 엔코딩/디코딩 클럭으로부터 완전히 독립적일 때 시스템의 적응성을 향상시킨다. 또한, 데이터가 변하지 않을 때("1" 또는 "0"의 논리 레벨이 반복됨), 9X 클럭이 도 7의 블록(710)에 있는 이진-위상 변조기를 스위칭하기 위해 사용될 것이다. 이는 디코딩 회로를 간단하게 한다. 본 발명의 원리는 비트 코딩뿐만 아니라 이진-위상 편이변조를 수행하는 처리도 포함한다. 교호의(alternate) 엔코딩된 비트가 이진위상 변조기에서  $0^{\circ}$ 에서  $180^{\circ}$ 로 스위칭될 때, 상기 이진-위상 변조기는 대척(antipodal) 잡음 벡터의 제거를 통해 잡음충을 감소시킨다. 도 2 및 도 4는 디지털 신호 프로세서(DSP), 이산 전용 논리회로 또는 FPGA를 사용하여 구현될 수 있다. 그러나, 도 7 및 도 8은, 더 높은 처리 이득을 갖는 직접 시퀀스 확산 스펙트럼 시스템이 디지털 정보를 아날로그 도메인에 삽입함으로써 구현되는 개념에 있어 독특하다.

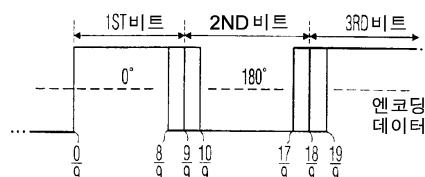

도 5는 가변 애퍼쳐 코딩을 도시하고 있다. 이 예에서 사전 결정된 인자(N)는 9인데, 그 이유는 이 예에서 각 코딩된 비트에 대해서 평균 9 클럭 주기가 제공되기 때문이다. 이 실시예에서 VAC 코딩 규칙은 위상 천이에 대해  $1/N$  만큼의 비트 구간을 반대 방향으로 증가 또는 감소시키기 때문에, 비트 구간의 평균은 시간 동안에 9개의 클럭 주기를 포함할 것이다. 어떠한 리셋도 코딩된 비트 데이터 내에서 필요하지 않은데, 그 이유는 어떠한 추가적인 위상 편이(VMSK 변조와는 다른)도 존재하지 않고, 코딩된 신호의 각 상승 또는 하강 에지가 하나의 데이터 비트를 나타내기 때문이다. VPSK는, 대조적으로, 입력 데이터의 각각의 N-1 비트에 대해서 하나의 데이터 비트로 제한되고, 이 후에 리셋은 코딩된 데이터스트림을 클럭에 재동기시켜야 한다.

도 5에서 보여지는 바와 같이, 한 비트는, 평균적으로, 이 예에서 N=9인 N 개의 클럭 주기와 동일하다. NRZ 데이터의 위상이 논리 "0"에서 논리 "1"로 천이될 때, 하나의 엔코딩된 비트 구간은 하나의 추가 클럭 주기, 즉 10 개의 클럭 주기( $10/9$ )를 포함한다. NRZ 데이터 위상이 논리 "1"에서 논리 "0"으로 천이할 때, 하나의 엔코딩된 비트 구간은 하나 적은 클럭 주기, 즉 8 개의 클럭 주기( $8/9$ )를 포함한다.

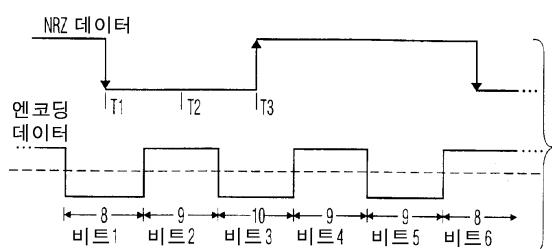

도 6은 가변 애퍼쳐 코딩(하단 파형)을 통해 엔코딩되는 입력 NRZ 파형(상단 파형)을 도시한다. 이 예에서, 입력 NRZ 데이터스트림은 하나의 논리 상태에서 시작하여 시간(T1)에서 다른 논리 상태로 스위칭한다. NRZ 데이터는 다음 2비트 동안 이 상태를 유지하고, 그런 다음 시간(T3)에서 다음 3비트 동안의 논리 상태로 스위칭한 후에, NRZ 데이터는 다시 상태를 스위칭한다. 엔코딩된 데이터는 위상으로부터 전압으로 변환하기 위해서  $90^{\circ}$ 만큼 위상 편이된다.

NRZ 데이터 자체가 이진위상 변조기를 스위칭하기 위해 사용되지는 않는다. NRZ 데이터는 논리 상태 "1" 또는 "0"의 비트스트림을 가질 수 있다. 이 비트스트림은 가변적인 시간 지속기간에 따라  $0^{\circ}$  및  $180^{\circ}$  천이를 갖는 비트스트림으로 엔코딩된다. 특정 비트가 "하이" 또는 "로우" 상태를 유지하는 시간 지속구간에서 이러한 변화성은 "1"에서 "0"으로의 천이, "0"에서 "1"로의 천이, 또는 원래의 NRZ 레벨에서의 무변화를 엔코딩한다. 이진위상 변조기를 변조시키는 것은 이러한 시변 파형(time varying waveform)이다. 변조기 출력 파형에서  $90^{\circ}$ 위상 편이는 이진위상 변조된 신호를 선형 위상 대역통과 필터를 통과시킴으로써 이루어지고, 상기 대역통과 필터는 위상 편이를 유도한다. 구형파 신호를 대역통과 필터링시킴으로써 사인파 신호가 생성된다.

데이터 코딩이 시작되었을 때, 만약 NRZ 데이터가 이전 비트로부터 위상을 스위칭하지 않는다면, 코딩된 비트의 지속기간은 9 클럭 주기이다. NRZ 데이터가 시간(T1)에서 논리 "1"에서 논리 "0"으로 위상 스위칭하였을 때, 대응하는 엔코딩된 비트(1)는 8 클럭 주기를 포함한다. 다음으로 코딩된 비트(2)는 NRZ 데이터가 위상 변화가 없기 때문에 9 클럭 주기를 포함한다. 다음의 코딩된 비트(3)는 대응하는 NRZ 비트가 시간(T3)에서 논리 "0"에서 논리 "1"로 위상 변화를 하기 때문에 10 클럭 주기를 포함한다. 이러한 코딩 패턴은 NRZ 데이터스트림의 존속기간 동안에 계속된다.

가변 애퍼쳐 코딩은, "1"에서 "0"으로의 논리 천이나 "0"에서 "1"로의 논리 천이를 나타내는 원래의 NRZ 파형에 따라, 출력 엔코딩된 파형이 조기에 또는 나중에(earlier or later) "제로 교차" 점을 교차한다는 사실에서 유도된다. 비트당 단지 한번의 천이가 존재하고, 이러한 정보를 사용하는 수신기는 원래의 NRZ 정보를 복구시키기 위해 사용된다. 엔코딩된 데이터는 상기 엔코딩된 데이터스트림에  $90^{\circ}$ 위상 편이를 제공하는 대역통과 필터{도 7에서 블록(720)}을 또한 통과한다. 이러한 위상 편이는 비트-극성 변화를 전압 최고점으로 변환한다. 저역 통과 필터, 또는 적분기는 적절한 대역통과 필터로 대체될 수 있다. 대역통과 필터는 대역 푸리에 성분(band fourier component)을 제거하고 측파대 신호 성분만을 제공하기 위해 필요하다. 이러한 대역통과 필터의 출력은 가변 주기를 갖는 사인 신호이다. 이 측파대 대역통과 필터는 선형적인 위상 지연 특성{예를 들어, 베셀 특성(Bessel characteristic)}을 나타낸다. 이 필터로부터의 필터링된 단일 측파대 신호는 엔코딩된 J1 베셀 신호이고, 송신 채널을 통한 송신을 위해 무선 주파수(RF) 반송파에 대한 위상 변조되거나 주파수 변조될 수 있다.

엔코딩된 파형에 비트 극성 변화가 존재할 때, 블록(710)에 도시된 것처럼, 평형 변조기는  $0^\circ$  또는  $180^\circ$  위상 반전될 상기 극성 변화를 반송파( $F_c$ )에 전달한다. 이러한 이진위상 편이된 신호는 주기적인 위상 반전을 갖는 일정한 엔별로프 신호를 갖기 위해서 이진위상 변조기의 출력에 결합된다. 다음으로, 이 신호는 대역통과 필터(720)에 인가되고, 상기 대역통과 필터(720)는 입력 파형에 대한  $90^\circ$  위상 편이를 제공한다. 이점에 있어서, 만약 구형파(하나는 높고 하나는 낮은 비트)가 대역통과 필터를 통과한다면, 최대 또는 최소 진폭 지점은 비트 구간의 중심에 해당할 것이다.

VAC 엔코딩된 신호의 수신기는 대역 신호 성분을 제거하기 위해 입력 선형 위상 지연 대역통과 필터를 포함한다. 이 대역통과 필터 다음에는 송신기에서 저역 적분기 필터에 의해 상기 신호에 포함된  $90^\circ$  위상 편이를 반전시키는 미분기가 수반된다. 이러한 반전 동작은 수신된 파형에 있는 정보를 전압 최고 지점으로부터 비트 극성 변화 지점으로 복구한다. 미분기 다음에는 송신기에서 생성된 3개의 사인 주파수 신호에 대해 제로 교차점 검출기로서 동작하는 직교 위상 검출기와 제한 증폭기가 수반된다. 이러한 세 신호는 VAC 엔코딩 처리에 의해 발생된 세 반송파에 대응하고, 상기 VAC 엔코딩 처리는 비트 폭을 증가시키거나, 비트 폭을 감소시키거나, 또는 이전에 논의된 바와 같이 비트 폭을 불변적인 상태로 유지한다. 제로 교차점은 다른 주파수에서도 발생하기 때문에, 검출기의 출력은 송신된 엔코딩 신호에 대응하는 가변 비트 폭을 갖는 NRZ 신호일 것이다. 이 신호는 원래의 송신된 NRZ 데이터를 복제하기 위해 적당한 비트 시퀀스를 재설정하도록 디코더에 인가된다.

도 2는 본 발명의 원리에 따른 가변 애퍼처 코더를 도시하고 있다. VAC 엔코딩될 입력 NRZ 비트스트림은 예를 들어 제2 플립-플롭(212)에 직렬접속된 공업용 7474 플립-플롭인 제1 플립-플롭(210)의 "D" 입력단에 인가된다. 이 플립-플롭의 출력은 도시된 바와 같이 배열된 논리 네트워크에 연결되는데, 상기 논리 네트워크는 exclusive-OR 논리 게이트(216 및 226)(7486 타입), 인버터(218), AND 게이트(220 및 222), OR 게이트(224), 논리 고속 카운터(230), J-K 플립-플롭(236), 및 클럭 출력을 관련 회로(210, 212 등)의 클럭 입력단에 제공하는 9분배 주파수 분배기(divide-by-nine frequency divider)(240)를 포함한다.

ex-OR 게이트(216)와 함께 플립-플롭(210 및 212)은 입력 데이터스트림에서 "0"에서 "1"로 또는 "1"에서 "0"으로의 논리 레벨 천이가 있는지를 결정한다. 플립-플롭(210 및 212)과 함께 게이트(220, 222, 224), 인버터(218) 및 ex-OR 게이트(226)는 플립-플롭(210 및 212)에서 비트마다 비교를 수행하기 위해 사용되는 클럭 속도의 10배인 클럭 주파수로 클럭된 고속 카운터(230)의 주파수 분배율(8, 4, 2, 1)을 설정한다. VAC 엔코딩된 데이터스트림(도 5 및 도 6)은 유닛(236)의 출력에 나타난다.

도 3은 도 5 및 도 6에 도시된 비트 폭 변동을 수행하는 고속 카운터(230)를 제어하기 위해, 도 2의 네트워크에 사용되는 여러 주파수 분배기 인자를 생성하도록 도 2의 네트워크에 사용되는 엔코더 논리를 도시한다. 카운터(230)의 출력이 J-K 플립-플롭(236)을 통과함으로써 플립-플롭(236)의 출력은 도 5 및 도 6에서 도시된 바와 같은 엔코딩된 파형의 비트 구간의 중간에서 원래의 NRZ 비트스트림 파형의 비트 천이를 나타낸다.

도 6은 플립-플롭(210)의 입력에 인가될 때 VAC 엔코딩될 입력 NRZ 데이터스트림과 도 2에서 플립-플롭(236)의 출력 단에서 발생되는 것과 같은 대응하는 출력 엔코딩된 데이터 파형을 도시한다. 도 6에서, 엔코딩된 데이터 파형은 9 클럭 주기의 공칭(nominal) 비트 폭을 나타낸다. 이러한 공칭 비트 폭은 입력 NRZ 파형의 논리 레벨이 변하지 않을 때 불변적인 상태로 존재한다. 입력 NRZ 파형이 시간(T1)에서 논리 레벨 "1"에서 "0"으로 변할 때, 출력 엔코딩된 데이터스트림에 있는 관련 비트(비트 1)의 폭은, 도 5의 VAC 엔코딩된 데이터 파형에 도시된 바와 같이, 8 클럭 주기 폭의 비트 폭을 생성하기 위해 1 클럭 주기 감소된다. 즉, 비트 폭은 공칭 비트 구간의 1/9만큼 감소된다. 입력 NRZ 파형이 예를 들어 시간(T2)을 포함하는 구간 동안 불변적인 상태로 존재할 때, 관련 비트(비트 2)의 폭은 9 클럭 주기를 포함하는 공칭 비트 폭으로부터 불변적인 상태로 존재한다. 입력 NRZ 파형이 시간(T3)에서 논리 레벨 "0"에서 "1"로 변할 때, 출력 엔코딩된 데이터스트림에서 관련 비트(비트 3)의 비트 폭은 10 클럭 주기의 넓은 비트 폭을 생성하기 위해 1 클럭 주기 증가된다. 즉, 비트 폭은 공칭 비트 구간의 10/9로 증가된다.

도 4는 수신기에서의 디코더(400)를 도시하고 있다. 제로 교차 검출기로부터 수신된 가변 비트 폭 비트스트림은 D-타입 플립-플롭(410)에 의해 수신기의 클럭과 동기된다. 플립-플롭(410)과 exclusive-OR 논리 게이트(412)를 포함하는 네트워크를 통해 예지 검출이 이루어지는데, 상기 네트워크는 데이터(예지) 천이를 추적한다. 게이트(412)로부터의 출력 신호는 NRZ 데이터 송신속도의 72 배로 클럭되는 7-비트 카운터(416)를 리셋하기 위해 사용된다. 카운터(416)의 출력은, 유닛(416)이 카운트 80에 도달하는 때를 나타내는 검출기(420)에 인가된다. 이러한 상황은 논리 "1" 레벨이 후속하는 논리 "0"의 수신을 나타내는 독특한 카운트를 나타낸다. 검출기(420)로부터의 이 신호는 7-비트 카운터(422)를 리셋시킨다. ex-OR 게이트(412)의 출력은 검출된 예지를 나타내고, 카운터(422)를 로딩하기 위해 사용된다. 카운터(422)는, 리셋된

후에, "32"(4×8 클럭)로 카운트하고 다시 리셋된다. 이러한 동작은 다음 데이터 비트의 시작단과 카운터를 재동기시킨다. 새로운 상수가 모든 검출된 에지에서 유닛(432)으로부터 카운터(422)에 로딩된다. 만약 검출된 에지가 리셋 후에 카운트 32{검출기(428)에 의해 결정됨}에서 발생한다면, "88"의 값(128-40)이 유닛(432)으로부터 카운터(422)에 로딩된다. 만약 에지가 리셋하고 나서 "40" 카운트{검출기(430)에 의해 결정됨} 후에 검출된다면, 상수 값 "96"이 유닛(432)으로부터 카운터(422)에 로딩된다. 카운터(422)의 제로점이 다음 엔코딩된 데이터 비트의 처음에 나타나도록 하기 위해 상기 로딩된 상수 값("88" 또는 "96")이 선택된다. R-S 플립-플롭(440)은 "32" 카운트 또는 "40" 카운트 중 어느 것이 유닛(422, 428 및 430)에 의해 검출되는지에 따라 셋(S) 또는 리셋(R)된다. 플립-플롭(440)의 출력은 디코더(400)의 NRZ 출력이다. 상기 상수의 용도는 프로그램 가능한 카운터 세팅을 통해 단일 카운터가 디코딩된 펄스열의 서로 다른 폭을 디코딩할 수 있도록 하는데 있다. 이러한 구성이 없다면, 별도의 카운터들이 결정을 내리기 위해 사용되어야 할 것이다.

본 발명의 확산 스펙트럼 구현이 아래에서 논의된다. 도 7 및 도 8은 본 발명에 따른 사용에 적합한 확산 스펙트럼 송신기와 수신기 장치를 각각 나타낸다. 도 7의 송신기에서, 도 2의 엔코더(200)로부터의 VAC 엔코딩된 데이터는 평형 변조기(710)의 한 입력에 인가되고, 상기 평형 변조기의 다른 입력은 주파수( $f_c$ )로 반송파를 수신한다. 유닛(710)으로부터의 변조된 신호는 엔코딩된 VAC 정보와 성분( $f_c + f_b$ )을 추출하기 위해 필터(720)에 의해 저역통과 필터링된다. 필터 출력 신호는 믹서(722)의 한 입력단에 인가되고, 상기 믹서의 다른 입력단은 믹서(724)로부터  $f_{RF} + PN$  신호를 수신한다. PN 신호, 즉 확산 스펙트럼 실행에 따른 의사불규칙(pseudorandom) 잡음 신호가 공지된 것과 같은 PN 발생기 및 차동 엔코더(differential encoder)(728)에 의해 제공된다. PN 발생기와 차동 엔코더는 확산 스펙트럼 시스템의 생성에 필수적이다. 믹서(722)로부터의 출력 신호는 RF 성분( $f_{RF}$ )과 확산 스펙트럼 실행에 따른 의사불규칙 잡음 성분(PN), 및 VAC 엔코딩된 정보로 구성된다. 주파수( $f_{TX}$ )로 송신될 이러한 신호는 송신 인터페이스와 출력 네트워크(도면의 간략성을 위해 미도시)를 통해 송신 안테나(734)에 인가된다. 국부 클럭 생성기(740)는 유닛(728)에는 확산 클럭을 제공하고 엔코더(200)에는 데이터 클럭을 제공한다.

예를 들어 902 Mhz-928 Mhz 대역으로의 송신을 위한 900 Mhz 시스템의 경우에, 다음의 신호 특성이 적용된다:

$$f_{TX} : f_{RF} + PN + f_c + f_b \quad (f_{TX}=905 \text{ Mhz}, f_{RF}=894.25 \text{ Mhz} \text{ 인 경우에})$$

NRZ 데이터 : 1.5 Mbps

$f_c$  : 10 Mhz

$f_b$  : 710 Khz, 750 Khz, 794 Khz

$f=f$  : 84 Khz

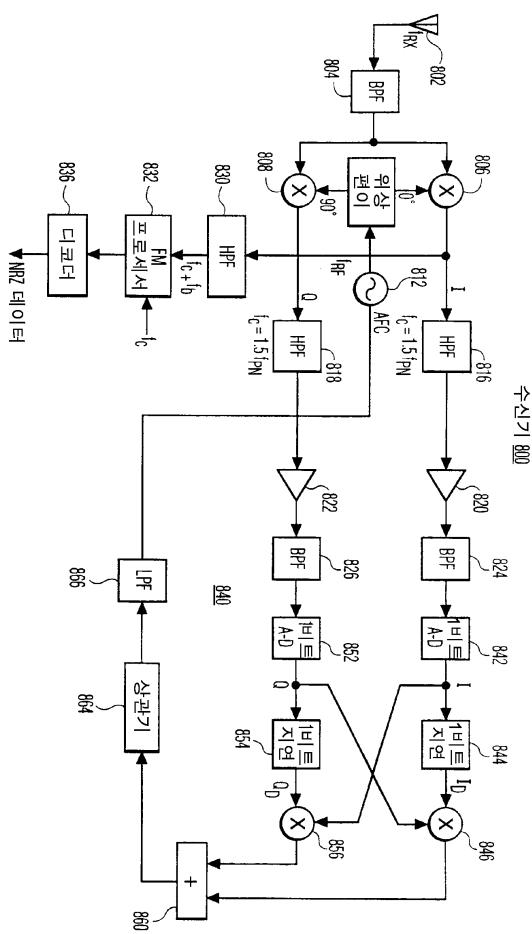

도 8의 확산 스펙트럼 수신기(800)에 있어서, 안테나(802)로부터의 수신된 신호는 대역 밖의 신호 성분을 저지하기 위해 필터(804)를 통해 대역통과 필터링된다. 필터링된 신호는 전력 분할기(미도시)에 의해 두 경로로 분할되기 이전에 저잡음 증폭기(도면의 간략성을 위해 미도시)를 통해 증폭된다. 분할된 신호는 믹서(806 및 808)의 입력단에 인가된다. 믹서에는 국부 발진기(812)와 위상 편이기(808)를 포함하는 네트워크로부터 상호 직교 위상형태인 입력 신호가 각각 제공된다. 국부 발진기 신호( $f_{RF}$ )의 주파수는 수신된 신호를 기저대역으로 다운변환하기 위해 사용된다.

믹서(806 및 808)로부터의 기저대역 직교 출력 신호는, 75 db의 이득과 거의 65 db의 이득 제어 범위를 갖는 이러한 신호들을 통과시키기 전에, DC로부터 거의 30 Khz의 주파수 성분을 제거하기 위해서 유닛(816 및 818)을 통해 각각 고역 필터링된다. 가변 이득 증폭기는 기저 대역 신호에 이득을 제공하는데, 상기 신호는 예를 들어 수신될 때 약하게 수신되고 국부 발진기와의 혼합을 통해 기저대역으로 변환되고 나서, 거의 1 V까지 증폭된다. 이득 제어는 인입 신호가 왜곡되는 것을 방지하기 위해 필요하다. 제어 신호는 마이크로컨트롤러(도면의 간략성을 위해 미도시)로부터 유도된다. 블록(820)에서 스위칭된 필터 커패시터는 PN 코드의 치핑율(chipping rate)에 따라 저역 통과 차단 주파수를 조정한다. 대역통과 필터의 통과대역 내에는, 기본 PN 코드, 송신 및 수신 국부 발진기의 비-동기 특징으로 인한 도플러 주파수, 및 송신기 전압 제어된 발진기(VCO) 상의 가변 애피쳐 신호로 인한 주파수 편이변조(FSK) 신호가 존재할 것이다. 이 FSK 신호는 모든 PN 신호에 대해 필터링되고 쌍-극 대역통과 필터(830)에 인가된다. 고역통과 필터(830)의 출력은 종래 타입의 FM 수신기/복조기 네트워크(832)에 인가되고, 상기 네트워크에서 입력 신호는 10.7 Mhz로 업변환되고, 대역통과 필터링되고, 대역 제한되며, 직교 검출된다. 네트워크(832)의 직교 검출기는 수신된 신호의 전압 최고점을 제로 교차 검출을 통해 비트 극성 변

화로 변환한다. 네트워크(832)의 검출기 출력은, 송신기로부터의 세 주파수에 대한 제로 교차점이 상기 검출기와 관련된 직교 코일의 판별기 "S" 곡선 상의 다른 점에 발생하기 때문에, 다른 펄스 폭을 나타낼 것이다. 이 검출기의 출력은 예를 들어 도 4에 도시된 바와 같이 가변 애피쳐 디코더(836)에 제공되고, 상기 가변 애피쳐 디코더는 원래의 NRZ 데이터 패형을 복구한다.

가변 이득 증폭기(820 및 822)로부터의 출력 신호는 필터(824 및 826)와 확산 스펙트럼 복조기 네트워크(840)에 인가되거나 전에 진폭 제한된다. 확산 스펙트럼 복조기는 종래 타입의 복조기일 수 있고, 본 예에서는 1-비트의 아날로그/디지털 변환기(842), 동위상 "I" 신호 경로에 있는 1 비트 지연기(844)와 곱셈기(846), 1-비트 아날로그/디지털 변환기(852), 동위상 "Q" 신호 경로에 있는 1 비트 지연기(854)와 곱셈기(856), 결합기(860), 상관기(864), 및 저역통과 필터(866)를 포함한다. 곱셈기(846)는 Q 경로 신호와 지연기(844)로부터의 지연된 I 경로 신호의 "내적(Q·I)"을 출력으로 생성한다. 마찬가지로, 곱셈기(856)는 내적 신호(I·Q)를 출력으로 생성한다. 이러한 I 및 Q 신호의 내적은 상기 I 및 Q 신호로부터 도플러 주파수 편이를 제거하기 위해 반송파 디로테이션(carrier derotation)을 지원한다. 상관기는 인입 PN 코드에 대해 선행하거나(advanced) 또는 지연(retarded) 적일 수 있는 국부적으로 생성된 PN 기준에 반응한다. 수신된 확산 코드는 상관기(864)에서 기준 PN 코드와 비교된다. 국부 PN 코드는 공지된 회로를 사용하여 인입 PN 코드와의 최대 상관관계를 획득하기 위해 선행하거나 지연적이다. I 및 Q의 두 채널에 있는 필터(824, 826)는 기저대역 신호를 필터링하기 위한 기저대역 필터이다. 상관기(864)로부터의 출력 펄스는 국부 확산 클럭 발진기(812)의 자동 주파수 제어(AFC)에 적절한 신호를 발생시키기 위해 유닛(866)을 통해 저역통과 필터링된다. 유닛(864)은 송신기 및 수신기가 동기되도록 하기 위해 인입 PN 시퀀스의 위상과 상관관계에 있다. 확산 클럭 및 데이터 클럭은, 일단 확산 클럭이 획득되고 데이터 클럭이 또한 획득되도록 하기 위해, 동일한 기준으로부터 모두 유도된다. 송신기와 수신기의 동기는 이러한 방식으로 달성된다. 국부 클럭 생성기는 상관기(864)에 확산 클럭을 제공하고 디코더(836)에는 데이터 클럭을 제공한다. 확산 클럭은 수신된 PN 시퀀스와 완전히 동기된 국부 PN 시퀀스를 갖는 클럭의 위상이다. 동기를 달성하기 위해서, 국부 PN 클럭의 위상은 신호가 최대한으로 상관적일 때까지 선행하거나 또는 지연되어야 한다.

네트워크(840)는 FSK, MSK, PSK 및 QPSK 변조에 대해 매우 효과적인 복조기이다. 거의 모든 이러한 변조 시스템은 상업적으로 유용한 전류 확산 스펙트럼 구현에서 사용된다.

### 산업상 이용 가능성

개시된 것 이외의 임의의 타입의 확산 스펙트럼을 갖는 압축된 데이터스트림을 사용하는 송신기 및 수신기 확산 스펙트럼 신호 처리 구성은 본 발명의 원리에 따라 가변 애피쳐 코딩/디코딩과 함께 사용될 수 있다. 예를 들어, 제로 중간 주파수(IF)나 단일/이중 변환 구조가 수신기에서 사용될 수 있고, 직접 구동구조나 또는 혼합 및 구동 구조가 송신기에 사용될 수 있다. 비록 900 Mhz 반송파 주파수로 동작하는 시스템의 예가 제공되고 있지만, 50 KHz 이상의 반송파 주파수를 갖는 구현이 또한 사용될 수 있다.

### (57) 청구의 범위

#### 청구항 1.

입력 디지털 데이터스트림을 처리하는 시스템에서, 상기 입력 신호의 논리 상태를 포함하는 파라미터에서의 변화에 대한 함수에 따라 코딩된 출력 신호를 생성하는 방법에 있어서,

상기 입력 신호가 상기 파라미터의 무변화(no change)를 나타낼 때, 미리 결정된 지속기간(duration)을 갖는 제 1 펄스 폭 코딩된 비트를 생성하는 단계,

상기 입력 신호가 상기 파라미터에서의 제 1 타입의 변화를 나타낼 때, 제 2 펄스 폭 코딩된 비트를 생성하는 단계, 및

상기 입력 신호가 상기 파라미터에서의 제 2 타입의 변화를 나타낼 때, 제 3 펄스 폭 코딩된 비트를 생성하는 단계를 포함하며, 여기서

상기 제 1 비트 내지 제 3 비트는 서로 다른 비트인, 코딩된 출력 신호를 생성하는 방법.

#### 청구항 2.

제 1항에 있어서, 상기 파라미터는 상기 입력 신호에 대한 논리 상태의 변화이고, 상기 제 1 타입의 변화는 제 1 방향으로의 논리 상태 변화이고, 제 2 타입의 변화는 다른 제 2 방향으로의 논리 상태 변화인, 코딩된 출력 신호를 생성하는 방법.

### 청구항 3.

제 1항에 있어서, 상기 제 1 코딩된 비트를 생성하는 단계는 미리 결정된 기준 비트 폭을 갖는 제 1 코딩된 비트를 생성하고,

상기 제 2 코딩된 비트를 생성하는 단계는 상기 기준 비트 폭에 대해 비트 폭에 있어서의 제 1 미리 결정된 변화를 갖는 제 2 코딩된 비트를 생성하고,

상기 제 3 코딩된 비트를 생성하는 단계는 상기 기준 비트 폭에 대해 비트 폭에 있어서의 제 2 다른 미리 결정된 변화를 갖는 제 3 코딩된 비트를 생성하는, 코딩된 출력 신호를 생성하는 방법.

### 청구항 4.

제 3항에 있어서, 상기 제 2 코딩된 비트를 생성하는 단계는, 상기 입력 신호가 한 방향으로의 논리 상태 변화를 나타낼 때, 상기 기준 비트 폭에 대해 비트 폭에 있어서의 미리 결정된 증가를 갖는 제 2 코딩된 비트를 생성하고,

상기 제 3 코딩된 비트를 생성하는 단계는, 상기 입력 신호가 다른 방향으로의 논리 상태 변화를 나타낼 때, 상기 기준 비트 폭에 대해 비트 폭에 있어서의 미리 결정된 감소를 갖는 제 3 코딩된 비트를 생성하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 5.

제 3항에 있어서, 상기 제 1 코딩된 비트를 생성하는 단계는, 상기 입력 신호가 논리 상태 변화를 나타내지 않을 때, 미리 결정된 수의 클럭 주기를 포함하는 제 1 코딩된 비트를 생성하고,

상기 제 2 코딩된 비트를 생성하는 단계는, 상기 입력 신호가 한 방향으로의 논리 상태 변화를 나타낼 때, 미리 결정된 클럭 주기 증가를 포함하는 제 2 코딩된 비트를 생성하고,

상기 제 3 코딩된 비트를 생성하는 단계는, 상기 입력 신호가 다른 방향으로의 논리 상태 변화를 나타낼 때, 미리 결정된 클럭 주기 감소를 포함하는 제 3 코딩된 비트를 생성하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 6.

제 5항에 있어서, 상기 제 1 코딩된 비트는 N 개의 미리 결정된 클럭 주기를 포함하고, 상기 제 2 코딩된 비트는 N+1 개의 클럭 주기를 포함하며, 제 3 코딩된 비트는 N-1 개의 코딩된 클럭 주기를 포함하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 7.

제 6항에 있어서, N은 15보다 작은 수인, 출력 코딩된 신호를 생성하는 방법.

### 청구항 8.

제 1항에 있어서, 확산 스펙트럼 시스템을 통해 상기 코딩된 출력 신호를 처리하는 단계를 더 포함하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 9.

제 8항에 있어서, 상기 처리 단계는,

변조된 신호를 생성하기 위해 반송파 상에 상기 코딩된 출력 신호를 변조하는 단계,

확산 스펙트럼 신호를 생성하기 위해 의사랜덤 잡음 신호(pseudorandom noise signal)와 상기 변조된 신호를 혼합하는 단계, 및

상기 확산 스펙트럼 신호를 송신하는 단계를 포함하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 10.

제 9항에 있어서, 상기 혼합 단계에 앞서 상기 변조된 신호를 저역통과 필터링하는 단계를 더 포함하는, 출력 코딩된 신호를 생성하는 방법.

### 청구항 11.

수신된 비트스트림의 파라미터의 변화를 나타내는 제 1, 제 2, 및 제 3 펄스 폭 코딩된 비트를 포함해야 하는 상기 수신된 비트스트림으로부터 디코딩된 데이터스트림을 생성하는 디코딩 방법에 있어서,

미리 결정된 지속기간의 제 1 코딩된 비트에 반응하여, 상기 파라미터의 무변화를 나타내는 제 1 데이터 성분을 생성하는 단계,

상기 제 2 코딩된 비트에 반응하여, 상기 파라미터의 제 1 타입의 변화를 나타내는 제 2 데이터 성분을 생성하는 단계, 및

상기 제 3 코딩된 비트에 반응하여, 상기 파라미터의 다른 제 2 타입의 변화를 나타내는 제 3 데이터 성분을 생성하는 단계

를 포함하는, 디코딩된 데이터스트림을 생성하는 디코딩 방법.

### 청구항 12.

제 11항에 있어서, 상기 파라미터는 출력 데이터스트림의 논리 상태이고, 상기 제 1 데이터 성분은 상기 논리 상태의 무변화를 나타내고, 상기 제 2 데이터 성분은 한 방향으로의 상기 논리 상태의 변화를 나타내며, 상기 제 3 데이터 성분은 다른 방향으로의 상기 논리 상태의 변화를 나타내는, 디코딩된 데이터스트림을 생성하는 디코딩 방법.

### 청구항 13.

제 11항에 있어서, 상기 제 1 코딩된 비트는 N 개의 미리 결정된 클럭 주기를 포함하고, 상기 제 2 코딩된 비트는 N+1 개의 클럭 주기를 포함하며, 상기 제 3 코딩된 비트는 N-1 개의 클럭 주기를 포함하는, 디코딩된 데이터스트림을 생성하는 디코딩 방법.

## 청구항 14.

제 11항에 있어서, 주파수 다운변환된 비트스트림을 생성하기 위해 기준 신호와 상기 수신된 비트스트림을 혼합하는 단계,

복조된 신호를 생성하기 위해 상기 다운변환된 비트스트림을 주파수 복조하는 단계, 및

상기 제 1, 제 2 및 제 3 데이터 성분을 생성하기 위해 상기 생성 단계들에 따라 상기 복조된 신호를 디코딩하는 단계

를 더 포함하는, 디코딩된 데이터스트림을 생성하는 디코딩 방법.

## 청구항 15.

제 11항에 있어서, 상기 혼합 단계는, 서로 직교하는 위상 신호를 생성하기 위해 상기 수신된 비트스트림을 위상 편이시키는 단계,

제어 신호를 생성하기 위해 확산 스펙트럼 복조기를 통해 상기 직교 신호를 처리하는 단계, 및

상기 혼합 단계에 상기 제어 신호를 인가하는 단계

를 포함하는, 디코딩된 데이터스트림을 생성하는 디코딩 방법.

## 도면

도면1

도면2

도면3

$$\begin{array}{l}

1 \rightarrow 0 : 4, 2, 1 : \left\{ \begin{array}{l} H \\ L \end{array} \right\} 8 \text{로 분배} \\

0 \rightarrow 1 : 8, 1 : \left\{ \begin{array}{l} H \\ L \end{array} \right\} 10 \text{으로 분해} \\

0 \rightarrow 0 : 8 \\

1 \rightarrow 1 : 4, 2, 1 : \left\{ \begin{array}{l} H \\ L \end{array} \right\} 9 \text{로 분배} \\

(\text{무변화})

\end{array}$$

| 상태        | ÷ | 8 | 4 | 2 | 1 |

|-----------|---|---|---|---|---|

| (A) 1 → 0 | - | X | X | X | X |

| (B) 0 → 1 | X | - | - | - | X |

| (C) 0 → 0 | X | - | - | - | - |

| (C) 1 → 1 | X | - | - | - | - |

도면4

도면5

도면6

도면7

도면8