(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5922317号

(P5922317)

(45) 発行日 平成28年5月24日(2016.5.24)

(24) 登録日 平成28年4月22日(2016.4.22)

(51) Int.Cl.

G06F 12/10 (2016.01)

G06F 12/08 (2016.01)

F 1

G06F 12/10 501Z

G06F 12/08 507B

G06F 12/10 551B

請求項の数 21 (全 25 頁)

(21) 出願番号 特願2015-552800 (P2015-552800)

(86) (22) 出願日 平成26年1月10日 (2014.1.10)

(65) 公表番号 特表2016-507096 (P2016-507096A)

(43) 公表日 平成28年3月7日 (2016.3.7)

(86) 國際出願番号 PCT/US2014/011027

(87) 國際公開番号 WO2014/113286

(87) 國際公開日 平成26年7月24日 (2014.7.24)

審査請求日 平成28年2月3日 (2016.2.3)

(31) 優先権主張番号 13/741,981

(32) 優先日 平成25年1月15日 (2013.1.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】変換索引バッファ(TLB)のための重複検査

## (57) 【特許請求の範囲】

## 【請求項1】

変換索引バッファを管理する方法であって、前記方法は、

入力仮想アドレスと入力ページサイズ指標とを変換索引バッファ(TLB)において受け取ることと、前記入力仮想アドレスおよび前記入力ページサイズ指標は、入力ページに対応し、

前記入力ページサイズ指標によって表される入力ページサイズと前記TLBのエントリのエントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定することと、ここにおいて、前記TLBの前記エントリは、エントリページに対応し、

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を第1の選択されたページサイズとして選択することと、

前記第1の選択されたページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとの第1のマスクされた比較を実行することと、

前記第1のマスクされた比較を実行した後、前記TLBが未調査のエントリを含む決定に基づいて、前記TLBによって、第2のマスクされた比較を選択的に実行することと、

を備える方法。

## 【請求項2】

前記第1のマスクされた比較を実行することが、前記入力仮想アドレスと前記エントリ仮想アドレスとの両方の、マスクされるべきビット

トの数を決定することと、前記ビットの数は、前記第1の選択されたページサイズに基づき、

前記入力ページが前記エントリページに重複するかを決定することと

を含む、請求項1に記載の方法。

**【請求項3】**

前記TLBが前記未調査のエントリを含むと決定した後で、

前記入力ページサイズと第2のエントリページサイズとのうちの大きい方を識別するためには、前記TLBの第2のエントリの第2のエントリページサイズ指標と前記入力ページサイズ指標とを比較することと、ここにおいて、前記TLBの前記第2のエントリは、第2のエントリページに対応し、

前記入力ページサイズと前記第2のエントリページサイズとのうちの前記識別された大きい方を第2の選択されたページサイズとして選択することと、

前記入力ページが前記第2のエントリページに重複するかを決定するために、前記第2の選択されたページサイズに基づいて、前記入力仮想アドレスと前記第2のエントリの第2のエントリ仮想アドレスとの前記第2のマスクされた比較を実行することと、ここにおいて、前記第2のマスクされた比較を実行することは、前記第2の選択されたページサイズに基づいて、前記入力仮想アドレスと前記第2のエントリ仮想アドレスとの両方の、マスクされるべきビットの第2の数を決定することを含む、

をさらに備える、請求項1に記載の方法。

**【請求項4】**

前記第1の選択されたページサイズは、前記第2の選択されたページサイズと異なり、前記第1の選択されたページサイズは、前記入力ページサイズに対応し、前記第2の選択されたページサイズは、前記第2のエントリページサイズに対応する、請求項3に記載の方法。

**【請求項5】**

前記第2のエントリページサイズ指標と前記入力ページサイズ指標とを比較することに先立って、前記第2のエントリページを前記TLBの未調査のエントリとして識別することをさらに備える、請求項3に記載の方法。

**【請求項6】**

重複検査命令を実行するように構成されたプロセッサと、前記重複検査命令は、入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを含み、前記プロセッサは、

少なくとも1つのエントリを備える変換索引バッファ(TLB)と、前記少なくとも1つのエントリは、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを含み、

前記入力ページサイズ指標と前記入力仮想アドレスとを受け取るように構成された入力ロジックと、

前記入力ページサイズ指標によって表される入力ページサイズと前記エントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定し、

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を選択されたページサイズとして選択し、

前記選択されたページサイズに基づいて、前記重複検査命令の結果を決定し、ここにおいて、前記結果は、前記入力ページが前記エントリページに重複するかに基づき、

前記重複検査の前記結果が決定された後で、前記TLBが、前記TLBは未調査のエントリを含む決定に基づいて、第2の重複検査の第2の結果を選択的に決定する

ように構成された重複検査ロジックと

を含み、

前記重複検査ロジックから1つまたは複数の結果を受け取るように構成されたレジスターと

を備える装置。

**【請求項7】**

10

20

30

40

50

前記少なくとも 1 つのエントリが、アプリケーション空間識別子（A S I D）とグローバル指標とをさらに含み、前記入力ロジックが、入力 A S I D を受け取るようにさらに構成され、ここにおいて、前記重複検査ロジックが、

第 1 の値を有する前記グローバル指標に応答して、前記 A S I D と前記入力 A S I D との比較に基づいて、前記入力ページが前記エントリページに重複するかを決定し、

第 2 の値を有する前記グローバル指標に応答して、前記 A S I D と前記入力 A S I D とは無関係に、前記入力ページが前記エントリページに重複するかを決定する

ようにさらに構成される、請求項 6 に記載の装置。

#### 【請求項 8】

前記入力ページサイズ指標が、第 1 のマスクまたは前記入力ページサイズによって表され、前記エントリページサイズ指標が、第 2 のマスクまたは前記エントリページサイズによって表される、請求項 6 に記載の装置。 10

#### 【請求項 9】

前記少なくとも 1 つのエントリが、前記エントリ仮想アドレス、アプリケーション空間識別子（A S I D）、キャッシュ可能指標、許可指標、グローバル指標、またはこれらの任意の組み合わせにマッピングされる物理アドレスを含む、請求項 6 に記載の装置。

#### 【請求項 10】

前記重複検査ロジックは、前記プロセッサに記憶された専用の重複検査ロジックを含む、請求項 6 に記載の装置。

#### 【請求項 11】

重複検査命令を実行する方法であって、前記方法は、

プロセッサにおいて重複検査命令を実行することと、ここにおいて、前記重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、前記重複検査命令を実行することは、

前記入力ページサイズ指標によって表される入力ページサイズと変換索引バッファ（T L B）のエントリのエントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定することと、

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を第 1 の選択されたページサイズとして選択することと、

前記入力ページがエントリページに重複するかを決定するために、前記第 1 の選択されたページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとのマスクされた比較を実行することと、

前記マスクされた比較を実行した後、前記 T L B が未調査のエントリを含む決定に基づいて、前記 T L B によって、第 2 のマスクされた比較を選択的に実行することと、

前記入力ページが前記エントリページに重複するかの前記決定に基づいて、および前記 T L B が前記未調査のエントリを含まない前記決定に基づいて、実行結果を出力することと

を含み、

前記実行結果に基づいて、前記 T L B を選択的に更新することと、ここにおいて、前記 T L B を選択的に更新することは、前記実行結果が重複を示さないことに応答して、前記入力ページサイズ指標と前記入力仮想アドレスとを前記 T L B の第 2 のエントリに書き込むことを含む、

を備える、方法。

#### 【請求項 12】

前記実行結果に基づいて、前記 T L B を選択的に更新することをさらに備え、前記 T L B を選択的に更新することは、前記実行結果が重複を示すことに応答して前記 T L B を維持することを含み、前記実行結果は、ブール出力を備える、請求項 11 に記載の方法。

#### 【請求項 13】

前記プロセッサは、前記重複検査命令を実行するために専用の重複検査ロジックを含み、前記重複検査命令を実行することは、前記実行結果を前記プロセッサのレジスタに記憶

10

20

30

40

50

することをさらに備える、請求項 1 1 に記載の方法。

**【請求項 1 4】**

条件付き変換索引バッファ書き込み命令を実行する方法であって、前記方法は、

T L B を含むプロセッサにおいて条件付き変換索引バッファ ( T L B ) 書き込み命令を実行することを備え、ここにおいて、前記 T L B は、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する第 1 のエントリを含み、前記条件付き T L B 書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、

前記条件付き T L B 書き込み命令を実行することは、

前記入力ページサイズ指標によって表される入力ページサイズと前記エントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定することと、

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を第 1 の選択されたページサイズとして選択することと、

前記入力ページが前記エントリページに重複するかを決定するために、前記第 1 の選択されたページサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされた比較を実行することと、

前記マスクされた比較を実行した後、前記 T L B が未調査のエントリを含む決定に基づいて、前記 T L B によって、第 2 のマスクされた比較を選択的に実行することと、

前記入力ページが前記エントリページに重複しないと決定することと、前記 T L B が前記未調査のエントリを含まないと決定することとに応答して、前記入力ページサイズ指標と前記入力仮想アドレスとを前記 T L B の第 2 のエントリに書き込むことと、を備える、方法。

**【請求項 1 5】**

前記条件付き T L B 書き込み命令を実行することが、前記入力ページが前記エントリページに重複すると決定することに応答して、書き込みエラーを示す実行結果を出力することをさらに備え、前記実行結果が、前記入力ページに重複する 1 つまたは複数のエントリページに対応する、前記 T L B のエントリの数を識別し、前記入力ページに重複する特定のエントリページに対応する、前記 T L B の特定のエントリ、またはこれらの組み合わせを識別する、請求項 1 4 に記載の方法。

**【請求項 1 6】**

重複検査命令を備え、

ここにおいて、前記重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、

前記重複検査命令は、変換索引バッファ ( T L B ) を含むプロセッサによって、

前記入力ページサイズ指標によって表される入力ページサイズと前記 T L B のエントリページのエントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定し、

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を選択されたページサイズとして選択し、

前記入力ページが前記エントリページに重複するかを決定するために、前記選択されたページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとのマスクされた比較を実行し、

前記マスクされた比較が実行された後、前記 T L B が未調査のエントリを含む決定に基づいて、前記 T L B によって、第 2 のマスクされた比較を選択的に実行し、

前記マスクされた比較に部分的にに基づいて、実行結果を出力する

ように実行可能である、非一時的なプロセッサ読み取可能な媒体。

**【請求項 1 7】**

前記実行結果が、前記入力ページに重複する少なくとも 1 つのエントリページに対応する、前記 T L B の少なくとも 1 つのエントリを識別する、請求項 1 6 に記載の非一時的な

10

20

30

40

50

プロセッサ読取可能な媒体。

**【請求項 1 8】**

条件付き変換索引バッファ (TLB) 書き込み命令を備え、

ここにおいて、前記条件付き TLB 書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、

前記条件付き TLB 書き込み命令は、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する第 1 のエントリを含む TLB を含むプロセッサによって、

前記入力ページサイズ指標によって表される入力ページサイズと前記エントリページサイズ指標によって表されるエントリページサイズとのうちの大きい方を決定し、10

前記入力ページサイズと前記エントリページサイズとのうちの前記決定された大きい方を選択されたページサイズとして選択し、

前記入力ページが前記エントリページに重複するかを決定するために、前記選択されたページサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされた比較を実行し、

前記マスクされた比較が実行された後、前記 TLB が未調査のエントリを含む決定に基づいて、前記 TLB によって、第 2 のマスクされた比較を選択的に実行し、

前記入力ページが前記エントリページに重複しないと決定することと、前記 TLB が前記未調査のエントリを含まないと決定することとに応答して、前記入力ページサイズ指標と前記入力仮想アドレスとを前記 TLB の第 2 のエントリに書き込む20

ように実行可能である、非一時的なプロセッサ読取可能な媒体。

**【請求項 1 9】**

前記条件付き TLB 書き込み命令は、前記プロセッサによって、前記入力ページが前記エントリページに重複すると決定することに応答して、前記 TLB 内の前記エントリページを維持するようにさらに実行可能である、請求項 1 8 に記載の非一時的なプロセッサ読取可能な媒体。

**【請求項 2 0】**

命令を変換索引バッファ (TLB) において受け取るための手段と、前記命令は、入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを含み、

前記 TLB のエントリページのエントリページサイズ指標と前記入力ページサイズ指標とのうちの大きい方を決定するための手段、30

前記入力ページサイズ指標と前記エントリページサイズ指標とのうちの前記決定された大きい方を選択されたページサイズ指標として選択するための手段と、

前記選択されたページサイズ指標に基づいて、前記入力ページが前記エントリページに重複するかを決定するために、前記入力仮想アドレスと前記エントリページに対応するエントリ仮想アドレスとの第 1 のマスクされた比較を実行し、前記第 1 のマスクされた比較が実行された後、前記 TLB が未調査のエントリを含む決定に基づいて、前記 TLB によって、第 2 のマスクされた比較を選択的に実行するための手段と

を備える、装置。

**【請求項 2 1】**

前記命令は、重複検査命令または条件付き変換索引バッファ (TLB) 書き込み命令である、請求項 2 0 に記載の装置。40

**【発明の詳細な説明】**

**【優先権の主張】**

**【0001】**

[0001]本願は、2013年1月15日に出願され、「OVERLAP CHECKING FOR A TRANSLATION LOOKASIDE BUFFER (TLB)」と題された米国非仮特許出願第13/741,981号の優先権を主張し、この出願の内容は、その全体が参照により組み込まれる。

**【技術分野】**

10

20

30

40

50

**【0002】**

[0002]本開示は、一般に、変換索引バッファ（T L B : translation lookaside buffer）の管理に関する。

**【背景技術】****【0003】**

[0003]技術における進歩は、より小さく、より強力なコンピューティングデバイスをもたらした。例えば、小型で、軽量で、ユーザによって簡単に持ち運ばれる携帯用ワイヤレス電話機、携帯情報端末（P D A）、タブレットコンピュータ、およびページングデバイスなどのワイヤレスコンピューティングデバイスを含む、様々な携帯用パーソナルコンピューティングデバイスが現在存在する。多くのそのようなコンピューティングデバイスは、そこに組み込まれる他のデバイスを含む。例えば、ワイヤレス電話機は、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレイヤも含み得る。また、そのようなコンピューティングデバイスは、インターネットにアクセスするために使用され得るウェブブラウザアプリケーション、およびスチルカメラまたはビデオカメラを利用し、マルチメディア再生機能性を提供するマルチメディアアプリケーションなどのソフトウェアアプリケーションを含む実行可能な命令を処理することができる。そのため、これらのデバイスは、典型的には、デスクトップコンピュータなどのより大きなデバイスによって実行される機能を実行することができる。

**【0004】**

[0004]ワイヤレス電話機および他のコンピューティングデバイスにおけるプロセッサなどのプロセッサは、1つまたは複数の変換索引バッファ（T L B）をしばしば含む。T L Bは、仮想アドレスと物理アドレスとの間のキャッシュ変換のために使用され得る。特定の仮想アドレスがT L B内で見つからない場合、その特定の仮想アドレスのために新たなエントリがT L B内に作成され、この新たなエントリは、対応する物理アドレス変換を含む。このエントリを作成することは、ハードウェアにおいて、またはソフトウェアによって行われ得る。あるいは、T L Bの既存のエントリは、特定の仮想アドレスについての変換情報を用いて上書きされ得る。特定の仮想アドレスが、見つかる場合、すなわち、T L Bのエントリに一致する場合、T L Bは、一致するエントリに記憶される物理アドレスを返す。

**【0005】**

[0005]データ整合性を維持するために、T L Bの複数のエントリが1つの入力仮想アドレスに一致する状況を防止することは有益であり得る。従来、この役目は、T L Bを使用するオペレーティングシステムにあった。しかしながら、プログラミング上の誤りおよび他の事情が原因で、この役目を果たすことをオペレーティングシステムに依存することは困難となり得る。また、システムには、複数のオペレーティングシステム（例えば、ハイパーバイザと通信するゲストオペレーティングシステム）を同時に実行し得るものもあり、これは、T L B管理にさらなる複雑さを導入し得る。ハイパーバイザは、（ソフトウェアによりプログラムされた）T L Bをプログラムする責任を負い得、ゲストオペレーティングシステムは、変換を定義するが、重複しない変換を作成することを任せることはできない。

**【発明の概要】****【0006】**

[0006]T L Bにおけるプロセッサレベルの（例えば、ハードウェアベースの）重複検査が開示される。T L Bは、ソフトウェアにより管理されても、またはハードウェアにより管理されてもよい。可変ページサイズの使用は、重複するページを可能にし得るため、重複検査は、可変ページサイズをサポートするシステムにおいて使用され得る。開示される技法は、ハードウェアにおいて実装され得るため、開示される技法は、ソフトウェアベースの重複検査よりも高速となり得る。

**【0007】**

[0007]1つまたは複数の命令が、開示されるハードウェアベースの重複検査技法を利用

10

20

30

40

50

するために実装され得る。例えば、重複検査命令が実装され得る。プロセッサによって実行される場合、重複検査命令は、T L B内のエントリに、特定の入力ページに重複するページに対応するものがあるかを示す出力を生成する。したがって、重複検査命令は、ある入力ページのためにT L B内に新たなエントリを生成することがT L B内の重複エントリをもたらすかを決定するために使用され得る。いくつかの実装において、重複検査命令の出力は、T L B内のいくつのエントリが入力ページに重複するかを示し得、または特定の重複エントリを示し得る。

#### 【0008】

[0008]別の例として、条件付きのT L B書き込み命令が実装され得る。条件付きT L B書き込み命令は、作成されるエントリがT L B内のいかなる既存エントリとも重複しない場合、入力ページのためにT L B内にエントリを作成し得る。エントリを作成することが重複をもたらす場合、条件付きT L B書き込み命令は、重複検査命令の出力に類似する出力を生成し得る。10

#### 【0009】

[0009]特定の実施形態において、方法は、入力仮想アドレスと入力ページサイズ指標とをT L Bにおいて受け取ることを備える。入力仮想アドレスおよび入力ページサイズ指標は、入力ページに対応する。本方法は、入力ページサイズ指標とT L Bのエントリのエントリページサイズとの比較に基づいて算出ページサイズを決定することも備え、T L Bのエントリは、エントリページに対応する。本方法は、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリ仮想アドレスとのマスクされた比較を実行することをさらに備える。20

#### 【0010】

[0010]別の特定の実施形態において、装置は、T L Bを備える。T L Bは、エントリ仮想アドレスとエントリページに対応するエントリページサイズ指標とを含む、少なくとも1つのエントリを備える。本装置は、入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを受け取るように構成された入力ロジックも備える。本装置は、エントリページサイズ指標と入力ページサイズ指標とに少なくとも一部は基づいて、入力ページがエントリページに重複するかを決定するように構成された重複検査ロジックをさらに備える。

#### 【0011】

[0011]別の特定の実施形態において、方法は、プロセッサにおいて重複検査命令を実行することを備える。重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含む。重複検査命令を実行することは、T L Bのエントリのエントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定することを含む。重複検査命令を実行することは、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリのエントリ仮想アドレスとのマスクされた比較を実行することも含む。重複検査命令を実行することは、入力ページがエントリページに重複するかの決定に基づいて、実行結果を出力することをさらに含む。30

#### 【0012】

[0012]別の特定の実施形態において、方法は、T L Bを含むプロセッサにおいて、条件付きT L B書き込み命令を実行することを備える。T L Bは、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する第1のエントリを含む。条件付きT L B書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含む。条件付きT L B書き込み命令を実行することは、エントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定することを含む。条件付きT L B書き込み命令を実行することは、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリ仮想アドレスとのマスクされた比較を実行することも含む。条件付きT L B書き込み命令を実行することは、入力ページがエントリページに重複しないと決定することに応答して、4050

入力ページサイズ指標と入力仮想アドレスとを T L B の第 2 のエントリに書き込むことをさらに含む。

**【 0 0 1 3 】**

[0013]別の特定の実施形態において、装置は、少なくとも 1 つのエントリを記憶するための手段を備える。少なくとも 1 つのエントリは、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを含む。本装置は、入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを受け取るための手段も含む。本装置は、エントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定するための手段をさらに含む。本装置は、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリ仮想アドレスとのマスクされた比較を実行するための手段を含む。10

**【 0 0 1 4 】**

[0014]別の特定の実施形態において、非一時的なプロセッサ読取可能な媒体は、重複検査命令を含む。重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含む。重複検査命令は、T L B を含むプロセッサによって、T L B のエントリのエントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定するように実行可能である。重複検査命令は、プロセッサによって、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリのエントリ仮想アドレスとのマスクされた比較を実行するようにも実行可能である。重複検査命令は、プロセッサによって、入力ページがエントリページに重複するかの決定に基づいて、実行結果を出力するようにさらに実行可能である。20

**【 0 0 1 5 】**

[0015]別の特定の実施形態において、非一時的なプロセッサ読取可能な媒体は、条件付き T L B 書き込み命令を含む。条件付き T L B 書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含む。条件付き T L B 書き込み命令は、T L B を含むプロセッサによって実行可能であり、T L B は、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する第 1 のエントリを含む。条件付き T L B 書き込み命令は、プロセッサによって、エントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定するように実行可能である。条件付き T L B 書き込み命令は、プロセッサによって、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリ仮想アドレスとのマスクされた比較を実行するようにも実行可能である。条件付き T L B 書き込み命令は、プロセッサによって、入力ページがエントリページに重複しないと決定することに応答して、入力ページサイズ指標と入力仮想アドレスとを T L B の第 2 のエントリに書き込むようにさらに実行可能である。30

**【 0 0 1 6 】**

[0016]開示される実施形態のうちの少なくとも 1 つによって提供される 1 つの特定の利点は、T L B においてプロセッサレベルの重複検査を実行するための能力であり、この能力は、潜在的に誤りのある第三者の方法（例えば、オペレーティングシステム T L B 検査）に依存することなく、コンピューティングシステムまたは電子デバイスにおける信頼性とデータ整合性とを向上させ得る。本開示の他の態様、利点、および特徴は、以下のセクションを含む出願全体のレビュー後に、より明確になるであろう：図面の簡単な説明、詳細な説明、および特許請求の範囲。40

**【図面の簡単な説明】**

**【 0 0 1 7 】**

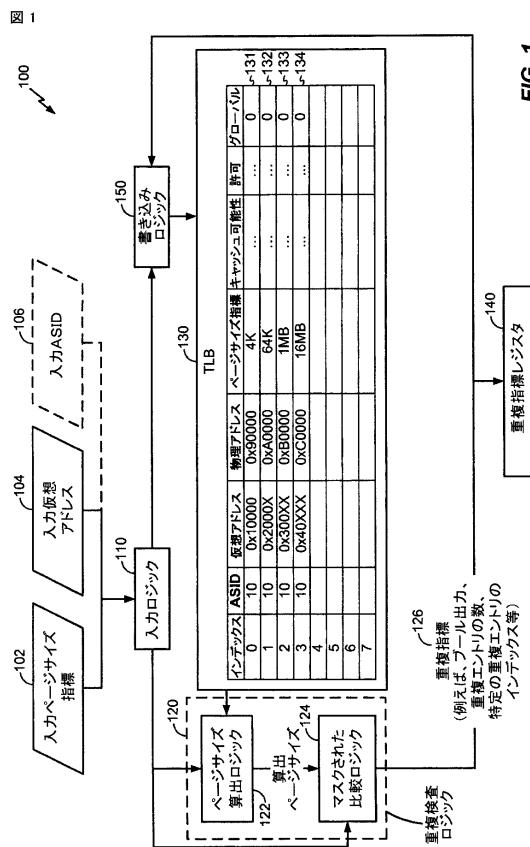

**【図 1】** [0017] T L B についての重複検査を実行するように動作可能であるシステムの特定の実施形態の図。

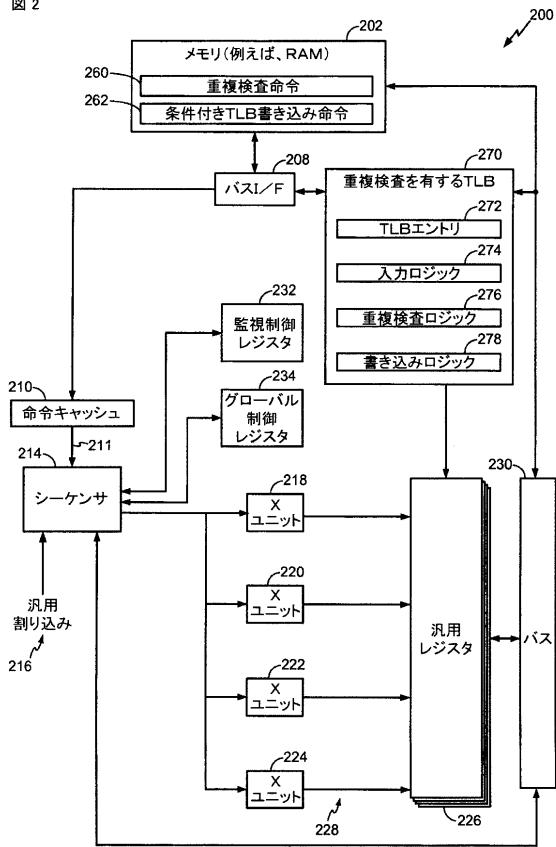

**【図 2】** [0018] T L B についての重複検査を実行するように動作可能であり、重複検査命令と条件付き T L B 書き込み命令とを実行するように動作可能であるプロセッサを含むというシステムの特定の実施形態の図。50

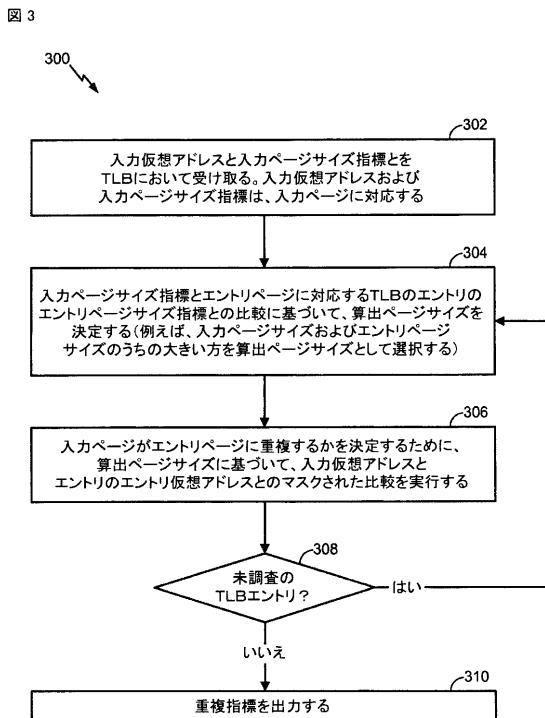

【図3】[0019] T L Bについての重複検査を実行する方法の特定の実施形態のフローチャート。

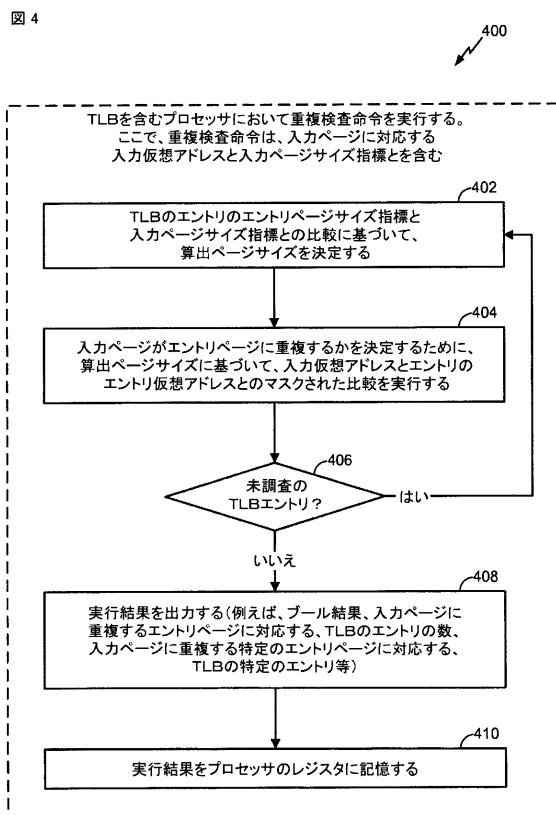

【図4】[0020]重複検査命令を実行する方法の特定の実施形態のフローチャート。

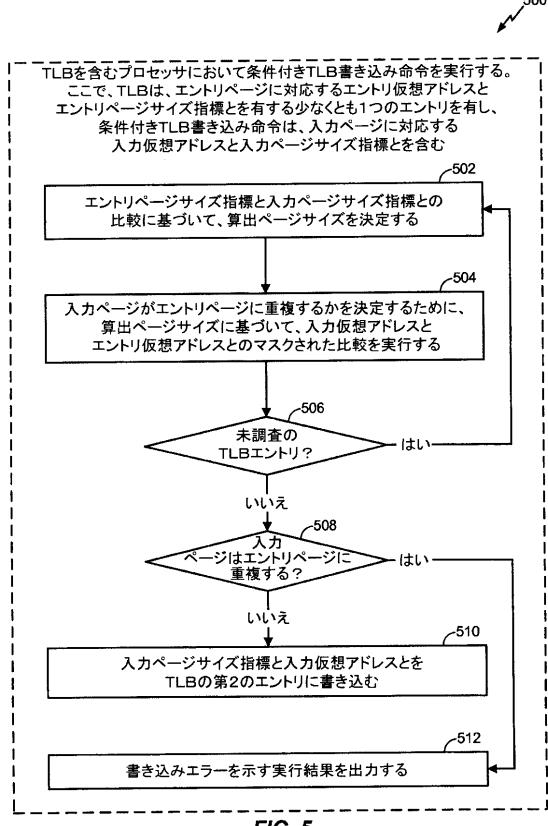

【図5】[0021]条件付きT L B書き込み命令を実行する方法の特定の実施形態のフローチャート。

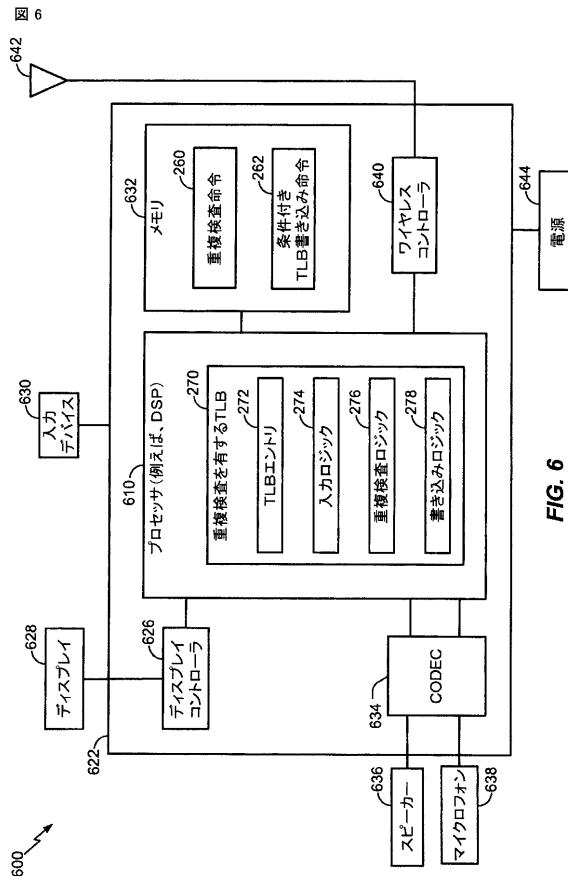

【図6】[0022]T L Bについての重複検査を実行するように動作可能な構成要素を含むワイヤレスデバイスのブロック図。

【発明を実施するための形態】

【0018】

[0023]図1は、変換索引バッファ(T L B)についての重複検査を実行するように動作可能であるシステム100の特定の実施形態の図である。システム100は、入力ロジック110と、重複検査ロジック120と、書き込みロジック150と、重複指標レジスター140とに結合されるT L B130を含む。特定の実施形態において、T L B130は、ソフトウェアにより管理されるT L Bである。あるいは、T L B130は、ハードウェアにより管理されるT L Bであってもよい。例示的な実施形態において、図1のシステム100および/またはその構成要素は、中央処理装置(C P U)またはデジタル信号プロセッサ(D S P)などのプロセッサに含まれ、または結合され得る。例えば、プロセッサは、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(P D A)、固定ロケーションデータユニット、コンピューティングデバイス、またはこれらの任意の組み合わせなどの電子デバイスに一体化され得る。10

【0019】

[0024]特定の実施形態において、入力ロジック110、重複検査ロジック120、および書き込みロジック150のうちの1つまたは複数は、ハードウェアを使用して(例えば、D S P、C P U、コントローラ、フィールドプログラマブルゲートアレイ(F P G A)デバイス、特定用途向け集積回路(A S I C)、別のハードウェアデバイス、またはこれらの任意の組み合わせによって)実装される。代替的に、または付加的に、入力ロジック110、重複検査ロジック120、および書き込みロジック150のうちの1つまたは複数は、図6を参照しつつさらに記載されるように、ソフトウェア(例えば、プロセッサによって実行可能な命令)を使用して実装され得る。20

【0020】

[0025]T L B130は、1つまたは複数のエントリを含み得る。図1において、T L B130は、第1のエントリ131と、第2のエントリ132と、第3のエントリ133と、第4のエントリ134とを含み、エントリ131～134の各々は、T L B130の行に対応する。各エントリ131～134は、仮想アドレス('V i r t . A d d r .')とページサイズ指標('P a g e S i z e I n d .')とを含み得る。例示される例において、ページサイズ指標は、実際のページサイズ(例えば、4キロバイト(K)、64 K、1メガバイト(M B)、16 M B等)を使用して表される。代替的な実施形態において、ページサイズ指標は、本明細書においてさらに記載されるように、ビットマスク('マスク'とも呼ばれる)を使用して表され得る。30

【0021】

[0026]T L B130のエントリ131～134は、仮想アドレスにマッピングされる物理アドレス('P h y s . A d d r .')も含み得る。エントリ131～134は、アプリケーション空間識別子('A S I D(application space identifier)')と、キャッシュ可能指標(例えば、エントリがキャッシュされ得るかを示す)と、許可指標('P e r m .') (例えば、読み出し許可、書き込み許可、および/またはユーザ許可)と、グローバル指標('G l o b .')とをさらに含み得る。T L B130の各エントリは、インデックスを有し得る。例えば、第1のエントリ131は、インデックス0を有し、第2のエントリ132は、インデックス1を有し、第3のエントリ133は、インデックス2を有し、第4のエントリ134は、インデックス3を有する。40

50

## 【0022】

[0027]図1の実施形態においては、32ビットのアドレス空間および4Kの最小ページサイズが例示の目的のために使用されることが留意されるべきである。したがって、(16進数の(hex)5桁に対応する)20個の最上位ビットのみが、TLB130の仮想アドレス列および物理アドレス列において表される。アドレスの(hex3桁に対応する)12個の最下位ビットは、使用されないかもしれない。なぜならば、最小ページサイズは4Kであり、そのため、12個の最下位ビットは(例えば、空間を節約するために)TLB130に含まれないことがあるためである。したがって、TLB130における仮想アドレスは、仮想ページの特定のアドレスよりもむしろ、仮想ページ番号を表し得る。代替的な実施形態においては、異なるサイズのアドレス空間および異なる最小ページサイズが使用され得る。10

## 【0023】

[0028]図1に示されるように、第1のエントリ131は、仮想アドレス $0 \times 10000$ において開始する4Kのページに対応する。したがって、32ビットのアドレス空間の観点からは、4Kのページは、仮想アドレス $0 \times 10000000$ から $0 \times 10000\text{FF}$ までを含む。同様に、インデックス1における第2のエントリ132は、仮想アドレス $0 \times 2000X$ において開始する64Kのページに対応する。大文字の「X」は、大文字の「X」によって表されるhexの桁の任意の値が64Kのページ内に存在することを示すために使用される。つまり、64Kのページは、32ビットの仮想アドレス範囲 $0 \times 20000000$ から $0 \times 2000\text{FFFF}$ に及ぶ。インデックス2における第3のエントリ133は、仮想アドレス $0 \times 300XX$ において開始する1MBのページに対応し、インデックス3における第4のエントリ134は、仮想アドレス $0 \times 40XXX$ において開始する16MBのページに対応する。20

## 【0024】

[0029]動作期間中、TLB130は、TLBルックアップを受け取り得る。典型的には、TLBルックアップは、入力仮想アドレス104を特定し得、TLBは、(入力仮想アドレスがTLB内で見つかった場合には)以前に記憶された対応する物理アドレス、または新たに作成されたマッピングについてTLBに追加された対応する物理アドレスのいずれかをTLBから返し得る。例示のために、仮想アドレス $0 \times 1000X$ によって表される64Kの入力ページを特定するTLBルックアップを考える。本明細書において、「入力ページ」という用語は、TLBルックアップまたはTLB130上での他の読み出し/書き込み動作によって表されるメモリのページを指し得る。64Kの入力ページは、 $0 \times 10000$ から $0 \times 1000\text{F}$ までの範囲に及び得る。したがって、64Kの入力ページは、TLB130の第1のエントリ131によって表される4Kのエントリページと重複し得る。本明細書において、「エントリページ」という用語は、TLB130内のエントリによって表されるメモリのページを指し得る。 $0 \times 10000$ は、 $0 \times 1000X$ によって表される任意の値に必ずしも等しいとは限らないため、重複が存在しても、入力仮想アドレス104は受け取るが入力ページサイズ指標102を受け取らない従来のTLB重複検査方法は、重複を検出しないことがあり得ることが留意されるべきである。したがって、重複するエントリが64Kの入力ページについてTLB130内で作成されるかもしれない、これは、望ましくないことがあり、未定義の動作および/またはデータ整合性の問題につながり得る(例えば、後続のTLBルックアップは、第1のエントリ131と新たに作成されるエントリの両方に一致し得るため)。3040

## 【0025】

[0030]記載される重複検査技法によれば、TLB130は、入力ロジック110と重複検査ロジック120とを含み、または入力ロジック110と重複検査ロジック120とに結合され得る。TLBルックアップの期間中、入力ロジック110は、入力仮想アドレス104に加えて、入力ページサイズ指標102を受け取り得る。例えば、入力仮想アドレス104は、 $0 \times 1000X$ であり、入力ページサイズ指標102は、64Kであり得る。代替の実施形態において、入力ページサイズ指標102は、本明細書においてさらに記50

載されるように、マスクを使用して表され得る。

#### 【0026】

[0031]重複検査ロジック120は、入力ページサイズ指標102と入力仮想アドレス104とを入力ロジック110から受け取り、エントリ131～134のうちのいずれかが、入力ページに重複するエントリページに対応するかを決定するために、TLB130のエントリ131～134を調査し得る。例えば、重複検査ロジック120は、ページサイズ算出口ロジック122とマスクされた比較ロジック124とを含み得る。エントリ131～134の各々について、ページサイズ算出口ロジック122は、算出ページサイズ（例えば、入力ページサイズおよび対応するエントリページサイズのうちの大きい方）を決定し得る。例えば、第1のエントリ131との重複を検査する場合、ロジック122は、64Kの算出ページサイズを決定し得、これは、64Kの入力ページサイズおよび4Kのエントリページサイズのうちの大きい方である。同様に、残りのエントリ132～134の重複検査についての算出ページサイズは、それぞれ64K、1MB、および16MBであり得る。10

#### 【0027】

[0032]マスクされた比較ロジック124は、算出ページサイズを受け取り、重複を検査するために、算出ページサイズに基づいて、入力仮想アドレス104と第1のエントリ131の仮想アドレスとのマスクされた比較を実行し得る。例示のために、第1のエントリ131については、算出サイズが64Kであるため、マスクされた比較ロジック124は、入力仮想アドレス $0 \times 1000X$ およびエントリ仮想アドレス $0 \times 10000$ のhexの最後の（例えば、最下位）1桁をマスクし得る。2つの仮想アドレスは、hexの最後の1桁がマスクされる場合に等しくなるため（すなわち、 $0 \times 1000 = 0 \times 1000$ ）、重複検査ロジック120は、64Kの入力ページが第1のエントリ131において表される4Kのエントリページに重複すると結論を出し得る。重複検査ロジック120は、TLB130の残りのエントリ132～134を同様に調査し得る。あるいは、重複検査ロジック120は、重複が検出され次第、TLBエントリの調査を停止し得る。20

#### 【0028】

[0033]重複検査ロジック120は、重複検査の結果を示す重複指標126を生成し得る。例えば、重複指標126は、少なくとも1つの重複が検出されたか否かを示すブール（例えば、真／偽）出力であり得る。別の例として、重複指標126は、重複をもたらした、TLB130内のエントリの数を示し得る。例示のために、重複指標126は、TLB130のエントリが重複をもたらすことにインクリメントされるカウンタであり得る。また別の例として、重複指標126は、特定の重複エントリのインデックスを示し得る。例示のために、TLB130のエントリが重複をもたらす場合、重複指標126は、そのエントリのインデックスに設定され得る。特定の実施形態において、重複指標126は、重複指標レジスタ140に記憶され、またはプロセッサーアーキテクチャの予備ビットに記憶され得る。30

#### 【0029】

[0034]TLB130のエントリ131～134のいずれも重複をもたらさない場合、入力ページのために新たなエントリがTLB130内に作成され得る。例えば、書き込みロジック150は、入力ページサイズ指標102と入力仮想アドレス104とを入力ロジック110から受け取り、重複が検出されなかったことを示す重複指標126を重複検査ロジック120から受け取り得る。応答して、書き込みロジック150は、入力ページのために新たなエントリをTLB130内に作成し得る。あるいは、TLB130が「いっぱい（full）」である場合、書き込みロジック150は、TLB130の既存の（例えば、最も古い、最も長く使用されていない等の）エントリを、入力ページについての仮想対物理アドレスマッピングを用いて上書きし得る。重複が検出される場合、書き込みロジック150は、TLB130を変更することを控え得る。40

#### 【0030】

[0035]図1の前述の記載は、入力ページサイズ指標102とTLB130内に記憶され50

るページサイズ指標とについてページサイズ（例えば、4 K、64 K等）を使用するが、代替の実施形態は、ページサイズをビットマスクとして表すことを含み得ることが留意されるべきである。そのような実施形態において、ページサイズ算出口ロジック122は、マスクの論理積を求めることによって、2つのページサイズのうちの大きい方を決定し得る。結果として得られる算出マスクは、重複を検査する際に、マスクされた比較ロジック124によって使用され得る。例示のために、上記の例において、ページサイズの代わりにマスクが使用される場合、入力仮想アドレス104は、 $0 \times 1000X$ のままであり得るが、入力ページサイズ指標102は、64 Kの代わりにFFF0となり得る。第1のエントリ131についてのページサイズ指標は、4 Kの代わりにFFF0となり得る。ページサイズ算出口ロジック122は、算出マスクFFF0（すなわち、FFF0 AN D FFFF0 = FFFF0）を生成するために、2つのマスクに対して論理積演算を実行し得るマスクされた比較ロジック124は、入力仮想アドレス104と第1のエントリ131の仮想アドレスとを比較する場合に、算出マスクFFF0を使用し得る。算出マスクFFF0が使用される場合、両方の仮想アドレスのhexの最後の（例えば、最下位）1桁は、比較に先立ってマスクされ得、重複の同じ肯定的な決定をもたらす（すなわち、 $0 \times 1000 = 0 \times 1000$ であるため）。

#### 【0031】

[0036]特定の実施形態において、TLB130は、各エントリ131～134においてグローバル指標項目とASID項目とを含み得る。例えば、図1のシステム100がハイパーバイザと共に使用される場合、異なるASIDは、異なるゲストオペレーティングシステムに対応し、仮想アドレスの拡張子として扱われ得る。例示のために、ASIDがサポートされる場合、第1のエントリ131の仮想アドレスは、 $0 \times 1010000$ となり得、上記の例における64 Kの入力ページについての入力仮想アドレスは、 $0 \times 101000X$ となり得る。ASIDがサポートされる場合、入力ロジック110は、入力ページサイズ指標102と入力仮想アドレス104とに加えて、入力ASID106を受け取り得る。TLB130の特定のエントリのグローバル指標が第1の値（例えば、1）を有する場合、重複検査ロジック120は、重複検査期間中に、入力ASID106とエントリASIDとを比較し得る。グローバル指標が第2の値（例えば、0）を有する場合、重複検査ロジック120は、入力ページがエントリページに重複するかを決定する際に、ASIDを無視し（例えば、マスクし、および/または比較することを控え）得る。

#### 【0032】

[0037]したがって、図1のシステム100は、TLB130における重複検査を可能にし得、これは、コンピューティングシステムまたは電子デバイスにおける信頼性とデータ整合性とを向上させ得る。さらに、図1のシステム100は、そのような重複検査を（例えば、TLB130内の、またはTLB130に結合されるロジックモジュールを使用して）プロセッサレベルで可能にし得るため、図1のシステム100は、潜在的に誤りのある第三者の方法に依存することなく、TLB重複検査を可能にし得る。したがって、図1のシステム100は、重複するTLBエントリを作成しようと試みるオペレーティングシステムまたはアプリケーションからの保護を提供し得る。

#### 【0033】

[0038]図1のシステム100は、TLB内に既に存在するエントリの代わりに、プロセッサ内（例えば、TLBのミスキュー内またはTLBの書き込みキュー内）で「飛行中（in flight）」であるデータと命令とを調査する重複検査方法に好適であり得る。例えば、飛行中であるデータ/命令を調査することは、重複エラーが修正され次第、再試行動作をもたらし得る。また、TLBのミス/書き込みキューを検査することは、マルチスレッドシステムにおいて計算コストが高くなり得る。

#### 【0034】

[0039]特定の実施形態において、1つまたは複数のプロセッサ実行可能な命令は、図1を参照しつつ記載された重複検査動作をトリガし、および/または使用し得る。例えば、重複検査命令と条件付きTLB書き込み命令とが実行され得る。重複検査命令は、入力仮

10

20

30

40

50

想アドレスと入力ページサイズ指標とを含み得る。重複検査命令は、（例えば、入力ページに重複するエントリがあるかを示す）ブル出力を生成し、入力ページに重複する特定のエントリを識別し、いくつのエントリが入力ページに重複するかを識別等し得る。いくつかの実施形態において、出力は、プロセッサのレジスタ（例えば、重複指標レジスタ140）に記憶され得る。

#### 【0035】

[0040]条件付きTLB書き込み命令も、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み得る。入力ページがエントリページに一致する場合、条件付きTLB書き込み命令は、重複検査命令の出力と同様の出力を生成し得る。重複が検出されない場合、条件付きTLB書き込み命令は、入力ページのためにTLB内に新たなエントリを書き込み、または入力ページを反映するためにTLB内の既存のエントリを変更し得る。10

#### 【0036】

[0041]特定の実施形態において、重複検査命令および／または条件付きTLB書き込み命令は、单一のサンプリング周期において実行され得る。例えば、命令は、TLBの内容参照メモリ（CAM：content-addressable memory）部分に対するアトミックイベントを表し得る。

#### 【0037】

[0042]図2は、重複検査命令と条件付きTLB書き込み命令とを実行するように動作可能であるシステム200の特定の実施形態の図である。システム200は、バスインターフェース（I/F）208を介して命令キャッシュ210に結合され得るメモリ202を含む。特定の実施形態において、システム200の全部または一部は、プロセッサに一体化され得る。あるいは、メモリ202は、プロセッサの外部にあり得る。20

#### 【0038】

[0043]メモリ202は、バスインターフェース208を介して命令キャッシュ210へ命令を送り得る。命令キャッシュ210は、バス211を介してシーケンサ214に結合され得る。シーケンサ214は、汎用割り込み216を受け取り得、汎用割り込み216は、割り込みレジスタ（図示せず）から取得され得る。特定の実施形態において、命令キャッシュ210は、複数の現行命令レジスタ（図示せず）を介してシーケンサ214に結合され得、複数の現行命令レジスタは、バス211に結合され、プロセッサの特定のスレッド（例えば、ハードウェアスレッド）に関連付けられ得る。特定の実施形態において、プロセッサは、複数のハードウェアスレッドを含む、インターリーブされたマルチスレッドプロセッサであり得る。30

#### 【0039】

[0044]データキャッシュも、バスインターフェース208を介してメモリ202に結合され得る。特定の実施形態において、システム200は、重複検査を含むTLB270を含む。例えば、TLB270は、TLBエントリ272（例えば、図1のTLBエントリ131～134）と、入力ロジック274（例えば、図1の入力ロジック110）と、重複検査ロジック276（例えば、図1の重複検査ロジック120）と、書き込みロジック278（例えば、図1の書き込みロジック150）とを含み得る。40

#### 【0040】

[0045]特定の実施形態において、バス211は、百二十八ビット（128ビット）バスであり得、シーケンサ214は、各々が1つまたは複数の命令を含む命令パケットを介してメモリ202から命令を取得するように構成され得る。バス211は、第1の命令実行ユニット（Xユニット）218と、第2の命令実行ユニット220と、第3の命令実行ユニット222と、第4の命令実行ユニット224とに結合され得る。4つよりも少ないまたは4つよりも多い命令実行ユニットが存在し得ることが留意されるべきである。各命令実行ユニット218～224は、ロード／記憶ロジックおよび／または算術論理演算ユニット（ALU：arithmetic-logic unit）などの演算ロジックを含み得る。各命令実行ユニット218～224は、バス228を介して汎用レジスタファイル226に結合され得50

る。汎用レジスタファイル 226 は、図示されるように、バス 230 を介して、シーケンサ 214 と、TLB 270 と、メモリ 202 とにも結合され得る。

#### 【0041】

[0046] システム 200 は、割り込み（例えば、汎用割り込み 216）を受け入れるかを決定し、命令の実行を制御するために、シーケンサ 214 内の制御ロジックによってアクセスされ得るビットを記憶するための監視制御レジスタ 232 とグローバル制御レジスタ 234 とも含み得る。

#### 【0042】

[0047] 動作期間中、実行可能な命令は、メモリ 202 からフェッチされ、命令キャッシュ 210 に記憶され得る。例えば、命令は、重複検査命令 260 および / または条件付き TLB 書き込み命令 262 を含み得る。動作期間中、命令 260 ~ 262 の各々は、重複検査動作が TLB 270 において実行されるようにし得る。10

#### 【0043】

[0048] 例えば、重複検査命令 260 は、入力ページに対応する命令コード（例えば、「TLB O C」）と、入力仮想アドレスと、入力ページサイズ指標とを含み得る。ASID がサポートされる場合、重複検査命令 260 は、入力 ASID も含み得る。重複検査命令 260 の実行期間中、入力ロジック 274 は、入力仮想アドレスと、入力ページサイズ指標と、（もしあれば）入力 ASID とを受け取り得る。TLB エントリ 272 のうちのいずれかが、入力ページに重複するエントリページに対応するかを決定するために、重複検査ロジック 276 は、TLB エントリ 272 を調査し得る。重複検査ロジック 276 は、重複検査の結果を示す命令実行結果を生成し得る（例えば、プール出力、重複エントリの数、特定の重複エントリのインデックス等）。命令実行結果は、記憶デバイス（例えば、メモリ 202 または汎用レジスタファイル 226 内）に記憶され得る。条件付き TLB 書き込み命令 262 と異なり、重複検査命令 260 は、TLB エントリ 272 を変更しない「読み出し専用（read-only）」命令であり得ることが留意されるべきである。20

#### 【0044】

[0049] 条件付き TLB 書き込み命令 262 は、入力ページに対応する命令コード（例えば、「TLB C W」）と、入力仮想アドレスと、入力ページサイズ指標とを含み得る。ASID がサポートされる場合、条件付き TLB 書き込み命令 262 は、入力 ASID も含み得る。条件付き TLB 書き込み命令 262 の実行期間中、入力ロジック 274 は、入力仮想アドレスと、入力ページサイズ指標と、（もしあれば）入力 ASID とを受け取り得る。TLB エントリ 272 のうちのいずれかが、入力ページに重複するエントリページに対応するかを決定するために、重複検査ロジック 276 は、TLB エントリ 272 を調査し得る。重複検査ロジック 276 が、少なくとも 1 つのエントリページは入力ページに重複すると決定する場合、重複検査ロジック 276 は、TLB 書き込みエラーを示す命令実行結果を出力し得る。重複検査ロジック 276 が重複を検出しない場合、重複検査ロジック 276 は、（例えば、入力ページについてのマッピングがメモリ 202 などのメモリに作成された後に）入力ページサイズ指標と、入力仮想アドレスと、入力 ASID（もしあれば）とを、TLB エントリ 272 のうちの 1 つに書き込み得る。30

#### 【0045】

[0050] したがって、図 2 のシステム 200 は、TLB 重複検査をトリガする 1 つまたは複数の命令を含む命令セットアーキテクチャ（ISA : instruction set architecture）を実装するために使用され得る。図 2 のシステム 200 は、プロセッサ設計者およびアプリケーション開発者に、ハードウェアベースの TLB 重複検査機能へのアクセスを提供し得る。40

#### 【0046】

[0051] 図 3 は、TLB についての重複検査を実行する方法 300 の特定の実施形態のフローチャートである。例示的な実施形態において、方法 300 は、図 1 のシステム 100 または図 2 のシステム 200 において実行され得る。

#### 【0047】

10

20

30

40

50

[0052]方法300は、302において、入力仮想アドレスと入力ページサイズ指標とをTLBにおいて受け取ることを含み得る。入力仮想アドレスおよび入力ページサイズ指標は、入力ページに対応する。例えば、図1において、入力ロジック110は、入力ページサイズ指標102と入力仮想アドレス104とを受け取り得る。例示のために、入力ページサイズ指標102は、1MBであり得、入力仮想アドレス104は、 $0 \times 200XX$ であり得る。

#### 【0048】

[0053]方法300は、304において、入力ページサイズ指標とエントリページに対応するTLBのエントリのエントリページサイズ指標との比較に基づいて、算出ページサイズを決定することも含み得る。特定の実施形態において、入力ページサイズおよびエントリページサイズのうちの大きい方が、算出ページサイズとして選択され得る。例えば、ページサイズ算出ロジック122は、第1のエントリ131について、算出ページサイズが1MBであると決定し得、これは、第1のエントリ131についての1MBの入力ページサイズおよび4Kのエントリページサイズのうちの大きい方である。10

#### 【0049】

[0054]方法300は、306において、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリのエントリ仮想アドレスとのマスクされた比較を実行することをさらに含み得る。例えば、図1において、マスクされた比較ロジック124は、第1のエントリ131について、入力仮想アドレス $0 \times 200XX$ とエントリ仮想アドレス $0 \times 10000$ とのマスクされた比較を実行し得る。算出ページサイズは1MBであるため、16進数の最下位（例えば、最も右側の）2桁は、比較に先立って、マスクされる。したがって、第1のエントリ131について、比較は、 $0 \times 200$ と $0 \times 100$ との間であり得、重複検査ロジック120は、入力ページと第1のエントリ131によって表されるエントリページとの間に重複は存在しないと決定し得る。20

#### 【0050】

[0055]方法300は、308において、TLBの未調査のエントリが残っているかを決定することを含み得る。未調査のエントリが残っていない場合、方法300は、310において、重複指標を出力することを含み得る。例えば、重複指標は、ブール出力、重複エントリの数、特定の重複エントリのインデックス、または何らかの他の重複指標であり得る。あるいは、重複指標は、重複が検出された場合に出力されてもよく、重複指標の不在は、重複が検出されなかったことを示してもよい。30

#### 【0051】

[0056]TLB内に依然として未調査のエントリが存在する場合、方法300は、304に戻り得る。例えば、図1において、重複検査ロジックは、TLB130の残りのエントリ132～134を調査し得る。第2のエントリ132の場合において、算出ページサイズは、1MBであり得、これは、1MBの入力ページサイズおよび64Kのエントリページサイズのうちの大きい方である。応答して、マスクされた比較ロジック124は、入力仮想アドレス $0 \times 200XX$ およびエントリ仮想アドレス $0 \times 2000X$ の16進数の最下位2桁をマスクし得る。結果として得られる値は一致するため（すなわち、 $0 \times 200 = 0 \times 200$ ）、重複検査ロジック200は、重複（例えば、第2のエントリ132によって表されるエントリページが、入力ページを含むこと）を検出し得る。40

#### 【0052】

[0057]特定の実施形態において、図3の方法300は、DSP、CPU、コントローラ、フィールドプログラマブルゲートアレイ（FPGA）デバイス、特定用途向け集積回路（ASIC）、別のハードウェアデバイス、ファームウェアデバイス、またはこれらの任意の組み合わせによって実装され得る。一例として、図3の方法300は、図6を参照しつつ記載されるように、命令を実行するプロセッサによって実行され得る。

#### 【0053】

[0058]図4は、重複検査命令を実行する方法400の特定の実施形態のフローチャート50

である。例示的な実施形態において、方法 400 は、図 1 のシステム 100 または図 2 のシステム 200 において実行され得る。

#### 【0054】

[0059] 図 4 に例示される各動作は、プロセッサにおける重複検査命令の実行期間中に実行され得る。重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み得る。方法 400 は、402、TLB のエントリのエントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定することを含み得る。例えば、図 2 において、重複検査命令 260 の実行期間中に、重複検査ロジック 276 は、TLB エントリ 272 のうちの 1 つのエントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定し得る。 10

#### 【0055】

[0060] 方法 400 は、404において、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリのエントリ仮想アドレスとのマスクされた比較を実行することをさらに含み得る。例えば、図 2 において、重複検査ロジック 276 は、算出ページサイズに基づいて、マスクされた比較を実行し得る。

#### 【0056】

[0061] 方法 400 は、406において、TLB の未調査のエントリが残っているかを決定することをさらに含み得る。特定の実施形態において、TLB のすべてのエントリは、同時に調査され得る。TLB 内に依然として未調査のエントリが存在する場合、方法 400 は、402 に戻り得る。未調査のエントリが残っていない場合、方法 400 は、408において、実行結果を出力することを、410において、この実行結果をプロセッサのレジスタに記憶することを含み得る。例えば、図 2 において、重複検査ロジック 276 は、実行結果を汎用レジスタファイル 226 に記憶し得る。実行結果は、ブール結果、入力ページに重複するエントリページに対応する、TLB のエントリの数、入力ページに重複する特定のエントリページに対応する、TLB の特定のエントリ等であり得る。代替の実施形態においては、重複が識別され次第、方法 400 は、重複指標を出力し、さらなる TLB エントリを調査することを継続する代わりに、終了し得る。したがって、図 4 の方法 400 は、入力ページのために TLB 内に新たなエントリを作成することが TLB 内に重複エントリをもたらすかを決定するために、重複検査命令の実行を可能にし得る。 30

#### 【0057】

[0062] 特定の実施形態において、図 4 の方法 400 は、DSP、CPU、コントローラ、フィールドプログラマブルゲートアレイ (FPGA) デバイス、特定用途向け集積回路 (ASIC)、別のハードウェアデバイス、ファームウェアデバイス、またはこれらの任意の組み合わせによって実装され得る。一例として、図 4 の方法 400 は、図 6 を参照しつつ記載されるように、命令を実行するプロセッサによって実行され得る。

#### 【0058】

[0063] 図 5 は、条件付き TLB 書き込み命令を実行する方法 500 の特定の実施形態のフローチャートである。例示的な実施形態において、方法 500 は、図 1 のシステム 100 または図 2 のシステム 200 において実行され得る。 40

#### 【0059】

[0064] 図 5 に例示される各動作は、TLB を含むプロセッサにおける条件付き TLB 書き込み命令の実行期間中に実行され得る。TLB は、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する少なくとも 1 つのエントリを含み得る。条件付き TLB 書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み得る。方法 500 は、502において、エントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定することを含み得る。例えば、図 2 において、条件付き TLB 書き込み命令 262 の実行期間中に、重複検査ロジック 276 は、TLB エントリ 272 のうちの 1 つのエントリページサイズ指標と入力ページサイズ指標との比較に基づいて、算出ページサイズを決定し得る。 50

**【 0 0 6 0 】**

[0065]方法 500 は、504において、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリのエントリ仮想アドレスとのマスクされた比較を実行することも備え得る。例えば、図2において、重複検査ロジック 276 は、算出ページサイズに基づいて、マスクされた比較を実行し得る。

**【 0 0 6 1 】**

[0066]方法 500 は、506において、TLB の未調査のエントリが残っているかを決定することをさらに含み得る。代替の実施形態においては、重複が識別され次第、方法 500 は、重複指標を出力し、さらなる TLB エントリを調査することを継続する代わりに、終了し得る。TLB 内に依然として未調査のエントリが存在する場合、方法 500 は、502 に戻り得る。未調査のエントリが残っていない場合、方法 500 は、508において、入力ページが少なくとも 1 つのエントリページに重複するかを決定することを含み得る。

10

**【 0 0 6 2 】**

[0067]入力ページに重複するエントリページが存在しない場合、方法 500 は、510において、入力ページサイズ指標と入力仮想アドレスとを TLB の第 2 のエントリに書き込むことを含み得る。少なくとも 1 つのエントリページが入力ページに重複する場合、方法 500 は、512において、書き込みエラーを示す実行結果を出力することを含み得る。したがって、図5の方法 500 は、TLB における重複を検査し、重複が検出されない場合には TLB 内に新たなエントリを作成するための単一の命令の実行を可能にする。

20

**【 0 0 6 3 】**

[0068]特定の実施形態において、図5の方法 500 は、DSP、CPU、コントローラ、フィールドプログラマブルゲートアレイ (FPGA) デバイス、特定用途向け集積回路 (ASIC)、別のハードウェアデバイス、ファームウェアデバイス、またはこれらの任意の組み合わせによって実装され得る。一例として、図5の方法 500 は、図6を参照しつつ記載されるように、命令を実行するプロセッサによって実行され得る。

**【 0 0 6 4 】**

[0069]図6を参照すると、電子デバイス 600 のブロック図が示される。特定の実施形態において、電子デバイス 600、またはその構成要素は、通信デバイス、コンピューティングデバイス、携帯情報端末 (PDA)、エンターテインメントユニット、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、ナビゲーションデバイス、固定ロケーションデータユニット、またはこれらの任意の組み合わせに含まれ得る。

30

**【 0 0 6 5 】**

[0070]電子デバイス 600 は、メモリ 632 に結合されるプロセッサ (例えば、DSP) 610 を含む。プロセッサ 610 は、マルチコアプロセッサであり、および / または、複数のハードウェアスレッドを含み得る。例えば、プロセッサ 610 は、インターリープされたマルチスレッド実行をサポートし得る。

**【 0 0 6 6 】**

[0071]図6は、プロセッサ 610 とディスプレイ 628 とに結合されるディスプレイコントローラ 626 を含む。コーダ / デコーダ (CODEC) 634 は、プロセッサ 610 に結合され得る。スピーカー 636 およびマイクロフォン 638 は、CODEC 634 に結合され得る。図6は、ワイヤレスコントローラ 640 が (例えば、無線周波数 (RF) インターフェースを介して) プロセッサ 610 とアンテナ 642 とに結合され得ることも示す。

40

**【 0 0 6 7 】**

[0072]メモリ 632 は、実行可能な命令を含む、有形の非一時的なコンピュータ読取可能またはプロセッサ読取可能な記憶媒体であり得る。命令は、図3、図4、および図5の方法 300 と、方法 400 と、方法 500 とを含む、本明細書において記載される様々な機能および方法を実行するために、プロセッサ 610 などのプロセッサによって実行され

50

得る。例えば、メモリ 632 は、重複検査命令 260 と条件付き T L B 書き込み命令 262 を記憶し得る。命令 260 および 262 の実行は、プロセッサ 610 の T L B 270 における重複検査動作をトリガし得る。例えば、そのような重複検査動作は、図 2 を参照しつつ記載されたように、T L B エントリ 272 と、入力ロジック 274 と、重複検査ロジック 276 と、および / または、書き込みロジック 278 とに関与し得る。

#### 【0068】

[0073]特定の実施形態において、プロセッサ 610、ディスプレイコントローラ 626、メモリ 632、C O D E C 634、およびワイヤレスコントローラ 640 は、システムインパッケージまたはシステムオンチップデバイス 622 に含まれる。特定の実施形態において、入力デバイス 630 および電源 644 は、システムオンチップデバイス 622 に結合される。さらに、特定の実施形態において、図 6 に例示されるように、ディスプレイ 628、入力デバイス 630、スピーカー 636、マイクロフォン 638、アンテナ 642、および電源 644 は、システムオンチップデバイス 622 の外部に存在する。ただし、ディスプレイ 628、入力デバイス 630、スピーカー 636、マイクロフォン 638、アンテナ 642、および電源 644 の各々は、インターフェースまたはコントローラなど、システムオンチップデバイス 622 の構成要素に結合され得る。10

#### 【0069】

[0074]記載された実施形態に関する限り、装置は、少なくとも 1 つのエントリを記憶するための手段を含む。少なくとも 1 つのエントリは、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを含む。例えば、記憶するための手段は、図 1 の T L B 130、図 2 の T L B 270、データを記憶するように構成された別のデバイスもしくはモジュール、またはこれらの任意の組み合わせであり得る。20

#### 【0070】

[0075]本装置は、入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを受け取るための手段も含み得る。例えば、受け取るための手段は、図 1 の入力ロジック 110、図 2 の入力ロジック 274、データを受け取るように構成された別のデバイスもしくはモジュール、またはこれらの任意の組み合わせを含み得る。

#### 【0071】

[0076]本装置は、エントリページサイズ指標と入力ページサイズ指標との比較に基づいて算出ページサイズを決定するための手段をさらに含み得る。例えば、決定するための手段は、図 1 のページサイズ算出ロジック 122、図 2 の重複検査ロジック 276、ページサイズを算出するように構成された別のデバイスもしくはモジュール、またはこれらの任意の組み合わせを含み得る。30

#### 【0072】

[0077]本装置は、入力ページがエントリページに重複するかを決定するために、算出ページサイズに基づいて、入力仮想アドレスとエントリ仮想アドレスとのマスクされた比較を実行するための手段を含み得る。例えば、マスクされた比較を実行するための手段は、図 1 のマスクされた比較ロジック 124、図 2 の重複検査ロジック 276、マスクされた比較を実行するように構成された別のデバイスもしくはモジュール、またはこれらの任意の組み合わせを含み得る。40

#### 【0073】

[0078]当業者は、本明細書において開示される実施形態と共に記載される論理ブロック、構成、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両者の組み合わせとして実装され得ることをさらに認識するであろう。様々な例示的な構成要素、ブロック、構成、モジュール、回路、およびステップは、一般に、これらの機能性の観点から上述されてきた。そのような機能性がハードウェアとして実装されるか、またはプロセッサ実行可能な命令として実行されるかは、特定の適用例およびシステム全体に課される設計制約に依存する。当業者は、記載された機能性を特定の適用例ごとに様々な手法で実装し得るが、そのような実装上の決定は、本開示の範囲からの逸脱を引き起こすものとして解釈されるべき50

ではない。

**【0074】**

[0079]本明細書において開示される実施形態に関連して記載される方法またはアルゴリズムのステップは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこの2つの組み合わせにおいて具現化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ( RAM )、フラッシュメモリ、読み出し専用メモリ( ROM )、プログラム可能読み出し専用メモリ( PROM )、消去可能プログラム可能読み出し専用メモリ( EEPROM (登録商標))、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み出し専用メモリ( CD - ROM )、デジタル多用途ディスク( DVD )、または、本技術分野において知られる、任意の他の形式の非一時的な記憶媒体において常駐し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替案において、記憶媒体は、プロセッサと一体化され得る。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)に存在し得る。ASICは、コンピューティングデバイスまたはユーザ端末に存在し得る。代替案において、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末における別個の構成要素として存在し得る。10

**【0075】**

[0080]開示された実施形態の前述の記載は、開示された実施形態を当業者が製造または使用することを可能にするために提供される。これらの実施形態への様々な変更は、当業者には容易に明らかとなるであろうし、本明細書において定義される原理は、本開示の範囲から逸脱することなく、他の実施形態に適用され得る。したがって、本開示は、本明細書において示される実施形態に限定されることは意図されないが、下記の請求項によって定義されるような原理および新規な特徴と一致する、考え得る最も広い範囲と合致すべきである。20

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

**[請求項 1]**

入力仮想アドレスと入力ページサイズ指標とを変換索引バッファ( T L B )において受け取ることと、前記入力仮想アドレスおよび前記入力ページサイズ指標は、入力ページに30

対応し、

前記入力ページサイズ指標と前記 T L B のエントリのエントリページサイズ指標との比較に基づいて、算出ページサイズを決定することと、ここにおいて、前記 T L B の前記エントリは、エントリページに対応し、

前記入力ページが前記エントリページに重複するかを決定するために、前記算出ページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとのマスクされた比較を実行することと、

を備える方法。

**[請求項 2]**

前記算出ページサイズを決定することが、前記入力ページサイズ指標によって表される入力ページサイズおよび前記エントリページサイズ指標によって表されるエントリページサイズのうちの大きい方を前記算出ページサイズとして選択することを備える、請求項 140

に記載の方法。

**[請求項 3]**

前記 T L B の第 2 のエントリの第 2 のエントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、第 2 の算出ページサイズを決定することと、ここにおいて、前記 T L B の前記第 2 のエントリは、第 2 のエントリページに対応し、

前記入力ページが前記第 2 のエントリページに重複するかを決定するために、前記第 2 の算出ページサイズに基づいて、前記入力仮想アドレスと前記第 2 のエントリの第 2 のエントリ仮想アドレスとの第 2 のマスクされた比較を実行することと、

をさらに備える、請求項 1 に記載の方法。50

[ 請求項 4 ]

前記算出ページサイズが、前記第 2 の算出ページサイズと異なる、請求項 3 に記載の方法。

[ 請求項 5 ]

少なくとも 1 つのエントリを備える変換索引バッファ ( T L B ) と、前記少なくとも 1 つのエントリは、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを含み、

入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを受け取るように構成された入力ロジックと、

前記エントリページサイズ指標および前記入力ページサイズ指標に少なくとも一部は基づいて、前記入力ページが前記エントリページに重複するかを決定するように構成された重複検査ロジックと、

を備える装置。

[ 請求項 6 ]

前記重複検査ロジックが、

前記エントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算出ページサイズを決定し、

前記入力ページが前記エントリページに重複するかを決定するために、前記算出ページサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされた比較を実行する

ようにさらに構成される、請求項 5 に記載の装置。

[ 請求項 7 ]

前記少なくとも 1 つのエントリが、アプリケーション空間識別子 ( A S I D ) とグローバル指標とをさらに含み、前記入力ロジックが、入力 A S I D を受け取るようにさらに構成され、ここにおいて、前記重複検査ロジックが、

第 1 の値を有する前記グローバル指標に応答して、前記入力ページが前記エントリページに重複するかを決定する際に前記 A S I D と前記入力 A S I D とを比較し、

第 2 の値を有する前記グローバル指標に応答して、前記入力ページが前記エントリページに重複するかを決定する際に前記 A S I D と前記入力 A S I D とを比較することを控える

ようにさらに構成される、請求項 6 に記載の装置。

[ 請求項 8 ]

前記入力ページサイズ指標が、第 1 のマスクによって表され、前記エントリページサイズ指標が、第 2 のマスクによって表される、請求項 5 に記載の装置。

[ 請求項 9 ]

前記入力ページサイズ指標が、第 1 のページサイズによって表され、前記エントリページサイズ指標が、第 2 のページサイズによって表される、請求項 5 に記載の装置。

[ 請求項 10 ]

前記少なくとも 1 つのエントリが、前記エントリ仮想アドレス、アプリケーション空間識別子 ( A S I D ) 、キャッシュ可能指標、許可指標、グローバル指標、またはこれらの任意の組み合わせにマッピングされる物理アドレスを含む、請求項 5 に記載の装置。

[ 請求項 11 ]

プロセッサにおいて重複検査命令を実行することを備え、ここにおいて、前記重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、前記重複検査命令を実行することは、

変換索引バッファ ( T L B ) のエントリのエントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算出ページサイズを決定することと、

前記入力ページがエントリページに重複するかを決定するために、前記算出ページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとのマスクされた比較を実行すること、

10

20

30

40

50

前記入力ページが前記エントリページに重複するかの前記決定に基づいて、実行結果を出力することと、

を含む、方法。

[請求項 12]

前記実行結果が、プール出力を備える、請求項 11 に記載の方法。

[請求項 13]

前記実行結果が、前記入力ページに重複するエントリページに対応する、前記 T L B の

エントリの数を識別する、請求項 11 に記載の方法。

[請求項 14]

前記実行結果が、前記入力ページに重複する特定のエントリページに対応する、前記 T

L B の特定のエントリを識別する、請求項 11 に記載の方法。

[請求項 15]

前記重複検査命令を実行することが、前記実行結果を前記プロセッサのレジスタに記憶

することをさらに備える、請求項 11 に記載の方法。

[請求項 16]

T L B を含むプロセッサにおいて条件付き変換索引バッファ (T L B) 書き込み命令を

実行することを備え、ここにおいて、前記 T L B は、エントリページに対応するエントリ

仮想アドレスとエントリページサイズ指標とを有する第 1 のエントリを含み、前記条件付

き T L B 書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指

標とを含み、

10

前記条件付き T L B 書き込み命令を実行することは、

前記エントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算

出ページサイズを決定することと、

前記入力ページが前記エントリページに重複するかを決定するために、前記算出ペ

ージサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされ

た比較を実行することと、

前記入力ページが前記エントリページに重複しないと決定することに応答して、前記

入力ページサイズ指標と前記入力仮想アドレスとを前記 T L B の第 2 のエントリに書き込

むことと、

を備える、方法。

20

[請求項 17]

前記条件付き T L B 書き込み命令を実行することが、前記入力ページが前記エントリペ

ージに重複すると決定することに応答して、書き込みエラーを示す実行結果を出力するこ

とをさらに備える、請求項 16 に記載の方法。

30

[請求項 18]

前記実行結果が、前記入力ページに重複するエントリページに対応する、前記 T L B の

エントリの数を識別し、前記入力ページに重複する特定のエントリページに対応する、前

記 T L B の特定のエントリ、またはこれらの任意の組み合わせを識別する、請求項 17 に

記載の方法。

40

[請求項 19]

少なくとも 1 つのエントリを記憶するための手段と、前記少なくとも 1 つのエントリは

、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを含み

、

入力ページに対応する入力ページサイズ指標と入力仮想アドレスとを受け取るための手

段と、

前記エントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算出

ページサイズを決定するための手段と、

前記入力ページが前記エントリページに重複するかを決定するために、前記算出ペ

ージサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされ

た比較を実行するための手段と、

50

を備える、装置。

[請求項 20]

重複検査命令を備え、

ここにおいて、前記重複検査命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、

前記重複検査命令は、変換索引バッファ（TLB）を含むプロセッサによって、

前記TLBのエントリのエントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算出ページサイズを決定し、

前記入力ページがエントリページに重複するかを決定するために、前記算出ページサイズに基づいて、前記入力仮想アドレスと前記エントリのエントリ仮想アドレスとのマスクされた比較を実行し、

前記入力ページが前記エントリページに重複するかの決定に基づいて、実行結果を出力する

ように実行可能である、非一時的なプロセッサ読取可能な媒体。

[請求項 21]

条件付き変換索引バッファ（TLB）書き込み命令を備え、

ここにおいて、前記条件付きTLB書き込み命令は、入力ページに対応する入力仮想アドレスと入力ページサイズ指標とを含み、

前記条件付きTLB書き込み命令は、エントリページに対応するエントリ仮想アドレスとエントリページサイズ指標とを有する第1のエントリを含むTLBを含むプロセッサによって、

前記エントリページサイズ指標と前記入力ページサイズ指標との比較に基づいて、算出ページサイズを決定し、

前記入力ページが前記エントリページに重複するかを決定するために、前記算出ページサイズに基づいて、前記入力仮想アドレスと前記エントリ仮想アドレスとのマスクされた比較を実行し、

前記入力ページが前記エントリページに重複しないと決定することに応答して、前記入力ページサイズ指標と前記入力仮想アドレスとを前記TLBの第2のエントリに書き込むように実行可能である、非一時的なプロセッサ読取可能な媒体。

10

20

【 四 1 】

FIG. 1

【図2】

**FIG. 2**

【 図 3 】

FIG. 3

【 図 4 】

**FIG. 4**

【図5】

図5

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

- (72)発明者 ベンクマハンティ、スレシュ・ケー。

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 プロンケ、エーリッヒ・ジェイ。

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 コドレスク、ルシアン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 マホン、シェイン・エム。

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

- (72)発明者 トレイ、ラーフル・アール。

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライ브 5775

- (72)発明者 ハムダン、ファディ・エー。

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 滝谷 亮一

- (56)参考文献 国際公開第96/12231(WO,A1)

米国特許第5765209(US,A)

米国特許第6233652(US,B1)

米国特許第6560689(US,B1)

特開2002-288038(JP,A)

特開平8-329687(JP,A)

特開平6-202954(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12/10

G 06 F 12/08