(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5906022号

(P5906022)

(45) 発行日 平成28年4月20日(2016.4.20)

(24) 登録日 平成28年3月25日(2016.3.25)

(51) Int.Cl.

H01L 21/60 (2006.01)

H01L 23/50 (2006.01)

F 1

H01L 21/60 311 S

H01L 21/92 604 J

H01L 23/50 P

請求項の数 4 (全 8 頁)

(21) 出願番号 特願2011-88708 (P2011-88708)

(22) 出願日 平成23年4月13日 (2011.4.13)

(65) 公開番号 特開2011-228704 (P2011-228704A)

(43) 公開日 平成23年11月10日 (2011.11.10)

審査請求日 平成26年4月9日 (2014.4.9)

(31) 優先権主張番号 12/762,610

(32) 優先日 平成22年4月19日 (2010.4.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 390041542

ゼネラル・エレクトリック・カンパニー

アメリカ合衆国、ニューヨーク州 123

45、スケネクタディ、リバーロード、1

番

(74) 代理人 100137545

弁理士 荒川 聰志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

最終頁に続く

(54) 【発明の名称】マクロピンハイブリッド相互接続アレイ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

テルル化カドミウム亜鉛(CZT)又はテルル化カドミウム(CdTe)結晶アノードアレイ(18)とアルミナセラミック基板(14)とを備えるマクロピンハイブリッド相互接続アレイ(10)であって、前記アレイ(18)と前記基板(14)とが、1を超える高さ対幅のアスペクト比を有する相互接続(12)幾何形状を介して共に接合されており、前記結晶アノードアレイ(18)が、はんだ無しで前記相互接続(12)に接続されたほぼ平坦なアノードパッド(16)を備えており、前記相互接続(12)が、前記基板(14)上の回路メタライゼーション(24)を介して基板(14)に接合されている、マクロピンハイブリッド相互接続アレイ(10)。

10

## 【請求項 2】

前記相互接続(12)が、複数の銅ピラー、金スタッフバンプ又は金めっきピラーを含む、請求項1記載のマクロピンハイブリッド相互接続アレイ(10)。

## 【請求項 3】

前記相互接続(12)を前記基板(14)上の回路メタライゼーション(24)に固定する継手が、はんだ継手、圧着継手、接着剤エポキシ樹脂継手、及びそれらの組み合わせのうち1つ以上を含む、請求項1又は請求項2記載のマクロピンハイブリッド相互接続アレイ(10)。

## 【請求項 4】

請求項1乃至請求項3のいずれか1項記載のマクロピンハイブリッド相互接続アレイ(

20

10) を形成する方法であって、

ほぼ平坦なアノードパッド(16)を備えるテルル化カドミウム亜鉛(CZT)又はテルル化カドミウム(CdTe)結晶アノードアレイ(18)と、アルミナセラミック基板(14)とを用意する工程と、

1を超える高さ対幅のアスペクト比を有する相互接続(12)幾何形状を介して前記アレイ(18)と前記基板(14)とを共に接合する工程であって、ほぼ平坦なアノードパッド(16)を、はんだ無しで前記相互接続(12)に接続し、前記相互接続(12)を、前記基板(14)上の回路メタライゼーション(24)を介して基板(14)に接合することを含む工程と

を含んでなる方法。

10

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、一般に、マクロピンハイブリッド相互接続アレイに関し、より詳細には、結晶とこの結晶を取り付ける基板との間の熱膨張係数(CTE: Coefficient of Thermal Expansion)の不整合を最小にする構造を作り出すマクロピンハイブリッド相互接続アレイ構造及び方法に関する。

#### 【背景技術】

#### 【0002】

20

テルル化カドミウム亜鉛(CZT: cadmium zinc telluride)結晶、及びテルル化カドミウム(CdTe)結晶は、大変脆い材料であり、特に大きく薄い結晶については、パッケージングが非常に困難となる。最近の発見により、マイクロクラックが、低温導電性エポキシ樹脂接着剤を用いて製造した相互接続に隣接するCZT中に生じることが分かっている。結晶と基板の間のCTEの不整合は、相互接続と結晶の界面にかなりの歪みを引き起こし、特にCTEが11 ppm/以上である有機基板を用いるときに、深刻な信頼性の問題をもたらす。最も大きい歪みは、その部分を(接着プロセスを用いる場合)硬化するとき、又は(はんだプロセスを用いる場合)その部分をリフローするときにしばしば起こる。

#### 【0003】

30

典型的には、基板材料は、基板及び結晶が膨張及び収縮する際、熱サイクル中に発生する全体的な歪み(global strain)を最小にするために、結晶にできる限り近くなるよう整合したCTEが選択される。通常、アルミナセラミック基板が、CZT検出器と共に使用するために選ばれる。

#### 【0004】

更なる分析により、単一の相互接続箇所内の導電性接着剤とCZTの間の局所的なCTEの不整合によって、マイクロクラックが、導電性エポキシ樹脂相互接続でセラミック基板に装着したCZT結晶中に生じ得ることが示されている。導電性エポキシ樹脂は、CZTよりずっと大きいCTEを有することで知られている。また、エポキシ樹脂の温度が、ガラス転移温度(Tg)を超えると、CTEは、Tg未満のCTEよりも典型的には4~5倍大きい値まで劇的に増加する。

40

#### 【0005】

現在、インジウムバンブンディング、導電性接着剤、及び低温はんだが、CZT検出器結晶基板を取り付けるために用いられている。これら結晶を用いたパッケージの信頼性に対してはほとんど研究がなされておらず、業界標準のパッケージと比べると、これまでに行われた研究は、非常に限定的であると思われる。薄い(<5mm)CZT結晶及びCdTe結晶は、損傷を与えずにパッケージングすることが困難であることで知られている。典型的には、CZT検出器は、非常に割れやすいことが知られているので、最も軽い信頼性試験だけを受ける。0.5mmの厚さのCdTe結晶は、注意深く取り扱っても簡単にひび割れる可能性があることがよく知られている。このタイプの結晶を有機インター

50

ーザなどの大きいC T Eのインター ポーザに取り付けるときに、ひび割れる可能性が非常に高い。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許第7,554,206号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

したがって、局所歪みが少なく、今日製造者が利用できる従来の取り付け方法に適合可能であるインター ポーザにC Z T及び/又はC d T eを相互接続するための構造を提供するすることが有益であろう。

10

【課題を解決するための手段】

【0008】

簡潔に言えば、一実施形態によれば、マクロピンハイブリッド相互接続アレイは、結晶アノードアレイ及びセラミック基板を備え、この結晶及び基板は、大きい高さ対幅のアスペクト比を有する相互接続幾何形状を介して共に接合され、相互接続を結晶アノードアレイに固定する継手は、無はんだである。

【0009】

別の実施形態によれば、マクロピンハイブリッド相互接続アレイは、結晶アノードアレイ及びセラミック基板を備え、このアレイ及び基板は、コンプライアントマイクロピンハイブリッド相互接続構成を介して共に接合され、熱暴走中のアレイと相互接続の間の力学的歪みが、結晶アノードアレイをセラミック基板に接合するために従来のはんだバンプボンディングを用いて生じる歪みより低くとどまるようになっている。

20

【0010】

更に別の実施形態によれば、マクロピンハイブリッド相互接続アレイを形成する方法は、結晶アノードアレイ及びセラミック基板を用意し、アレイ及び基板が共に接合される各領域内で局所歪みを減少させるコンプライアントマイクロピンハイブリッド相互接続構成を介してアレイ及び基板を共に接合し、熱暴走中のアレイと相互接続の間の力学的歪みが、結晶アノードアレイを相互接続に接合しマクロピンハイブリッド相互接続アレイを形成するためのはんだボンディングを用いて生じ得る歪みより低くとどまるようになっていることを含んでなる。

30

【0011】

本発明のこれら及び他の特徴、態様及び利点は、添付図面を参照して下記の詳細な説明を読むとより良く理解されよう。この図面では、図面全体を通じて、同じ符号が同じ部分を表している。

【図面の簡単な説明】

【0012】

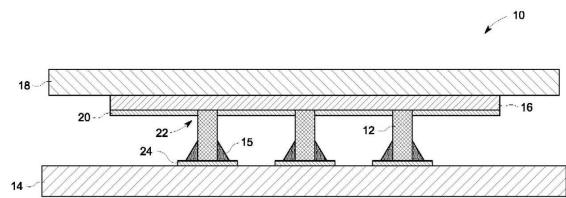

【図1】一実施形態による、はんだを用いてセラミック基板に取り付けられると共に、はんだを用いずに結晶アノードアレイに更に取り付けられる銅スタッフ又はピラー相互接続を用いるマクロピンハイブリッド相互接続アレイの説明図である。

40

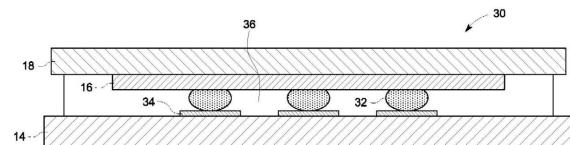

【図2】別の実施形態による、無はんだの圧着によってセラミック基板と結晶アノードアレイの両方に取り付けられる金スタッフバンプ又はめっきピラー相互接続を用いるマクロピンハイブリッド相互接続アレイの説明図である。

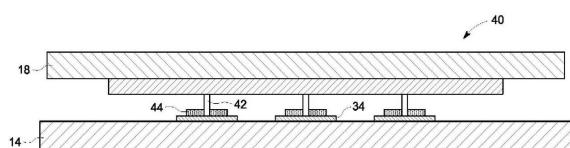

【図3】更に別の実施形態による、導電性エポキシ樹脂の微細堆積物によってセラミック基板に取り付けられ、はんだ又はエポキシ樹脂を用いずに結晶アノードアレイに更に取り付けられる金スタッフバンプ又はめっきピラー相互接続を用いるマクロピンハイブリッド相互接続アレイの説明図である。

【発明を実施するための形態】

【0013】

50

上記図面の各図は、代替実施形態を説明するが、説明の中で言及したように本発明の他の実施形態も考えられる。どの場合も、本開示は、代表によって本発明の例示の実施形態を示すものであり、限定するものではない。当業者は、本発明の本原理の範囲及び精神の範囲内に入る多数の他の修正形態及び実施形態を考え出すことができる。

#### 【0014】

図1は、一実施形態による、はんだ15を用いてセラミック基板14に取り付けられると共に、はんだを用いずに結晶アノードアレイ18の1つのアノードパッド16に更に取り付けられる銅スタッド又はピラー相互接続12を用いるマクロピンハイブリッド相互接続アレイ10を示す。一実施形態によるこのタイプの相互接続を作り出す好ましい方法は、まず、結晶アノードアレイ18を洗浄することを含む。結晶アノードアレイ18の洗浄に続いて、バンプ下地金属(UBM: under bump metallization)層(Ti-W、Ni、Au又はTi-W、Cu、Ni、Au)を付着して結晶にアノードパッド16を形成し、続いてこのアノードパッド16にフォトレジストシート20を施す。次いで、フォトレジストシート20をパターニングしてフォトレジストシート20に開口部22を形成する。開口部22を電解めっき又は無電解めっきによって銅(Cu)でめっきして、高さ対幅の高いアスペクト比のCuピラー12を形成する。次いで、残りのフォトレジスト20を除去して、結晶アノードアレイ18のアノードパッド16に今取り付けられているCuピラー12だけを残す。

#### 【0015】

次いで、Cuピラー12と、セラミック基板14上の回路メタライゼーション24との取り付けが行われることになる領域内で、はんだペースト、例えばタイプ6、又はより微細なペーストを、基板14に施すことができる。次いで、はんだペーストをリフローして、はんだ付着物を形成する。本発明の一態様によれば、はんだ付着物は、各はんだ付着物がほぼ平坦でほぼ等しい高さであることを確かなものとするように圧印加工してもよい。次に、はんだフラックスを基板14全体にわたって塗布し、はんだ付着物を覆う。はんだフラックスの塗布に続いて、各Cuピラー12が基板14上の対応するはんだ付着物と位置合わせされるように、結晶アノードアレイ18に取り付けられたCuピラー12を配置する。再び、はんだをリフローして、はんだと対応するCuピラー12の間に金属継手15を形成する。結晶アノードアレイ18とセラミック基板14の自己整合は、このリフロープロセス中に起こる。得られたマクロピンハイブリッド相互接続アレイ10に残っている残留フラックスは、はんだフラックスが水溶性である場合、洗浄によって除去することができる。最後に、基板14は、本発明の一態様によるプラズマエッティング及び続くアンダーフィルの塗布によってコンディショニングすることができる。

#### 【0016】

上記のようにはんだペーストをリフローしない場合、前述のはんだ付着物の形成は、必要とされない。更に、フラックスは、Cuピラー12の先端をフラックスの中に浸すことによって一態様による相互接続箇所にだけ塗布されてもよい。はんだとCuピラー12の間に金属継手15を形成するリフロープロセスの後に、得られたマクロピンハイブリッド相互接続アレイ10を試験することによって、相互接続の歩留まりを判定することができる。次いで、不十分な相互接続は、必要又は望ましいと分かった場合、手直しされてもよい。

#### 【0017】

図2は、別の実施形態による、無はんだの圧着によってセラミック基板14と結晶アノードアレイ18の両方に取り付けられる金スタッドバンプ又はめっきピラー相互接続32を用いるマクロピンハイブリッド相互接続アレイ30を示す。スタッドバンプ又はめっきピラー32は、一実施形態による基板14上に貴金属めっきパッドをそれぞれ備えることができる1つ以上の基板パッド34に圧縮変位ボンディングプロセス(compressive displacement bonding process)によって接合される。一実施形態による前述のボンディング作業中に硬化するインターポーザ32を封入する低温アンダーフィル36が、使用されてもよい。前述のボンディングプロセスは、室

10

20

30

40

50

温で行われてもよく、それにより基板 14 は、過度の歪みをもたらすことなく結晶 18 とのより大きい CTE の不整合を有することが可能になる。

#### 【 0 0 1 8 】

マクロピンハイブリッド相互接続アレイ構造 30 を実現するためのあるポンディングプロセスは、まず、結晶アノードアレイ 18 の洗浄によって開始する。次に、金スタッドバンプ又はめっきピラー 32 を、図 1 に関連して本明細書に記載したプロセスのような圧縮変位ポンディングプロセス又は低温はんだ取り付けプロセスによって、アレイピクセル (array pixel) 上の UBM アノードパッドに施す。次いで、エポキシアンダーフィル 36 を基板 14 の表面に塗布して、金スタッドバンプ又はめっきピラー 32 を封入する。結晶アノードアレイ 18 は、バンプ又はピラー 32 が対応する基板パッド 34 と位置合わせするように配置される。バンプ又はピラー 32 を対応する基板パッド 34 と位置合わせした後に、圧力が、各バンプ又はピラー 32 とその対応する基板パッド 34 の間の圧縮変位接着力を実現するために加えられる。前述のポンディングプロセスの完了に続いて、アンダーフィル 36 を硬化するため必要な場合、熱が、エポキシアンダーフィル 36 に加えられてもよい。

#### 【 0 0 1 9 】

図 3 は、更に別の実施形態による、導電性エポキシ樹脂 44 の微細堆積物によってセラミック基板 14 に取り付けられ、はんだ又はエポキシ樹脂を用いずに結晶アノードアレイ 18 に更に取り付けられる金スタッドバンプ又はめっきピラー相互接続 42 を用いるマクロピンハイブリッド相互接続アレイ 40 を示す。各金スタッドバンプ又はめっきピラー 42 は、図示のように、各金スタッドバンプ又はめっきピラー 42 を基板 14 に取り付けるところで導電性エポキシ樹脂の微細堆積物に埋設される。好ましくは、各バンプ又はピラー 42 は、1 を超える高さ対幅のアスペクト比を有する。

#### 【 0 0 2 0 】

マクロピンハイブリッド相互接続アレイ 40 は、まず、結晶アノードアレイ 18 を洗浄することによって、一実施形態により形成することができる。次いで、金めっき又はスタッドバンプを用いて、図 1 及び図 2 に関連して本明細書に記載したようなプロセスによって、金スタッドバンプ又はめっきピラー 42 を形成する。導電性接着剤ペースト 44 の微細堆積物は、例えばステンシル印刷又はシリンジ塗布プロセスを用いて、基板パッド 34 上へ塗布される。次いで、結晶アノードアレイ 18 に取り付けられたバンプ又はピラー 42 は、導電性エポキシ樹脂 (接着剤ペースト) 44 の対応する付着物と位置合わせされ、所定の位置に押圧される。次いで、接着剤 44 は、温度で硬化され、必要があるときはプラズマエッティングが適用される。必要があるときは、図 2 に関連して説明したアンダーフィル 36 などのアンダーフィルが、特定の用途に適合するように用いられてもよい。

#### 【 0 0 2 1 】

本明細書に記載したマクロピンハイブリッド相互接続アレイは、各検出器・基板電極ペアに施された単一の相互接続を用いて示されるが、本発明はそれに限定されず、各検出器・基板電極ペアは、電極ごとに複数の小径相互接続を用いて同様に容易に実施できることを理解されよう。電極ごとに複数の小径相互接続を用いると、より大きい高さ対幅のアスペクト比のインターポーザを用いることが可能になり、応力除去がより大きくなり、信頼性を改善する。例えば、複数の小径相互接続とすると、接続の冗長性によって信頼性が高まる。

#### 【 0 0 2 2 】

要約を述べると、本明細書に記載した本原理によるマクロピンハイブリッド相互接続アレイの実施形態は、結晶アノードアレイ及びセラミック基板を含む。このアレイ及び基板は、大きい高さ対幅のアスペクト比を有する相互接続幾何形状を用いて共に接合される。相互接続を結晶アノードアレイに固定する継手は、無はんだである。

#### 【 0 0 2 3 】

本明細書に記載した本原理により実施されるマクロピンハイブリッド相互接続アレイは、検出器結晶にあるパッドがフラックスのはんだに直接さらされないので、リフローはん

だプロセス中に非常に薄いAl電極の消耗に耐えるためにアノードパッドに対して複雑で独特なバンプ下地金属(UMB)構造を必要としないことで有利である。大きい高さ対幅のアスペクト比のバンプ又はピラー相互接続により、バンプ又はピラー相互接続がわずかに曲がって、はんだリフローに必要とされる熱サイクルの間に基板とのCTE不整合によって引き起こされる歪みを吸収することが可能になる。この特徴は、処理中に、検出器結晶の使用環境において割れやすい検出器結晶のひび割れを防ぐ。

#### 【0024】

バンプ又はピラー相互接続が、CZTに形成されると、処理の残りは、広く普及している製造装置を用いて実施できることが有利である。更に、バンプ又はピラー相互接続を形成するときに用いるめっきプロセスは、高価な装置又は専用の装置を特に必要とはしない。

10

#### 【0025】

検出器結晶は、本明細書に記載した本原理による処理中に最小限の機械的取扱いを受けることが有利である。更に、相互接続は、図1及び図2に関連して本明細書に記載したプロセスを利用するとき、アンダーフィルの前に手直しされてもよい。

#### 【0026】

更に、有利には、本明細書に記載した本原理により実施されるマクロピンハイブリッド相互接続アレイは、約0.050mmのピッチまでの非常に微小なピッチのアノードアレイを与えることができる。この特徴を実現するために用いる既知のプロセスは、この既知のプロセスが、非常に高価であり、従来の処理装置及び処理方法と相性が良くないという点において不利である。本明細書に記載した本原理により実施されるマクロピンハイブリッド相互接続アレイは、例えば、有利なことに、リフロープロセス中に自己整合性があり、これにより基板上の結晶の位置合わせ及び配置に必要な精度を小さくする。

20

本発明のいくつかの特徴だけを本明細書に例示及び記載したが、当業者は、多くの修正形態及び変更形態に想到するであろう。したがって、添付の特許請求の範囲は、本発明の本来の精神の範囲内に入るような修正形態及び変更形態の全てを対象として含むものであることが理解されよう。

#### 【符号の説明】

#### 【0027】

- |    |                    |    |

|----|--------------------|----|

| 10 | マクロピンハイブリッド相互接続アレイ | 30 |

| 12 | ピラー相互接続            |    |

| 14 | セラミック基板            |    |

| 15 | はんだ                |    |

| 16 | アノードパッド            |    |

| 18 | 結晶アノードアレイ          |    |

| 20 | フォトレジスト、フォトレジストシート |    |

| 22 | 開口部                |    |

| 24 | 回路メタライゼーション        |    |

| 30 | マクロピンハイブリッド相互接続アレイ |    |

| 32 | めっきピラー             | 40 |

| 34 | 基板パッド              |    |

| 36 | アンダーフィル            |    |

| 40 | マクロピンハイブリッド相互接続アレイ |    |

| 42 | めっきピラー             |    |

| 44 | 導電性エポキシ樹脂          |    |

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

---

フロントページの続き

(72)発明者 チャールズ・ジェラード・ウォイチク

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1-4エイ59、グローバル

・リサーチ、パテント・ドケット・ルーム（番地なし）

(72)発明者 ジョン・エリック・トカチク

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1-4エイ59、グローバル

・リサーチ、パテント・ドケット・ルーム（番地なし）

(72)発明者 ブライアン・デビッド・ヤノフ

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1-4エイ59、グローバル

・リサーチ、パテント・ドケット・ルーム（番地なし）

(72)発明者 タン・ツアン

アメリカ合衆国、ニューヨーク州、ニスカユナ、ビルディング・ケイ1-4エイ59、グローバル

・リサーチ、パテント・ドケット・ルーム（番地なし）

審査官 工藤 一光

(56)参考文献 特開2004-048012（JP, A）

米国特許出願公開第2007/0131868（US, A1）

特開平11-017309（JP, A）

特開2001-102481（JP, A）

特開2007-81380（JP, A）

特開2007-214191（JP, A）

特開2009-81153（JP, A）

特表2010-521587（JP, A）

(58)調査した分野(Int.Cl., DB名)

H01L21/60-21/607

H01L23/12-23/15

H01L23/50

G01T1/24