(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5899454号 (P5899454)

(45) 発行日 平成28年4月6日(2016.4.6)

(24) 登録日 平成28年3月18日 (2016.3.18)

(51) Int.Cl. F 1

HO2M

7/487

(2007.01)

HO2M

7/487

HO2M

7/48

(2007.01)

HO2M

7/48

請求項の数 8 (全 25 頁)

(21) 出願番号 特願2013-546971 (P2013-546971)

(86) (22) 出願日 平成24年11月15日 (2012.11.15)

(86) 国際出願番号 PCT/JP2012/007320

(87) 国際公開番号 W02013/080465

(87) 国際公開日 平成25年6月6日 (2013.6.6) 審査請求日 平成27年2月23日 (2015.2.23)

(31) 優先権主張番号 特願2011-262404 (P2011-262404)

(32) 優先日 平成23年11月30日 (2011.11.30)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 314012076

パナソニック I P マネジメント株式会社 大阪府大阪市中央区域見2 T 目1番61号

|(74)代理人 100105957

弁理士 恩田 誠

$\mathbf{F}$

|(74)代理人 100068755

弁理士 恩田 博宣

||(72)発明者 木寺 和憲

大阪府門真市大字門真1006番地 パナ

ソニック 株式会社 内

(72) 発明者 西 真理子

大阪府門真市大字門真1006番地 パナ

ソニック 株式会社 内

審査官 松本 泰典

最終頁に続く

## (54) 【発明の名称】インバータ装置の制御方法及びインバータ装置

## (57)【特許請求の範囲】

## 【請求項1】

インバータ装置の制御方法であって、

該インバータ装置は、複数のレベルの第1出力電圧を生成可能な第1のインバータと、前記第1のインバータと並列に接続され、複数のレベルの第2出力電圧を生成可能な第2のインバータと、前記第1出力電圧及び前記第2出力電圧を合成して正弦波形を有する出力電圧を生成するフィルター回路と、前記第1のインバータ及び前記第2のインバータを制御して、前記フィルター回路にて予め定められた正弦波形を有する出力電圧が生成されるように、前記第1のインバータに複数のレベルの第1出力電圧を生成させ、前記第2のインバータに複数のレベルの第2出力電圧を生成させる制御回路とを含み、

前記制御回路により、第1出力電圧のレベルを切り替えるように前記第1のインバータ を高周波でデューティー制御すること、

前記制御回路により、第2出力電圧のレベルを切り替えるように前記第2のインバータを制御すること

#### を備え、

前記第2のインバータを制御することは、前記第2のインバータが前記第2出力電圧の レベルを切り替える時に、前記第2のインバータを高周波でデューティー制御することを 含み、

前記制御回路により、前記第2のインバータを高周波でデューティー制御している間、 前記高周波でデューティー制御されている前記第1のインバータのデューティー制御を停

止させることを備える、インバータ装置の制御方法。

#### 【請求項2】

請求項1に記載のインバータ装置の制御方法において、

前記第1及び第2のインバータの各々は、3レベルインバータであり、直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとの間の接続点に接続されており、

前記第1及び第2のインバータが、前記接続点における電圧を用いて、3レベルの前記第1及び第2出力電圧を生成することを備える、インバータ装置の制御方法。

#### 【請求項3】

インバータ装置であって、

複数のレベルの第1出力電圧を生成可能な第1のインバータと、

前記第1のインバータと並列に接続され、複数のレベルの第2出力電圧を生成可能な第2のインバータと、

前記第1のインバータ及び前記第2のインバータに接続され、前記第1出力電圧及び前記第2出力電圧を合成して正弦波形を有する出力電圧を生成するフィルター回路と、

前記第1のインバータ及び前記第2のインバータを制御して、前記フィルター回路にて予め定められた正弦波形を有する出力電圧が生成されるように、前記第1のインバータに複数のレベルの第1出力電圧を生成させ、前記第2のインバータに複数のレベルの第2出力電圧を生成させる制御回路と

## を備え、

前記制御回路は、前記第1出力電圧のレベルを切り替えるように前記第1のインバータを高周波でデューティー制御するとともに、前記第2出力電圧のレベルを切り替えるように前記第2のインバータを制御し、

前記制御回路は、前記第2のインバータが前記第2出力電圧のレベルを切り替える時に、前記第2のインバータを高周波でデューティー制御し、

前記制御回路は、前記第2のインバータを高周波でデューティー制御している間、前記 高周波でデューティー制御させている前記第1のインバータのデューティー制御を停止さ せる、インバータ装置。

## 【請求項4】

インバータ装置であって、

複数のレベルの第1出力電圧を生成可能な第1のインバータと、

前記第1のインバータと並列に接続され、複数のレベルの第2出力電圧を生成可能な第 2のインバータと、

前記第1のインバータ及び前記第2のインバータに接続され、前記第1出力電圧及び前記第2出力電圧を合成して正弦波形を有する出力電圧を生成するフィルター回路と、

前記第1のインバータ及び前記第2のインバータを制御して、前記フィルター回路にて予め定められた正弦波形を有する出力電圧が生成されるように、前記第1のインバータに複数のレベルの第1出力電圧を生成させ、前記第2のインバータに複数のレベルの第2出力電圧を生成させる制御回路と

## を備え、

前記制御回路は、前記第1出力電圧のレベルを切り替えるように前記第1のインバータを高周波でデューティー制御するとともに、前記第2出力電圧のレベルを切り替えるように前記第2のインバータを制御し、

前記制御回路は、前記第2のインバータが前記第2出力電圧のレベルを切り替える時に 、前記第2のインバータを高周波でデューティー制御し、

前記制御回路は、

前記第2のインバータを高周波でデューティー制御している間、前記第1のインバータを高周波でデューティー制御する第1制御モードと、

前記第2のインバータを高周波でデューティー制御している間、前記第1のインバータのデューティー制御を停止させる第2制御モードと

10

20

30

40

を有している、インバータ装置。

## 【請求項5】

請求項3又は4に記載のインバータ装置において、

直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとを備 え、前記第1及び第2のインバータの各々は、3レベルインバータであり、かつ前記第1 コンデンサと前記第2コンデンサとの間の接続点に接続され、前記第1及び第2のインバ ータは、前記接続点における電圧を用いて、3レベルの前記第1及び第2出力電圧を生成 する、インバータ装置。

## 【請求項6】

請求項4に記載のインバータ装置において、

直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとを備 え、前記制御回路は、前記第1コンデンサと前記第2コンデンサとの間の接続点における 電圧に基づいて、制御モードを前記第1制御モード及び前記第2制御モードのいずれかに 切り替える、インバータ装置。

#### 【請求項7】

請求項5又は6に記載のインバータ装置において、

前記制御回路は、前記第1コンデンサと前記第2コンデンサとの間の接続点の電圧に基 づいて、前記第2のインバータの高周波でのデューティー制御を開始し、前記第2のイン バータを高周波でデューティー制御している間、前記第1のインバータのデューティー制 御を停止させる、インバータ装置。

### 【請求項8】

請求項5~7のいずれか1つに記載のインバータ装置において、

前記第1及び第2のインバータの各々は、

直列に接続された4個のスイッチング素子を含む第1の直列回路と、

直列に接続された2個のクランプダイオードを含む第2の直列回路と

## を含み、

前記4個のスイッチング素子は、上側アーム側の2個のスイッチング素子と、下側アー ム側の2個のスイッチング素子とを含み、前記2個のクランプダイオードは、上側アーム 側のクランプダイオードと、下側アーム側のクランプダイオードとを含み、

上側アーム側のクランプダイオードは、前記上側アーム側の2個のスイッチング間の接 続点に接続されたカソード端子を有し、前記下側アーム側のクランプダイオードは、前記 下側アーム側の2個のスイッチング素子間の接続点に接続されたアノード端子を有し、

前記2個のクランプダイオード間の接続点に、前記第1コンデンサと前記第2コンデン サとの間の接続点が接続され、前記上側アーム側の2個のスイッチング素子と前記下側ア ーム側の2個のスイッチング素子との間の接続点に前記フィルター回路が接続される、イ ンバータ装置。

## 【発明の詳細な説明】

## 【技術分野】

## [00001]

本発明は、インバータ装置の制御方法及びインバータ装置に関するものである。

## 【背景技術】

## [0002]

近年、マルチレベルインバータを含むインバータ装置は、インバータモータや太陽光発 電システムおけるパワーコンディショナーに益々利用されている(例えば、特許文献1) 。殊に、3レベルインバータは、2レベルインバータに比べて低い耐圧のスイッチング素 子を用いることができることから、注目されている。

## [0003]

3 レベルインバータは、直列に接続された4個のスイッチング素子と、直列接続された 2個のクランプダイオードとを含む。4個のスイッチング素子からなる直列回路は、直流 電源の電圧を分担する直列に接続された2個のコンデンサに対して並列に接続されている 10

20

30

40

。そして、4個のスイッチング素子の内、正極側の2個のスイッチング素子を上側アームのスイッチング素子といい、負極側の2個のスイッチング素子を下側アームのスイッチング素子という。

## [0004]

また、2個のクランプダイオードの接続点は、2個のコンデンサの接続点と接続されている。一方、正極側のクランプダイオードのカソード端子は、上側アームの2個のスイッチング素子の接続点に接続されている。負極側のクランプダイオードのアノード端子は、下側アームの2個のスイッチング素子の接続点に接続されている。

## [0005]

そして、 4 個のスイッチング素子のオン・オフを切り替えることによって、インバータ 装置は、上側アームと下側アームとの接続点において、 3 レベルの出力電圧を生成する。

#### [0006]

ところで、並列に接続された2個の3レベルインバータを含むインバータ装置も提案されている。このインバータ装置は、2個の3レベルインバータの上側アームと下側アームの接続点から出力された2つの3レベルの出力電圧を、フィルター回路に供給し、そのフィルター回路にて2つの3レベルの出力電圧を合成して正弦波を作ることができる。

## 【先行技術文献】

## 【特許文献】

#### [0007]

【特許文献1】特開2002-199738号公報

#### 【発明の概要】

【発明が解決しようとする課題】

### [0008]

ところで、この種の3レベルインバータは、直流電源の電圧を分担する直列に接続された2個のコンデンサにて等分に分割された電圧を受信し、該電圧から3レベルの出力電圧を生成することから、コンデンサの容量が出力電力に対して、十分に大きな値を有する必要があった。その結果、コンデンサが大型化しインバータ装置が大型化する問題があった

## [0009]

また、出力レベルを段階的に切り替える時に生じる出力波形の歪みを抑えるために、フィルター回路に設けられているAC(交流)リアクトルを大きくする必要があった。その結果、ACリアクトルが大型化しインバータ装置が大型化する問題があった。

## [0010]

複数個の並列に接続された3レベルインバータを含むインバータ装置においては、一方の3レベルインバータを高周波動作させ、他方の3レベルインバータを低周波動作させて、その出力の差分を出力電圧として用いて出力電圧を増加させる。この方法によって、電流を平滑化するACリアクトルを小型化したり、低周波動作する3レベルインバータのスイッチング回数を減らしたりして、スイッチングロスを少なくしインバータ装置の動作を高効率化することができる。

## [0011]

しかし、上記インバータ装置において、出力レベルを段階的に切り替える時には、その出力波形に歪みが発生していた。また、この種のインバータ装置においても、直流電源の電圧を分担する2個のコンデンサの値を大きくする必要があり、コンデンサの大型化、ひいては、インバータ装置の大型化につながっていた。

#### [0012]

本発明は、上記問題を解決するためになされたものであり、その目的は、出力波形の歪みを小さくでき、しかも、高効率で、小型化を実現できるインバータ装置の制御方法及びインバータ装置を提供することにある。

## 【課題を解決するための手段】

## [0013]

20

10

30

40

10

20

30

40

50

上記課題を解決するために、本発明の第1の側面によれば、インバータ装置の制御方法 であって、該インバータ装置は、複数のレベルの第1出力電圧を生成可能な第1のインバ ータと、前記第1のインバータと並列に接続され、複数のレベルの第2出力電圧を生成可 能な第2のインバータと、前記第1出力電圧及び前記第2出力電圧を合成して正弦波形を 有する出力電圧を生成するフィルター回路と、前記第1のインバータ及び前記第2のイン バータを制御して、前記フィルター回路にて予め定められた正弦波形を有する出力電圧が 生成されるように、前記第1のインバータに複数のレベルの第1出力電圧を生成させ、前 記第2のインバータに複数のレベルの第2出力電圧を生成させる制御回路とを含み、前記 制御回路により、第1出力電圧のレベルを切り替えるように前記第1のインバータを高周 波でデューティー制御すること、前記制御回路により、第2出力電圧のレベルを切り替え るように前記第2のインバータを制御することを備え、前記第2のインバータを制御する ことは、前記第2のインバータが前記第2出力電圧のレベルを切り替える時に、前記第2 のインバータを高周波でデューティー制御することを含み、 前記制御回路により、前記 第2のインバータを高周波でデューティー制御している間、前記高周波でデューティー制 御されている前記第1のインバータのデューティー制御を停止させることを備える、イン バータ装置の制御方法が提供される。

## [0015]

また、上記方法において、前記第1及び第2のインバータの各々は、3レベルインバータであり、直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとの間の接続点に接続されており、前記第1及び第2のインバータが、前記接続点における電圧を用いて、3レベルの前記第1及び第2出力電圧を生成することを備えることが好ましい。

## [0016]

上記課題を解決するために、本発明の第2の側面によれば、インバータ装置であって、複数のレベルの第1出力電圧を生成可能な第1のインバータと、前記第1のインバータと、前記第1のインバータと、前記第1のインバータと、前記第1のインバータと、前記第2のインバータに接続され、前記第1出力電圧及び前記第2出力電圧を生成するフィルター回路と、前記第1のインバータ及び前記第2のインバータに接続され、前記第1出力電圧及び前記第1のインバータ及び前記第2のインバータを制御して、前記フィルター回路にて予め定められた正弦波形を有する出力電圧が生成されるように、前記第1のインバータに複数のレベルの第1出力電圧を生成指せ、前記第2のインバータに複数のレベルの第2出力電圧を生成指せ、前記第2のインバータに複数のレベルの第2出力電圧を生成指せ、前記第1のインバータに複数のレベルを切り替えるように前記第2のインバータを制御し、前記第2出力電圧のレベルを切り替えるように前記第2のインバータを制御し、前記制御回路は、前記第2のインバータを高周波でデューティー制御し、前記制御回路は、前記第2のインバータを高周波でデューティー制御と停止させる、インバータ装置が提供される。

## [0018]

また、上記インバータ装置において、前記制御回路は、前記第2のインバータを高周波でデューティー制御している間、前記第1のインバータを高周波でデューティー制御する第1制御モードと、前記第2のインバータを高周波でデューティー制御している間、前記第1のインバータのデューティー制御を停止させる第2制御モードとを有していることが好ましい。

## [0019]

また、上記インバータ装置において、直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとを備え、前記第1及び第2のインバータの各々は、3レベルインバータであり、かつ前記第1コンデンサと前記第2コンデンサとの間の接続点に接続され、前記第1及び第2のインバータは、前記接続点における電圧を用いて、3レベルの前記第1及び第2出力電圧を生成することが好ましい。

#### [0020]

また、上記インバータ装置において、直列接続され、かつ直流電圧を等分に分担する第1コンデンサと第2コンデンサとを備え、前記制御回路は、前記第1コンデンサと前記第2コンデンサとの間の接続点における電圧に基づいて、制御モードを前記第1制御モード及び前記第2制御モードのいずれかに切り替えることが好ましい。

#### [0021]

また、上記インバータ装置において、前記制御回路は、前記第1コンデンサと前記第2コンデンサとの間の接続点の電圧に基づいて、前記第2のインバータの高周波でのデューティー制御を開始し、前記第2のインバータを高周波でデューティー制御している間、前記第1のインバータのデューティー制御を停止させることが好ましい。

#### [0022]

また、上記インバータ装置において、前記第1及び第2のインバータの各々は、直列に接続された4個のスイッチング素子を含む第1の直列回路と、直列に接続された2個のクランプダイオードを含む第2の直列回路とを含み、前記4個のスイッチング素子は、上側アーム側の2個のスイッチング素子と、下側アーム側の2のスイッチング素子とを含み、前記2個のクランプダイオードは、上側アーム側のクランプダイオードと、下側アーム側のクランプダイオードは、前記上側アーム側の2のスイッチング間の接続点に接続されたカソード端子を有し、前記下側アーム側のクランプダイオードは、前記下側アーム側の2個のスイッチング素子間の接続点に接続されたアノード端子を有し、前記2個のクランプダイオード間の接続点に、前記第1コンデンサと前記第2コンデンサとの間の接続点が接続され、前記上側アーム側の2個のスイッチング素子と前記下側アーム側の2個のスイッチング素子との間の接続点に前記フィッチング素子と前記下側アーム側の2個のスイッチング素子との間の接続点に前記フィッチング素子と前記下側アーム側の2個のスイッチング素子との間の接続点に前記フィー回路が接続されることが好ましい。

#### 【発明の効果】

#### [0023]

本発明によれば、インバータ装置において、出力波形の歪みを小さくでき、しかも、高 効率で、小型化を実現できる。

#### 【図面の簡単な説明】

## [0024]

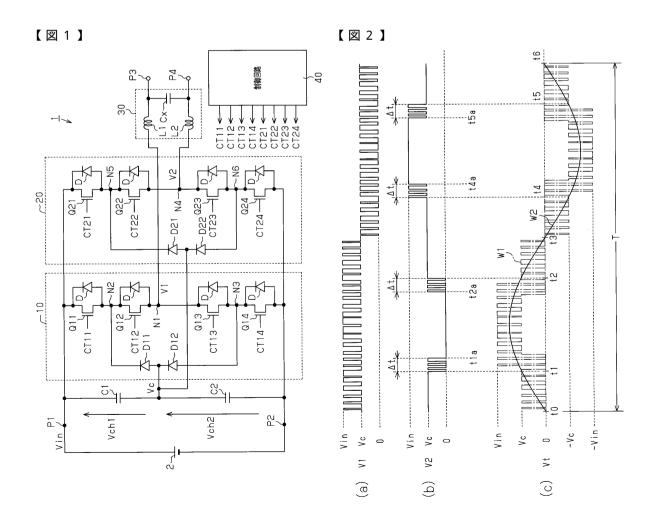

【図1】本発明の第1実施形態のインバータ装置の電気回路図。

【図2】本発明の第1実施形態のインバータ装置の作用を説明するための波形図であって、(a)は第1のインバータの第1出力電圧の波形図、(b)は第2のインバータの第2出力電圧の波形図、(c)はインバータ装置の出力電圧の波形図を示す。

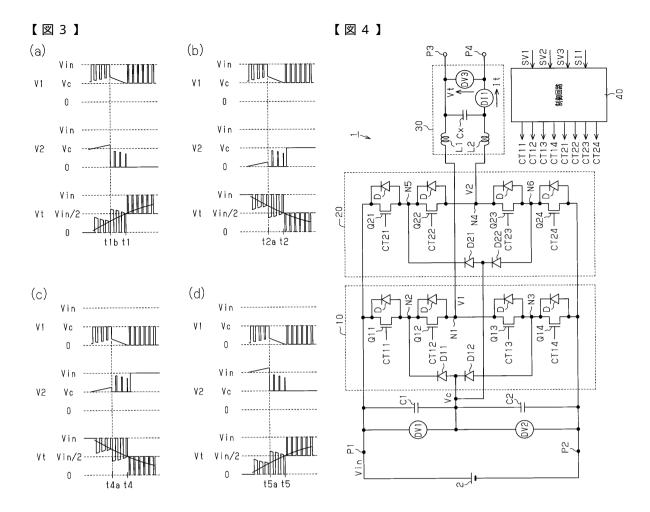

【図3】本発明の第2実施形態のインバータ装置の作用を説明するための波形図であって、(a)は時刻t1付近の電圧波形図、(b)は時刻t2付近の電圧波形図、(c)は時刻t4付近の電圧波形図、(d)は時刻t5付近の電圧波形図を示す。

【図4】本発明の第3実施形態のインバータ装置の電気回路図。

【発明を実施するための形態】

## [0025]

(第1実施形態)

以下、本発明の第1実施形態によるインバータ装置を図面に従って説明する。

#### [0026]

図1に示すように、インバータ装置1は、第1のインバータ10と第2のインバータ20とを含む。第1のインバータ10と第2のインバータ20とは、並列に接続されて、並列回路を形成し、その並列回路は、電源電圧Vinを生成する直流電源2の正極出力端子P1と負極出力端子P2との間に接続されている。

## [0027]

また、正極出力端子 P 1 と負極出力端子 P 2 との間には、同じ容量値を有する第 1 コンデンサ C 1 及び第 2 コンデンサ C 2 の直列回路が接続されている。第 1 及び第 2 コンデンサ C 1 、 C 2 の直列回路は、第 1 コンデンサ C 1 の一方の端子が正極出力端子 P 1 に接続

10

20

30

40

10

20

30

40

50

され、第2コンデンサC2の一方の端子が負極出力端子P2に接続されるように、直流電源2と直列に接続されている。第1コンデンサC1及び第2コンデンサC2は、同じ容量値を有するので、第1コンデンサC1の第1端子間電圧Vch1及び第2コンデンサC2の第2端子間電圧Vch2の各々は、直流電源2の電源電圧Vinの半分(=Vin/2)に等しい。

## [0028]

つまり、第1コンデンサC1と第2コンデンサC2との接続点を基準として、第1コンデンサC1及び第2コンデンサC2の各々は、直流電源2の電源電圧Vinを半分(=Vin/2)ずつ分担している。以下、電源電圧Vinの半分を、入力電圧Vcという。

## [0029]

(第1のインバータ10)

第1のインバータ10は、3レベルインバータであって、第1、第2、第3、及び第4スイッチング素子Q11,Q12,Q13,Q14を有している。各スイッチング素子Q11~Q14は、NチャネルのMOSトランジスタにて形成され、各MOSトランジスタのソース・ドレイン間にボディーダイオードDが接続されている。なお、第1実施形態では、各スイッチング素子Q11~Q14は、MOSトランジスタに具体化されているが、転流電流を流せるようにダイオードと並列に接続されたIGBT(Insulated Gate Bipolar Transistor)等、他のスイッチング素子で実施してもよい。

## [0030]

第1~第4スイッチング素子Q11~Q14は、第1スイッチング素子Q11、第2スイッチング素子Q12、第3スイッチング素子Q13、第4スイッチング素子Q14の順で直列に接続され、第1スイッチング素子Q11は、正極出力端子P1に接続されている。そして、第1~第4スイッチング素子Q11~Q14は、それらのドレイン端子が正極出力端子P1側に、また、ソース端子が負極出力端子P2側に配置されるように直列接続されている。

## [0031]

ちなみに、4個の第1~第4スイッチング素子Q11~Q14の内、正極側の第1及び第2スイッチング素子Q11,Q12を上側アームのスイッチング素子という。また、負極側の第3及び第4スイッチング素子Q13,Q14を下側アームのスイッチング素子という。そして、上側アームの第2スイッチング素子Q12と下側アームの第3スイッチング素子Q13の接続点(ノードN1)が出力端子として形成され、出力端子(ノードN1)がフィルター回路30に接続されている。

## [0032]

第1スイッチング素子Q11のゲート端子には、第1駆動信号CT11が供給される。 第1スイッチング素子Q11は、ハイ・レベルの第1駆動信号CT11でオンし、ロウ・ レベルの第1駆動信号CT11でオフする。

## [0033]

第2スイッチング素子Q12のゲート端子には、第2駆動信号CT12が供給される。 第2スイッチング素子Q12は、ハイ・レベルの第2駆動信号CT12でオンし、ロウ・ レベルの第2駆動信号CT12でオフする。

## [0034]

第3スイッチング素子Q13のゲート端子には、第3駆動信号CT13が供給される。 第3スイッチング素子Q13は、ハイ・レベルの第3駆動信号CT13でオンし、ロウ・ レベルの第3駆動信号CT13でオフする。

#### [0035]

第4スイッチング素子Q14のゲート端子には、第4駆動信号CT14が供給される。 第4スイッチング素子Q14は、ハイ・レベルの第4駆動信号CT14でオンし、ロウ・ レベルの第4駆動信号CT14でオフする。

## [0036]

第1のインバータ10は、第1クランプダイオードD11と第2クランプダイオードD

12とを含む。第1クランプダイオードD11と第2クランプダイオードD12とは、互いに直列に接続されている。

## [0037]

第1クランプダイオードD11は、上側アームの第1スイッチング素子Q11と第2スイッチング素子Q12の接続点(ノードN2)に接続されたカソード端子と、第2クランプダイオードD12のカソード端子に接続されたアノード端子とを有する。第2クランプダイオードD12は、第1クランプダイオードD11のアノード端子と接続されたカソード端子と、下側アームの第3スイッチング素子Q13と第4スイッチング素子Q14の接続点(ノードN3)に接続されたアノード端子とを有する。

#### [0038]

第 1 クランプダイオード D 1 1 と第 2 クランプダイオード D 1 2 の接続点は、第 1 コンデンサ C 1 と第 2 コンデンサ C 2 との接続点に接続されている。従って、第 1 クランプダイオード D 1 1 と第 2 クランプダイオード D 1 2 の接続点には、第 1 コンデンサ C 1 と第 2 コンデンサ C 2 との接続点からの入力電圧 V c ( = V i n / 2 )が印加される。

## [0039]

第1のインバータ10は、第1~第4スイッチング素子Q11~Q14のオン・オフが、適宜、切り替えられることにより、0ボルト、入力電圧Vc、及び電源電圧Vinの3段階の第1出力電圧V1を、出力端子(ノードN1)において生成することができる。

#### [0040]

つまり、第1及び第2スイッチング素子Q11,Q12がオフ、第3及び第4スイッチング素子Q13,Q14がオンの時には、出力端子(ノードN1)において生成される第 1出力電圧 V 1 は、 0 ボルトである。

## [0041]

また、第1及び第4スイッチング素子Q11,Q14がオフ、第2及び第3スイッチング素子Q12,Q13がオンの時には、出力端子(ノードN1)において生成される第1出力電圧V1は、入力電圧Vcと同じである。

## [0042]

さらに、第1及び第2スイッチング素子Q11,Q12がオン、第3及び第4スイッチング素子Q13,Q14がオフの時には、出力端子(ノードN1)において生成される第1出力電圧V1は電源電圧Vinと同じである。

### [0043]

## (第2のインバータ20)

第2のインバータ20は、3レベルインバータであって、第5、第6、第7、及び第8スイッチング素子Q21,Q22,Q23,Q24を含む。各スイッチング素子Q21~Q24は、NチャネルのMOSトランジスタにて形成され、各MOSトランジスタのソース・ドレイン間にボディーダイオードDが接続されている。なお、第1実施形態では、各スイッチング素子Q21~Q24は、MOSトランジスタに具体化されているが、転流電流を流せるようにダイオードと並列に接続されたIGBT (Insulated Gate Bipolar Transistor)等、他のスイッチング素子で実施してもよい。

## [0044]

第5~第8スイッチング素子Q21~Q24は、第5スイッチング素子Q21、第6スイッチング素子Q22、第7スイッチング素子Q23、第8スイッチング素子Q24の順で直列に接続され、第5スイッチング素子Q21は、正極出力端子P1に接続されている。そして、第5~第8スイッチング素子Q21~Q24は、それらのドレイン端子が正極出力端子P1側に、また、ソース端子が負極出力端子P2側に配置されるように直列接続されている。

## [0045]

ちなみに、4個の第5~第8スイッチング素子Q21~Q24の内、正極側の第5及び第6スイッチング素子Q21,Q22を上側アームのスイッチング素子という。また、負極側の第7及び第8スイッチング素子Q23,Q24を下側アームのスイッチング素子と

10

20

30

40

(9)

いう。そして、上側アームの第6スイッチング素子Q22と下側アームの第7スイッチング素子Q23の接続点(ノードN4)が出力端子として形成され、出力端子(ノードN4)がフィルター回路30に接続されている。

#### [0046]

第5スイッチング素子Q21のゲート端子には、第5駆動信号CT21が供給される。 第5スイッチング素子Q21は、ハイ・レベルの第5駆動信号CT21でオンし、ロウ・ レベルの第5駆動信号CT21でオフする。

## [0047]

第6スイッチング素子Q22のゲート端子には、第6駆動信号CT22が供給される。 第6スイッチング素子Q22は、ハイ・レベルの第6駆動信号CT22でオンし、ロウ・ レベルの第6駆動信号CT22でオフする。

[0048]

第7スイッチング素子Q23のゲート端子には、第7駆動信号CT23が供給される。 第7スイッチング素子Q23は、ハイ・レベルの第7駆動信号CT23でオンし、ロウ・ レベルの第7駆動信号CT23でオフする。

[0049]

第8スイッチング素子Q24のゲート端子には、第8駆動信号CT24が供給される。 第8スイッチング素子Q24は、ハイ・レベルの第8駆動信号CT24でオンし、ロウ・ レベルの第8駆動信号CT24でオフする。

[0050]

第2のインバータ20は、第3クランプダイオードD21と第4クランプダイオードD22とを含む。第3クランプダイオードD21と第4クランプダイオードD22とは、互いに直列に接続されている。

[0051]

第3クランプダイオードD21は、上側アームの第5スイッチング素子Q21と第6スイッチング素子Q22の接続点(ノードN5)に接続されたカソード端子と、第4クランプダイオードD22のカソード端子に接続されたアノード端子とを有する。第4クランプダイオードD22は、第3クランプダイオードD21のアノード端子と接続されたカソード端子と、下側アームの第7スイッチング素子Q23と第8スイッチング素子Q24の接続点(ノードN6)に接続されたアノード端子とを有する。

[0052]

第 3 クランプダイオード D 2 1 と第 4 クランプダイオード D 2 2 の接続点は、第 1 コンデンサ C 1 と第 2 コンデンサ C 2 との接続点に接続されている。従って、第 3 クランプダイオード D 2 1 と第 4 クランプダイオード D 2 2 の接続点には、第 1 コンデンサ C 1 と第 2 コンデンサ C 2 との接続点からの入力電圧 V c ( = V i n / 2 )が印加される。

[0053]

第2のインバータ20は、第5~第8スイッチング素子Q21~Q24のオン・オフが、適宜、切り替えられることにより、0ボルト、入力電圧Vc、及び電源電圧Vinの3段階の第2出力電圧V2を、出力端子(ノードN4)において生成することができる。

[0054]

つまり、第 5 及び第 6 スイッチング素子 Q 2 1 , Q 2 2 がオフ、第 7 及び第 8 スイッチング素子 Q 2 3 , Q 2 4 がオンの時には、出力端子(ノード N 4 ) において生成される第 2 出力電圧 V 2 は 0 ボルトである。

[0055]

また、第5及び第8スイッチング素子Q21,Q24がオフ、第6及び第7スイッチング素子Q22,Q23がオンの時には、出力端子(ノードN4)において生成される第2出力電圧V2は入力電圧Vcと同じである。

[0056]

さらに、第5及び第6スイッチング素子Q21,Q22がオン、第7及び第8スイッチング素子Q23,Q24がオフの時には、出力端子(ノードN4)において生成される第

10

20

30

40

2出力電圧 V 2 は電源電圧 Vinと同じである。

## [0057]

そして、第1のインバータ10にて生成された第1出力電圧V1と、第2のインバータ 20にて生成された第2出力電圧V2とがフィルター回路30に供給される。

## [0058]

(フィルター回路30)

フィルター回路30は、図2(a)に示される第1のインバータ10から供給される第1出力電圧V1と、図2(b)に示される第2のインバータ20から供給される第2出力電圧V2を合成し、図2(c)に示される出力電圧Vtを生成する。フィルター回路30は、図2(c)に1点鎖線で示される、第1出力電圧V1と第2出力電圧V2との差分である合成波形W1をフィルタリングして、図2(c)に実線で示される正弦波形W2の出力電圧Vt(=V1・V2)を供給する。

#### [0059]

フィルター回路30は、第1交流リアクトルL1、第2交流リアクトルL2及び平滑用コンデンサC×を含む。第1交流リアクトルL1は、第1のインバータ10の出力端子(ノードN1)と、第1出力端子P3との間に接続されている。第2交流リアクトルL2は、第2のインバータ20の出力端子(ノードN4)と、第2出力端子P4との間に接続されている。平滑用コンデンサC×は、第1出力端子P3と第2出力端子P4との間に接続されている。

## [0060]

そして、第1交流リアクトルL1に第1のインバータ10からの第1出力電圧V1が印加され、第2交流リアクトルL2に第2のインバータ20からの第2出力電圧V2が印加される。そして、フィルター回路30は、第1出力電圧V1と第2出力電圧V2とを合成し、第1及び第2出力端子P3,P4間から、図2(c)に示される正弦波形W2を有する出力電圧Vtを供給する。

## [0061]

インバータ装置1は、制御回路40を含む。

#### [0062]

制御回路40は、フィルター回路30の第1及び第2出力端子P3,P4間から、図2(c)に示される正弦波形W2の出力電圧Vtを供給するための第1~第8駆動信号CT11~CT14,CT21~CT24を生成する。

## [0063]

制御回路40は、第1のインバータ10の第1~第4スイッチング素子Q11~Q14を、高周波にてオン・オフ動作させて、第1のインバータ10から3段階のレベルの第1出力電圧V1を供給するための第1~第4駆動信号CT11~CT14を生成する。

#### [0064]

詳述すると、図2(a)に示すように、制御回路40は、正弦波形W2の出力電圧Vtを生成するために、1周期Tの前半周期において、入力電圧Vcと電源電圧Vinとの間で、第1出力電圧V1がデューティー制御されるように、第1~第4駆動信号CT11~CT14を生成する。また、制御回路40は、正弦波形W2の出力電圧Vtを生成するために、残り後半周期において、0ボルトと入力電圧Vcとの間で、第1出力電圧V1がデューティー制御されるように、第1~第4駆動信号CT11~CT14を生成する。

## [0065]

そして、第1実施形態では、正弦波形W2の出力電圧Vtの1周期Tである時刻t0から時刻t6は予め決められている。この時刻t0~t6は、フィルター回路30に接続された負荷(図示せず)に対して供給される出力電圧Vtの図2(c)に示される正弦波形W2から予め理論的に、又は実験、試験等により求められる。ここで、正弦波形W2の半周期の時刻は、時刻t3(=t6/2)である。

#### [0066]

制御回路40は、第1のインバータ10の第1出力電圧V1が、第2のインバータ20

20

10

30

40

の第2出力電圧 V 2 と合成されて、予め定められた正弦波形 W 2 の出力電圧 V t を生成すべく、第1出力電圧 V 1 が高周波でデューティー制御されるように第1のインバータ10を制御する。そこで、制御回路 4 0 は、図2 (a)に示すように、時刻 t 0 ~ t 3 の期間では、第1出力電圧 V 1 が入力電圧 V c と電源電圧 V t 1 n の間でデューティー制御されるように第1のインバータ10を制御する。また、制御回路 40 は、時刻 t 3 ~ t 6 の期間では、第1出力電圧 V 1 が 0 ボルトと入力電圧 V c の間でデューティー制御されるように第1のインバータ10を制御する。

## [0067]

ここで、時刻 t 0 ~ t 6 の期間での、第 1 のインバータ 1 0 のデューティー制御は、高周波のデューティー制御である。

10

## [0068]

第1実施形態では、その時々の、第1のインバータ10に対するデューティー制御のパターンが決められている。このパターンは、フィルター回路30に接続された負荷に供給される出力電圧Vtが、図2(c)に示す正弦波形W2を有するように、予め理論的に、又は実験、試験等により求められる。そして、そのパターンのデータが制御回路40のメモリに記憶されている。

## [0069]

第1実施形態では、予め定められたパターンにてデューティー制御が行なわれている。これを、出力電圧Vtが、図2(c)に実線で示される予め定められた正弦波形W2となるように、その時々の出力電圧Vtをモニタし、フィードバックすることにより、デューティー制御を行うようにしてもよい。

20

#### [0070]

一方、制御回路40は、第1のインバータ10の第1出力電圧V1と第2のインバータ20の第2出力電圧V2との合成により正弦波形W2の出力電圧Vtを出力するために、1周期T中の所定のタイミングで、第2出力電圧V2のレベルを3段階に切り替えるように第2のインバータ20を制御する。

### [0071]

制御回路40は、0ボルト、入力電圧Vc、電源電圧Vinの3種類の第2出力電圧V2を生成するように第2のインバータ20を制御する。ここで、第2出力電圧V2のレベルの切り替えは、正弦波形W2を有する出力電圧Vtが、+Vc及び-Vcに近づく(通過する)タイミングで行なわれる。

30

## [0072]

第2出力電圧 V 2 のレベルの切り替えのタイミングは、以下のように設定する。図 2 (c)に示されるように、出力電圧 V t の正弦波形 W 2 について、時刻 t 0 から時刻 t 6 で 1 周期 T が設定され(すなわち、T = t 6 - t 0)、時刻 t 0 から時刻 t 3 で半周期が設定される(すなわち、T / 2 = t 3 - t 0)。

## [0073]

そして、時刻 t 1 において、正弦波形W 2 の出力電圧 V t が、最大値に向かって入力電圧 V c のレベルを通過する。

## [0074]

40

50

また、時刻 t 2 において、正弦波形W 2 の出力電圧 V t が、 0 ボルトに向かって入力電圧 V c のレベルを通過する。

## [0075]

## [0076]

さらにまた、時刻 t 5 において、正弦波形W 2 の出力電圧 V t が、 0 ボルトに向かって 負の入力電圧 - V c のレベルを通過する。

#### [0077]

この時刻 t 1、 t 2、 t 4、 t 5 の直前又は直後では、第 1 のインバータ 1 0 のデュー

ティー制御だけでは、正弦波形W2の出力電圧Vtを生成できない。そのため、第2出力電圧V2のレベルを切り替える時、第2のインバータ20においてもデューティー制御を行うことにより、正弦波形W2の出力電圧Vtが生成される。ここでの、第2のインバータ20のデューティー制御は、高周波のデューティー制御である。

## [0078]

つまり、制御回路40は、第2のインバータ20の第2出力電圧V2が、第1のインバータ10の第1出力電圧V1と合成されることにより、フィルター回路30から供給される出力電圧Vtが予め定められた正弦波形W2を有するように、第2のインバータ20を高周波でデューティー制御する。

## [0079]

第1実施形態では、第2のインバータ20の、高周波でのデューティー制御のパターンが決められている。このパターンは、フィルター回路30に接続された負荷に供給される出力電圧Vtが、図2(c)に示す正弦波形W2を有するように、予め理論的に、又は実験、試験等により求められる。そして、そのパターンのデータが、制御回路40のメモリに記憶されている。

#### [0800]

詳述すると、図 2 ( b ) に示すように、制御回路 4 0 は、時刻 t 0 ~ t 6 で設定された 1 周期 T における、時刻 t 1 、時刻 t 2 、時刻 t 4 、時刻 t 5 の各時刻において、該時刻 を基準に予め定められた時間幅 t を設定している。そして、制御回路 4 0 は、その各時刻 t 1 , t 2 , t 4 , t 5 を基準に予め定められた時間幅 t で、第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 を高周波で動作させた後に、第 2 出力電圧 V 2 のレベルを切り替える。

## [0081]

この時間幅 tは、フィルター回路30に接続された負荷に対して、フィルター回路30の出力電圧Vtが、図2(c)に示される正弦波形W2を有するように、予め理論的に、又は実験、試験等により求められる。

### [0082]

そして、制御回路 4 0 は、時刻 t 0 ~ t 1 までの間、第 2 出力電圧 V 2 が入力電圧 V c に維持されるように、第 5 ~ 第 8 駆動信号 C T 2 1 ~ C T 2 4 を生成する。続いて、制御回路 4 0 は、時刻 t 1 ~ t 1 a (= t 1 + t)までの間、 0 ボルトと入力電圧 V c の間で、第 2 出力電圧 V 2 が高周波でデューティー制御されるように、第 5 ~ 第 8 駆動信号 C T 2 1 ~ C T 2 4 を生成する。

### [0083]

次に、制御回路40は、時刻t1a~t2a(= t2・ t)までの間、第2出力電圧 V2が0ボルトに維持されるように、第5~第8駆動信号CT21~CT24を生成する。続いて、制御回路40は、時刻t2a~t2までの間、0ボルトと入力電圧Vcの間で、第2出力電圧V2が高周波でデューティー制御されるように、第5~第8駆動信号CT 21~CT24を生成する。

## [0084]

次に、制御回路40は、時刻t2~t4a(=t4・ t)までの間、第2出力電圧V2が入力電圧Vcに維持されるように、第5~第8駆動信号CT21~CT24を生成する。続いて、制御回路40は、時刻t4a~t4までの間、入力電圧Vcと電源電圧Vinの間で、第2出力電圧V2が高周波でデューティー制御されるように、第5~第8駆動信号CT21~CT24を生成する。

## [0085]

次に、制御回路40は、時刻t4~t5a(=t5- t)までの間、第2出力電圧V2が電源電圧Vinに維持されるように、第5~第8駆動信号CT21~CT24を生成する。続いて、制御回路40は、時刻t5a~t5までの間、入力電圧Vcと電源電圧Vinの間で、第2出力電圧V2が高周波でデューティー制御されるように、第5~第8駆動信号CT21~CT24を生成する。

10

20

30

40

[0086]

最後に、制御回路40は、時刻t5~t6(=t0)の間、第2出力電圧V2が入力電圧Vcに維持されるように、第5~第8駆動信号CT21~CT24を生成する。

[0087]

そして、第1のインバータ10の第1出力電圧V1と第2のインバータ20の第2出力電圧V2とが、フィルター回路30に供給される。これによって、フィルター回路30の第1及び第2出力端子P3,P4の間に生成される出力電圧Vtは、第1出力電圧V1と第2出力電圧V2の差分に等しい。その結果、図2(c)に示されるように、出力電圧Vt(=V1-V2)は、正弦波形W2を有する。

[0088]

次に、上記のように構成されたインバータ装置1の作用について説明する。

[0089]

(第1のインバータ10)

(時刻t0~t3)

今、時刻 t 0 ~ t 3 の間、制御回路 4 0 は、第 1 のインバータ 1 0 に対して高周波で第 1 ~ 第 4 スイッチング素子 Q 1 1 ~ Q 1 4 をデューティー制御して、入力電圧 V c と電源電圧 V i n の間のレベルでデューティー制御された第 1 出力電圧 V 1 を生成する。

[0090]

つまり、時刻 t 0 ~ t 3 間においては、第 2 スイッチング素子 Q 1 2 がオンに保持され、第 4 スイッチング素子 Q 1 4 がオフに保持されている。そして、第 1 スイッチング素子 Q 1 1 と第 3 スイッチング素子 Q 1 3 が、相補的にオン・オフされる。

[0091]

ちなみに、第1スイッチング素子Q11がオフされ、第3スイッチング素子Q13がオンされた時、第1出力電圧V1は入力電圧Vcと同じである。反対に、第1スイッチング素子Q11がオンされ、第3スイッチング素子Q13がオフされた時、第1出力電圧V1は電源電圧Vinと同じである。

[0092]

(時刻t3~t6)

[0093]

つまり、時刻 t 3 ~ t 6 間においては、第 1 スイッチング素子 Q 1 1 がオフに保持され、第 3 スイッチング素子 Q 1 3 がオンに保持されている。そして、第 2 スイッチング素子 Q 1 2 と第 4 スイッチング素子 Q 1 7 と第 4 スイッチング素子 Q 1 7 と第 4 スイッチング素子 Q 1 8 が、相補的にオン・オフされる。

[0094]

ちなみに、第2スイッチング素子Q12がオフされ、第4スイッチング素子Q14がオンされた時、第1出力電圧V1は0ボルトである。反対に、第2スイッチング素子Q12がオンされ、第4スイッチング素子Q14がオフされた時、第1出力電圧V1は入力電圧Vcと同じである。

[0095]

このように、制御回路40は、時刻t0~t6を1周期Tとして、第1のインバータ1 0の第1~第4スイッチング素子Q11~Q14を繰り返し駆動制御し、図2(a)に示される波形の第1出力電圧V1を繰り返し、フィルター回路30に供給する。

[0096]

(第2のインバータ20)

(時刻t0~t1)

一方、時刻 t 0 ~ t 1 の間、制御回路 4 0 は、第 2 のインバータ 2 0 に、入力電圧 V c と同じ第 2 出力電圧 V 2 を生成させる。

[0097]

10

20

30

40

10

20

30

40

つまり、時刻 t 0 ~ t 1 においては、制御回路 4 0 は、第 5 及び第 8 スイッチング素子 Q 2 1 , Q 2 4 をオフに固定し、第 6 及び第 7 スイッチング素子 Q 2 2 , Q 2 3 をオンに 固定する。

## [0098]

(時刻t1~t1a)

時刻 t 1 ~ t 1 a の間(t 1 a - t 1 = t)、制御回路 4 0 は、第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子Q 2 1 ~ Q 2 4 を高周波でデューティー制御する。そして、 0 ボルトと入力電圧 V c の間のレベルでデューティー制御された第 2 出力電圧 V 2 が生成される。

## [0099]

つまり、時刻 t 1 ~ t 1 a においては、第 5 スイッチング素子 Q 2 1 がオフに保持され、第 7 スイッチング素子 Q 2 3 がオンに保持される。一方、第 6 スイッチング素子 Q 2 2 と第 8 スイッチング素子 Q 2 4 とが、相補的にオン・オフされる。

## [0100]

ちなみに、第6スイッチング素子Q22がオフされ、第8スイッチング素子Q24がオンされた時、第2出力電圧V2は0ボルトである。反対に、第6スイッチング素子Q22がオンされ、第8スイッチング素子Q24がオフされた時、第2出力電圧V2は入力電圧Vcと同じである。

#### [0101]

これによって、第1のインバータ10のデューティー制御に加えて、第2のインバータ 20においてもデューティー制御が行なわれることから、第2出力電圧V2が切り替わっ ても、出力電圧Vtは、出力電圧Vtの正弦波形W2が歪むことなく、緩やかに入力電圧 Vcを通過する。

#### [0102]

(時刻t1a~t2a)

時刻 t 1 a ~ t 2 a の間、制御回路 4 0 は、第 2 のインバータ 2 0 に、 0 ボルトである第 2 出力電圧 V 2 を生成させる。つまり、時刻 t 1 a ~ t 2 a においては、制御回路 4 0 は、第 5 及び第 6 スイッチング素子 Q 2 1 , Q 2 2 をオフに固定し、第 7 及び第 8 スイッチング素子 Q 2 3 , Q 2 4 をオンに固定する。

## [0103]

(時刻t2a~t2)

時刻 t 2 a ~ t 2 の間 ( t 2 - t 2 a = t )、制御回路 4 0 は、第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 を高周波でデューティー制御する。そして、 0 ボルトと入力電圧 V c の間のレベルでデューティー制御された第 2 出力電圧 V 2 が生成される。

## [0104]

つまり、時刻 t 2 a ~ t 2 においては、第 5 スイッチング素子 Q 2 1 がオフに保持され、第 7 スイッチング素子 Q 2 3 がオンに保持されている。一方、第 6 スイッチング素子 Q 2 と第 8 スイッチング素子 Q 2 とが、相補的にオン・オフされる。

## [0105]

ちなみに、第6スイッチング素子Q22がオフされ、第8スイッチング素子Q24がオンされた時、第2出力電圧V2は0ボルトである。反対に、第6スイッチング素子Q22がオンされ、第8スイッチング素子Q24がオフされた時、第2出力電圧V2は入力電圧Vcと同じである。

#### [0106]

これによって、第1のインバータ10のデューティー制御に加えて、第2のインバータ20においてもデューティー制御が行なわれることから、第2出力電圧V2が切り替わっても、出力電圧Vtは、出力電圧Vtの正弦波形W2が歪むことなく、緩やかに入力電圧Vcを通過する。

## [0107]

(時刻t2~t4)

時刻 t 2 ~ t 4 の間、制御回路 4 0 は、第 2 のインバータ 2 0 に、入力電圧 V c と同じ第 2 出力電圧 V 2 を生成させる。つまり、時刻 t 2 ~ t 4 a においては、制御回路 4 0 は、第 5 及び第 8 スイッチング素子 Q 2 1 , Q 2 4 をオフに固定し、第 6 及び第 7 スイッチング素子 Q 2 2 , Q 2 3 をオンに固定する。

### [0108]

(時刻t4~t4a)

時刻 t 4 ~ t 4 a の間 ( t 4 a - t 4 = t )、制御回路 4 0 は、第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 を高周波でデューティー制御する。そして、入力電圧 V c と電源電圧 V i n の間のレベルでデューティー制御された第 2 出力電圧 V 2 が生成される。

[0109]

つまり、時刻 t 4 ~ t 4 a においては、第 6 スイッチング素子 Q 2 2 がオンに保持され、第 8 スイッチング素子 Q 2 4 がオフに保持されている。一方、第 5 スイッチング素子 Q 2 1 と第 7 スイッチング素子 Q 2 3 とが、相補的にオン・オフされる。

[0110]

ちなみに、第5スイッチング素子Q21がオフされ、第7スイッチング素子Q23がオンされた時、第2出力電圧V2は入力電圧Vcと同じである。反対に、第5スイッチング素子Q21がオンされ、第7スイッチング素子Q23がオフされた時、第2出力電圧V2は電源電圧Vinと同じである。

[0111]

これによって、第1のインバータ10のデューティー制御に加えて、第2のインバータ20においてもデューティー制御が行なわれることから、第2出力電圧 V2が切り替わっても、出力電圧 Vtは、出力電圧 Vtの正弦波形W2が歪むことなく、緩やかに負の入力電圧 - Vcを通過する。

[0112]

(時刻t4a~t5a)

時刻 t 4 a ~ t 5 a の間、制御回路 4 0 は、第 2 のインバータ 2 0 に、電源電圧 V i n と同じ第 2 出力電圧 V 2 を生成させる。つまり、時刻 t 4 ~ t 5 a においては、制御回路 4 0 は、第 5 及び第 6 スイッチング素子 Q 2 1 , Q 2 2 をオンに固定し、第 7 及び第 8 スイッチング素子 Q 2 3 , Q 2 4 をオフに固定する。

[0113]

(時刻t5a~t5)

時刻 t 5 a ~ t 5 の間 ( t 5 - t 5 a = t )、制御回路 4 0 は、第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 を高周波でデューティー制御する。そして、入力電圧 V c と電源電圧 V i n の間のレベルでデューティー制御された第 2 出力電圧 V 2 が生成される。

[0114]

つまり、時刻 t 5 a ~ t 5 においては、第 6 スイッチング素子 Q 2 2 がオンに保持され、第 8 スイッチング素子 Q 2 4 がオフに保持されている。一方、第 5 スイッチング素子 Q 2 1 と第 7 スイッチング素子 Q 2 3 とが、相補的にオン・オフされる。

[0115]

ちなみに、第5スイッチング素子Q21がオフされ、第7スイッチング素子Q23がオンされた時、第2出力電圧V2は入力電圧Vcと同じである。反対に、第5スイッチング素子Q21がオンされ、第7スイッチング素子Q23がオフされた時、第2出力電圧V2は電源電圧Vinと同じである。

[0116]

これによって、第1のインバータ10のデューティー制御に加えて、第2のインバータ 20においてもデューティー制御が行なわれることから、第2出力電圧V2が切り替わっても、出力電圧Vtは、出力電圧Vtの正弦波形W2が歪むことなく、緩やかに負の入力

10

20

30

40

電圧 - V c を通過する。

## [0117]

(時刻t5~t6)

時刻 t 5 ~ t 6 ( = t 0 ) の間、制御回路 4 0 は、第 2 のインバータ 2 0 に、入力電圧 V c と同じ第 2 出力電圧 V 2 を生成させる。つまり、時刻 t 5 ~ t 6 においては、制御回路 4 0 は、第 5 及び第 8 スイッチング素子 Q 2 1 , Q 2 4 をオフに固定し、第 6 及び第 7 スイッチング素子 Q 2 2 , Q 2 3 をオンに固定する。

## [0118]

このように、制御回路 4 0 は、時刻 t 0 ~ t 6 を 1 周期 T として、第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 を繰り返し駆動制御し、図 2 ( b ) に示される波形を有する第 2 出力電圧 V 2 を繰り返し、フィルター回路 3 0 に供給する。

## [0119]

フィルター回路30は、第1出力電圧V1と第2出力電圧V2を受信して合成し、出力電圧Vtを生成する。そして、フィルター回路30は、図2(c)に破線で示される第1出力電圧V1と第2出力電圧V2との差分である合成波形W1をフィルタリングして、図2(c)に実線で示される正弦波形W2を有する出力電圧Vtを生成する。

## [0120]

この時、制御回路40は、第2出力電圧V2のレベルをあるレベルから別のレベルに切り替える時に、第5~第8スイッチング素子Q21~Q24を高周波で動作させたので、このレベルの切り替えに起因して発生する出力電圧Vtの正弦波形W2の歪みが抑えられる。

### [0121]

次に、上記のように構成されたインバータ装置1の効果について以下に記載する。

#### [0122]

(1)第1実施形態によれば、予め定められた正弦波形W2の出力電圧Vtを生成するために、高周波でデューティー制御される第1のインバータ10に対して、第2のインバータ20の第2出力電圧V2が、0ボルト、入力電圧Vc、電源電圧Vinの3種類の間で切り替えられる。そのため、第2のインバータ20の第5~第8スイッチング素子Q21~Q24のスイッチング回数を少なくでき、スイッチングロスを低減させることができ、高効率のインバータ装置1を実現できる。

## [0123]

(2)第1実施形態によれば、第2出力電圧V2のレベルの切り替えが行なわれる時刻t1~t1~t1a、時刻t2a~t2、時刻t4~t4a、時刻t5a~t5に、第2のインバータ20が高周波動作させられる。その結果、第2出力電圧V2のレベルが段階的に大きく変化することに起因して生じる出力電圧Vtの正弦波形W2の歪を小さく抑えることができる。

## [0124]

(3)第1実施形態によれば、第1のインバータ10の第1出力電圧V1と第2のインバータ20の出力電圧V2とを合成することで、5種類のレベルの出力電圧Vt(=V1-V2)が生成された。つまり、電源電圧Vin、入力電圧Vc、0ボルト、負の入力電圧・Vc、負の電源電圧・Vinを含む5つの出力レベルの出力電圧Vtを生成することにより正弦波形W2を形成するようにしたので、フィルター回路30の第1及び第2交流リアクトルL1,L2を小さくできる。その結果、インバータ装置1を小型化することができる。

## [0125]

(第2実施形態)

次に、本発明の第2実施形態のインバータ装置について図3に従って説明する。

#### [0126]

第 2 実施形態のインバータ装置は、第 1 のインバータ 1 0 の第 1 ~ 第 4 スイッチング素 子 Q 1 1 ~ Q 1 4 と第 2 のインバータ 2 0 の第 5 ~ 第 8 スイッチング素子 Q 2 1 ~ Q 2 4 10

20

30

40

の駆動制御において、第1実施形態のインバータ装置と相違している。

## [0127]

第2実施形態のインバータ装置においては、第1及び第2出力電圧 V 1 , V 2 のその時々の変動に対して、第1コンデンサ C 1 と第2コンデンサ C 2 との接続点の入力電圧 V c が変動しても、出力電圧 V t の歪みが抑えられるように、第1~第8スイッチング素子 Q 1 1 ~ Q 1 4 , Q 2 1 ~ Q 2 4 が駆動制御される。

#### [0128]

従って、第2実施形態は、制御回路40による、第1のインバータ10の第1~第4スイッチング素子Q11~Q14、及び第2のインバータ20の第5~第8スイッチング素子Q21~Q24の制御方法においてのみ、第1実施形態と相違し、他の構成は基本的に同じである。そのため、説明の便宜上、異なる制御回路40の制御方法のみ詳細に説明し、共通する部分の説明は省略する。

## [0129]

(時刻t0~t1b(=t1- t))(図3(a)参照)

制御回路40は、第1実施形態と同様に、第1のインバータ10の第1~第4スイッチング素子Q11~Q14を高周波でデューティー制御する。そして、制御回路40は、第1のインバータ10に、入力電圧Vcと電源電圧Vinの間のレベルでデューティー制御された第1出力電圧V1を生成させる。一方、制御回路40は、第1実施形態と同様に、第5及び第8スイッチング素子Q21,Q24をオフに固定し、第6及び第7スイッチング素子Q22,Q23をオンに固定する。そして、制御回路40は、第2のインバータ20に、入力電圧Vcと同じ第2出力電圧V2を生成させる。

#### [0130]

この時、第1コンデンサC1と第2コンデンサC2の容量値が小さいと、第1コンデンサC1の電荷が放電され、時刻t1に近づくにつれて、第1コンデンサC1の第1端子間電圧Vch1が下がり、第2コンデンサC2の第2端子間電圧Vch2が上がる。

## [0131]

これによって、図3 (a)に示すように、デューティー制御された第1のインバータ10の第1出力電圧 V1の振幅は次第に小さくなり、反対に、第2のインバータ20の第2出力電圧 V2のレベルは次第に大きくなる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧 Vcは、電源電圧 Vinの2分の1にならなくなり、それ以上に高くなる。

## [0132]

(時刻t1b~t1)

制御回路40は、時刻t1bに到達すると、第1及び第4スイッチング素子Q11,Q14をオフ、第2及び第3スイッチング素子Q12,Q13をオンに固定して、第1のインバータ10に、入力電圧Vcと同じ第1出力電圧V1を生成させる。この制御は、時刻t1になるまで実行される。一方、制御回路40は、第2のインバータ20の第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御して、第2のインバータ20に、0ボルトと入力電圧Vcの間のレベルでデューティー制御された第2出力電圧V2を生成させる。

## [0133]

これによって、第1コンデンサC1の電荷の放電が停止され、第2コンデンサC2の電荷が放電されて、第2コンデンサC2の第2端子間電圧Vch2が下がり、第1コンデンサC1の第1端子間電圧Vch1が上がる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧Vcは、電源電圧Vinの2分の1(=Vin/2)に戻る。

#### [0134]

(時刻t1~t2a(図3(b)参照))

制御回路40は、第1のインバータ10に対して、第1実施形態と同様に、高周波で第1~第4スイッチング素子Q11~Q14をデューティー制御する。そして、制御回路4

10

20

30

40

0は、第1のインバータ10に、入力電圧Vcと電源電圧Vinの間のレベルでデューティー制御された第1出力電圧V1を生成させる。一方、制御回路40は、第1実施形態と同様に、第5及び第6スイッチング素子Q21,Q22をオフに固定し、第7及び第8スイッチング素子Q23,Q24をオンに固定する。そして、制御回路40は、第2のインバータ20に、0ボルトの第2出力電圧V2を生成させる。

### [0135]

この時、第1コンデンサC1と第2コンデンサC2の容量値が小さいと、第1コンデンサC1の電荷が放電され、時刻t2aに近づくにつれて、第1コンデンサC1の第1端子間電圧Vch1が下がり、第2コンデンサC2の第2端子間電圧Vch2が上がる。

## [0136]

これによって、図3(b)に示すように、デューティー制御された第1のインバータ10の第1出力電圧 V1の振幅は次第に小さくなり、反対に、第2のインバータ20の第2出力電圧 V2のレベルは次第に大きくなる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧 Vcは、電源電圧 Vinの2分の1にならなくなり、それ以上に高くなる。

## [0137]

## (時刻t2a~t2)

制御回路40は、時刻t2aに到達すると、第1及び第4スイッチング素子Q11,Q14をオフ、第2及び第3スイッチング素子Q12,Q13をオンに固定する。そして、制御回路40は、第1のインバータ10に、入力電圧Vcと同じ第1出力電圧V1を生成させる。この制御は、時刻t2になるまで実行される。一方、制御回路40は、第2のインバータ20の第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御する。そして、制御回路40は、第2のインバータ20に、0ボルトと入力電圧Vcの間のレベルでデューティー制御された第2出力電圧V2を生成させる。

#### [0138]

これによって、第1コンデンサC1の電荷の放電が停止され、第2コンデンサC2の電荷が放電されて、第2コンデンサC2の第2端子間電圧Vch2が下がり、第1コンデンサC1の第1端子間電圧Vch1が上がる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧Vcは、電源電圧Vinの2分の1(=Vin/2)に戻る。

## [0139]

## (時刻t3~t4(図3(c)参照))

制御回路40は、時刻 t 3 ~ t 4 において、第1のインバータ10に対して、高周波で第1~第4スイッチング素子Q11~Q14をデューティー制御する。そして、0ボルトと入力電圧 V c の間のレベルでデューティー制御された第1出力電圧 V 1 が生成される。一方、制御回路40は、第1実施形態と同様に、第5及び第8スイッチング素子Q21,Q24をオフに固定し、第6及び第7スイッチング素子Q22,Q23をオンに固定する。そして、制御回路40は、第2のインバータ20に、入力電圧 V c と同じ第2出力電圧 V 2を生成させる。

## [0140]

この時、第1コンデンサC1と第2コンデンサC2の容量値が小さいと、第1コンデンサC1の電荷が放電され、時刻t2aに近づくにつれて、第1コンデンサC1の第1端子間電圧Vch1が下がり、第2コンデンサC2の第2端子間電圧Vch2が上がる。

## [0141]

これによって、図3 (c)に示すように、デューティー制御された第1のインバータ10の第1出力電圧 V1の振幅も次第に小さくなり、反対に、第2のインバータ20の第2出力電圧 V2のレベルは次第に大きくなる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧 Vcは、電源電圧 Vinの2分の1にならなくなり、それ以上に高くなる。

## [0142]

10

20

30

10

20

30

40

50

#### (時刻t4~t4a)

制御回路40は、時刻 t 4に到達すると、第1及び第2スイッチング素子Q11,Q12をオフ、第3及び第4スイッチング素子Q13,Q14をオンに固定する。そして、制御回路40は、第1のインバータ10に、0ボルトの第1出力電圧V1を生成させる。この制御は、時刻 t 4になるまで実行される。一方、制御回路40は、第2のインバータ20の第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御して、第2のインバータ20に、入力電圧Vcと電源電圧Vinの間のレベルでデューティー制御された第2出力電圧V2を生成させる。

#### [0143]

これによって、第1コンデンサC1の電荷の放電が停止され、第2コンデンサC2の電荷が放電されて、第2コンデンサC2の第2端子間電圧Vch2が下がり、第1コンデンサC1の第1端子間電圧Vch1が上がる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧Vcは、電源電圧Vinの2分の1(=Vin/2)に戻る。

## [0144]

(時刻t4a~t5a(図3(d)参照))

制御回路 4 0 は、時刻 t 4 a ~ t 5 a において、第 1 のインバータ 1 0 に対して、第 1 実施形態と同様に、高周波で第 1 ~ 第 4 スイッチング素子 Q 1 1 ~ Q 1 4 をデューティー制御する。そして、 0 ボルトと入力電圧 V c の間のレベルでデューティー制御された第 1 出力電圧 V 1 が生成される。一方、制御回路 4 0 は、第 1 実施形態と同様に、第 5 及び第 6 スイッチング素子 Q 2 1 , Q 2 2 をオフに固定し、第 7 及び第 8 スイッチング素子 Q 2 3 , Q 2 4 をオンに固定する。そして、制御回路 4 0 は、第 2 のインバータ 2 0 に、電源電圧 V 1 n と同じ第 2 出力電圧 V 2 を生成させる。

#### [0145]

この時、第1コンデンサC1と第2コンデンサC2の容量値が小さいと、第1コンデンサC1の電荷が放電され、時刻t5aに近づくにつれて、第1コンデンサC1の第1端子間電圧Vch1が下がり、第2コンデンサC2の第2端子間電圧Vch2が上がる。

#### [0146]

これによって、図3(d)に示すように、デューティー制御された第1のインバータ10の第1出力電圧V1の振幅は次第に小さくなり、反対に、第2のインバータ20の第2出力電圧V2のレベル値は次第に大きくなる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧Vcは、電源電圧Vinの2分の1にならなくなり、それ以上に高くなる。

## [0147]

(時刻t5a~t5)

制御回路40は、時刻t5aに到達すると、第1及び第2スイッチング素子Q11,Q12をオフ、第3及び第4スイッチング素子Q13,Q14をオンに固定する。そして、制御回路40は、第1のインバータ10に、0ボルトの第1出力電圧V1を生成させる。この制御は、時刻t5になるまで実行される。一方、制御回路40は、第1実施形態と同様に、第2のインバータ20の第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御して、第2のインバータ20に、入力電圧Vcと電源電圧Vinの間のレベルでデューティー制御された第2出力電圧V2を生成させる。

## [0148]

これによって、第1コンデンサC1の電荷の放電が停止され、第2コンデンサC2の電荷が放電されて、第2コンデンサC2の第2端子間電圧Vch2が下がり、第1コンデンサC1の第1端子間電圧Vch1が上がる。その結果、第1コンデンサC1と第2コンデンサC2との接続点の入力電圧Vcは、電源電圧Vinの2分の1(=Vin/2)に戻る。

## [0149]

このように、第2実施形態では、第2のインバータ20のレベルを切り替えるとき、第

1のインバータ10の高周波でのデューティー制御を停止させた。そして、第2のインバータ20が高周波でデューティー制御された。第2のインバータ20が高周波でデューティー制御されている短時間の切り替えの間において、第1コンデンサC1の第1端子間電圧Vch1と第2コンデンサC2の第2端子間電圧Vch2を等しくすることができる。

## [0150]

従って、第2実施形態によれば、第1実施形態の効果に加えて、直流電源2の電源電圧 Vinを半分ずつ分担している第1コンデンサC1と第2コンデンサC2の容量値を小さ くできる。その結果、より小型化が図れるインバータ装置1を実現することができる。

## [0151]

#### (第3実施形態)

次に、本発明の第3実施形態のインバータ装置について図4に従って説明する。

#### [0152]

第1及び第2実施形態のインバータ装置では、制御回路40が予め定められたパターンに基づいて第1及び第2のインバータ10,20に対してデューティー制御を行なう。

### [0153]

これに対して、第3実施形態のインバータ装置では、第2のインバータ20の第2出力電圧V2の切り替え時における時間幅 tに依存せずに、図2(c)に示される出力電圧Vtの正弦波形W2が生成される。つまり、第3実施形態のインバータ装置では、インバータ装置1のその時々の状態に応じて第1及び第2のインバータ10,20がデューティー制御される。

### [0154]

従って、説明の便宜上、第1及び第2実施形態と相違する点を詳細に説明し、同じ構成部分の詳細な説明は省略する。

#### [0155]

図4において、第1コンデンサC1には、第1電圧検出器DV1が並列に接続されている。第1電圧検出器DV1は、第1コンデンサC1のその時々の第1端子間電圧Vch1を検出し、検出された第1端子間電圧Vch1を示す第1電圧検出信号SV1を制御回路40に供給する。

## [0156]

また、第2コンデンサC2には、第2電圧検出器DV2が並列に接続されている。第2電圧検出器DV2は、第2コンデンサC2のその時々の第2端子間電圧Vch2を検出し、検出された第2端子間電圧Vch2を示す第2電圧検出信号SV2を制御回路40に供給する。

## [0157]

フィルター回路30の第1及び第2出力端子P3,P4間には、第3電圧検出器DV3が接続されている。第3電圧検出器DV3は、フィルター回路30から供給されるその時々の出力電圧Vtを検出し、検出された出力電圧Vtを示す第3電圧検出信号SV3を制御回路40に供給する。

## [0158]

また、フィルター回路30の第2交流リアクトルL2と第2出力端子P4との間には、電流検出器DI1が接続されている。電流検出器DI1は、フィルター回路30から図示しない負荷に流れる電流を検出し、検出された電流を示す電流検出信号SI1を制御回路40に出力する。

## [0159]

制御回路40は、第1~第3電圧検出器DV1~DV3から第1~第3電圧検出信号SV1~SV3を受信するとともに、電流検出器DI1から電流検出信号SI1を受信する。そして、制御回路40は、第1電圧検出器DV1の第1電圧検出信号SV1に基づいて、その時々の第1コンデンサC1の第1端子間電圧Vch1を算出する。また、制御回路40は、第2電圧検出器DV2の第2電圧検出信号SV2に基づいて、その時々の第2コンデンサC2の第2端子間電圧Vch2を算出する。

10

20

30

40

#### [0160]

さらに、制御回路40は、第3電圧検出器DV3の第3電圧検出信号SV3及び電流検出器DI1の電流検出信号SI1に基づいて、その時々のフィルター回路30から供給される出力電圧Vt、出力電流It及び出力電力PW(=Vt×It)を算出する。

## [0161]

制御回路40は、その時々に求められた第1端子間電圧Vch1、第2端子間電圧Vch2、出力電圧Vt、出力電流It及び出力電力PWに基づいて、第1のインバータ10及び第2のインバータ20を、種々の態様で制御することができる。

#### [0162]

以下、その制御態様の実施例について記載する。

#### 10

#### [0163]

(実施例1)

第1実施形態では、第2出力電圧 V2のレベルを切り替える時に、制御回路40は、第2のインバータ20に対して、予め定められた時間幅 tにて第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御する。

#### [0164]

一方、実施例1では、制御回路40は、第2のインバータ20の高周波でのデューティー制御を、出力電力PWが予め定められた値になった時に開始させる。また、制御回路40は、第2のインバータ20の高周波でのデューティー制御を、出力電力PWが予め定められた値になった時に終了させる。

## 20

### [ 0 1 6 5 ]

この時、この第2のインバータ20の高周波でのデューティー制御は、制御回路40内に設けられた比較器を使って行われる。制御回路40は、その時々の出力電圧Vtと予め定められた基準値(例えば、予め定められた三角波形)とを比較することによってデューティー比(%)を決定する。そして、制御回路40は、決定されたデューティー比(%)に基づいて第2のインバータ20を高周波でデューティー制御する。

## [0166]

また、第1実施形態では、時刻t0~t6の期間での、第1のインバータ10の高周波のデューティー制御は、予め決められたデューティー制御のパターンを用いて行なわれる

30

## [0167]

一方、実施例1では、制御回路40は、時刻t0~t6の期間でのその時々の出力電力PWに基づいてデューティー比を決定し、その決定されたデューティー比に基づいて第1のインバータ10を高周波でデューティー制御する。

## [0168]

この時刻 t 0 ~ t 6 の期間での、第 1 のインバータ 1 0 の高周波でのデューティー制御は、同様に、制御回路 4 0 内に設けられた比較器を使って行われる。制御回路 4 0 は、その時々の出力電圧 V t と予め定められた基準値(例えば、予め定められた三角波形)とを比較することによってデューティー比(%)を決定する。そして、制御回路 4 0 は、決定されたデューティー比(%)に基づいて第 1 のインバータ 1 0 を高周波でデューティー制御する。

40

#### [0169]

従って、この場合、その時々にフィルター回路30から供給される実際の出力電力PWに基づいて第2のインバータ20の高周波のデューティー制御の開始と終了が決定され、出力電圧Vtに基づいて高周波のデューティー制御におけるデューティー比が決定される

## [0170]

その結果、本実施例1では、第1実施形態の効果に加えて、現実に即した制御が行えるため、より歪みの少ない正弦波形W2を有する出力電圧Vtを生成することができる。

## [0171]

## (実施例2)

上記実施例1(第2実施形態も同様)では、第2出力電圧V2のレベルを切り替える時に、制御回路40は、第2のインバータ20に対して、予め定められた時間幅 tにて第5~第8スイッチング素子Q21~Q24を高周波でデューティー制御する。

## [0172]

これに対して、第1実施形態では、第1のインバータ10は、高周波でデューティー制御されていた。これを、第2実施形態のように、第2のインバータ20が高周波でデューティー制御されている間、第1のインバータ10を第1出力電圧V1が一定の電圧値に維持されるよう制御させる。

## [0173]

実施例2では、制御回路40は、その時々に求めた第1コンデンサC1の第1端子間電圧Vch1と第2コンデンサC2の第2端子間電圧Vch2に基づいて、第1のインバータ10を制御して、第1出力電圧V1が一定の電圧値に維持されるようにする。制御回路40は、第1コンデンサC1と第2コンデンサC2とが電源電圧Vinを等分に分担できない場合がある。そして、第1コンデンサC1と第2コンデンサC2との接続点の電圧が、電源電圧Vinの1/2である基準から予め定められた規定値を超えて変動する時、制御回路40は、第1のインバータ10に対して、第1出力電圧V1を一定の電圧値に維持する制御を開始させる。

## [0174]

この時、制御回路40は、第2のインバータ20に対して、高周波でのデューティー制御を開始させる。この時、高周波での第2のインバータ20のデューティー制御は、実施例1と同様に、制御回路40内の比較器を使って得られたデューティー比に基づいて行なわれる。そして、制御回路40は、実施例1と同様に、第2のインバータ20の高周波によるデューティー制御が終了すると、第1のインバータ10を高周波でデューティー制御させる。

## [0175]

従って、この場合、その時々の実際の第1コンデンサC1の第1端子間電圧Vch1と第2コンデンサC2の第2端子間電圧Vch2とに基づいて、第1のインバータ10の第1出力電圧V1を一定の電圧値に維持する制御の開始タイミングが決定される。

## [0176]

その結果、本実施例2では、第2実施形態の効果に加えて、現実に即した制御が行えるため、より歪みの少ない正弦波形W2を有する出力電圧Vtを生成することができる。

### [0177]

## (実施例3)

上記実施例1では、第2のインバータ20の第2出力電圧のレベルを切り替える時、制御回路40は、第2のインバータ20を高周波でデューティー制御してから第2出力電圧のレベルを切り替えた。そして、その第2のインバータ20が高周波でデューティー制御されている間においても、第1のインバータ10は、高周波でデューティー制御された。

## [0178]

一方、上記実施例2では、第2のインバータ20の第2出力電圧のレベルを切り替える時、制御回路40は、第2のインバータ20を高周波でデューティー制御してから第2出力電圧のレベルを切り替えた。そして、第2のインバータ20が高周波でデューティー制御される時、第1のインバータ10は、第1出力電圧V1を一定の電圧値に維持するように制御された。

#### [0179]

これを、実施例3では、実施例1の制御態様(第1制御という)と、実施例2の制御態様(第2制御という)とが、状況に応じて切り替え可能である。

## [0180]

つまり、制御回路40は、その時々の第1コンデンサC1の第1端子間電圧Vch1と 第2コンデンサC2の第2端子間電圧Vch2に基づいて、第1コンデンサC1と第2コ 10

20

30

40

ンデンサ C 2 との接続点の電圧が、電源電圧 V i n の 1 / 2 を基準として予め定められた 規定値の範囲内にある時、第 1 制御を実行する。

## [0181]

反対に、制御回路40は、その時々の第1コンデンサC1の第1端子間電圧Vch1と第2コンデンサC2の第2端子間電圧Vch2に基づいて、第1コンデンサC1と第2コンデンサC2との接続点の電圧が、電源電圧Vinの1/2を基準として予め定められた規定値を超えた時に、第2制御を実行する。

## [0182]

従って、この実施例3の場合、その時々の負荷の変動に応じて、第1制御及び第2制御の中から最適な制御が選択される。また、このインバータ装置1においては、用途に応じて、第1及び第2コンデンサC1,C2の容量値が変更されても対応することができる。

## [0183]

その結果、本実施例3では、実施例1及び実施例2の効果に加えて、より現実に即した制御が行えるため、より歪みの少ない正弦波形W2を有する出力電圧Vtを生成することができる。

## [0184]

尚、上記実施形態は以下のように変更してもよい。

## [0185]

上記各実施形態の第1及び第2インバータ10,20は、3レベルインバータであったが、これを、例えば4レベルインバータ、5レベルインバータを用いて具体化してもよい

20

# フロントページの続き

(56)参考文献 特開平08-182342(JP,A)

国際公開第2010/058536(WO,A1)

特開2011-004464(JP,A)

特開2006-191743(JP,A)

国際公開第97/025766(WO,A1)

(58)調査した分野(Int.CI., DB名)

H 0 2 M 7 / 4 8 7

H 0 2 M 7 / 4 8