(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-533728

(P2004-533728A)

(43) 公表日 平成16年11月4日(2004.11.4)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 29/423

H01L 29/49

H01L 29/786

F 1

H01L 29/78 301X

H01L 29/78 618C

H01L 29/78 617K

H01L 29/78 617L

H01L 29/78 617N

テーマコード(参考)

4M104

5F110

5F140

審査請求有 予備審査請求有 (全48頁) 最終頁に続く

(21) 出願番号 特願2003-509521 (P2003-509521)

(86) (22) 出願日 平成14年6月25日 (2002.6.25)

(85) 翻訳文提出日 平成15年12月26日 (2003.12.26)

(86) 國際出願番号 PCT/EP2002/007028

(87) 國際公開番号 WO2003/003442

(87) 國際公開日 平成15年1月9日 (2003.1.9)

(31) 優先権主張番号 101 31 276.8

(32) 優先日 平成13年6月28日 (2001.6.28)

(33) 優先権主張國 ドイツ(DE)

(81) 指定国 JP, KR, US

(71) 出願人 501055020

インフィネオン テクノロジーズ アクチ

エンゲゼルシャフト

ドイツ連邦共和国, テー-81669 ミ

ュンヘン, ザンクト-マルティン-シュト

ラーゼ 53

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

(72) 発明者 ポップ, マルティン

ドイツ国 01109 ドレスデン, ゼ

リーナ シュトラーゼ. 17

最終頁に続く

(54) 【発明の名称】電界効果トランジスタおよびこれを製造する方法

## (57) 【要約】

本発明は、隆起の上面上のプレーナチャネル領域が、隆起の側面上のさらなる垂直チャネル領域だけ幅が広げられたプレーナチャネル領域電界効果トランジスタに関する。このさらなる垂直チャネル領域は、プレーナチャネル領域と直接的に結合される（垂直に拡大されたチャネル領域）。この電界効果トランジスタは、達成可能な集積密度を低減させる必要なく、電流の流れ  $I_{ON}$  のための実効チャネル幅の著しい拡大が、これまで利用された従来のトランジスタ構造と比較して、より保証され得るという有利な点を有する。さらに、この電界効果トランジスタは、低い逆電流  $I_{OFF}$  を有する。上述の利点は、ゲート絶縁体から電荷移送トンネリングの領域までの厚みを低減するか、または安定性を低減する必要なく達成される。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

電界効果トランジスタ、特に、MIS電界効果トランジスタであって、

a) 半導体基板(1)上に配置され、かつ、上面(2a)および側面(2b)を有する、少なくとも1つのウェブタイプの隆起(2)と、

b) 該ウェブタイプの隆起(2)の該上面(2a)上に配置される、第1のゲート酸化物層(4)と、

c) 該第1のゲート酸化物層(4)上に配置される第1のゲート電極であって、上面および側面を有する、第1のゲート電極(5)と、

d) 該ウェブタイプの隆起(2)の該側面(2b)および該第1のゲート電極(4)の少なくとも一部分に配置される、第2のゲート酸化物層(6)と、10

e) 該第2のゲート酸化物層(6)および該第1のゲート電極(5)の該上面に配置される、第2のゲート電極(7)と、

f) 該ウェブタイプの隆起(2)上に配置されるソース領域およびドレイン領域とを備える、電界効果トランジスタ。

**【請求項 2】**

前記第2のゲート酸化物層(6)は、前記ウェブタイプの隆起(2)の前記側面(2b)上よりも、前記第1のゲート電極(5)の側面上で、より厚く製造される、請求項1に記載の電界効果トランジスタ。20

**【請求項 3】**

絶縁スペース(14)は、前記第1のゲート電極(5)のレベルで前記第2のゲート酸化物層(6)上に配置される、請求項1または2に記載の電界効果トランジスタ。20

**【請求項 4】**

電界効果トランジスタ、特に、MIS電界効果トランジスタであって、

a) 半導体基板(1)上に配置され、かつ、上面(2a)および側面(2b)を有する、少なくとも1つのウェブタイプの隆起(2)と、

b) 該ウェブタイプの隆起(2)の該側面(2b)の少なくとも一部分に配置される、第1のゲート酸化物層(4)と、

c) 該第1のゲート酸化物層(4)に配置される第1のゲート電極(5)であって、該第1のゲート電極層(5)は、上面および側面を有する、第1のゲート電極(5)と、30

d) 該ウェブタイプの隆起(2)の該上面(2a)、および該第1のゲート電極(5)の該上面に配置される、第2のゲート酸化物層(6)と、

e) 該第2のゲート酸化物層(6)、および該第1のゲート電極(5)の該側面に配置される、第2のゲート電極(7)と、

f) 該ウェブタイプの隆起(2)上に配置される、ソースおよびドレイン領域とを有する、電界効果トランジスタ。

**【請求項 5】**

前記ウェブタイプの隆起(2)の前記エッジ(8)は、前記上面(2a)と前記側面(2b)との間で丸み付けされる、請求項1～4のいずれか1つに記載の電界効果トランジスタ。40

**【請求項 6】**

前記エッジ(8)の湾曲の半径は、前記第1のゲート酸化物層(4)または前記第2のゲート酸化物層(6)の層の厚さの大きさの次数である、請求項5に記載の電界効果トランジスタ。

**【請求項 7】**

前記ソース領域と前記ゲート電極との間、さらに、前記ドレイン領域と該ゲート電極との間にスペースが配置される、請求項1～7のいずれか1つに記載の電界効果トランジスタ。

**【請求項 8】**

前記第1のゲート電極(5)は、ポリシリコン層を有する、請求項1～8のいずれか1つ50

に記載の電界効果トランジスタ。

【請求項 9】

前記第 2 のゲート電極(7)は、ポリシリコン金属の 2 重層またはポリサイド層を有する、請求項 1 ~ 8 のいずれか 1 つに記載の電界効果トランジスタ。

【請求項 10】

ゲート酸化物層(4、6)によって覆われた前記ウェブタイプの隆起(2)の前記側面(2 b)の一部分は、トレンチアイソレーション(3)によって境界付けされる、請求項 1 ~ 9 のいずれか 1 つに記載の電界効果トランジスタ。

【請求項 11】

前記ソースおよびドレイン領域のドーピングプロファイル深さは、ゲート酸化物層(4、106)によって覆われた前記ウェブタイプの隆起(2)の前記側面(2 b)の一部分の広がりよりも大きい、請求項 1 ~ 10 のいずれか 1 つに記載の電界効果トランジスタ。

【請求項 12】

電界効果トランジスタ、特に、MIS 電界効果トランジスタを製造する方法は、

a ) 第 1 のゲート酸化物層(4)が上に付与され、かつ第 1 のゲート電極層(5)が該ゲート酸化物層(4)に付与された半導体基板(1)が提供される工程と、

b ) 上面(2 a)および側面(2 b)を有する、少なくとも 1 つのウェブタイプの隆起(2)が生成され、該第 1 のゲート酸化物層(4)および該第 1 のゲート電極層(5)が該上面(2 a)上に配置される工程と、

c ) 第 2 のゲート酸化物層(6)が、該ウェブタイプの隆起(2)の該側面(2 b)および該第 1 のゲート電極層(5)の少なくとも一部分に生成される工程と、

d ) 第 2 のゲート電極層が付与され、これにより、該第 2 のゲート電極層(7)は、該第 2 のゲート酸化物層(6)、および該第 1 のゲート電極層(5)の該上面上に配置される工程と、

e ) 該第 1 のゲート電極層(5)および該第 2 のゲート電極層(7)は、第 1 および第 2 のゲート電極を形成するようにパターニングされ、ソースおよびドレイン領域が生成される工程と

を包含する、電界効果トランジスタを製造する方法。

【請求項 13】

前記ウェブタイプの隆起(2)は、トレンチアイソレーション(3)用のトレンチのパターニングにより生成される、請求項 1 2 に記載の方法。30

【請求項 14】

前記トレンチアイソレーション用の前記トレンチは、酸化物(3)で充填され、かつ、エッティングバックが実行され、これにより、前記ウェブタイプの隆起(2)の前記側面(2 b)の一部分が露出される、請求項 1 3 に記載の方法。

【請求項 15】

エッティングバックの前に、CMP 工程が実行される、請求項 1 4 に記載の方法。

【請求項 16】

前記上面(2 a)と前記側面(2 b)との間の前記ウェブタイプの隆起(2)の前記エッジ(8)を丸み付けするために、少なくとも 1 回の熱処理が実行される、請求項 1 2 ~ 1 5 のいずれか 1 つに記載の方法。40

【請求項 17】

前記ゲート酸化物層(4、6)は、それぞれ、熱酸化によって生成される、請求項 1 2 ~ 1 6 のいずれか 1 つに記載の方法。

【請求項 18】

前記第 2 のゲート酸化物層(6)は、選択的酸化によって生成され、これにより、前記第 2 のゲート酸化物層(6)は、前記ウェブタイプの隆起(2)の前記側面(2 b)上よりも、前記第 1 のゲート電極(5)の前記側面上で、より厚く製造される、請求項 1 2 ~ 1 7 のいずれか 1 つに記載の方法。

【請求項 19】

絶縁スペースは、前記第1のゲート電極層(5)が生成された後に生成され、これにより、該第1のゲート電極(5)のレベルで、絶縁層(14)が前記第2のゲート酸化物層(6)上に配置される、請求項12~18のいずれか1つに記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電界効果トランジスタ、および、これを製造する方法に関する。

【背景技術】

【0002】

従来の電界効果トランジスタ、特に、プレーナMIS電界効果トランジスタ(MISFET)の特性パラメータは、構造が小型化するにつれ(スケーリング)、および集積回路の充填密度が高くなるにつれて益々低下する。従って、例えば、トランジスタのチャネル長が短縮されるにつれ、トランジスタの閾値電圧 $V_T$ は小さくなる。同時に、チャネル長が短縮されるにつれ、チャネル領域における電界強度、および逆電流 $I_{OFF}$ は大きくなる(SCE: 短チャネル効果; ロールオフ)。さらに、チャネル幅が縮小されるにつれ、順方向電流 $I_{ON}$ が非線形的に変動する。さらに、電界効果トランジスタのジオメトリおよびドーピングは、チャネルと絶縁部との間の接合部において改変される。通常、スケーリングの場合、チャネル境界部は、中心のチャネル領域に対して比較的重要である(NCE: 狹チャネル効果、INC E: 逆狭チャネル効果)。

【0003】

上述の問題にもかかわらず、構造の小型化の進行(スケーリング)という意味合いで、電界効果トランジスタの性能の向上/維持を保証することができるよう、一連の措置が提示または実行される。従って、例えば、内部の動作電圧レベルに適合されたスケーリングは、MISFETスケーリングと同時に行われる。さらに、ウェルおよびチャネル領域の、さらに、ソースおよびドレイン領域のドーピングプロファイルが、通常、最適化される。同時に、厚さおよび材料に関してゲート絶縁体のスケーリングが、通常、行われる。

【0004】

サリサイド化されたソースおよびドレイン領域(S/D)、ならびにサリサイド化されたゲート電極を使用することによって、さらなる向上がもたらされる。例えば、銅線および中間絶縁体を用いることによって、または、例えば、いわゆる「ロー-k」材料を用いることによって、接続メタライゼーションの寄生抵抗または容量の最小化によりさらなる向上がもたらされ得る。DRAMメモリセルの場合、読み出しロジックを、それぞれのアレイトランジスタの「ON」電流(「縮小(shrink)」する毎に小さくなる)に適合させることも可能である(例えば、ゲートトラックの抵抗の低減)。

【0005】

電界効果トランジスタの性能を維持または向上するためのさらなる可能性は、例えば、上昇したソース/ドレイン領域(「上昇したS/D」)を有するか、または、いわゆる「silicon on insulator」技術(SOI)に基づくか、または、チャネル領域において、SiGe等の、より高いキャリア移動度の材料を有する改変されたトランジスタ構成を使用することである。動作温度が低下した場合に結果として生じるさらなる可能性は、本明細書中には示されない。

【0006】

従来のLOCOSフィールド絶縁に代わるトレニチフィールドアイソレーション(STI: シャロートレンチアイソレーション)の導入は、同様に、状況を改善するために寄与する。トレニチフィールドアイソレーション(STI: シャロートレンチアイソレーション)が、従来のLOCOSフィールドアイソレーションの変わりに用いられる場合、いわゆる「逆狭チャネル効果」(INC E)を最小化するためのさらなる措置をとることが、通常、必要とされる。従って、いわゆる「ラップアラウンドゲート」を回避するために、例えば、半導体表面上のSTI上部エッジの正のステップ高さが設定される。さらに、フィールドアイソレーションを有する接合部におけるトランジスタチャネルの局所的ドーピン

10

20

30

40

50

グ、いわゆる「コーナ領域」は、通常のチャネルドーピングに加えて提供され得る。

【0007】

S T I 处理の間の S T I 側壁の酸化は、いわゆる「バーズビークジオメトリ」の生成をもたらし、かつトレンチアイソレーションを有する接合部における活性領域のエッジが丸み付けされ得る。プロセスシーケンスにおいて、本明細書中で用いられる用語は、「コーナの丸み付け」、「ミニLOCOS」または「ポストC M P酸化」である。これらは、さらに、「逆狭チャネル効果（I N C E）」に対処するために利用され得る。この効果は、パッド酸化物を事前に長手方向にエッチングバックすることによって強化され得る。活性領域のエッジの丸み付けは、熱による表面の変質によっても生成される。さらに、窒化物スペーサ保護リングが生成され得る。コーナ領域へのゲートの重なりを回避するために、フィールドアイソレーション境界部分の前に、ゲートエッジの自己整合的終端を提供することが可能である。これは、例えば、S T I パターニングの間に、ポリゲートおよび活性領域が共にパターニングされることによって行われ得る。

【0008】

しかしながら、これらのすべての措置にも関わらず、M I S F E T のトンネリング、またはゲート酸化物の安定性が悪化する危険なしに、約 1 0 0 n m の構造サイズ上に適切な順方向電流 I <sub>O N</sub> を保証することが益々困難になる。従って、一連の代替的トランジスタ構成が提示される。

【0009】

特許文献米国第 4 , 9 7 9 , 0 1 4 号は、半導体基板上にウェブタイプの隆起を有するM O Sトランジスタを開示する。このトランジスタのチャネルは、ウェブタイプの隆起に沿って構成され、かつ、ウェブタイプの隆起の上面のチャネル領域の他に、ウェブタイプの隆起の側壁に 2 つのさらなるチャネル領域を有する。特許文献米国第 4 , 9 7 9 , 0 1 4 号によるトランジスタは、大きい空乏ゾーンを生成するために用いられる、明確な「コーナ効果」を示す。

【0010】

H u a n g らによる特許文献「Sub 50 nm FinFET ; PMOS」IEDM (1999年)は、「FinFET」と呼ばれるトランジスタを開示し、これは、ウェブタイプの隆起（「Fin」）の側壁にデュアルゲート構造を有する。FinFETは、表面を覆う狭いFin上により厚い絶縁層によってI N C E を回避する。

【0011】

残念ながら、上述のすべての措置のいずれも、制限された効果のみを有するか、またはプロセス技術上のコストおよび労力を多く必要とする。従って、本発明の目的は、電界効果トランジスタ、および上述の問題を低減または回避する電界効果トランジスタを製造する方法を提供することである。本発明の目的は、特に、適切な順方向電流 I <sub>O N</sub> を利用可能にし、かつ、わずかな出費で、これまでの従来のプレーナM O S F E T の集積プロセスとの互換性を有するように製造され得る電界効果トランジスタを提供することである。

【0012】

この目的は、独立請求項 1 に記載の電界効果トランジスタ、または独立請求項 4 に記載の電界効果トランジスタ、および独立請求項 12 に記載の電界効果トランジスタを製造する方法により達成される。本発明のさらなる有利な実施形態、改良点および局面は、従属請求項、明細書および添付の図面から明らかである。

【発明の開示】

【課題を解決するための手段】

【0013】

本発明の第 1 の局面は、以下の特徴

- a ) 半導体基板上に配置され、かつ、上面および側面を有する少なくとも 1 つのウェブタイプの隆起と、

- b ) ウェブタイプの隆起の上面に配置される第 1 のゲート酸化物層と、

- c ) 第 1 のゲート酸化物層上に配置される第 1 のゲート電極であって、上面および側面を

10

20

30

40

50

有する第1のゲート電極と、

d) ウェブタイプの隆起の側面および第1のゲート電極の該側面の少なくとも一部分に配置される第2のゲート酸化物層と、

e) 第2のゲート酸化物層および第1のゲート電極の上面上に配置される第2のゲート電極と、

f) 隆起上に配置されるソースおよびドレイン領域と

を有する電界効果トランジスタを提供する。

本発明のさらなる局面は、以下の特徴

a) 半導体基板上に配置され、かつ、上面および側面を有する、少なくとも1つのウェブ 10

タイプの隆起と、

b) ウェブタイプの隆起の側面の少なくとも一部分に配置される第1のゲート酸化物層と、

c) 第1のゲート酸化物層に配置される第1のゲート電極であって、第1のゲート電極層は、上面および側面を有する、第1のゲート電極と、

d) ウェブタイプの隆起の上面、および第1のゲート電極の上面上に配置される第2のゲート酸化物層と、

e) 第2のゲート酸化物層、および第1のゲート電極の側面に配置される第2のゲート電極と、

f) 隆起上に配置されるソースおよびドレイン領域と

を有する電界効果トランジスタを提供する。 20

#### 【0014】

さらに、本発明は、以下の工程

a) 第1のゲート酸化物層が上に付与され、かつ第1のゲート電極層がゲート酸化物層に付与された半導体基板が提供される工程と、

b) 上面および側面を有する少なくとも1つのウェブタイプの隆起が生成され、第1のゲート酸化物層および第1のゲート電極層が上面上に配置される工程と、

c) 第2のゲート酸化物層が、ウェブタイプの隆起の側面および第1のゲート電極層の少なくとも一部分に生成される工程と、

d) 第2のゲート電極層が付与され、これにより、第2のゲート電極層は第2のゲート酸化物層、および第1のゲート電極層の上面上に配置される工程と、 30

e) 第1および第2のゲート電極層は、第1および第2のゲート電極を形成するようにパターニングされ、ソースおよびドレイン領域が生成される工程と

を包含する電界効果トランジスタを製造する方法を提供する。

#### 【0015】

本発明による電界効果トランジスタは、達成され得る集積密度を低減せしめる必要なく、すでに公知の従来のトランジスタ構造と比較して、順方向電流  $I_{ON}$  のために効果的なチャネル幅の著しい拡大が保証され得るという有利な点を有する。本発明による電界効果トランジスタの場合、隆起の上面のプレーナチャネル領域が、隆起の側方面積におけるさらなる垂直チャネル領域だけ幅が広くなる。これらのさらなる垂直チャネル領域は、プレーナチャネル領域（垂直に伸ばされたチャネル領域）に直接的に隣接する。さらに、本発明による電界効果トランジスタは、小量の逆電流  $I_{OFF}$  を有する。これらの有利な点は、ゲート絶縁体の厚さを電荷キャリアのトンネリングの領域にまで低減することも、安定性を低減することなく達成される。 40

#### 【0016】

この場合、さらなる垂直チャネル領域が、本発明により、好適には、STIパターニング（「シャロートレンチアイソレーション」）の間に従来のプレーナトランジスタ構成と同様に生成され得、垂直STI側壁を形成し得る垂直半導体面を利用することによって、達成される。従って、本発明によるトランジスタを製造するプロセスは、従来のプレーナトランジスタが集積され得、かつ本発明によるトランジスタを有する同じチップ上に非常に簡単に組み込まれ得る従来のSTI絶縁されたプレーナトランジスタのプロセスシーケン 50

スと密接に関連する。

【0017】

プレーナチャネル領域と垂直チャネル領域との間に凸状に曲げられたエッジの形態の遷移部が、ウェブタイプの隆起上にソース／ドレイン方向に配置され、活性チャネルの構成部分として存在する。前に提示されたトランジスタ構成の場合、このエッジは、常に、明確な「コーナ効果」をもたらす。これは、トランジスタの閾値電圧に不利な影響を及ぼす。本発明による電界効果トランジスタの場合、この問題は、第1および第2のゲート酸化物層、さらに、第1および第2のゲート電極を有する特定の包囲構成によって大幅に回避される。

【0018】

本発明による電界効果トランジスタの好適な1実施形態によると、第2のゲート酸化物層は、ウェブタイプの隆起の側面上よりも、第1のゲート電極の側面上で、より厚く製造される。さらに、第1のゲート電極のレベルで、絶縁スペーサが第2のゲート酸化物層上に配置された場合、好適である。これは、エッジにおける電界の大きさをさらに低減することを可能にする。

【0019】

本発明による電界効果トランジスタのさらなる好適な実施形態によると、ウェブタイプの隆起のエッジは、上面と側面との間で丸み付けされる。この丸み付けは、好適には、短い高温プロセスを用いて生成され得る。従って、本発明によるトランジスタは、著しく低減された温度収支で生成され得る。これは、特に、ドーピングプロファイルおよび性能に関して、有利な点をもたらす。さらに、その結果、プレーナと垂直チャネル領域との間の遷移領域が小さく保持され、垂直には、トランジスタのジオメトリが非常に著しくスケーリングされた場合、幾何学的チャネル領域の幅および深さ全体が活性チャネルとして利用され得る。

【0020】

この場合、エッジの湾曲の半径が第1または第2のゲート酸化物層の層厚さの大きさの次数である場合、特に好適である。従って、いわゆる「寄生コーナーデバイス」の閾値電圧は、プレーナチャネル領域の閾値電圧値よりも大きい値にされ得る。従って、結果として生じた、エッジの湾曲の表面に沿う電界の大きさは、チャネルのプレーナ部分における電界の大きさを超過しない。

【0021】

本発明による電界効果トランジスタのさらなる好適な実施形態によると、スペーサは、ソース領域とゲート電極との間、さらに、ドレイン領域とゲート電極との間に配置される。さらに、第1のゲート電極がポリシリコン層を有する場合、好適である。さらに、第2のゲート電極がポリシリコン金属の2重層またはポリサイド層を有する場合、特に好適である。

【0022】

本発明による電界効果トランジスタのさらなる好適な実施形態によると、ゲート酸化物層によって覆われたウェブタイプの隆起の側面の一部分は、トレンチアイソレーションによって境界付けられる。さらに、ソースおよびドレイン領域のドーピングプロファイルの深さが、ゲート酸化物層によって覆われたウェブタイプの隆起の側面の一部分の広がりよりも大きい場合、特に、好適である。

【0023】

本発明による製造法の好適な1実施形態によると、ウェブタイプの隆起がトレンチアイソレーションのためのトレンチのパターニングにより生成される。この場合、トレンチアイソレーションのためのトレンチが酸化物で充填され、かつ、エッチングバックが、好適には、C M P 工程の後に実行され、これにより、ウェブタイプの隆起の側面の一部分が露出される場合、特に好ましい。

【0024】

本発明による製造方法のさらなる好適な実施形態によると、上面と側面との間のウェブタ

10

20

30

40

50

イブの隆起のエッジを丸み付けするために、少なくとも1回の熱処理が実行される。さらに、ゲート酸化物層が、各場合について、熱酸化によって生成された場合、特に好適である。

#### 【0025】

本発明による製造方法のさらなる好適な実施形態によると、第2のゲート酸化物層が選択的酸化によって生成され、これにより、第2のゲート酸化物層は、ウェブタイプの隆起の側面上よりも、第1のゲート電極の側面上で、より厚く製造される。さらに、絶縁スペーサが、第1のゲート電極層が生成された後に生成され、これにより、第1のゲート電極のレベルで、絶縁スペーサが第2のゲート酸化物層上に配置された場合に好適である。

#### 【0026】

本発明は、次に、図面を参照してより詳細に説明される。

#### 【発明を実施するための最良の形態】

#### 【0027】

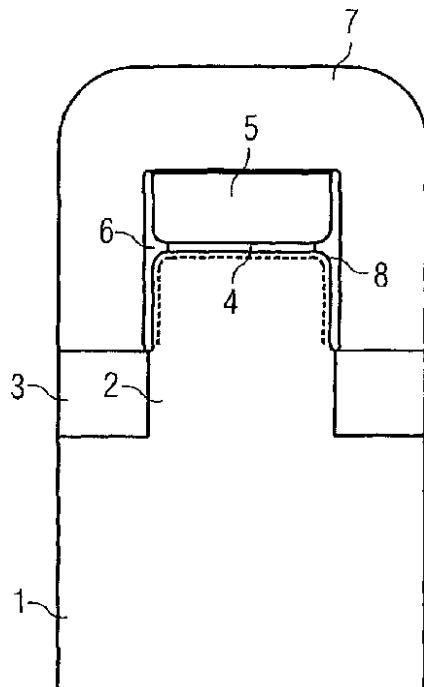

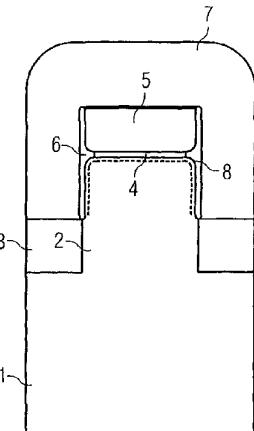

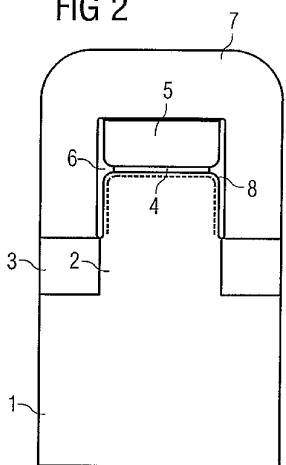

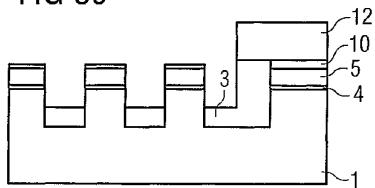

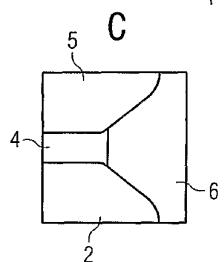

図1および図2は、本発明による電界効果トランジスタの第1の実施形態を示す。この場合、図1は、本発明による電界効果トランジスタのこの実施形態の一般的構造を示し、図2は、本発明による電界効果トランジスタのこの実施形態の詳細を断面図で示す。図1から見出され得るように、本発明による電界効果トランジスタは、半導体基板1上に配置され、かつ上面2a、および2つの側面2bを有するウェブタイプの隆起2を有する。ウェブタイプの隆起2は、この場合、活性半導体領域を構成する。

#### 【0028】

半導体基板1と垂直に接続する活性半導体領域2は、STIフィールドアイソレーション領域3によって隣接し合う活性領域（図示せず）から長手方向に絶縁される。活性領域の面2a、2bは、ソースおよびドレイン領域に、ならびにプレーナチャネル領域になるようにパターニングされる。ウェブタイプの隆起2は、STI面上に突き出し、その結果、活性領域の側方領域2bが、アイソレーション3によって部分的に覆われない。対応するプレーナ領域と直接的に隣接するこれらの露出した側方領域は、ソース、ドレインおよびチャネル領域になるように同様にパターニングされる。この場合、活性半導体領域とSTI表面との間の高さの差が垂直チャネル領域の幅に対応する。ソースおよびドレイン領域のドーピングプロファイルの深さは、好適には、上述の高さの差よりも大きい。

#### 【0029】

図2から見出され得るように、本発明による電界効果トランジスタは、ウェブタイプの隆起2の上面2a上に配置される第1のゲート酸化物層4を有する。さらに、第1のゲート酸化物層4上に配置された第1のゲート電極5が提供され、第1のゲート電極は、上面および2つの側面を有する。第2のゲート酸化物層6は、ウェブタイプの隆起2の側面2bおよび第1のゲート電極4に配置される。さらに、第2のゲート電極7は、第2のゲート酸化物層6上、および第1のゲート電極5の上面に配置される。

#### 【0030】

従って、活性および埋没STI面を備える起伏構造は、チャネル領域において2重ゲート電極によって覆われる。この場合、第1のゲート電極5は、好適には、高濃度ドーピングポリシリコンからなる一方で、第2のゲート電極7は、好適には、ポリシリコン金属層のスタッカを有する。この場合、2つのゲート電極5、7は、第1のゲート電極5が活性領域のプレーナ部分のみを覆い、かつ、その側壁でほぼ終端する一方で、第2のゲート電極7は、活性領域の垂直方向の側壁を覆い、かつ第1のゲート電極5を包囲するように配置される。この場合、第2のゲート電極7は、プレーナ表面上の第1のゲート電極5と接触する一方で、第2のゲート酸化物層6によってその長手方向の側壁から絶縁される。

#### 【0031】

本発明による電界効果トランジスタの本実施形態の場合、活性領域のエッジ8が丸み付けされる。この丸み付けの湾曲の半径は、ゲート酸化物の厚さの大きさの次数である。さらに、チャネル領域は、デュアルゲート電極5、7をS/Dコンタクト領域から長手方向に絶縁するスペーサ（図示せず）によってソースおよびドレイン側で支えられる（fan

10

20

30

40

50

k e d )。

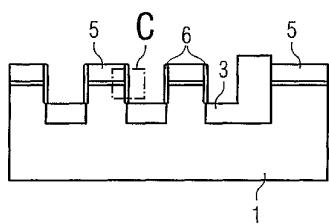

**【 0 0 3 2 】**

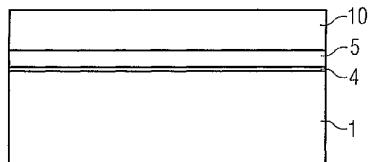

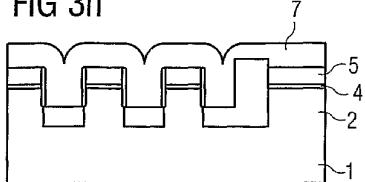

図3 a ~ 図3 hは、電界効果トランジスタを製造するための本発明による方法の第1の実施形態を示す。いくつかの予備製造工程の後、第1のゲート酸化物層4、さらに、第1のゲート電極層5およびパッド窒化物層10が半導体基板1、特に、シリコン基板上に生成される。この場合、ゲート酸化が、例えば、熱酸化を用いて実行され得る。ゲート電極層およびパッド窒化物堆積が、例えば、CVD法を用いて実行される。結果として生じた状態が図3 aに示される。

**【 0 0 3 3 】**

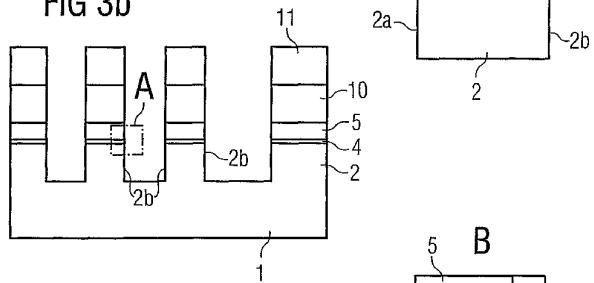

その後、レジストマスク11を用いて、この層スタックは、STIパターニングと共にパターニングされる。この共通のパターニングは、例えば、化学的物理的ドライエッチングにより、行われる。その結果、上面2aおよび2つの側面2bを有するウェブタイプの隆起2が生成され、第1のゲート酸化物層4および第1のゲート電極層5が、上面2a上に配置される。上面2aと2つの側面2bとの間のエッジ8は、この処理工程において、垂直に90度に鋭く切断される。この結果生じた状態が図3 bに示される。

**【 0 0 3 4 】**

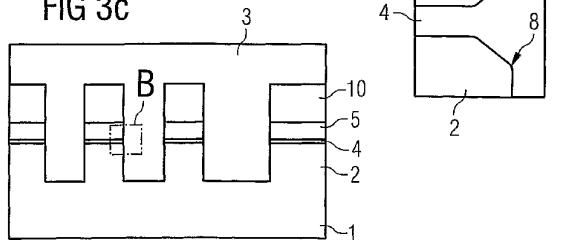

その後、垂直の側方領域、および、さらに、第1のゲート電極層5の側壁のシーリングの質を向上させるために、レジストマスク11の除去、さらに、洗浄および短時間の熱酸化が行われる。その後、生成された表面起伏が酸化物3で充填され(図3 c)、熱により高密度化され、かつCMP法(化学的機械的研磨)により窒化物の残留物の厚さに平坦化される(図3 d)。この処理セクションの熱処理は、結果として、エッジ8における第1のゲート酸化物層4の幅をわずかに広くし、かつ、ウェブタイプの隆起2の上面2aと2つの側面2bとの間のエッジ8を丸み付けする。

**【 0 0 3 5 】**

STI酸化物3は、次に、意図的に垂直チャネルを拡大することなく、トランジスタのすべての領域を覆うブロックマスク12を用いた異方性エッチングによりプレーナの様相で所定の深さにエッチングされる。このエッチングは、パッド窒化物層10に関して特定の選択性を有し、これにより、ウェブタイプの隆起2の上面2aが、依然としてシリコン窒化物10で確実に覆われた状態になる。残ったSTI充填深さは、後で確実なフィールドアイソレーションが保証される大きさにされる。その結果生じた状態が図3 eに示される。

**【 0 0 3 6 】**

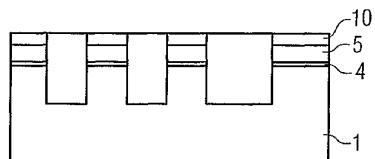

ブロックマスクの除去、洗浄/オーバーエッチングの後に、第2のゲート酸化が行われる(図3 f)。この場合、第2のゲート酸化物層6は、ウェブタイプの隆起2の露出された側壁、および第1のゲート電極層5の露出された側壁上で成長する。この酸化工程は、さらに、エッジ8における第1のゲート酸化物層4の幅を広くし、かつ、基板およびポリエッジの湾曲をさらに低減する。その後、第1のゲート電極層の表面に残ったパッド窒化物の残留層10が除去され(図3 g)、かつ、さらなる洗浄工程の後、第2のゲート電極層7が堆積する(図3 h)。

**【 0 0 3 7 】**

その後、マスクを用いて(図示せず)、第1および第2のゲート電極層がエッチング、好適には、プラズマエッチングにより共にパターニングされ、エッチングは、第1のゲート酸化物層で停止する。この後に、従来のプロセスシーケンスにより、ソース/ドレイン領域を完全な回路になるように製造する工程を含むさらなる処理が続く。

**【 0 0 3 8 】**

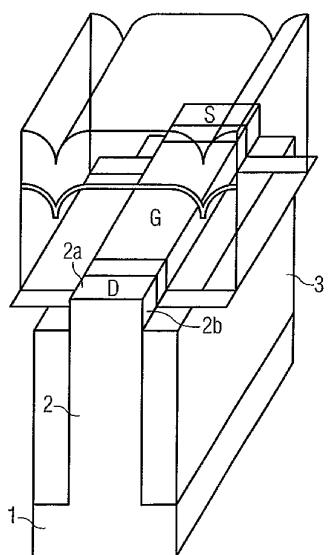

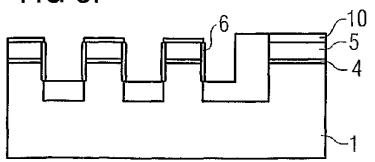

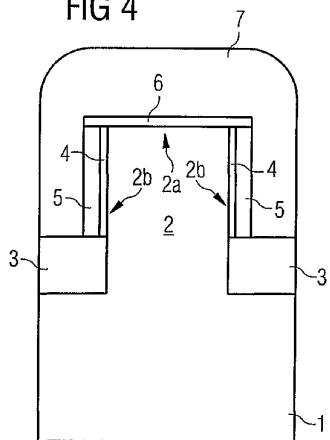

図4は、本発明による電界効果トランジスタのさらなる実施形態を示す。図4から見出され得るように、本発明による電界効果トランジスタのさらなる実施形態は、さらに、半導体基板1上に配置され、かつ、上面2aおよび2つの側面2bを有するウェブタイプの隆起2を有する。ウェブタイプの隆起2は、この場合、活性半導体領域を構成する。

**【 0 0 3 9 】**

10

20

30

40

50

半導体基板と垂直に接続される活性半導体領域もまた、S T I フィールドアイソレーション領域3によって隣接し合う活性領域から長手方向に絶縁される。活性領域の表面は、ソースおよびドレイン領域ならびにプレーナチャネル領域へとパターニングされる。これはS T I 表面の上に突き出し、その結果、活性領域の側壁は、部分的に露出される。これらの露出された側壁は、対応するプレーナ領域に直接的に隣接し、ソース、ドレインおよびチャネル領域へと同様にパターニングされる。活性面とS T I 表面との間の高さの差は、垂直チャネル領域の幅に対応する。ソースおよびドレイン領域のドーピングプロファイルの深さは、好適には、その高さの差よりも大きい。

## 【0040】

従って、活性面および埋没S T I 表面を含む起伏構造は、チャネル領域において、デュアルゲート電極5、7によって覆われる。この場合、第1のゲート電極5は、好適には、高濃度ドーピングポリシリコンからなる一方で、第2のゲート酸化物7は、好適には、ポリシリコン金属層のスタックを有する。2つのゲート電極5、7は、第1のゲート電極5が、活性領域2の垂直部分2 bのみを覆い、かつ、その上面でほぼ終端する一方で、第2のゲート電極7は、活性領域2の上面を覆い、かつ第1のゲート電極5を包囲するように配置される。この場合、第2のゲート電極は、その側面上の第1のゲート電極と接触する一方で、第2のゲート酸化物層6によってその上部側壁から絶縁される。チャネル領域は、そのプレーナ部分で第2のゲート酸化物層6によって、およびその垂直領域において第1のゲート酸化物層4によって覆われる。

## 【0041】

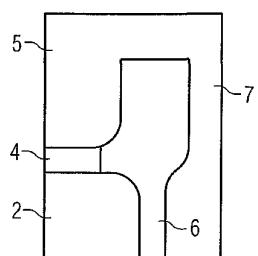

図5は、本発明による電界効果トランジスタのさらなる実施形態を示す。図5に示されるように、本発明による電界効果トランジスタの実施形態は、第2のゲート酸化物層6が、ウェブタイプの隆起2の側面2 bよりも、第1のゲート電極5の側面上で、より厚く製造されることを除いて、実質的に、図2に示される本発明による電界効果トランジスタの実施形態に対応する。第1のゲート電極5の側面上の第2のゲート酸化物層6を厚くすることは、選択的ゲート酸化によって達成され、ここで、プロセスパラメータが、適切に選択された場合、単結晶シリコン上よりもポリシリコン上において高い酸化率が取得されるという事実が利用される。

## 【0042】

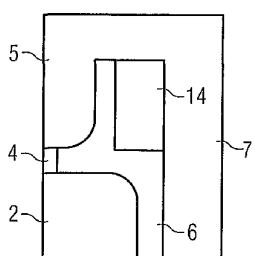

図6は、本発明による電界効果トランジスタのさらなる実施形態を示す。図6に示される、本発明による電界効果トランジスタの実施形態は、第1のゲート電極5のレベルで、スペーサ14、特に、酸化物スペーサが第2のゲート酸化物層6上に配置されることを除いて、実質的に、図2に示される本発明による電界効果トランジスタの実施形態に対応する。この場合、スペーサ14は、そのパターニングの直後、さらにウェブタイプの隆起2の形成の前に第1のゲート電極層5の側壁に形成され得る。第2のゲート酸化物層6を生成するための酸化は、第1のゲート電極層5の側面のすぐ上のさらなる酸化物層によって、このスペーサ14を強化する。

## 【0043】

本発明による電界効果トランジスタは、順方向電流 $I_{DN}$ 用の実効チャネル幅の著しい増加は、達成され得る集積密度を低減させる必要なく、すでに公知の従来のトランジスタ構造と比較して、保証され得るという有利な点を有する。本発明による電界効果トランジスタの場合、隆起の上面におけるプレーナチャネル領域は、隆起の側方領域におけるさらなる垂直チャネル領域だけ幅が拡大される（垂直に拡大されたチャネル領域）。さらに、本発明による電界効果トランジスタは、小量の逆電流 $I_{OFF}$ を有する。これらの有利な点は、ゲート絶縁体から電荷キャリアのトンネリング領域までの厚みの低減、または安定性の低減の必要なく達成される。

## 【図面の簡単な説明】

## 【0044】

【図1】図1は、本発明による電界効果トランジスタの第1の実施形態を示す。

【図2】図2は、本発明による電界効果トランジスタの第1の実施形態を示す。

10

20

30

40

50

【図3a】図3aは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3b】図3bは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3c】図3cは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3d】図3dは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3e】図3eは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

10

【図3f】図3fは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3g】図3gは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図3h】図3hは、電界効果トランジスタを製造する、本発明による方法の第1の実施形態を示す。

【図4】図4は、本発明による電界効果トランジスタのさらなる実施形態を示す。

【図5】図5は、本発明による電界効果トランジスタのさらなる実施形態を示す。

【図6】図6は、本発明による電界効果トランジスタのさらなる実施形態を示す。

## 【国際公開パンフレット】

(12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum

9. Januar 2003 (09.01.2003)

PCT

(10) Internationale Veröffentlichungsnummer

**WO 03/003442 A1**

(51) Internationale Patentklassifikation: **H01L 21/336.** (71) Anmelder (*für alle Bestimmungsstaaten mit Ausnahme von US:*) INFINEON TECHNOLOGIES AG [DE/DE]; St.-Martin Strasse 53, 81669 München (DE).

(21) Internationales Aktenzeichen: PCT/EP02/07028

(22) Internationales Anmeldedatum:

25. Juni 2002 (25.06.2002)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität:

101 31 276.8 28. Juni 2001 (28.06.2001) DE (74) Anwälte: ZIMMERMANN & PARTNER usw.; Postfach 330 920, 80069 München (DE).

*[Fortsetzung auf der nächsten Seite]*

(54) Title: FIELD EFFECT TRANSISTOR AND METHOD FOR PRODUCTION THEREOF

(54) Bezeichnung: FELDEFETKTRANSISTOR UND VERFAHREN ZU SEINER HERSTELLUNG

(57) Abstract: The invention relates to a field effect transistor in which the planar channel region on the upper surface of the elevation is extended in width by means of additional vertical channel regions on the lateral surfaces of the elevation. Said additional vertical channel regions connect directly to the planar channel region (vertical extended channel regions). Said field effect transistor has the advantage that a significant increase in the effective channel width for the current flow  $I_{on}$  can be guaranteed relative to conventional transistor structures used up until the present, without having to accept a reduction in the achievable integration density. Said field effect transistor furthermore has a low reverse current  $I_{off}$ . The above advantages are achieved without the thickness of the gate insulators up to the region of the charge transfer tunnels having to be reduced or a reduced stability.

(57) Zusammenfassung: Bei dem erfundungsgemäßen Feldefekttransistor wird das planare Kanalgebiet an der oberen Oberfläche der Erhebung durch zusätzliche vertikale Kanalgebiete an den Seitenflächen der Erhebung in der Weite ausgedehnt. Diese zusätzlichen vertikalen Kanalgebiete schließen sich unmittelbar an das planare Kanalgebiet an (vertical extended channel regions). Der erfundungsgemäße Feldefektransistor besitzt den Vorteil, dass eine deutliche Erhöhung der für den Flussstrom  $I_{on}$  wirksamen Kanalweite gegenüber bisher verwendeten, konventionellen Transistorstrukturen gewährleistet werden kann, ohne dass eine Verringerung der erzielbaren Integrationsdichte hingenommen werden muss. Weiterhin besitzt der erfundungsgemäße Feldefektransistor eine geringen Sperrstrom  $I_{off}$ . Diese Vorteile werden erzielt, ohne dass die Dicke des Gate Isolators bis in den Bereich des Tunnels von Ladungsträgern oder einer vermindernden Stabilität verringert werden muss.

WO 03/003442 A1

---

**WO 03/003442 A1****(81) Bestimmungstaaten (national):** JP, KR, US.**Veröffentlicht:**

— mit internationalem Recherchebericht

Zur Erklärung der Zweibuchstaben-Codes und der anderen Abkürzungen wird auf die Erklärungen ("*Guidance Notes on Codes and Abbreviations*") am Anfang jeder regulären Ausgabe der PCT-Gazette verwiesen.

1

**Beschreibung****Feldeffekttransistor und Verfahren zu seiner Herstellung**

5

Die vorliegende Erfindung betrifft einen Feldeffekttransistor und ein Verfahren zu seiner Herstellung.

Die charakteristischen Parameter von herkömmlichen Feldeffekttransistoren, insbesondere von planaren MIS-Feldeffekttransistoren (MISFET), verschlechtern sich zunehmend mit fortgesetzter Strukturverkleinerung (Skalierung) und Erhöhung der Packungsdichte von integrierten Schaltungen. So sinkt beispielsweise mit verkürzter Kanallänge des Transistors die Einsatzspannung  $V_t$  des Transistors. Gleichzeitig erhöhen sich mit verkürzter Kanallänge die Feldstärke im Kanalgebiet und der Sperrstrom  $I_{off}$  (SCE: short channel effect; roll-off). Weiterhin verändert sich mit verminderter Kanalweite der Flußstrom  $I_{on}$  in nichtlinearer Weise. Zusätzlich werden am Übergang des Kanals zur Isolation die Geometrie und Dotierung des Feldeffekttransistors modifiziert. Allgemein gewinnen die Kanalgrenzen bei Skalierung gegenüber dem zentralen Kanalbereich an relativer Bedeutung (NCE: narrow channel effect, INCE: inverse narrow channel effect).

Um trotz der genannten Schwierigkeiten eine Verbesserung/Aufrechterhaltung der Performance von Feldeffekttransistoren bei fortschreitender Strukturverkleinerung (Skalierung) gewährleisten zu können, werden eine Reihe von Maßnahmen vorgeschlagen bzw. durchgeführt. So erfolgt beispielsweise mit der MISFET-Skalierung zugleich eine angepaßte Skalierung der internen Betriebsspannungspegel. Weiterhin erfolgt in der Regel eine Optimierung der Dotierungsprofile der Wannen- und Kanalgebiete sowie der Source- und Draingebiete. Gleichzeitig

wird üblicherweise eine Skalierung des Gateisolators bezüglich Dicke und Material durchgeführt.

Weitere Verbesserungen ergeben sich durch die Verwendung von salinierten Source- und Drain-Gebieten (S/D) sowie salinierten Gate-Elektroden. Durch eine Minimierung der parasitären Widerstände bzw. Kapazitäten der Anschlußmetallisierung, beispielsweise durch die Verwendung einer Kupferverdrahtung, und der Zwischenisolatoren, beispielsweise durch die Verwendung von sogenannten „low-k“ Materialien, kann eine weitere Verbesserung erzielt werden. Im Fall von DRAM-Speicherzellen kann auch eine Anpassung der Ausleselogik an die sich mit jedem „Shrink“ verkleinernden „ON“-Ströme der jeweiligen Arraytransistoren (z.B. Reduktion der Widerstände der Gatebahnen) vorgenommen werden.

Eine weitere Möglichkeit, die Performance von Feldeffekttransistoren aufrechtzuerhalten bzw. zu verbessern, besteht in der Verwendung modifizierte Transistoranordnungen, die beispielsweise erhöhte Source/Drainbereiche („elevated S/D“) aufweisen oder die auf einer sogenannten „silicon on insulator“ Technologie (SOI) basieren oder die im Kanalgebiet ein Material mit einer höheren Trägerbeweglichkeit, z.B. SiGe, aufweisen. Zusätzliche Möglichkeiten, die sich bei Senkung der Betriebstemperatur ergeben, sind hier nicht dargestellt.

Die Einführung der Trench-Feldisolation (STI: shallow trench isolation) anstelle konventioneller LOCOS-Feldisolation tragt ebenfalls zur Verbesserung der Situation bei. Wird eine Trench-Feldisolation (STI: shallow trench isolation) anstelle einer konventionellen LOCOS-Feldisolation eingesetzt, so müssen in der Regel zusätzliche Maßnahmen zur Minimierung des sogenannten „inverse narrow channel effect“ (INCE) ergriffen werden. So wird beispielsweise eine positiven Stufenhöhe der STI-Oberkante über der Halbleiteroberfläche eingestellt, um ein sogenanntes „wrap-

around Gate" zu vermeiden. Weiterhin kann eine lokale Aufdotierung des Transistorkanals am Übergang zur Feldisolation, der sogenannten „corner region, zusätzlich zur normalen Kanaldotierung vorgesehen sein.

5

Durch eine Oxidation der STI-Flanken während der STI-Prozessierung kann eine sogenannte „birdsbeak Geometrie“ und Kantenverrundung der aktiven Gebiete am Übergang zur Trenchisolation erzeugt werden. Im Prozeßablauf spricht man dabei von „corner rounding“, „mini LOCOS“ bzw. „post CMP oxidation“. Auch diese Maßnahmen dienen dazu, dem „inverse narrow channel effect“ (INCE) entgegenzuwirken. Eine Verstärkung dieser Wirkung kann dabei durch ein vorheriges laterales Rückätzen des Padoxids erreicht werden. Eine Kantenverrundung der aktiven Gebiete kann auch mittels thermischer Oberflächentransformation erzeugt werden. Weiterhin kann ein Nitrid-Spacer Schutzring („guardring“) vorgesehen sein. Zur Vermeidung einer Gateüberlappung über die corner-Region kann ein selbstjustierter Abschluß der Gatekante vor der Feldisolationsgrenze vorgesehen sein. Dies kann beispielsweise durch eine gemeinsame Strukturierung von Poly-Gate und aktivem Gebiet bei der STI-Strukturierung erfolgen.

25 Trotz all dieser Maßnahmen wird es jedoch immer schwieriger, ab etwa 100nm Strukturgröße eine ausreichenden Flußströme  $I_{DS}$  zu gewährleisten, ohne daß die Gefahr des Tunnelns oder der Degradation der Gateoxid-Stabilität des MISFET besteht. Daher wurden eine Reihe von alternativen

30 Transistoranordnungen vorgeschlagen.

Das Dokument US 4,979,014 offenbart eine MOS-Transistor, der eine stegförmige Erhöhung auf einem Halbleitersubstrat aufweist. Der Kanal dieses Transistors ist entlang der stegförmigen Erhöhung angeordnet und weist neben dem Kanalbereich an der Oberseite der stegförmigen Erhöhung noch zwei weitere Kanalbereiche an den Seitenwänden der

stegförmigen Erhöhung auf. Der Transistor gemäß Dokument US 4,979,014 zeigt einen ausgeprägten „Ecken-Effekt“ („corner effect“), der dazu verwendet wird, eine große Verarmungszone zu erzeugen.

5

Das Dokument Huang et al. „Sub 50-nm FinFET: PMOS“ IEDM 1999 offenbart einen „FinFET“ genannten Transistor, der eine Doppel-Gate Struktur an den Seitenwänden der stegförmigen Erhöhung („Fin“) aufweist. Der FinFET vermeidet den INCE mittels einer dickeren Isolatorschicht auf der schmalen Fin-Deckfläche.

Leider besitzen all die genannten Maßnahme entweder nur eingeschränkte Wirksamkeit oder sie erfordern einen großen prozeßtechnischen Aufwand. Es ist daher die Aufgabe der vorliegenden Erfindung, einen Feldeffekttransistor und Verfahren zu seiner Herstellung bereitzustellen, welche die genannten Schwierigkeiten vermindern bzw. vermeiden. Es ist insbesondere die Aufgabe der vorliegenden Erfindung, einen Feldeffekttransistor bereitzustellen, der einen ausreichenden Flußstrom  $I_{on}$  zur Verfügung stellt und der mit einem geringem Aufwand, kompatibel zum bisherigen, konventionellen Integrationsprozeß für planare MOSFETs hergestellt werden kann.

25

Diese Aufgabe wird von dem Feldeffekttransistor gemäß dem unabhängigen Patentanspruch 1 bzw. von dem Feldeffekttransistor gemäß dem unabhängigen Patentanspruch 4 sowie von dem Verfahren zur Herstellung eines Feldeffekttransistors gemäß dem unabhängigen Patentanspruch 12 gelöst. Weitere vorteilhafte Ausführungsformen, Ausgestaltungen und Aspekte der vorliegenden Erfindung ergeben sich aus den abhängigen Patentansprüchen, der Beschreibung und den beiliegenden Zeichnungen.

35

Gemäß einem ersten Aspekt der vorliegenden Erfindung wird ein Feldeffekttransistor bereitgestellt, der die folgenden Merkmale umfaßt:

- 5        a) zumindest eine auf einem Halbleitersubstrat angeordnete stegförmige Erhebung, die eine obere Oberfläche und seitliche Oberflächen aufweist,

- 10      b) eine erste Gateoxidschicht, die auf der oberen Oberfläche der stegförmigen Erhebung angeordnet ist,

- 15      c) eine erste Gateelektrode, die auf der ersten Gateoxidschicht angeordnet ist, wobei die erste Gateelektrode eine obere Oberfläche und seitliche Oberflächen aufweist,

- 20      d) eine zweite Gateoxidschicht, die zumindest auf einem Teil der seitlichen Oberflächen der stegförmigen Erhebung und der ersten Gateelektrode angeordnet ist,

- 25      e) eine zweite Gateelektrode, die auf der zweiten Gateoxidschicht und der oberen Oberfläche der ersten Gateelektrode angeordnet ist, und

- 30      f) Source- und Draingebiete, die auf der Erhebung angeordnet sind.

Gemäß einem weiteren Aspekt der vorliegenden Erfindung wird ein Feldeffekttransistor bereitgestellt, der die folgenden Merkmale umfaßt:

- 35      a) zumindest eine auf einem Halbleitersubstrat angeordnete stegförmige Erhebung, die eine obere Oberfläche und seitliche Oberflächen aufweist,

- b) eine erste Gateoxidschicht, die zumindest auf einem Teil der seitlichen Oberflächen der stegförmigen Erhebung angeordnet ist,

- 5       c) eine erste Gateelektrode, die auf der ersten Gateoxidschicht angeordnet ist, wobei die erste Gateelektrodenschicht eine obere Oberfläche und seitliche Oberflächen aufweist,

- 10      d) eine zweite Gateoxidschicht, die auf der oberen Oberfläche der stegförmigen Erhebung und der oberen Oberfläche der ersten Gateelektrode angeordnet ist,

- 15      e) eine zweite Gateelektrode, die auf der zweiten Gateoxidschicht und den seitlichen Oberflächen der ersten Gateelektrode angeordnet ist, und

- 20      f) Source- und Draingebiete, die auf der Erhebung angeordnet sind.

- Weiterhin wird erfindungsgemäß ein Verfahren zur Herstellung eines Feldeffekttransistors bereitgestellt, das die folgenden Schritte umfaßt:

- 25      a) ein Halbleitersubstrat mit einer darauf aufgebrachten ersten Gateoxidschicht und einer auf die Gateoxidschicht aufgebrachten ersten Gateelektrodenschicht wird bereitgestellt,

- 30      b) zumindest eine stegförmige Erhebung mit einer oberen Oberfläche und seitlichen Oberflächen wird erzeugt, wobei die erste Gateoxidschicht und die erste Gateelektrodenschicht auf der oberen Oberfläche angeordnet sind,

- 35      c) zumindest auf einem Teil der seitlichen Oberflächen der stegförmigen Erhebung und der ersten

Gateelektrodenschicht wird eine zweite Gateoxidschicht erzeugt,

- 5 d) eine zweite Gateelektrodenschicht wird aufgebracht, so daß die zweite Gateelektrodenschicht auf der zweiten Gateoxidschicht und der oberen Oberfläche der ersten Gateelektrodenschicht angeordnet ist, und

- 10 e) die erste und die zweite Gateelektrodenschicht werden zu ersten und zweiten Gatelektroden strukturiert und Source- und Draingebiete werden erzeugt.

Der erfindungsgemäße Feldeffekttransistor besitzt den Vorteil, daß eine deutliche Erhöhung der für den Flußstrom  $I_{ON}$  wirksamen Kanalweite gegenüber bisher verwendeten, konventionellen Transistorstrukturen gewährleistet werden kann, ohne daß eine Verringerung der erzielbaren Integrationsdichte hingenommen werden muß. Bei dem erfindungsgemäßen Feldeffekttransistor wird das planare Kanalgebiet an der oberen Oberfläche der Erhebung durch zusätzliche vertikale Kanalgebiete an den Seitenflächen der Erhebung in der Weite ausgedehnt. Diese zusätzlichen vertikalen Kanalgebiete schließen sich unmittelbar an das planare Kanalgebiet an (vertical extended channel regions). Weiterhin besitzt der erfindungsgemäße Feldeffekttransistor einen geringen Sperrstrom  $I_{OFF}$ . Diese Vorteile werden erzielt, ohne daß Dicke des Gate-Isolators bis in den Bereich des Tunnels von Ladungsträgern oder einer verminderten Stabilität verringert werden muß.

30 Die zusätzlichen vertikalen Kanalgebiete werden dabei erfindungsgemäß durch Nutzung der vertikalen Halbleiteroberflächen gewonnen, die bevorzugt analog zur konventionellen planaren Transistoranordnung bei der STI-Strukturierung („shallow trench isolation“) erzeugt werden können und die vertikalen STI Flanken bilden. Der Herstellungsprozeß des erfindungsgemäßen Transistors ist

somit dem Prozeßablauf des konventionellen STI-isolierten, planaren Transistors so eng verwandt, daß herkömmliche, planare Transistoren sehr einfach auf demselben Chip mit erfundungsgemäßen Transistoren integriert und kombiniert werden können.

Zwischen dem planaren Kanalgebiet und den vertikalen Kanalgebieten existiert ein Übergangsgebiet in Form einer konkav gekrümmten, in Source/Drain-Richtung angeordnete Kante auf der stegförmigen Erhebung als Bestandteil des aktiven Kanals. Diese Kante führte bei bisher vorgeschlagenen Transistoranordnung immer zu einem ausgeprägten „Ecken-Effekt“ („corner effect“), der die Einsatzspannung des Transistors negativ beeinflußte. Bei dem erfundungsgemäßen Feldeffekttransistors wird dieses Problem durch die spezielle Umschließungsanordnung, welche die erste und zweite Gateoxidschicht sowie die erste und zweite Gateelektrode aufweist, weitgehend vermieden.

Gemäß einer bevorzugten Ausführungsform des erfundungsgemäßen Feldeffekttransistors ist die zweite Gateoxidschicht auf den seitlichen Oberflächen der ersten Gateelektrode dicker ausgebildet als auf den seitlichen Oberflächen der stegförmigen Erhebung. Weiterhin ist es bevorzugt, wenn an der zweiten Gateoxidschicht auf der Höhe der ersten Gateelektrode ein isolierender Spacer angeordnet ist. Dadurch läßt sich die elektrische Feldstärke an den Kanten weiter verringern.

Gemäß einer weiteren bevorzugten Ausführungsform des erfundungsgemäßen Feldeffekttransistors sind die Kanten der stegförmigen Erhebung zwischen der oberen Oberfläche und den seitlichen Oberflächen verrundet. Diese Verrundung kann bevorzugt mit Hilfe eines kurzen Hochtemperaturprozesses erzeugt werden. Dementsprechend kann der erfundungsgemäße Transistor mit einem deutlich reduziertem Temperaturbudget prozessiert werden. Dadurch ergeben sich Vorteile u.a.

hinsichtlich Dotierprofile und Performance. Auch wird dadurch der Übergangsbereich zwischen dem planaren und vertikalen Kanalgebiet gering gehalten, und nahezu die gesamte Breite und Tiefe der geometrischen Kanalfläche kann selbst bei sehr

5 stark skalierter Transistorgeometrie als aktiver Kanal genutzt werden.

Dabei ist es insbesondere bevorzugt, wenn der Krümmungsradius der Kanten in der Größenordnung der

10 Schichtdicke der ersten oder zweiten Gateoxidschicht liegt. Dementsprechend kann die Einsatzspannung des sogenannten "parasitic corner device" auf einen Wert gebracht werden, der größer als der Wert der Einsatzspannung des planaren Kanalbereichs ist. Die resultierende elektrische Feldstärke

15 entlang der Oberfläche der Kantenkrümmung übersteigt somit nicht die im ebenen Teil des Kanals herrschenden elektrische Feldstärke.

Gemäß einer weiteren bevorzugten Ausführungsform des

20 erfindungsgemäßen Feldeffekttransistors sind zwischen dem Sourcegebiet und den Gateelektroden sowie zwischen dem Draingebiet und den Gateelektroden Spacer angeordnet. Weiterhin ist es bevorzugt, wenn die erste Gateelektrode eine Polysiliziumschicht aufweist. Darüber hinaus ist es

25 insbesondere bevorzugt, wenn die zweite Gateelektrode eine Polysilizium-Metall-Doppelschicht oder eine Polyzidschicht aufweist.

Gemäß einer weiteren bevorzugten Ausführungsform des

30 erfindungsgemäßen Feldeffekttransistors ist der Teil der seitlichen Oberflächen der stegförmigen Erhebung, der von einer Gateoxidschicht bedeckt ist, von einer Grabenisolierung begrenzt. Weiterhin ist es insbesondere bevorzugt, wenn die Dotierungsprofiltiefe der Source- und Draingebiete größer als

35 die Ausdehnung des Teils der seitlichen Oberflächen der stegförmigen Erhebung ist, der von einer Gateoxidschicht bedeckt ist.

WO 03/003442

PCT/EP02/07028

10

Gemäß einer bevorzugten Ausführungsform des erfundungsgemäßen Herstellungsverfahrens erfolgt die Erzeugung der stegförmige Erhebung mit der Strukturierung der Gräben für eine Grabenisolierung. Dabei ist es insbesondere bevorzugt, wenn die Gräben für die Grabenisolierung mit Oxid gefüllt werden und eine Rückkästzung, bevorzugt nach einem CMP-Schritt, durchgeführt wird, so daß ein Teil der seitlichen Oberflächen der stegförmigen Erhebung freigelegt wird.

10

Gemäß einer weiteren bevorzugten Ausführungsform des erfundungsgemäßen Herstellungsverfahrens wird zumindest ein thermischer Prozeß zur Verrundung der Kanten der stegförmigen Erhebung zwischen der oberen Oberfläche und den seitlichen Oberflächen durchgeführt. Weiterhin ist es insbesondere bevorzugt, wenn die Gateoxidschichten jeweils durch thermische Oxidation erzeugt werden.

Gemäß einer weiteren bevorzugten Ausführungsform des erfundungsgemäßen Herstellungsverfahrens wird die zweite Gateoxidschicht mit selektiver Oxidation erzeugt, so daß die zweite Gateoxidschicht auf den seitlichen Oberflächen der ersten Gateelektrode dicker ausgebildet ist als auf den seitlichen Oberflächen der stegförmigen Erhebung. Weiterhin ist es bevorzugt, wenn nach der Erzeugung der ersten Gateelektrodenschicht ein isolierender Spacer erzeugt wird, so daß an der zweiten Gateoxidschicht auf der Höhe der ersten Gateelektrode ein isolierender Spacer angeordnet ist.

30 Die Erfindung wird nachfolgend anhand von Figuren der Zeichnungen näher dargestellt. Es zeigen:

Fig. 1 und 2 eine erste Ausführungsform des erfundungsgemäßen Feldeffekttransistors,

WO 03/003442

PCT/EP02/07028

11

Fig. 3a - 3h eine erste Ausführungsform des erfundungsgemäßen Verfahrens zur Herstellung eines Feldeffekttransistors,

5 Fig. 4 eine weitere Ausführungsform des erfundungsgemäßen Feldeffekttransistors,

Fig. 5 eine weitere Ausführungsform des erfundungsgemäßen Feldeffekttransistors, und

10 Fig. 6 eine weitere Ausführungsform des erfundungsgemäßen Feldeffekttransistors.

15 Die Fig. 1 und 2 zeigen eine erste Ausführungsform des erfundungsgemäßen Feldeffekttransistors. Dabei zeigt die Fig. 1 die allgemeine Struktur dieser Ausführungsform des erfundungsgemäßen Feldeffekttransistors während Fig. 2 die Details dieser Ausführungsform des erfundungsgemäßen 20 Feldeffekttransistors in einem Querschnitt darstellt. Wie aus Fig. 1 ersichtlich weist der erfundungsgemäße Feldeffekttransistor eine auf einem Halbleitersubstrat 1 angeordnete stegförmige Erhebung 2 auf, die eine obere Oberfläche 2a und zwei seitliche Oberflächen 2b besitzt. Die 25 stegförmige Erhebung 2 stellt dabei das aktive Halbleitergebiet dar.

Das aktive Halbleitergebiet 2 mit vertikaler Verbindung zum Halbleitersubstrat 1 ist von benachbarten aktiven Gebieten (nicht dargestellt) durch STI-Feldisolationsgebiete 3 lateral isoliert. Die Oberfläche 2a, 2b des aktiven Gebiets ist in Source- und Draingebiete sowie in ein planares Kanalgebiet strukturiert. Die stegförmige Erhebung 2 überragt die STI-Oberfläche, wodurch die Seitenflächen 2b des aktiven 30 Gebiets teilweise nicht durch die Isolation 3 bedeckt sind. Diese freiliegenden Seitenflächen sind, unmittelbar an die entsprechenden planaren Gebiete anschließend, gleichartig in 35

Source-, Drain- und Kanalgebiete strukturiert. Der Höhenunterschied zwischen dem aktiven Halbleitergebiet und der STI-Oberfläche entspricht dabei der Weite der vertikalen Kanalgebiete. Die Dotierungsprofiltiefe der Source- und 5 Draingebiete ist vorzugsweise größer als dieser Höhenunterschied.

Wie aus Fig. 2 ersichtlich weist der erfindungsgemäße Feldeffekttransistor eine erste Gateoxidschicht 4 auf, die 10 auf der oberen Oberfläche 2a der stegförmigen Erhebung 2 angeordnet ist. Weiterhin ist eine erste Gateelektrode 5 vorgesehen, die auf der ersten Gateoxidschicht 4 angeordnet ist, wobei die erste Gateelektrode eine obere Oberfläche und zwei seitliche Oberflächen aufweist. Eine zweite 15 Gateoxidschicht 6 ist auf den seitlichen Oberflächen 2b der stegförmigen Erhebung 2 und der ersten Gateelektrode 4 angeordnet. Auf dieser zweiten Gateoxidschicht 6 und auf der oberen Oberfläche der ersten Gateelektrode 5 ist weiterhin eine zweite Gateelektrode 7 angeordnet.

20 Die Reliefstruktur aus aktiver und abgesenkter STI-Oberfläche ist somit im Kanalbereich von einer doppelten Gateelektrode bedeckt. Dabei besteht die erste Gateelektrode 5 vorzugsweise aus hochdotiertem Polysilizium während die zweite Gateelektrode 7 vorzugsweise einen Polysilizium-Metall-Schichtstapel aufweist. Die beiden Gateelektroden 5, 7 sind dabei so angeordnet, daß die erste Gateelektrode 5 ausschließlich den planaren Teil des aktiven Gebiets bedeckt und etwa mit dessen Flanken abschließt, während die zweite 25 Gateelektrode 7 die Vertikalfanken des aktiven Gebiets bedeckt und die erste Gateelektrode 5 umschließt. Dabei kontaktiert die zweite Gateelektrode 7 die erste Gateelektrode 7 auf deren planarer Oberfläche, während sie 30 von deren seitlichen Flanken durch die zweite Gateoxidschicht 6 isoliert ist.

Bei der vorliegenden Ausführungsform des erfindungsgemäßen Feldeffektransistors ist die Kante 8 des aktiven Gebiets verrundet. Der Krümmungsradius dieser Rundung liegt dabei in der Größenordnung der Gateoxiddicke. Weiterhin 5 ist das Kanalgebiet source- und drainseitig von Spacern (nicht gezeigt) flankiert, welche die doppelte Gateelektrode 5, 7 lateral von den S/D-Kontaktflächen isolieren.

Die Fig. 3a - 3h zeigen eine erste Ausführungsform des 10 erfindungsgemäßen Verfahrens zur Herstellung eines Feldeffektransistors. Nach einigen vorbereitenden Herstellungsschritten wird auf einem Halbleitersubstrat 1, insbesondere einem Siliziumsubstrat, eine erste 15 Gateoxidschicht 4 sowie eine erste Gateelektrodenschicht 5 und Padnitridschicht 10 erzeugt. Dabei kann die Gateoxidation beispielsweise mit Hilfe einer thermischen Oxidation durchgeführt werden. Die Gateelektrodenschicht- und Padnitridabscheidung erfolgt beispielsweise mit Hilfe von CVD-Verfahren. Die sich daraus ergebende Situation ist in 20 Fig. 3a gezeigt.

Anschließend erfolgt mittels einer Lackmaske 11 die Strukturierung dieses Schichtstapels gemeinsam mit der STI-Strukturierung. Diese gemeinsame Strukturierung erfolgt 25 beispielsweise mit Hilfe einer chemisch-physikalischen Trockenätzung. Somit wird eine stegförmige Erhebung 2 mit einer oberen Oberfläche 2a und zwei seitlichen Oberflächen 2b erzeugt, wobei die erste Gateoxidschicht 4 und die erste Gateelektrodenschicht 5 auf der oberen Oberfläche 2a 30 angeordnet sind. Die Kanten 8 zwischen der oberen Oberfläche 2a und den zwei seitlichen Oberflächen 2b sind in diesem Bearbeitungsstadium scharf, nahezu mit 90°C geschnitten. Die sich daraus ergebende Situation ist in Fig. 3b gezeigt.

35 Danach erfolgt die Entfernung der Lackmaske 11 sowie eine Reinigung und eine kurze thermische Oxidation zur Verbesserung der Qualität der senkrechten Seitenflächen,

sowie Versiegelung der Flanken der ersten Gateelektrodenschicht 5. Dann wird das erzeugte Oberflächenrelief mit Oxid 3 verfüllt (Fig. 3c), thermisch verdichtet und mittels eines CMP-Verfahrens (chemical mechanical polishing) bis auf eine Nitrid-Restdicke planarisiert (Fig. 3d). Durch die thermischen Prozesse dieses Bearbeitungsabschnitts erfolgt eine geringe Aufweitung des erste Gateoxidschicht 4 an der Kante 8 sowie eine Abrundung der Kanten 8 zwischen der oberen Oberfläche 2a und den zwei seitlichen Oberflächen 2b der stegförmigen Erhebung 2.

Im Anschluß wird mittels anisotroper Ätzung über eine Blockmaske 12, die alle Bereiche für Transistoren ohne beabsichtigte vertikale Kanalerweiterung abdeckt, das STI-Oxid 3 bis in eine definierte Tiefe planar zurückgeätzt. Diese Ätzung hat eine gewisse Selektivität zu der Padnitritidschicht 10, so daß die obere Oberflächen 2a der stegförmigen Erhebungen 2 noch sicher mit Siliziumnitrid 10 bedeckt bleiben. Die verbleibende STI-Fülltiefe ist so dimensioniert, daß eine spätere sichere Feldisolierung garantiert ist. Die sich daraus ergebende Situation ist in Fig. 3e gezeigt.

Nach Entfernung der Blockmaske, Reinigung / Überätzung erfolgt die 2. Gateoxidation (Fig. 3f). Auf den freiliegenden Flanken der stegförmigen Erhebung 2 und auf den freiliegenden Flanken der ersten Gateelektrodenschicht 5 wächst dabei die zweite Gateoxidschicht 6 auf. Dieser Oxidationsschritt weitet die erste Gateoxidschicht 4 an den Kanten 8 zusätzlich auf und vermindert die Krümmung der Substrat- und Poly-Kanten weiter. Anschließend erfolgt die Entfernung der auf den Oberflächen der ersten Gateelektrodenschicht verbliebenen Padnitrid-Restschicht 10 (Fig. 3g) und, nach einer weiteren Reinigung, die Abscheidung der zweiten Gateelektrodenschicht 7 (Fig. 3h).

Danach wird über eine Maske (nicht gezeigt) die erste und die zweite Gateelektrodenbeschichtung gemeinsam mit Hilfe einer Ätzung, bevorzugt Plasmaätzung, strukturiert, wobei die Ätzung in der ersten Gateoxidschicht stoppt. Im Anschluß 5 daran erfolgt die weitere Prozessierung incl. Herstellung der Source/Drain-Gebiete bis zur kompletten Schaltung entsprechend dem konventionellen Prozeßablauf.

Fig. 4 zeigt eine weitere Ausführungsform des

10 erfindungsgemäßen Feldeffekttransistors. Wie aus Fig. 4 ersichtlich weist auch die weitere Ausführungsform des erfindungsgemäßen Feldeffekttransistors eine auf einem Halbleitersubstrat 1 angeordneten stegförmigen Erhebung 2 auf, die eine obere Oberfläche 2a und zwei seitliche 15 Oberflächen 2b besitzt. Die stegförmige Erhebung 2 stellt dabei das aktive Halbleitergebiet dar.

Das aktive Halbleitergebiet mit vertikaler Verbindung zum Halbleitersubstrat ist wiederum von benachbarten aktiven Gebieten durch STI-Feldisolationsgebiet 3 lateral isoliert. 20 Die Oberfläche des aktiven Gebiets ist in Source- und Drain- und planares Kanalgebiet strukturiert. Sie überragt die STI-Oberfläche, wodurch die Seitenflanken des aktiven Gebiets teilweise freiliegen. Diese freiliegenden Seitenflanken sind, 25 unmittelbar an die entsprechenden planaren Gebiete anschließend, gleichartig in Source-, Drain- und Kanalgebiete strukturiert. Der Höhenunterschied zwischen aktiver und STI-Oberfläche entspricht der Weite der vertikalen Kanalgebiete. Die Dotierungsprofiltiefe der Source- und Draingebiete ist 30 vorzugsweise größer als dieser Höhenunterschied.

Die Reliefstruktur aus aktiver und abgesenkter STI-Oberfläche ist somit im Kanalbereich von einer doppelten Gateelektrode 5, 7 bedeckt. Dabei besteht die erste 35 Gateelektrode 5 vorzugsweise aus hochdotiertem Polysilizium während die zweite Gateelektrode 7 vorzugsweise einen Polysilizium-Metall-Schichtstapel aufweist. Die beiden

Gateelektroden 5, 7 sind dabei so angeordnet, daß die erste Gateelektrode 5 ausschließlich den vertikalen Teil 2b des aktiven Gebiets 2 bedeckt und etwa mit dessen oberen Oberflächen abschließt, während die zweite Gateelektrode 7

5 die obere Oberfläche des aktiven Gebiets 2 bedeckt und die erste Gateelektrode 5 umschließt. Dabei kontaktiert die zweite Gateelektrode die erste Gateelektrode auf deren seitlichen Oberflächen, während sie von deren oberen Flanken durch die zweite Gateoxidschicht 6 isoliert ist. Das

10 Kanalgebiet ist auf seinem planaren Teil von der zweiten Gateoxidschicht 6 und auf seinen Vertikalfächern von der ersten Gateoxidschicht 4 bedeckt.

Fig. 5 zeigt eine weitere Ausführungsform des erfindungsgemäßen Feldeffekttransistors. Die in Fig. 5 gezeigte Ausführungsform des erfindungsgemäßen Feldeffekttransistors entspricht im wesentlichen der in Fig. 2 gezeigte Ausführungsform des erfindungsgemäßen Feldeffekttransistors mit der Ausnahme, daß die zweite Gateoxidschicht 6 auf den seitlichen Oberflächen der ersten Gateelektrode 5 dicker ausgebildet ist als auf den seitlichen Oberflächen 2b der stegförmigen Erhebung 2. Die Verdickung der zweiten Gateoxidschicht 6 auf den seitlichen Oberflächen der ersten Gateelektrode 5 wird durch eine selektive

20 Oxidation erzielt, wobei die Tatsache ausgenutzt wird, daß bei geeignet gewählten Prozeßparametern an Polysilizium eine höhere Oxidationsrate erzielt wird als an monokristallinem Silizium.

25

Fig. 6 zeigt eine weitere Ausführungsform des erfindungsgemäßen Feldeffekttransistors. Die in Fig. 6 gezeigte Ausführungsform des erfindungsgemäßen Feldeffekttransistors entspricht im wesentlichen der in Fig. 2 gezeigte Ausführungsform des erfindungsgemäßen Feldeffekttransistors mit der Ausnahme, daß an der zweiten Gateoxidschicht 6 auf der Höhe der ersten Gateelektrode 5 ein Spacer 14, insbesondere ein Oxidspacer, angeordnet ist. Dabei

kann die Ausbildung des Spacers 14 an den Flanken der ersten Gateelektrodenschicht 5 unmittelbar nach deren Strukturierung erfolgen, noch bevor die stegförmige Erhebung 2 ausgebildet ist. Die Oxidation zur Erzeugung der zweiten Gateoxidschicht 6 verstärkt dann diesen Spacer 14 durch eine zusätzliche Oxidschicht unmittelbar an den seitlichen Oberflächen der ersten Gateelektrodenschicht 5.

Der erfindungsgemäße Feldeffekttransistor besitzt den Vorteil, daß eine deutliche Erhöhung der für den Flußstrom  $I_{ON}$  wirksamen Kanalweite gegenüber bisher verwendeten, konventionellen Transistorstrukturen gewährleistet werden kann, ohne daß eine Verringerung der erzielbaren Integrationsdichte hingenommen werden muß. Bei dem erfindungsgemäßen Feldeffekttransistor wird das planare Kanalgebiet an der oberen Oberfläche der Erhebung durch zusätzliche vertikale Kanalgebiete an den Seitenflächen der Erhebung in der Weite ausgedehnt. Diese zusätzlichen vertikalen Kanalgebiete schließen sich unmittelbar an das planare Kanalgebiet an (vertical extended channel regions). Weiterhin besitzt der erfindungsgemäße Feldeffekttransistor einen geringen Sperrstrom  $I_{OFF}$ . Diese Vorteile werden erzielt, ohne daß Dicke des Gate-Isolators bis in den Bereich des Tunnels von Ladungsträgern oder einer verminderten Stabilität verringert werden muß.

## Patentansprüche

1. Feldeffekttransistor, insbesondere MIS-Feldeffekttransistor, mit:

- a) zumindest einer auf einem Halbleitersubstrat (1) angeordneten stegförmigen Erhebung (2), die eine obere Oberfläche (2a) und seitliche Oberflächen (2b) aufweist,

- b) einer ersten Gateoxidschicht (4), die auf der oberen Oberfläche (2a) der stegförmigen Erhebung (2) angeordnet ist,

- c) einer ersten Gateelektrode (5), die auf der ersten Gateoxidschicht (4) angeordnet ist, wobei die erste Gateelektrode eine obere Oberfläche und seitliche Oberflächen aufweist,

- d) einer zweiten Gateoxidschicht (6), die zumindest auf einem Teil der seitlichen Oberflächen (2b) der stegförmigen Erhebung (2) und der ersten Gateelektrode (4) angeordnet ist,

- e) einer zweiten Gateelektrode (7), die auf der zweiten Gateoxidschicht (6) und der oberen Oberfläche der ersten Gateelektrode (5) angeordnet ist, und

- f) Source- und Draingebiete, die auf der stegförmigen Erhebung (2) angeordnet sind.

2. Feldeffekttransistor nach Anspruch 1, dadurch gekennzeichnet, daß die zweite Gateoxidschicht (6) auf den seitlichen Oberflächen der ersten Gateelektrode (5) dicker

ausgebildet ist als auf den seitlichen Oberflächen (2b) der stegförmigen Erhebung (2).

3. Feldeffekttransistor nach Anspruch 1 oder 2,

5 d a u r c h g e k e n n z e i c h n e t , daß

an der zweiten Gateoxidschicht (6) auf der Höhe der ersten

Gateelektrode (5) ein isolierender Spacer (14) angeordnet

ist.

10 4. Feldeffekttransistor, insbesondere MIS-

Feldeffekttransistor, mit:

- 15 a) zumindest einer auf einem Halbleitersubstrat (1)

angeordneten stegförmigen Erhebung (2), die eine obere

Oberfläche (2a) und seitliche Oberflächen (2b)

aufweist,

- b) einer ersten Gateoxidschicht (4), die zumindest auf

einem Teil der seitlichen Oberflächen (2b) der

stegförmigen Erhebung (2) angeordnet ist,

- c) einer ersten Gateelektrode (5), die auf der ersten

Gateoxidschicht (4) angeordnet ist, wobei die erste

Gateelektrode (4) eine obere Oberfläche und seitlichen

Oberflächen aufweist,

- d) einer zweiten Gateoxidschicht (6), die auf der oberen

Oberfläche (2a) der stegförmigen Erhebung (2) und der

oberen Oberfläche der ersten Gateelektrode (5)

angeordnet ist,

- e) einer zweiten Gateelektrode (7), die auf der zweiten

Gateoxidschicht (6) und den seitlichen Oberflächen der

ersten Gateelektrode (5) angeordnet ist, und

- 35 f) Source- und Draingebiete, die auf der stegförmigen

Erhebung (2) angeordnet sind.

5. Feldeffekttransistor nach einem der Anspruch 1 bis 4,

d a d u r c h g e k e n n z e i c h n e t , daß

die Kanten (8) der stegförmigen Erhebung (2) zwischen der

5 oberen Oberfläche (2a) und den seitlichen Oberflächen (2b)

verrundet sind.

- 10 6. Feldeffekttransistor nach Anspruch 5,

d a d u r c h g e k e n n z e i c h n e t , daß

der Krümmungsradius der Kanten (8) in der Größenordnung

der Schichtdicke der ersten oder zweiten Gateoxidschicht

(4, 6) liegt.

- 15 7. Feldeffekttransistor nach einem der Ansprüche 1 bis 7,

d a d u r c h g e k e n n z e i c h n e t , daß

zwischen dem Sourcegebiet und den Gateelektroden sowie

zwischen dem Draingebiet und den Gateelektroden Spacer

angeordnet sind.

- 20 8. Feldeffekttransistor nach einem der Ansprüche 1 bis 8,

d a d u r c h g e k e n n z e i c h n e t , daß

die erste Gateelektrode (5) eine Polysiliziumschicht

aufweist.

- 25 9. Feldeffekttransistor nach einem der Ansprüche 1 bis 8,

d a d u r c h g e k e n n z e i c h n e t , daß

die zweite Gateelektrode (7) eine Polysilizium-Metall-

Doppelschicht oder eine Polyzidschicht aufweist.

- 30 10. Feldeffekttransistor nach einem der Ansprüche 1 bis 9,

d a d u r c h g e k e n n z e i c h n e t , daß

der Teil der seitlichen Oberflächen (2b) der stegförmigen

Erhebung (2), der von einer Gateoxidschicht (4, 6) bedeckt

ist, von einer Grabenisolation (3) begrenzt ist.

- 35 11. Feldeffekttransistor nach einem der Ansprüche 1 bis 10,

d a d u r c h g e k e n n z e i c h n e t , daß

die Dotierungsprofiltiefe der Source- und Draingegebiete größer als die Ausdehnung des Teils der seitlichen Oberflächen (2b) der stegförmigen Erhebung (2) ist, der von einer Gateoxidschicht (4, 6) bedeckt ist.

5

12. Verfahren zur Herstellung eines Feldeffekttransistor, insbesondere eines MIS-Feldeffekttransistor, mit den Schritten:

- 10 a) ein Halbleitersubstrat (1) mit einer darauf aufgebrachten ersten Gateoxidschicht (4) und einer auf die Gateoxidschicht (4) aufgebrachten ersten Gateelektrodenschicht (5) wird bereitgestellt,

- 15 b) zumindest eine stegförmige Erhebung (2) mit einer oberen Oberfläche (2a) und seitlichen Oberflächen (2b) wird erzeugt, wobei die erste Gateoxidschicht (4) und die erste Gateelektrodenschicht (5) auf der oberen Oberfläche (2a) angeordnet sind,

- 20 c) zumindest auf einen Teil der seitlichen Oberflächen (2b) der stegförmigen Erhebung (2) und der ersten Gateelektrodenschicht (5) wird eine zweite Gateoxidschicht (6) erzeugt,

- 25 d) eine zweite Gateelektrodenschicht (7) wird aufgebracht, so daß die zweite Gateelektrodenschicht (7) auf der zweiten Gateoxidschicht (6) und der oberen Oberfläche der ersten Gateelektrodenschicht (5) angeordnet ist, und

- 30 e) die erste und die zweite Gateelektrodenschicht (5, 7) werden zu ersten und zweiten Gatelektroden strukturiert und Source- und Draingegebiete werden erzeugt.

35 13. Verfahren nach Anspruch 12,

d a d u r c h g e k e n n z e i c h n e t , daß

die Erzeugung der stegförmige Erhebung (2) mit der

Strukturierung der Gräben für eine Grabenisolierung (3)

erfolgt.

5

14.Verfahren nach Anspruch 13,

d a d u r c h g e k e n n z e i c h n e t , daß

die Gräben für die Grabenisolierung mit Oxid (3) gefüllt

werden und eine Rückätzung durchgeführt wird, so daß ein

10 Teil der seitlichen Oberflächen (2b) der stegförmigen

Erhebung (2) freigelegt wird.

15.Verfahren nach Anspruch 14,

d a d u r c h g e k e n n z e i c h n e t , daß

15 vor der Rückätzung ein CMP-Schritt durchgeführt wird.

16.Verfahren nach einem der Ansprüche 12 bis 15,

d a d u r c h g e k e n n z e i c h n e t , daß

zumindest ein thermischer Prozeß zur Verrundung der Kanten

20 (8) der stegförmigen Erhebung (2) zwischen der oberen

Oberfläche (2a) und den seitlichen Oberflächen (2b)

durchgeführt wird.

17.Verfahren nach einem der Ansprüche 12 bis 16,

25 d a d u r c h g e k e n n z e i c h n e t , daß

die Gateoxidschichten (4, 6) jeweils durch eine thermische

Oxidation erzeugt werden.

18.Verfahren nach einem der Ansprüche 12 bis 17,

30 d a d u r c h g e k e n n z e i c h n e t , daß

die zweite Gateoxidschicht (6) mit selektiver Oxidation

erzeugt wird, so daß die zweite Gateoxidschicht (6) auf

den seitlichen Oberflächen der ersten Gateelektrode (5)

35 dicker ausgebildet ist als auf den seitlichen Oberflächen

(2b) der stegförmigen Erhebung (2).

19.Verfahren nach einem der Ansprüche 12 bis 18,

WO 03/003442

PCT/EP02/07028

23

d a d u r c h g e k e n n z e i c h n e t , daß

nach der Erzeugung der ersten Gateelektrodenschicht (5)

ein isolierender Spacer erzeugt wird, so daß an der

zweiten Gateoxidschicht (6) auf der Höhe der ersten

5 Gateelektrode (5) ein isolierender Spacer (14) angeordnet

ist.

WO 03/003442

PCT/EP02/07028

1/5

FIG 1

FIG 2

FIG 3a

FIG 3b

FIG 3c

FIG 3d

FIG 3e

FIG 3f

FIG 3g

FIG 3h

FIG 4

FIG 5

FIG 6

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                     |                                                                                                                                                                       | International Application No<br>PCT/EP 02/07028                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H01L21/336 H01L29/78                                                                                                                               |                                                                                                                                                                       |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                               |                                                                                                                                                                       |                                                                                |

| B. FIELDS SEARCHED                                                                                                                                                                              |                                                                                                                                                                       |                                                                                |

| Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                         |                                                                                                                                                                       |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                   |                                                                                                                                                                       |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                      |                                                                                                                                                                       |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                          |                                                                                                                                                                       |                                                                                |

| Category *                                                                                                                                                                                      | Citation of document, with indication, where appropriate, of the relevant passages                                                                                    | Relevant to claim No.                                                          |

| A                                                                                                                                                                                               | US 5 844 278 A (MIZUNO TOMOHISA ET AL)<br>1 December 1998 (1998-12-01)<br>column 10, line 53 -column 11, line 54;<br>figures 11,12<br>---                             | 1,2,4,<br>7-9,12                                                               |

| A                                                                                                                                                                                               | WO 00 30181 A (WIEDER ARMIN ;INFINEON<br>TECHNOLOGIES AG (DE); WIDMANN HELGA HF<br>(DE)) 25 May 2000 (2000-05-25)<br>page 7, line 7 -page 9, line 30; figure 6<br>--- | 1,4                                                                            |

| A                                                                                                                                                                                               | US 5 391 506 A (KUNITOMO HIROYASU ET AL)<br>21 February 1995 (1995-02-21)<br>the whole document<br>---                                                                | 1-19                                                                           |

| A                                                                                                                                                                                               | US 5 583 362 A (MAEGAWA SHIGETO)<br>10 December 1996 (1996-12-10)<br>figure 30<br>---                                                                                 | 1,4<br>-/-                                                                     |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                  |                                                                                                                                                                       | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents:                                                                                                                                                        |                                                                                                                                                                       |                                                                                |

| *A* document disclosing the general state of the art which is not considered to be of particular relevance                                                                                      |                                                                                                                                                                       |                                                                                |

| *B* earlier document but published on or after the international filing date                                                                                                                    |                                                                                                                                                                       |                                                                                |

| *L* document which may throw doubt on novelty, claim(s) or priority date to establish the publication date of another citation or other special reason (as specified)                           |                                                                                                                                                                       |                                                                                |

| *C* document referring to an oral disclosure, use, exhibition or other means                                                                                                                    |                                                                                                                                                                       |                                                                                |

| *P* document published prior to the international filing date but later than the priority date claimed                                                                                          |                                                                                                                                                                       |                                                                                |

| Date of the actual completion of the international search<br><br>15 October 2002                                                                                                                | Date of mailing of the International search report<br><br>23/10/2002                                                                                                  |                                                                                |

| Name and mailing address of the ISA<br><br>Proprietary Patent Office, P.O. Box 5816 Patentlaan 2<br>NL-2200 NV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 51 651 epo nl.<br>Fax. (+31-70) 340-3016 | Authorized officer<br><br>Nesso, S                                                                                                                                    |                                                                                |

Form PCT/ISA210 (second sheet) (July 1992)

| INTERNATIONAL SEARCH REPORT                          |                                                                                     | International Application No.<br>PCT/EP 02/07028 |

|------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------|

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                     |                                                  |

| Category *                                           | Citation of document, with indication, where appropriate, of the relevant passages  | Relevant to claim No.                            |

| A                                                    | US 5 567 959 A (MINEJI AKIRA)<br>22 October 1996 (1996-10-22)<br>figure 8D<br>----- | 1,4                                              |

Form PCT/ISA/210 (continuation of second sheet) (July 1992)

page 2 of 2

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/EP 02/07028

| Patent document cited in search report |   | Publication date |                   | Patent family member(s)                                                           |                                                                                  | Publication date |

|----------------------------------------|---|------------------|-------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|

| US 5844278                             | A | 01-12-1998       | JP KR             | 8139325 A<br>170468 B1                                                            | 31-05-1996<br>01-02-1999                                                         |                  |

| WO 0030181                             | A | 25-05-2000       | DE CN WO EP TW US | 19853268 A1<br>1333923 T<br>0030181 A2<br>1138085 A2<br>457722 B<br>2002014669 A1 | 31-05-2000<br>30-01-2002<br>25-05-2000<br>04-10-2001<br>01-10-2001<br>07-02-2002 |                  |

| US 5391506                             | A | 21-02-1995       | JP JP JP          | 5218415 A<br>5218416 A<br>5343679 A                                               | 27-08-1993<br>27-08-1993<br>24-12-1993                                           |                  |

| US 5583362                             | A | 10-12-1996       | JP DE KR US       | 7135325 A<br>4433086 A1<br>220039 B1<br>5578513 A                                 | 23-05-1995<br>30-03-1995<br>01-09-1999<br>26-11-1996                             |                  |

| US 5567959                             | A | 22-10-1996       | JP JP             | 2734962 B2<br>7193251 A                                                           | 02-04-1998<br>28-07-1995                                                         |                  |

Form PCT/ISA/210 (patent family entries) (July 1992)

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/EP 02/07028

A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES

IPK 7 HO1L21/336 HO1L29/78

Nach der internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK

## B. RECHERCHIERTE GEBIETE

Rechercheierter Münzapräzess (Klassifikationssystem und Klassifikationsymbole)

IPK 7 HO1L

Recherchierte aber nicht zum Münzapräzess gehörende Veröffentlichungen, sowie diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

EPO-Internal

## C. ALS WESENTLICH ANGESIEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                                                | Betr. Anspruch Nr. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| A          | US 5 844 278 A (MIZUNO TOMOHISA ET AL)<br>1. Dezember 1998 (1998-12-01)<br>Spalte 10, Zeile 53 - Spalte 11, Zeile 54;<br>Abbildungen 11,12<br>---                                 | 1,2,4,<br>7-9,12   |

| A          | WO 00 30181 A (WIEDER ARMIN ; INFINEON<br>TECHNOLOGIES AG (DE); WIDMANN HELGA HF<br>(DE)) 25. Mai 2000 (2000-05-25)<br>Seite 7, Zeile 7 -Seite 9, Zeile 30;<br>Abbildung 6<br>--- | 1,4                |

| A          | US 5 391 506 A (KUNITOMO HIROYASU ET AL)<br>21. Februar 1995 (1995-02-21)<br>das ganze Dokument<br>---                                                                            | 1-19               |

| A          | US 5 583 362 A (MAEGAWA SHIGETO)<br>10. Dezember 1996 (1996-12-10)<br>Abbildung 30<br>---                                                                                         | 1,4                |

|            | -/-                                                                                                                                                                               |                    |

Weitere Veröffentlichungen sind der Fortsetzung von Folg C zu entnehmen

Siehe Anhang Patentfamilie

\* Besondere Kategorien von angegebenen Veröffentlichungen :

\*A\* Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonderes bedeutsam anzusehen ist

\*E\* älteres Dokument, das jedoch erst am oder nach dem Internationalen Anmeldedatum veröffentlicht wurde

\*L\* Veröffentlichung, die gezeigt hat, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belogen werden soll und aus einem anderen besonderen Grund angegeben ist (siehe ausgetragen)

\*O\* Veröffentlichung, die sich auf eine Erfindung, eine Erfindungsumwandlung, eine Darstellung oder eine Herstellung bezieht

\*P\* Veröffentlichung, die vor dem Internationalen Anmeldedatum, aber nach dem bausepruchlichen Prioritätsdatum veröffentlicht worden ist

\*\* Später: Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung relevanten Hintergrundes oder der in Zugriff befindlichen Theorie angegeben ist

\*\*\* Veröffentlichung von besonderer Bedeutung, die bausepruchte Erfüllung einer Erfindung ermöglicht, Veröffentlichung kann neu oder auf erforderlicher Fälligkeit herumgehend betrachtet werden

\*\*\*\* Veröffentlichung von besonderer Bedeutung, die bausepruchte Erfüllung kann nicht als auf erforderlicher Fälligkeit herumgehend betrachtet werden, weil die Veröffentlichung eine Verbindung zu anderen vorherigen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann natürlegend ist

\*\*X\* Veröffentlichung, die Mitglied derselben Patentfamilie ist

Datum des Abschlusses der internationalen Recherche

Absendetermin des Internationalen Recherchenberichts

15. Oktober 2002

23/10/2002

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P. B. 5018 Patentanlagen 2

D-8036 München

Tel. (+49-70) 340-2040, Tx. 91 651 epo n,

Fax: (+49-70) 340-3016

Bevollmächtigter Bediensteter

Nesso, S

Formblatt PCT/ISA/210 (Blatt 2) (Juli 1996)

## INTERNATIONAHLER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/EP 02/07028

| C.(Fortsetzung) ALS WESENTLICH ANGEGEHENE UNTERLAGEN |                                                                                                    |                    |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------|

| Kategorie*                                           | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile | Sehr. Anspruch Nr. |

| A                                                    | US 5 567 959 A (MINEJI AKIRA)<br>22. Oktober 1996 (1996-10-22)<br>Abbildung 8D<br>-----            | 1,4                |

Formblatt PCT/ISA210 (Fortsetzung von Blatt 2) (Juli 1998)

## INTERNATIONAL RECHERCHENBERICHT

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Patentzertifikat

PCT/EP 02/07028

| Im Recherchenbericht angeführtes Patentdokument | Datum der Veröffentlichung |                                  | Mitglied(er) der Patentfamilie                                                    | Datum der Veröffentlichung                                                       |

|-------------------------------------------------|----------------------------|----------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US 5844278                                      | A 01-12-1998               | JP<br>KR                         | 8139325 A<br>170468 B1                                                            | 31-05-1996<br>01-02-1999                                                         |

| WO 0030181                                      | A 25-05-2000               | DE<br>CN<br>WO<br>EP<br>TW<br>US | 19853268 A1<br>1333923 T<br>0030181 A2<br>1138085 A2<br>457222 B<br>2002014669 A1 | 31-05-2000<br>30-01-2002<br>25-05-2000<br>04-10-2001<br>01-10-2001<br>07-02-2002 |

| US 5391506                                      | A 21-02-1993               | JP<br>JP<br>JP                   | 5218415 A<br>5218416 A<br>5343679 A                                               | 27-08-1993<br>27-08-1993<br>24-12-1993                                           |