(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3782327号

(P3782327)

(45) 発行日 平成18年6月7日(2006.6.7)

(24) 登録日 平成18年3月17日(2006.3.17)

(51) Int.C1.

F 1

HO4N 5/335 (2006.01)

HO1L 27/146 (2006.01)HO4N 5/335

HO1L 27/14

E

A

請求項の数 3 (全 10 頁)

(21) 出願番号 特願2001-233698 (P2001-233698)

(22) 出願日 平成13年8月1日 (2001.8.1)

(65) 公開番号 特開2003-46865 (P2003-46865A)

(43) 公開日 平成15年2月14日 (2003.2.14)

審査請求日 平成15年6月17日 (2003.6.17)

(73) 特許権者 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110000040

特許業務法人池内・佐藤アンドパートナーズ

(72) 発明者 春日 繁孝

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72) 発明者 山口 琢己

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 松田 岳士

最終頁に続く

(54) 【発明の名称】 固体撮像装置およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子と、前記光電変換素子に対応するフローティングディフュージョン(FD)部と、前記FD部の電位を検出する画素アンプと、前記光電変換素子で光電変換された電荷信号を前記FD部に読み出す読出しトランジスタと、前記FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、前記リセットトランジスタを介して前記FD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、前記画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、前記リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、

選択行のドレイン線を「High」レベルにし、非選択行のドレイン線を「Low」レベルにする工程と、

全ての光電変換セルのリセットトランジスタと各列の出力信号線につながった前記ロードトランジスタをオンし、次に前記全ての光電変換セルのリセットトランジスタと前記ロードトランジスタをオフして、選択行の光電変換セル内の前記FD部の電位を信号のない基準レベルとして前記画素アンプで検出する工程と、

前記ロードトランジスタと前記読出しトランジスタをオンし、次に前記ロードトランジスタと前記読出しトランジスタをオフして、前記選択行の光電変換セル内の前記FD部の電位を蓄積信号レベルとして前記画素アンプで検出する工程と、

10

20

前記選択行のドレイン線を「High」レベルから「Low」レベルにした後、前記全ての光電変換セルのリセットトランジスタをオン／オフして、前記選択行を非選択にする工程とを含むことを特徴とする固体撮像装置の駆動方法。

【請求項 2】

光電変換素子と、前記光電変換素子に対応するフローティングディフュージョン(FD)部と、前記FD部の電位を検出する画素アンプと、前記光電変換素子で光電変換された電荷信号を前記FD部に読み出す読み出しトランジスタと、前記FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、前記リセットトランジスタを介して前記FD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、前記画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、前記リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、

選択行のドレイン線を「High」レベルにし、非選択行のドレイン線を「Low」レベルにし、全ての光電変換セルのリセットトランジスタと各列の出力信号線につながった前記ロードトランジスタをオンし、先に前記全ての光電変換セルのリセットトランジスタをオフした後に前記ロードトランジスタをオフして、選択行の光電変換セル内の前記FD部の電位を信号のない基準レベルとして前記画素アンプで検出し、

前記ロードトランジスタと前記読み出しトランジスタをオンし、次に読み出しトランジスタをオフした後に前記ロードトランジスタをオフして、前記選択行の光電変換セル内の前記FD部の電位を蓄積信号レベルとして前記画素アンプで検出し、

次に、前記選択行のドレイン線を「High」レベルから「Low」レベルにした後、前記全ての光電変換セルのリセットトランジスタをオン／オフして、前記選択行を非選択にすることを特徴とする固体撮像装置の駆動方法。

【請求項 3】

光電変換素子と、前記光電変換素子に対応するフローティングディフュージョン(FD)部と、前記FD部の電位を検出する画素アンプと、前記光電変換素子で光電変換された電荷信号を前記FD部に読み出す読み出しトランジスタと、前記FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、前記リセットトランジスタを介して前記FD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、前記画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、前記リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、

選択行のドレイン線および非選択行のドレイン線を「High」レベルにし、各列の出力信号線につながった前記ロードトランジスタのゲート電圧を「Low」レベルに設定し、全ての光電変換セルのリセットトランジスタをオン／オフした後、前記読み出しトランジスタをオン／オフして、前記全ての光電変換セルで生成された電荷信号を初期化することで前記光電変換素子に蓄積された不要電荷の掃き出しを行うことを特徴とする固体撮像装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、複数の光電変換素子が配置された固体撮像装置およびその駆動方法に係り、特に光電変換セルの開口率向上やサイズ縮小化技術に関する。

【0002】

【従来の技術】

従来のMOS型イメージセンサは、フローティングディフュージョン部（以下、FD部と略称する）を縮小化して感度向上を図るためと、フォトダイオード部（以下、PD部と略称する）の表面をP型半導体で覆い白キズ対策を図るために、フローティング・ディフュ

10

20

30

40

50

ーション・アンプリファーア（以下、FDAと略称する）方式の画素構造を採用してきた。

【0003】

【発明が解決しようとする課題】

この方式は、PD部に蓄積された電荷を一旦FD部に読み出す読出しトランジスタと、光電変換セルごとに設けられた画素アンプと、FD部の電位をリセットするリセットトランジスタと、垂直走査を行う行選択トランジスタとで構成され、1つの光電変換セルに合計4つのトランジスタが必要となり、セルに占めるトランジスタ部分のサイズが大きくなり、PD部の面積の確保や一つの光電変換セルサイズの微細化が困難であるという問題を抱えている。

【0004】

本発明は、かかる問題点に鑑みてなされたものであり、その目的は、FDA方式で一般的に使用される前記4つのトランジスタのうち、行選択トランジスタをなくすことによって、1つの光電変換セルを3つのトランジスタのみで構成できるようにするとともに、リセットトランジスタのゲート電圧印加線を、光電変換セル領域を遮光する遮光層と兼用させることもできるため、PD部の面積確保や光電変換セルサイズの微細化を容易に実現できる固体撮像装置およびその駆動方法を提供することにある。

【0005】

【課題を解決するための手段】

前記の目的を達成するため、本発明に係る固体撮像装置の第1の駆動方法は、光電変換素子（PD部）と、光電変換素子に対応するフローティングディフュージョン（FD）部と、FD部の電位を検出する画素アンプと、光電変換素子で光電変換された電荷信号をFD部に読み出す読出しトランジスタと、FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、リセットトランジスタを介してFD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、選択行のドレイン線を「High」レベルにし、非選択行のドレイン線を「Low」レベルにする工程と、全ての光電変換セルのリセットトランジスタと各列の出力信号線につながったロードトランジスタをオンし、次に全ての光電変換セルのリセットトランジスタとロードトランジスタをオフして、選択行の光電変換セル内のFD部の電位を信号のない基準レベルとして画素アンプで検出する工程と、ロードトランジスタと読出しトランジスタをオンし、次にロードトランジスタと読出しトランジスタをオフして、選択行の光電変換セル内のFD部の電位を蓄積信号レベルとして画素アンプで検出する工程と、選択行のドレイン線を「High」レベルから「Low」レベルにした後、全ての光電変換セルのリセットトランジスタをオン／オフして、選択行を非選択にする工程とを含むことを特徴とする。

【0006】

この構成によれば、1つの光電変換セル内のトランジスタを、画素アンプと、読出しトランジスタと、リセットトランジスタの3つのみで構成し、リセットトランジスタのゲート電圧印加線を、光電変換セル領域を遮光する遮光層と兼用させ、ドレイン線にパルス信号（VDDCEL）を与えて、その「High」レベル時と「Low」レベル時のそれぞれで、全ての光電変換セルのリセットトランジスタをオン／オフすることで、垂直走査機能を実現することができ、従来では光電変換セルに必要であった行選択トランジスタが不要となり、PD部の面積確保や光電変換セルサイズの微細化を実現することが可能になる。

【0010】

さらに、基準レベルの検出は、リセットトランジスタとロードトランジスタが共にオフのときに行われ、この時、ロードトランジスタがオフすると、信号線内の電子が、基準レベルのFD部の電位がかかった、画素内アンプゲートの下を通ってVDD電源に流れ、安定したリセットゲート下の電位になり、安定した信号線電位を実現することができる。また、信号レベルの検出は、読出しトランジスタとロードトランジスタが共にオフのときに

10

20

30

40

50

行われ、この時、ロードトランジスタがオフすると、信号線内の電子が、信号レベルのF D部の電位がかかった、画素内アンプゲートの下を通ってV D D電源に流れ、安定したリセットゲート下の電位になり、安定した信号線電位を実現することができる。

#### 【0011】

本発明に係る固体撮像装置の第2の駆動方法は、光電変換素子(PD部)と、光電変換素子に対応するフローティングディフュージョン(FD)部と、FD部の電位を検出する画素アンプと、光電変換素子で光電変換された電荷信号をFD部に読み出す読出しトランジスタと、FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、リセットトランジスタを介してFD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、選択行のドレイン線を「High」レベルにし、非選択行のドレイン線を「Low」レベルにし、全ての光電変換セルのリセットトランジスタと各列の出力信号線につながったロードトランジスタをオンし、先に全ての光電変換セルのリセットトランジスタをオフした後にロードトランジスタをオフして、選択行の光電変換セル内のFD部の電位を信号のない基準レベルとして画素アンプで検出し、ロードトランジスタと読出しトランジスタをオンし、次に読み出しトランジスタをオフした後にロードトランジスタをオフして、選択行の光電変換セル内のFD部の電位を蓄積信号レベルとして画素アンプで検出し、次に、選択行のドレイン線を「High」レベルから「Low」レベルにした後、全ての光電変換セルのリセットトランジスタをオン／オフして、選択行を非選択にすることを特徴とする。

10

#### 【0012】

この構成によれば、第1の固体撮像装置の駆動方法による利点に加えて、第2の固体撮像装置の駆動方法に比較して、基準レベルを検出する際に、リセットトランジスタをロードトランジスタよりも早くオフにすることで、FD部の基準レベルを早く安定にさせるため、信号線の電位が更に安定化する。

#### 【0015】

本発明に係る固体撮像装置の第3の駆動方法は、光電変換素子(PD部)と、光電変換素子に対応するフローティングディフュージョン(FD)部と、FD部の電位を検出する画素アンプと、光電変換素子で光電変換された電荷信号をFD部に読み出す読出しトランジスタと、FD部の電荷信号をリセット信号によりリセットするリセットトランジスタと、リセットトランジスタを介してFD部へ「Low」レベルおよび「High」レベルのパルス電圧を供給するためのドレイン線とを有する光電変換セルが複数個半導体基板上で行列状に配置され、画素アンプの出力信号線を一定電圧に設定するためのロードトランジスタを有し、リセットトランジスタのリセット信号の印加線が全ての光電変換セルに共通接続された固体撮像装置を駆動する方法であって、選択行のドレイン線および非選択行のドレイン線を「High」レベルにし、各列の出力信号線につながったロードトランジスタのゲート電圧を「Low」レベルに設定し、全ての光電変換セルのリセットトランジスタをオン／オフした後、読出しトランジスタをオン／オフして、全ての光電変換セルで生成された電荷信号を初期化することで光電変換素子に蓄積された不要電荷の掃き出しを行うことを特徴とする。

30

40

#### 【0016】

この構成によれば、画素アンプは電位検出することなく、光電変換素子のみリセット状態にすることことができ、電子シャッター機能を実現することができる。

#### 【0017】

##### 【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照して説明する。なお、以下の実施形態では、固体撮像装置としてMOS型イメージセンサを例に説明する。

#### 【0018】

(第1の実施形態)

まず、本発明の第1の実施形態について、図1から図3を参照して説明する。

【0019】

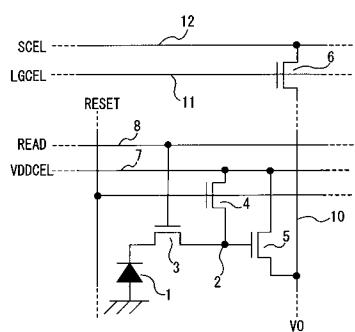

図1は、本発明の第1の実施形態に係るMOS型イメージセンサにおける光電変換セルの回路構成図である。なお、図1の光電変換セルの構成は、後述する他の実施形態においても同様である。

【0020】

図1において、1は光電変換を行なうPD部、2は光電変換後の電荷を蓄積するFD部、3はFD部2に電荷読出しを行う読出しトランジスタ、4はFD部2の電位をドレイン線信号VDDCELの電位に初期化するリセットトランジスタ、5はFD部2の電荷検出を行う画素アンプ、6は画素アンプ5と共にソースフォロワアンプを形成するためのロードトランジスタ、7はドレイン線、8は読出しトランジスタ3に読み出し信号READを印加する読み出しパルス線、9はFD部2の電位をドレイン電圧信号VDDCELの電位に初期化するリセット信号RESETが印加されるリセットパルス線、10は画素アンプ5で検出された画素信号VOを伝達する出力信号線、11はロードトランジスタ6のゲートにロードゲート信号LGCELを印加するロードゲート線、12はロードトランジスタ6のソースにソース電圧信号SCELを印加するソース線である。

10

【0021】

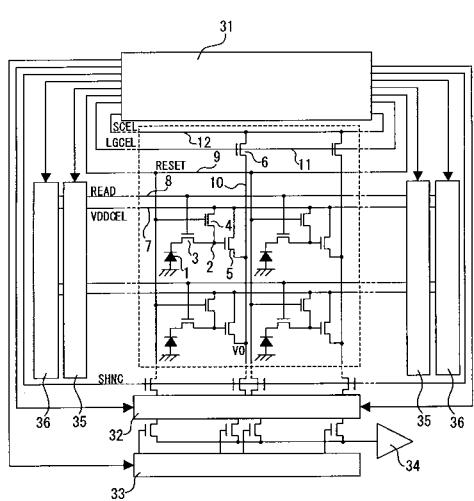

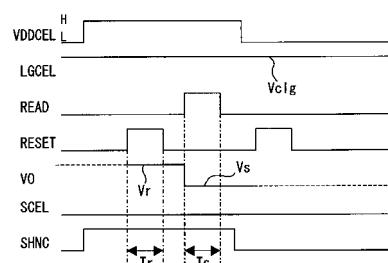

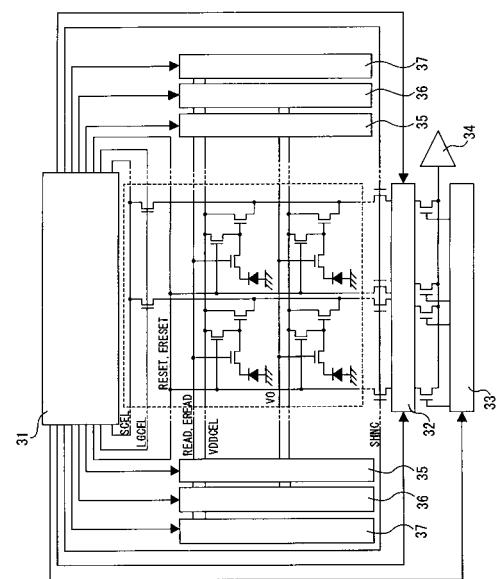

図2は、図1の光電変換セルをアレイ状に配置したMOS型イメージセンサの全体回路構成図で、図3はその駆動方法を示す動作タイミング図である。

20

【0022】

図2において、31はタイミング発生回路、32はノイズキャンセル回路、33は水平ライン走査回路、34は出力アンプ、35はマルチプレクサ、36は垂直ライン走査回路である。タイミング発生回路31は、ロードゲート信号LGCEL、ソース電圧信号SCEL、リセット信号RESET、サンプルホールドパルスSHNCを生成するとともに、ドレイン電圧信号VDDCEL、読み出し信号READの生成タイミングを制御する。

【0023】

以下、図2および図3を用いて、本実施形態によるMOS型イメージセンサの動作について詳細に説明する。なお、図3の動作タイミングは、水平プランギング期間内で一連の動作を完結させるものである。

30

【0024】

まず、ロードゲート線11にロードゲート信号LGCELとして、画素アンプ5が動作する所定の一定電圧Vc1gを印加する。次に、選択対象行のドレイン電圧信号VDDCELを「High」レベルにした後、全ての光電変換セルに共通するリセット信号RESETを活性化して、FD部2の電位をドレイン電圧信号VDDCELの電位に初期化する。このとき、FD部2の電位をリセットレベルVrとして画素アンプで検出し、出力信号線10を介して、このリセットレベルVrをサンプルホールドパルスSHNCでサンプリングして、ノイズキャンセル回路32にて、画素信号VOのリセットレベルクランプを行なう(図3の期間Tr)。

【0025】

40

次に、全ての光電変換セルに共通するリセット信号RESETを非活性化した後、選択行の読み出し信号READを活性化してFD部2にPD部1の蓄積電荷を読み出し、画素アンプ5で蓄積信号レベルVsを検出し、出力信号線10を介して、この蓄積信号レベルVsをサンプルホールドパルスSHNCでサンプリングして、ノイズキャンセル回路32にて、画素信号VOのサンプルホールドを行なう(図3の期間Ts)。以上の動作により、画素アンプ5の閾値ばらつきやノイズ成分を除去した画素信号VOを検出することができる。

【0026】

続いて、選択行のドレイン電圧信号VDDCELを「Low」レベルにして、全ての光電変換セルに共通するリセット信号RESETを活性化すると、FD部2の電位は、ドレイ

50

ン電圧信号V D D C E Lの「L o w」レベル（この場合、G N D）になり、画素アンプ5は動作しなくなる。以降、垂直ライン走査回路3 6によって、再び該選択行のドレイン電圧信号V D D C E Lと読み出し信号R E A Dが活性化されるまで、該画素アンプ5は動作しないため、非選択状態となる。

#### 【0027】

すなわち、ドレイン電圧信号V D D C E L、読み出し信号R E A D及びリセット信号R E S E Tのタイミングによって、3つのトランジスタ3、4、5だけで、光電変換セルの蓄積信号読み出し、蓄積信号リセット、および垂直走査が行えることになり、従来では必要であった行選択トランジスタが不要になるとともに、リセット信号R E S E Tが印加されるリセット線9を遮光層と兼用できるため、光電変換セル内のP D部1のサイズが大きくされ、セルサイズの微細化に有利になる。10

#### 【0028】

##### （第2の実施形態）

次に、本発明の第2の実施形態について、図2および図4を参照して説明する。

#### 【0029】

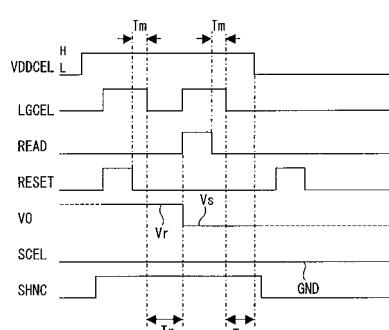

図4は、本発明の第2の実施形態に係るM O S型イメージセンサの駆動方法を示す動作タイミング図である。以下、図2および図4を用いて、本実施形態によるM O S型イメージセンサの動作について詳細に説明する。なお、図4の動作タイミングは、水平プランキング期間内で一連の動作を完結させるものである。

#### 【0030】

まず、選択対象行のドレイン電圧信号V D D C E Lを「H i g h」レベルにした後、各列のロードトランジスタ6に共通するロードゲート信号L G C E Lと、全ての光電変換セルに共通するリセット信号R E S E Tとを活性化して、F D部2の電位をドレイン電圧信号V D D C E Lの電位に初期化する。次に、リセット信号R E S E Tを非活性化した後、マージン期間T mを設けて、ロードゲート信号L G C E Lを非活性化し、この直後に、画素アンプ5で信号のない基準レベルV rを検出し、出力信号線1 0を介して、この基準レベルV rをサンプルホールドパルスS H N Cでサンプリングして、ノイズキャンセル回路3 2にて、画素信号V Oの基準レベルクランプを行なう（図4の期間T r）。20

#### 【0031】

次に、ロードゲート信号L G C E Lと選択行の読み出し信号R E A Dを活性化して、F D部2にP D部1の蓄積電荷を読み出した後、読み出し信号R E A Dを非活性化した後、マージン期間T mを設けて、ロードゲート信号L G C E Lを非活性化し、この直後に、画素アンプ5で蓄積信号レベルV sを検出し、出力信号線1 0を介して、この蓄積信号レベルV sをサンプルホールドパルスS H N Cでサンプリングして、ノイズキャンセル回路3 2にて、画素信号V Oのサンプルホールドを行なう（図4の期間T s）。30

#### 【0032】

上記のように、リセット信号R E S E Tをロードゲート信号L G C E Lよりも早く非活性化することで、F D部2の基準レベルV rが早く安定化する。また、読み出し信号R E A Dをロードゲート信号L G C E Lよりも早く非活性化することで、P D部1から読み出した蓄積信号レベルが早く安定化する。これにより、安定した信号検出が可能になる。40

#### 【0033】

続いて、選択行のドレイン電圧信号V D D C E Lを「L o w」レベルにして、リセット信号R E S E Tを活性化にすると、F D部2の電位は、ドレイン電圧信号V D D C E Lの「L o w」レベル（この場合G N D）になり、画素アンプ5は動作しなくなる。以降、垂直ライン走査回路3 6によって、再び該選択行のドレイン電圧信号V D D C E Lと読み出し信号R E A Dが活性化されるまで、該画素アンプ5は動作しないため、非選択状態となる。

#### 【0034】

すなわち、ドレイン電圧信号V D D C E L、読み出し信号R E A D及びリセット信号R E S E Tのタイミングによって、3つのトランジスタ3、4、5だけで、光電変換セルの蓄50

積信号読み出し、蓄積信号リセット、および垂直走査が行えることになり、従来では必要であった行選択トランジスタが不要になるとともに、リセット信号 R E S E T が印加されるリセット線 9 を遮光層と兼用できるため、光電変換セル内の P D 部 1 のサイズが大きくされ、セルサイズの微細化に有利になる。

#### 【0035】

##### (第3の実施形態)

次に、本発明の第3の実施形態について、図5および図6を参照して説明する。

#### 【0036】

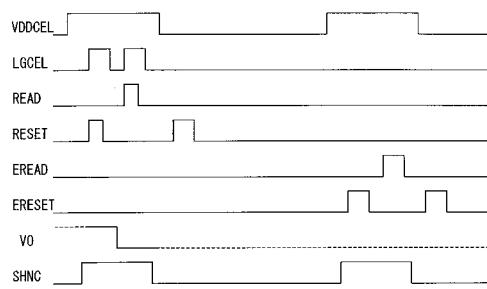

図5は、本発明の第3の実施形態に係るMOS型イメージセンサの全体回路構成図であり、図6は、その駆動方法を示す動作タイミング図である。 10

#### 【0037】

図5に示す本実施形態が第1および第2の実施形態と異なる点は、図2の構成に加えて、電子シャッター走査回路37を設けた点にあり、電子シャッター走査回路37から、FD部2の電位をドレイン電圧信号VDDCELの電位に初期化するために、電子シャッターワンチリセット信号ERESTが、またPD部1からFD部2への蓄積信号読み出し用に、電子シャッター時読み出し信号EREADが出力される。

#### 【0038】

図7に示す動作タイミングは、図4の動作タイミングに電子シャッター動作を組み込んだ例を示し、ロードゲート信号LGECLのタイミングに特徴を持たせている。すなわち、蓄積信号を検出する場合は、ロードゲート信号LGECLとしてパルス信号あるいは所定の一定電圧をロードトランジスタ6のゲートに印加して画素アンプ5を動作させ、蓄積信号を出力せずに蓄積信号の初期化のみを行う場合は、ロードゲート信号LGECLをGND状態にして、画素アンプ5を動作させないようにしている。この初期化のみを行う動作により、電子シャッター動作を実現するものである。 20

#### 【0039】

##### 【発明の効果】

以上説明したように、本発明によれば、FDA方式であるにもかかわらず、1つの光電変換セルを3つのトランジスタだけで構成することができ、開口率の向上およびセルサイズの微細化を実現することが可能となる。

##### 【図面の簡単な説明】

##### 【図1】 光電変換セルの回路構成図

【図2】 本発明の第1および第2の実施形態に係るMOS型イメージセンサの全体回路構成図

【図3】 本発明の第1の実施形態に係るMOS型イメージセンサの駆動方法を示す動作タイミング図

【図4】 本発明の第2の実施形態に係るMOS型イメージセンサの駆動方法を示す動作タイミング図

##### 【図5】 本発明の第3の実施形態に係るMOS型イメージセンサの全体回路構成図

##### 【図6】 図5のMOS型イメージセンサの駆動方法を示す動作タイミング図

##### 【符号の説明】

- 1 フォトダイオード部(PD部)、

- 2 フローティングディフュージョン部(FD部)

- 3 読出しトランジスタ

- 4 リセットトランジスタ

- 5 画素アンプ

- 6 ロードトランジスタ

- 7 ドレイン線

- 8 読み出しパルス線

- 9 リセットパルス線

- 10 出力信号線

30

40

50

- 1 1 ロードゲート線

1 2 ソース線

3 1 タイミング発生回路

3 2 ノイズキャンセル回路

3 3 水平ライン走査回路

3 4 出力アンプ

3 5 マルチプレクサ

3 6 垂直ライン走査回路

3 7 電子シャッター走査回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開平08-293591(JP,A)

特開平10-093066(JP,A)

特開平09-051480(JP,A)

特開平11-177076(JP,A)

特開2001-332714(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/335

H01L 27/146