(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6176826号

(P6176826)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

H04L 25/02 (2006.01)

H03K 19/0944 (2006.01)

F 1

H04L 25/02

H03K 19/0944

H04L 25/02R

V

請求項の数 4 (全 15 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2013-39970 (P2013-39970)    |

| (22) 出願日     | 平成25年2月28日 (2013.2.28)        |

| (65) 公開番号    | 特開2013-214957 (P2013-214957A) |

| (43) 公開日     | 平成25年10月17日 (2013.10.17)      |

| 審査請求日        | 平成28年2月26日 (2016.2.26)        |

| (31) 優先権主張番号 | 13/435,981                    |

| (32) 優先日     | 平成24年3月30日 (2012.3.30)        |

| (33) 優先権主張国  | 米国(US)                        |

|           |                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>エヌエックスピー ユーエスエイ インコ<br>ーポレイテッド<br>N X P U S A, I n c.<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                                            |

| (72) 発明者  | ヘクター サンチェス<br>アメリカ合衆国 78613 テキサス州<br>セダー パーク ベント ボウ コーブ<br>2010                                                                  |

審査官 阿部 弘

最終頁に続く

(54) 【発明の名称】起動回路を有する完全相補型自己バイアス差動受信機

## (57) 【特許請求の範囲】

## 【請求項 1】

起動回路に接続された、正ドライバ部分および負ドライバ部分であって、前記正ドライバ部分および負ドライバ部分のそれぞれに正入力信号および負入力信号を入力し、かつ前記正ドライバ部分および負ドライバ部分から出力信号を出力する、前記正ドライバ部分および前記負ドライバ部分を含んでなり、および、前記起動回路には第1の導電型のテール電流トランジスタおよび第2の導電型のテール電流トランジスタが結合し、前記第1の導電型のテール電流トランジスタに正電圧が結合し、前記第2の導電型のテール電流トランジスタに負電圧が結合している、差動受信機の動作方法において、

前記第1の導電型のテール電流トランジスタを、前記第2の導電型のテール電流トランジスタが与える仮想負電圧によって変調する工程であって、前記第1の導電型のテール電流トランジスタは前記正電圧と仮想正電圧との間に置かれる、第1の導電型のテール電流トランジスタを変調する工程と、

前記第2の導電型のテール電流トランジスタを、前記第1の導電型のテール電流トランジスタが与える仮想正電圧によって変調する工程であって、前記第2の導電型の前記テール電流トランジスタは前記仮想負電圧と前記負電圧との間に置かれる、第2の導電型のテール電流トランジスタを変調する工程とを備え、

前記第1および第2の導電型のテール電流トランジスタを変調する結果、前記差動受信機を製造する時に生じる欠陥の結果生じる欠陥電流を前記起動回路が補償する、方法。

## 【請求項 2】

10

20

第1のイネーブル入力において第1のイネーブル信号を受信する工程であって、前記第1のイネーブル入力は第1のテール電流源イネーブルトランジスタに結合され、前記第1のテール電流源イネーブルトランジスタは、テール電流の総量の第1の部分が流れることを可能にし、前記第1のテール電流源イネーブルトランジスタは、前記第1の導電型の前記テール電流トランジスタおよび前記第2の導電型の前記テール電流トランジスタから成る群から選択される要素に結合される、第1のイネーブル入力において第1のイネーブル信号を受信する工程と、

第2のイネーブル入力において第2のイネーブル信号を受信する工程であって、前記第2のイネーブル入力は第2のテール電流源イネーブルトランジスタに結合され、前記第2のテール電流源イネーブルトランジスタは、前記テール電流の総量の第2の部分が流れることを可能にする、第2のイネーブル入力において第2のイネーブル信号を受信する工程とをさらに備える、請求項1に記載の方法。10

#### 【請求項3】

前記正ドライバ部分は前記仮想正電圧に結合し、および前記負ドライバ部分は前記仮想負電圧に結合する、請求項1に記載の方法。

#### 【請求項4】

請求項1に記載の差動受信機の動作方法において、

前記第1の導電型のテール電流トランジスタのソース、ドレイン、ゲート、およびボディから成る群から選択される第1の端子を前記仮想正電圧に結合する工程と、20

前記第1の導電型のテール電流トランジスタの前記ソース、前記ドレイン、前記ゲート、および前記ボディから成る群から選択される第2の端子を前記仮想負電圧に結合する工程と、

前記第1の導電型のテール電流トランジスタのソース、前記ドレイン、前記ゲート、および前記ボディから成る群から選択される第3の端子を正電圧に結合する工程と、

前記第1の導電型のテール電流トランジスタの前記ソース、前記ドレイン、前記ゲート、前記および前記ボディから成る群から選択される第4の端子を負電圧に結合する工程と、20

正テール電流源の基準を、負テール電流源に関連付けられる仮想負電圧に置く工程と、

前記負テール電流源の基準を、前記正テール電流源に関連付けられる仮想正電圧に置く工程とを備える、方法。30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、一般的には差動受信機に関し、より詳細には、相補型自己バイアス差動増幅器に関する。

##### 【背景技術】

##### 【0002】

電子デバイスがより洗練された物になり、消費者が機能の向上、デバイスサイズの小型化、およびバッテリ寿命の延長を期待している中で、機能を犠牲にすることなくデバイスサイズを低減するとともに電力消費を低減する技法が利用されている。1つのこのような技法は、電子デバイスを低電圧で動作させることを含む。しかしながら、低電圧動作は、所望の機能を達成するまでの障害をもたらす可能性がある。40

##### 【0003】

低電圧動作をするための1つの技法は、差動シグナリングを採用することであって、それによって、他のデバイスから差動モード信号を受信するために差動受信機が使用される。いくつかの差動受信機は自己バイアス差動増幅器を使用する。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【特許文献1】米国特許第4937476号明細書50

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、動作電圧が低減されると従来の自己バイアス増幅器には速度が遅くなるという問題が生じ、また大きな回路面積を必要とする可能性もある。たとえば、いくつかの自己バイアス増幅器トポロジは、自己バイアス電圧を与えるために専用に用いられるべきトランジスタのスタックを必要とし、そのような自己バイアストランジスタスタックは、大きな面積を必要とし、これは電子デバイスの小型化の追求を妨げる。その上、出力振幅が限られていること、ならびに、プロセス、電圧、および温度(PVT)における変動に対する許容性がないことが、さらに、一般的な自己バイアス増幅器トポロジを使用する妨げとなる。たとえば、低い供給電圧差(すなわち、供給電圧において負電圧と相対して正電圧(Vdd)が低い)では、一般的な自己バイアス増幅器においては、テール電流源に、テール電流源トランジスタのしきい値電圧(Vth)と比較して相対的に低いバイアスがもたらされ、これによって回路の適切な動作が妨げられる。10

**【課題を解決するための手段】****【0006】**

自己バイアス増幅器に対するバイアス電圧を変化させて、改善されたPVT許容性を提供する。たとえば、第1の導電型のトランジスタが強く、第2の導電型のトランジスタが弱い場合、負テール電流源に印加される仮想正バイアス電圧(たとえば、BIASN)によって電位を上げ、第2の導電型のトランジスタの弱さを補償する。そのような補償によって、増幅器がより広い範囲の入力信号に対して効率的に動作することが可能になる。20

**【図面の簡単な説明】****【0007】**

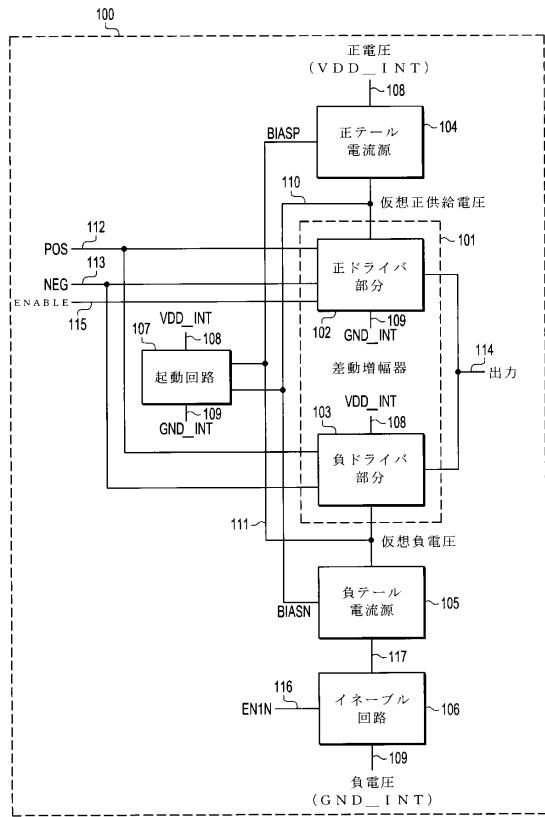

【図1】少なくとも1つの実施形態による相補型自己バイアス増幅器を示すブロック図。

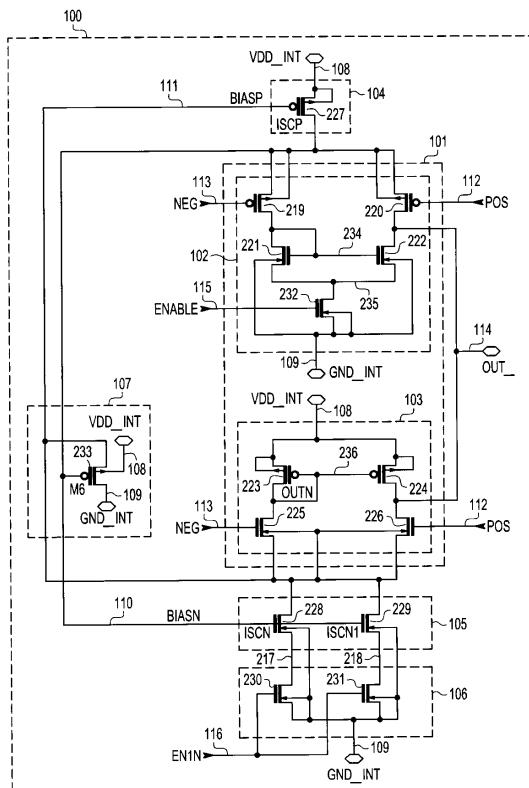

【図2】少なくとも1つの実施形態による相補型自己バイアス増幅器を示す概略図。

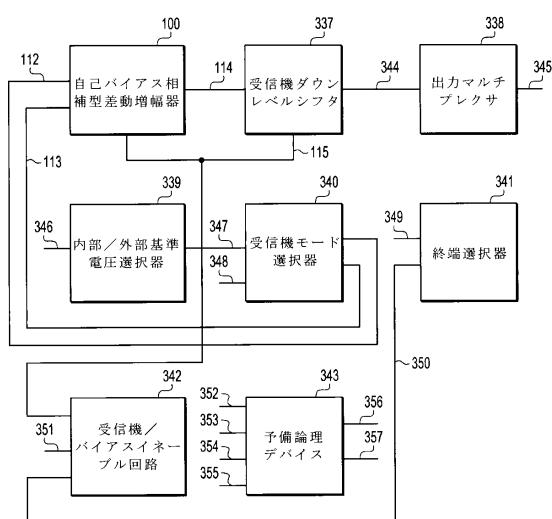

【図3】少なくとも1つの実施形態による相補型自己バイアス増幅器を利用するシステムのブロック図。

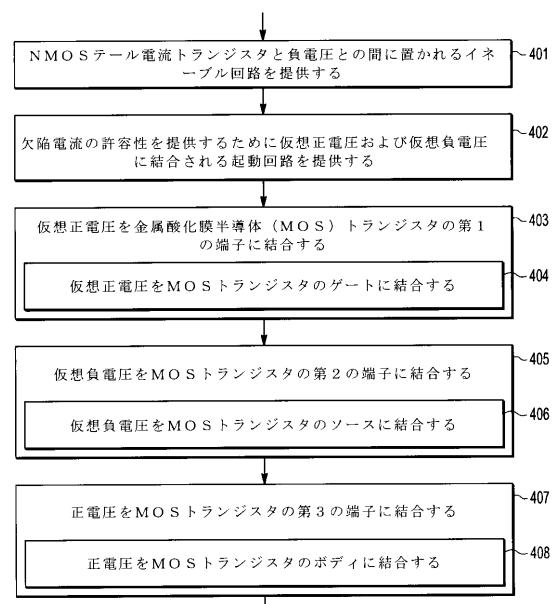

【図4】少なくとも1つの実施形態による方法を示すブロック図。

【図5】少なくとも1つの実施形態による方法を示すブロック図。

【図6】少なくとも1つの実施形態による方法を示すブロック図。30

**【発明を実施するための形態】****【0008】**

本開示は、添付の図面を参照することによってよりよく理解されることができ、その特徴が当業者に明らかとなる。

異なる図面において同じ参照符号が使用されている場合、これは、類似または同一の項目であることを示す。

**【0009】**

図1は、少なくとも1つの実施形態による相補型自己バイアス増幅器100を示すブロック図である。自己バイアス相補型差動増幅器100は、ドライバ部分101と、正テール電流源104と、負テール電流源105と、イネーブル回路106と、起動回路107とを備える。ドライバ部分101は、正ドライバ部分102と負ドライバ部分103とを備える。正電圧(たとえば、VDD\_INT)108が正テール電流源104に接続される。正テール電流源104仮想正電圧(たとえば、BIASN)110を提供し、これは正テール電流源104から正ドライバ部分102、負テール電流源105、および起動回路107へ接続される。40

**【0010】**

負電圧(たとえば、GND\_INT)109はイネーブル回路106へ接続される。イネーブル回路106は、イネーブル入力(たとえば、EN1N)116のイネーブル状態に応じて差動増幅器(たとえば、ドライバ部分101)の動作をイネーブルする。イネーブル回路106は、ノード117を介して負テール電流源105に結合される。負テール

電流源 105 は仮想負電圧（たとえば、BIASP）111 を提供し、これは負テール電流源 105 から負ドライバ部分 103、正テール電流源 104、および起動回路 107 へ結合される。

#### 【0011】

正差動信号入力 112 が正ドライバ部分 102 および負ドライバ部分 103 へ提供される。負差動信号入力 113 が正ドライバ部分 102 および負ドライバ部分 103 へ提供される。イネーブル信号（たとえば、ENABLE）115 が正ドライバ部分 102 へ提供される。少なくとも 1 つの実施形態によれば、イネーブル信号（たとえば、ENABLE）115（またはその逆数 / 補数）がイネーブル入力（たとえば、EN1N）116 に印加されてもよい。正ドライバ部分 102 および負ドライバ部分 103 は出力 114 に接続され、そこには出力信号も提供される。正電圧（たとえば、VDD\_INT）108 が起動回路 107 および負ドライバ部分 103 に提供される。負電圧（たとえば、GND\_INT）109 が起動回路 107 および正ドライバ部分 102 に提供される。10

#### 【0012】

仮想正電圧 110 が負テール電流源 105 をバイアスする。仮想負電圧 111 が正テール電流源 104 をバイアスする。起動回路 107 は、半導体製造プロセスから生じる欠陥の結果生じる欠陥電流を補償し、差動増幅器に電力が印加されたときの差動増幅器の信頼性のある動作を保証する。

#### 【0013】

少なくとも 1 つの実施形態によれば、相補型イネーブル回路が、イネーブル回路 106 が負電圧 109 と負テール電流源 105との間に据えられたのと同様にして、正電圧 108 と正テール電流源 104との間に置かれることができる。正電圧（たとえば、VDD\_INT）108 が相補型イネーブル回路に接続される。相補型イネーブル回路は、相補的イネーブル入力（たとえば、EN1P）の相補的イネーブル状態に応じて差動増幅器（たとえば、ドライバ部分 101）の動作をイネーブルする。相補型イネーブル回路は相補型イネーブル回路ノードを介して正テール電流源 104 に結合される。20

#### 【0014】

少なくとも 1 つの実施形態によれば、イネーブル入力（たとえば、EN1N）116 に印加されるものと同じ信号（またはその逆数 / 補数）が相補的イネーブル入力（たとえば、EN1P）に印加されることができる。少なくとも 1 つの実施形態によれば、イネーブル信号（たとえば、ENABLE）115（またはその逆数 / 補数）が相補的イネーブル入力（たとえば、EN1P）に印加されてもよい。30

#### 【0015】

少なくとも 1 つの実施形態によれば、供給電圧システムは負電圧 109 を正電圧 108 に橋渡しする。適切な動作を確実にするために、仮想正電圧（BIASN）110 は仮想負電圧（BIASP）111 よりも正の電圧であるべきであり、事実、回路が適切に作動しているとき、仮想正電圧（BIASN）110 は正電圧 108 に近くなり、仮想負電圧（BIASP）111 は負電圧 109 に近くなる。しかしながら、起動回路 107 がないと、理論的には、仮想正電圧（BIASN）110 および仮想負電圧（BIASP）111 が、回路内にはそれらの適切な状態を積極的に保証するものが他に何もないため、相対的に逆の極性になり得るという可能性がある。電源投入されると、正電圧 108 が負電圧 109 と同じ電位において（たとえば、ゼロボルト（0V）において）開始するものと推定される。正電圧 108 および / または負電圧 109 がその指定された電圧（またはそれらの指定された電圧）に傾き始めると、起動回路 107 内の能動デバイス（たとえば、起動回路 107 内の PMOSFET のゲート）が、事実上、（たとえば、ゼロボルト（0V）初期電位の影響によって）オンになる。これによって、仮想負電圧（BIASP）111 のあらゆる変化が散逸させられて負電圧 109 になる。これによって、PMOS テール電流デバイスが電荷の仮想正電圧（BIASN）110 へのポンピングを開始するようになる（たとえば、公称ゼロボルト（0V）において開始し、この時点で上昇し始める）。このフィードバック機構によって、仮想負電圧（BIASP）111 が瞬間的に低くさせ4050

られて仮想正電圧 (B I A S N) 110 が上昇することが可能になり、その後、PMOS テール電流デバイスの助けによってNMOS テール電流トランジスタが係合されて仮想正電圧 (B I A S N) 110 をその意図される動作点に向かってプルするため、適切な電源投入が保証される。仮想正電圧 (B I A S N) 110 が上昇して仮想負電圧 (B I A S P) が下降すると、起動回路 107 (たとえば、起動回路 107 内のPMOS 起動トランジスタ) が、そのゲートの電位が上昇し、一方でそのソースの電位が下降するため、切れる。

#### 【0016】

仮想正電圧 (B I A S N) 110 および仮想負電圧 (B I A S P) 111 に対する実効的な電荷の注入を引き起こす、半導体デバイスの欠陥が存在し得る可能性がある。起動トランジスタ (たとえば、起動回路 107 内のPMOSFET) は、電源投入時に、たとえば、仮想正電圧 (B I A S N) 110 および仮想負電圧 (B I A S P) 111 の両方において印加される、最大で三マイクロアンペア ( $3 \mu A$ ) の欠陥に「打ち勝つ」ことができるように、相当量の欠陥電流をハンドリングするようなサイズにされる。10

#### 【0017】

図2は、少なくとも1つの実施形態による、図1の相補型自己バイアス増幅器の具体的な実施形態を示す概略図である。相補型自己バイアス増幅器 100 は、正テール電流源 104 と、差動増幅器 101 と、負テール電流源 105 と、イネーブル回路 106 と、起動回路 107 とを備える。正テール電流源 104 は、正型 (p型) チャネル金属酸化膜半導体 (PMOS) 電界効果トランジスタ (FET) 227 を備える。正テール電流源 104 は、起動回路 107 によって加減される、PMOSFET 227 のゲートに印加される仮想負電圧によって制御される電流源として機能する。20

#### 【0018】

差動増幅器 101 は、正ドライバ部分 102 と負ドライバ部分 103 とを備える。正ドライバ部分 102 は、PMOSFET 219 と、PMOSFET 220 と、負型 (n型) チャネル金属酸化膜半導体 (NMOS) 電界効果トランジスタ (FET) 221 と、NMOSFET 222 と、NMOSFET 232 を備える。負ドライバ部分 103 は、PMOSFET 223 と、PMOSFET 224 と、NMOSFET 225 と、NMOSFET 226 を備える。正ドライバ部分 102 は、正入力信号 112 および負入力信号 113 を受信し、出力 114 を提供する。負ドライバ部分 103 は、正入力信号 112 および負入力信号 113 を受信し、出力 114 を提供する。正ドライバ部分 102 および負ドライバ部分 103 は完全に相補的である (すなわち、各PMOSFET は対応するNMOSFET とプッシュプル式に動作する)。正ドライバ部分 102 および負ドライバ部分 103 の協調動作が完全に相補的であることによって、大きな入力電圧範囲がもたらされ、正入力信号および負入力信号の電圧の大きな振幅に対してさえ、差動増幅器が適切に作動する。架橋バイアス技法によって、入力信号電圧範囲および出力電圧範囲が改善され、さらに拡大される。30

#### 【0019】

正ドライバ部分 102 において、PMOSFET 219 および 220 はそれぞれ、負入力信号 113 および正入力信号 112 を受信する。NMOSFET 221 および 222 は、出力 114 の駆動を支援するか、または支援から外れるために正ドライバ部分 102 の左側から正ドライバ部分 102 の右側に電流が誘導されると相補的な電流をそれぞれの側に反映するカレントミラーとして構成される、負荷デバイスを形成する。正テール電流源 104 は PMOSFET 219 および PMOSFET 220 を通じて流れる最大電流を設定する。PMOSFET 219 および PMOSFET 220 のゲート - ソース電圧 ( $V_{gs}$ ) によって制限される。NMOSFET 232 は、イネーブル信号 (ENABLE) 115 に基づいて正ドライバ部分 102 を選択的にイネーブルおよびディセーブルすることを可能にする。40

#### 【0020】

負ドライバ部分 103 において、NMOSFET 225 および 226 はそれぞれ、それ

50

らのゲートにおいて負入力信号 113 および正入力信号 112 を受信する。NMOSFET 223 および 224 は、出力 114 の駆動を支援するか、または支援から外れるために負ドライバ部分 103 の左側から負ドライバ部分 103 の右側に電流が誘導されると相補的な電流をそれぞれの側に反映するカレントミラーとして構成される、負荷デバイスを形成する。負テール電流源 105 は、NMOSFET 225 および NMOSFET 226 を通じて流れる最大電流を設定する。NMOSFET 225 および NMOSFET 226 を通る電流は、主に、NMOSFET 225 および NMOSFET 226 のゲート - ソース電圧 (V<sub>gs</sub>) によって制限される。

#### 【0021】

負テール電流源 105 は、NMOSFET 228 および NMOSFET 229 を備える。<sup>10</sup> イネーブル回路 106 は、NMOSFET 230 および NMOSFET 231 を備える。起動回路 107 は PMOSFET 233 を備える。負テール電流源 105 は、起動回路 107 によって加減される、NMOSFET 228 および 229 のゲートに印加される仮想正電圧によって制御される電流源として機能する。NMOSFET 228 および 229 は、NMOSFET 228 および 229、ならびにそれゆえ負ドライバ部分 103 を通じて流れる電流によって並行して動作するように構成され、これはイネーブル信号 (EN1N) 116 の NMOSFET 230 および 231 のゲート端子への印加によって選択的にイネーブルおよびディセーブルされる。NMOSFET 230 は、NMOSFET 228 を通じて流れる電流をイネーブルおよびディセーブルし、NMOSFET 231 は、NMOSFET 229 を通じて流れる電流をイネーブルおよびディセーブルする。少なくとも<sup>20</sup> 1つの実施形態によれば、別個の左イネーブル信号 (EN1NL) が NMOSFET 230 のゲート端子に印加され、別個の右イネーブル信号 (EN1NR) が NMOSFET 231 のゲート端子に印加されてそれぞれ、NMOSFET 228 および 229 を通る選択可能な量の電流がもたらされる。したがって、負テール電流源 105 はプログラム可能負テール電流源として実装することができる。

#### 【0022】

正電圧 (たとえば、VDD\_INT) 108 が、PMOSFET 227 のソース端子およびボディ端子に結合される。PMOSFET 227 のドレン端子が、仮想正電圧ノード (たとえば、BIASN) 110 に結合される。PMOSFET 227 のゲート端子が、仮想負電圧ノード (たとえば、BIAFP) 111 に結合される。<sup>30</sup>

#### 【0023】

少なくとも 1 つの実施形態によれば、正テール電流源 104 は、負テール電流源 105 のものと相補的なトランジスタ構成を用いて実装されることができる。また、正テール電流源 104 は、たとえば、それぞれ、相補的左イネーブル PMOSFET に結合される相補的左バイアス交差結合 PMOSFET および相補的右イネーブル PMOSFET に結合される相補的右バイアス交差結合 PMOSFET を通る選択可能な量の電流を提供するために、別個の相補的左イネーブル信号 (EN1PL) を相補的左イネーブル PMOSFET のゲート端子に印加し、別個の相補的右イネーブル信号 (EN1PR) を相補的右イネーブル PMOSFET のゲート端子に印加することによって、プログラム可能正テール電流源として実装することができる。<sup>40</sup>

#### 【0024】

仮想正電圧ノード 110 は、PMOSFET 219 のソース端子およびボディ端子、PMOSFET 220 のソース端子およびボディ端子、PMOSFET 233 のゲート端子、NMOSFET 228 のゲート端子、および NMOSFET 229 のゲート端子にも結合される。負正信号入力 113 は PMOSFET 219 のゲート端子に結合される。正信号入力 112 は PMOSFET 220 のゲート端子に結合される。PMOSFET 219 のドレン端子はノード 234 に結合され、当該ノードは NMOSFET 221 のドレン端子、NMOSFET 221 のゲート端子、および NMOSFET 222 のゲート端子に結合される。PMOSFET 220 のドレン端子は NMOSFET 222 のドレン端子および出力端子 114 に結合される。NMOSFET 221 のボディ端子および NM<sup>50</sup>

O S F E T 2 2 2 のボディ端子は負電圧 1 0 9 に結合される。N M O S F E T 2 2 1 のソース端子およびN M O S F E T 2 2 2 のソース端子はノード 2 3 5 に結合され、当該ノードはN M O S F E T 2 3 2 のドレイン端子に結合される。イネーブル入力 1 1 5 がN M O S F E T 2 3 2 のゲート端子に結合される。N M O S F E T 2 3 2 のソース端子およびボディ端子は負電圧 1 0 9 に結合される。

#### 【0025】

正電圧 1 0 8 が、P M O S F E T 2 2 3 のソース端子およびボディ端子ならびにP M O S F E T 2 2 4 のソース端子およびボディ端子に結合される。P M O S F E T 2 2 3 のゲート端子およびドレイン端子はノード 2 3 6 に結合され、当該ノードはP M O S F E T T 2 2 4 のゲート端子、N M O S F E T 2 2 5 ドレイン端子に結合される。P M O S F E T 2 2 4 のドレイン端子はN M O S F E T 2 2 6 のドレイン端子および出力端子 1 1 4 に結合される。負信号入力 1 1 3 はN M O S F E T 2 2 5 のゲート端子に結合される。正信号入力 1 1 2 はP M O S F E T 2 2 6 のゲート端子に結合される。N M O S F E T 2 2 5 のソース端子およびゲート端子ならびにN M O S F E T 2 2 6 のソース端子およびゲート端子が仮想負電圧ノード 1 1 1 に結合され、当該ノードは、N M O S F E T 2 2 8 のドレイン端子、N M O S F E T 2 2 9 のドレイン端子、P M O S F E T 2 3 3 のソース端子、およびP M O S F E T 2 2 7 のゲート端子に結合される。

#### 【0026】

N M O S F E T 2 2 8 のソース端子はN M O S F E T 2 3 0 のドレイン端子に結合される。N M O S F E T 2 2 9 のソース端子はN M O S F E T 2 3 1 のドレイン端子に結合される。イネーブル入力（たとえば、E N 1 N）が、N M O S F E T 2 3 0 のゲート端子およびN M O S F E T 2 3 1 のゲート端子に結合される。N M O S F E T 2 3 0 のソース端子およびボディ端子ならびにN M O S F E T 2 3 1 のソース端子およびボディ端子は負電圧 1 0 9 に結合される。

#### 【0027】

起動回路 1 0 7 はP M O S F E T 2 3 3 を備えるものとして示されているが、少なくとも 1 つの実施形態によれば、起動回路 1 0 7 はN M O S F E T を備えてもよいことは理解されたい。一例として、N M O S F E T を備える起動回路は、供給電圧 1 0 8 が供給電圧 1 0 9 よりも負の電圧において動作する変更された回路構成において有用であり得る。たとえば、起動回路 1 0 7 のN M O S F E T のソース端子は相対的に負のバージョンの供給電圧 1 0 8 に結合されてもよく、それによって、相対的に負の供給電圧 1 0 8 が電源を切られると、起動回路 1 0 7 のN M O S F E T が電荷を注入する。

#### 【0028】

図 3 は、少なくとも 1 つの実施形態による相補型自己バイアス増幅器を利用するシステムのブロック図である。システムは、自己バイアス相補型差動増幅器 1 0 0 と、受信機ダウンレベルシフタ 3 3 7 と、出力マルチプレクサ 3 3 8 と、内部 / 外部基準電圧選択器 3 3 9 と、受信機モード選択器 3 4 0 と、終端選択器 3 4 1 と、受信機 / バイアスイネーブル回路 3 4 2 と、予備論理デバイス 3 4 3 とを備える。正信号入力 1 1 2 および負信号入力 1 1 3 が自己バイアス相補型差動増幅器 1 0 0 および受信機モード選択器 3 4 0 に結合される。受信機 / バイアスイネーブル回路 3 4 2 からのイネーブル信号 1 1 5 が自己バイアス相補型差動増幅器 1 0 0 および受信機ダウンレベルシフタ 3 3 7 に結合される。自己バイアス相補型差動増幅器 1 0 0 からの出力 1 1 4 が受信機ダウンレベルシフタ 3 3 7 に結合される。受信機ダウンレベルシフタ 3 3 7 からの出力 3 4 4 が出力マルチプレクサ 3 3 8 に結合される。出力マルチプレクサ 3 3 8 が出力 3 4 5 を提供する。

#### 【0029】

基準電圧選択信号 3 4 6 が内部 / 外部基準電圧選択器 3 3 9 に結合される。内部 / 外部基準電圧選択器 3 3 9 が受信機モード選択器 3 4 0 に対する出力 3 4 7 を提供する。入力 3 4 8 が受信機モード選択器 3 4 0 に結合される。入力 3 4 9 が終端選択器 3 4 1 に結合される。終端選択器 3 4 1 はノード 3 5 0 に結合され、当該ノードは受信機 / バイアスイネーブル回路 3 4 2 に結合される。入力 3 5 1 が受信機 / バイアスイネーブル回路 3 4 2

に結合される。入力 352、353、および 354 が予備論理デバイス 343 に結合され、予備論理デバイス 343 からの出力 356 を提供するのに使用されることがある。入力 355 が予備論理デバイス 343 に結合され、予備論理デバイス 343 からの出力 357 を提供するのに使用されることがある。

#### 【0030】

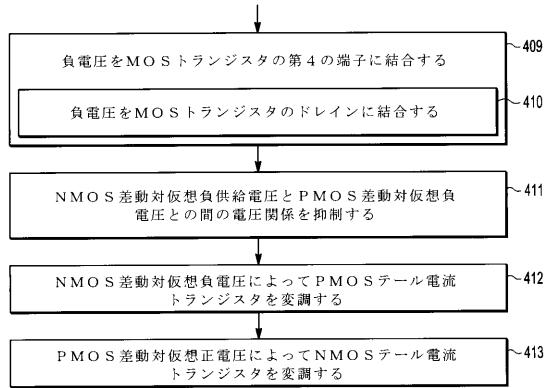

図 4, 5 は、少なくとも 1 つの実施形態による方法を示すブロック図である。方法はステップ 401 において開始する。ステップ 401 は、NMOS テール電流トランジスタと負電圧との間に置かれるイネーブル回路を提供することを含む。ステップ 401 から、方法はステップ 402 に続く。ステップ 402 は、欠陥電流の許容性を提供するために仮想正電圧および仮想負電圧に結合される起動回路を提供することを含む。ステップ 402 から、方法はステップ 403 に続く。少なくとも 1 つの実施形態によれば、そのような起動回路を提供することは、以下のステップを実行する起動回路を提供することを含むことができる、すなわち、電源投入時に、正電圧 108 および / または負電圧 109 をその指定された電圧（またはそれらの指定された電圧）まで傾けることが始まる。正電圧 108 は、負電圧 109 と同じ電位において（たとえば、ゼロボルト（0V））において始まると推測され、起動回路 107 内の能動デバイス（たとえば、起動回路 107 内の PMOSFET のゲート）が、（たとえば、ゼロボルト（0V）初期電位の影響によって）事実上オンになる。したがって、仮想負電圧（BIASP）111 のあらゆる変化の、負電圧 109 への散逸が起こる。次いで、PMOS テール電流デバイスが電荷の仮想正電圧（BIASN）110 へのポンピングを開始するようになる（たとえば、公称ゼロボルト（0V）において開始し、この時点で上昇し始める）。仮想負電圧（BIASP）111 が瞬間に低くさせられて仮想正電圧（BIASN）110 が上昇することが可能になり、その後、PMOS テール電流デバイスの助けによって NMOS テール電流トランジスタが係合されて仮想正電圧（BIASN）110 がその意図される動作点に向かってプルされる。仮想正電圧（BIASN）110 が上昇して仮想負電圧（BIASP）が下降すると、起動回路 107（たとえば、起動回路 107 内の PMOS 起動トランジスタ）が、そのゲートの電位が上昇し、一方でそのソースの電位が下降するため、切れる。相当量の欠陥電流に対応するために、起動トランジスタ（たとえば、起動回路 107 内の PMOSFET）は、電源投入時に、たとえば、仮想正電圧（BIASN）110 および仮想負電圧（BIASP）111 の両方において印加される、最大で三マイクロアンペア（ $3 \mu A$ ）の欠陥に「打ち勝つ」ことができるよう、十分な電流を通すようなサイズにされる。ステップ 403 は、仮想正電圧を金属酸化膜半導体（MOS）トランジスタの第 1 の端子に結合することを含む。少なくとも 1 つの実施形態によれば、ステップ 403 はステップ 404 をさらに含む。ステップ 404 は、仮想正電圧を MOS トランジスタのゲートに結合することを含む。ステップ 403 から、方法はステップ 405 に続く。ステップ 405 は、仮想負電圧を MOS トランジスタの第 2 の端子に結合することを含む。少なくとも 1 つの実施形態によれば、ステップ 405 はステップ 406 をさらに含む。ステップ 406 は、仮想負電圧を MOS トランジスタのソースに結合することを含む。ステップ 405 から、方法はステップ 407 に続く。ステップ 407 は、正電圧を MOS トランジスタの第 3 の端子に結合することを含む。少なくとも 1 つの実施形態によれば、ステップ 407 はステップ 408 をさらに含む。ステップ 408 は、正電圧を MOS トランジスタのボディに結合することを含む。

#### 【0031】

ステップ 407 から、方法はステップ 409 に続く。ステップ 409 は、負電圧を MOS トランジスタの第 4 の端子に結合することを含む。少なくとも 1 つの実施形態によれば、ステップ 409 はステップ 410 をさらに含む。ステップ 410 は、負電圧を MOS トランジスタのドレインに結合することを含む。ステップ 409 から、方法はステップ 411 に続く。ステップ 411 は、NMOS 差動対仮想負電圧と PMOS 差動対仮想負電圧との間の電圧関係を抑制することを含む。ステップ 411 から、方法はステップ 412 に続く。ステップ 412 は、NMOS 差動対仮想負電圧によって PMOS テール電流トランジ

10

20

30

40

50

スタを変調することを含む。ステップ412から、方法はステップ413に続く。ステップ413は、PMOS差動対仮想正電圧によってNMOSテール電流トランジスタを変調することを含む。

#### 【0032】

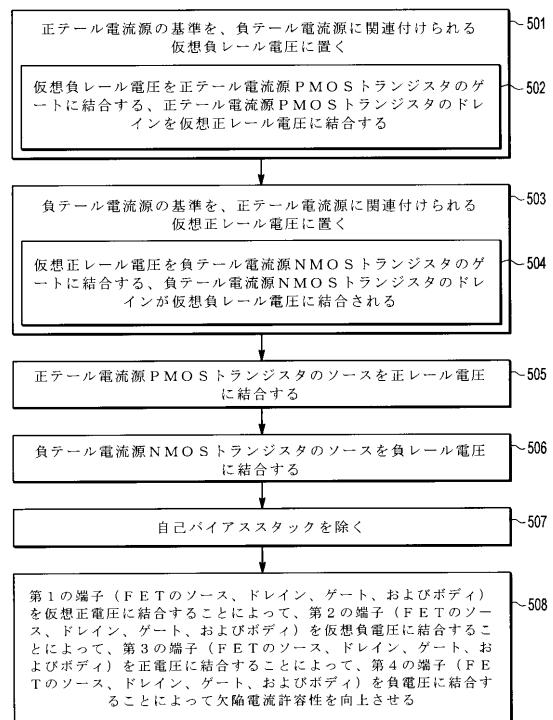

図6は、少なくとも1つの実施形態による方法を示すブロック図である。方法はステップ501において開始する。ステップ501は、正テール電流源の基準を、負テール電流源に関連付けられる仮想負レール電圧に置くことを含む。少なくとも1つの実施形態によれば、ステップ501はステップ502をさらに含む。ステップ502は、仮想負レール電圧を正テール電流源PMOSトランジスタのゲートに結合することを含み、正テール電流源PMOSトランジスタのドレインが仮想正レール電圧に結合される。ステップ501から、方法はステップ503に続く。ステップ503は、負テール電流源の基準を、正テール電流源に関連付けられる仮想正レール電圧に置くことを含む。少なくとも1つの実施形態によれば、ステップ503はステップ504を含む。ステップ504は、仮想正レール電圧を負テール電流源NMOSトランジスタのゲートに結合することを含み、負テール電流源NMOSトランジスタのドレインが仮想負レール電圧に結合される。

10

#### 【0033】

ステップ503から、方法はステップ505に続く。ステップ505は、正テール電流源PMOSトランジスタのソースを正レール電圧に結合することを含む。ステップ505から、方法はステップ506に続く。ステップ506は、負テール電流源NMOSトランジスタのソースを負レール電圧に結合することを含む。ステップ506から、方法はステップ507に続く。ステップ507は、自己バイアススタックを除くことを含む。ただ1つのバイアス電圧を差動増幅器の複数の部分に提供するためにトランジスタの自己バイアススタックを除くことは、少なくとも1つの実施形態によれば、出力振幅を向上させる（たとえば、低供給電圧（すなわち、正電圧と負電圧との間の差が小さい）において動作する差動増幅器に関してさえもより大きな電圧範囲にわたって出力が変化することを可能にする）ために有用である可能性がある。そのようなトランジスタの自己バイアススタックを除くことは、少なくとも1つの実施形態によれば、差動増幅器の速度（すなわち、スルーレート／応答時間／切り替え時間）を向上させるためにも有用である可能性がある。ステップ507から、方法はステップ508に続く。ステップ508は、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第1の端子を仮想正電圧に結合することによって、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第2の端子を仮想負電圧に結合することによって、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第3の端子を正電圧に結合することによって、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第4の端子を負電圧に結合することによって、欠陥電流許容性を向上させることを含む。第1の端子、第2の端子、第3の端子、および第4の端子は相互に排他的である（たとえば、第1の端子がFETのゲート端子である場合、FETの第2の端子、第3の端子、および第4の端子のいずれもFETのゲート端子でなく、また、たとえば、第2の端子がFETのソース端子である場合、FETの第1の端子、第3の端子、および第4の端子のいずれもソース端子でなく、また、さらに、別の例として、第3の端子がFETのボディ端子である場合、FETの第1の端子、第2の端子、および第4の端子のいずれもボディ端子でなく、また、同様に別の例として、第4の端子がFETのドレイン端子である場合、FETの第1の端子、第2の端子、および第3の端子のいずれもドレイン端子でない）。換言すれば、第1の端子、第2の端子、第3の端子、および第4の端子は各々、FETのソース端子、ドレイン端子、ゲート端子、およびボディ端子の中で固有の端子であるが、さまざまな実施形態によれば、第1の端子、第2の端子、第3の端子、および第4の端子の、FETのソース端子、ドレイン端子、ゲート端子、およびボディ端子に対する関係は、実施形態ごとに変化してもよい。

20

#### 【0034】

少なくとも1つの実施形態が、差動入力信号を受信するものとして例示および記載され

40

50

ているが、少なくとも 1 つの実施形態はシングルエンド（すなわち、非差動）受信機として使用されてもよく、少なくとも 1 つの実施形態はレベルシフタとして使用されてもよいことは理解されたい。一例として、差動入力信号を受信するための実施形態は、シングルエンド受信機および / またはレベルシフタとして使用するのに適した少なくとも 1 つの実施形態を提供するために、2 つの差動入力のうちの 1 つを固定電圧に固定することによって、差動入力段のうちの一方の側を除くことによって、および / または、ノードの電圧を相殺することによって変更されてもよい。

【 0 0 3 5 】

少なくとも1つの実施形態によれば、差動受信機を改善するための方法が提供される。少なくとも1つの実施形態によれば、方法は、正型金属酸化膜半導体（PMOS）テール電流トランジスタを、負型金属酸化膜半導体（NMOS）差動対仮想負電圧によって変調することと、NMOSテール電流トランジスタを、PMOS差動対仮想正電圧によって変調することとを含む。少なくとも1つの実施形態によれば、PMOSテール電流トランジスタは正電圧と仮想正電圧との間に置かれ、NMOSテール電流トランジスタは仮想負電圧と負電圧との間に置かれる。

10

【 0 0 3 6 】

少なくとも 1 つの実施形態によれば、方法は、N MOS テール電流トランジスタと負電圧との間に置かれるイネーブル回路を提供することをさらに含む。少なくとも 1 つの実施形態によれば、方法は、欠陥電流の許容性を提供するために、仮想正電圧および仮想負電圧に結合される起動回路を提供することをさらに含む。

20

【 0 0 3 7 】

少なくとも1つの実施形態によれば、方法は、仮想正電圧を金属酸化膜半導体(MOS)トランジスタの第1の端子に結合することと、仮想負電圧をMOSトランジスタの第2の端子に結合することと、正電圧をMOSトランジスタの第3の端子に結合することと、負電圧をMOSトランジスタの第4の端子に結合することとをさらに含む。少なくとも1つの実施形態によれば、仮想正電圧をMOSトランジスタの第1の端子に結合することは、仮想正電圧をMOSトランジスタのゲートに結合することをさらに含み、仮想負電圧をMOSトランジスタの第2の端子に結合することは、仮想負電圧をMOSトランジスタのソースに結合することをさらに含み、正電圧をMOSトランジスタの第3の端子に結合することは、正電圧をMOSトランジスタのボディに結合することをさらに含み、負電圧をMOSトランジスタの第4の端子に結合することは、負電圧をMOSトランジスタのドレインに結合することをさらに含む。

30

[ 0 0 3 8 ]

少なくとも 1 つの実施形態によれば、欠陥電流の許容性を提供するために、仮想正電圧および仮想負電圧に結合される起動回路を提供することは、仮想正電圧を金属酸化膜半導体 (MOS) ランジスタの第 1 の端子に結合することをさらに含む。少なくとも 1 つの実施形態によれば、欠陥電流の許容性を提供するために、仮想正電圧および仮想負電圧に結合される起動回路を提供することは、仮想負電圧を MOS ランジスタの第 2 の端子に結合することをさらに含む。少なくとも 1 つの実施形態によれば、欠陥電流の許容性を提供するために、仮想正電圧および仮想負電圧に結合される起動回路を提供することは、正電圧を MOS ランジスタの第 3 の端子に結合することをさらに含む。少なくとも 1 つの実施形態によれば、欠陥電流の許容性を提供するために、仮想正電圧および仮想負電圧に結合される起動回路を提供することは、負電圧を MOS ランジスタの第 4 の端子に結合することをさらに含む。少なくとも 1 つの実施形態によれば、仮想正電圧を MOS ランジスタの第 1 の端子に結合することは、仮想正電圧を MOS ランジスタのゲートに結合することをさらに含む。少なくとも 1 つの実施形態によれば、仮想負電圧を MOS ランジスタの第 2 の端子に結合することは、仮想負電圧を MOS ランジスタのソースに結合することをさらに含む。少なくとも 1 つの実施形態によれば、正電圧を MOS ランジスタの第 3 の端子に結合することは、正電圧を MOS ランジスタのボディに結合することをさらに含む。少なくとも 1 つの実施形態によれば、負電圧を MOS ランジスタの第 4

40

の端子に結合することは、負電圧をMOSトランジスタのドレインに結合することをさらに含む。少なくとも1つの実施形態によれば、上記のステップ少なくとも一部が適切な起動動作を保証する。少なくとも1つの実施形態によれば、上記のステップ少なくとも一部が欠陥電流の許容性を提供する。

#### 【0039】

少なくとも1つの実施形態は、正テール電流源および負テール電流源のいずれかまたは両方のためのテール電流量を「プログラム」する能力を提供する。テール電流源に対して別個のイネーブル入力を提供することであって、別個のイネーブル入力はそれぞれ別個のトランジスタに結合され、各トランジスタは、テール電流源をソースとするかまたはそこに溜められたテール電流の総量のそれぞれの部分が流れることを可能にする、提供することによって、テール電流量は用途の需要に基づいてそれを「プログラム」するように選択されることができる。したがって、少なくとも1つの実施形態は、少なくとも1つのプログラム可能テール電流源を提供する。少なくとも1つの実施形態は、第1のイネーブル入力において第1のイネーブル信号を受信することであって、第1のイネーブル入力は第1のテール電流源イネーブルトランジスタに結合され、第1のテール電流源イネーブルトランジスタは、テール電流の総量の第1の部分が流れることを可能にする、受信することと、第2のイネーブル入力において第2のイネーブル信号を受信することであって、第2のイネーブル入力は第2のテール電流源イネーブルトランジスタに結合され、第2のテール電流源イネーブルトランジスタは、テール電流の総量の第2の部分が流れることを可能にする、受信することとを含む。第1のテール電流源イネーブルトランジスタは、第1の導電型のテール電流トランジスタおよび第2の導電型のテール電流トランジスタから成る群から選択される要素に接続される。第1のテール電流源イネーブルトランジスタおよび第2のテール電流源イネーブルトランジスタは、たとえば、それぞれ、イネーブル回路106のNMOSFET230およびNMOSFET231として、および/またはそれらの相補的なバージョンとして実装することができ、そのようなイネーブル回路は、たとえば、正電圧(たとえば、VDD\_INT)108と正テール電流源104との間に配置される。

10

20

#### 【0040】

少なくとも1つの実施形態によれば、完全に差動かつ相補的なトポロジを改善するための方法が提供される。少なくとも1つの実施形態によれば、方法は、正テール電流源の基準を、負テール電流源に関連付けられる仮想負レール電圧に置くことと、負テール電流源の基準を、正テール電流源に関連付けられる仮想正レール電圧に置くこととを含む。少なくとも1つの実施形態によれば、正テール電流源の基準を、負テール電流源に関連付けられる仮想負レール電圧に置くことは、仮想負レール電圧を正テール電流源正型金属酸化膜半導体(PMOS)トランジスタのゲートに結合することをさらに含み、正テール電流源PMOSトランジスタのドレインが仮想正レール電圧に結合され、負テール電流源の基準を、正テール電流源に関連付けられる仮想正レール電圧に置くことは、仮想正レール電圧を負テール電流源負型金属酸化膜半導体(NMOS)トランジスタのゲートに結合することをさらに含み、負テール電流源NMOSトランジスタのドレインが仮想負レール電圧に結合される。少なくとも1つの実施形態によれば、正テール電流源PMOSトランジスタのソースは正レール電圧に結合される。少なくとも1つの実施形態によれば、負テール電流源NMOSトランジスタのソースは負レール電圧に結合される。

30

40

#### 【0041】

少なくとも1つの実施形態によれば、方法は、出力振幅および速度を向上させるために自己バイアススタックを除くことをさらに含む。少なくとも1つの実施形態によれば、方法は、電界効果トランジスタ(FET)のソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第1の端子を仮想正電圧に結合することによって、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第2の端子を仮想負電圧に結合することによって、FETのソース、ドレイン、ゲート、およびボディから成る群から選択されるFETの第3の端子を正電圧に結合することによって、F

50

E T のソース、ドレイン、ゲート、およびボディから成る群から選択される F E T の第 4 の端子を負電圧に結合することによって、欠陥電流許容性を向上させることをさらに含む。

#### 【 0 0 4 2 】

少なくとも 1 つの実施形態によれば、自己バイアス受信機が提供される。少なくとも 1 つの実施形態によれば、正電圧が正テール電流源に結合され、正テール電流源は仮想正電圧を提供し、負電圧が負テール電流源に結合され、負テール電流源は仮想負電圧を提供し、差動増幅器は仮想正電圧に結合される正ドライバ部分および仮想負電圧に結合される負ドライバ部分を備える。仮想正電圧は負テール電流源を制御し、仮想負電圧は正テール電流源を制御する。

10

#### 【 0 0 4 3 】

少なくとも 1 つの実施形態によれば、正テール電流源は正型金属酸化膜半導体 ( P M O S ) ドライバを備え、P M O S ドライバのゲートは仮想負電圧に結合され、P M O S ドライバのソースは正電圧に結合され、P M O S ドライバのドレインは仮想正電圧に結合される。少なくとも 1 つの実施形態によれば、負テール電流源は負型金属酸化膜半導体 ( N M O S ) ドライバを備え、N M O S ドライバのゲートは仮想正電圧に結合され、N M O S ドライバのソースは負電圧に結合され、N M O S ドライバのドレインは仮想負電圧に結合される。

#### 【 0 0 4 4 】

少なくとも 1 つの実施形態によれば、自己バイアス受信機はイネーブル回路をさらに備え、イネーブル回路はN M O S ドライバのソースを負電圧に選択的に結合する。少なくとも 1 つの実施形態によれば、自己バイアス受信機は、仮想正電圧および仮想負電圧に結合される起動回路を含む。少なくとも 1 つの実施形態によれば、起動回路は金属酸化膜半導体 ( M O S ) ドライバをさらに備え、M O S ドライバの第 1 の端子は仮想正電圧に結合され、M O S ドライバの第 2 の端子は仮想負電圧に結合され、M O S ドライバの第 3 の端子は負電圧に結合され、M O S ドライバの第 4 の端子は正電圧に結合される。少なくとも 1 つの実施形態によれば、M O S ドライバは第 2 の P M O S ドライバをさらに備え、第 2 の P M O S ドライバのゲートは仮想正電圧に結合され、第 2 の P M O S ドライバのソースは仮想負電圧に結合され、第 2 の P M O S ドライバのドレインは負電圧に結合され、第 2 の P M O S ドライバのボディは正電圧に結合される。少なくとも 1 つの実施形態によれば、起動回路は少なくとも 3 マイクロアンペアの欠陥電流許容性を提供する。

20

#### 【 0 0 4 5 】

少なくとも 1 つの実施形態によれば、本明細書に記載のさまざまな F E T はそれらのボディ端子がさまざまな電位 ( すなわち、電圧 ) に結合されて示されている。いくつかのボディは電源に結合されており、一方で他はソースに結合されている。ボディ端子接続は、性能 / 電力 / 面積 / 他の考慮に基づくさまざまな電位 ( たとえば、電源またはソースの電位 ) に対するものであり得ることは理解されたい。その上、いくつかの事例においては、F E T のボディ端子は他の F E T 端子 ( たとえば、ゲート端子またはドレイン端子 ) に接続され得る。

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開2000-306382(JP,A)

米国特許出願公開第2009/0251214(US,A1)

米国特許第06046638(US,A)

特開2006-157262(JP,A)

特開2005-063026(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 25/02

H03K 19/0944