(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6132506号

(P6132506)

(45) 発行日 平成29年5月24日(2017.5.24)

(24) 登録日 平成29年4月28日(2017.4.28)

(51) Int.Cl.

F 1

H04N 5/378 (2011.01)

H04N 5/335

780

H03M 1/56 (2006.01)

H03M 1/56

H01L 27/146 (2006.01)

H01L 27/14

A

請求項の数 16 (全 17 頁)

(21) 出願番号

特願2012-223307 (P2012-223307)

(22) 出願日

平成24年10月5日 (2012.10.5)

(65) 公開番号

特開2014-75748 (P2014-75748A)

(43) 公開日

平成26年4月24日 (2014.4.24)

審査請求日

平成27年8月31日 (2015.8.31)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 中村 恒一

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 岩田 公一郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の列を成すように設けられた複数の画素と、

各々が前記複数の列のいずれか1つに対応して設けられた複数の比較器と、

前記複数の比較器に参照信号を供給する参照信号生成部と、

グレイコードを構成する複数のビットを含むカウント信号を、第1のクロック信号に同期して生成するカウンタと、

前記カウンタから出力された前記グレイコードを構成する複数のビットを第2のクロック信号に同期化することによって生成された同期化後カウント信号を出力する同期化部と、

各々が前記比較器に対応して設けられ、対応する前記比較器の出力の変化を受けて前記同期化後カウント信号を保持する複数のメモリを有することを特徴とする光電変換装置。

## 【請求項 2】

前記カウンタは、バイナリコードのカウント信号を生成するバイナリカウンタ部と、前記バイナリカウンタ部の出力をグレイコードに変換するEXOR回路とを含むことを特徴とする請求項1記載の光電変換装置。

## 【請求項 3】

複数の列を成すように設けられた複数の画素と、

各々が前記複数の列のいずれか1つに対応して設けられた複数の比較器と、

10

20

前記複数の比較器に参照信号を供給する参照信号生成部と、

複数のビットを含むカウント信号を、第1のクロック信号に同期して生成するカウンタと、

前記複数のビットを第2のクロック信号に同期化することによって生成された同期化後カウント信号を出力する同期化部と、

各々が前記比較器に対応して設けられ、対応する前記比較器の出力の変化を受けて前記同期化後カウント信号を保持する複数のメモリと、

デジタルデータを供給するデータ供給部と、

選択部と、を備え、

前記選択部は、前記デジタルデータと前記カウント信号を選択的に前記同期化部に出力すること 10

を特徴とする光電変換装置。

#### 【請求項4】

前記デジタルデータは、前記カウンタが出力する最大値に対応するデータであることを特徴とする請求項3に記載の光電変換装置。

#### 【請求項5】

前記同期化部から出力された前記同期化後カウント信号を前記第2のクロック信号に同期して出力する第2の同期化部を有し、

前記同期化部から出力された前記同期化後カウント信号を前記複数のメモリのうちの一部に供給し、前記第2の同期化部の出力を前記複数のメモリの別の一部に供給すること 20

を特徴とする請求項1～4のいずれかに記載の光電変換装置。

#### 【請求項6】

前記第2のクロック信号は、前記第1のクロック信号よりも周波数が高いことを特徴とする請求項1～5のいずれかに記載の光電変換装置。

#### 【請求項7】

前記第2のクロック信号の周波数は、nを自然数として、前記第1のクロック信号の周波数の2n倍であることを特徴とする請求項6に記載の光電変換装置。

#### 【請求項8】

前記カウンタは、グレイコードを前記カウント信号として出力するグレイコードカウンタであることを特徴とする請求項3または4に記載の光電変換装置。 30

#### 【請求項9】

前記カウンタは、バイナリコードを前記カウント信号として出力するバイナリカウンタであることを特徴とする請求項3または4に記載の光電変換装置。

#### 【請求項10】

前記同期化部は、フリップフロップを含むことを特徴とする請求項1～9のいずれかに記載の光電変換装置。

#### 【請求項11】

複数の列を成すように配された複数の画素と、

前記複数の列に対応して設けられた複数の比較器と、

前記複数の比較器に参照信号を供給する参照信号生成部と、

前記複数の比較器に対応して設けられた複数のデジタル信号生成部と、 40

互いに位相の異なる複数のクロック信号を生成するクロック信号生成部と、

前記複数のクロック信号を第2のクロック信号に同期化することによって生成された複数の同期化後クロック信号を出力する同期化部と、を備え、

前記複数のデジタル信号生成部の各々は、デコード回路とカウンタとを含み、

前記デコード回路は、前記複数の同期化後クロック信号をデコードして第1のデジタル値に変換し、

前記カウンタは、前記複数の同期化後クロック信号の1つを受けてカウント動作を行うこと

を特徴とする光電変換装置。 50

**【請求項 1 2】**

前記デジタル信号生成部は、前記比較器の出力が反転した時に前記カウンタが保持しているカウント値を上位ビットとし、前記比較器の出力が反転した時に前記デコード回路が出力する前記第1のデジタル値を下位ビットとして、デジタル信号を生成することを特徴とする請求項11に記載の光電変換装置。

**【請求項 1 3】**

前記同期化部から出力された前記複数の同期化後クロック信号を前記第2のクロック信号に同期して複数の第2の同期化後クロック信号を出力する第2の同期化部を有し、

前記同期化部から出力された前記複数の同期化後クロック信号を前記複数のデジタル信号生成部のうちの一部に供給し、前記第2の同期化部から出力された前記複数の第2の同期化後クロック信号を前記複数のデジタル信号生成部の別の一部に供給すること

を特徴とする請求項11または請求項12に記載の光電変換装置。

**【請求項 1 4】**

前記第2のクロック信号は、前記複数のクロック信号よりも周波数が高いことを特徴とする請求項11～13のいずれかに記載の光電変換装置。

**【請求項 1 5】**

前記第2のクロック信号の周波数は、nを自然数として、前記複数のクロック信号の周波数の2n倍であることを特徴とする請求項14に記載の光電変換装置。

**【請求項 1 6】**

請求項1～15のいずれかに記載の光電変換装置と、

前記複数の画素から成る画素アレイに像を形成する光学系と、

前記光電変換装置から出力された信号を処理して画像データを生成する信号処理部と、

をさらに備えたこと

を特徴とする撮像システム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置及び撮像システムに関する。

**【背景技術】****【0002】**

行列状に画素が設けられた画素アレイの各列に応じて、A/D変換器が設けられた固体撮像素子が知られている。特許文献1には、各A/D変換器がカウンタ回路を備え、各カウンタに対して位相の異なる複数のクロック信号を供給することが記載されている。各クロック信号のデューティズレを低減するために、特許文献1は、クロック信号の伝送部において、複数のリピートバッファを直列に接続した主伝送ラインと、複数のリピートバッファを直列に接続した副伝送ラインとを備え、副伝送ラインが主伝送ラインから分岐する構成を用いている。

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2011-166197号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

ところが、特許文献1に記載された構成ではクロック信号のデューティズレを十分に抑制できないおそれがある。

また、複数のA/D変換器でカウンタ回路を共有する構成においても、デューティズレの問題が生じるおそれがある。

本発明は、上述した問題の少なくとも一方を解決することを目的とする。

**【課題を解決するための手段】**

10

20

30

40

50

**【0005】**

本発明の一側面である光電変換装置は、複数の列を成すように設けられた複数の画素と、各々が前記複数の列のいずれか1つに対応して設けられた複数の比較器と、前記複数の比較器に参照信号を供給する参照信号生成部と、グレイコードを構成する複数のビットを含むカウント信号を、第1のクロック信号に同期して生成するカウンタと、前記カウンタから出力された前記グレイコードを構成する複数のビットを第2のクロック信号に同期化することによって生成された同期化後カウント信号を出力する同期化部と、各々が前記比較器に対応して設けられ、対応する前記比較器の出力の変化を受けて前記同期化後カウント信号を保持する複数のメモリを有することを特徴とする。

**【0006】**

10

本発明の別の側面である光電変換装置は、複数の列を成すように配された複数の画素と、前記複数の列に対応して設けられた複数の比較器と、前記複数の比較器に参照信号を供給する参照信号生成部と、前記複数の比較器に対応して設けられた複数のデジタル信号生成部と、互いに位相の異なる複数のクロック信号を生成するクロック信号生成部と、前記複数のクロック信号を第2のクロック信号に同期化することによって生成された複数の同期化後クロック信号を出力する同期化部と、を備え、前記複数のデジタル信号生成部の各々は、デコード回路とカウンタとを備え、前記デコード回路は、前記複数の同期化後クロック信号をデコードして第1のデジタル値に変換し、前記カウンタは、前記複数の同期化後クロック信号の1つを受けてカウント動作を行うことを特徴とする。

**【発明の効果】**

20

**【0007】**

本発明によればデューティズレを低減できる。

**【図面の簡単な説明】****【0008】**

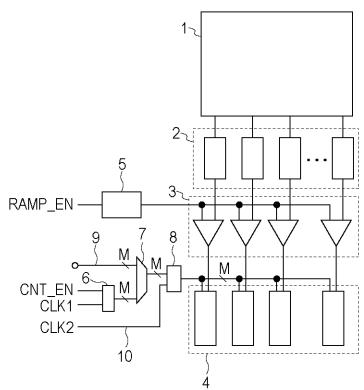

【図1】光電変換装置の構成を示す図である。

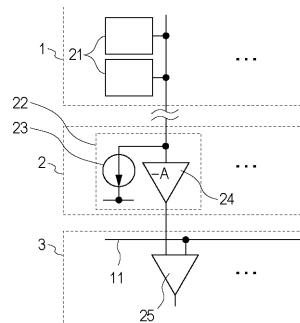

【図2】光電変換装置の一部の構成を図である。

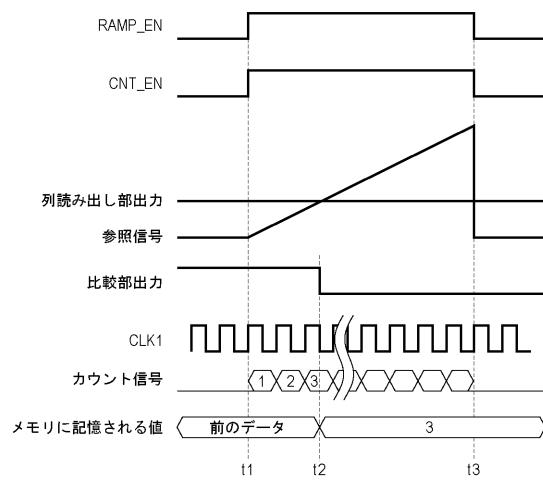

【図3】光電変換装置の動作を示すタイミング図である。

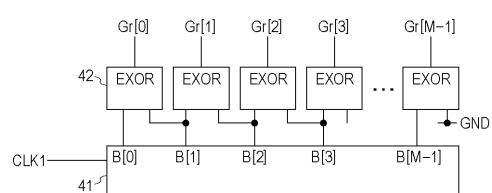

【図4】カウンタの構成を示す図である。

【図5】EXOR回路の構成を示す図である。

【図6】EXOR回路の動作を示すタイミング図である。

30

【図7】グレイコードカウンタ回路におけるデューティズレを説明するためのタイミング図である。

【図8】同期化部の構成を示す図である。

【図9】カウンタの動作を説明するためのタイミング図である。

【図10】選択部の構成を示す図である。

【図11】バイナリコードカウンタ回路におけるデューティズレを説明するための図である。

【図12】光電変換装置の構成を示す図である。

【図13】同期化後カウント信号の伝送経路の構成を示す図である。

【図14】光電変換装置の構成を示す図である。

40

【図15】光電変換装置の一部の構成を示す図である。

【図16】デジタル信号生成部の動作を示すタイミング図である。

【図17】撮像システムの構成を示す図である。

**【発明を実施するための形態】****【0009】**

(実施例1)

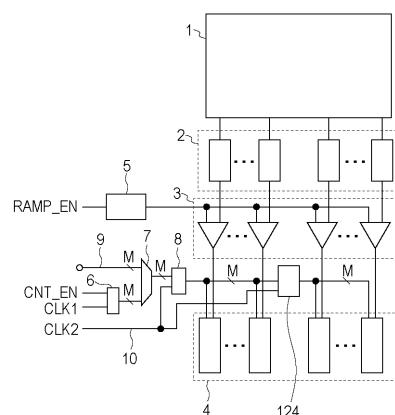

図1は、実施例1に係る光電変換装置の構成を示すブロック図である。光電変換装置は、画素アレイ1、読み出し部群2、比較部群3、メモリ部群4、参照信号生成部5、カウンタ6、選択部7、同期化部8を含む。

**【0010】**

50

画素アレイ 1 は、複数列設けられた複数の画素を含む。読み出し部群 2 は、それぞれが画素アレイ 1 の各列に対応して設けられた複数の読み出し部を含む。比較部群 3 は、それぞれが各読み出し部に対応して設けられた複数の比較器を含む。メモリ部群 4 は、それぞれが各比較器に対応して設けられた複数のメモリ部を含む。参照信号生成部 5 は、ランプイネーブル信号 R A M P\_E N の入力に応じて、時間に対して信号レベルが変化する参照信号を出力する。カウンタ 6 は、カウントイネーブル信号 C N T\_E N に応じて、第 1 のクロック信号 C L K 1 をカウントして M ビットのカウント信号を出力する。選択部 7 は、カウンタ 6 から出力されたカウント信号および M ビットのデジタルデータ 9 のいずれかを選択的に同期化部 8 に出力する。デジタルデータ 9 は、不図示のデータ供給部から与えられる。同期化部 8 は、選択部 7 から出力された M ビットの信号を、第 2 のクロック信号 C L K 2 に同期した同期化後クロック信号を出力する。各列のメモリ部は対応する比較部の出力が変化すると、それをトリガとして同期化部 8 の出力を保持する。

10

#### 【 0 0 1 1 】

図 2 は、画素アレイ 1 、読み出し部群 2 、および比較部群 3 の構成例を 1 列分だけ示したブロック図である。画素アレイ 1 には複数の画素 2 1 が 1 個の読み出し部 2 2 に共通に接続されている。読み出し部 2 2 は例えば定電流源 2 3 と増幅器 2 4 を含む。定電流源 2 3 は、画素 2 1 が増幅トランジスタを有する場合に、増幅トランジスタとともにソースフォロワ回路を構成する。増幅器 2 4 は、図示したように画素から出力された信号に - A 倍のゲインをかける反転増幅回路でも良いし、正のゲインをかける非反転増幅回路でも良く、バッファリングのみを行うバッファ回路であっても良い。読み出し部 2 2 は、画素から出力された信号に含まれるノイズ成分を低減するノイズ低減回路をさらに備えても良い。ここでは、増幅器 2 4 の出力が、読み出し部 2 2 の出力として比較器 2 5 に与えられる。

20

#### 【 0 0 1 2 】

図 3 は、図 1 に示した光電変換装置の動作を説明するためのタイミング図である。説明を簡単にするために、カウンタから出力されるカウント信号の値を 10 進数で示しているが、実際には M ビットの信号として出力される。また、時刻 t 1 から時刻 t 3 までの期間、選択部 7 は、カウンタ 6 から出力されたカウント信号をメモリ部群 4 に供給するように設定される。

#### 【 0 0 1 3 】

時刻 t 1 より前に、デジタル信号に変換されるべきアナログ信号が、比較部群 3 に、読み出し部群 2 から与えられているものとする。時刻 t 1 にランプイネーブル信号 R A M P\_E N およびカウントイネーブル信号 C N T\_E N が H レベルになる。これにより、参照信号生成部の出力が時間に対して変化を開始するとともに、カウンタ 6 が第 1 のクロック信号 C L K 1 のカウント動作を開始する。本例では、第 1 のクロック信号 C L K 1 の立ち上がりとともにカウント値がインクリメントする。参照信号は、時間に対してスロープ状に変化するものでもよいし、ステップ状に変化するものであっても良い。

30

#### 【 0 0 1 4 】

時刻 t 2 に読み出し部の出力と参照信号のレベルの大小関係が逆転すると、比較部の出力が H レベルから L レベルに変化し、メモリ部はこの時のカウント信号を保持する。このとき保持されたカウント信号は、読み出し部から出力されたアナログ信号に相当するデジタル信号となる。

40

#### 【 0 0 1 5 】

その後、時刻 t 3 まで参照信号のレベルが変化し続けてから参照信号の出力がリセットされる。

#### 【 0 0 1 6 】

変換されるアナログ信号が、A D 変換できるダイナミックレンジに入らない場合には、時刻 t 3 までに比較部の出力が変化しない。この場合、当該列のメモリ部には時刻 t 1 よりも前のデータが保持されたままになっているので、異常値となってしまう。そこで、時刻 t 3 の後に、カウント信号に換えてデジタルデータ 9 をメモリ部に供給するように選択部 7 を制御して、メモリ部にデジタルデータ 9 を保持させる。デジタルデータ 9 は所定の

50

値であり、例えば A/D 変換できる最大値に対応するデジタル信号である。

**【0017】**

この後、メモリ部群 4 に保持されたデジタル信号を、不図示の列選択部により後段の回路へと出力させる。

**【0018】**

カウンタ 6 の構成例として、Gr [ 0 ] から Gr [ M - 1 ] の M ビット出力を行うグレイコードカウンタ回路の構成を図 4 に示す。グレイコードカウンタは、M ビットのバイナリカウンタ回路 4 1 と M 個の排他的論理和 (EXOR) 回路 4 2 とを含む。バイナリカウンタは第 1 のクロック信号 CLK 1 の入力を受けてカウント動作を行う。グレイコードカウンタ回路の最上位ビット Gr [ M - 1 ] を出力する EXOR 回路 4 2 を除く各 EXOR 回路 4 2 は、バイナリカウンタ回路 4 1 の出力のうちの隣接する 2 個のビットの出力を入力として、1 ビットの出力を行う。具体的には、バイナリカウンタの出力 B [ n ] および B [ n + 1 ] を入力としてグレイコードカウンタの出力 Gr [ n ] が生成される (n は自然数)。最上位ビット Gr [ M - 1 ] を出力する EXOR 回路 4 2 は、B [ M - 1 ] と GND とに接続される。

10

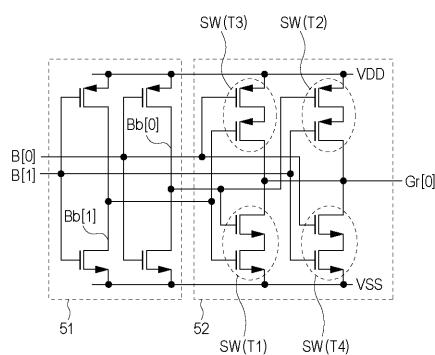

**【0019】**

最下位ビット Gr [ 0 ] を例に取って、EXOR 回路 4 2 の構成を図 5 に示す。EXOR 回路 4 2 はインバータ回路部 5 1 とスイッチ回路部 5 2 とを含む。インバータ回路部 5 1 は 2 個のインバータ回路を含み、B [ 0 ] と B [ 1 ] とを受けて、これらの反転信号 Bb [ 0 ] と Bb [ 1 ] とを出力する。

20

**【0020】**

スイッチ回路部 5 2 は、4 個のスイッチ部 SW (T 1) ~ SW (T 4) を含む。スイッチ部 SW (T 1) は、反転信号 Bb [ 0 ] で制御される NMOS トランジスタと反転信号 Bb [ 1 ] で制御される NMOS トランジスタが直列に接続されて構成される。スイッチ部 SW (T 2) は、反転信号 Bb [ 0 ] で制御される PMOS トランジスタと信号 B [ 1 ] で制御される PMOS トランジスタが直列に接続されて構成される。スイッチ部 SW (T 3) は、信号 B [ 0 ] で制御される PMOS トランジスタと反転信号 Bb [ 1 ] で制御される PMOS トランジスタが直列に接続されて構成される。スイッチ部 SW (T 4) は、信号 B [ 0 ] で制御される NMOS トランジスタと信号 B [ 1 ] で制御される NMOS トランジスタが直列に接続されて構成される。

30

**【0021】**

これらのスイッチ部のうち、スイッチ部 SW (T 3) とスイッチ部 SW (T 1) とが直列に接続されており、両者の共通ノードが EXOR 回路 4 2 の出力ノード Gr [ 0 ] に接続される。同様に、スイッチ部 SW (T 2) とスイッチ部 SW (T 4) とが直列に接続されており、両者の共通ノードが EXOR 回路 4 2 の出力ノード Gr [ 0 ] に接続される。

**【0022】**

次に、図 6 を参照しながら EXOR 回路 4 2 の動作を説明する。インバータ回路部 5 1 の各インバータで生じる遅延を t とする。

**【0023】**

バイナリカウンタ回路 4 1 の出力 B [ 0 ] および B [ 1 ] は、出力 B [ 0 ] に対して 1 / 2 の周波数で変化する。出力 B [ 0 ] および B [ 1 ] の状態を踏まえて、T 1 ~ T 4 の期間に分けて説明する。

40

**【0024】**

期間 T 1 は、出力 B [ 0 ] および B [ 1 ] がともに L レベルである。このとき反転信号 Bb [ 0 ] および Bb [ 1 ] はともに H レベルとなりスイッチ部 SW (T 1) がオンする。これにより、EXOR 回路 4 2 の出力 Gr [ 0 ] は L レベルになる。

**【0025】**

期間 T 2 は、出力 B [ 0 ] が H レベルになり、出力 B [ 1 ] は L レベルを維持する。出力 B [ 0 ] の遷移により、その反転信号 Bb [ 0 ] も L レベルに遷移するが、インバータ回路による t だけ遅れて遷移する。期間 T 2 にはスイッチ部 SW (T 2) がオンするの

50

で、信号 B [ 0 ] の遷移から  $t$  だけ遅れて EXOR 回路 42 の出力 G<sub>r</sub> [ 0 ] が H レベルになる。

#### 【 0 0 2 6 】

期間 T3 は、出力 B [ 0 ] が再び L レベルになり、出力 B [ 1 ] が H レベルになる。反転信号 B<sub>b</sub> [ 0 ] と B<sub>b</sub> [ 1 ] はともに出力 B [ 0 ] と B [ 1 ] の遷移から  $t$  だけ遅れて遷移する。期間 T3 にはスイッチ部 SW ( T3 ) がオンするので、EXOR 回路 42 の出力 G<sub>r</sub> [ 0 ] は H レベルを維持する。

#### 【 0 0 2 7 】

期間 T4 は、出力 B [ 0 ] が H レベルになり、出力 B [ 1 ] が H レベルを維持する。

反転信号 B<sub>b</sub> [ 0 ] は信号 B [ 0 ] に対して  $t$  だけ遅れて遷移する。期間 T4 にはスイッ

チ部 SW ( T4 ) がオンするので、EXOR 回路 42 の出力 G<sub>r</sub> [ 0 ] は L レベルになる。

。

10

#### 【 0 0 2 8 】

以上の説明から理解されるとおり、EXOR 回路 42 の出力 G<sub>r</sub> [ 0 ] は、L レベルか

ら H レベルに遷移するときに  $t$  だけ遅延し、H レベルから L レベルに遷移するときには

遅延が生じない。この結果、出力 G<sub>r</sub> [ 0 ] は H レベルである期間が L レベルである期間

よりも短くなり、デューティ比が 50 % でなくなる。つまり、デューティズレガ生じた状

態となる。

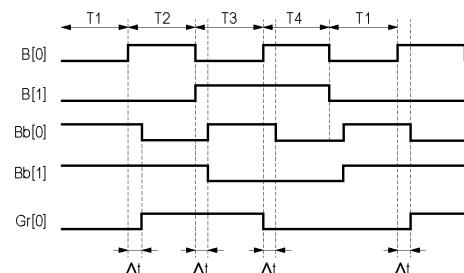

#### 【 0 0 2 9 】

4 ビットのグレイコードカウンタ回路において、上述したデューティズレガ各ビットで

発生する場合のタイミング図を図 7 に示す。

。

20

#### 【 0 0 3 0 】

グレイコードが、あるビットの立ち上がりエッジから別のビットの立ち上がりエッジま

でで決定される場合には、正常な期間だけそのコードが維持される。図 7 においては 1 お

よび 4 のグレイコードが該当する。同様に、あるビットの立ち下がりエッジから別のビ

ットの立ち下がりエッジまでで決定される場合にも、正常な期間だけそのコードが維持され

る。図 7 においては 6 のグレイコードが該当する。

#### 【 0 0 3 1 】

しかし、グレイコードがあるビットの立ち下がりエッジから別のビットの立ち上がりエ

ッジまでで決定される場合には、正常な期間よりも長くそのコードが維持される。図 7 に

においては 0、3、7 のグレイコードが該当する。

。

30

#### 【 0 0 3 2 】

一方、グレイコードがあるビットの立ち上がりエッジから別のビットの立ち下がりエッ

ジまでで決定される場合には、正常な期間よりも短くそのコードが維持される。図 7 に

においては 2 および 5 のグレイコードが該当する。

#### 【 0 0 3 3 】

グレイコードカウンタ回路が各グレイコードを出力する期間の長さが異なる場合には、

このグレイコードをカウント信号として用いて A/D 変換を行うと、変換されるアナログ信

号に対して得られるデジタルデータの関係がリニアではなくなる。つまり、A/D 変換部の

リニアリティが低下することになり、ひいては得られる画像の画質が劣化する。

。

40

#### 【 0 0 3 4 】

そこで、本実施例では、カウンタ 6 の出力を第 2 のクロック信号 C<sub>L</sub>K<sub>2</sub> に同期させて

、同期化後クロック信号をメモリ部群 4 に供給する。

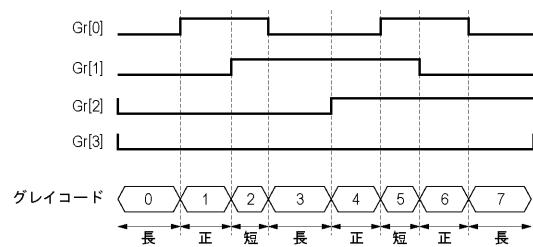

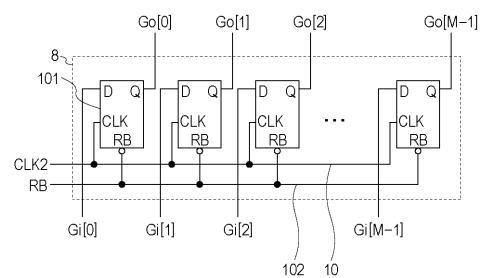

#### 【 0 0 3 5 】

図 8 に同期化部 8 の構成を示す。同期化部 8 は M 個のフリップフロップ 101 を含む。

各フリップフロップ 101 は、第 2 のクロック信号 C<sub>L</sub>K<sub>2</sub> が共通に与えられるほか、リ

セット信号 R<sub>B</sub> も共通に与えられる。リセット信号 R<sub>B</sub> が L レベルになるとフリップフロ

ップ 101 の出力がリセットされる。各フリップフロップ 101 の D 端子には、それぞれ

グレイコード G<sub>i</sub> [ 0 : M - 1 ] の各ビットが与えられる。そして、Q 端子からは対応す

るグレイコードを第 2 のクロック信号 C<sub>L</sub>K<sub>2</sub> に同期した同期化後クロック信号として、

。

50

$G_o[0:M-1]$  を出力する。

【0036】

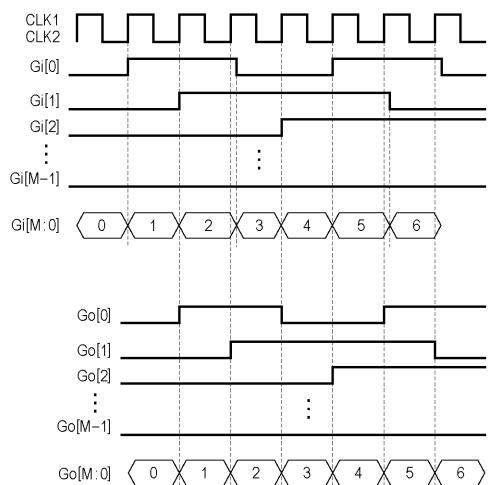

図9をさらに参照しながら、カウンタ6の出力である  $G_i[0:M-1]$  と同期化後クロック信号  $G_o[0:M-1]$  の関係を説明する。説明を簡単にするために、第1および第2のクロック信号が同位相で同周波数のクロック信号であるとする。

【0037】

カウンタ6の出力  $G_i[0:M-1]$  は、先述の通り正常な期間の長さよりも長いあるいは短い期間だけ出力されるグレイコードがある。これに対して、カウンタ6の出力  $G_i[0:M-1]$  をクロック信号の立ち上がりに同期させると、得られる同期化後カウント信号からは各コードが等しい長さで得られる。この同期化後カウント信号をメモリ部群4に与えることにより、A/D変換部のリニアリティが低下することを抑制できる。

10

【0038】

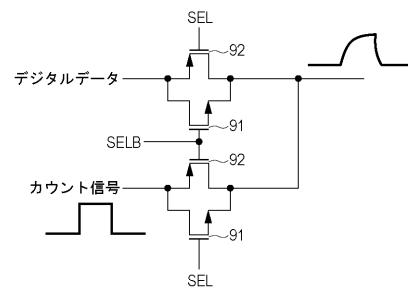

同期化部8は、カウント信号のデューティズレを低減するだけでなく、位相ズレも低減できる。図10は選択部7の1ビット分の構成例を示した回路図である。

【0039】

図10に示した選択部7は、カウント信号が入力される系とデジタルデータが入力される系とを含む。各系に対してN MOSトランジスタ91とP MOSトランジスタ92で構成されたCMOSスイッチが設けられており、2つのCMOSスイッチは、信号SELとその反転信号SELBによって排他的にオンするように構成されている。図1では信号SELおよびSELBは図示を省略した。仮にN MOSトランジスタ91とP MOSトランジスタ92とが、例えば製造時のプロセスばらつきによって異なる駆動力をを持つと、選択部7から出力される信号はデューティがずれるおそれがある。さらに、ビット間でもデューティズレの量が異なると、選択部7を経由して出力されたカウント信号はビット間で位相のズレが生じるおそれもある。したがって、図1のように選択部7を備える構成では、選択部7の後段に同期化部8を設けることで、選択部7に起因して生じうるデューティズレや位相ズレも低減することができる。

20

【0040】

本実施例ではカウンタ6がグレイコードカウンタである場合を詳細に説明したが、例えばバイナリコードカウンタであっても良い。

【0041】

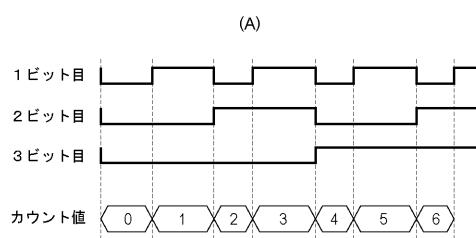

バイナリコードカウンタにデューティズレが生じた場合の影響を説明する。図11(A)は3ビットのカウンタにおいて、最下位ビット(1ビット目)にデューティズレが生じて、Hレベルの期間が長い場合のカウント値を示すタイミング図である。2ビット目および3ビット目にはデューティズレが生じておらず、それぞれデューティズレが生じていない場合の最下位ビットの信号に対して1/2倍、1/4倍の周期で遷移するものとする。

30

【0042】

この場合には、2、4、6のカウント値が出力される期間が他のカウント値よりも短くなってしまう。この条件の下、図1に示した光電変換装置に含まれるA/D変換部の入出力特性を図11(B)に示す。横軸が変換されるべきアナログ信号で、縦軸がA/D変換された後のデジタル信号に対応する。実線で示した理想的な入出力特性に対して、図11(A)に示したデューティズレが生じた場合の入出力特性は破線で示している。破線で示した入出力特性は、理想値からずれているため、A/D変換部のリニアリティが低下していることになる。

40

【0043】

上記のように、バイナリコードカウンタをカウンタ6として用いても、同期化部8を設けることにより、デューティズレを低減し、A/D変換部のリニアリティが低下することを抑制できる。

【0044】

本実施例では選択部7がデジタルデータ9またはカウンタ6から出力されたカウント信号を選択的に同期化部8に出力する構成を説明したが、選択部7およびデジタルデータ9

50

を省略しても、カウント信号のビット間のデューティズレを低減できる。

#### 【0045】

また、本実施例では、第2のクロック信号の立ち上がりエッジに同期して同期化後カウント信号を生成する例を説明したが、立ち下がりエッジを用いても良いし、ビットによって第2のクロック信号のどちらのエッジに同期するかが異なっていてもよい。

#### 【0046】

また、第1のクロック信号と第2のクロック信号とは異なるものとして説明したが、同一のクロックでも良い。さらに、第1のクロック信号はカウンタを動作させるために用いるため、周波数を過剰に上げるとカウンタが正常に動作しなくなるおそれがある。一方、第2のクロック信号は、カウント信号を同期させるために用いるものなので、第1のクロック信号よりも高い周波数を設定することが容易である。例えば、第2のクロック信号を、第1のクロック信号の $2^n$  ( $n$ は自然数)倍の周波数を有するクロック信号としても良い。具体的な構成としては、分周器を設けて、第2のクロック信号を $1/(2^n)$ に分周したものを作成することができる。

10

#### 【0047】

以上で説明したとおり、本実施例によれば、デューティズレを低減することができる。

#### 【0048】

##### (実施例2)

実施例2を、実施例1との相違点を中心に説明する。

#### 【0049】

20

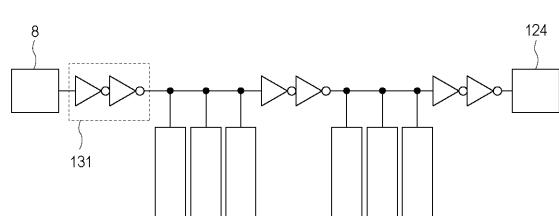

図12は、本実施例に係る光電変換装置の構成を示すブロック図である。図1に示した構成と異なるのは第2の同期化部124を備える点である。本実施例では、第1の同期化部である同期化部8から出力された同期化後カウント信号を、第2の同期化部124がさらに第2のクロック信号CLK2に同期して出力する。

#### 【0050】

画素アレイの列が増大すると、これに合わせて同期化部8から出力された同期化後カウント信号を伝送する配線も長くなる。これらの配線の寄生抵抗や寄生容量も増大するため、同期化後カウント信号のデューティズレや、各ビット間の位相ズレが生じやすくなる。そこで、本実施例のように構成することで、画素アレイの列が増大しても、同期化後カウント信号のデューティズレを低減することができる。

30

#### 【0051】

また、同期化後カウント信号を伝送するために、リピートバッファを設けることが考えられる。図13は、同期化部8から出力される同期化後カウント信号の1ビット分を伝送する経路の構成例を示す図である。図のように、リピートバッファとしてリピータ131を伝送系路上に設けて、リピータ131の出力を同期化後カウント信号としてメモリ部群4に供給する。リピータ131は例えば2段のインバータで構成され、インバータを構成するNMO SトランジスタとPMOSトランジスタとの駆動力のばらつきによって各ビットのデューティズレや各ビット間の位相ズレも生じうる。第2の同期化部124を設けることにより、リピータ131に起因するデューティズレや位相のズレを低減できる。

#### 【0052】

40

本実施例では、第2の同期化部124を1個設けた例を示したが、複数の第2の同期化部124を設けても良い。

#### 【0053】

##### (実施例3)

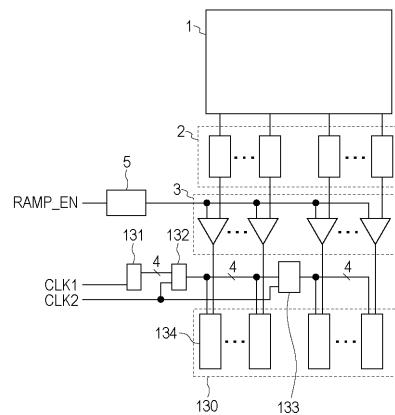

図14を参照しながら、実施例3に係る光電変換装置を実施例1との相違点を中心に説明する。

#### 【0054】

本実施例に係る光電変換装置は、メモリ部群4に換えて、デジタル信号生成部群130を備え、カウンタ6に換えてクロック信号生成部131を備える。さらに、本実施例に係る光電変換装置において、第1の同期化部132および第2の同期化部133は、クロッ

50

ク信号生成部 131 から出力されたクロック信号を第2のクロック信号 CLK2 に同期させて同期化後クロック信号を出力する。本実施例では、クロック信号生成部 131 は第1のクロック信号 CLK1 を受けて、位相の異なる4個のクロック信号を生成する。第1および第2の同期化部 132 および 133 は、図8に示したものと同様の構成とすることができます。ただし、カウンタの出力として各フリップフロップに与えられた信号は、クロック信号生成部 131 から与えられたクロック信号となる点で異なる。

#### 【0055】

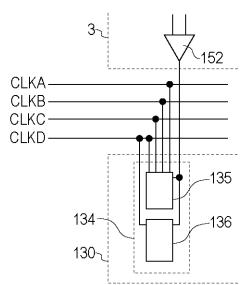

図15に、比較部群3とデジタル信号生成部群130のうち、画素アレイの1列に対応する部分を抜き出した図を示す。

#### 【0056】

1個のデジタル信号生成部 134 はラッチ回路とデコード回路とを含むラッチ&デコード部 135 と、カウンタ 136 とを含む。ラッチ&デコード部 135 は、4個の同期化後クロック信号 CLK\_A ~ CLK\_D および比較部の出力を入力信号として受け、比較部の出力が変化したことに応じて、同期化後クロック信号 CLK\_A ~ CLK\_D をラッチ回路がラッチする。ラッチされた同期化後クロック信号は、デコード回路によりデコードされてデコード値として出力される。カウンタ 136 は、同期化後クロック信号 CLK\_D と比較部の出力を入力信号として受け、同期化後クロック信号 CLK\_D 信号に応じてカウント動作を行う。比較部の出力が変化すると、カウンタ 136 はカウント動作を停止し、その時点でのカウント値を保持する。

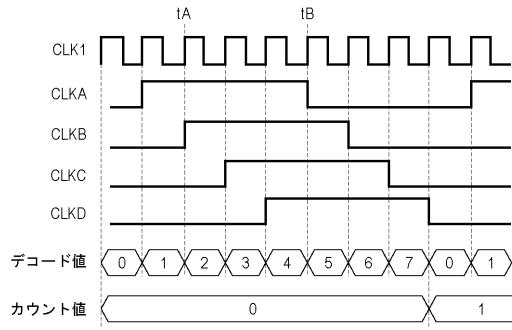

#### 【0057】

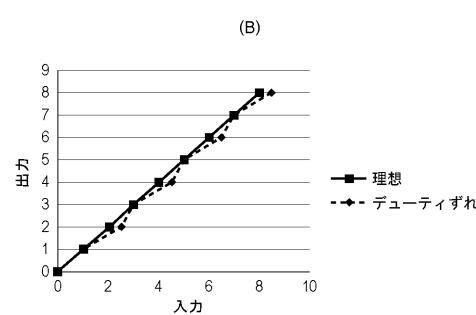

図16は、ラッチ&デコード部 135 およびカウンタ 136 の動作例を示すタイミング図である。同期化後クロック信号 CLK\_A ~ CLK\_D は、45度ずつ位相がずれたクロック信号であり、それぞれは、第1のクロック信号 CLK1 の8周期が1周期となっている。

#### 【0058】

カウンタ 136 は同期化後クロック信号 CLK\_D に応じてカウント動作を行う一方で、ラッチ&デコード部 135 には同期化後クロック信号 CLK\_A ~ CLK\_D が与えられるため、カウンタ 136 の1カウントに対してラッチ&デコード部 135 の出力は8個の状態を取り得る。デジタル信号生成部 134 がカウンタ 136 しか持たない場合には、比較器の出力が時刻 t\_A に変化しても、時刻 t\_B に変化しても「0」のカウント値しか得られない。しかし、本例のように構成することで、時刻 t\_A と時刻 t\_B とでラッチ&デコード部 135 の出力は異なるため、カウント値「0」をさらに高分解能で表現することができる。

#### 【0059】

以上で説明した本実施例によれば、クロック信号生成部 131 で生成されたカウント信号を第1の同期化部 132 で第2のクロック信号に同期させることにより、クロック信号のデューティずれや位相のずれを低減することができる。したがって、光電変換装置の入射光量に対する出力特性のリニアリティが低下することを抑制できる。

#### 【0060】

本実施例では、第2の同期化部 133 を設けて、第1の同期化部 132 が一部のデジタル信号生成部 134 に同期化後クロック信号を与え、第2の同期化部 133 が別の一部のデジタル信号生成部 134 に同期化後クロック信号を与える構成を示した。しかし、第1の同期化部 132 から出力されるクロック信号を全てのデジタル信号生成部に与えても良いし、同期化部 132 の出力を、リピータを介してデジタル信号生成部群 130 に与えても良い。

#### 【0061】

本実施例でも、先の実施例と同じく、第2のクロック信号 CLK2 の周波数は、第1のクロック信号 CLK1 の周波数よりも高く設定することができる。第2のクロック信号 CLK2 が第1のクロック信号 CLK1 の $2^n$ 倍の周波数を持っていても良く、分周器を用いてこの関係を実現することも先の実施例と同じである。

10

20

30

40

50

**【0062】**

また、各デジタル信号生成部が備えるカウンタは、バイナリコードカウンタでもグレイコードカウンタでも良い。

**【0063】****(実施例4)**

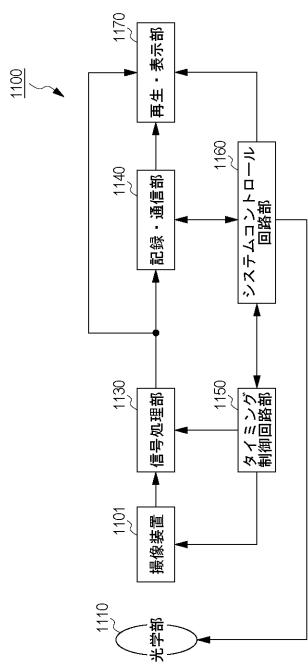

本発明に係る別の実施例を説明する。撮像システムの概略を、図17に示す。

**【0064】**

撮像システム1100は、例えば、光学部1110、撮像装置1101、信号処理部1130、記録・通信部1140、タイミング制御回路部1150、システムコントロール回路部1160、および再生・表示部1170を含む。撮像装置1101は、先述の各実施形態で説明した光電変換装置100が用いられる。例えば信号処理部1130は、第2の実施例で説明した、光電変換装置の後段に設けられた回路の機能を有してもよい。10

**【0065】**

レンズなどの光学系である光学部1110は、被写体からの光を撮像装置1101の、複数の画素が2次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置1101は、タイミング制御回路部1150からの信号に基づくタイミングで、画素アレイに結像された光に応じた信号を出力する。

**【0066】**

撮像装置1101から出力された信号は、映像信号処理部である信号処理部1130に入力され、信号処理部1130が、プログラムなどによって定められた方法に従って、入力された電気信号に対して補正などの処理を行う。信号処理部1130での処理によって得られた信号は画像データとして記録・通信部1140に送られる。記録・通信部1140は、画像を形成するための信号を再生・表示部1170に送り、再生・表示部1170に動画や静止画像が再生・表示される。記録通信部1140は、また、信号処理部1130からの信号を受けて、システムコントロール回路部1160とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。20

**【0067】**

システムコントロール回路部1160は、撮像システムの動作を統括的に制御するものであり、光学部1110、タイミング制御回路部1150、記録・通信部1140、および再生・表示部1170の駆動を制御する。また、システムコントロール回路部1160は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部1160は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例としては、読み出す行やりセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。30

**【0068】**

タイミング制御回路部1150は、制御部であるシステムコントロール回路部1160による制御に基づいて撮像装置1101および信号処理部1130の駆動タイミングを制御する。

**【0069】**

上述の各実施例は例示的なものであり、本発明の思想を逸脱しない範囲で適宜変更を加えることが可能である。40

**【符号の説明】****【0070】**

- 1 画素アレイ

- 2 読み出し部群

- 3 比較部群

- 4 メモリ部群

- 5 参照信号生成部

- 6 カウンタ

7 選択部

8 同期化部

1 2 4、1 3 3 第2の同期化部

1 3 0 デジタル信号生成部

1 3 1 クロック信号生成部

1 3 2 第1の同期化部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

---

フロントページの続き

(72)発明者 斎藤 和宏

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 秋山 健史

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 板野 哲也

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 横山 拓己

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 武藤 隆

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2011-234326 (JP, A)

特開2010-258806 (JP, A)

特開平11-068553 (JP, A)

特開2011-023900 (JP, A)

特開2009-124269 (JP, A)

特開2005-303648 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762

H03M 1/00 - 1/88