(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4072583号

(P4072583)

(45) 発行日 平成20年4月9日(2008.4.9)

(24) 登録日 平成20年2月1日(2008.2.1)

(51) Int.Cl.

H04L 12/44 (2006.01)

F 1

H 0 4 L 12/44

Z

請求項の数 12 (全 12 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平10-535773                 |

| (86) (22) 出願日 | 平成10年1月29日(1998.1.29)        |

| (65) 公表番号     | 特表2001-511977(P2001-511977A) |

| (43) 公表日      | 平成13年8月14日(2001.8.14)        |

| (86) 國際出願番号   | PCT/US1998/001760            |

| (87) 國際公開番号   | W01998/036535                |

| (87) 國際公開日    | 平成10年8月20日(1998.8.20)        |

| 審査請求日         | 平成17年1月6日(2005.1.6)          |

| (31) 優先権主張番号  | 60/038,025                   |

| (32) 優先日      | 平成9年2月14日(1997.2.14)         |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 08/992,921                   |

| (32) 優先日      | 平成9年12月18日(1997.12.18)       |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンノイバール、<br>ピィ・オウ・ボックス・3453、ワン<br>・エイ・エム・ディ・プレイス、メイル<br>・トップ・68(番地なし) |

| (74) 代理人  | 弁理士 深見 久郎                                                                                                                             |

| (74) 代理人  | 弁理士 森田 俊雄                                                                                                                             |

| (74) 代理人  | 弁理士 伊藤 英彦                                                                                                                             |

最終頁に続く

(54) 【発明の名称】共有媒体アクセス制御回路を有する統合マルチポートスイッチ

## (57) 【特許請求の範囲】

## 【請求項 1】

データネットワークとインターフェースして前記データネットワークに結合された複数のリモートステーション間のデータ通信を可能にするための統合マルチポートワクスイッチであって、前記スイッチは、

前記データネットワークにデータフレームを送信し前記データネットワークからデータフレームの受信を行なうための複数のポートと、

前記ポートの各々でのデータフレームの流れを制御するための媒体アクセス制御(MAC)回路とを含む、論理チップを有し、前記MAC回路は前記ポートの各々に時分割形式で共通に結合され、前記MAC回路が媒体アクセス機能を実行するための論理回路手段と、前記複数のポートの媒体アクセスステートをストアするためのストートメモリ手段とを含み、前記論理チップはさらに、

それぞれのポートでネットワークから受信されたデータフレームを一時的に保持するための各ポートでの少なくとも1つの入力受信先入れ先出し(FIFO)バッファと、

それぞれのポートでネットワークに送信すべきデータフレームを一時的に保持するための各ポートの少なくとも1つの送信FIFOバッファとを含み、前記FIFOバッファの各々が前記論理回路手段に結合される、統合マルチポートネットワクスイッチ。

## 【請求項 2】

前記MAC回路が前記チップの中央に位置づけられた、請求項1に記載の統合マルチポートネットワクスイッチ。

10

20

**【請求項 3】**

前記媒体アクセス制御機能が、データ送信、データ受信、およびデータ衝突調停を含み、前記FIFOバッファの各々が前記論理回路手段に結合される、請求項1に記載の統合マルチポートネットワークスイッチ。

**【請求項 4】**

前記スイッチがそれぞれのリモートネットワークステーションに対応する複数のスイッチトランシーバを含み、前記チップはさらに、

前記論理回路手段と前記複数のスイッチトランシーバとの間に結合された時分割多重化／非多重化トランシーバインターフェースを含む、請求項1に記載の統合マルチポートネットワークスイッチ。 10

**【請求項 5】**

前記スイッチトランシーバのうち少なくとも1つが、複数の前記リモートステーションに対するデータ通信を時分割共有するための多重化／非多重化手段を含む、請求項4に記載の統合マルチポートネットワークスイッチ。

**【請求項 6】**

前記ステートメモリ手段が、

前記ポートの各々の現在のステートを表わすデータにそれぞれ割当てられた部分を有するデータ記憶部と、

前記データ記憶部に結合されてそこから前記ポートの第1に指定されたもののステートを表わすストアされたデータを受信するための出力レジスタと、前記出力レジスタは前記論理回路手段に結合されてそこへデータを出力し。 20

前記論理回路手段に結合されてそこから前記ポートの第2に指定されたもののステートを表わすデータを受信するための入力レジスタと、前記入力レジスタは前記データ記憶部に結合されてそこへデータを入力し、

順次的な、クロック動作されたステージによって前記データ記憶部にアクセスするためのアクセス手段とを含む、統合マルチポートネットワークスイッチ。

**【請求項 7】**

前記データ記憶部がスイッチポートアドレスによって特定され、前記アクセス手段が、クロック信号に応答し、前記出力レジスタに結合されて、対応のデータ記憶部からデータが取出されるべきポートアドレスをそこに順次的に供給するためのカウンタと。 30

前記カウンタと前記入力レジスタとの間に接続されて前記カウンタが供給したポートアドレスをそこへ与えるのを少なくとも1つのクロックステージだけ遅らせるための遅延手段とを含み、

それによってカウンタが供給したポートアドレスについての更新された媒体アクセスステートデータが前記論理回路手段から受信され、対応するデータ記憶部へと与えられる、請求項6に記載の統合マルチポートネットワークスイッチ。

**【請求項 8】**

前記論理回路手段が、前記出力レジスタからデータを受信するための第1の入力と、前記トランシーバインターフェースからデータを受信するための第2の入力とを有するレジスタを含む、請求項7に記載の統合マルチポートネットワークスイッチ。 40

**【請求項 9】**

データネットワークに結合されたマルチポート統合ネットワークスイッチの複数のポートでの媒体アクセスを制御して、前記データネットワークに接続された複数のリモートステーション間のデータ通信を可能にするための方法であって、

共通のデータ記憶ステートメモリ手段から各々のポートの各々のアクセスステートを順次読み出すステップと、

前記順次読み出すステップの各々について、前記ポートに結合されたトランシーバインターフェースから受信されたデータに応答して対応するポートでデータ通信アクセス機能を実行するステップと、

前記実行するステップの各々について、前記共通のデータ記憶ステートメモリを更新する 50

ステップとを含み、

前記順次読出すステップが、

クロック動作したカウンタの出力に応答して前記共通のデータ記憶ステートメモリのアドレス指定をするステップを含み、前記更新するステップが、

前記クロック動作したカウンタの出力を遅延させるステップと、

前記遅延されたクロック動作したカウンタの出力に応答して前記共通のデータ記憶ステートメモリのアドレスを指定するステップと、

ステートメモリの前記アドレス指定するステップにおけるアドレスのメモリに前記新規ステートデータを書込むステップとを含み、

前記実行するステップが、前記読み出すステップで読み出されたデータおよび前記インターフェースから受信されたデータを前記ポートのすべてに共通する論理回路で処理するステップを含み、

前記共通の論理回路において、前記ポートについて新規ステートデータを生成するステップを含む、方法。

【請求項 10】

前記実行するステップが、前記ポートの送信バッファにストアされたデータをデータネットワークへ送信するステップを含む、請求項 9 に記載の方法。

【請求項 11】

前記実行するステップが、前記ポートの受信バッファで前記ネットワークからデータを受信するステップを含む、請求項 9 に記載の方法。

【請求項 12】

前記実行するステップが前記ポートでデータ衝突を調停するステップを含む、請求項 9 に記載の方法。

【発明の詳細な説明】

技術分野

この発明はネットワークスイッチングに関し、より特定的には、データネットワークスイッチ論理チップにおける共有マルチポート媒体アクセス制御に関する。

背景技術

データネットワークスイッチは、ローカルエリアネットワーク内の複数のメディアステーション間のデータ通信を可能にする。データフレーム、またはパケットは、各スイッチポートでネットワークインターフェースカードまたは回路を可能化するデータネットワークスイッチ媒体アクセス制御 (MAC) によってステーション間で転送される。MAC は、ポートからネットワークへのデータトラヒック送信とポートにおけるネットワークからのデータトラヒックの受信を管理し、衝突を回避するためにポートでのデータトラヒックを調停する。ネットワークスイッチは送信ステーションから受けたデータフレームを、受信データフレームのヘッダ情報に基づいて宛先ステーションへ伝達する。各ポートの送信および受信バッファが MAC に結合される。動作モードによって、一時的にポート受信バッファに保持される入力パケットは、後からの送信のためにスイッチ外部のメモリへ移動されることもあり、またはネットワークへすぐに送信するために適切なポートの送信バッファに配されてもよい。

パケット送信イベントは、典型的には、各データネットワークスイッチポートに関するネットワーク動作の統計的分析の基礎を提供するために追跡される。たとえば送信パケット、受信パケット、および送信衝突の数などは、定期的に計数されて集計される。統計カウンタを用いることによって、たとえばパケット損失などの不適切な装置動作の判定がなされ得る。典型的には、各 MAC ユニットは、それぞれのスイッチポートを通過する各フレームについての少数の送信イベントパラメータを計数するための、容量が制限された内部カウンタを有する、受信ステートマシンおよび送信ステートマシンを含み得る。特定のパラメータ専用のフリップフロップが、そのフレーム内の項目が識別されるたびにそれぞれ増分される。各入力フレームに関しては、これらは受信 FIFO バッファ内に一時的にストアされてもいいが、受信ステートマシンのそれぞれのフリップフロップが読み出され、そ

10

20

30

40

50

の結果生じるデータがフレームに添付される。出力フレームについても、同様の処理が行なわれる。こうして、送信 FIFO バッファに一時的にストアされた出力フレームは、受信動作および送信動作に関する添付データを含む。送信動作データは、フレームが送信 FIFO バッファから送信されるときに付加される。

データネットワークがよりロバストになりデータトラヒックが増すにつれて、付加的な動作パラメータが重要になる。より多数のパラメータを追跡するには、たとえば、より多くのレジスタ、サポートのための論理素子、およびより大きなバッファの容量を提供するなど、MAC をますます複雑にする必要がある。各 MAC に対するこれらの付加的要素をスイッチ論理チップ上に集積すると、チップアーキテクチャに負担がかかる。スイッチの発達によりトラヒックフローの容量も大きくなり、スイッチポートの数が増えるので、チップアーキテクチャを効率よく用いることはより一層重大な問題となる。10

EP-A-0603443 は、トーカンリングローカルエリアネットワークを相互接続させるためのブリッジを開示する。これは、ポート毎に設けられていた MAC を集中型プロセッサ内部の集中機能によって置き換えるという「共有 MAC」の概念を開示する。

EP-A-0603444 は、EP-A-0603443 と同様の開示を示し、これは各々がトーカンリング物理セグメントに接続されている N 個のポートを有するスイッチに関するものである。

#### 発明の開示

この発明は、各ポートに対する特定の MAC 機能が、従来の態様で各ポートに個別には設けられる必要のない回路によって実行可能であると認識することによって、上述の要求および決定に部分的に取組む。この発明の利点は、複数のスイッチポートについて同様の機能を実行するために 1 つの組合せ論理およびレジスタ配置が提供されることである。この利点は、共通回路の機能性がいかなる所与の時刻においてもそれぞれのポートと正確に対応づけられ得る場合、同様の回路を各ポートに別個に設けることは、冗長かつ不需要になるという認識に部分的に基づく。20

この発明のさらなる利点は、複数のスイッチポートの各々での現在のアクセスステートが单一のステート記憶場所で維持され、それによって、格納されたポート MAC のステートのアクセスおよびその更新が簡単になるという点である。この発明のまた別の利点は、单一の共通組合せ論理およびレジスタ配置にしたがってステート記憶部へアクセスすることにより、複数のポートの各々に対する MAC 機能の実行が時分割という形で可能化されるという点である。この発明はしたがって、先行技術の従来の装置と比べてより効率的なチップリソースおよびアーキテクチャスペースの使用を提供する。30

この発明のさらなる利点は、次の詳細な説明から当業者には容易に明らかになるであろう。詳細な説明にはこの発明の好ましい実施例のみが図示および記述され、これはこの発明を実施するのに企図された最良の態様を表わすために過ぎない。後にわかるように、この発明は、この発明から全く離れることなく、他の異なる実施例が可能であり、またそれらの詳細部分は種々の明らかな点においていくらか修正することもできる。したがって、図面および説明は例示的な性質のものとしてみなされるべきであり、限定的なものではない。

#### 【図面の簡単な説明】

添付の図面を参照して、同じ参照番号で指定される要素は全図面を通して同様の要素を示す。

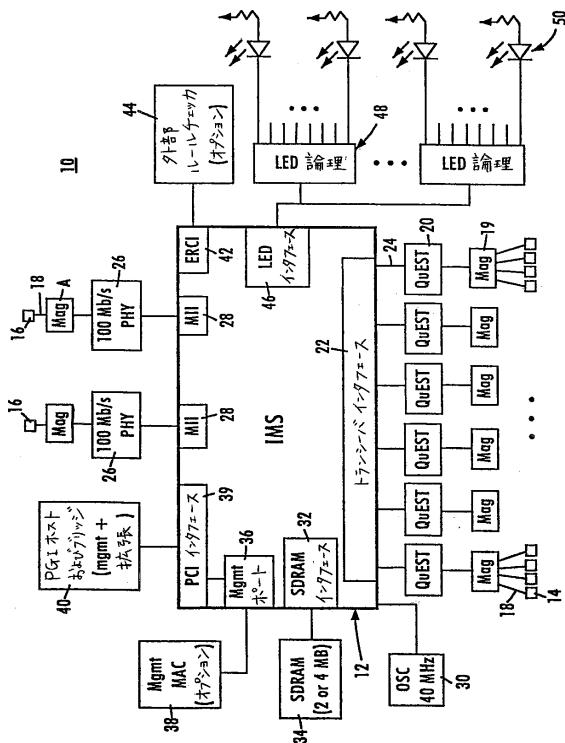

図 1 は、この発明のパケット交換システム環境のブロック図である。

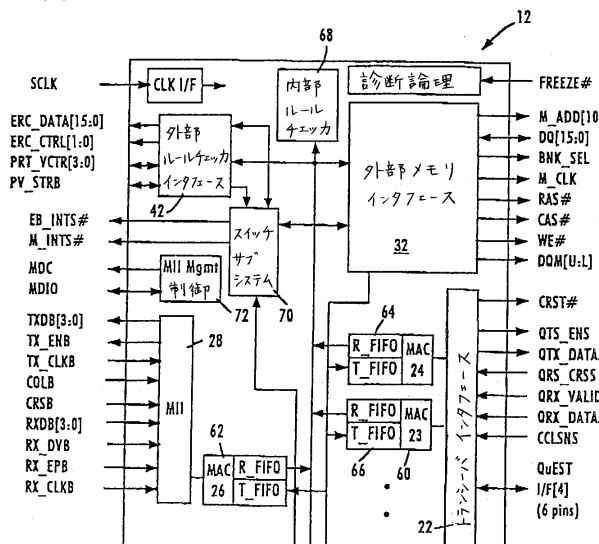

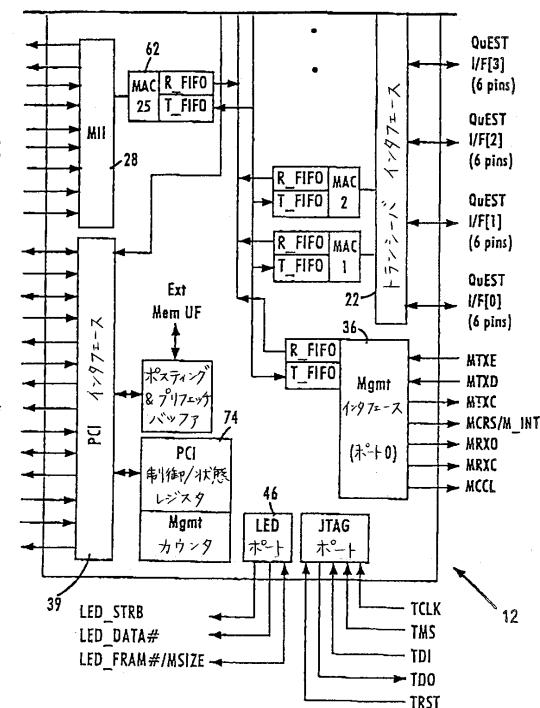

図 2 は、図 1 のパケット交換システムで用いられ得る、この発明に関するマルチポートスイッチのブロック図である。

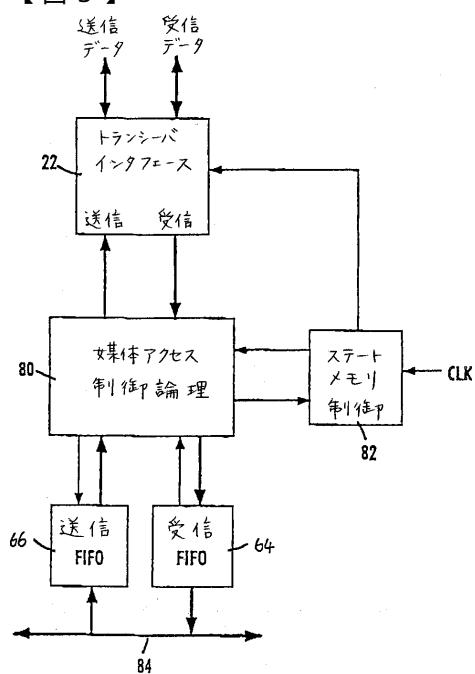

図 3 は、この発明に従った媒体アクセス制御を表わすブロック図である。

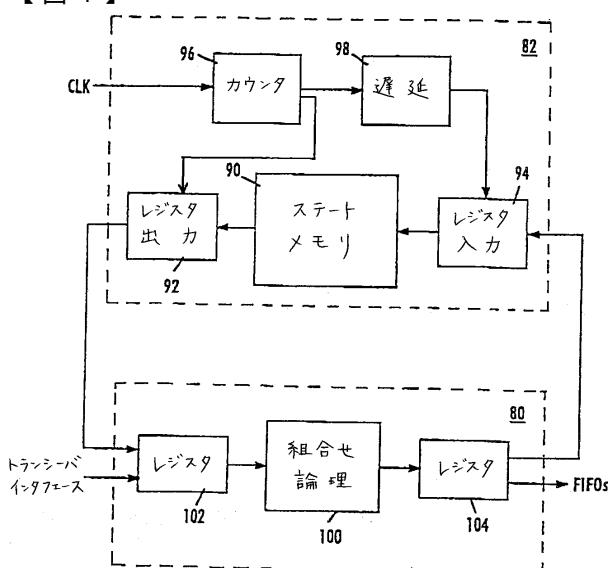

図 4 は、この発明の媒体アクセス制御論理ユニット 80 およびステートメモリ制御ユニット 82 の好ましい配置の、より詳細なブロック図である。

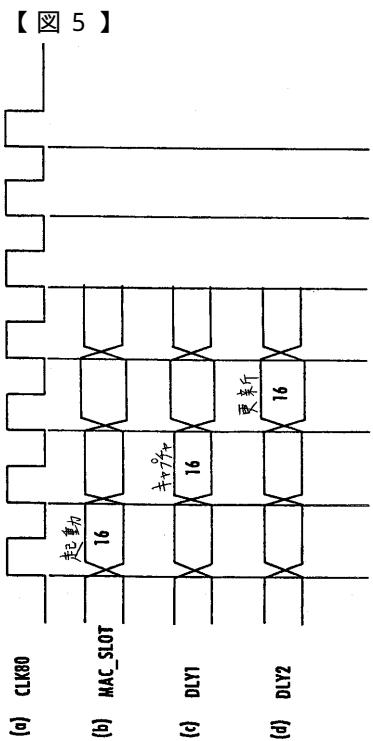

図 5 は、この発明に従ったステージに分割されたパイプライン動作を表わす波形図である。

。

10

20

30

40

50

### 発明を実施するための最良の様態

イーサネット(IEEE 802.3)網などのパケット交換ネットワークにおけるスイッチを例に挙げてこの発明を説明する。以下の詳細な説明から、この発明は他のパケット交換システムにも適用可能であることが明らかとなるであろう。図1は、この発明の環境を提供するパケット交換システム10のブロック図である。パケット交換ネットワークは、ネットワークステーション間でのデータパケットの通信を可能にする統合マルチポートスイッチ(IMS)12を含む。ネットワークステーションは種々の構成を有し得る。現在の例では、24個の毎秒10メガビットの速度(Mb/s)のネットワークステーション14は10Mb/sのネットワークデータレートでデータの授受を行ない、2つの100Mb/sネットワークステーション16は100Mb/sのネットワーク速度でデータパケットの授受を行なう。マルチポートスイッチ12はネットワークステーション14または16から受けたデータパケットをイーサネットプロトコルに基づく適切な宛先に選択的に転送する。

10Mb/sネットワークステーション14は媒体18を介して、かつ半二重イーサネットプロトコルに従って、マルチポートスイッチ12に対してデータパケットの授受を行なう。イーサネットプロトコルISO/IEC 8802-3(ANSI/IEEE Std. 802.3, 1993 Ed.)は、すべてのステーション14が等しくネットワークチャネルにアクセスできるようにする半二重媒体アクセス機構を規定する。半二重環境のトラヒックは媒体18と区別されたりまたはそれより優先されることはない。各ステーション14はむしろ、媒体上のトラヒックを認識するために搬送波感知多重アクセス/衝突検出(CSMA/CD)を用いるイーサネットインターフェースカードを含む。媒体上の受信搬送波がデアサートされたことを感知することによりネットワークトラヒックの不在が検出される。送信するデータを有するステーション14はすべて、パケット間ギャップ期間(IPG)として公知である、媒体上の受信搬送波がデアサートされた後、予め定められた時間だけ待機することにより、チャネルにアクセスしようとする。複数のステーション14がネットワーク上に送信するデータを有する場合、ステーションの各々が、媒体上の受信搬送波の、デアサートが感知されたことに応答してIPG期間の後に送信を行なうとするため、衝突が生じる。したがって、送信ステーションは、別のステーションが同時にデータを送信することにより衝突が生じていないかを判断するために媒体を監視する。衝突が検出されれば、両方のステーションが停止し、ランダムな期間だけ待機し、再度送信を試みる。

100Mb/sネットワークステーション16は好ましくは、提案されているフロー制御によるイーサネット規格IEEE 802.3×全二重-草案(0.3)に従う全二重モードで動作する。全二重環境は各100Mb/sネットワークステーション16とマルチポートスイッチ12との間に双方向ポイントツーポイント通信リンクを設け、IMSおよびそれぞれのステーション16は衝突することなくデータパケットの送受信を同時に行なうことができる。100M/b/sネットワークステーション16の各々は、登録商標100ベース-TX、100ベース-T4または100ベース-FXとして公知のタイプの100Mb/s物理(PHY)装置26を介してネットワーク媒体18に結合される。マルチポートスイッチ12は、物理装置26への接続をもたらす媒体独立インターフェース(MII)28を含む。100Mb/sネットワークステーション16は他のネットワークへの接続のためのサーバまたはルータとして実現され得る。同様に、10Mb/sネットワークステーション14はフロー制御による全二重プロトコルに従って動作するように修正され得る。

図1に示されるように、パケット交換システム10は、マルチポートスイッチ12と10Mb/sステーション14との間で送信されたデータパケットの時分割多重化および時分割非多重化を行なう、QUESTとラベル付けされた一連のスイッチトランシーバ20を含む。磁気トランスモジュール19は媒体18上の信号の波形を維持する。マルチポートスイッチ12は、時分割多重化プロトコルを用いて单一のシリアルノンリターンツーゼロ(NRZ)インターフェース線24を介して各スイッチトランシーバ20に対するデータパ

ケットの送受信を行なうトランシーバインターフェース 18 を含む。スイッチトランシーバ 20 はシリアル N R Z インタフェース線 24 からパケットを受信し、受信されたパケットを非多重化し、ネットワーク媒体 18 を介して適切なエンドステーション 14 にそのパケットを出力する。開示される実施例によると、各スイッチトランシーバ 20 は独立した 4 つの 10 Mb / s ツイストペアポートを有し、マルチポートスイッチ 12 が必要とする PIN の数が 4 分の 1 に減少するようにするシリアル N R Z インタフェースを介する 4 : 1 多重化を用いる。

マルチポートスイッチ 12 は、意思決定エンジン、切換エンジン、バッファメモリインターフェース、構成 / 制御 / 状態レジスタ、管理カウンタ、ならびにネットワークステーション 14 および 16 のためのイーサネットポート間でデータパケットの経路制御を行なうための MAC ( 媒体アクセス制御 ) プロトコルインターフェースを含む。マルチポートスイッチ 12 はまた、インテリジェントな切換決定を行ない、後に説明するように、外部の管理エンティティに管理情報ベース ( MIB ) オブジェクトの形式で統計的なネットワーク情報を与えるための優れた機能を有する。マルチポートスイッチ 12 はさらに、マルチポートスイッチ 12 のチップサイズを最小にするためにパケットデータの外部ストアおよびスイッチ論理を可能にするインターフェースを含む。たとえば、マルチポートスイッチ 12 は、受信したフレームデータ、メモリ構造および MIB カウンタ情報をストアするための外部メモリ 34 へのアクセスをもたらす同期型ダイナミック RAM ( SDRAM ) インタフェース 32 を含む。メモリ 34 は 2 Mb または 4 Mb のメモリサイズを有する 80 、 100 または 120 MHz 同期型 DRAM であってもよい。

管理ポート 36 は、外部管理エンティティが管理 MAC インタフェース 38 によってマルチポートスイッチ 12 の全体的な動作を制御できるようにする。PCI インタフェース 39 は、PCI ホストおよびブリッジ 40 を介して管理エンティティがアクセスできるようになる。これに代えて、PCI ホストおよびブリッジ 40 が複数の IMS デバイスに対する拡張バスとしての役割を果たしてもよい。

スイッチ 12 に含まれる内部意思決定エンジンは、1 つのソースから少なくとも 1 つの宛先ステーションに受信されたデータパケットを選択的に送信する。内部意思決定エンジンには外部ルールチェッカが代用されてもよい。外部ルールチェッカインターフェース ( ERCI ) 42 は、内部意思決定エンジンの代わりにフレーム転送決定を行なうために外部ルールチェッカ 44 が用いられるようになる。したがって、フレーム転送決定は、内部切換エンジンまたは外部ルールチェッカ 44 のいずれかによって行なわれ得る。

LED インタフェース 46 は、ポートごとのステータスをクロックに合せて出力し LED 外部論理 48 を駆動する。LED 外部論理 48 は人間が読取ることができる LED ディスプレイエレメント 50 を駆動する。発振器 30 はマルチポートスイッチ 12 のシステム機能に 40 MHz のクロック入力を与える。

図 2 は、図 1 のパケット交換システムにおいて用いられ得る、この発明に関連するマルチポートスイッチのより詳細なブロック図である。マルチポートスイッチ 12 はそれぞれの 10 Mb / s ネットワークステーション 14 間で半二重のデータパケットの送受信を行なうための 24 個の 10 Mb / s 媒体アクセス制御 ( MAC ) ポート 60 ( ポート 1 から 24 ) と、それぞれの 100 Mb / s ネットワークステーション 16 間で全二重のデータパケットの送受信を行なうための 2 つの 100 M / bps MAC ポート 62 ( ポート 25 および 26 ) とを含む。上述のとおり、管理インターフェース 36 もまた MAC 層プロトコル ( ポート 0 ) に従って動作する。

MAC ポート 60 、 62 および 36 の各々は、データ送信、データ受信、およびポートでの衝突調停の制御を可能にする、従来の論理およびレジスタアクセス制御回路を含む。受信先入れ先出し ( FIFO ) バッファ 64 および送信 FIFO 66 もまた、各ポートに設けられる。外部メモリインターフェース 32 は一つの共有バスによって MAC 受信 FIFO バッファの各々に接続され、また別の共有バスによって MAC 送信 FIFO バッファの各々に接続される。

ネットワークステーションからのデータパケットは対応の MAC ポートで受信され、対応

10

20

30

40

50

の受信 FIFO バッファ 64 にストアされる。受信されたデータパケットは対応の受信 FIFO バッファ 64 から外部メモリインタフェース 32 に出力されて、外部メモリ 34 にストアされる。

受信されたパケットのヘッダもまた、内部ルールチェックカ 68 および外部ルールチェックカ インタフェース 42 を含む、意思決定エンジンに転送され、いずれの MAC ポートからデータパケットが出力されるかが決定される。パケットヘッダが、内部ルールチェックカ 58 または外部ルールチェックカインタフェース 40 のいずれに送られるかは、マルチポートスイッチ 12 の動作の構成による。外部ルールチェックカ 44 を使用することにより、容量の増加、およびフレームが外部メモリに完全にバッファされる前にフレーム転送決定を可能にし、かつマルチポートスイッチ 12 がフレームを受信する順からは独立した順で決定が行なわれるようとする、決定キュー内でのランダムな順序付け、といった利点がもたらされる。

内部ルールチェックカ 68 および外部ルールチェックカ 44 は、所与のデータパケットに関する宛先 MAC ポートを決定するための意思決定論理を提供する。意思決定エンジンは、単一ポート、複数ポートまたは全ポート（すなわちブロードキャスト）のいずれかに所与のデータパケットを出力し得る。各データパケットにはソースおよび宛先アドレスを有するヘッダが含まれ、意思決定エンジンは宛先アドレスに基づいて適切な出力 MAC ポートを特定できる。宛先アドレスは、意思決定エンジンが複数のネットワークステーションの出力ポートに対応するものと特定するバーチャルアドレスに対応してもよい。これに代えて、受信されたデータパケットは、(100Mb/s ステーション 16 のうちの 1 つのルータを介する) 別のネットワークまたは所定のグループのステーションを特定する IEEE 802.1d プロトコルに準拠する VLAN (バーチャル LAN) タグ付フレームを含んでもよい。したがって、内部ルールチェックカ 68 または外部ルールチェックカ 44 のいずれかがインタフェース 42 を介して、バッファメモリ 34 に一時的にストアされたフレームが单一の MAC ポートまたは複数の MAC ポートに出力されるべきかを決定する。

意思決定エンジンは、データパケットを受信すべき各 MAC ポートを特定するポートベクタの形式で転送決定をスイッチサブシステム 70 に出力する。適切なルールチェックカからのポートベクタは、外部メモリ 34 にデータパケットをストアするアドレス場所と、データパケットを受信して送信するための MAC ポート（たとえば MAC ポート 0 から 26）の識別子とを含む。スイッチサブシステム 70 はポートベクタに特定されたデータパケットを外部メモリインタフェース 32 を介して外部メモリ 34 から取出し、取出されたデータパケットを特定されたポートの適切な送信 FIFO 66 に与える。

付加的なインタフェースにより、次の要素で例示される管理および制御情報が与えられる。管理データインターフェース 72 は、MII 管理仕様 (IEEE 802.3u) に従うスイッチトランシーバ 20 および 100M/b/s 物理装置 26 と制御およびステータス情報をマルチポートスイッチ 12 が交換できるようにする。管理データインターフェース 72 は、双方向管理データ I/O (MDIO) 信号経路に時間基準を与える管理データクロック (MDC) を出力する。PCI インタフェース 39 は、PCI ホストプロセッサ 40 によって内部IMS ステータスおよび構成レジスタ 74 にアクセスし、かつ外部メモリ SDR AM 34 にアクセスするための、32 ビット PCI 改訂 2.1 に適合したスレーブインターフェースである。PCI インタフェース 39 は複数の IMS デバイスのための拡張バスとしての役割も果たし得る。管理ポート 36 は標準 7 ワイヤ反転シリアル GPSI インタフェースを介して外部 MAC エンジンにインタフェースされ、標準 MAC 層プロトコルによりホストコントローラがスイッチ 12 にアクセスできるようにする。

図 3 はこの発明に従った図 1 のシステムの媒体アクセス制御を表わすブロック図である。図 2 に示す配置とは対照的に、単一の媒体アクセス制御論理ユニット 80 が設けられ、24 個の 10Mb/s スイッチポート 60 および MII 管理制御ポートに共通して用いられる。ユニット 80 は送信接続および受信接続によってトランシーバインターフェース 22 に結合される。ユニット 80 はまた、各ポート 60 で送信 FIFO 66 および受信 FIFO 64 にも接続される。ポート FIFO は簡明のため 1 対のみが図示されるが、これは当

10

20

30

40

50

然ながら、すべてのポート 60 の対応する FIFO を表わす。FIFO 64 および FIFO 66 はバス 84 に接続される。バス 84 は 1 本線で示されるが、これはすべてのポート 60 の受信 FIFO および外部メモリインターフェース 32 間の共通受信バス接続と、すべてのポート 60 の送信 FIFO および外部メモリインターフェース 32 間の共通送信バス接続とを表わしている。

ステートメモリ制御ユニット 82 はポート 60 の各々の媒体アクセスのステートをストアする。ユニット 82 はユニット媒体アクセス制御論理ユニット 80 に接続されてその間でステートデータを転送する。データ通信はまた、ステートメモリ制御ユニット 82 とトランシーバインターフェース 22との間に存在する。ステートメモリ制御ユニット 82 は 80 MHz 信号を受信するためのクロック入力を有する。以下により詳しく説明するように、クロック信号は 24 個のスイッチポート 60 の各々について論理ユニット 80 が果たす時分割共有された媒体アクセス制御の機能性に同期のタイミングを与える。

図 4 は図 3 の媒体アクセス制御論理ユニット 80 およびステートメモリ制御ユニット 82 の好ましい構成をより詳細に表わすブロック図である。ステートメモリ制御ユニット 82 は、ステートメモリ 90 と、出力レジスタ 92 と、入力レジスタ 94 と、カウンタ 96 と、遅延回路 98 とを含む。ポート 60 の各々でのアクセスステートをストアするステートメモリ 90 は、たとえば、ランダムアクセスメモリ (RAM) によって、または各ポート 60 専用の 1 つ以上のレジスタによって、具体化され得る。出力レジスタ 92 および入力レジスタ 94 はステートメモリ 90 にそれぞれ接続されて、ステートメモリに対してデータを受信または入力する。80 MHz クロックソースからの入力を有するカウンタ 96 は、ポート 60 の各々を一意に識別するのに十分なビット数を有するデータ信号を出力する。図 1 の 25 のポート実施例に関しては、カウンタ出力信号は好ましくは 5 ビットの長さである。この信号の値は受信したクロック信号パルスの各々により増分される。

カウンタ出力信号は出力レジスタ 92 に与えられ、それによってステートメモリ 90 からステートメモリデータにアクセスすべきポートを特定する。カウンタ出力信号はまた遅延回路 98 にも与えられ、これは信号を保持し複数のクロックステージの間遅延させる。遅延回路 98 の出力は入力レジスタ 94 に与えられ、それによってデータをステートメモリ 90 内にストアすべきポートを特定する。したがって、所与のポートにストアされたデータの取出しとそのポートへの新規なデータの書き込みとの間の時間は、遅延回路 98 によって遅延されたクロックステージの数に依存する。この数は媒体アクセス制御論理ユニット 80 が必要とするクロックパイプラインステージの数に従って定められる。レジスタ、カウンタおよび遅延回路は各々、従来の周知の要素である。

媒体アクセス制御機能およびアクセスステートの表示は、複数の論理ゲートを含む組合せ論理ユニット 100 で処理される。レジスタ 102 は、ステート出力レジスタ 92 およびトランシーバインターフェース 22 から得たデータを論理ユニットへ入力するように接続される。レジスタ 102 から受信されたデータの処理後、論理ユニットは処理済データをレジスタ 104 へと出力する。この処理済データは、関連のポートの FIFO へ送信されるべき命令と、転送すべき通信データすべてと、もしあればポートアクセスステートの変更とを含み、後者はステート入力レジスタ 94 へと送信される。レジスタ 102 へのデータの入力、レジスタ 102 から論理ユニット 100 へのデータ送信および処理、レジスタ 104 からステート入力レジスタ 94 への処理済データの転送、およびステートメモリ 90 の更新は、クロック動作するパイプラインステージで連続的に起こる。

図 5 はステージに分割されたパイプライン動作を表わす波形図である。好ましい実施例では、遅延回路 98 は 2 つの遅延ステージを含む。波形 (a) は 80 MHz クロック信号を表わす。波形 (b) は、波形 (a) のクロック信号の各サイクル中のカウンタ 96 の出力を表わす。この信号は MAC ポートを特定し、各クロック信号によって増分され、これによって順次的な時分割共有動作を確立する。各クロックサイクルはしたがってカウンタによって特定されたポートに対応する「MAC スロット」を規定する。たとえば、第 1 のクロックサイクル中にカウンタ出力によって特定された MAC スロットはスロット 16 である。波形 (c) および (d) は各クロック信号サイクル中 2 つの遅延ステージに対する M

10

20

30

40

50

A C スロットの特定を表わす。したがって、M A C スロット 1 6 は第 2 のクロックサイクル中は波形 ( c ) で示され、第 3 のクロックサイクル中は波形 ( d ) で示される。

波形 ( b ) から ( c ) の各々は媒体アクセス制御のアクティビティの 3 つのステージ ( 図には概略のラベルで「起動」、「キャプチャ」および「更新」と示される ) のうち 1 つに対応し、よってそのアクティビティが関連する M A C ポートを特定する。これらの 3 つのアクティビティは、各クロックサイクル中にそれぞれ異なる M A C ポートに対して同時に動作する。図面は M A C ポート 1 6 に関する動作の 3 つのステージを表わす。このポートの起動ステージは先頭に図示されたクロックサイクル中に起こる。このサイクルの間、カウンタは、データがステートメモリ 9 0 からアクセスされ、レジスタ 9 2 に保持されるポート 1 6 を特定する。次のクロックサイクルの間には、M A C ポート 1 6 のキャプチャステージが起こる。このとき、レジスタ 9 2 およびトランシーバインターフェースからのデータはレジスタ 8 0 へ入力されて組合せ論理ユニット 1 0 0 によって処理され、その結果生じるデータはレジスタ 1 0 4 に保持される。また、このサイクル中には、カウンタは起動ステージ動作に関する次の M A C ポートも特定しているであろう。その後のクロックサイクルの間に、M A C ポート 1 6 の更新ステージが起こる。レジスタ 1 0 4 からのステート更新データは入力レジスタ 9 4 へと転送され、ステートメモリ 9 0 内にストアされる。演算データは適切な F I F O へと転送される。媒体アクセス制御はこの態様で各 M A C ポートについて連続して行なわれる。

この発明は従って、チップアーキテクチャを保存しつつ効率のよい媒体アクセス制御を提供するという効果を奏する。この開示には、発明の好ましい実施例のみが図示および記述され、そのさまざまな用例は少ししか示されていない。当然ながら、この発明は他の種々の組合せおよび環境において使用可能であり、またここに述べた発明の概念の範囲内での変更または修正が可能である。

10

20

【図 1】

【図 2】

Fig. 2

Fig. 1

【図2A】

Fig. 2A

【 図 2 B 】

Fig. 2B

( 3 )

Fig. 3

( 四 )

Fig. 4

Fig. 5

---

フロントページの続き

(74)代理人

弁理士 堀井 豊

(72)発明者 ルナルデュー, トーマス・ジェファーソン

アメリカ合衆国、95117 カリフォルニア州、サン・ノゼ、ブラックフォード・アベニュー、3

701

(72)発明者 チョウ, ピーター・カ - ファイ

アメリカ合衆国、95131 カリフォルニア州、サン・ノゼ、マックスウェル・ウェイ、141

6

(72)発明者 ビスワナス, ゾムナス

アメリカ合衆国、94086 カリフォルニア州、サニイベイル、サウス・フェア・オーツ・ア

ベニュー、655、エイチ・112

審査官 矢頭 尚之

(56)参考文献 特開平07-074782(JP, A)

特開平04-233352(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/28