(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7689428号

(P7689428)

(45)発行日 令和7年6月6日(2025.6.6)

(24)登録日 令和7年5月29日(2025.5.29)

|                         |                 |

|-------------------------|-----------------|

| (51)国際特許分類              | F I             |

| H 1 0 D 30/60 (2025.01) | H 1 0 D 30/60 K |

| H 1 0 D 89/60 (2025.01) | H 1 0 D 89/60   |

| H 1 0 D 8/50 (2025.01)  | H 1 0 D 30/60 G |

|                         | H 1 0 D 30/60 S |

|                         | H 1 0 D 8/50 L  |

請求項の数 5 (全9頁)

|          |                             |          |                                    |

|----------|-----------------------------|----------|------------------------------------|

| (21)出願番号 | 特願2021-9959(P2021-9959)     | (73)特許権者 | 715010864                          |

| (22)出願日  | 令和3年1月26日(2021.1.26)        |          | エイブリック株式会社                         |

| (65)公開番号 | 特開2022-113931(P2022-113931) |          | 長野県北佐久郡御代田町大字御代田 4 1               |

|          | A)                          |          | 0 6 番地 7 3                         |

| (43)公開日  | 令和4年8月5日(2022.8.5)          | (72)発明者  | 鷹巣 博昭                              |

| 審査請求日    | 令和5年12月5日(2023.12.5)        |          | 東京都港区三田三丁目 9 番 6 号 エイブ<br>リック株式会社内 |

|          |                             | 審査官      | 大橋 達也                              |

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

MOSトランジスタのゲート電極及びソース領域が接地され、ドレイン領域が外部信号端子に接続されているオートランジスタを有する半導体装置において、

前記オートランジスタは、前記ドレイン領域及び前記ソース領域が接地電位のウェル領域に形成されており、前記ゲート電極がチャネル領域に加えて前記ドレイン領域の上方に延設され、

前記ゲート電極と前記ドレイン領域との間で形成される容量は、前記ゲート電極と前記ウェル領域及び前記ソース領域との間に生じる容量よりも大きいことを特徴とする半導体装置。

## 【請求項2】

前記ゲート電極は、前記ドレイン領域を覆う箇所に開口部が設けられている請求項1に記載の半導体装置。

## 【請求項3】

前記開口部を平面視した際の形状は、矩形状である請求項2に記載の半導体装置。

## 【請求項4】

前記開口部を平面視した際の形状は、矩形状の一部に凹部を有する請求項3に記載の半導体装置。

## 【請求項5】

前記開口部を平面視した際の形状が 状である請求項に記載の半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体装置に関する。

## 【背景技術】

## 【0002】

半導体装置には、静電気放電（Electro-Static Discharge：ESD）を代表とする様々なサージやノイズから内部素子を保護するために ESD 保護素子が設けられている場合がある。

## 【0003】

ESD 保護素子の例としては、独立して、あるいは、寄生的に形成されているダイオード素子、バイポーラ素子、サイリスタ素子などが挙げられる。これらの中でも、N型のMOS（Metal-Oxide-Semiconductor）トランジスタのドレインを外部端子に接続するとともにゲート及びソースを接地してオフ状態で使用する、いわゆる「オフトランジスタ」が良く知られている。このオフトランジスタは、静電気のサージが内部素子へ伝播することを防止し、サージを基板などへ逃がす機能を有する。

## 【0004】

このようなオフトランジスタにおいて、様々な提案がされている。たとえば、ESD 保護特性の改善を図ることを目的として、抵抗素子と容量素子が直列接続された RC タイマーが接続されているオフトランジスタが提案されている（例えば、特許文献 1 参照）。

10

## 【0005】

また、半導体装置の破壊に関わる静電気放電のモデルとして、サージの波形、エネルギー、時間などの観点で分類した、人体モデル（Human Body Model：HBM）及びデバイス帶電モデル（Charged Device Model：CDM）が良く知られている。

20

## 【0006】

HBM は、帯電した人間から半導体装置に放電するモデルであり、比較的大きなエネルギーを数 10 nsec ~ 数 100 nsec で半導体装置に放電する。

一方、CDM は、近年の製造工程の自動化により人間が半導体装置に触れる作業が減っていることから HBM よりも注目されている。この CDM は、帯電した半導体装置の端子から装置や治工具類などの金属部に接触して放電するモデルであり、比較的小さいエネルギー量ではあるが数 10 psec ~ 数 100 psec という極めて短い時間で半導体装置から放電する。

30

## 【0007】

このため、CDM では厳しい過渡現象が発生してしまい、オフトランジスタにおいてはゲート電極とドレイン領域との間に大きい電位差が生じると破壊に至る可能性がある。

## 【先行技術文献】

## 【特許文献】

## 【0008】

## 【文献】特開 2012-146899 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

40

## 【0009】

そこで、本発明の一つの側面では、オフトランジスタのゲート絶縁膜が静電破壊されにくい半導体装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0010】

本発明の一実施形態における半導体装置は、

MOS トランジスタのゲート電極及びソース領域が第 1 の電源端子又は第 2 の電源端子に接続され、ドレイン領域が外部信号端子に接続されているオフトランジスタを有する半導体装置において、

50

前記オフランジスタは、ゲート電極がチャネル領域に加えてドレイン領域の一部又は全部の上方に延設され、前記ドレイン領域と前記ドレイン領域の上方に延設されている前記ゲート電極との間に容量形成領域を備える。

【発明の効果】

【0011】

本発明の一つの側面によれば、オフランジスタのゲート絶縁膜が静電破壊されにくい半導体装置を提供することができる。

【図面の簡単な説明】

【0012】

【図1】図1は、第1の実施形態に係る半導体装置が有するオフランジスタを示す回路図である。

10

【図2】図2は、第1の実施形態に係るオフランジスタを示す概略平面図である。

【図3】図3は、図2で示したオフランジスタにおいてゲート電極を除いた際の概略平面図である。

【図4】図4は、図2で示したI-I線における概略断面図である。

【図5】図5は、第2の実施形態に係る半導体装置が有するオフランジスタを示す概略平面図である。

【図6】図6は、図5のII-II線における概略断面図である。

【発明を実施するための形態】

【0013】

20

以下、本発明の実施形態について、図面を参照しながら詳細に説明する。

【0014】

(第1の実施形態)

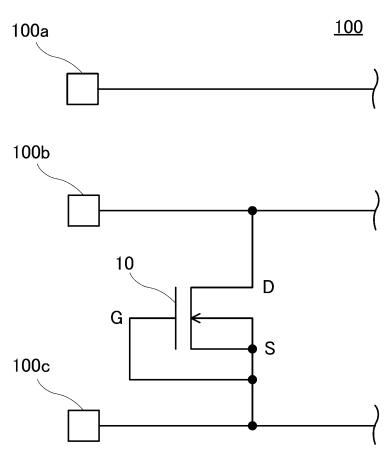

図1は、第1の実施形態に係る半導体装置が有するオフランジスタを示す回路図である。

図1に示すように、半導体装置100は、電源電位である第1の電源端子100aと、半導体装置100をオンオフする制御信号が入力される外部信号端子100bと、接地電位である第2の電源端子100cと、オフランジスタ10と、を有する。

なお、本実施形態では、外部信号端子100bに半導体装置100をオンオフする制御信号が入力されたとしたが、これに限ることなく、他の信号でもよい。

30

【0015】

オフランジスタ10は、本実施形態ではN型MOSトランジスタであり、ドレイン端子Dが外部信号端子100bに接続され、ゲート端子G及びソース端子Sが接地電位である第2の電源端子100cに接続されている。

【0016】

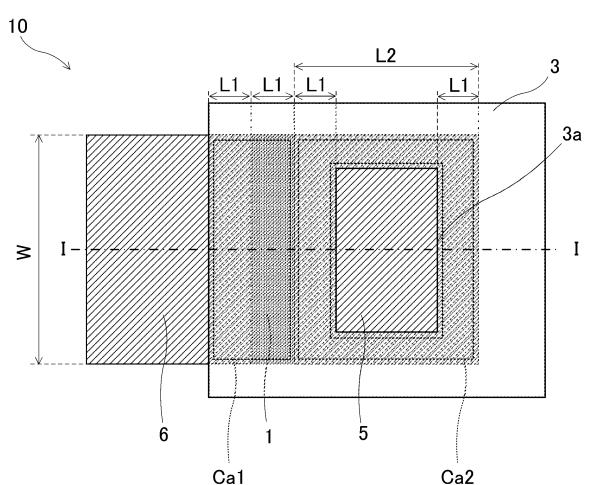

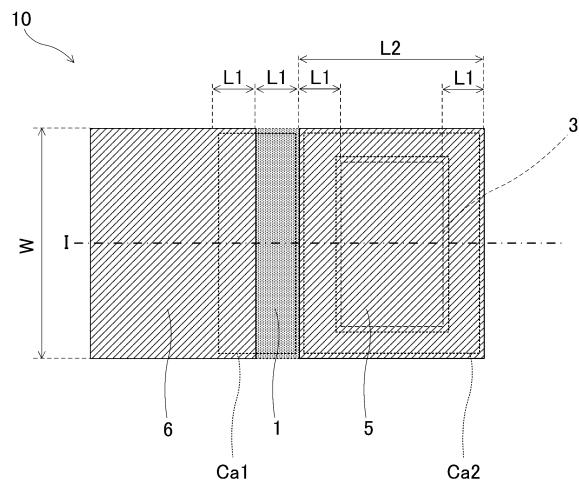

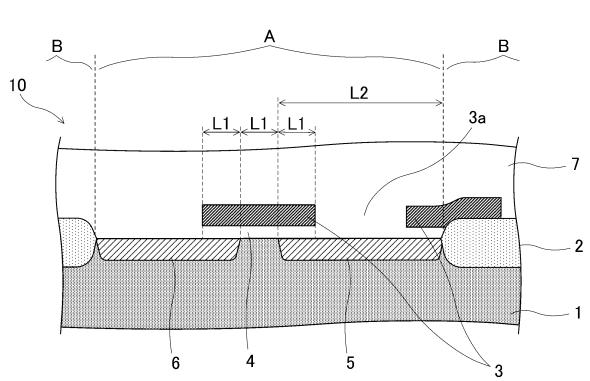

図2は、第1の実施形態に係るオフランジスタを示す概略平面図である。図3は、図2で示したオフランジスタにおいてゲート電極を除いた際の概略平面図である。図4は、図2で示したI-I線における概略断面図である。

なお、半導体装置としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、レギュレータ、センサ、メモリ、バッテリ制御等の機能を有する半導体装置などが挙げられる。

40

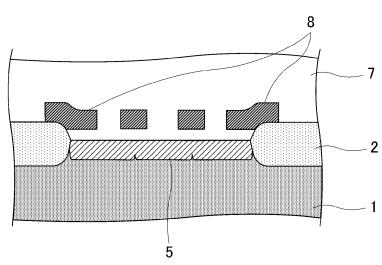

【0017】

図4に示すように、オフランジスタ10は、シリコン半導体基板の表面のアクティブ領域Aに形成されており、ウェル領域1と、分離用酸化膜2と、ゲート電極3と、ゲート絶縁膜4と、ドレイン領域5と、ソース領域6と、層間絶縁膜7と、を構造的に組み合わせることにより形成されている。

なお、アクティブ領域Aは、素子分離領域Bで他の素子から電気的に分離されている。

【0018】

ウェル領域1は、シリコン半導体基板の表面に、P型の不純物が注入されている領域である。

50

## 【 0 0 1 9 】

分離用酸化膜 2 は、L O C O S ( L O C a l O x i d a t i o n o f S i l i c o n ) 膜であり、オフトランジスタ 1 0 の周囲のシリコン半導体基板の表面に形成されている。素子分離領域 B は、この分離用酸化膜 2 により形成されている。

なお、素子分離領域 B は、本実施形態のように分離用酸化膜 2 として L O C O S 膜を用いたもので形成してもよく、トレンチ分離 ( S h a l l o w T r e n c h I s o l a t i o n : S T I ) により形成してもよい。

## 【 0 0 2 0 】

ゲート電極 3 は、ウェル領域 1 の上に形成されたゲート絶縁膜 4 の更にその上にポリシリコン膜を形成し、そのポリシリコン膜に N 型の不純物を注入して形成された電極である。このゲート電極 3 は、ゲート絶縁膜 4 を介して、ドレイン領域 5 とソース領域 6 との間のウェル領域 1 ( いわゆるチャネル領域 ) のみならず、ドレイン領域 5 の一部及びソース領域 6 の一部を覆うように配置されている。また、ゲート電極 3 は、ドレイン領域 5 が半導体装置の表面に配置されている端子部に対しコンタクトホールを介してアルミニウムなどの導電体で電気的に接続可能なように、ドレイン領域 5 の上方に開口部 3 a が設けられている。ゲート電極 3 の上層には、層間絶縁膜 7 が形成されている。

10

## 【 0 0 2 1 】

ドレイン領域 5 及びソース領域 6 は、ウェル領域 1 の表面に N 型の不純物を高濃度に注入した領域である。

ドレイン領域 5 及びソース領域 6 の N 型の不純物は、イオン注入法などによりシリコン半導体基板面の略法線方向からゲート電極 3 の周囲に注入され、続く半導体装置の製造工程における熱処理によってゲート電極 3 の下面にも拡散する。このため、シリコン半導体基板をその法線方向から平面視した際に、ドレイン領域 5 及びソース領域 6 には、ゲート電極 3 の外周部の直下に位置する部分が存在する。

20

## 【 0 0 2 2 】

また、ドレイン領域 5 は、ドレイン端子 D を介して外部信号端子 1 0 0 b に接続されている。ソース領域 6 は、ソース端子 S を介して第 2 の電源端子 1 0 0 c に接続され、接地電位とされている。また、ウェル領域 1 においても接地電位とされている。

これにより、ゲート電極 3 の直下には、ゲート絶縁膜 4 を介して、ウェル領域 1 、ドレイン領域 5 及びソース領域 6 が存在することから、それぞれ容量が形成される。

30

## 【 0 0 2 3 】

ここで、ウェル領域 1 及びソース領域 6 が接地電位であるため、ゲート電極 3 との間に形成されている容量は共通したものとなる。このため、図 2 及び図 3 に示すように、ゲート電極 3 とウェル領域 1 及びソース領域 6 との間には、平面視すると矩形状である容量形成領域 C a 1 が形成される。また、ゲート電極 3 とドレイン領域 5 との間には、平面視すると矩形状であり、その中央付近に開口部 3 a が配置されている容量形成領域 C a 2 が形成される。

## 【 0 0 2 4 】

このように、オフトランジスタ 1 0 では、ゲート電極 3 とドレイン領域 5 との間に容量形成領域 C a 2 が形成されていることにより、たとえ C D M での静電気放電によりゲート - ドレイン間に高速の電位変化が発生しても、ゲート電極 3 の電位がドレイン領域 5 の電位に追従しやすくなる。このため、オフトランジスタ 1 0 は、ゲート電極 3 とドレイン領域 5 との間に電位差が生じにくくなり、ゲート絶縁膜 4 を破壊されにくい。

40

## 【 0 0 2 5 】

また、容量形成領域 C a 2 による容量 C 2 が容量形成領域 C a 1 による容量 C 1 よりも大きいと、即ち次式、  $C 2 > C 1$  を満たすと、ゲート電極 3 の電位は接地電位よりもドレイン領域 5 の電位に追従しやすくなる。これにより、オフトランジスタ 1 0 は、ゲート電極 3 とドレイン領域 5 との間に電位差がより生じにくくなり、ゲート絶縁膜 4 の破壊を更に抑制することができる。

## 【 0 0 2 6 】

50

具体的には、一般的なトランジスタの場合では、ゲート電極3の長さ( $L_1 + L_1 + L_1$ )を3μm、ゲート電極3の幅Wを100μm、ドレイン領域5及びソース領域6のゲート電極3下への拡散長をそれぞれ $L_1$ (即ち1μm)とし、ゲート電極3を延伸させない場合を考える。この場合には、容量形成領域Ca1と容量形成領域Ca2との面積比は、(2μm×100μm×ゲート絶縁膜4の膜厚):(1μm×100μm×ゲート絶縁膜4の膜厚)となり、2:1であることが分かる。このようにすると、ゲート電極3の電位は、ドレイン領域5の電位よりも、接地電位に追従しやすくなってしまう。

#### 【0027】

そこで、本実施形態のオーフトランジスタ10では、図2に示すように、容量形成領域Ca2の面積を容量形成領域Ca1の2倍以上となることから、ゲート電極3の電位がドレイン領域5の電位に追従しやすくなるため、ゲート電極3とドレイン領域5との間に電位差がより生じにくくなり、ゲート絶縁膜4の破壊を更に抑制することができる。

10

#### 【0028】

なお、素子分離領域Bと接する部分までドレイン領域5を延設する必要がない場合は、ゲート電極3の幅を広くし、素子分離領域Bとドレイン領域5とを離間させててもよい。

また、素子分離領域B下に形成されているチャネルストッパーの役目を果たすウェル領域1よりもP型の不純物濃度の高い領域とドレイン領域5との接触を避けるように故意に離間させて高耐圧構造としてもよい。これにより、ゲート電極3とドレイン領域5との間の容量形成領域Ca2を大きく増大させることが可能となる。

20

#### 【0029】

##### (第2の実施形態)

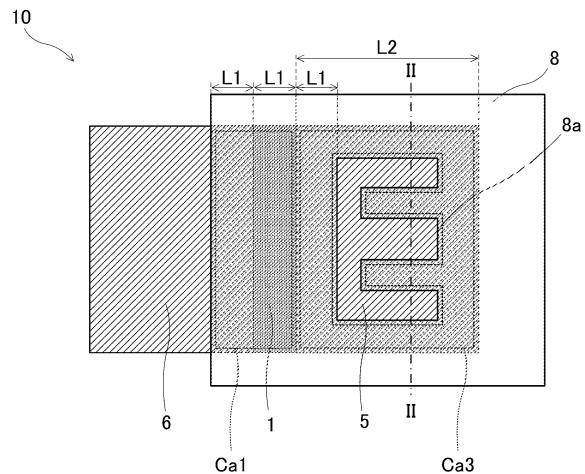

図5は、第2の実施形態に係る半導体装置が有するオーフトランジスタを示す概略平面図である。図6は、図5のII-II'線における概略断面図である。

図5及び図6に示すように、第2の実施形態は、第1の実施形態において開口部3aを平面視した際の形状を矩形状から状とした開口部8aに変更した以外は、第1の実施形態と同様である。したがって、図2～図4で説明した第1の実施形態と同じ構成については、同じ符号を記すことで説明に代える。

30

#### 【0030】

第2の実施形態では、開口部8aを状にしたことにより、第1の実施形態と比較して、ゲート電極8とドレイン領域5との間に形成される容量形成領域Ca3の面積を容量形成領域Ca1の面積よりも大きくすることができる。これにより、ゲート電極8の電位がドレイン領域5の電位に第1の実施形態よりも追従しやすくなるため、ゲート電極3とドレイン領域5との間に電位差がより生じにくくなり、ゲート絶縁膜4の破壊を更に抑制することができる。

また、開口部8aが状であると、ドレイン領域5及びソース領域6を形成する際に、ウェル領域1の表面に不純物を注入しやすくなる点で有利である。

40

#### 【0031】

なお、第2の実施形態では、開口部にゲート電極の2つの凹部がX方向に設けられているとしたが、これに限ることなく、凹部の数、向き、幅などは任意に設けることができる。すなわち、開口部を平面視した際の形状は、容量形成領域Ca3の面積を大きくする観点から、矩形状の一部に凹部を有することが好ましい。この凹部は、矩形状の開口部の角部が欠けるように設けてもよい。

#### 【0032】

以上説明したように、N型MOSトランジスタのゲート及びソースが接地されているオーフトランジスタを有する半導体装置において、オーフトランジスタは、ゲート電極がチャネル領域に加えてドレイン領域の一部又は全部の上方に延設されている。これにより、オーフトランジスタは、ゲート電極の電位がドレイン領域5の電位に追従しやすくなるため、ゲート電極とドレイン領域との間に電位差が生じにくくなり、ゲート絶縁膜の破壊を抑制することができる。

#### 【0033】

50

以上、この発明の実施形態について詳述したが、本発明はこれらの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等も含まれる。

【0034】

なお、第1及び第2の実施形態では、ドレイン領域から半導体装置の表面に配置されている端子部に対してコンタクトホールを介して電気的に接続可能とするためにゲート電極に開口部を設けたが、他の経路から接続可能であれば開口部は設けなくてもよい。

【0035】

また、第1及び第2の実施形態では、オフトランジスタをN型とし、ウェル領域をP型としたが、これに限ることなく、オフトランジスタをP型とし、ウェル領域をN型としてもよい。この場合、オフトランジスタは、P型MOSトランジスタのゲート電極及びソース領域が第1の電源端子に接続され、ゲート電極がチャネル領域に加えてソース領域の一部又は全部の上方に延設される。

10

【0036】

そして、これまで述べた外部信号端子は、外部信号が入力される端子としてきたが、静電気が印加されるなどの端子においても同様であることはいうまでもない。例えば、静電気が印加される端子として、第1の電源や第2の電源といった電源電圧が入力される電源端子であっても構わない。

【符号の説明】

【0037】

- |           |                                |    |

|-----------|--------------------------------|----|

| 1         | ウェル領域                          | 20 |

| 2         | 分離用酸化膜                         |    |

| 3 , 8     | ゲート電極                          |    |

| 3 a , 8 a | 開口部                            |    |

| 4         | ゲート絶縁膜                         |    |

| 5         | ドレイン領域                         |    |

| 6         | ソース領域                          |    |

| 1 0       | オフトランジスタ                       |    |

| 1 0 0     | 半導体装置                          |    |

| 1 0 0 a   | 第1の電源端子                        |    |

| 1 0 0 b   | 外部信号端子                         | 30 |

| 1 0 0 c   | 第2の電源端子                        |    |

| A         | アクティブ領域                        |    |

| B         | 素子分離領域                         |    |

| C a 1     | (ゲート電極とウェル領域及びソース領域との間の)容量形成領域 |    |

| C a 2     | (ゲート電極とドレイン領域との間の)容量形成領域       |    |

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

## 【図 3】

## 【図 4】

40

50

20

30

【図5】

【図6】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献      特開平10-242296 (JP, A)

特開平07-321306 (JP, A)

特開2011-192843 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

H10D 30/60

H10D 89/60

H10D 8/50