(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5352149号

(P5352149)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 616U

H01L 29/78 616T

H01L 29/78 619A

請求項の数 6 (全 31 頁)

(21) 出願番号 特願2008-199142 (P2008-199142)

(22) 出願日 平成20年8月1日 (2008.8.1)

(65) 公開番号 特開2009-60095 (P2009-60095A)

(43) 公開日 平成21年3月19日 (2009.3.19)

審査請求日 平成23年8月1日 (2011.8.1)

(31) 優先権主張番号 特願2007-205615 (P2007-205615)

(32) 優先日 平成19年8月7日 (2007.8.7)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100108741

弁理士 渡邊 順之

(72) 発明者 小林 脍

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 宮口 厚

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 守屋 芳隆

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置及び当該表示装置を具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に設けられたゲート電極と、

前記ゲート電極上に設けられたゲート絶縁膜と、

前記ゲート電極上に前記ゲート絶縁膜を介して設けられた微結晶半導体膜と、

前記微結晶半導体膜において、前記微結晶半導体膜と接して設けられたチャネル保護膜と、

前記ゲート絶縁膜上であり、且つ前記微結晶半導体膜及び前記チャネル保護膜の側面に設けられた非晶質半導体膜と、

前記非晶質半導体膜上に設けられた不純物半導体膜と、

10

前記不純物半導体膜上に接して設けられたソース電極及びドレイン電極と、を有し、

前記非晶質半導体膜の膜厚は、前記微結晶半導体膜の膜厚より大きい薄膜トランジスタを有することを特徴とする表示装置。

## 【請求項 2】

基板上に設けられたゲート電極と、

前記ゲート電極上に設けられたゲート絶縁膜と、

前記ゲート電極上に前記ゲート絶縁膜を介して設けられた微結晶半導体膜と、

前記微結晶半導体膜において、前記微結晶半導体膜と接して設けられたチャネル保護膜と、

前記ゲート絶縁膜上であり、且つ前記微結晶半導体膜及び前記チャネル保護膜の側面に

20

設けられた非晶質半導体膜と、

前記非晶質半導体膜上に設けられた不純物半導体膜と、

前記不純物半導体膜上に接して設けられたソース電極及びドレイン電極と、を有し、

前記非晶質半導体膜の膜厚は、前記微結晶半導体膜の膜厚より大きく、

前記ソース電極及び前記ドレイン電極の外側において、前記不純物半導体膜の一部、及び前記非晶質半導体膜の一部が露出しており、

前記不純物半導体膜の端部と、前記非晶質半導体膜の端部は一致している薄膜トランジスタを有することを特徴とする表示装置。

#### 【請求項 3】

基板上に設けられたゲート電極と、

10

前記ゲート電極上に設けられたゲート絶縁膜と、

前記ゲート電極上に前記ゲート絶縁膜を介して設けられた微結晶半導体膜と、

前記微結晶半導体膜上において、前記微結晶半導体膜と接して設けられたチャネル保護膜と、

前記ゲート絶縁膜上であり、且つ前記微結晶半導体膜及び前記チャネル保護膜の側面に設けられた非晶質半導体膜と、

前記非晶質半導体膜上に設けられた不純物半導体膜と、

前記不純物半導体膜上に接して設けられたソース電極及びドレイン電極と、

前記ソース電極及び前記ドレイン電極、前記不純物半導体膜、並びに前記非晶質半導体膜に接する絶縁膜と、

20

前記絶縁膜上に形成され、前記絶縁膜に形成されるコンタクトホールにおいて、前記ソース電極または前記ドレイン電極に接続する画素電極と、を有し、

前記非晶質半導体膜の膜厚は、前記微結晶半導体膜の膜厚より大きい薄膜トランジスタを有することを特徴とする表示装置。

#### 【請求項 4】

基板上に設けられたゲート電極と、

前記ゲート電極上に設けられたゲート絶縁膜と、

前記ゲート電極上に前記ゲート絶縁膜を介して設けられた微結晶半導体膜と、

前記微結晶半導体膜上において、前記微結晶半導体膜と接して設けられたチャネル保護膜と、

30

前記ゲート絶縁膜上であり、且つ前記微結晶半導体膜及び前記チャネル保護膜の側面に設けられた非晶質半導体膜と、

前記非晶質半導体膜上に設けられた不純物半導体膜と、

前記不純物半導体膜上に接して設けられたソース電極及びドレイン電極と、

前記ソース電極及び前記ドレイン電極、前記不純物半導体膜、並びに前記非晶質半導体膜に接する絶縁膜と、

前記絶縁膜上に形成され、前記絶縁膜に形成されるコンタクトホールにおいて、前記ソース電極または前記ドレイン電極に接続する画素電極と、を有し、

前記非晶質半導体膜の膜厚は、前記微結晶半導体膜の膜厚より大きく、

前記ソース電極及び前記ドレイン電極の外側において、前記不純物半導体膜の一部、及び前記非晶質半導体膜の一部が露出しており、

40

前記不純物半導体膜の端部と、前記非晶質半導体膜の端部は一致している薄膜トランジスタを有することを特徴とする表示装置。

#### 【請求項 5】

請求項 1 乃至 4 のいずれか一項において、

前記チャネル保護膜は、窒化珪素膜または窒化酸化珪素膜であることを特徴とする表示装置。

#### 【請求項 6】

請求項 1 乃至 5 のいずれか一項に記載の表示装置を具備することを特徴とする電子機器

。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置及び当該表示装置を用いた電子機器に関する。特に、画素部に薄膜トランジスタを用いた表示装置及び当該表示装置を用いた電子機器に関する。

**【背景技術】****【0002】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数nm～数百nm程度）を用いて薄膜トランジスタを構成する技術が多くの電子機器で実用化されている。薄膜トランジスタは、特に、表示装置の画素部におけるスイッチング素子として実用化が進み、なおも研究開発が盛んである。10

**【0003】**

液晶表示装置のスイッチング素子としては、大型のパネルでは非晶質半導体膜を用いた薄膜トランジスタ、小型のパネルでは多結晶半導体膜を用いた薄膜トランジスタが用いられている。多結晶半導体膜の形成方法としては、パルス発振のエキシマレーザビームを光学系により線状に加工して、非晶質半導体膜に対し線状ビームを走査させながら照射して結晶化する技術が知られている。

**【0004】**

また、画像表示装置のスイッチング素子として、微結晶半導体膜を用いた薄膜トランジスタが用いられている（特許文献1乃至3）。また、非晶質半導体膜の特性の向上を目的とした薄膜トランジスタの作製方法として、ゲート絶縁膜上に非晶質シリコン膜を成膜した後、その上面に金属膜を形成し、当該金属膜にダイオードレーザを照射して、非晶質シリコン膜を微結晶シリコン膜に改質するものが知られている（非特許文献1）。この方法によれば、非晶質シリコン膜上に形成した金属膜は、ダイオードレーザの光エネルギーを熱エネルギーに変換するためのものであり、薄膜トランジスタの完成のためにはその後除去されるべきものである。すなわち、金属膜からの伝導加熱によってのみ非晶質シリコン膜が加熱され、微結晶半導体膜である微結晶シリコン膜を形成する方法である。20

【特許文献1】特開平4-242724号公報

【特許文献2】特開2005-49832号公報

【特許文献3】米国特許第5591987号30

【非特許文献1】トシアキ・アライ（Toshiaki Arai）他、エス・アイ・ディー 07 ダイジェスト（SID 07 DIGEST）、2007、p.1370-1373

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

多結晶半導体膜を用いた薄膜トランジスタは、非晶質半導体膜を用いた薄膜トランジスタに比べて移動度が2桁以上高く、表示装置の画素部とその周辺の駆動回路を同一基板上に一体形成できるという利点を有している。しかしながら、非晶質半導体膜を用いた場合に比べて、半導体膜の結晶化のために工程が複雑化するため、その分歩留まりが低下し、コストが高まるという問題がある。40

**【0006】**

また、微結晶半導体膜の表面は、酸化されやすいという問題がある。このため、チャネル形成領域の結晶粒が酸化されると、結晶粒の表面に酸化膜が形成されてしまい、当該酸化膜がキャリアの移動の障害となり、薄膜トランジスタの電気特性が低下するという問題がある。また、微結晶半導体膜は、非晶質半導体膜及び多結晶半導体膜と比べ、膜厚を大きくすることが難しく、ゲート電極と、ソース電極又はドレイン電極との間に生じる寄生容量の増加を招くといった問題がある。

**【0007】**

また、製造の容易さの点から、表示装置の画素部に設けられるスイッチング素子として逆50

スタガ構造の薄膜トランジスタが有望である。画素の開口率向上の観点から、逆スタガ構造の薄膜トランジスタの高性能化及び小型化が望まれる一方で、薄膜トランジスタがオフの状態のときのソース領域とドレイン領域間を流れるリーク電流（オフ電流ともいう）の増加の問題がある。そのため、薄膜トランジスタのサイズを小型化することが難しく、保持容量の小型化及び消費電力の低減を図ることが難しいといった問題がある。

#### 【0008】

上述した問題に鑑み、本発明は歩留まりの低下を抑制しつつ、且つ寄生容量の増加及び製造コストの増加を抑え、加えて、電気特性が高く、オフ電流の低減を図ることができる薄膜トランジスタを具備する表示装置を提案することを課題とする。

#### 【課題を解決するための手段】

10

#### 【0009】

本発明の一は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極上にゲート絶縁膜を介して設けられた微結晶半導体膜と、微結晶半導体膜上において、微結晶半導体膜と接して設けられたチャネル保護層と、ゲート絶縁膜上であり、且つ微結晶半導体膜及びチャネル保護層の側面に設けられた非晶質半導体膜と、非晶質半導体膜上に設けられた不純物半導体層と、不純物半導体層上に接して設けられたソース電極及びドレイン電極と、を有し、非晶質半導体膜の膜厚は、微結晶半導体膜の膜厚より大きい薄膜トランジスタを有する表示装置である。

#### 【0010】

また別の本発明の一は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極上にゲート絶縁膜を介して設けられた微結晶半導体膜と、微結晶半導体膜上において、微結晶半導体膜と接して設けられたチャネル保護層と、ゲート絶縁膜上であり、且つ微結晶半導体膜及びチャネル保護層の側面に設けられた非晶質半導体膜と、非晶質半導体膜上に設けられた不純物半導体層と、不純物半導体層上に接して設けられたソース電極及びドレイン電極と、を有し、非晶質半導体膜の膜厚は、微結晶半導体膜の膜厚より大きく、ソース電極及びドレイン電極の外側において、不純物半導体層の一部、及び非晶質半導体膜の一部が露出しており、ゲート電極上に形成される不純物半導体層の端部と、非晶質半導体膜の端部は一致している薄膜トランジスタを有する表示装置である。

20

#### 【0011】

30

また別の本発明の一は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極上にゲート絶縁膜を介して設けられた微結晶半導体膜と、微結晶半導体膜上において、微結晶半導体膜と接して設けられたチャネル保護層と、ゲート絶縁膜上であり、且つ微結晶半導体膜及びチャネル保護層の側面に設けられた非晶質半導体膜と、非晶質半導体膜上に設けられた不純物半導体層と、不純物半導体層上に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極、不純物半導体層、並びに非晶質半導体膜に接する絶縁膜と、絶縁膜上に形成され、絶縁膜に形成されるコンタクトホールにおいて、ソース電極またはドレイン電極に接続する画素電極と、を有し、非晶質半導体膜の膜厚は、微結晶半導体膜の膜厚より大きい薄膜トランジスタを有する表示装置である。

40

#### 【0012】

また別の本発明の一は、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極上にゲート絶縁膜を介して設けられた微結晶半導体膜と、微結晶半導体膜上において、微結晶半導体膜と接して設けられたチャネル保護層と、ゲート絶縁膜上であり、且つ微結晶半導体膜及びチャネル保護層の側面に設けられた非晶質半導体膜と、非晶質半導体膜上に設けられた不純物半導体層と、不純物半導体層上に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極、不純物半導体層、並びに非晶質半導体膜に接する絶縁膜と、絶縁膜上に形成され、絶縁膜に形成されるコンタクトホールにおいて、ソース電極またはドレイン電極に接続する画素電極と、を有し、非晶質半導体膜の膜厚は、微結晶半導体膜の膜厚より大きく、ソース電極及びドレイン電

50

極の外側において、不純物半導体層の一部、及び非晶質半導体膜の一部が露出しており、ゲート電極上に形成される不純物半導体層の端部と、非晶質半導体膜の端部は一致している薄膜トランジスタを有する表示装置である。

【0013】

なお本発明の表示装置において、チャネル保護層は、窒化珪素膜または窒化酸化珪素膜であってもよい。

【0014】

ソース電極及びドレイン電極の端部と、不純物半導体層の端部が一致せず、ソース電極及びドレイン電極の端部の外側に不純物半導体層の端部が形成されることにより、ソース電極及びドレイン電極の端部の距離が離れるため、ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。また、ソース電極及びドレイン電極並びに不純物半導体層の端部に電界が集中せず、ゲート電極と、ソース電極及びドレイン電極との間でのリーク電流を防止することができる。

10

【0015】

また、非晶質半導体層は、微結晶半導体膜及びチャネル保護層の側面に設けられている。非晶質半導体層が設けられることにより、ソース領域及びドレイン領域間となる不純物半導体層間の距離を長く取ることができ、不純物半導体層の間に流れるリーク電流を低減することができる。また、非晶質半導体層を設けることにより、ゲート電極と、ソース電極及びドレイン電極との間の膜厚を厚く設定することができるため、ゲート電極と、ソース電極及びドレイン電極との間に生じる寄生容量を低減することができる。

20

【0016】

また、微結晶半導体膜上において、微結晶半導体膜と接してチャネル保護層が設けられている。そして微結晶半導体膜はチャネル形成領域として機能する。チャネル保護層は、微結晶半導体膜の酸化を防止すると共に、薄膜トランジスタ作製工程におけるエッティングストッパーとして機能する。微結晶半導体膜に接してチャネル保護層が設けられていることにより、微結晶半導体膜の膜厚を小さくすることができ、且つ微結晶半導体膜に含まれる結晶粒の酸化を防止することができるため、移動度が高く、且つリーク電流が少なく、耐圧の高い薄膜トランジスタを得ることができる。

【0017】

微結晶半導体膜は、多結晶半導体膜と異なり、微結晶半導体膜として直接基板上に成膜することができる。具体的には、水素化珪素を原料ガスとし、プラズマCVD装置を用いて成膜することができる。上記方法を用いて作製された微結晶半導体膜は、0.5 nm ~ 20 nmの結晶粒を非晶質半導体中に含む微結晶半導体膜も含んでいる。よって、多結晶半導体膜を用いる場合と異なり、半導体膜の成膜後に結晶化の工程を設ける必要がない。薄膜トランジスタの作製における工程数を削減することができ、表示装置の歩留まりを高め、コストを抑えることができる。また、周波数が1 GHz以上のマイクロ波を用いたプラズマは電子密度が高く、原料ガスである水素化珪素の解離が容易となる。このため、周波数が数十MHz ~ 数百MHzのマイクロ波プラズマCVD法と比較して、微結晶半導体膜を容易に作製することが可能であり、成膜速度を高めることができます。このため、表示装置の量産性を高めることができる。

30

【0018】

また、微結晶半導体膜を用い、薄膜トランジスタ(TFT)を作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示装置を作製する。微結晶半導体膜を用いた薄膜トランジスタは、その移動度が $1 \sim 20 \text{ cm}^2 / \text{V} \cdot \text{sec}$ と、非晶質半導体膜を用いた薄膜トランジスタの2~20倍の移動度を有しているので、駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

40

【0019】

また、表示装置は液晶素子または発光素子(総じて、表示素子ともいう)を含む。また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに本発明は、該表示装置を作製

50

する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電圧を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッティングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

#### 【0020】

なお、本明細書中における表示装置とは、画像表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えばFPC（Flexible Printed Circuit）もしくはTAB（Tape Automated Bonding）テープもしくはTCP（Tape Carrier Package）が取り付けられたモジュール、TABテープやTCPの後にプリント配線板が設けられたモジュール、または表示素子にCOG（Chip On Glass）方式によりIC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。10

#### 【発明の効果】

#### 【0021】

本発明により、歩留まりの低下を抑制しつつ、且つ寄生容量の増加及び製造コストの増加を抑え、加えて電気特性が高く、オフ電流の低減を図ることができる薄膜トランジスタを具備する表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる様様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本実施の形態の記載内容に限定して解釈されるものではない。20

#### （実施の形態1）

#### 【0023】

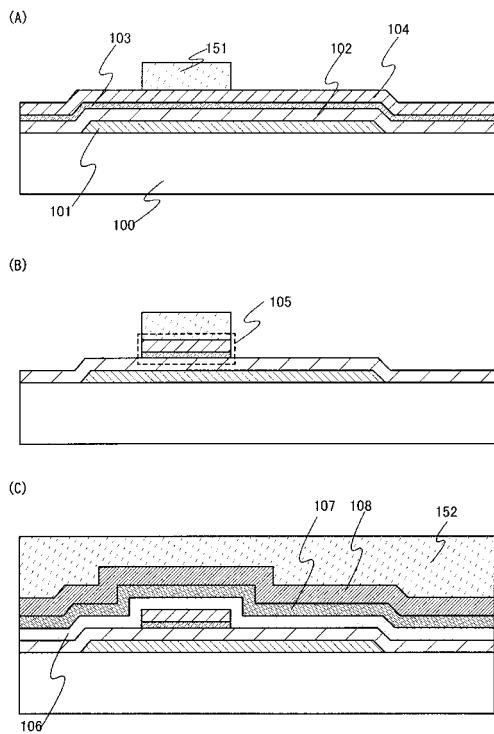

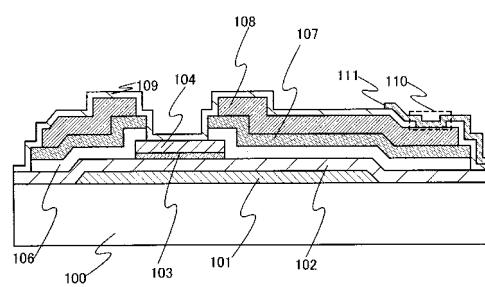

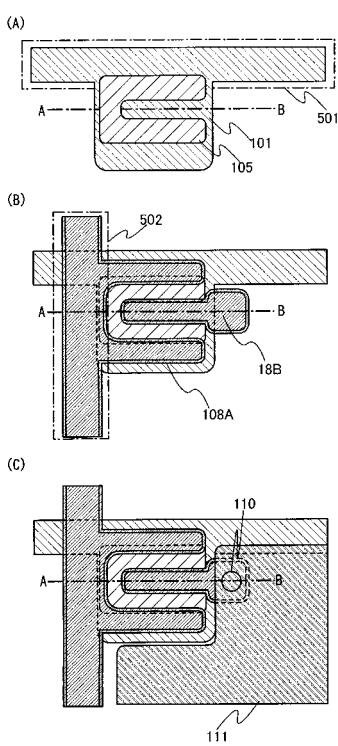

本実施の形態では、表示装置に用いられる薄膜トランジスタの作製工程について、図1乃至図5を用いて説明する。図1乃至図4は、薄膜トランジスタの作製工程を示す断面図であり、図5は、表示装置の一画素における薄膜トランジスタ及び画素電極の接続領域の上面図である。30

#### 【0024】

微結晶半導体膜を有する薄膜トランジスタは、p型よりもn型の方が、移動度が高いので駆動回路に用いるのにより適している。同一の基板上に形成する薄膜トランジスタを全て同じ極性にそろえておくことが、工程数を抑えるためにも望ましい。ここでは、nチャネル型の薄膜トランジスタを用いて説明する。

#### 【0025】

図1(A)に示すように、基板100上にゲート電極101を形成する。基板100は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。基板100がマザーガラスの場合、基板の大きさは、第1世代(320mm×400mm)、第2世代(400mm×500mm)、第3世代(550mm×650mm)、第4世代(680mm×880mm、または730mm×920mm)、第5世代(1000mm×1200mmまたは1100mm×1250mm)、第6世代(1500mm×1800mm)、第7世代(1900mm×2200mm)、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、2450mm×3050mm)、第10世代(2950mm×3400mm)等を用いることができる。40

#### 【0026】

ゲート電極101は、チタン、モリブデン、クロム、タンタル、タングステン、アルミニ50

ウムなどの金属材料またはその合金材料を用いて形成する。ゲート電極 101 は、スパッタリング法や真空蒸着法で基板 100 上に導電膜を形成し、当該導電膜上にフォトリソグラフィ技術またはインクジェット法によりマスクを形成し、当該マスクを用いて導電膜をエッチングすることで、形成することができる。なお、ゲート電極 101 の密着性向上と下地への拡散を防ぐバリアメタルとして、上記金属材料の窒化物膜を、基板 100 及びゲート電極 101 の間に設けてよい。ここでは、第 1 のフォトマスクを用いて形成したレジストマスクを用いて基板 100 上に形成された導電膜をエッチングしてゲート電極を形成する。

#### 【0027】

なお、ゲート電極 101 上には半導体膜や配線を形成するので、段切れ防止のため端部がテーパー状になるように加工することができる。また、図示しないがこの工程でゲート電極に接続する配線も同時に形成することができる。

#### 【0028】

次に、ゲート電極 101 上に、ゲート絶縁膜 102、微結晶半導体膜 103、チャネル保護層 104、を順に形成する。次に、チャネル保護層 104 上にレジスト 151 を塗布する。なお、少なくとも、ゲート絶縁膜 102、微結晶半導体膜 103、及びチャネル保護層 104 を連続的に形成することが好ましい。ゲート絶縁膜 102、微結晶半導体膜 103、及びチャネル保護層 104 を大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができる、薄膜トランジスタ特性のばらつきを低減することができる。

#### 【0029】

ゲート絶縁膜 102 は、CVD 法やスパッタリング法等を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜で形成することができる。なお、ゲート絶縁膜 102 として、ゲート絶縁膜を単層とせず、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化酸化珪素膜との順に 2 層を積層して形成することができる。なお、ゲート絶縁膜を 2 層とせず、基板側から窒化珪素膜または窒化酸化珪素膜と、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化酸化珪素膜との順に 3 層積層して形成することができる。

#### 【0030】

ここでは、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が 55 ~ 65 原子%、窒素が 1 ~ 20 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものをいう。また、窒化酸化珪素膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が 15 ~ 30 原子%、窒素が 20 ~ 35 原子%、Si が 25 ~ 35 原子%、水素が 15 ~ 25 原子% の範囲で含まれるものを使う。

#### 【0031】

微結晶半導体膜 103 は、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的に安定な第 3 の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、粒径が 0.5 ~ 20 nm の柱状または針状結晶が基板表面に対して法線方向に成長している。また、微結晶半導体と非単結晶半導体とが混在している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す  $521 \text{ cm}^{-1}$  よりも低波数側にシフトしている。即ち、単結晶シリコンを示す  $521 \text{ cm}^{-1}$  とアモルファスシリコンを示す  $480 \text{ cm}^{-1}$  の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダンギングボンド）を終端するため水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。このような微結晶半導体膜に関する記述は、例えば、米国特許 4,409,134 号で開示されている。

#### 【0032】

10

20

30

40

50

この微結晶半導体膜は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を50倍以上1000倍以下、好ましくは50倍以上200倍以下、更に好ましくは100倍とする。なお、水素化珪素の代わりに、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ 等を用いることができる。

## 【0033】

10

また、微結晶半導体膜は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導性を示すので、薄膜トランジスタのチャネル形成領域として機能する微結晶半導体膜に対しては、p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物元素としては、代表的には硼素であり、 $\text{B}_2\text{H}_6$ 、 $\text{BF}_3$ などの不純物気体を1ppm～1000ppm、好ましくは1～100ppmの割合で水素化珪素に混入させると良い。そしてボロンの濃度を、例えば $1 \times 10^{14} \sim 6 \times 10^{16}$ atoms/cm<sup>3</sup>とすると良い。

## 【0034】

また、微結晶半導体膜の酸素濃度を、 $5 \times 10^{19}$ cm<sup>-3</sup>以下、 $1 \times 10^{19}$ cm<sup>-3</sup>以下、窒素及び炭素の濃度それぞれを $3 \times 10^{18}$ cm<sup>-3</sup>以下とすることが好ましい。酸素、窒素、及び炭素が微結晶半導体膜に混入する濃度を低減することで、微結晶半導体膜がn型化になることを防止することができる。

20

## 【0035】

微結晶半導体膜103は、1nm以上50nm以下、好ましくは5nm以上20nmで形成する。微結晶半導体膜103は後に形成される薄膜トランジスタのチャネル形成領域として機能する。微結晶半導体膜103の厚さを5nm以上50nmとすることで、後に形成される薄膜トランジスタは、完全空乏型となる。また、微結晶半導体膜103は成膜速度が非晶質半導体膜の成膜速度の1/10～1/100と遅いため、膜厚を薄くすることでスループットを向上させることができる。微結晶半導体膜は微結晶で構成されているため、非晶質半導体膜と比較して抵抗が低い。このため、微結晶半導体膜を用いた薄膜トランジスタは、電流電圧特性を示す曲線の立ち上がり部分の傾きが急峻となり、スイッチング素子としての応答性が優れ、高速動作が可能となる。また、薄膜トランジスタのチャネル形成領域に微結晶半導体膜を用いることで、薄膜トランジスタの閾値の変動を抑制することができる。このため、電気特性のばらつきの少ない表示装置を作製することができる。

30

## 【0036】

また、微結晶半導体膜は非晶質半導体膜と比較して移動度が高い。このため、表示素子である液晶素子のスイッチングとして、チャネル形成領域が微結晶半導体膜で形成される薄膜トランジスタを用いることで、チャネル形成領域の面積、即ち薄膜トランジスタの面積を縮小することが可能である。このため、一画素あたりに示す薄膜トランジスタの面積が小さくなり、画素の開口率を高めることができる。

40

## 【0037】

なお、微結晶半導体膜の電気的特性の向上を目的として、ゲート絶縁膜上に微結晶半導体の表面側からレーザ光を照射してもよい。レーザ光は、微結晶半導体膜が溶融しないエネルギー密度で照射する。すなわち、微結晶半導体膜へのレーザ処理は、輻射加熱により微結晶半導体膜を溶融させないで行う固相結晶成長によるものである。すなわち、堆積された微結晶半導体膜が液相にならない臨界領域を利用するものであり、その意味において「臨界成長」ともいうことができる。

## 【0038】

50

レーザ光は微結晶半導体膜とゲート絶縁膜の界面にまで作用させることができる。それにより、微結晶半導体膜の表面側における結晶を種として、該表面からゲート絶縁膜の界面に向けて固相結晶成長が進み略柱状の結晶が成長する。レーザ処理による固相結晶成長は、結晶粒径を拡大させるものではなく、むしろ膜の厚さ方向における結晶性を改善するものである。レーザ処理は矩形長尺状に集光（線状レーザビーム）することで、例えば730 mm × 920 mmのガラス基板上の微結晶半導体膜を1回のレーザビームスキャンで処理することができる。この場合、線状レーザビームを重ね合わせる割合（オーバーラップ率）を0～90%（好ましくは0～67%）として行う。これにより、基板1枚当たりの処理時間が短縮され、生産性を向上させることができる。レーザビームの形状は線状に限定されるものでなく面状としても同様に処理することができる。また、本レーザ処理は前記ガラス基板のサイズに限定されず、さまざまなものに適用することができる。レーザ処理により、ゲート絶縁膜界面領域の結晶性が改善され、ボトムゲート構造を有するトランジスタの電気的特性を向上させる作用を奏する。このような臨界成長においては、従来の低温多結晶シリコンで見られた表面の凹凸（リッジと呼ばれる凸状体）が形成されず、レーザ処理後の半導体膜表面は平滑性が保たれていることも特徴である。本形態におけるように、成膜後の微結晶半導体膜に直接的にレーザ光を作用させて得られる結晶性の半導体膜は、堆積されたままの微結晶半導体膜、伝導加熱により改質された微結晶半導体膜（非特許文献1におけるもの）とは、その成長メカニズム及び膜質が明らかに異なる。本明細書では、成膜後の微結晶半導体膜（Semi Amorphous Semiconductor；SAS）にレーザ処理（Laser Process、以下「LP」ともいう。）を行って得られたものを総じてLPSAS（Laser Process Semi Amorphous Semiconductor）と呼ぶこととする。

#### 【0039】

チャネル保護層104は、窒化珪素膜または窒化酸化珪素膜を400 nm以下、好ましくは50 nm以上200 nm以下で形成する。例えば、窒化珪素膜はSiH<sub>4</sub>とNH<sub>3</sub>をソースガスとしてプラズマCVD法で形成する。窒化酸化珪素膜はSiH<sub>4</sub>、N<sub>2</sub>O及びNH<sub>3</sub>を用いてプラズマCVD法で形成する。チャネル保護層104は微結晶半導体膜上に接して設けられるため、窒化珪素膜または窒化酸化珪素膜で形成されることにより、微結晶半導体膜への不純物の拡散防止の効果が得られる他、微結晶半導体膜に含まれる結晶粒の表面の酸化を防止することができる。さらに、チャネル保護層104を設けることにより微結晶半導体膜表面の酸化を防止することができるため、微結晶半導体膜の膜厚を薄膜化することができる。そのため、本実施の形態における薄膜トランジスタは、完全空乏型のトランジスタとして動作させることが可能になるため、トランジスタをオフにした際のリーク電流を小さくすることができる。

#### 【0040】

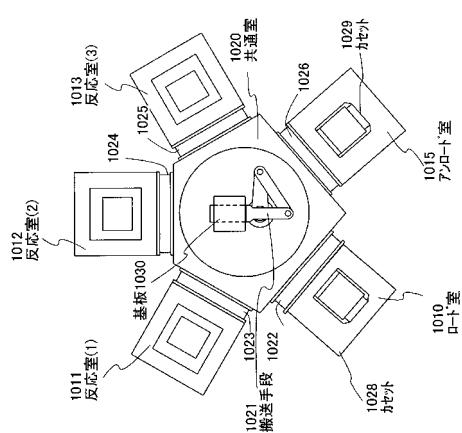

ここで、ゲート絶縁膜102からチャネル保護層104を連続成膜することが可能なプラズマCVD装置について、図6を用いて示す。図6はプラズマCVD装置の上断面を示す模式図であり、共通室1020の周りに、ロード室1010、アンロード室1015、反応室（1）1011、反応室（2）1012、反応室（3）1013を備えた構成となっている。共通室1020と各室の間にはゲートバルブ1022、ゲートバルブ1023、ゲートバルブ1024、ゲートバルブ1025、ゲートバルブ1026が備えられ、各室で行われる処理が、相互に干渉しないように構成されている。基板はロード室1010、アンロード室1015のカセット1028、カセット1029に装填され、共通室1020の搬送手段1021により反応室（1）1011～反応室（3）～1013へ運ばれる。この装置では、堆積膜種ごとに反応室をあてがうことが可能であり、複数の異なる被膜を大気に触れさせることなく連続して形成することができる。一例としては、反応室（1）1011でゲート絶縁膜102、反応室（2）1012で微結晶半導体膜103を形成し、反応室（3）1013は、チャネル保護層104を形成する構成がありえる。

#### 【0041】

このように、複数のチャンバが接続されたマイクロ波プラズマCVD装置で、同時にゲー

10

20

30

40

50

ト絶縁膜 102、微結晶半導体膜 103、及びチャネル保護層 104を成膜することができるため、量産性を高めることができる。また、ある反応室がメンテナンスやクリーニングを行っていても、残りの反応室において成膜処理が可能となり、成膜のタクトを向上させることができる。また、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタ特性のばらつきを低減することができる。

#### 【0042】

なお、図6に示すプラズマCVD装置には、ロード室及びアンロード室が別々に設けられているが、一つとしロード／アンロード室とでもよい。また、プラズマCVD装置に複数の予備室を設けてもよい。予備室で基板を予備加熱することで、各反応室において成膜までの加熱時間を短縮することが可能であるため、スループットを向上させることができる。

10

#### 【0043】

図1(A)の説明に戻る。図1(A)におけるレジスト151は、ポジ型レジストまたはネガ型レジストを用いることができる。本実施の形態では。ポジ型レジストを用いて示す。そして第2のフォトマスクを用いて、図1(A)に示すようにレジスト151が加工されたレジストマスクが形成される。そして図1(B)に示すように、チャネル保護層上に形成されたレジストマスクにより、微結晶半導体膜103及びチャネル保護層104をエッチングして、ゲート電極101上に、島状微結晶半導体膜105を形成する。なお、図1(B)は図5(A)のA-Bにおける断面図に相当する(但しレジスト151、ゲート絶縁膜102を除く)。なお、本明細書では、島状結晶性半導体膜とは、微結晶半導体膜とチャネル保護層とは積層して設けられているものとして説明する。なお、図5(A)に示す図では走査線501を示しており、走査線501とゲート電極101は、電気的に接続されるものである。

20

#### 【0044】

なお、島状微結晶半導体膜105の端部側面が傾斜させることにより、島状微結晶半導体膜側面に形成される非晶質半導体膜と、島状微結晶半導体膜105の底部にある微結晶半導体膜との間で良好な電気的接続を得ることができる。島状微結晶半導体膜105の端部側面の傾斜角度は、30°～90°、好ましくは45°～80°である。このような角度とすることで、段差形状によるソース電極またはドレイン電極の段切れを防止することができる。

30

#### 【0045】

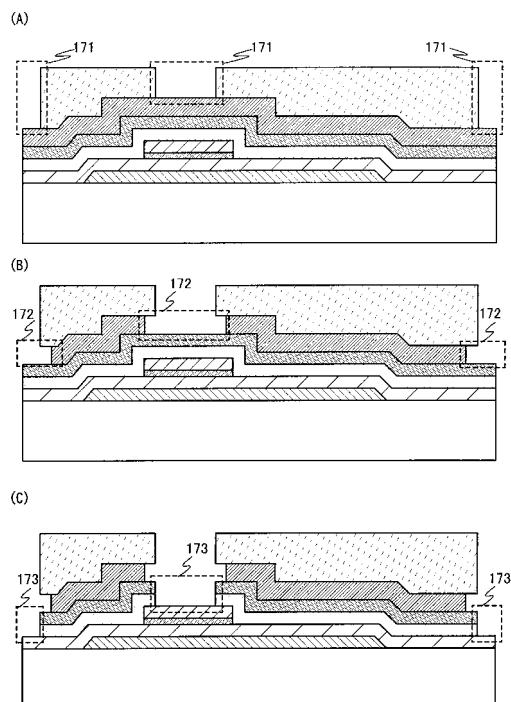

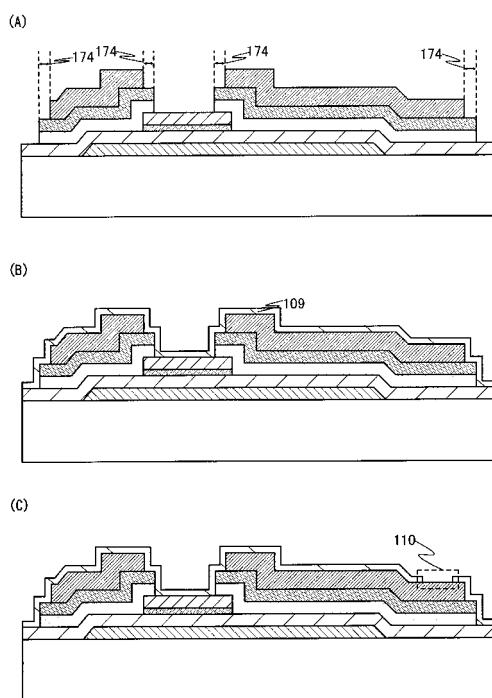

次に図1(C)に示すように、島状微結晶半導体膜105を覆うように非晶質半導体膜106、非晶質半導体膜106上に不純物半導体層107、不純物半導体層107上に導電膜108を形成する。なお導電膜108は、形状を加工することにより、ソース電極及びドレイン電極並びに信号線の配線となる。レジスト152は、ポジ型レジストまたはネガ型レジストを用いることができる。本実施の形態では。ポジ型レジストを用いて示す。そして第3のフォトマスクを用いてレジストマスクを形成する。本実施の形態では、一例として、図2(A)に示すように、レジストマスクに形成された穴部171より等方性のエッチングであるウェットエッチングを行う。ウェットエッチングを行うことにより、穴部171下の導電膜108は、図2(B)に示すように、穴部171の径より、大きな穴部172が形成される。続いて、レジストマスクに形成された穴部171より、異方性のエッチングであるドライエッチングを行う。ドライエッチングを行うことにより、穴部171下の不純物半導体層107及び非晶質半導体膜106は、レジストマスクに形成された穴部171と同程度の穴部173が形成される。その結果、図3(A)に示すように、後のソース電極及びドレイン電極となる導電膜108の端部と、不純物半導体層107の端部は一致せずにずれており(図3(A)における幅174)、導電膜108の端部の外側に、不純物半導体層107の端部が形成される。図3(A)に示すように、後のソース電極及びドレイン電極となる導電膜108の端部と、不純物半導体層107の端部は一致せずにずれた形状である幅174を有することで、ソース電極及びドレイン電極の端部の距

40

50

離が離れるため、ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。また、後のソース電極及びドレイン電極となる導電膜 108 の端部と、不純物半導体層 107 の端部は一致せずにずれた形状である幅 174 を有することで、導電膜 108 及び不純物半導体層 107 の端部に電界が集中せず、ゲート電極 101 と、導電膜 108 との間でのリーク電流を防止することができる。このため、信頼性が高く、且つ耐圧の高い薄膜トランジスタを作製することができる。このあと、レジストマスクは除去され、図 3 (A) に示すような開口部を得ることができる。なお、図 3 (A) は図 5 (B) の A - B における断面図に相当する（但しゲート絶縁膜 102 を除く）。なお、図 5 (B) に示す図では信号線 502、ソース電極 108a、ドレイン電極 108b を示しており、信号線 502 とソース電極 108a は、電気的に接続されるものである。

10

#### 【0046】

なお、トランジスタのソース電極とドレイン電極とは、トランジスタの動作条件等によって変わるため、いずれがソース電極またはドレイン電極と呼ぶかを限定することが困難である。そこで、本実施の形態においては、信号線 502 に接続された電極をソース電極 108a とし、後に画素電極に接続される電極をドレイン電極 108b として表記するものとする。

#### 【0047】

なお、図 5 (B) に示すように、不純物半導体層 107 の端部は、ソース電極 108a 及びドレイン電極 108b の端部の外側に位置することが分かる。また、ソース電極 108a、ドレイン電極 108b の一方はソース電極 108a、ドレイン電極 108b の他方を囲む形状（具体的には、U 字型、C 字型）である。このため、キャリアが移動する領域の面積を増加させることができるのであるため、電流量を増やすことが可能であり、薄膜トランジスタの面積を縮小することができる。また、ゲート電極 101 上において、微結晶半導体膜 103、非晶質半導体膜 106、不純物半導体層 107、ソース電極 108a 及びドレイン電極 108b が重畠されているため、ゲート電極 101 の凹凸の影響が少なく、被覆率の低減及びリーク電流の発生を抑制することができる。

20

#### 【0048】

また、図 3 (A) に示すように本実施形態で示す薄膜トランジスタにおいては、島状微結晶半導体膜の側面に非晶質半導体膜が設けられている。非晶質半導体膜は、先に設けられた微結晶半導体膜よりも膜厚を大きく設けることで、ソース電極及びドレイン電極と、ゲート電極との間に発生する寄生容量を小さくすることができる。代表的には、非晶質半導体膜の膜厚は、200 nm 以上 400 nm 以下の厚さで形成することが好ましい。また、薄膜トランジスタのソースとドレインの間に流れるキャリア（電子や空孔）は、ゲート電極近傍のゲート絶縁膜との界面にあたる微結晶半導体膜を経由してソースとドレインの間を流れる。薄膜トランジスタは、キャリアが流れる微結晶半導体膜のチャネル長方向の距離より、キャリアが流れる非晶質半導体膜の膜厚方向の距離が大きい。そのため、本発明の薄膜トランジスタを具備する表示装置では、微結晶半導体膜の長所を生かしつつ、且つソース電極及びドレイン電極と、ゲート電極との間に発生する寄生容量を低減することができる。加えて、ゲート電極への印加電圧の高い（例えば 15 V 程度）表示装置において、非晶質半導体膜の膜厚を微結晶半導体膜より厚く形成すると、ゲートと、ソースまたはドレイン間との耐圧が高くなり、薄膜トランジスタが劣化することを抑制することができる。

30

#### 【0049】

非晶質半導体膜 106 は、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub> などの水素化珪素を用いて、プラズマ CVD 法により形成することができる。また、上記水素化珪素に、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して非晶質半導体膜を形成することができる。水素化珪素の流量の 1 倍以上 20 倍以下、好ましくは 1 倍以上 10 倍以下、更に好ましくは 1 倍以上 5 倍以下の流量の水素を用いて、水素を含む非晶質半導体膜を形成することができる。また、上記水素化珪素と窒素またはアンモニアとを用いることで、窒素を含む非晶質半導体膜を形成することができる。また、上記水素化珪素

40

50

と、フッ素、塩素、臭素、またはヨウ素を含む気体 ( $F_2$ 、 $Cl_2$ 、 $Br_2$ 、 $I_2$ 、 $HF$ 、 $HCl$ 、 $HBr$ 、 $HI$ 等) を用いることで、フッ素、塩素、臭素、またはヨウ素を含む非晶質半導体膜を形成することができる。なお、水素化珪素の代わりに、 $SiH_2Cl_2$ 、 $SiHCl_3$ 、 $SiCl_4$ 、 $SiF_4$  等を用いることができる。

#### 【0050】

また、非晶質半導体膜 106 は、エネルギーギャップが微結晶半導体膜 103 に比べて大きく(非晶質半導体膜のエネルギーギャップは  $1.6 \sim 1.8\text{ eV}$ 、微結晶半導体膜のエネルギーギャップは  $1.1 \sim 1.5\text{ eV}$ )、また抵抗が高く、移動度が低く、微結晶半導体膜の  $1/5 \sim 1/10$  である。このため、後に形成される薄膜トランジスタにおいて、ソース領域及びドレイン領域と、微結晶半導体膜との間に形成される非晶質半導体膜 106 は一部チャネル形成領域として機能するものの大部分は高抵抗領域として機能し、微結晶半導体膜は全体がチャネル形成領域として機能する。このため、薄膜トランジスタのオフ電流を低減することができる。10

#### 【0051】

一導電型を付与する不純物が添加された不純物半導体層 107 は、n チャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてリンを添加すれば良く、水素化珪素に  $PH_3$  などの不純物気体を加えれば良い。また、p チャネル型の薄膜トランジスタを形成する場合には、代表的な不純物元素としてボロンを添加すれば良く、水素化珪素に  $B_2H_6$  などの不純物気体を加えれば良い。一導電型を付与する不純物が添加された不純物半導体層 107 は、微結晶半導体膜、または非晶質半導体で形成することができる。さらには一導電型を付与する不純物が添加された不純物半導体層 107 を、一導電型を付与する不純物が添加された非晶質半導体膜と、一導電型を付与する不純物が添加された微結晶半導体膜との積層で形成してもよい。一導電型を付与する不純物が添加された不純物半導体層 107 は  $2\text{ nm}$  以上  $50\text{ nm}$  以下の厚さで形成する。一導電型を付与する不純物が添加された半導体膜の膜厚を、薄くすることでスループットを向上させることができる。20

#### 【0052】

導電膜 108 は、アルミニウム、若しくは銅、シリコン、チタン、ネオジム、スカンジウム、モリブデンなどの耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウム合金の単層または積層で形成することが好ましい。また、導電性半導体膜と接する側の膜を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で挟んだ積層構造としてもよい。ここでは、導電膜 108 としては、導電膜が 3 層積層した構造の導電膜が挙げられ、アルミニウム膜をモリブデン膜で挟持する積層導電膜や、アルミニウム膜をチタン膜で挟持する積層導電膜がその一例である。導電膜は、スパッタリング法や真空蒸着法で形成する。30

#### 【0053】

なお、上述した微結晶半導体膜に対する価電子制御を目的とした不純物元素の添加は、微結晶半導体膜上部の非晶質半導体膜 106、不純物半導体層 107、及び導電膜 108 のエッチング工程を施した後に、チャネル保護層 104 を介してドープするよう行ってもよい。微結晶半導体膜上部の非晶質半導体膜 106、不純物半導体層 107、及び導電膜 108 のエッチング工程を施した後に、チャネル保護層 104 を介してドープすることにより、チャネル形成領域となる島状微結晶半導体膜 105 への選択的な不純物元素の添加をおこなうことができる。40

#### 【0054】

以上の工程により、薄膜トランジスタを形成することができる。また、3 枚のフォトマスクを用いて薄膜トランジスタを形成することができる。

#### 【0055】

次に、図 3 (B) に示すように、導電膜 108、不純物半導体層 107、非晶質半導体膜

106、島状微結晶半導体膜105、及びゲート絶縁膜102上に絶縁膜109を形成する。絶縁膜109は、ゲート絶縁膜102と同様に形成することができる。なお、絶縁膜109は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。

**【0056】**

次に、図3(C)に示すように絶縁膜109にコンタクトホール110を形成する。そして、図4に示すように、コンタクトホール110において導電膜108におけるドレイン電極108bに接する画素電極111を形成する。なお、図4は、図5(C)のA-Bの断面図に相当する。

**【0057】**

画素電極111は、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

**【0058】**

また、画素電極111として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 /以下、波長550nmにおける光の透過率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

**【0059】**

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

**【0060】**

以上により表示装置に用いることが可能な薄膜トランジスタを得ることができる。特に本実施の形態によって得られる薄膜トランジスタは、歩留まりの低下を抑制しつつ、且つ寄生容量の増加及び製造コストの増加を抑え、加えて電気特性が高く、オフ電流の低減を図ることができるために、電気特性の信頼性の高い薄膜トランジスタで駆動する表示装置を得ることができる。

**【0061】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

(実施の形態2)

**【0062】**

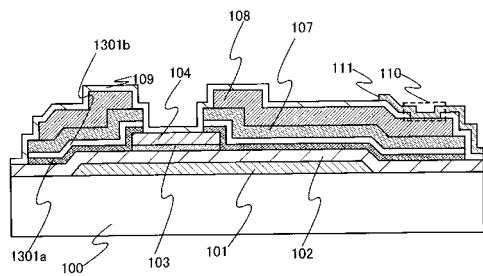

本実施の形態では、表示装置に用いられる薄膜トランジスタについて、実施の形態1と異なる構成について、図13を用いて説明する。図13は、薄膜トランジスタの断面図である。なお、本実施の形態において、実施の形態1と同様の箇所の説明については、同様の符号を付し、実施の形態1の説明を参照するものとして以下説明していく。

**【0063】**

なお本実施の形態で説明する薄膜トランジスタは実施の形態1と同様にnチャネル型の薄膜トランジスタを用いて説明する。

**【0064】**

まず、基板100上にゲート電極101、ゲート絶縁膜102、微結晶半導体膜103、チャネル保護層104を形成し、レジストマスク及びエッチング工程により、実施の形態1の図1(B)で示した状態を得る。基板100、ゲート電極101、ゲート絶縁膜102、微結晶半導体膜103、及びチャネル保護層104は、実施の形態1と同様のものを用いるものとする。

**【0065】**

10

20

30

40

50

次に、図13に示すように弱いp型を付与する不純物元素を含む非晶質半導体膜1301a、真性半導体となる非晶質半導体膜1301bを成膜する。真性半導体となる非晶質半導体膜1301b上には実施の形態1と同様に、不純物半導体層107及び導電膜108を成膜する。なお、弱いp型を付与する不純物元素を含む非晶質半導体膜1301a、真性半導体となる非晶質半導体膜1301bを成膜した後は、実施の形態1で示した非晶質半導体膜106と同様に、不純物半導体層107及び導電膜108を形成して、レジストマスクの形成及びエッチング工程を行う。そして、図13に示すように薄膜トランジスタを得ることができる。また得られた薄膜トランジスタには、実施の形態1と同様に、薄膜トランジスタを覆うように絶縁膜109を設け、コンタクトホール110によって、画素電極111と電気的な接続を取ることができる。

10

#### 【0066】

本実施の形態で示す薄膜トランジスタのソースとドレインとの間を流れる電気的なキャリアは、導電膜108(ソース電極またはドレイン電極)、不純物半導体層107、真性半導体となる非晶質半導体膜1301b、弱いp型を付与する不純物元素を含む非晶質半導体膜1301a、微結晶半導体膜103、弱いp型を付与する不純物元素を含む非晶質半導体膜1301a、真性半導体となる非晶質半導体膜1301b、不純物半導体層107、導電膜108(ソース電極またはドレイン電極)の順に流れるものとなる。すなわち、本実施の形態で示す薄膜トランジスタのソースとドレインとの間を流れる電気的なキャリアにとって、高抵抗領域となる弱いp型を付与する不純物元素を含む非晶質半導体膜1301a、真性半導体となる非晶質半導体膜1301bを通る。そのため本実施の形態で示す薄膜トランジスタは、ソースとドレインの間に流れるリーク電流を低減することができる。そのため、本実施の形態で示す薄膜トランジスタは、上記実施の形態1で示した優れた電気的特性に加え、リーク電流の低減といった効果を奏すことができる。

20

#### 【0067】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

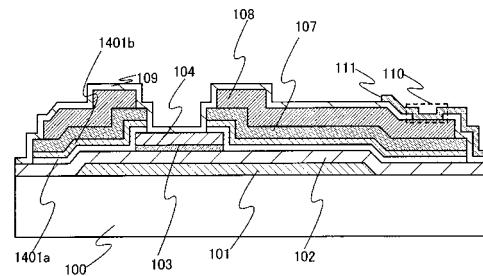

#### (実施の形態3)

#### 【0068】

本実施の形態では、表示装置に用いられる薄膜トランジスタについて、実施の形態1及び実施の形態2と異なる構成について、図14を用いて説明する。図14は、薄膜トランジスタの断面図である。なお、本実施の形態において、実施の形態1と同様の箇所の説明については、同様の符号を付し、実施の形態1の説明を参照するものとして以下説明していく。

30

#### 【0069】

なお本実施の形態で説明する薄膜トランジスタは実施の形態1と同様にnチャネル型の薄膜トランジスタを用いて説明する。

#### 【0070】

まず、基板100上にゲート電極101、ゲート絶縁膜102、微結晶半導体膜103、チャネル保護層104を形成し、レジストマスク及びエッチング工程により、実施の形態1の図1(B)で示した状態を得る。基板100、ゲート電極101、ゲート絶縁膜102、微結晶半導体膜103、及びチャネル保護層104は、実施の形態1と同様のものを用いるものとする。

40

#### 【0071】

次に、図14に示すように真性半導体となる非晶質半導体膜1401a、弱いn型を付与する不純物元素を含む非晶質半導体膜1401bを成膜する。弱いn型を付与する不純物元素を含む非晶質半導体膜1401b上には実施の形態1と同様に、不純物半導体層107及び導電膜108を成膜する。なお、真性半導体となる非晶質半導体膜1401a、弱いn型を付与する不純物元素を含む非晶質半導体膜1401bを成膜した後は、実施の形態1で示した非晶質半導体膜106と同様に、不純物半導体層107及び導電膜108を形成して、レジストマスクの形成及びエッチング工程を行う。そして、図14に示すよう

50

に薄膜トランジスタを得ることができる。また得られた薄膜トランジスタには、実施の形態1と同様に、薄膜トランジスタを覆うように絶縁膜109を設け、コンタクトホール110によって、画素電極111と電気的な接続を取ることができる。

#### 【0072】

本実施の形態で示す薄膜トランジスタのソースとドレインとの間を流れる電気的なキャリアは、導電膜108（ソース電極またはドレイン電極）、不純物半導体層107、弱いn型を付与する不純物元素を含む非晶質半導体膜1401b、真性半導体となる非晶質半導体膜1401a、微結晶半導体膜103、真性半導体となる非晶質半導体膜1401a、弱いn型を付与する不純物元素を含む非晶質半導体膜1401b、不純物半導体層107、導電膜108（ソース電極またはドレイン電極）の順に流れるものとなる。すなわち、本実施の形態で示す薄膜トランジスタのソースとドレインとの間を流れる電気的なキャリアにとって、不純物半導体層107、弱いn型を付与する不純物元素を含む非晶質半導体膜1401b、真性半導体となる非晶質半導体膜1401aと段階的に高抵抗領域となるように半導体膜を積層することによるリーク電流の低減に加えて、段階的に抵抗値を大きくすることにより急激な電圧の変化に伴う電子の加速による薄膜トランジスタの劣化を低減することができる。そのため本実施の形態では、ソースとドレインの間に流れるリーク電流を低減及び薄膜トランジスタの長寿命化を図ることができる。そのため、本実施の形態で示す薄膜トランジスタは、上記実施の形態1で示した優れた電気的特性に加え、リーク電流の低減といった効果を奏することができる。

#### 【0073】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### (実施の形態4)

#### 【0074】

本実施の形態では、実施の形態1で示す薄膜トランジスタを有する表示装置について、以下に示す。本実施の形態で示す表示装置としては、液晶表示装置を挙げて説明する。

#### 【0075】

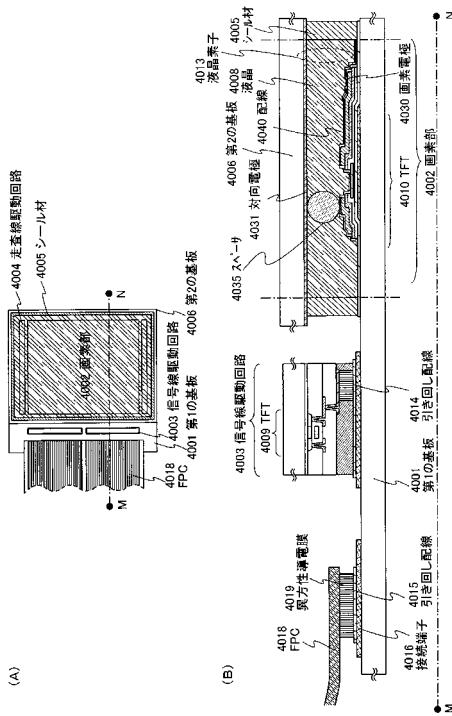

液晶表示装置の一形態に相当する液晶表示パネルの外観及び断面について、図7を用いて説明する。図7は、第1の基板4001上に形成された微結晶半導体膜を有する薄膜トランジスタ4010及び液晶素子4013を、第2の基板4006との間にシール材4005によって封止した、パネルの上面図であり、図7(B)は、図7(A)のM-Nにおける断面図に相当する。

#### 【0076】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶4008と共に封止されている。また第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体膜で形成された信号線駆動回路4003が実装されている。なお本実施の形態では、多結晶半導体膜を用いた薄膜トランジスタを有する信号線駆動回路を、第1の基板4001に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで信号線駆動回路を形成し、貼り合わせるようにしても良い。図7では、信号線駆動回路4003に含まれる、多結晶半導体膜で形成された薄膜トランジスタ4009を例示する。

#### 【0077】

また第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図7(B)では、画素部4002に含まれる薄膜トランジスタ4010とを例示している。薄膜トランジスタ4010は微結晶半導体膜を用いた薄膜トランジスタに相当し、実施の形態1に示す工程で同様に作製することができる。

10

20

30

40

50

**【0078】**

また液晶4008に面する画素電極4030は、薄膜トランジスタ4010と配線4040を介して電気的に接続されている。そして液晶素子4013の対向電極4031は第2の基板4006上に形成されている。画素電極4030と対向電極4031と液晶4008とが重なっている部分が、液晶素子4013に相当する。

**【0079】**

なお、第1の基板4001、第2の基板4006としては、ガラス、金属（代表的にはステンレス）、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP（Fiberglass-Reinforced Plastics）板、PVF（ポリビニルフルオライド）フィルム、ポリエスチルフィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエスチルフィルムで挟んだ構造のシートを用いることもできる。10

**【0080】**

また4035は球状のスペーサであり、画素電極4030と対向電極4031との間の距離（セルギャップ）を制御するために設けられている。なお絶縁膜を選択的にエッチングすることで得られるスペーサを用いていても良い。

**【0081】**

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、配線4014、4015を介して、FPC4018から供給されている。20

**【0082】**

本実施の形態では、接続端子4016が、液晶素子4013が有する画素電極4030と同じ導電膜から形成されている。また、配線4014、4015は、配線4040と同じ導電膜で形成されている。

**【0083】**

接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

**【0084】**

なお図示していないが、本実施の形態に示した液晶表示装置は配向膜、偏光板を有し、更にカラーフィルタや遮蔽膜を有していても良い。30

**【0085】**

また図7において、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

**【0086】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

**(実施の形態5)****【0087】**

本実施の形態では、実施の形態1で示す薄膜トランジスタを有する表示装置について、以下に示す。本実施の形態で示す表示装置としては、発光素子を具備する発光装置を挙げて説明する。

**【0088】**

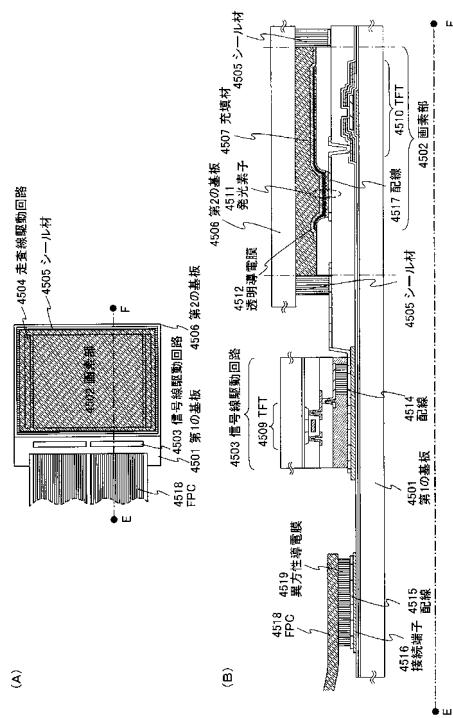

発光装置の一形態に相当する発光表示パネルの外観及び断面について、図8を用いて説明する。図8は、第1の基板上に形成された微結晶半導体膜を用いた薄膜トランジスタ及び発光素子を、第2の基板との間にシール材によって封止した、パネルの上面図であり、図8(B)は、図8(A)のE-Fにおける断面図に相当する。

**【0089】**

第1の基板4501上に設けられた画素部4502と、走査線駆動回路4504とを囲む50

ようにして、シール材 4505 が設けられている。また画素部 4502 と、走査線駆動回路 4504 の上に第 2 の基板 4506 が設けられている。よって画素部 4502 と、走査線駆動回路 4504 とは、第 1 の基板 4501 とシール材 4505 と第 2 の基板 4506 とによって、充填材 4507 と共に密封されている。また第 1 の基板 4501 上のシール材 4505 によって囲まれている領域とは異なる領域に、別途用意された基板上に多結晶半導体膜で形成された信号線駆動回路 4503 が実装されている。なお本実施の形態では、多結晶半導体膜を用いた薄膜トランジスタを有する信号線駆動回路を、第 1 の基板 4501 に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで信号線駆動回路を形成し、貼り合わせるようにしても良い。図 8 では、信号線駆動回路 4503 に含まれる、多結晶半導体膜で形成された薄膜トランジスタ 4509 を例示する。

10

#### 【0090】

また第 1 の基板 4501 上に設けられた画素部 4502 と、走査線駆動回路 4504 は、薄膜トランジスタを複数有しており、図 8 (A) では、画素部 4502 に含まれる薄膜トランジスタ 4510 を例示している。なお本実施の形態では、薄膜トランジスタ 4510 が駆動用 TFT であると仮定するが、薄膜トランジスタ 4510 は電流制御用 TFT であっても良いし、消去用 TFT であっても良い。薄膜トランジスタ 4510 は微結晶半導体膜を用いた薄膜トランジスタに相当し、実施の形態 1 に示す工程で同様に作製することができる。

#### 【0091】

また 4511 は発光素子に相当し、発光素子 4511 が有する画素電極は、薄膜トランジスタ 4510 のソース電極またはドレイン電極と、配線 4517 を介して電気的に接続されている。そして本実施の形態では、発光素子 4511 の共通電極と透光性を有する導電性材料 4512 が電気的に接続されている。なお発光素子 4511 の構成は、本実施の形態に示した構成に限定されない。発光素子 4511 から取り出す光の方向や、薄膜トランジスタ 4510 の極性などに合わせて、発光素子 4511 の構成は適宜変えることができる。

20

#### 【0092】

また、別途形成された信号線駆動回路 4503 と、走査線駆動回路 4504 または画素部 4502 に与えられる各種信号及び電位は、図 8 (B) に示す断面図では図示されていないが、配線 4514 及び 4515 を介して、FPC 4518 から供給されている。

30

#### 【0093】

本実施の形態では、接続端子 4516 が、発光素子 4511 が有する画素電極と同じ導電膜から形成されている。また、配線 4514、4515 は、配線 4517 と同じ導電膜から形成されている。

#### 【0094】

接続端子 4516 は、FPC 4518 が有する端子と、異方性導電膜 4519 を介して電気的に接続されている。

#### 【0095】

発光素子 4511 からの光の取り出し方向に位置する基板には、第 2 の基板は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

40

#### 【0096】

また、充填材 4507 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、PVB (ポリビニルブチラル) または EVA (エチレンビニルアセテート) を用いることができる。本実施の形態は充填材として窒素を用いた。

#### 【0097】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板（楕円偏光板を含む）、位相差板（1/4 板、1/2 板）、カラーフィルタなどの光学フィルムを適宜設けてもよ

50

い。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

#### 【0098】

なお、図8では、信号線駆動回路4503を別途形成し、第1の基板4501に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

#### 【0099】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

10

(実施の形態6)

#### 【0100】

本発明の表示装置の一形態である表示パネルの構成について、以下に示す。

#### 【0101】

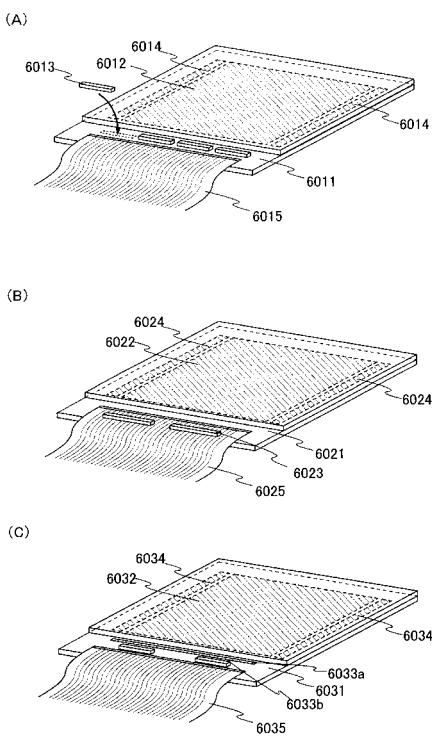

図9(A)に、信号線駆動回路6013のみを別途形成し、基板6011上に形成された画素部6012と接続している表示パネルの形態を示す。画素部6012及び走査線駆動回路6014は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。微結晶半導体膜を用いた薄膜トランジスタよりも高い移動度が得られるトランジスタで信号線駆動回路を形成することで、走査線駆動回路よりも高い駆動周波数が要求される信号線駆動回路の動作を安定させることができる。なお、信号線駆動回路6013は、単結晶の半導体を用いたトランジスタ、多結晶の半導体を用いた薄膜トランジスタ、またはSOI基板を用いて形成されたトランジスタであっても良い。画素部6012と、信号線駆動回路6013と、走査線駆動回路6014とに、それぞれ電源の電位、各種信号等が、FPC6015を介して供給される。

20

#### 【0102】

なお、信号線駆動回路及び走査線駆動回路を、共に画素部と同じ基板上に形成しても良い。

#### 【0103】

また、駆動回路を別途形成する場合、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えばFPC上に貼り合わせるようにしても良い。図9(B)に、信号線駆動回路6023のみを別途形成し、基板6021上に形成された画素部6022及び走査線駆動回路6024と接続している液晶表示パネルの形態を示す。画素部6022及び走査線駆動回路6024は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。信号線駆動回路6023は、FPC6025を介して画素部6022と接続されている。画素部6022と、信号線駆動回路6023と、走査線駆動回路6024とに、それぞれ電源の電位、各種信号等が、FPC6025を介して供給される。

30

#### 【0104】

また、信号線駆動回路の一部または走査線駆動回路の一部のみを、微結晶半導体膜を用いた薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電気的に接続するようにしても良い。図9(C)に、信号線駆動回路が有するアナログスイッチ6033aを、画素部6032、走査線駆動回路6034と同じ基板6031上に形成し、信号線駆動回路が有するシフトレジスタ6033bを別途異なる基板に形成して貼り合わせる液晶表示パネルの形態を示す。画素部6032及び走査線駆動回路6034は、微結晶半導体膜を用いた薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ6033bは、FPC6035を介して画素部6032と接続されている。画素部6032と、信号線駆動回路と、走査線駆動回路6034とに、それぞれ電源の電位、各種信号等が、FPC6035を介して供給される。

40

#### 【0105】

図9(A)乃至(C)に示すように、本発明の表示装置は、駆動回路の一部または全部

50

を、画素部と同じ基板上に、微結晶半導体膜を用いた薄膜トランジスタを用いて形成することができる。

#### 【0106】

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知のCOG方法、ワイヤボンディング方法、或いはTAB方法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図9(A)乃至(C)に示した位置に限定されない。また、コントローラ、CPU、メモリ等を別途形成し、接続するようにしても良い。

#### 【0107】

なお本発明で用いる信号線駆動回路は、シフトレジスタとアナログスイッチのみを有する形態に限定されない。シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有していても良い。また、シフトレジスタとアナログスイッチは必ずしも設ける必要はなく、例えばシフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

#### 【0108】

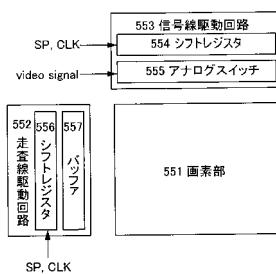

図10に本発明の液晶表示装置のブロック図を示す。図10に示す液晶表示装置は、液晶素子を備えた画素を複数有する画素部551と、各画素を選択する走査線駆動回路552と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路553とを有する。

10

20

#### 【0109】

図10において信号線駆動回路553は、シフトレジスタ554、アナログスイッチ555を有している。シフトレジスタ554には、クロック信号(CLK)、スタートパルス信号(SP)が入力されている。クロック信号(CLK)とスタートパルス信号(SP)が入力されると、シフトレジスタ554においてタイミング信号が生成され、アナログスイッチ555に入力される。

#### 【0110】

またアナログスイッチ555には、ビデオ信号(video signal)が与えられている。アナログスイッチ555は入力されるタイミング信号に従ってビデオ信号をサンプリングし、後段の信号線に供給する。

30

#### 【0111】

次に、走査線駆動回路552の構成について説明する。走査線駆動回路552は、シフトレジスタ556、バッファ557を有している。また場合によってはレベルシフタを有していても良い。走査線駆動回路552において、シフトレジスタ556にクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファ557において緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のトランジスタのゲートが接続されている。そして、1ライン分の画素のトランジスタを一斉にONにしなくてはならないので、バッファ557は大きな電流を流すことが可能なものが用いられる。

#### 【0112】

フルカラーの液晶表示装置で、R(赤)、G(緑)、B(青)に対応するビデオ信号を、順にサンプリングして対応する信号線に供給している場合、シフトレジスタ554とアナログスイッチ555とを接続するための端子数が、アナログスイッチ555と画素部551の信号線を接続するための端子数の1/3程度に相当する。よって、アナログスイッチ555を画素部551と同じ基板上に形成することで、アナログスイッチ555を画素部551と異なる基板上に形成した場合に比べて、別途形成した基板の接続に用いる端子の数を抑えることができ、接続不良の発生確率を抑え、歩留まりを高めることができる。

40

#### 【0113】

なお、図10の走査線駆動回路552は、シフトレジスタ556、及びバッファ557を有するが、シフトレジスタ556で走査線駆動回路552を構成してもよい。

50

**【0114】**

なお、図10に示す構成は、本発明の表示装置の一形態を示したに過ぎず、信号線駆動回路と走査線駆動回路の構成はこれに限定されない。

**【0115】**

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することが可能である。

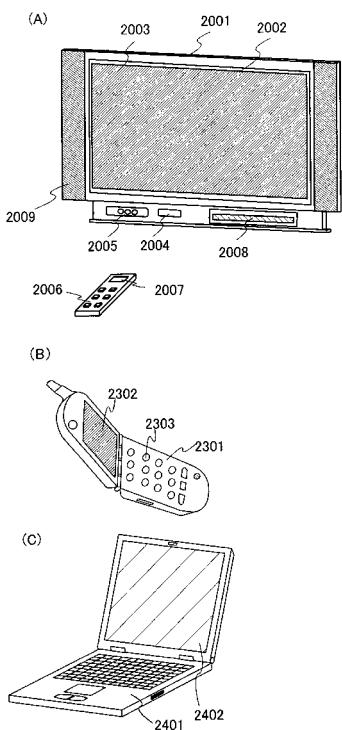

**(実施の形態7)****【0116】**

本発明により得られる表示装置によって、アクティブマトリクス型液晶モジュールに用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施できる。10

**【0117】**

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図11に示す。

**【0118】**

図11(A)はテレビジョン装置である。表示モジュールを、図11(A)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。20

**【0119】**

図11(A)に示すように、筐体2001に液晶素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向（送信者から受信者）又は双方向（送信者と受信者間、又は受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。30

**【0120】**

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面2003を視野角の優れた液晶表示パネルで形成し、サブ画面を低消費電力で表示可能な液晶表示パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面2003を液晶表示パネルで形成し、サブ画面を液晶表示パネルで形成し、サブ画面は点滅可能とする構成としても良い。

**【0121】**

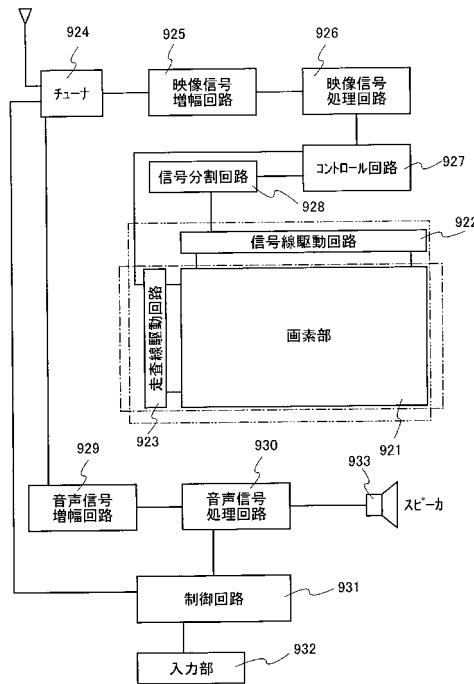

図12はテレビ装置の主要な構成を示すブロック図を示している。表示パネル900には、画素部921が形成されている。信号線駆動回路922と走査線駆動回路923は、表示パネル900にCOG方式により実装されていても良い。40

**【0122】**

その他の外部回路の構成として、映像信号の入力側では、チューナ924で受信した信号のうち、映像信号を增幅する映像信号増幅回路925と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路926と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路927などを有している。コントロール回路927は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路928を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

**【0123】**

チューナ 924 で受信した信号のうち、音声信号は、音声信号增幅回路 929 に送られ、その出力は音声信号処理回路 930 を経てスピーカ 933 に供給される。制御回路 931 は受信局（受信周波数）や音量の制御情報を入力部 932 から受け、チューナ 924 や音声信号処理回路 930 に信号を送出する。

#### 【0124】

勿論、本発明はテレビジョン装置に限定されず、コンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

#### 【0125】

図 11 (B) は携帯電話機 2301 の一例を示している。この携帯電話機 2301 は、表示部 2302、操作部 2303 などを含んで構成されている。表示部 2302 においては、上記実施の形態で説明した表示装置を適用することで、量産性を高めることができる。

#### 【0126】

また、図 11 (C) に示す携帯型のコンピュータは、本体 2401、表示部 2402 等を含んでいる。表示部 2402 に、上記実施の形態に示す表示装置を適用することにより、量産性を高めることができる。

#### 【0127】

本実施の形態は、他の実施の形態に記載した構成と組み合わせて実施することが可能である。

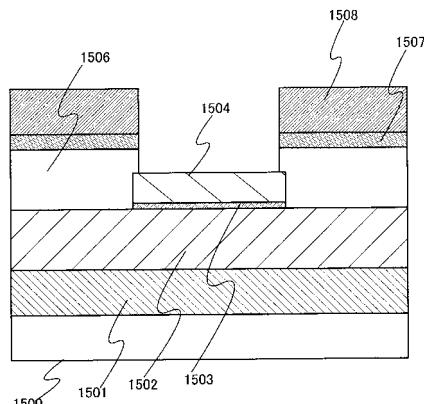

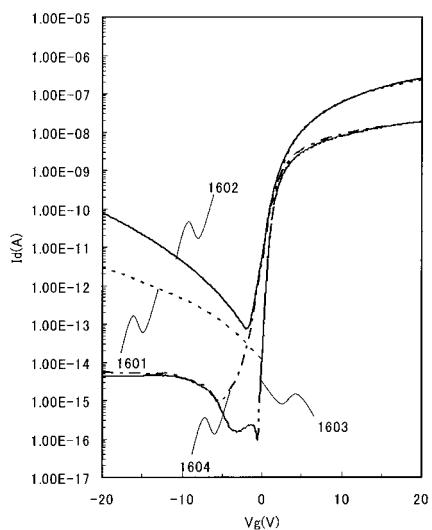

#### 【0128】

##### (実施の形態 8)

本実施の形態では上記実施の形態で説明した本発明のトランジスタの構成について、デバイスシミュレーションの結果について示す。図 15 には、デバイスシミュレーションに用いたトランジスタの構造について示し、図 16 には図 15 で示したトランジスタ構造の電流 - 電圧特性について示している。なお、デバイスシミュレーションには、Silvaco 社製デバイスシミュレータ "ATLAS" を用いた。

#### 【0129】

図 15 に示すトランジスタ構造の積層構造について説明する。図 15 に示す構造は、基板 1500、ゲート電極 1501、ゲート絶縁膜 1502、微結晶半導体膜 1503、チャネル保護層 1504、非晶質半導体膜 1506、不純物半導体層 1507、導電膜 1508（ソース電極、ドレイン電極）を順次形成したものである。なお、作製方法については実施の形態 1 で述べた通りである。積層される各膜としては、基板 1500 としてガラス基板を厚さ 100 nm、ゲート電極 1501 としてモリブデン膜 (Mo) を膜厚 150 nm、ゲート絶縁膜 1502 として窒化珪素膜 (Si<sub>3</sub>N<sub>4</sub>) を膜厚 300 nm、微結晶半導体膜 1503 として微結晶状態の珪素膜を膜厚 10 nm、チャネル保護層 1504 として窒化珪素膜 (Si<sub>3</sub>N<sub>4</sub>) を 90 nm、非晶質半導体膜 1506 として非晶質状態の珪素膜 200 nm、不純物半導体層 1507 としてリンが添加された非晶質珪素膜を膜厚 50 nm、導電膜 1508 としてはモリブデン膜 (Mo) を膜厚 150 nm、を挙げて説明する。なお、微結晶半導体膜 1503 及びチャネル保護層 1504 のチャネル長方向の長さは 10 μm、チャネル保護層 1504 上の端部に重畠して設けられる非晶質半導体膜 1506 の長さは 200 nm としている。また、デバイスシミュレーションについては、積層された各膜の物理的特性に基づいて行った。

#### 【0130】

また、非晶質半導体膜 1506 を構成する非晶質の半導体膜のデバイスシミュレーションにおけるパラメータを以下に示す数値に設定した。

#### 【0131】

アクセプタタイプ欠陥準位（テール状分布）の伝導帯端における状態密度 ( $n_{ta} = 3.0 \times 10^{21} [\text{cm}^{-3} \text{eV}]$ )、ドナータイプ欠陥準位（テール状分布）の価電子帯端における状態密度 ( $n_{td} = 4.0 \times 10^{20} [\text{cm}^{-3} \text{eV}]$ )、アクセプタタイプ欠陥準位（テール状分布）状態密度の減衰係数 ( $w_{ta} = 0.025 [\text{eV}]$ )、ドナータイプ欠陥

10

20

30

40

50

準位（テール状分布）状態密度の減衰係数（ $w_{td} = 0.05$  [eV]）、アクセプタタイプ欠陥準位（バンプ状分布）のピーク位置における状態密度（ $n_{ga} = 5.0 \times 10^{17}$  [/ $\text{cm}^3$  eV]）、ドナータイプ欠陥準位（バンプ状分布）のピーク位置における状態密度（ $n_{gd} = 5.0 \times 10^{17}$  [/ $\text{cm}^3$  eV]）、アクセプタタイプ欠陥準位（バンプ状分布）のピーク位置（ $e_{ga} = 0.28$  [eV]）、ドナータイプ欠陥準位（バンプ状分布）のピーク位置（ $e_{gd} = 0.79$  [eV]）、アクセプタタイプ欠陥準位（バンプ状分布）状態密度の減衰係数（ $w_{ga} = 0.1$  [eV]）、ドナータイプ欠陥準位（バンプ状分布）状態密度の減衰係数（ $w_{gd} = 0.2$  [eV]）、アクセプタ準位の裾野における電子の捕獲断面積（ $\sigma_{gtae} = 3.0 \times 10^{-15}$  [ $\text{cm}^2$ ]）、アクセプタ準位の裾野におけるホールの捕獲断面積（ $\sigma_{gtah} = 3.0 \times 10^{-13}$  [ $\text{cm}^2$ ]）、ドナー準位の裾野における電子の捕獲断面積（ $\sigma_{gtdc} = 3.0 \times 10^{-13}$  [ $\text{cm}^2$ ]）、ドナー準位の裾野におけるホールの捕獲断面積（ $\sigma_{gtdh} = 3.0 \times 10^{-15}$  [ $\text{cm}^2$ ]）、アクセプタのガウシアン分布における電子の捕獲断面積（ $\sigma_{giga} = 3.0 \times 10^{-15}$  [ $\text{cm}^2$ ]）、アクセプタのガウシアン分布におけるホールの捕獲断面積（ $\sigma_{gigh} = 3.0 \times 10^{-13}$  [ $\text{cm}^2$ ]）、ドナーのガウシアン分布における電子の捕獲断面積（ $\sigma_{gigd} = 3.0 \times 10^{-13}$  [ $\text{cm}^2$ ]）、ドナーのガウシアン分布におけるホールの捕獲断面積（ $\sigma_{gigd} = 3.0 \times 10^{-15}$  [ $\text{cm}^2$ ]）とした。

10

#### 【0132】

また、微結晶半導体膜1503を構成する微結晶状態の珪素膜のパラメータを以下に示す数値に設定した。なお、微結晶状態の珪素膜の欠陥密度を非晶質状態の珪素膜の10分の1とした。

20

#### 【0133】

アクセプタタイプ欠陥準位（テール状分布）の伝導帯端における状態密度（ $n_{ta} = 2.0 \times 10^{21}$  [/ $\text{cm}^3$  eV]）、ドナータイプ欠陥準位（テール状分布）の価電子帯端における状態密度（ $n_{td} = 4.0 \times 10^{19}$  [/ $\text{cm}^3$  eV]）、アクセプタタイプ欠陥準位（バンプ状分布）のピーク位置における状態密度（ $n_{ga} = 9.0 \times 10^{17}$  [/ $\text{cm}^3$  eV]）、ドナータイプ欠陥準位（バンプ状分布）のピーク位置における状態密度（ $n_{gd} = 5.0 \times 10^{17}$  [/ $\text{cm}^3$  eV]）とする。その他のパラメータは、アモルファスシリコン膜のパラメータと同じとした。

30

#### 【0134】

図16には、図15で示したトランジスタのデバイスシミュレーションの結果について示す。図16の曲線1601は、図15に示したトランジスタのソース電極に0V、ドレイン電極に14Vを印加した際のゲート電極に印加する電圧（ $V_g$ ）に応じたドレイン電極に流れる電流（ $I_d$ ）の変化について示したものである。また、図16の曲線1602は、図15におけるチャネル保護層1504の領域が非晶質珪素膜である場合に、ソース電極に0V、ドレイン電極に14Vを印加した際のゲート電極に印加する電圧（ $V_g$ ）に応じたドレイン電極に流れる電流（ $I_d$ ）の変化について示したものである。また図16の曲線1603は、図15に示したトランジスタのソース電極に0V、ドレイン電極に1Vを印加した際のゲート電極に印加する電圧（ $V_g$ ）に応じたドレイン電極に流れる電流（ $I_d$ ）の変化について示したものである。また、図16の曲線1604は、図15におけるチャネル保護層1504の領域が非晶質珪素膜である場合に、ソース電極に0V、ドレイン電極に1Vを印加した際のゲート電極に印加する電圧（ $V_g$ ）に応じたドレイン電極に流れる電流（ $I_d$ ）の変化について示したものである。

40

#### 【0135】

図16に示すトランジスタの電流-電圧特性をみればわかるように、本発明のトランジスタ構造は、ソースとドレインの間の電圧に依存することなく、トランジスタがオンになった際の電流量を変化させずに、トランジスタがオフになった際の電流量を減少させることができる。また図16より $V_g$ に対する $I_d$ の特性であるS値が向上していることがわかる。このトランジスタの特性の向上は、トランジスタのチャネル形成領域の膜厚が薄くなるので完全空乏型のトランジスタと同様にS値を改善すること、及びチャネル形成領域の

50

上部が絶縁膜とすることにより、生成電流及び再結合電流が発生しなくなり、トランジスタはオフになった際の電流量を減少させることができること、によるものである。上述の通り、本発明によって、電気特性が高く、オフ電流の低減を図ることができる薄膜トランジスタを具備する表示装置を提供することができ、且つ上述したように、歩留まりの低下を抑制しつつ、且つ寄生容量の増加及び製造コストの増加を抑えることができる。

【図面の簡単な説明】

【0136】

【図1】本発明の表示装置の作製方法を説明する断面図である。

【図2】本発明の表示装置の作製方法を説明する断面図である。

【図3】本発明の表示装置の作製方法を説明する断面図である。

10

【図4】本発明の表示装置の作製方法を説明する断面図である。

【図5】本発明の表示装置を説明する上面図である。

【図6】マイクロ波プラズマCVD装置を説明する上面図である。

【図7】本発明の表示装置を説明する図である。

【図8】本発明の表示装置を説明する図である。

【図9】本発明の表示装置を説明する図である。

【図10】本発明の表示装置を説明する図である。

【図11】本発明の表示装置を具備する電子機器を説明する図である。

【図12】本発明の表示装置を具備する電子機器を説明する図である。

【図13】本発明の表示装置が具備する薄膜トランジスタを説明する断面図である。

20

【図14】本発明の表示装置が具備する薄膜トランジスタを説明する断面図である。

【図15】シミュレーション計算を行ったトランジスタの断面構造を説明する図。

【図16】実施の形態8で示すトランジスタ構造の電流-電圧特性について示す図。

【符号の説明】

【0137】

100 基板

101 ゲート電極

102 ゲート絶縁膜

103 微結晶半導体膜

104 チャネル保護層

30

105 島状微結晶半導体膜

106 非晶質半導体膜

107 不純物半導体層

108 導電膜

108a ソース電極

108b ドレイン電極

109 絶縁膜

110 コンタクトホール

111 画素電極

151 レジスト

40

152 レジスト

171 穴部

172 穴部

173 穴部

174 幅

501 走査線

502 信号線

551 画素部

552 走査線駆動回路

553 信号線駆動回路

50

|           |          |    |

|-----------|----------|----|

| 5 5 4     | シフトレジスタ  |    |

| 5 5 5     | アナログスイッチ |    |

| 5 5 6     | シフトレジスタ  |    |

| 5 5 7     | パッファ     |    |

| 9 0 0     | 表示パネル    |    |

| 9 2 1     | 画素部      |    |

| 9 2 2     | 信号線駆動回路  | 10 |

| 9 2 3     | 走査線駆動回路  |    |

| 9 2 4     | チューナ     |    |

| 9 2 5     | 映像信号增幅回路 |    |

| 9 2 6     | 映像信号処理回路 |    |

| 9 2 7     | コントロール回路 |    |

| 9 2 8     | 信号分割回路   |    |

| 9 2 9     | 音声信号增幅回路 |    |

| 9 3 0     | 音声信号処理回路 |    |

| 9 3 1     | 制御回路     |    |

| 9 3 2     | 入力部      |    |

| 9 3 3     | スピーカ     |    |

| 1 0 1 0   | ロード室     |    |

| 1 0 1 1   | 反応室(1)   | 20 |

| 1 0 1 2   | 反応室(2)   |    |

| 1 0 1 3   | 反応室(3)   |    |

| 1 0 1 5   | アンロード室   |    |

| 1 0 2 0   | 共通室      |    |

| 1 0 2 1   | 搬送手段     |    |

| 1 0 2 2   | ゲートバルブ   |    |

| 1 0 2 3   | ゲートバルブ   |    |

| 1 0 2 4   | ゲートバルブ   |    |

| 1 0 2 5   | ゲートバルブ   |    |

| 1 0 2 6   | ゲートバルブ   | 30 |

| 1 0 2 8   | カセット     |    |

| 1 0 2 9   | カセット     |    |

| 1 3 0 1 a | 非晶質半導体膜  |    |

| 1 3 0 1 b | 非晶質半導体膜  |    |

| 1 4 0 1 a | 非晶質半導体膜  |    |

| 1 4 0 1 b | 非晶質半導体膜  |    |

| 1 5 0 0   | 基板       |    |

| 1 5 0 1   | ゲート電極    |    |

| 1 5 0 2   | ゲート絶縁膜   |    |

| 1 5 0 3   | 微結晶半導体膜  | 40 |

| 1 5 0 4   | チャネル保護層  |    |

| 1 5 0 6   | 非晶質半導体膜  |    |

| 1 5 0 7   | 不純物半導体層  |    |

| 1 5 0 8   | 導電膜      |    |

| 1 6 0 1   | 曲線       |    |

| 1 6 0 2   | 曲線       |    |

| 1 6 0 3   | 曲線       |    |

| 1 6 0 4   | 曲線       |    |

| 2 0 0 1   | 筐体       |    |

| 2 0 0 2   | 表示用パネル   | 50 |

|         |          |    |

|---------|----------|----|

| 2 0 0 3 | 主画面      |    |

| 2 0 0 4 | モデム      |    |

| 2 0 0 5 | 受信機      |    |

| 2 0 0 6 | リモコン操作機  |    |

| 2 0 0 7 | 表示部      |    |

| 2 0 0 8 | サブ画面     |    |

| 2 0 0 9 | スピーカー部   |    |

| 2 3 0 1 | 携帯電話機    |    |

| 2 3 0 2 | 表示部      |    |

| 2 3 0 3 | 操作部      | 10 |

| 2 4 0 1 | 本体       |    |

| 2 4 0 2 | 表示部      |    |

| 4 0 0 1 | 基板       |    |

| 4 0 0 2 | 画素部      |    |

| 4 0 0 3 | 信号線駆動回路  |    |

| 4 0 0 4 | 走査線駆動回路  |    |

| 4 0 0 5 | シール材     |    |

| 4 0 0 6 | 基板       |    |

| 4 0 0 8 | 液晶       |    |

| 4 0 0 9 | 薄膜トランジスタ | 20 |

| 4 0 1 0 | 薄膜トランジスタ |    |

| 4 0 1 3 | 液晶素子     |    |

| 4 0 1 4 | 配線       |    |

| 4 0 1 5 | 配線       |    |

| 4 0 1 6 | 接続端子     |    |

| 4 0 1 8 | F P C    |    |

| 4 0 1 9 | 異方性導電膜   |    |

| 4 0 3 0 | 画素電極     |    |

| 4 0 3 1 | 対向電極     |    |

| 4 0 3 5 | スペーサー    | 30 |

| 4 0 4 0 | 配線       |    |

| 4 5 0 1 | 基板       |    |

| 4 5 0 2 | 画素部      |    |

| 4 5 0 3 | 信号線駆動回路  |    |

| 4 5 0 4 | 走査線駆動回路  |    |

| 4 5 0 5 | シール材     |    |

| 4 5 0 6 | 基板       |    |

| 4 5 0 7 | 充填材      |    |

| 4 5 0 9 | 薄膜トランジスタ |    |

| 4 5 1 0 | 薄膜トランジスタ | 40 |

| 4 5 1 1 | 発光素子     |    |

| 4 5 1 2 | 導電性材料    |    |

| 4 5 1 4 | 配線       |    |

| 4 5 1 5 | 配線       |    |

| 4 5 1 6 | 接続端子     |    |

| 4 5 1 7 | 配線       |    |

| 4 5 1 8 | F P C    |    |

| 4 5 1 9 | 異方性導電膜   |    |

| 6 0 1 1 | 基板       |    |

| 6 0 1 2 | 画素部      | 50 |

|           |          |

|-----------|----------|

| 6 0 1 3   | 信号線駆動回路  |

| 6 0 1 4   | 走査線駆動回路  |

| 6 0 1 5   | F P C    |

| 6 0 2 1   | 基板       |

| 6 0 2 2   | 画素部      |

| 6 0 2 3   | 信号線駆動回路  |

| 6 0 2 4   | 走査線駆動回路  |

| 6 0 2 5   | F P C    |

| 6 0 3 1   | 基板       |

| 6 0 3 2   | 画素部      |

| 6 0 3 4   | 走査線駆動回路  |

| 6 0 3 5   | F P C    |

| 6 0 3 3 a | アナログスイッチ |

| 6 0 3 3 b | シフトレジスタ  |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 黒川 義元

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 河江 大輔

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 竹口 泰裕

(56)参考文献 特開平6-326314(JP,A)

特開2005-51211(JP,A)

特開2006-221162(JP,A)

特開2007-5508(JP,A)

特開2008-140984(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336、29/786