(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6219676号

(P6219676)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

G05F 3/24 (2006.01)

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)G05F 3/24

H01L 27/04Z

H

請求項の数 11 (全 12 頁)

(21) 出願番号 特願2013-226682 (P2013-226682)

(22) 出願日 平成25年10月31日 (2013.10.31)

(65) 公開番号 特開2014-106967 (P2014-106967A)

(43) 公開日 平成26年6月9日 (2014.6.9)

審査請求日 平成28年10月31日 (2016.10.31)

(31) 優先権主張番号 13/686,889

(32) 優先日 平成24年11月27日 (2012.11.27)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

エヌエックスピー ユーエスエイ インコ

ーポレイテッド

N X P U S A, I n c.

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 ジョン エス. チョイ

アメリカ合衆国 78735 テキサス州

オースティン メンラー ドライブ 7

624

最終頁に続く

(54) 【発明の名称】 ランプアップ電圧からの保護

## (57) 【特許請求の範囲】

## 【請求項 1】

電圧基準回路に動作可能に結合される電圧クランプ回路を備え、前記電圧基準回路は、第1のノードにおいて第1の電圧を受け取るように、および、第2のノードにおいて前記第1の電圧よりも小さい第2の電圧を出力するように構成されており、前記電圧基準回路は、前記第1の電圧のスルーレートと不相応な伝搬遅延を有する第1の増幅器を含み、前記電圧クランプ回路は第2の増幅器を含んでおり、前記第2の増幅器は、所定の電圧を受け取るために結合された第1の入力部と、前記第2のノードに結合された第2の入力部とを有し、前記第2の増幅器は、前記第1のノードから前記第2のノードへと流れる過剰な電流に比例するバイアス電流を受け取るように構成され、前記第2の増幅器の出力部は、前記第1の電圧の前記スルーレートによって前記第1のノードと前記第2のノードとの間のスニーク状態がトリガされることに応答して、前記第2のノードを駆動して前記第2の電圧の値を低減するように構成される、集積回路。

## 【請求項 2】

前記スニーク状態は、前記過剰な電流が前記第1のノードから前記第2のノードへと流れることを可能にする電流路を含む、請求項1に記載の集積回路。

## 【請求項 3】

前記電圧基準回路はバンドギャップ回路である、請求項1に記載の集積回路。

## 【請求項 4】

前記第2の増幅器は、該第2の電圧と、前記集積回路に提供されるデジタル電源電圧と

の間の差に比例して前記第2のノードにおける前記第2の電圧の値を低減するように構成される、請求項1に記載の集積回路。

【請求項5】

前記電圧クランプ回路は、パワー・オン・リセット(PoR)事象に応答してオンになるように構成される、請求項1に記載の集積回路。

【請求項6】

前記電圧クランプ回路は、前記PoR事象から所定の期間の後にオフになるように構成される、請求項5に記載の集積回路。

【請求項7】

回路を使用して第1のノードにおける第1の電圧を第2のノードにおける第2の電圧に変換するステップであって、前記回路は、前記第1のノードと前記第2のノードとの間に動作可能に結合された第1の増幅器を含み、前記第1のノードは、前記第2のノードに存在する第2の電圧よりも高い第1の電圧を受け取るように構成されており、前記回路は、少なくとも1つのアナログ供給電圧および少なくとも1つのデジタル供給電圧を受け取るように構成される、前記変換するステップと、

所定の電圧を受け取るために結合された第1の入力部と、前記第2のノードに結合された第2の入力部とを有する第2の増幅器を提供するステップであって、前記第2の増幅器は、第1のノードから第2のノードへと流れる過渡電流に比例するバイアス電流を受け取るように構成される、前記第2の増幅器を提供するステップと、

前記第1の電圧のスリーレートが前記第1のノードと前記第2のノードとの間にスニーケン状態を作り出すことに応答して、前記少なくとも1つのデジタル供給電圧を基準電圧として使用して前記スニーケン状態を解消するために、前記第2の増幅器が、前記第2のノードを駆動するステップとを含む、方法。

【請求項8】

前記第1の電圧は前記少なくとも1つのアナログ供給電圧である、請求項7に記載の方法。

【請求項9】

前記第1の増幅器が、前記第1の電圧のランプアップ時間よりも長い伝搬遅延を有する、請求項7に記載の方法。

【請求項10】

前記スニーケン状態を解消するステップは、前記第2の電圧を、前記基準電圧に基づいて定義される所定値以下に維持するステップを含む、請求項7に記載の方法。

【請求項11】

別の回路を過電圧状態から保護するステップをさらに含み、前記別の回路は前記第2のノードに動作可能に結合され、前記第2の電圧を受け取るように構成される、請求項7に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、概して電子デバイスに関し、より具体的には、ランプアップ電圧からの保護のためのシステムおよび方法に関する。

【背景技術】

【0002】

相補型金属酸化膜半導体(CMOS)技術が、集積回路(IC)を製造するために一般的に使用されている。最新のICの例は、マイクロプロセッサ、マイクロコントローラ、メモリなどを含む。概して、IC内の1つ以上の構成要素は「電圧基準」に基づいて動作する場合がある。このような電圧基準を提供するために、IC内に「電圧基準回路」が設計されている場合がある。

【0003】

電圧基準回路の一例が、「バンドギャップ回路」である。バンドギャップ回路は、約1

10

20

30

40

50

.25Vの値、または、0Kにおけるシリコンの理論上の1.22eV、すなわち、電子をその価電子帯からその伝導帯へと推進して可動電荷にするために必要とされるエネルギーを適切に近似する別の値を有する温度非依存電圧基準を出力するように構成される。たとえば、一般的なバンドギャップ回路は、開ループ構成において動作する、セルフカスコードMOS電界効果トランジスタ(SCM)構造と、1つ以上のバイポーラトランジスタ(複数の場合もあり)との1組を含む場合がある。

【0004】

なお、電流モードにより制御されるDC/DC変換器が、エラー増幅器クランプ回路を有することによって、急速な遷移応答出力におけるオーバーシュートを低減させることについて、特許文献1に記載されている。

10

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7,518,348号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

ランプアップ電圧からの保護のためのシステムおよび方法が必要とされている。

【課題を解決するための手段】

【0007】

上記問題点を解決するために、請求項1に記載の発明は、集積回路であって、第1のノードおよび第2のノードに動作可能に結合される電圧クランプ回路を備え、前記第1のノードは第1の電圧を受け取るように構成されており、前記第2のノードは前記第1の電圧よりも小さい第2の電圧を出力するように構成されており、前記電圧クランプ回路は、前記第1の電圧のスルーレートによって前記第1のノードと前記第2のノードとの間のスニーケ状態がトリガされることに応答して、前記第2の電圧を変更するように構成されることを要旨とする。

20

【0008】

請求項11に記載の発明は、回路の第1のノードまたは第2のノードの少なくとも一方を監視するステップであって、前記第1のノードは、第2のノードに存在する第2の電圧よりも高い第1の電圧を受け取るように構成されており、前記回路は、少なくとも1つのアナログ供給電圧および少なくとも1つのデジタル供給電圧を受け取るように構成される、前記監視するステップと、

30

前記第1の電圧のスルーレートが前記第1のノードと前記第2のノードとの間にスニーケ状態を作り出すことに応答して、前記少なくとも1つのデジタル供給電圧を基準電圧として使用して前記スニーケ状態を解消するステップとを含むことを要旨とする。

【図面の簡単な説明】

【0009】

【図1】いくつかの実施形態に応じた、1つ以上の集積回路を含む電子デバイスの一例の図。

40

【図2】いくつかの実施形態に応じた、集積回路の一例のプロック図。

【図3】いくつかの実施形態に応じた、ランプアップ電圧からの保護を提供するように構成される回路の一例の回路図。

【図4】いくつかの実施形態に応じたランプアップからの保護動作の一例を示すグラフ。

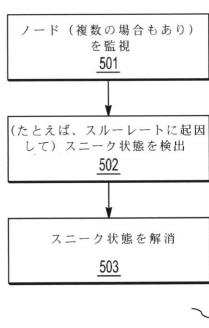

【図5】いくつかの実施形態に応じたランプアップ電圧からの保護のための方法の一例のフローチャート。

【発明を実施するための形態】

【0010】

本明細書に開示の実施形態は、ランプアップ電圧からの保護のためのシステムおよび方法を対象とする。多くの実施態様において、これらのシステムおよび方法は、たとえば、

50

コンピュータ・システムまたは情報技術(ＩＴ)製品(たとえば、サーバ、デスクトップ、ラップトップ、スイッチ、ルータなど)、遠隔通信ハードウェア、消費者向け装置または電化製品(たとえば、携帯電話機、タブレット、テレビ、カメラ、音響システムなど)、科学機器、産業ロボット、医療用または実験用電子機器(たとえば、撮像、診断、もしくは治療用機器など)、運搬用車両(たとえば、自動車、バス、列車、船舶、航空機など)、軍装備品などを含む、広範な電子デバイス内に組み込まれてもよい。より一般的には、本明細書において説明するシステムおよび方法は、1つ以上の電子部品または構成要素を有する任意のデバイスまたはシステム内に組み込まれてもよい。

#### 【0011】

図1を参照すると、電子デバイス100のブロック図が示される。いくつかの実施形態において、電子デバイス100は、上記の電子デバイスのいずれか、または任意の他の電子デバイスであってもよい。図示されるように、電子デバイス100は、1つ以上のプリント回路基板(PCB)101を含み、当該PCB101のうちの少なくとも1つは、1つ以上の電子チップ(複数の場合もあり)または集積回路(複数の場合もあり)102を含む。いくつかの実施形態において、集積回路(複数の場合もあり)102は、下記により詳細に説明するシステムおよび方法のうちの1つ以上を実施してもよい。

10

#### 【0012】

集積回路(複数の場合もあり)102の例は、たとえば、システム・オン・チップ(SoC)、特定用途向け集積回路(ASIC)、デジタル信号プロセッサ(DSP)、フィールドプログラマブル・ゲート・アレイ(FPGA)、プロセッサ、マイクロプロセッサ、コントローラ、マイクロコントローラ(MCU)などを含んでもよい。付加的にまたは代替的に、集積回路(複数の場合もあり)102は、たとえば、ランダム・アクセス・メモリ(RAM)、スタティックRAM(SRAM)、磁気抵抗RAM(MRAM)、不揮発性RAM(「フラッシュ」メモリなどのNVRAM)、および/または同期DRAM(SDRAM)などのダイナミックRAM(DRAM)、ダブル・データ・レート(たとえば、DDR、DDR2、DDR3など)RAM、消去可能プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)などのメモリ回路またはデバイスを含んでもよい。付加的にまたは代替的に、集積回路(複数の場合もあり)102は、たとえば、アナログ-デジタル変換器(ADC)、デジタル-アナログ変換器(DAC)、位相ロックループ(PLL)、発振器、フィルタ、增幅器、変圧器などの、1つ以上の混合信号またはアナログ回路を含んでもよい。付加的にまたは代替的に、集積回路(複数の場合もあり)102は、1つ以上の微小電気機械システム(MEMS)、ナノ電気機械システム(NEMS)などを含んでもよい。

20

#### 【0013】

このように、集積回路(複数の場合もあり)102はいくつかの異なる部分、エリア、または領域を含んでもよい。これらのさまざまな部分は、1つ以上の処理コア、キャッシュメモリ、内部バス(複数の場合もあり)、タイミングユニット、コントローラ、アナログセクション、機械的要素などを含んでもよい。したがって、さまざまな実施形態において、集積回路(複数の場合もあり)102は、2つ以上の供給電圧(たとえば、2つ、3つ、4つなど)を受け取るように構成される回路を含んでもよい。たとえば、デュアル給電回路が、アナログ構成要素に給電するように構成されるアナログ供給電圧、および、論理構成要素またはデジタル構成要素に給電するように構成されるデジタル供給電圧を受け取ってもよい。いくつかの実施態様において、たとえば、アナログ供給電圧はほぼ5V±10%程度であってもよく、一方でデジタル供給電圧はほぼ1.2V±10%程度であってもよい。他のタイプの回路が任意の適切な数の供給電圧を受け取ってもよい。

30

#### 【0014】

概して、集積回路(複数の場合もあり)102は、たとえば、ボール・グリッド・アレイ(BGA)パッケージングなどの任意の適切なパッケージング技術を使用してPCB101上に取り付けられるように構成された電子構成要素パッケージ内に配置されてもよい。いくつかの実施態様において、PCB101は、電子デバイス100内に機械的に取り

40

50

付けられるか、または電子デバイス 100 に固定されてもよい。なお、いくつかの実施態様において、PCB 101 は、さまざまな形態をとってもよく、かつ / または、集積回路（複数の場合もあり）102 に加えて複数の他の要素もしくは構成要素を含んでもよい。

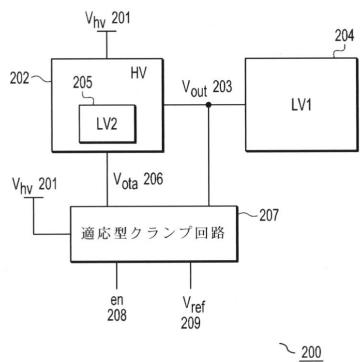

【0015】

図 2 は、いくつかの実施形態に応じた、図 1 において説明した集積回路（複数の場合もあり）102 の一例を示す集積回路 200 のブロック図である。図示されるように、集積回路 200 は、高電圧供給電圧（ $V_{hv}$ ）201 を受け取るように構成される高電圧（HV）回路 202 を含む。HV 回路 202 は、第 1 の低電圧（LV1）回路 204 に動作可能に結合され、当該低電圧回路に出力電圧（ $V_{out}$ ）203 を提供するように構成される。HV 回路 202 は、適応型クランプ回路 207 にも動作可能に結合され、当該適応型クランプ回路に演算相互コンダクタンス増幅器（OTA）電圧出力（ $V_{t_a}$ ）を提供するように構成される。この例において、HV 回路 202 は、第 2 の低電圧（LV2）回路 205 を含んでもよい。

【0016】

適応型クランプ回路 207 は  $V_{hv}$  201 を受け取るように構成され、 $V_{out}$  203 のノード（下記図 3 により詳細に図示する）に動作可能に結合される。加えて、適応型クランプ回路 207 は、イネーブル信号（en）208 および基準電圧（ $V_{ref}$ ）209 を受け取るように構成される。

【0017】

「高電圧」および「低電圧」という用語は、概して、特定の回路が別の回路のものよりも高い供給電圧によって動作することを示すのに使用される。概して、HV 回路は LV 回路よりも厚い酸化物デバイスを有してもよく、かつ / または低圧回路よりも多くの電力を使用してもよい。たとえば、HV 回路 202 はバンドギャップ基準回路であってもよく、LV1 回路 204 は HV 回路 202 によって提供されるより低い電圧（たとえば、バンドギャップ電圧）（すなわち、 $V_{out}$  203）に基づいて動作する任意の他のアナログ回路またはデジタル回路であってもよい。

【0018】

いくつかの実施態様において、 $V_{hv}$  201 は、外部電源（図示せず）によって I C 200 に提供されるアナログ供給電圧であってもよく、たとえば、ほぼ  $5V \pm 10\%$  程度であってもよく、一方で  $V_{ref}$  209 は、別の外部電源（図示せず）によって I C 200 に提供されるデジタル供給電圧であってもよく、ほぼ  $1.2V \pm 10\%$  程度であってもよい。その一方で、LV1 回路 204 は HV 回路 202 の内部生成供給電圧  $V_{out}$  203 を受け取ってもよく、当該電圧はほぼ  $0.9V \pm 10\%$  程度であってもよい。しかしながら、本開示に照らして、HV 回路 202、適応型クランプ回路 207、および LV1 回路 204 に供給される正確な電圧（すなわち、 $V_{hv}$  201、 $V_{out}$  203、および  $V_{ref}$  209）は技術、用途などのタイプに応じて変わってもよいことを理解されたい。

【0019】

いくつかの実施態様において、適応型クランプ回路 207 は、en 信号 208 の印加に応答して動作するように構成されてもよい。たとえば、状況によっては、en 信号 208 は、「パワー・オン・リセット」（POR）事象に関連して提供されてもよい。POR 事象は、電子デバイスもしくはその部分（複数の場合もあり）に対する電力がオンになるのに応答して I C 200 によってもしくは I C 200 上で実行される 1 つ以上の動作、または、I C 200 を既知の状態におくように構成されるリセット信号を作成する他のコマンドを含んでもよい。付加的にまたは代替的に、POR 事象の所定の時間量（たとえば、約 10 秒または約  $20 \mu$  秒）の後に en 信号 208 が適応型クランプ回路 207 へ提供されることが中止されてもよい。

【0020】

動作中、適応型クランプ回路 207 は  $V_{t_a}$  206 を受け取り、 $V_{out}$  203 を  $V_{ref}$  209 と比較して、 $V_{out}$  203 が、 $V_{out}$  203 と  $V_{ref}$  209 との間の差に比例して変更されるように構成されてもよい。このように、適応型クランプ回路 20

10

20

30

40

50

7 は、 LV1 回路 204 および / または LV2 回路 205 を、高電圧供給に不用意に露出されることから保護することができる。このような露出は、たとえば、 I C 200 の電源投入の間に  $V_{h.v}201$  のスルーレートが速いことに起因して引き起こされる場合がある。特に、場合によっては、  $V_{h.v}201$  の変化の速度は LV2 回路 205 の伝搬遅延よりも速い場合があり、したがって  $V_{h.v}201$  のノードと  $V_{o.u.t}203$  のノードとの間に「スニーク経路」または「スニーク状態」が生じ、このスニーク経路は、適応型クランプ回路 207 がなければ、過剰な電流または望ましくない電流が  $V_{h.v}201$  のノードから  $V_{o.u.t}203$  のノードへと流れることを可能にする。

#### 【0021】

したがって、いくつかの実施形態において、適応型クランプ回路 207 は、  $V_{h.v}201$  のノードおよび / または  $V_{o.u.t}203$  のノードを監視してもよい。その後、  $V_{h.v}201$  のスルーレートによって  $V_{h.v}201$  のノードおよび / または  $V_{o.u.t}203$  のノードの間のスニーク状態が生じることに応答して、適応型クランプ回路 207 はスニーク状態を解消するように動作してもよい。

#### 【0022】

いくつかの実施態様において、図 2 に示すモジュールまたはブロックは、指定動作を実行する実行するように構成される処理回路、論理機能、他の回路および / またはデータ構造を表してもよい。これらのモジュールは別個のブロックとして図示されるが、他の実施形態において、これらのモジュールによって実行される動作のうちの少なくともいくつかは組み合わされたより少ないブロックであってもよい。たとえば、場合によっては、適応型クランプ回路 207 は HV 回路 202 内に組み込まれてもよい。逆に、モジュール 202、204、205、および / または 207 のうちの任意の所与のモジュールが、その動作が 2 つ以上の論理ブロックの間で分割されるように実装されてもよい。特定の構成によって図示されるが、他の実施形態において、これらのさまざまなモジュールまたはブロックは、他の適切な方法によって再構成されてもよい。

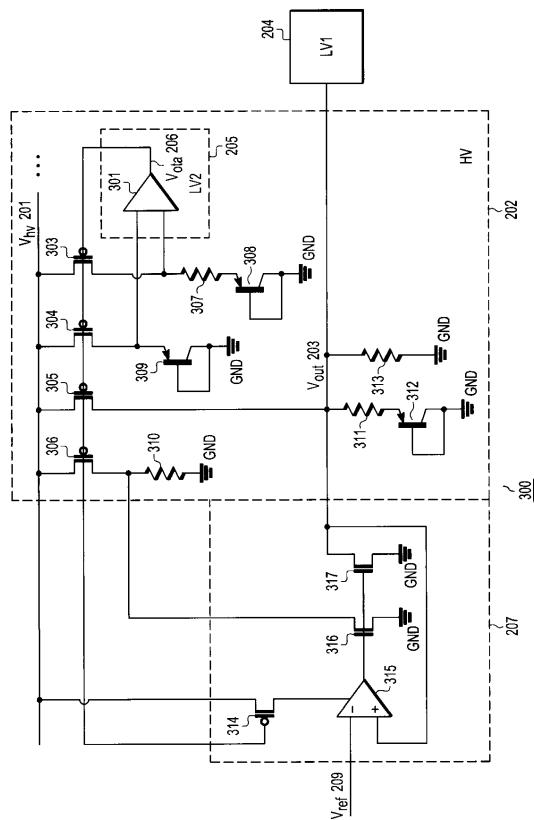

#### 【0023】

図 3 は、いくつかの実施形態に応じた、ランプアップ電圧からの保護を提供するように構成される回路 300 の一例の回路図である。この特定の例において、 HV 回路 202 は、 OTA 301 を有する LV2 回路 205 を含むバンドギャップ基準回路である。 OTA 301 の出力が  $V_{o.t.a}206$  を生成し、  $V_{o.t.a}206$  は P 型金属酸化膜半導体 (PMOS) トランジスタ 303 ~ 306 のゲートに動作可能に結合される。 PMOS トランジスタ 303 ~ 306 は PMOS トランジスタ 303 ~ 306 ら自体のソースを  $V_{h.v}201$  に結合される。 PMOS トランジスタ 303 のドレインは抵抗器 307 に動作可能に結合されており、当該抵抗器は、 PNP バイポーラ接合トランジスタ (BJT) 308 のエミッタに動作可能に結合されており、当該トランジスタのベースおよびコレクタはグランド (Gnd) に動作可能に結合される。 PMOS トランジスタ 303 のドレインは OTA 301 の第 1 の入力にも動作可能に結合される。

#### 【0024】

PMOS トランジスタ 304 のドレインは BJT 309 のエミッタに動作可能に結合されており、当該 BJT のベースおよびコレクタは Gnd に結合される。 PMOS トランジスタ 304 のドレインは OTA 205 の第 2 の入力にも動作可能に結合される。 PMOS トランジスタ 305 のドレインは  $V_{o.u.t}203$  のノードにおいて抵抗器 311 に動作可能に結合されており、  $V_{o.u.t}203$  のノードは、 BJT 312 のエミッタに動作可能に結合されており、当該 BJT のベースおよびコレクタは Gnd に動作可能に結合されている。 PMOS トランジスタ 306 のドレインは抵抗器 310 に動作可能に結合されており、当該抵抗器は Gnd に動作可能に結合される。もう 1 つの抵抗器 313 が、  $V_{o.u.t}203$  のノードと Gnd との間に動作可能に結合される。

#### 【0025】

動作中、 HV 回路 202 は  $V_{h.v}201$  を受け取り、バンドギャップ電圧  $V_{o.u.t}203$  を生成する。 OTA 301 は 1 つ以上の低電力要素を含んでもよく、場合によっては、

10

20

30

40

50

その信号伝搬遅延は、 $V_{h_v}201$ のスルーレートに不相応であってもよい。言い換れば、特定の閾値の後、OTA301によって提供されるフィードバック経路は、 $V_{h_v}201$ の変化の速度についていくことが可能でなくてもよい。したがって、望ましくない電流または過剰な電流が、HV回路202内の「スニーク経路」を通じて $V_{h_v}201$ から（たとえば、PMOSトランジスタ305を通じて） $V_{out}203$ への方向において一時的に流れてもよい。このような「スニーク状態」は、 $V_{out}203$ の値を増大させ、LV1回路204および/またはLV2回路205の動作に悪影響を及ぼす場合がある。

#### 【0026】

適応型クランプ回路207はスニーク状態を解消するように動作することができる。特に、この例において、適応型クランプ回路207は、適応型クランプ回路207のソースが $V_{h_v}201$ に動作可能に結合されており、適応型クランプ回路207のゲートがPMOSトランジスタ303～306のゲートに動作可能に結合されており、適応型クランプ回路207のドレインが増幅器315をバイアスするPMOSトランジスタ314を含む。増幅器315は、増幅器315の反転入力において $V_{ref}209$ を受け取り、増幅器315の非反転入力において $V_{out}203$ を受け取ってもよい。増幅器315の出力はN型MOS(NMOS)トランジスタ316および317のゲートに動作可能に結合される。NMOSトランジスタ316のソースはPMOSトランジスタ306のドレインに動作可能に結合されており、NMOSトランジスタ316のドレインはGndに動作可能に結合される。NMOSトランジスタ317のソースは $V_{out}203$ のノードに動作可能に結合されており、NMOSトランジスタ317のドレインはGndに動作可能に結合される。

#### 【0027】

いくつかの実施態様において、NMOSトランジスタ316のチャネル長はPMOSトランジスタ306、305、304、および/または303のチャネル長と同じであってもよい。それゆえ、NMOSトランジスタ316のソースにおいて受け取られる電流は、HV回路202内を循環する過渡電流に比例するテール電流であってもよい。言い換れば、増幅器315は、 $V_{h_v}201$ のスルーレートに起因してHV回路202を流れている過剰な過渡電流に比例するバイアス電流を受け取るように構成されている。このように、適応型クランプ回路207は $V_{h_v}201$ の供給の変化(スルーリング)を効果的に検出する。

#### 【0028】

増幅器315の出力は、 $V_{out}203$ の値が、 $V_{out}203$ と $V_{ref}209$ との間の差に比例するように低減され、したがってHV回路202内のスニーク状態を解消するように構成される。場合によっては、イネーブルNMOSトランジスタまたはスイッチ(図示せず)が、PMOSトランジスタ314のドレインと増幅器315との間に動作可能に結合されてもよい。イネーブルトランジスタのゲートは、図2に示すen信号208を受け取るように構成されてもよく、en信号208はPOR信号などであってもよい。したがって、適応型クランプ回路207は、電源投入などの間の $V_{h_v}201$ における電圧のランプアップに対するLV1回路204の脆弱性を改善することができ、それ以外のときにはオフになることによってエネルギーを節約することができる。

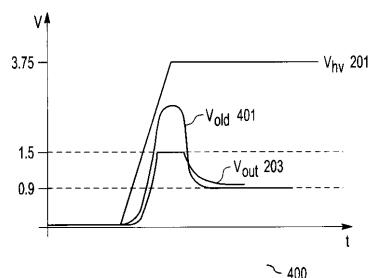

#### 【0029】

図4は、いくつかの実施形態に応じたランプアップからの保護動作の一例を示すグラフ400を示す。特に、 $V_{h_v}201$ に関するランプアップのシナリオを示しており、 $V_{h_v}201$ は所与の期間内に(たとえば、1000V/ミリ秒の速度で)0Vから3.75Vになる。適応型クランプ回路207の無い状態が $V_{1d}401$ によって示されており、1.5Vを十分に超えてピークに達し、その後所望の $V_{out}$ に落ち着く。この場合、所望の $V_{out}$ 値は、LV1回路204に提供されることになる0.9V(たとえば、バンドギャップ基準電圧)である。対照的に、適応型クランプ回路207を使用するとき、 $V_{out}203$ は1.5Vにクランピングされた後、0.9Vの $V_{out}$ に落ち着く。それゆえ、適応型クランプ回路207は、LV1回路204を、1.5Vよりも大きい電圧

10

20

30

40

50

を受け取ることから効果的に保護する。

【0030】

なお、図4に示す電圧値は説明を容易にするために提供されているに過ぎない。任意の所与の用途において、それらの電圧値および／またはスルーレート（複数の場合もあり）は、特定の用途または設計要件に応じて変化してもよい。

【0031】

図5は、ランプアップ電圧からの保護のための方法500の一例のフローチャートである。いくつかの実施態様において、方法500は、少なくとも部分的に、図2および図3に示す適応型クランプ回路207によって実行されてもよい。図示されるように、ブロック501において、方法500は、高電圧回路内の1つ以上のノードを監視することを含んでもよい。たとえば、適応型クランプ回路207は、HV回路202の $V_{h_v}201$ および／または $V_{out}203$ を監視してもよい。

10

【0032】

ブロック502において、方法500は、スニーク状態を検出することを含んでもよい。たとえば、適応型クランプ回路207が、PMOSトランジスタ314を通じて、過剰な電流がHV回路202内のスニーク経路を流れていることを検出してもよい。その後、ブロック503において、方法500は、スニーク状態を解消することを含んでもよい。たとえば、適応型クランプ回路207は、 $V_{ref}209$ を $V_{out}203$ と比較してもよく、 $V_{out}203$ から $V_{ref}209$ と $V_{out}203$ との2つの間の差に比例した電圧を減算し、すなわち、 $V_{out}203$ を選択されている閾値を下回った状態にしてもよい。いくつかの実施態様において、 $V_{ref}209$ はIC200に対する低電圧供給電圧（たとえば、ほぼ1.2V±10%程度）であってもよい。

20

【0033】

本明細書、特に図2～図5に関連して説明されたさまざまな動作は、処理回路、電子ハードウェア、またはこれらの組み合せにおいて実施されてもよいことを理解されたい。所与の方法の各動作が実行される順序は変更されてもよく、本明細書に示すシステムのさまざまな要素は追加、結合、並べ替え、省略、改変などされてもよい。本明細書に記載の発明（複数の場合もあり）は、すべてのこのような改変および変更を包含することが意図されており、したがって、上記の記載は限定的な意味ではなく例示的な意味においてみなされるべきである。

30

【0034】

上述のように、いくつかの実施態様において、適応型クランプ回路207は、 $V_{h_v}201$ におけるランプアップ電圧に対するLV1回路204の脆弱性を改善することができる。たとえば、適応型クランプ回路207は、LVデバイス（たとえば、LV1回路204）をそれらの信頼性範囲を超える電圧に露出することなく、高いスルーレートにおいてHV供給（たとえば、 $V_{hs}201$ ）をランプアップする（立ち上げる）能力を提供することができる。

【0035】

状況によっては、適応型クランプ回路207は、最大100V／ミリ秒の $V_{h_v}201$ のスルーレートの結果として生じるスニーク経路を解消することが可能であってもよい。付加的にまたは代替的に、適応型クランプ回路207は、最大1000V／ミリ秒の $V_{h_v}201$ のスルーレートの結果として生じるスニーク経路を解消することが可能であってもよい。たとえば、図3に示す実施形態は、ミラー電流を活用して $V_{out}203$ をクランピングする動作を加速してもよい。言い換えれば、スニーク状態、すなわち過剰な電流を作り出す同じメカニズムが、検出およびクランピングを促進するために使用されてもよい。

40

【0036】

たとえば、IC200がデュアル給電回路である場合（または、3つ以上の供給電圧を受け取るように構成される場合）、ICは、外部回路からのデジタル供給電圧または論理供給電圧であって、 $V_{ref}209$ として使用され得る電圧を受け取ってもよく、デジタ

50

ル供給電圧または論理供給電圧は I C 2 0 0 がその目的のために追加の基準電圧を生成する必要なしに V<sub>u t</sub> 2 0 3 をクランピングするために使用されてもよい。さらに、電源の優先順位付けに関して、上述のシステムおよび方法は、( I C 2 0 0 に対するアナログ電源およびデジタル電源の間で) いずれの電源が最初にオンにされるかにかかわらず動作するように設計されることに留意されたい。たとえば、I C 2 0 0 に対するアナログ電源がデジタル電源または論理電源の前にオンになる場合(たとえば、V<sub>h v</sub> 2 0 1 が 5 V であり、一方で V<sub>r e f</sub> が 0 V である)、V<sub>u t</sub> 2 0 3 がグランドにクランピングされ、したがって L V 1 回路 2 0 4 が保護される。逆に、アナログ電源の前に I C 2 0 0 に対するデジタル電源または論理電源がオンになる場合、V<sub>h v</sub> 2 0 1 から V<sub>u t</sub> 2 0 3 へのスニーク経路は存在しない。

10

#### 【 0 0 3 7 】

さらに、適応型クランプ回路 2 0 7 は小型なフットプリントを有し、V<sub>u t</sub> 2 0 3 の出力レベルを損なわない。対照的に、従来の容量性結合のソリューション(たとえば、スルー・レート・レール検出器など)は、フットプリントが大きく、かつ/またはラッチ・タイム・アウト値が長く、それによって I C 2 0 0 の始動タイミングが損なわれる場合がある。

#### 【 0 0 3 8 】

例示的な、限定ではない実施形態において、集積回路は、第 1 のノードおよび第 2 のノードに動作可能に結合されている電圧クランプ回路を含んでもよく、第 1 のノードは第 1 の電圧を受け取るように構成されており、第 2 のノードは第 1 の電圧よりも小さい第 2 の電圧を出力するように構成されており、電圧クランプ回路は、第 1 の電圧のスルーレートによって第 1 のノードと第 2 のノードとの間のスニーク状態がトリガされることに応答して第 2 の電圧を変更するように構成される。たとえば、スニーク状態は、意図しない電流が第 1 のノードから第 2 のノードへと流れることを可能にする傾向にある電流路を含んでもよい。

20

#### 【 0 0 3 9 】

また、第 1 のノードおよび第 2 のノードは、電圧基準回路の一部であってもよい。たとえば、電圧基準回路は、バンドギャップ回路であってもよい。電圧基準回路は、第 1 の電圧のスルーレートと不相応な伝搬遅延を有する少なくとも 1 つの要素を含んでもよい。たとえば、少なくとも 1 つの要素は第 1 の増幅器を含んでもよい。その場合、電圧クランプ回路は第 2 の増幅器を含んでおり、該第 2 の増幅器は、第 1 のノードから第 2 のノードへと流れる過剰な電流に比例するバイアス電流を受け取るように構成される。第 2 の増幅器は、該第 2 の電圧と、集積回路に提供されるデジタル電源電圧との間の差に比例して前記第 2 のノードにおける前記第 2 の電圧の値を低減するように構成されてもよい。

30

#### 【 0 0 4 0 】

いくつかの実施態様において、電圧クランプ回路は、パワー・オン・リセット( P o R )事象に応答してオンになるように構成されてもよい。付加的にまたは代替的に、電圧クランプ回路は、 P o R 事象の所定の期間の後にオフになるように構成されてもよい。

#### 【 0 0 4 1 】

別の例示的な、限定ではない実施形態において、方法は、回路の第 1 のノードまたは第 2 のノードの少なくとも一方を監視するステップを含んでもよく、第 1 のノードは、第 2 のノードに存在する第 2 の電圧よりも高い第 1 の電圧を受け取るように構成されており、回路は、少なくとも 1 つのアナログ供給電圧および少なくとも 1 つのデジタル供給電圧を受け取るように構成されている。方法は、第 1 の電圧のスルーレートが第 1 のノードと第 2 のノードとの間にスニーク状態を作り出すのに応答して、少なくとも 1 つのデジタル供給電圧を基準電圧として使用してスニーク状態を解消するステップを含んでもよい。たとえば、スニーク状態は、過剰な電流が第 1 のノードから第 2 のノードへと流れのに有利にはたらく場合があり、状況によっては、第 1 の電圧は少なくとも 1 つのアナログ供給電圧であってもよい。

40

#### 【 0 0 4 2 】

50

場合によっては、第1のノードと第2のノードとの間に動作可能に結合されている回路要素が、第1の電圧の立ち上がり時間よりも長い伝搬遅延を有してもよい。また、スニーケ状態を解消するステップは、第2の電圧を、基準電圧に基づいて定義される所定値以下に維持するステップを含んでもよい。付加的にまたは代替的に、第2の電圧を所定値以下に維持するステップは、第2の電圧が、第2の電圧と基準電圧との間の差に比例して変更されるステップを含んでもよい。

#### 【0043】

たとえば、第1のノードおよび第2のノードが第1の回路の一部であってもよく、第1の回路が第1の増幅器を含んでもよい場合、方法は、第2の増幅器を提供するステップであって、該第2の増幅器は、第1のノードから第2のノードへと流れる過剰な電流に比例するバイアス電流を受け取るように構成される、前記第2の増幅器を提供するステップを含んでもよい。第1の回路はバンドギャップ電圧回路である。方法は、回路を過電圧状態から保護するステップを含んでもよく、回路は第2のノードに動作可能に結合されており、第2の電圧を受け取るように構成される。

10

#### 【0044】

ここでも、監視するステップおよび解消するステップは、パワー・オン・リセット（P o R）事象に応答して行われてもよい。付加的にまたは代替的に、P o R事象の所定の期間の後に監視するステップおよび解消するステップが行われることが中止されてもよい。

#### 【0045】

20

本明細書において、具体的な実施形態を参照して本発明（複数の場合もあり）を説明したが、添付の特許請求の範囲に明記される本発明（複数の場合もあり）の範囲から逸脱することなくさまざまな改変および変更をなすことができる。たとえば、バンドギャップ回路のコンテキストにおいて提示されるが、本明細書に記載のさまざまなシステムおよび方法は、他のタイプの電圧基準回路、または他のタイプの回路において実装されてもよい。したがって、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明（複数の場合もあり）の範囲内に含まれることが意図される。本明細書において具体的な実施形態に関して記載されるいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるように意図されない。

30

#### 【0046】

別途記載されない限り、「第1の」および「第2の」などの用語は、このような用語が説明する要素間で適宜区別するように使用される。したがって、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されない。「結合される」または「動作可能に結合される」という用語は、接続されるとして定義されるが、必ずしも直接ではなく、必ずしも機械的ではない。「1つ（“a” and “an”）」という用語は、別途指定されない限り、1つ以上として定義される。「備える（comprise）」（ならびに「comprises」および「comprising」のようなcompriseの任意の変形形）、「有する（have）」（ならびに「has」および「having」のようなhaveの任意の変形形）、「含む（include）」（ならびに「includes」および「including」のようなincludeの任意の変形形）、ならびに「包含する（contain）」（ならびに「contains」および「containing」などのcontainの任意の変形形）といった用語は非限定連結動詞である。結果として、1つ以上の要素を「備える」、「有する」、「含む」または「包含する」システム、デバイス、または装置は、それらの1つ以上の要素を保持するが、これらの1つ以上の要素のみを保持するようには限定されない。同様に、1つ以上の動作を「備える」、「有する」、「含む」または「包含する」方法またはプロセスは、それらの1つ以上の動作を保持するが、それらの1つ以上の動作のみを保持するように限定されない。

40

【図1】

【図3】

【図2】

【図4】

【図5】

~ 500

---

フロントページの続き

(72)発明者 リチャード チトフ ラーラ サエズ

ブラジル国 13085-000 サンパウロ カンピーナス エストラーダ ダ ロディア 7

150 シーエス 19

(72)発明者 ルイス エドゥアルド ルエダ ゲレロ

オランダ国 2624HA サウスホランド デルフト ロラント ホルストラーン 45

審査官 柳下 勝幸

(56)参考文献 再公表特許第2005/101156 (JP, A1)

特開2004-318604 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 05 F 3/00 - 3/30

H 01 L 21/822

H 01 L 27/04