(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6125521号

(P6125521)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

(51) Int.Cl.

F 1

H01L 21/683 (2006.01)

H01L 21/68

R

H01L 21/3065 (2006.01)

H01L 21/302

1 O 1 G

H02N 13/00 (2006.01)

H02N 13/00

D

請求項の数 13 (全 20 頁)

(21) 出願番号 特願2014-543598 (P2014-543598)

(86) (22) 出願日 平成24年11月23日 (2012.11.23)

(65) 公表番号 特表2015-504609 (P2015-504609A)

(43) 公表日 平成27年2月12日 (2015.2.12)

(86) 國際出願番号 PCT/US2012/066467

(87) 國際公開番号 WO2013/078465

(87) 國際公開日 平成25年5月30日 (2013.5.30)

審査請求日 平成27年11月20日 (2015.11.20)

(31) 優先権主張番号 13/684,065

(32) 優先日 平成24年11月21日 (2012.11.21)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/563,526

(32) 優先日 平成23年11月23日 (2011.11.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 592010081

ラム・リサーチ コーポレーション

LAM RESEARCH CORPORATION

アメリカ合衆国、カリフォルニア 945

38, フレモント, クッシング パークウェイ 4650

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(74) 代理人 100113527

弁理士 堀研一

(72) 発明者 サトー・アーサー

アメリカ合衆国 カリフォルニア州 945

38-6470 フレモント, クッシング

・パークウェイ, 4650

最終頁に続く

(54) 【発明の名称】中間周波数RF帯域の高電圧バイアス電力のためのバイパスコンデンサ

## (57) 【特許請求の範囲】

## 【請求項1】

プラズマチャンバにおいてアークRF信号を分離させるためのシステムであって、

プラズマチャンバであって、

トップ電極と、

半導体ウエハを支えるための静電チャックと、

前記静電チャックの表面内の複数のクランプ電極の少なくとも1つと前記静電チャックのベース板との間に結合されたコンデンサであって、1.9ナノファラッドを上回る静電容量を有し、前記静電チャックの内部空間内に配される、コンデンサと、

を含むプラズマチャンバと、

前記静電チャックの前記表面内の対応する複数のリフトピン穴内に支えられた複数のリフトピンと、を含み、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する1つのピン内の対応する側面との間に、0.011インチ(0.25mm)未満の隙間を有する、

プラズマチャンバを備えるシステム。

## 【請求項2】

請求項1に記載のシステムであって、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する1つのピン内の対応する側面との間に、0.005インチ(0.12mm)

10

20

mm) 未満の隙間を有する、システム。

**【請求項3】**

請求項1に記載のシステムであって、

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が丸いリフトピンである

、システム。

**【請求項4】**

請求項1に記載のシステムであって、

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が平らなリフトピンである

、システム。

**【請求項5】**

請求項1に記載のシステムであって、

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が広がっておりかつ平ら

なリフトピンである、システム。

**【請求項6】**

請求項1に記載のシステムであって、

コンデンサは、19ナノファラッドから43ナノファラッドまでの間の静電容量を有す

る、システム。

**【請求項7】**

プラズマチャンバにおいてアークRF信号を分離する方法であって、

プラズマチャンバにおいてトップ電極と静電チャックの上面との間の領域内にプラズマ

を発生させることであって、前記トップ電極および前記静電チャックの一方または両方に

1つ以上のRF信号を印加することを含み、前記静電チャックの前記上面で半導体ウエハ

が支えられ、前記静電チャックの表面内の対応する複数のリフトピン穴内に支えられた複

数のリフトピンが設けられており、前記複数のリフトピンの各ピンは、前記静電チャック

の前記表面内の複数のリフトピン穴のうちの対応する1つのピン内に對応する側面との間に、0.011インチ(0.25mm)未満の隙間を有する、プラズマの発生と、

前記1つ以上のRF信号の一部を、前記静電チャックの前記上面内の複数のクランプ電

極と前記静電チャックのベース板との間に結合されたコンデンサを通じて、結合すること

であって、前記コンデンサは、少なくとも19ナノファラッドの静電容量を有し、前記コ

ンデンサは、前記静電チャックの内部空間内に配される、ことと、

を備える方法。

**【請求項8】**

請求項7に記載の方法であって、

前記コンデンサは、19ナノファラッドから43ナノファラッドまでの間の静電容量を

有する、方法。

**【請求項9】**

請求項7に記載の方法であって、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン

穴のうちの対応する1つのピン内に對応する側面との間に、0.005インチ(0.12

mm)未満の隙間を有する、方法。

**【請求項10】**

請求項7に記載の方法であって、

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が丸いリフトピンである

、方法。

**【請求項11】**

請求項7に記載の方法であって、

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が平らなリフトピンである

、方法。

**【請求項12】**

請求項7に記載の方法であって、

10

20

30

40

50

前記複数のリフトピンのうちの少なくとも1つのピンは、先端が広がっておりかつ平らなリフトピンである、方法。

【請求項13】

プラズマチャンバにおいてアークRF信号を分離させるためのシステムであって、

プラズマチャンバであって、

トップ電極と、

半導体ウエハを支えるための静電チャックと、

前記静電チャックの表面内の複数のクランプ電極の少なくとも1つと前記静電チャックのベース板との間に結合されたコンデンサであって、19ナノファラッドから43ナノ

ファラッドまでの間の静電容量を有し、前記静電チャックの内部空間内に配される、コン

10

デンサと、

前記静電チャックの前記表面内の対応する複数のリフトピン穴内に支えられた複数のリフトピンと、

を含むプラズマチャンバを備え、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する1つのピン内の対応する側面との間に、0.005インチ(0.12

mm)未満の隙間を有する、システム。

【発明の詳細な説明】

【背景技術】

【0001】

20

本発明は、総じて、プラズマ処理チャンバに関し、特に、静電チャック内のリフトピン周囲におけるプラズマ発光を阻止するためのシステム、方法、および装置に関する。

【0002】

プラズマ処理は、半導体を製造する際によく使われる。プラズマ処理は、プラズマ中に形成されたプラズマイオンが基板の露出層と反応するプラズマエッティングプロセスである。プラズマイオンが基板の露出層内に進入することができる深さは、プラズマイオンのエネルギーによって決定される。プラズマイオンのエネルギーは、少なくとも一部には、基板に印加されるバイアスに関係する。

【0003】

半導体素子の小型化および高密度化に伴って、かつてない高さの深さ／幅アスペクト比が求められている。アスペクト比が高いほど、より高いエネルギーレベルのプラズマイオンが必要になる。

30

【0004】

プラズマイオンのエネルギーを高めるためのアプローチの1つは、バイアス電圧を増加させることである。あいにく、バイアス電圧が増すにつれて、基板と処理チャンバとの間、および電極と処理チャンバ構造およびリフトピンとの間にアークが発生する。

【0005】

リフトピンおよびその隣接構造は、バイアスレベルが増すにつれて、アークによって損傷される恐れがある。以上を鑑みると、プラズマ処理チャンバにおいてリフトピンにおけるアークをいっそう阻止するための、システム、方法、および装置が必要とされていることがわかる。

40

【発明の概要】

【0006】

概して、本発明は、プラズマチャンバにおいてアークRF信号を分離するためのシステムおよび方法を提供することによって、これらの必要を満たすものである。なお、本発明は、プロセス、装置、システム、コンピュータ可読媒体、または機器を含む数々の形態で実現可能であることを認識されるべきである。本発明の発明実施形態の幾つかが、以下で説明される。

【0007】

一実施形態は、トップ電極と、半導体ウエハを支えるための静電チャックと、静電チャ

50

ックの表面内の複数のクランプ電極の少なくとも1つと静電チャックのベース板との間に結合されたコンデンサとを含むプラズマチャンバにおいてアークRF信号を分離するためのシステムを提供する。ここで、コンデンサは、約19ナノファラッドを上回る静電容量を有し、静電チャックの内部空間内に配される。

#### 【0008】

システムは、また、静電チャックの表面内の対応するリフトピン穴内に支えられた複数のリフトピンも含む。各リフトピンは、対応するリフトピン穴内の対応する側面との間に、約0.011インチ(0.25mm)未満の隙間を有することができる。各リフトピンは、対応するリフトピン穴内の対応する側面との間に、約0.005インチ(0.12mm)未満の隙間を有することができる。リフトピンのうちの少なくとも1本は、先端が丸いリフトピン、先端が平らなリフトピン、および/または先端が広がっておりかつ平らなリフトピンであってよい。コンデンサは、約19ナノファラッドから約43ナノファラッドまでの間の静電容量を有することができる。10

#### 【0009】

別の一実施形態は、プラズマチャンバにおいてアークRF信号を分離する方法を提供する。該方法は、プラズマチャンバにおいてトップ電極と静電チャックの上面との間の領域内にプラズマを発生させることを含み、該プラズマを発生させることは、トップ電極および静電チャックの一方または両方に1つ以上のRF信号を印加することを含む。静電チャックの上面で、半導体ウエハが支えられる。1つ以上のRF信号の一部が、静電チャックの上面内のクランプ電極と静電チャックのベース板との間に結合されたコンデンサを通じて結合される。コンデンサは、少なくとも19ナノファラッドの静電容量を有する。コンデンサは、静電チャックの内部空間内に配される。20

#### 【0010】

本発明の原理を例として示した添付の図面に関連させた以下の詳細な説明から、本発明のその他の態様および利点が明らかになる。

#### 【図面の簡単な説明】

#### 【0011】

添付の図面に関連させた以下の詳細な説明によって、本発明が容易に理解される。

#### 【0012】

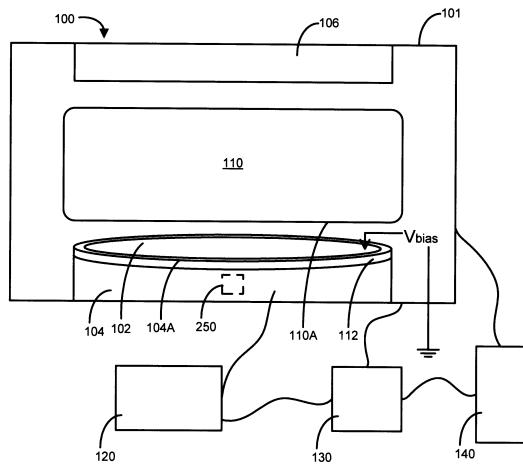

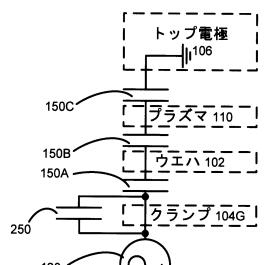

【図1A】本発明の実施形態にしたがった、プラズマチャンバシステムのブロック図である。30

#### 【0013】

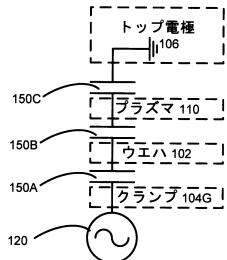

【図1B】本発明の実施形態にしたがった、プラズマチャンバ内の等価静電容量の概略図である。

#### 【0014】

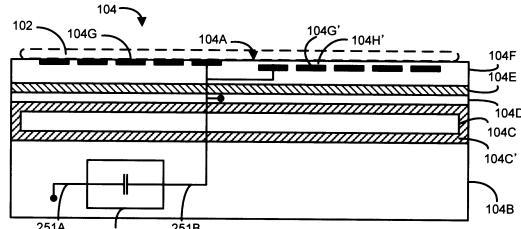

【図2A】本発明の実施形態にしたがった、静電チャックの概略断面図である。

#### 【0015】

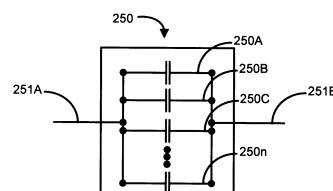

【図2B】本発明の実施形態にしたがった、コンデンサの平行配列の概略図である。

#### 【0016】

【図2C】本発明の実施形態にしたがった、プラズマチャンバ内の等価静電容量および追加コンデンサの概略図である。40

#### 【0017】

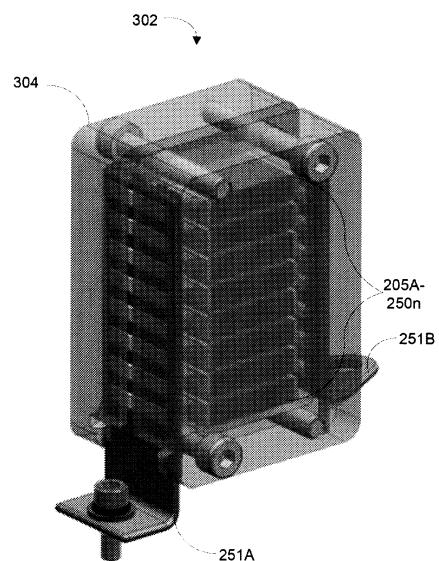

【図3A】本発明の実施形態にしたがった、封入コンデンサ配列の斜視図である。

【図3B】本発明の実施形態にしたがった、封入コンデンサ配列の斜視図である。

#### 【0018】

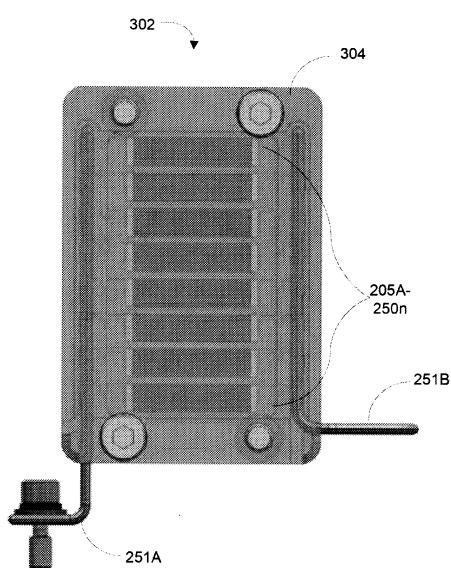

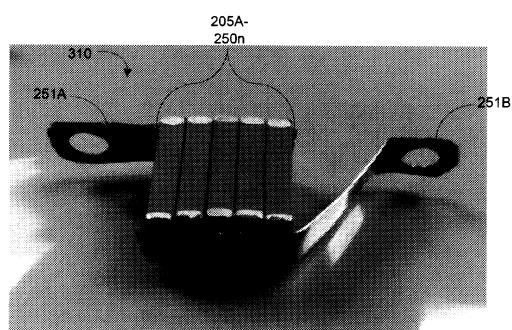

【図3C】本発明の実施形態にしたがった、コンデンサ配列の斜視図である。

#### 【0019】

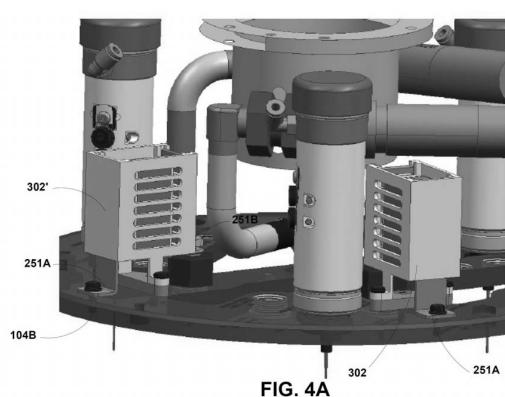

【図4A】本発明の実施形態にしたがった、静電チャック104内に搭載された複数の封入コンデンサ配列の斜視図である。

#### 【0020】

10

20

30

40

50

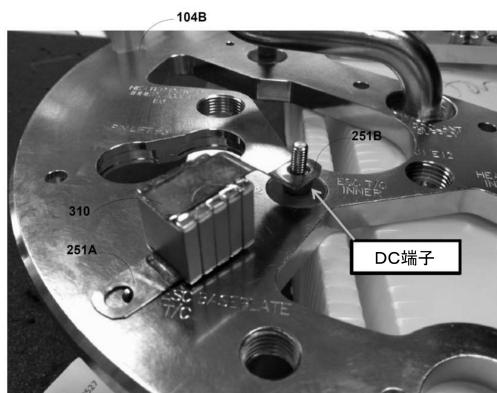

【図4B】本発明の実施形態にしたがった、静電チャック内に搭載されたコンデンサ配列の斜視図である。

【0021】

【図5A】本発明の実施形態にしたがった、静電チャック内に結合された第1の電気終端スタブの詳細斜視図である。

【0022】

【図5B】本発明の実施形態にしたがった、静電チャック内に結合された第2の電気終端スタブの詳細斜視図である。

【0023】

【図5C】本発明の実施形態にしたがった、静電チャック内に結合されたRF信号源からのRF入力接続の詳細斜視図である。 10

【0024】

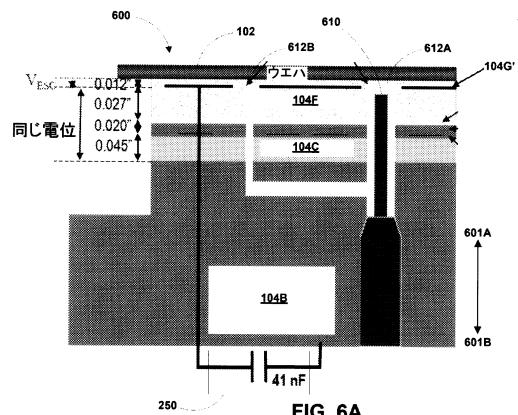

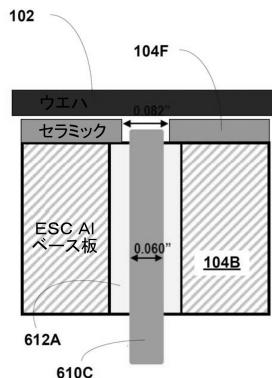

【図6A】本発明の実施形態にしたがった、静電チャック内のリフトピンの詳細断面図である。

【0025】

【図6B】本発明の実施形態にしたがった、先端が丸いリフトピンの詳細断面図である。

【0026】

【図6C】本発明の実施形態にしたがった、先端が広がっておりかつ平らなリフトピンの詳細断面図である。 20

【0027】

【図6D】本発明の実施形態にしたがった、先端が平らなリフトピンの詳細断面図である。

【0028】

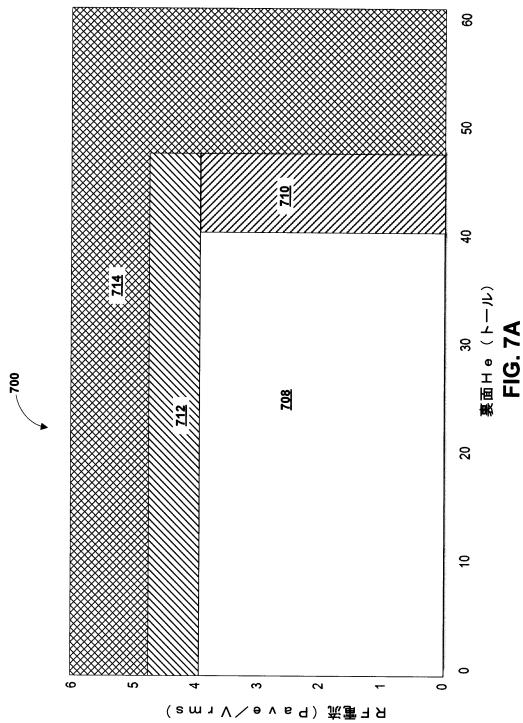

【図7A】本発明の一実施形態にしたがった、代表的なプラズマチャンバ101の動作域のグラフである。

【0029】

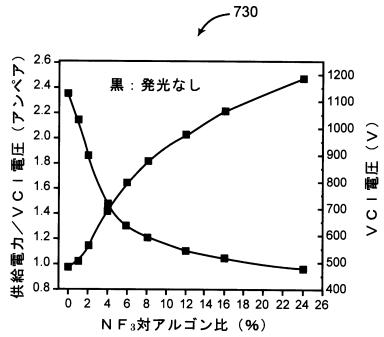

【図7B】本発明の一実施形態にしたがった、追加コンデンサの使用によってアーク(発光)が生じない代表的なプラズマチャンバのグラフである。 30

【0030】

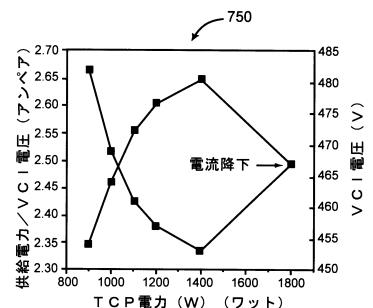

【図7C】本発明の一実施形態にしたがった、追加コンデンサの使用による電流降下を示した代表的なプラズマチャンバのグラフである。

【0031】

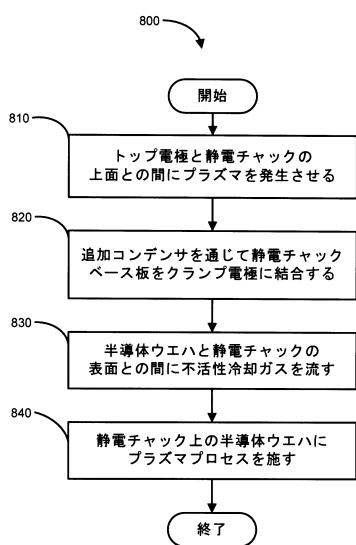

【図8】本発明の実施形態にしたがった、半導体ウエハと静電チャックとの間のアークを低減するために実施される方法動作を示したフローチャートである。

【0032】

【図9】本発明にしたがって処理を行うための代表的なコンピュータシステムのブロック図である。

【0033】

【図10】本発明の実施形態にしたがった、1つ以上のプラズマチャンバシステムを含む統合システムのブロック図である。 40

【発明を実施するための形態】

【0034】

リフトピンにおけるアークをいっそう阻止するためのシステム、方法、および装置の幾つかの代表的実施形態が説明される。当業者にならば、本発明が、本明細書に明記された具体的詳細の一部または全部を伴わずに実施されてもよいことが明らかである。

【0035】

静電チャックで測定される電圧が400キロヘルツで1000ボルト近いと、基板サポートの裏面におけるリフトピン上および静電チャック上に発光およびアークが生じることがある。この高電圧状態は、酸化物のエッティング速度が高い応用に有用である。

【0036】

10

20

30

40

50

静電チャックの基部と極との間に 19 ナノファラッドを超える追加の静電容量を加えると、電圧が劇的に減少し、裏面における発光およびアークを伴わない高バイアス電圧動作が可能になる。

#### 【 0 0 3 7 】

代表的な方法は、発光を抑えるために、誘電体スリーブによってリフトピン穴を覆うことおよび静電チャック内のヘリウム穴をセラミックで塞ぐことに頼る。該代表的な方法は、アークを阻止しつつ約 900 ボルトを超える動作を可能にすることに失敗している。

#### 【 0 0 3 8 】

静電チャックの基部と極との間の静電容量を最大にすることは、この静電容量を静電チャックの内部空間内に提供することに対する物理寸法上および環境上の懸念および制約ゆえに、困難である。22 ナノファラッドのコンデンサ配列が使用可能である。理想を言うと、更に大きい静電容量も望ましい。例えば、43 ナノファラッドのコンデンサ配列が使用されてよいだろう。

#### 【 0 0 3 9 】

図 1 A は、本発明の実施形態にしたがった、プラズマチャンバシステム 100 のプロック図である。プラズマチャンバシステム 100 は、プラズマチャンバ 101 と、静電チャック ( ESC ) 104 と、ESC 104 の上面内のエッジリング 112 と、トップ電極 106 とを含む。トップ電極 106 および ESC 104 は、具体的プロセスにおける必要性に応じ、1 つ以上の対応する RF 信号源 120 または大地電位に結合することができる。プラズマチャンバ 101 には、プロセスガス供給源 140 も結合される。静電チャック 104 は、以下で更に詳しく説明されるように、追加コンデンサ 250 を含む。

#### 【 0 0 4 0 】

コントローラ 130 もまた、プラズマチャンバ 101 、1 つ以上の RF 信号源 120 、およびプロセスガス源 140 に結合される。コントローラ 130 は、所望のレシピまたはプロセスに応じてシステム 100 を監視制御するために、ソフトウェアシステム、ロジックシステム、メモリシステム、入力システム、および出力システムを含む。入力システムおよび出力システムは、ユーザとやり取りするためのユーザインターフェースシステムを含む。入力システムおよび出力システムは、また、その他のコンピュータシステム、ならびに周辺機器（例えば、ディスプレイ、プリンタ、リモート記憶装置、およびその他の入出力機器）とデータをやり取りするためのネットワーキングプロトコルも含む。コントローラ 130 は、標準的な、すなわち汎用のコンピュータ、または特定の用途にあわせた専用のコンピュータであってよい。

#### 【 0 0 4 1 】

静電チャック ( ESC ) 104 は、表面 104A 上で半導体ウエハ 102 を支えるおよび固定することができる。1 つ以上の RF 信号源 120 は、1 つ以上の DC バイアス源も含むことができる。

#### 【 0 0 4 2 】

図 1 B は、本発明の実施形態にしたがった、プラズマチャンバ 101 内の等価静電容量 150A 、B 、C の概略図である。等価コンデンサ 150A は、図 2 A に更に詳細に示されたクランプ電極 104G 、104G' と、半導体ウエハ 102 との間に形成される。等価コンデンサ 150B は、半導体ウエハ 102 とプラズマ 110 との間に形成される。等価コンデンサ 150C は、プラズマ 110 とトップ電極 106 との間に形成される。トップ電極 106 は、接地されるのが一般的である。

#### 【 0 0 4 3 】

図 2 A は、本発明の実施形態にしたがった、静電チャック 104 の概略断面図である。ベース板 104 から始まって、層を追って順に表面 104A まで説明すると、静電チャック 104 は、導電性ベース板 104B と、ベース板上に搭載された絶縁加熱 / 冷却層 104C と、該加熱 / 冷却層上に搭載された導電性層 104D と、該導電性層上に搭載された絶縁層 104E と、セラミックトップ層 104F とを含む。セラミックトップ層 104F は、複数のクランプ電極 104G 、104G' を含む。加熱 / 冷却層 104C は、加熱 /

10

20

30

40

50

冷却層を隣接層 104B、104D から絶縁するために、絶縁体 104C' を含むことができる。

**【0044】**

複数のクランプ電極 104G' の第 1 の部分を、非導電性の表面層 104H' で覆うことができる。或いは、複数のクランプ電極 104G、104G' の第 2 の部分 104G または全部を、静電チャック 104 の上面 104A 上に露出させてよい。

**【0045】**

動作中、複数のクランプ電極 104G、104G' に対するバイアス電圧の印加は、半導体ウエハ 102 と静電チャック 104 の上面 104A との間に静電引力を形成し、それによって、半導体ウエハを静電チャックの上面上の適所に留め付ける。

10

**【0046】**

静電チャック 104 内には、コンデンサ 250 が含まれる。コンデンサ 250 は、静電チャック 104 の複数のクランプ電極 104G、104G' の少なくとも一部分または全部に電気的に結合された第 1 の電気終端スタブ 251A を有する。コンデンサの第 2 の電気終端スタブ 251B は、静電チャック 104 のベース板 104B および / または導電性層 104D の少なくとも 1 つに電気的に結合される。

**【0047】**

コンデンサ 250 は、単一のコンデンサ、または複数コンデンサの配列であってよい。コンデンサ 250 は、上述された等価静電容量 150A、150B、および 150C に追加して、約 19 ナノファラッドから約 43 ナノファラッドまでの間、またはそれを上回る静電容量を有する。

20

**【0048】**

図 2B は、本発明の実施形態にしたがった、コンデンサ 250A ~ n の平行配列の概略図である。コンデンサ 250 は、図に示されるように並列に結合された複数のコンデンサ 250A ~ n で形成することができる。コンデンサの数は、それらのコンデンサが存在している物理的空间に制限される。

**【0049】**

図 2C は、本発明の実施形態にしたがった、プラズマチャンバ 101 内の等価静電容量 150A、B、C および追加コンデンサ 250 の概略図である。追加コンデンサ 250 は、以下で更に詳しく説明されるように、静電チャック 104 に並列に結合される。追加コンデンサ 250 は、等価静電容量 150A、B、C に加えて、プラズマチャンバ 101 に電気的な静電容量を追加する。

30

**【0050】**

図 3A および図 3B は、本発明の実施形態にしたがった、封入コンデンサ配列 302 の斜視図である。封入コンデンサ配列 302 は、ケース 304 と、複数のコンデンサ 250A ~ 250n を有するコンデンサ配列とを含む。複数のコンデンサ 250A ~ 250n の実際の数は、1 つから、ケース 304 内に物理的に含まれうる数までの幅がある。封入コンデンサ配列 302 は、第 1 の電気終端スタブ 251A と、第 2 の電気終端スタブ 251B とを含む。

40

**【0051】**

図 3C は、本発明の実施形態にしたがった、コンデンサ配列 310 の斜視図である。コンデンサ配列 310 は、複数のコンデンサ 250A ~ 250n を有するコンデンサ配列を含む。複数のコンデンサ 250A ~ 250n の実際の数は、1 つから、ケース 304 内に物理的に含まれうる数までの幅がある。コンデンサ配列 310 は、第 1 の電気終端スタブ 251A と、第 2 の電気終端スタブ 251B とを含む。

**【0052】**

図 4A は、本発明の実施形態にしたがった、静電チャック 104 内に搭載された複数の封入コンデンサ配列 302、302' の斜視図である。図 4B は、本発明の実施形態にしたがった、静電チャック 104 内に搭載されたコンデンサ配列 310 の斜視図である。

**【0053】**

50

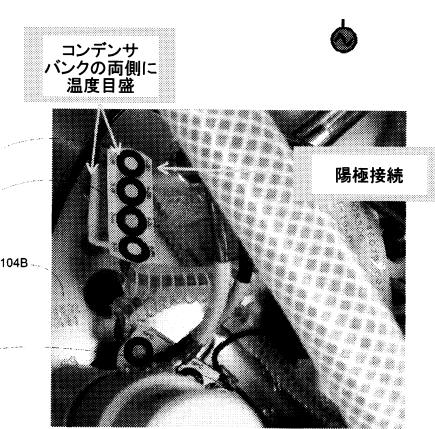

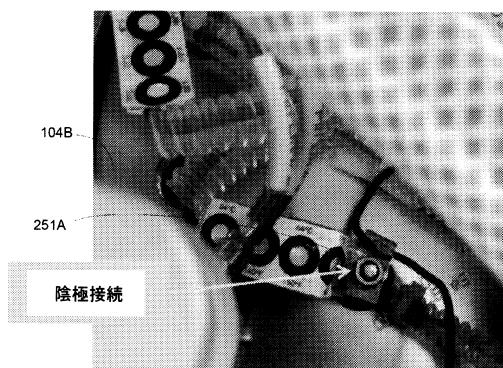

図 5 A は、本発明の実施形態にしたがった、静電チャック 104 内に結合された第 1 の電気終端スタブ 251A の詳細斜視図である。図 5 B は、本発明の実施形態にしたがった、静電チャック 104 内に結合された第 2 の電気終端スタブ 251B の詳細斜視図である。図 5 C は、本発明の実施形態にしたがった、静電チャック 104 内に結合された RF 信号源 120 からの RF 入力接続 510 の詳細斜視図である。

#### 【0054】

図 6 A は、本発明の実施形態にしたがった、静電チャック内の中のリフトピン 610 の詳細断面図 600 である。リフトピン 610 は、半導体ウエハ 102 を上昇させるために方向 610A に上方移動され、半導体ウエハを静電チャック 104 の表面 104A まで下降させるために方向 601B に下方移動される。リフトピン穴 612A および冷却剤穴 612B には、ヘリウムまたはその他の不活性冷却ガスが流される。ヘリウムは、プロセスガスがリフトピン穴 612A および冷却剤穴 612B に進入するのを阻止する。ヘリウムは、また、半導体ウエハと、静電チャック 104 の上面 104A との間を流れるにつれて、半導体ウエハ 102 の冷却も行う。

#### 【0055】

リフトピン 610 とクランプ電極 104G' との間で過剰な電圧電位が測定されると、半導体ウエハ 102 を損傷しうるアークが引き起こされる恐れがある。追加コンデンサ 250 は、静電チャック 104 のベース板 104B と、クランプ電極 104G' との間に結合される。

#### 【0056】

リフトピン穴 612A とリフトピン 610 との間の隙間が大きすぎても、やはり、アークが引き起こされる恐れがある。リフトピン穴 612A とリフトピン 610 との間の隙間を最小限に抑えるための様々なアプローチとして、様々な形状のリフトピンを使用することが挙げられる。リフトピン 610 は、任意の適切な材料で形成することができる。リフトピンに適した代表的な材料として、サファイヤおよびニタノールが挙げられるが、これらは非限定的な例である。

#### 【0057】

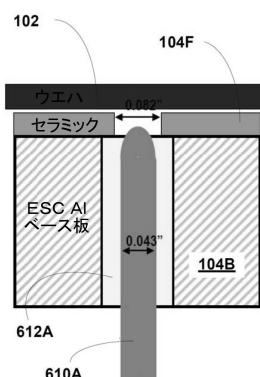

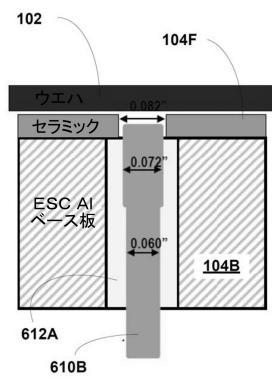

図 6 B は、本発明の実施形態にしたがった、先端が丸いリフトピン 610A の詳細断面図 620 である。図 6 C は、本発明の実施形態にしたがった、先端が広がっておりかつ平らなリフトピン 610B の詳細断面図 630 である。図 6 D は、本発明の実施形態にしたがった、先端が平らなリフトピン 610C の詳細断面図 640 である。リフトピン穴 612A は、リフトピン 610 の直径よりも僅かに大きい直径を有する。

#### 【0058】

例えば、図 6 B を参照すると、先端が丸いリフトピン 610A は、約 0.043 インチ (1.0 mm) の直径を有し、リフトピン穴 612A は、0.082 インチ (1.9 mm) の直径を有する。したがって、先端が丸いリフトピン 610A の各側面と、対応するリフトピン穴 612A の側面との間の隙間は、約 0.021 インチ (0.5 mm) である。

#### 【0059】

図 6 D の先端が平らなリフトピン 610C は、0.060 インチ (1.5 mm) の直径を有し、リフトピン穴 612A は、0.082 インチ (1.9 mm) の直径を有する。したがって、先端が平らなリフトピン 610C の各側面と、対応するリフトピン穴 612A の側面との間の隙間は、約 0.011 インチ (0.25 mm) である。

#### 【0060】

図 6 C の先端が広がっておりかつ平らなリフトピン 610B は、平らな先端の直径よりも小さい軸径を有する。例えば、軸径は、0.060 インチ (1.5 mm) であってよく、平らな先端は、0.072 インチ (1.7 mm) の直径を有することができる。リフトピン穴 612A は、0.082 インチ (1.9 mm) の直径を有する。したがって、先端が広がっておりかつ平らなリフトピン 610B の各側面と、対応するリフトピン穴 612A の側面との間の隙間は、約 0.005 インチ (0.12 mm) である。

#### 【0061】

10

20

30

40

50

図7Aは、本発明の一実施形態にしたがった、代表的なプラズマチャンバ101の動作域710のグラフ700である。動作域708は、追加コンデンサ250を伴わない場合の代表的な動作域である。追加動作域710および712は、ベース板104Bとクランプ電極104G、104G'との間に追加コンデンサ250が結合されたときに提供される動作域708の拡張を示している。安全でない動作域は、網目模様の領域714によって表される。追加コンデンサ250は、ヘリウム圧力およびRF電流の両方において動作域を拡張する。ヘリウムの圧力は、40トールから約48トールまで拡張することができる。RF電流は、約3.9Vrmsから約4.8Vrmsまで拡張される。

#### 【0062】

図7Bは、本発明の一実施形態にしたがった、追加コンデンサ250の使用によってアーク(発光)が生じない代表的なプラズマチャンバ101のグラフ730である。図7Cは、本発明の一実施形態にしたがった、追加コンデンサ250の使用による電流降下を示した代表的なプラズマチャンバ101のグラフ750である。

#### 【0063】

図8は、本発明の実施形態にしたがった、半導体ウエハと静電チャック104との間のアークを低減するために実施される方法動作800を示したフローチャートである。ここで示される動作は、例示であり、動作によっては下位の動作を含んでよいものがあること、およびここで説明される動作には例示の動作に含まれなくてよいものがあることが、理解されるべきである。これを念頭に置いて、次に、方法および動作800が説明される。

#### 【0064】

動作810では、トップ電極106と静電チャックの上面105との間の領域内にプラズマ110を発生させるために、トップ電極106および静電チャック104の一方または両方に(1つ以上の)RF源120からの1つ以上のRF信号が印加される。

#### 【0065】

動作820では、静電チャック104のベース板104Bが、追加コンデンサ250を通じてクランプ電極104G、104G'に電気的に結合される。

#### 【0066】

動作830では、半導体ウエハ102と静電チャック104の上面104Aとの間に不活性冷却ガスが流される。不活性冷却ガスは、ヘリウム、または類似の不活性冷却ガスであってよい。不活性冷却ガスは、1つ以上のリフトピン穴612Aおよび/または1つ以上の冷却ガス穴612Bを通じて半導体ウエハ102と静電チャック104の上面104Aとの間に注入することができる。1つ以上のリフトピン穴612Aおよび/または1つ以上の冷却ガス穴612Bは、静電チャック内の冷却ガス分配システム(例えば導管やブレナムなど)に流体結合される。冷却ガス分配システムは、冷却ガス源に結合される。

#### 【0067】

動作840では、静電チャック104上の半導体ウエハ102にプラズマプロセスが施される。方法動作は、プラズマプロセスが完了したときに終了することができる。

#### 【0068】

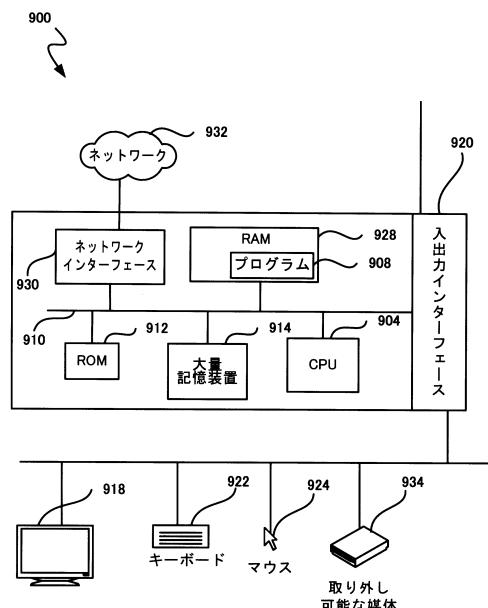

図9は、本発明にしたがって処理を行うための代表的なコンピュータシステム900のブロック図である。コンピュータシステム900は、上述のように、コントローラ103に含められてよい代表的なコンピュータシステムである。コンピュータシステム900は、中央演算処理ユニット904、ディスプレイ画面(またはモニタ)918、プリンタ906、フロッピィディスク媒体/光媒体/フラッシュ媒体、またはその他の取り外し可能媒体のドライブ934、大量記憶装置914(例えば1つ以上のハードディスクドライブもしくはソリッドステートドライブ)、ネットワークインターフェース930、キーボード922を含む。

#### 【0069】

コンピュータ900は、メモリバス910、ランダムアクセスメモリ(RAM)928、読み出し専用メモリ(ROM)912、入出力インターフェース920も含む。コンピュータ900は、パソコン(IBM適合パソコン、Macintoshコンピュータ、も

10

20

30

40

50

しくはMacintosh適合パソコンなど)、ワークステーションコンピュータ(Sun MicrosystemsワークステーションもしくはHewlett-Packardワークステーションなど)、またはその他の何らかのタイプのコンピュータであつてよい。

#### 【0070】

CPU904は、汎用のデジタルプロセッサであり、コンピュータシステム900の動作を制御する。CPU904は、単一チップのプロセッサであつてよい、または複数の構成要素で構成することができる。メモリから読み出されたプログラム命令908を使用して、CPU904は、入力データの受信および操作、ならびに出力機器へのデータの出力および表示を制御する。

10

#### 【0071】

バス910は、RAM928およびROM912にアクセスするために、CPU904によって使用される。RAM928は、一般的な記憶域として、およびスクラッチパッドメモリとしてCPU904によって使用され、入力されたデータおよび処理されたデータを記憶させるためにも使用することができる。ROM912は、CPU904がしたがう命令またはプログラムコードを、およびその他のデータを記憶させるために使用することができる。

#### 【0072】

出入力インターフェース920は、コンピュータ900によって使用される入力機器、出力機器、および記憶装置にアクセスするために使用される。説明されている実施形態では、これらの機器および装置は、ディスプレイ画面918、フロッピィディスク媒体／光媒体／フラッシュ媒体／取り外し可能媒体のドライブ934、およびネットワークインターフェース930を含む。

20

#### 【0073】

ディスプレイ画面918は、出入力インターフェース920を通じてCPU904によって提供されるまたはコンピュータシステム900内のその他の構成要素によって提供されるデータの画像を表示する出力機器である。プリンタ、プロッタ、タイプセッタ(植字機器)などの、他の出力機器も使用することができる。

#### 【0074】

フロッピィディスク媒体／光媒体／フラッシュ媒体／または他の取り外し可能媒体のドライブ934、および大量記憶装置914は、様々なタイプのデータを記憶させるために使用することができる。フロッピィディスク媒体／光媒体／フラッシュ媒体、または他の取り外し可能媒体のドライブ934は、他のコンピュータシステムへのこのようなデータの伝送を促し、大量記憶装置914は、記憶された大量のデータへの高速アクセスを可能にする。

30

#### 【0075】

CPU904は、オペレーティングシステムと協働し、コンピュータプログラム命令またはコード908の実行、ならびにデータの生成および使用を行う。コンピュータプログラム命令またはコード908、およびデータは、RAM928上、ROM912上、または大量記憶装置914上にあってよい。

40

#### 【0076】

コンピュータプログラム命令またはコード908、およびデータは、取り外し可能なプログラム媒体上にあってもよく、必要に応じてコンピュータシステム900に取り込むまたはインストールすることができるだろう。取り外し可能なプログラム媒体には、例えば、CD-ROM、PC-CARD、フロッピィディスク、フラッシュメモリ、光媒体、および磁気テープがある。

#### 【0077】

ネットワークインターフェース930は、他のコンピュータシステムに接続されたネットワークを通じてデータを送信および受信するために使用される。コンピュータシステム900を既存のネットワークに接続するためにおよび標準プロトコルにしたがってデ

50

ータを転送するために、インターフェースカードまたは類似の機器と、CPU904によって実行される適切なソフトウェアとを使用することができる。

#### 【0078】

キーボード918は、コマンドおよびその他の命令をコンピュータシステム900に入力するために、ユーザによって使用される。本発明との関連では、その他のタイプのユーザ入力機器も使用することができる。例えば、汎用コンピュータの画面上でポインタを操作するために、コンピュータマウス、トラックボール、タッチペン、またはタブレットなどの位置指示機器を使用することができる。

#### 【0079】

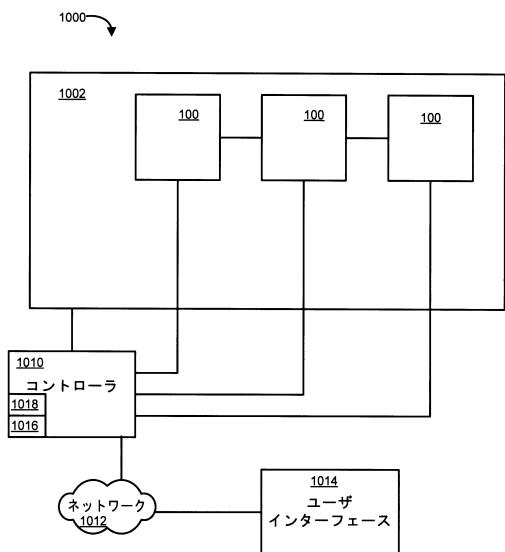

図10は、本発明の実施形態にしたがつた、1つ以上のプラズマチャンバシステム100を含む統合システム1000のブロック図である。統合システム1000は、1つ以上のプラズマチャンバシステム100と、1つの工場1002のなかの(1つ以上の)プラズマチャンバに結合された統合システムコントローラ1010とを含む。統合システムコントローラ1010は、ユーザインターフェース1014を含む、または(例えば有線もしくは無線のネットワーク1012を通じて)ユーザインターフェース1014に結合される。ユーザインターフェース1014は、ユーザが読み取ることが可能な出力および指示を提供し、また、ユーザ入力を受信して、統合システムコントローラ1010へのユーザアクセスを提供することができる。

#### 【0080】

統合システムコントローラ1010は、特殊用途コンピュータ、または汎用コンピュータを含むことができる。統合システムコントローラ1010は、(1つ以上の)プラズマチャンバシステム100についてのデータ1018(例えば、性能履歴、性能または欠陥の分析、オペレータのログ、および履歴など)を監視、制御、収集、および記憶するために、コンピュータプログラム1016を実行することができる。例えば、統合システムコントローラ1010は、収集されたデータが(1つ以上のプラズマチャンバシステムおよび/またはそのなかの構成要素の動作(例えば、圧力、流量、バイアス信号、基板102の取り込みおよび取り出しなど)の調整を指示している場合に、その動作を調整することができる。

#### 【0081】

上記の実施形態を念頭に置くと、本発明は、コンピュータシステムに記憶されているデータを伴う様々なコンピュータ実行動作を用いてよいことが、理解されるべきである。これらの動作は、物理量の物理的操作を必要とする動作である。通常、これらの量は、格納する、転送する、結合する、比較する、およびそれ以外のやり方で操作することができる電気信号または磁気信号の形をとるが、必ずしもそうである必要はない。更に、実施される操作は、作成する、識別する、決定する、または比較するなどの用語でしばしば言及される。

#### 【0082】

本発明は、コンピュータ可読媒体上のコンピュータ可読コードとしても実現することができる。コンピュータ可読媒体は、コンピュータシステムによってあとで読み出し可能なデータを記憶することができる任意のデータ記憶装置である。コンピュータ可読媒体の例には、ハードドライブ、ネットワーク接続記憶装置(NAS)、読み出し専用メモリ、ランダムアクセスメモリ、CD-ROM、CD-R、CD-RW、DVD、フラッシュ、磁気テープ、ならびにその他の光および非光データ記憶装置がある。コンピュータ可読媒体は、コンピュータ可読コードが分散方式で記憶および実行されるように、ネットワークで結合されたコンピュータシステムに分散させることもできる。

#### 【0083】

更には、上記の図で動作によって表されている命令が例示の順序で実施される必要はないこと、および動作によって表されている処理の必ずしも全てが本発明の実施に必要とは限らないことが、認識されるべきである。更に、上記のどの図で説明されているプロセスも、RAM、ROM、またはハードディスクドライブのうちの任意の1つまたはこれらの

10

20

30

40

50

任意の組み合わせに記憶されたソフトウェアの形で実現することもできる。

**【0084】**

以上の発明は、理解を明瞭にする目的で幾らか詳細に説明されてきたが、添付の特許請求の範囲内で特定の変更および修正が可能であることが明らかである。したがって、これらの実施形態は、例示的で尚且つ非限定的であると見なされ、本発明は、本明細書で与えられた詳細に限定されることではなく、添付の特許請求の範囲およびそれらの均等物の範囲内で変更されてよい。

本発明は、たとえば、以下のような態様で実現することもできる。

適用例 1 :

10

プラズマチャンバにおいてアーク R F 信号を分離させるためのシステムであって、

プラズマチャンバであって、

トップ電極と、

半導体ウエハを支えるための静電チャックと、

前記静電チャックの表面内の複数のクランプ電極の少なくとも 1 つと前記静電チャックのベース板との間に結合されたコンデンサであって、約 19 ナノファラッドを上回る静電容量を有し、前記静電チャックの内部空間内に配される、コンデンサと、

を含むプラズマチャンバを備えるシステム。

適用例 2 :

20

適用例 1 のシステムであって、更に、

前記静電チャックの前記表面内の対応する複数のリフトピン穴内に支えられた複数のリフトピンを備えるシステム。

適用例 3 :

適用例 2 のシステムであって、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する 1 つのピン内の対応する側面との間に、約 0.011 インチ (0.25 mm) 未満の隙間を有する、システム。

30

適用例 4 :

適用例 2 のシステムであって、

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する 1 つのピン内の対応する側面との間に、約 0.005 インチ (0.12 mm) 未満の隙間を有する、システム。

適用例 5 :

適用例 2 のシステムであって、

前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が丸いリフトピンである、システム。

40

適用例 6 :

適用例 2 のシステムであって、

前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が平らなリフトピンである、システム。

適用例 7 :

適用例 2 のシステムであって、

前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が広がっておりかつ平らなリフトピンである、システム。

50

適用例 8 :適用例 1 のシステムであって、コンデンサは、約 19 ナノファラッドから約 43 ナノファラッドまでの間の静電容量を有する、システム。適用例 9 :プラズマチャンバにおいてアーク R F 信号を分離する方法であって、プラズマチャンバにおいてトップ電極と静電チャックの上面との間の領域内にプラズマを発生させることであって、前記トップ電極および前記静電チャックの一方または両方に 1 つ以上の R F 信号を印加することを含み、前記静電チャックの前記上面で半導体ウエハが支えられる、ことと、前記 1 つ以上の R F 信号の一部を、前記静電チャックの前記上面内の複数のクランプ電極と前記静電チャックのベース板との間に結合されたコンデンサを通じて、結合することであって、前記コンデンサは、少なくとも 19 ナノファラッドの静電容量を有し、前記コンデンサは、前記静電チャックの内部空間内に配される、ことと、

を備える方法。適用例 10 :適用例 9 の方法であって、前記コンデンサは、約 19 ナノファラッドから約 43 ナノファラッドまでの間の静電容量を有する、方法。

20

適用例 11 :適用例 9 の方法であって、更に、前記静電チャックの前記表面内の対応する複数のリフトピン穴内に支えられた複数のリフトピン備える方法。適用例 12 :適用例 11 の方法であって、前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する 1 つのピン内の対応する側面との間に、約 0.011 インチ (0.25 mm) 未満の隙間を有する、方法。

30

適用例 13 :適用例 11 の方法であって、前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する 1 つのピン内の対応する側面との間に、約 0.005 インチ (0.12 mm) 未満の隙間を有する、方法。

40

適用例 14 :適用例 11 の方法であって、前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が丸いリフトピンである、方法。適用例 15 :適用例 11 の方法であって、前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が平らなリフトピンである、方法。

50

適用例 1 6 :適用例 1 1 の方法であって、前記複数のリフトピンのうちの少なくとも 1 つのピンは、先端が広がっておりかつ平らなリフトピンである、方法。適用例 1 7 :プラズマチャンバにおいてアーク R F 信号を分離させるためのシステムであって、プラズマチャンバであって、トップ電極と、半導体ウエハを支えるための静電チャックと、

10

前記静電チャックの表面内の複数のクランプ電極の少なくとも 1 つと前記静電チャックのベース板との間に結合されたコンデンサであって、約 19 ナノファラッドから約 43 ナノファラッドまでの間の静電容量を有し、前記静電チャックの内部空間内に配される、コンデンサと、前記静電チャックの前記表面内の対応する複数のリフトピン穴内に支えられた複数のリフトピンと、を含むプラズマチャンバを備えるシステム。適用例 1 8 :適用例 1 7 のシステムであって、

20

前記複数のリフトピンの各ピンは、前記静電チャックの前記表面内の複数のリフトピン穴のうちの対応する 1 つのピン内の対応する側面との間に、約 0.005 インチ (0.12 mm) 未満の隙間を有する、システム。

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図 2 C】

FIG. 2C

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

【図 3 C】

FIG. 3C

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

【図 5 C】

FIG. 5C

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 7 A】

【図 7 B】

FIG. 7B

【図 7 C】

FIG. 7C

【図 8】

FIG. 8

【図 9】

FIG. 9

【図10】

FIG. 10

---

フロントページの続き

審査官 鈴木 和樹

(56)参考文献 米国特許第06494958(US, B1)

特表2011-527522(JP, A)

特表2008-516462(JP, A)

特開平10-261498(JP, A)

特開2000-252267(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/683

H01L 21/3065

H02N 13/00