(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-54760

(P2011-54760A)

(43) 公開日 平成23年3月17日(2011.3.17)

| (51) Int.Cl.                | F 1        |       | テーマコード (参考) |

|-----------------------------|------------|-------|-------------|

| <b>H01L 29/74</b> (2006.01) | H01L 29/74 | E     | 2 C 1 6 2   |

| <b>H01L 33/08</b> (2010.01) | H01L 33/00 | 1 2 O | 5 C 0 5 1   |

| <b>B41J 2/44</b> (2006.01)  | B41J 3/21  | L     | 5 F 0 0 5   |

| <b>B41J 2/45</b> (2006.01)  | HO4N 1/036 | A     | 5 F 0 4 1   |

| <b>B41J 2/455</b> (2006.01) | H01L 27/15 | B     |             |

審査請求 未請求 請求項の数 11 O L (全 32 頁) 最終頁に続く

|           |                              |          |                                                          |

|-----------|------------------------------|----------|----------------------------------------------------------|

| (21) 出願番号 | 特願2009-202379 (P2009-202379) | (71) 出願人 | 591044164<br>株式会社沖データ<br>東京都港区芝浦四丁目11番22号                |

| (22) 出願日  | 平成21年9月2日 (2009.9.2)         | (71) 出願人 | 500002571<br>株式会社沖デジタルイメージング<br>群馬県高崎市西横手町1番地1           |

|           |                              | (74) 代理人 | 100086807<br>弁理士 柿本 恒成                                   |

|           |                              | (74) 代理人 | 100091362<br>弁理士 阿仁屋 節雄                                  |

|           |                              | (74) 代理人 | 100145872<br>弁理士 福岡 昌浩                                   |

|           |                              | (72) 発明者 | 南雲 章<br>東京都八王子市東浅川町550番地の1<br>株式会社沖デジタルイメージング内<br>最終頁に続く |

(54) 【発明の名称】半導体複合装置、この製造方法、光プリントヘッド及び画像形成装置

## (57) 【要約】

【課題】製造工程を簡略化して低コスト化を図る。

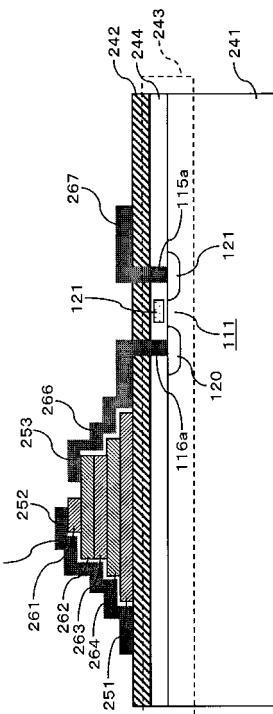

【解決手段】半導体複合装置は、シフトレジスタと、これにより時分割駆動される半導体薄膜からなる発光サイリスタアレイとにより構成されている。この製造方法は、例えば、シフトレジスタを構成する複数の回路構成素子243が形成されたシリコン基板241を用意する。シフトレジスタにより駆動される複数の発光サイリスタ261～264が配列された結晶構造を持った半導体薄膜からなる発光サイリスタアレイを、パッシベーション膜242を介してシリコン基板241上に貼着する。フォトリソグラフィ法により、複数の回路構成素子243間を電気的に接続してシフトレジスタを形成すると共に、そのシフトレジスタ及び複数の発光サイリスタ261～264間を電気的に接続するメタル配線265～267を形成する。

【選択図】図1

本発明の実施例1の半導体複合装置の配線構造

**【特許請求の範囲】****【請求項 1】**

駆動回路を構成する複数の回路構成素子が形成された基板と、

前記基板上に絶縁膜を介して貼着され、前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイと、

前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続する配線と、

を有することを特徴とする半導体複合装置。

**【請求項 2】**

駆動回路を構成する複数の回路構成素子が形成された基板と、

前記基板上に絶縁膜を介して貼着され、前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイと、

前記半導体薄膜中に拡散され、前記被駆動素子の主要部を形成する不純物拡散領域と、

前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続する配線と、

を有することを特徴とする半導体複合装置。

**【請求項 3】**

前記被駆動素子は、スイッチ素子であることを特徴とする請求項 1 又は 2 記載の半導体複合装置。

**【請求項 4】**

前記スイッチ素子は、電気信号により光を射出する発光素子であることを特徴とする請求項 3 記載の半導体複合装置。

**【請求項 5】**

前記発光素子は、P N P N 構造又は P N P N P N 構造を有する発光サイリスタであることを特徴とする請求項 4 記載の半導体複合装置。

**【請求項 6】**

前記駆動回路は、前記複数の被駆動素子を時分割駆動するシフトレジスタであることを特徴とする請求項 1 ~ 5 のいずれか 1 項に記載の半導体複合装置。

**【請求項 7】**

前記複数の回路構成素子は、前記シフトレジスタを構成するためのトランジスタの集合であることを特徴とする請求項 6 記載の半導体複合装置。

**【請求項 8】**

駆動回路を構成する複数の回路構成素子が形成された基板を用意する工程と、

前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイを、パッシベーション膜を介して前記基板上に貼着する工程と、

フォトリソグラフィ法により、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続するメタル配線を形成する工程と、

を有することを特徴とする半導体複合装置の製造方法。

**【請求項 9】**

駆動回路を構成する複数の回路構成素子が形成された基板を用意する工程と、

前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイを、パッシベーション膜を介して前記基板上に貼着する工程と、

前記被駆動素子の主要部を形成する不純物を前記半導体薄膜中に拡散する工程と、

フォトリソグラフィ法により、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続するメタル配線を形成する工程と、

を有することを特徴とする半導体複合装置の製造方法。

10

20

30

40

50

**【請求項 10】**

請求項 4 ~ 7 のいずれか 1 項に記載の半導体複合装置と、前記複数の発光素子の出射光を収束するレンズアレイと、を有することを特徴とする光プリントヘッド。

**【請求項 11】**

請求項 10 記載の光プリントヘッドを有し、前記光プリントヘッドにより感光体を露光して静電潜像を形成し、前記静電潜像を現像して記録媒体に画像を形成することを特徴とする画像形成装置。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は、発光サイリスタ等の被駆動素子とこれを駆動する駆動回路等とを有する半導体複合装置と、半導体複合装置の製造方法と、半導体複合装置を備えた光プリントヘッドと、光プリントヘッドを備えた電子写真プリンタ等の画像形成装置に関するものである。

**【背景技術】****【0002】**

従来、電子写真プリンタ等の画像形成装置には、発光素子を多数配列させて露光部を形成したものがある。発光素子としては、発光ダイオード（以下「LED」という。）のほか、有機エレクトロルミネセンス（以下「有機EL」という。）や、発光サイリスタ等が用いられる。

20

**【0003】**

発光サイリスタを用いたものでは、駆動回路と発光サイリスタとが 1 対 1、もしくは 1 対 N ( $N < 1$ ) に対応するように設けられ、発光サイリスタのアノード端子（以下単に「アノード」という。）及びカソード端子（以下単に「カソード」という。）間に駆動電流を流すか否かにより、点灯 / 非点灯の状態を切り替えている。点灯状態における発光サイリスクの光出力は、前記駆動電流値により決まるものであり、この駆動電流値を調整することで、プリンタ感光体ドラム等の露光部への露光エネルギー量を調整することができる。

**【0004】**

一般に発光サイリスタは、化合物半導体を用いて形成されており、この化合物半導体の結晶欠陥に起因する光量ばらつきが不可避であって、化合物半導体を用いた画像形成装置に印刷濃度むらを生じてしまう。そのため、発光サイリスタへの駆動電流値を発光サイリスタ毎に調整することで、光量補正を行う構成が知られている。

30

**【0005】**

又、下記の特許文献 1 の技術では、ガリウム・砒素（GaAs）ウェハ基材上に形成したエピタキシャル層に発光サイリスタを形成しておき、該エピタキシャル層をフィルム状に剥離することで得られるエピタキシャルフィルム（以下単に「エピフィルム」という。）を用いている。そして、駆動回路が形成されたシリコン基板のウェハに、エピフィルムを貼着し、発光サイリスタと駆動回路とを薄膜配線を用いて電気的に接続することで、発光サイリスタと駆動回路とを一体化させた半導体複合装置の製造方法が開示されている。

40

**【先行技術文献】****【特許文献】****【0006】****【特許文献 1】特開 2007-81081 号公報****【発明の概要】****【発明が解決しようとする課題】****【0007】**

しかしながら、従来の半導体複合装置及びこの製造方法では、次の (a)、(b) のような課題があった。

**【0008】**

50

(a) 駆動回路内の各構成素子間を接続するメタル配線をフォトリソグラフィ法により予め形成したシリコンウェハを用い、発光サイリスタが形成されたエピフィルムをそのシリコンウェハに貼着した後、駆動回路の出力端子と発光サイリスタのゲート端子（以下単に「ゲート」という。）とをメタル配線により再び接続する必要があった。そのため、半導体複合装置の製造工程において、前記メタル配線工程が2重に必要となり、コスト的な無駄を生じていた。

#### 【0009】

(b) 駆動回路内のメタル配線として、例えば、アルミニウム（A1）を主材料とする薄膜配線が用いられるのに起因して、耐熱性に制約を生じ、前記エピフィルムをシリコンウェハに貼着した後、不純物の熱拡散等の高温を要する処理を行うことが困難であった。10

#### 【課題を解決するための手段】

#### 【0010】

本発明の内の第1の発明の半導体複合装置は、駆動回路を構成する複数の回路構成素子が形成された基板と、前記基板上にパッシベーション膜を介して貼着され、前記駆動回路により駆動される複数の被駆動素子（例えば、発光素子）が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイと、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続する配線と、を有することを特徴とする。

#### 【0011】

第2の発明の半導体複合装置は、駆動回路を構成する複数の回路構成素子が形成された基板と、前記基板上にパッシベーション膜を介して貼着され、前記駆動回路により駆動される複数の被駆動素子（例えば、発光素子）が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイと、前記半導体薄膜中に拡散され、前記被駆動素子の主要部を形成する不純物拡散領域と、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続する配線と、を有することを特徴とする。20

#### 【0012】

第3の発明の半導体複合装置の製造方法は、駆動回路を構成する複数の回路構成素子が形成された基板を用意する工程と、前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイを、パッシベーション膜を介して前記基板上に貼着する工程と、フォトリソグラフィ法により、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続するメタル配線を形成する工程と、を有することを特徴とする。30

#### 【0013】

第4の発明の半導体複合装置の製造方法は、駆動回路を構成する複数の回路構成素子が形成された基板を用意する工程と、前記駆動回路により駆動される複数の被駆動素子が配列された結晶構造を持った半導体薄膜からなる被駆動素子アレイを、パッシベーション膜を介して前記基板上に貼着する工程と、前記被駆動素子の主要部を形成する不純物を前記半導体薄膜中に拡散する工程と、フォトリソグラフィ法により、前記複数の回路構成素子間を電気的に接続して前記駆動回路を形成すると共に、前記駆動回路及び前記複数の被駆動素子間を電気的に接続するメタル配線を形成する工程と、を有することを特徴とする。40

#### 【0014】

第5の発明の光プリントヘッドは、前記第1又は第2の発明の半導体複合装置と、前記複数の被駆動素子（例えば、発光素子）の出射光を収束するレンズアレイと、を有することを特徴とする。

#### 【0015】

第6の発明の画像形成装置は、前記第5の発明の光プリントヘッドを有し、前記光プリントヘッドにより感光体を露光して静電潜像を形成し、前記静電潜像を現像して記録媒体

に画像を形成することを特徴とする。

【発明の効果】

【0016】

第1及び第3の発明の半導体複合装置及びこの製造方法によれば、被駆動素子アレイとこの駆動回路との間の配線工程において、駆動回路自体を構成するための複数の回路構成素子間の回路配線をも同時に形成することが可能となる。これにより、製造工程を簡略化できるので、製造コストの大幅な削減が可能となる。

【0017】

第2及び第4の発明の半導体複合装置及びこの製造方法によれば、前記第1及び第3の発明と同様の効果を有している。その上、被駆動素子アレイを基板上に貼着した後に、被駆動素子の主要部を形成する不純物を半導体薄膜中に拡散するので、不純物濃度を高くでき、被駆動素子の性能を向上できる。更に、不純物を選択的に拡散させることで、この拡散位置の位置決めが容易になって位置精度の向上を図ることができ、併せて拡散面積の小型化を図ることも可能となる。

【0018】

第5の発明の光プリントヘッドによれば、被駆動素子の配列ピッチの小さい高精細な光プリントヘッドを実現することができる。

【0019】

第6の発明の画像形成装置によれば、スペース効率及び光取り出し効率に優れた高品質の画像形成装置を実現することができる。

【図面の簡単な説明】

【0020】

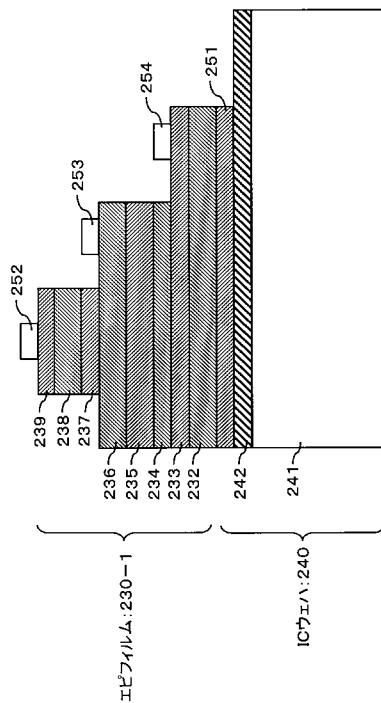

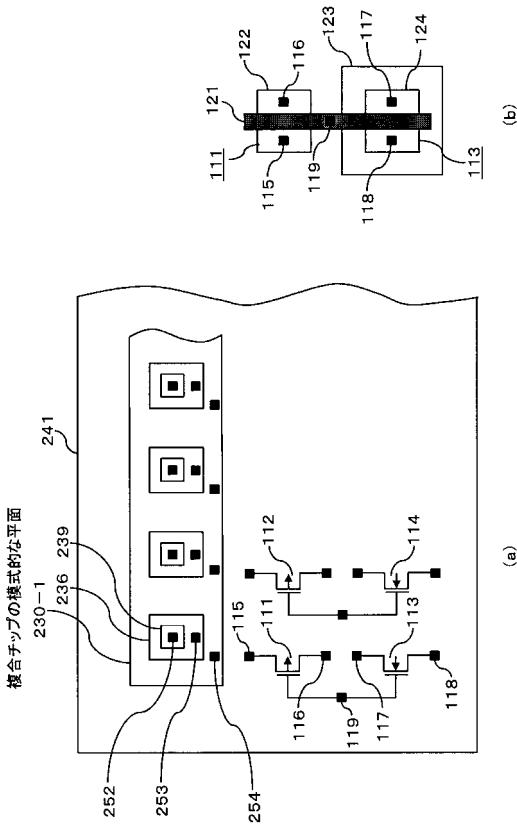

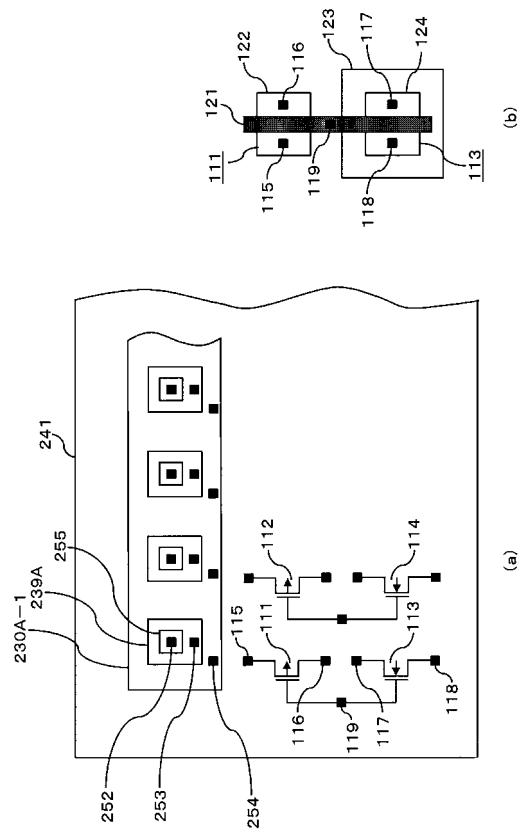

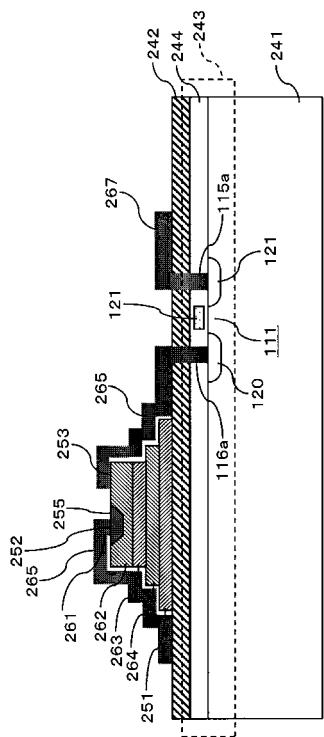

【図1】図1は本発明の実施例1における図7-4の半導体複合装置の配線構造を示す模式的な断面図である。

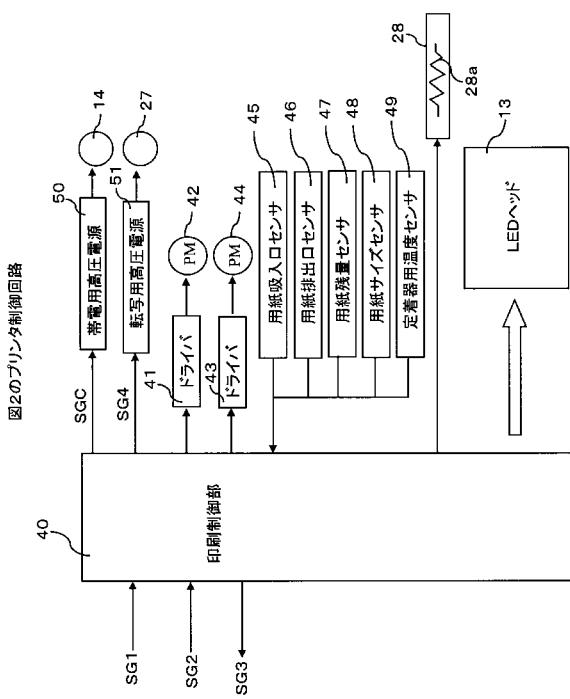

【図2】図2は本発明の実施例1における画像形成装置を示す概略の構成図である。

【図3】図3は図2の画像形成装置1におけるプリンタ制御回路の構成を示すブロック図である。

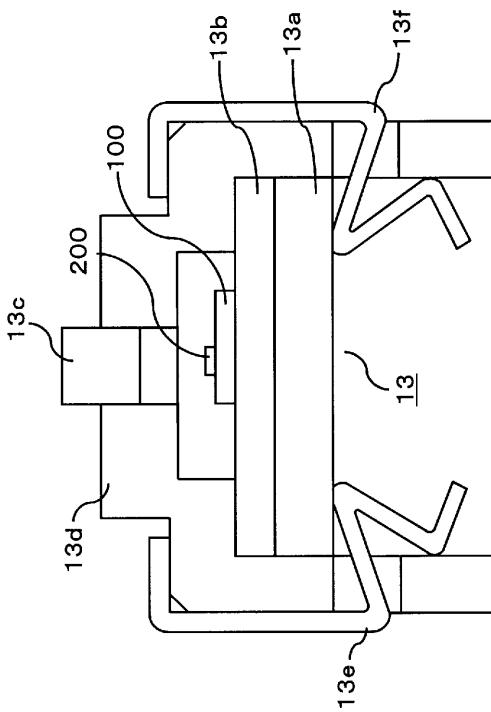

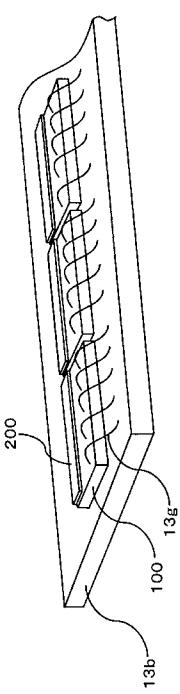

【図4】図4は図3中の光プリントヘッド13の構造を示す概略の断面図である。

【図5】図5は図4中の光プリントヘッド基板ユニットを示す斜視図である。

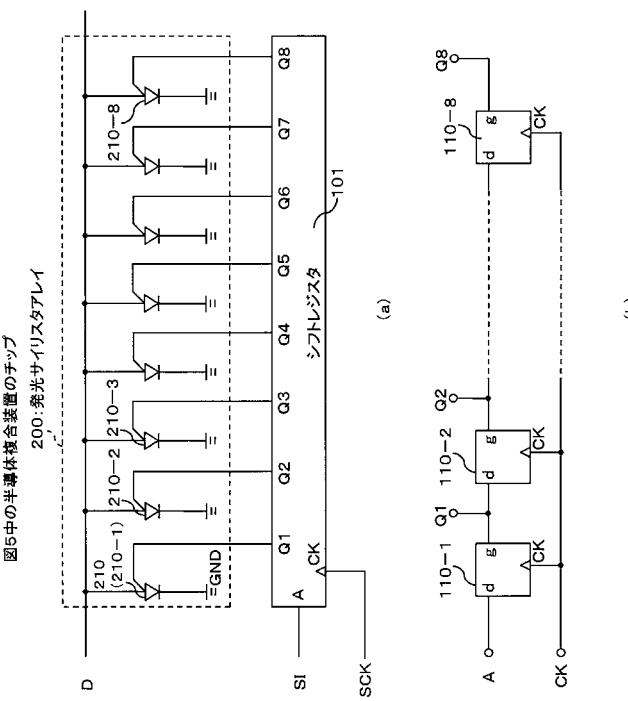

【図6】図6は図5中のドライバIC100及び発光サイリスタアレイ200からなる半導体複合装置のチップの構成を示す回路図である。

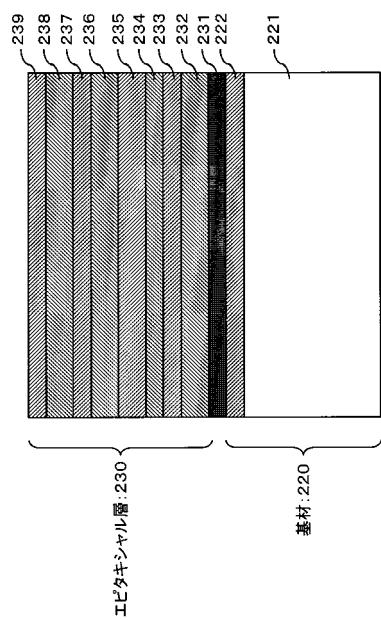

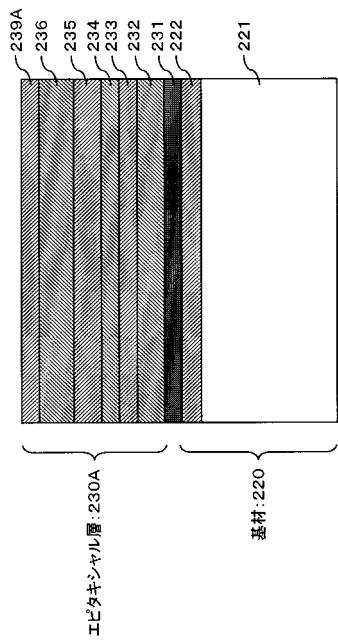

【図7-1】図7-1は図6中のメサ型発光サイリスタ210の製造方法を示す模式的な断面図である。

【図7-2】図7-2は図6中のメサ型発光サイリスタ210の製造方法を示す模式的な断面図である。

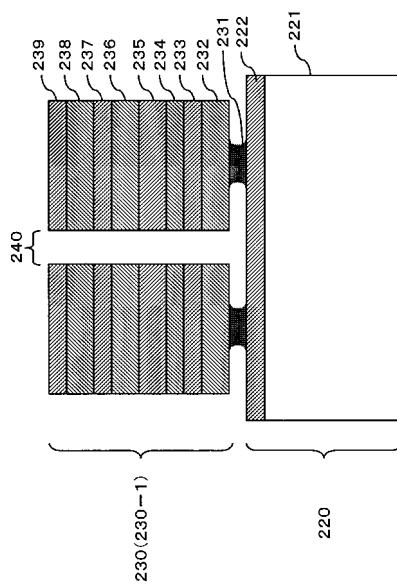

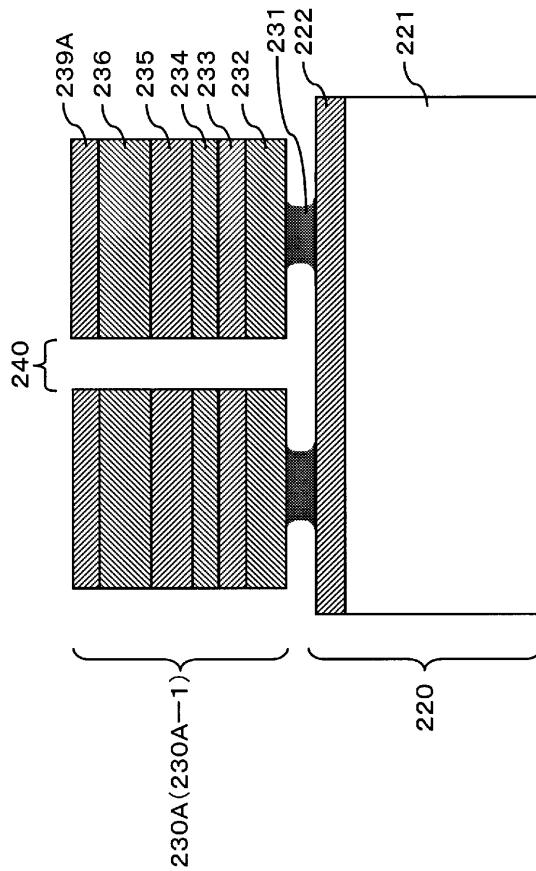

【図7-3】図7-3は半導体複合装置の製造方法を示す模式的な断面図である。

【図7-4】図7-4は複合チップの模式的な平面を示す図である。

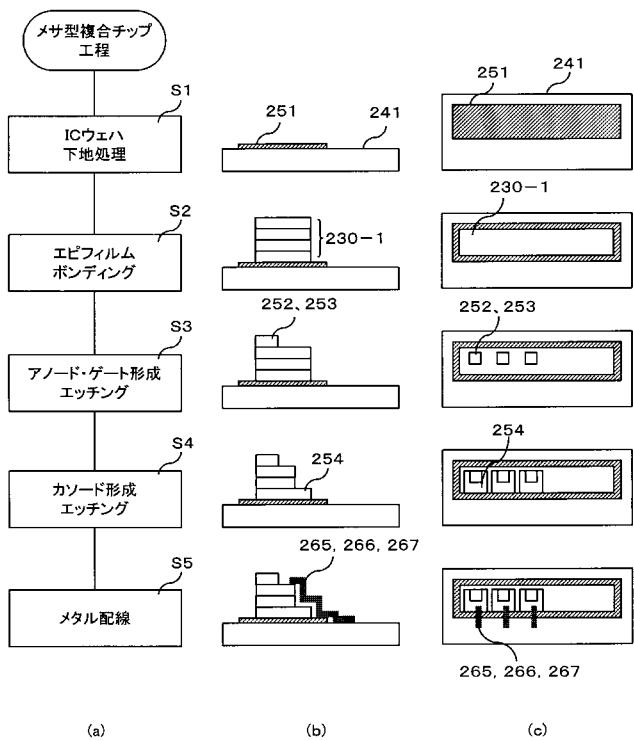

【図8】図8は図7-3及び図1におけるメサ型複合チップの概略の製造工程を示す図である。

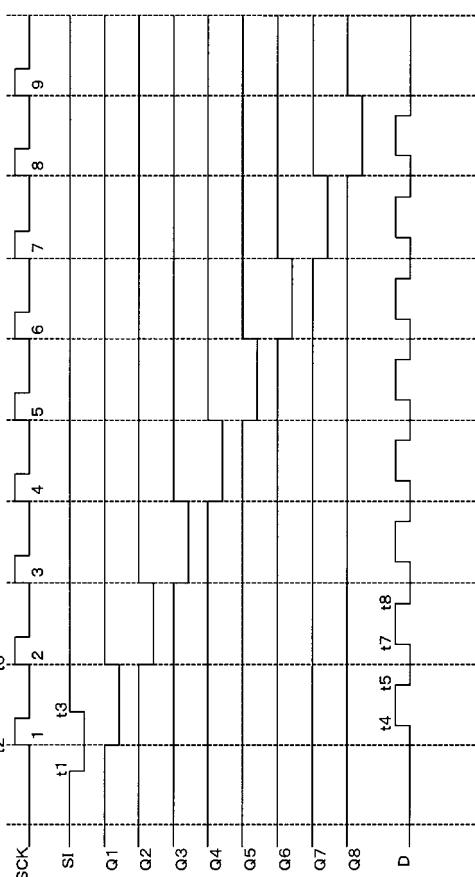

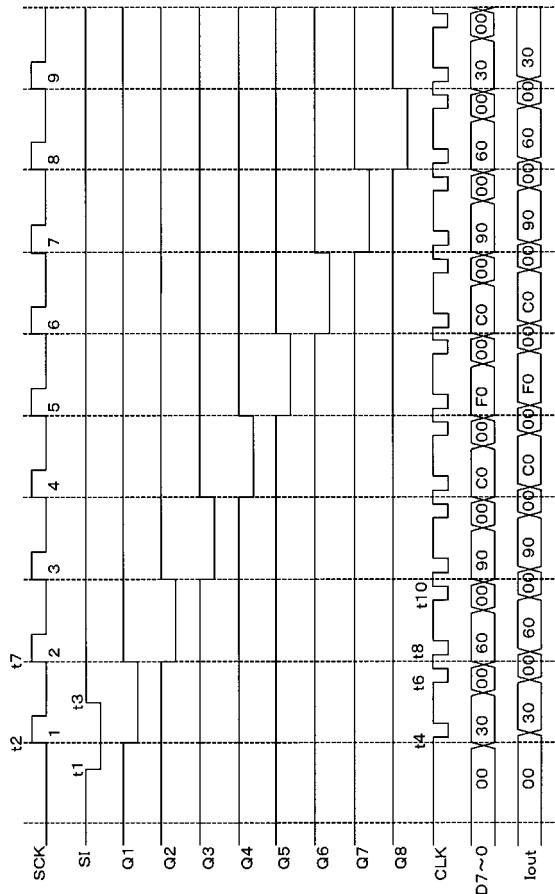

【図9】図9は図6の光プリントヘッド13の動作を説明するためのタイムチャートである。

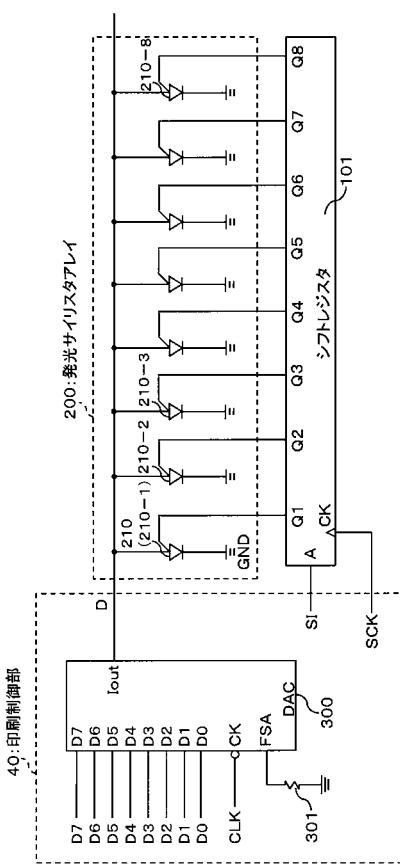

【図10】図10は実施例1の図6(a)における光プリントヘッド13の構成の変形例を示す回路図である。

【図11】図11は図10の光プリントヘッド13の動作を説明するためのタイムチャートである。

【図12-1】図12-1は拡散型発光サイリスタ210Aの製造方法を示す模式的な断面図である。

【図12-2】図12-2は拡散型発光サイリスタ210Aの製造方法を示す模式的な断面図である。

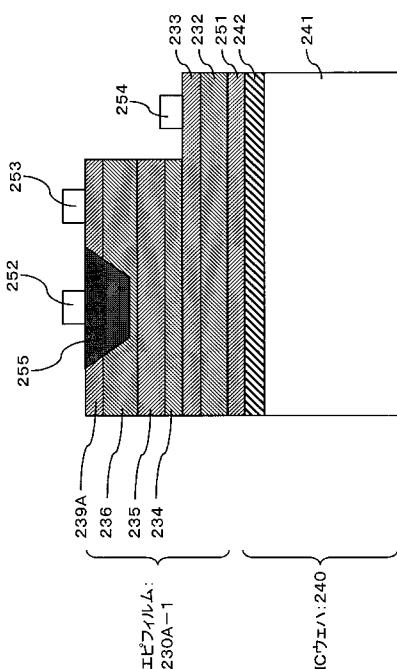

【図12-3】図12-3は半導体複合装置の製造方法を示す模式的な断面図である。

10

20

30

40

50

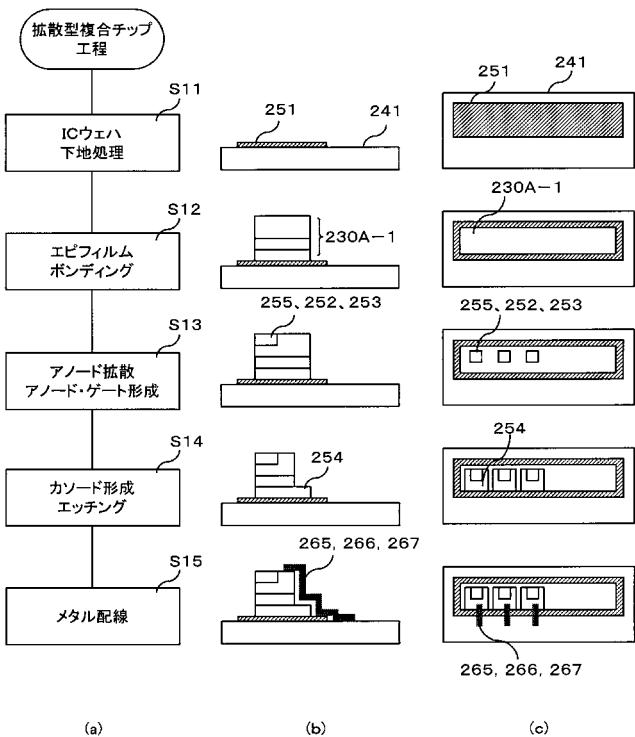

【図12-4】図12-4は本実施例2における複合チップの模式的な平面を示す図である。

【図13】図13は本発明の実施例2における図12-4の半導体複合装置の配線構造を示す模式的な断面図である。

【図14】図14は図12-3及び図13における拡散型複合チップの概略の製造工程を示す図である。

【発明を実施するための形態】

【0021】

本発明を実施するための形態は、以下の好ましい実施例の説明を添付図面と照らし合わせて読むと、明らかになるであろう。但し、図面はもっぱら解説のためのものであって、本発明の範囲を限定するものではない。10

【実施例1】

【0022】

(実施例1の画像形成装置)

図2は、本発明の実施例1における画像形成装置を示す概略の構成図である。

【0023】

この画像形成装置1は、被駆動素子である発光素子（例えば、三端子スイッチ素子である発光サイリスタ）及びこの駆動回路を有する半導体複合装置を搭載した光プリントヘッドを用いた電子写真カラープリンタであり、ブラック（K）、イエロー（Y）、マゼンタ（M）及びシアン（C）の各色の画像を各々に形成する4個のプロセスユニット10-1～10-4を有し、これらが記録媒体（例えば、用紙）20の搬送経路の上流側から順に配置されている。各プロセスユニット10-1～10-4の内部構成は共通しているため、例えば、マゼンタのプロセスユニット10-3を例にとり、これらの内部構成を説明する。20

【0024】

プロセスユニット10-3には、像担持体としての感光体ドラム11が図2中の矢印方向に回転可能に配置されている。感光体ドラム11の周囲には、この回転方向上流側から順に、感光体ドラム11の表面に電荷を供給して帯電させる帯電装置12と、帯電された感光体ドラム11の表面に選択的に光を照射して静電潜像を形成する露光装置（例えば、光プリントヘッド）13が配設されている。更に、静電潜像が形成された感光体ドラム11の表面に、マゼンタ（所定色）のトナーを付着させて顕像を発生させる現像器14と、感光体ドラム11上のトナーの顕像を用紙20に転写した後に残留したトナーを除去するクリーニング装置15が配設されている。なお、これら各装置に用いられているドラム又はローラは、図示しない駆動源からギア等を経由して動力が伝達され回転する。30

【0025】

画像形成装置1の下部には、用紙20を堆積した状態で収納する用紙カセット21が装着され、その上方に、用紙20を1枚ずつ分離させて搬送するためのホッピングローラ22が配設されている。用紙20の搬送方向におけるホッピングローラ22の下流側には、ピンチローラ23, 24と共に用紙20を挟持することによってこの用紙20を搬送する搬送ローラ25と、用紙20の斜行を修正し、プロセスユニット10-1に搬送するレジストローラ26とが配設されている。これらのホッピングローラ22、搬送ローラ25及びレジストローラ26は、図示しない駆動源からギア等を経由して動力が伝達され回転する。40

【0026】

プロセスユニット10-1～10-4の各感光体ドラム11に対向する位置には、それぞれ半導電性のゴム等によって形成された転写器27が配設されている。各転写器27には、感光体ドラム11上に付着されたトナーによる顕像を用紙20に転写する転写時に、各感光体ドラム11の表面電位とこれら各転写器27の表面電位に電位差を持たせるための電圧が印加されている。

【0027】

10

20

30

40

50

プロセスユニット 10 - 4 の下流には、定着器 28 が配設されている。定着器 28 は、ヒータが内蔵された加熱ローラとバックアップローラとを有し、用紙 20 上に転写されたトナーを加圧・加熱することによって定着する装置であり、この下流に、排出口ーラ 29, 30、排出部のピンチローラ 31, 32、及び用紙スタッカ部 33 が設けられている。排出口ーラ 29, 30 は、定着器 28 から排出された用紙 20 を、排出部のピンチローラ 31, 32 と共に挟持し、用紙スタッカ部 33 に搬送する。これら定着器 28 及び排出口ーラ 29 等は、図示しない駆動源からギア等を経由して動力が伝達されて回転する。

#### 【0028】

このように構成される画像形成装置 1 は、次のように動作する。

先ず、用紙カセット 21 に堆積した状態で収納されている用紙 20 が、ホッピングローラ 22 によって、上から 1 枚ずつ分離されて搬送される。続いて、この用紙 20 は、搬送ローラ 25、レジストローラ 26 及びピンチローラ 23, 24 に挟持されて、プロセスユニット 10 - 1 の感光体ドラム 11 と転写器 27 の間に搬送される。その後、用紙 20 は、感光体ドラム 11 及び転写器 27 に挟持され、その記録面にトナー像が転写されると同時に感光体ドラム 11 の回転によって搬送される。同様にして、用紙 20 は、順次プロセスユニット 10 - 2 ~ 10 - 4 を通過し、その通過過程で、各光プリントヘッド 13 により形成された静電潜像を各現像器 14 によって現像した各色のトナー像が、その記録面に順次転写されて重ね合わされる。

#### 【0029】

このようにして記録面上に各色のトナー像が重ね合わされた後、定着器 28 によってトナー像が定着された用紙 20 は、排出口ーラ 29, 30 及びピンチローラ 31, 32 に挟持されて、画像形成装置 1 の外部の用紙スタッカ部 33 に排出される。以上の過程を経て、カラー画像が用紙 20 上に形成される。

#### 【0030】

(プリンタ制御回路)

図 3 は、図 2 の画像形成装置 1 におけるプリンタ制御回路の構成を示すブロック図である。

#### 【0031】

このプリンタ制御回路は、画像形成装置 1 における印字部の内部に配設された印刷制御部 40 を有している。印刷制御部 40 は、マイクロプロセッサ、読み出し専用メモリ (ROM)、随時読み書き可能なメモリ (RAM)、信号の入出力を行う入出力ポート、タイマ等によって構成され、図示しない画像処理部からの制御信号 SG1、及びビデオ信号 (ドットマップデータを一次元的に配列したもの) SG2 等によって画像形成装置全体をシーケンス制御して印刷動作を行う機能を有している。印刷制御部 40 には、プロセスユニット 10 - 1 ~ 10 - 4 の 4 個の光プリントヘッド 13、定着器 28 のヒータ 28a、ドライバ 41, 43、用紙吸入口センサ 45、用紙排出口センサ 46、用紙残量センサ 47、用紙サイズセンサ 48、定着器用温度センサ 49、帯電用高圧電源 50、及び転写用高圧電源 51 等が接続されている。ドライバ 41 には現像・転写プロセス用モータ (PM) 42 が、ドライバ 43 には用紙送りモータ (PM) 44 が、帯電用高圧電源 50 には現像器 14 が、転写用高圧電源 51 には転写器 27 が、それぞれ接続されている。

#### 【0032】

このような構成のプリンタ制御回路では、次のような動作を行う。

印刷制御部 40 は、画像処理部からの制御信号 SG1 によって印刷指示を受信すると、先ず、温度センサ 49 によって定着器 28 内のヒータ 28a が使用可能な温度範囲にあるか否かを検出し、温度範囲になければヒータ 28a に通電し、使用可能な温度まで定着器 28 を加熱する。次に、ドライバ 41 を介して現像・転写プロセス用モータ 42 を回転させ、同時にチャージ信号 SG C によって帯電用高圧電源 50 をオン状態にし、現像器 14 の帯電を行う。

#### 【0033】

そして、セットされている図 2 中の用紙 20 の有無及び種類が用紙残量センサ 47、用

10

20

30

40

50

紙サイズセンサ48によって検出され、その用紙20に合った用紙送りが開始される。ここで、用紙送りモータ44には、図示しない遊星ギア機構が接続されており、ドライバ43を介して双方に回転させることができるのである。そのため、用紙送りモータ44の回転方向を変えることにより、画像形成装置内部の異なる用紙送り用の搬送ローラ25等を選択的に駆動することができる構成になっている。

#### 【0034】

用紙1ページの印刷開始毎に、用紙送りモータ44を最初に逆転させて、用紙吸入口センサ45が検知するまで、セットされた用紙20を予め設定された量だけ送る。続いて、正回転させて用紙20を画像形成装置内部の印刷機構内に搬送する。

#### 【0035】

印刷制御部40は、用紙20が印刷可能な位置まで到達した時点において、図示しない画像処理部に対してタイミング信号SG3（主走査同期信号、副走査同期信号を含む）を送信し、ビデオ信号SG2を受信する。画像処理部においてページ毎に編集され、印刷制御部40に受信されたビデオ信号SG2は、印刷データ信号として各光プリントヘッド13に転送される。各光プリントヘッド13は、それぞれ1ドット（ピクセル）の印字のために設けられた発光サイリスタを複数個線上に配列したものである。

#### 【0036】

ビデオ信号SG2の送受信は、印刷ライン毎に行われる。光プリントヘッド13からの発光は、マイナス電位に帯電された感光体ドラム11上に照射される。これにより、印刷される情報は、感光体ドラム11上において電位の上昇したドットとして潜像化される。そして、現像器14において、マイナス電圧に帯電された画像形成用のトナーが、電気的な吸引力によって各ドットに吸引され、トナー像が現像形成される。

#### 【0037】

その後、トナー像は転写器27へ送られ、一方、転写信号SG4によってプラス電圧に転写用高圧電源51がオン状態になり、転写器27は感光体ドラム11と転写器27との間隔を通過する用紙20上にトナー像を転写する。転写されたトナー像を有する用紙20は、ヒータ28aを内蔵する定着器28に当接して搬送され、この定着器28の熱によって用紙20に定着される。この定着された画像を有する用紙20は、更に搬送されて画像形成装置1の印刷機構から用紙排出口センサ46を通過して画像形成装置外部へ排出される。

#### 【0038】

印刷制御部40は、用紙サイズセンサ48、及び用紙吸入口センサ45の検知に対応して、用紙20が転写器27を通過している間だけ転写用高圧電源51からの電圧を転写器27に印加する。印刷が終了し、用紙20が用紙排出口センサ46を通過すると、帶電用高圧電源50による現像器14への電圧の印加を終了し、同時に現像・転写プロセス用モータ42の回転を停止させる。以後、上記の動作を繰り返す。

#### 【0039】

（光プリントヘッドの構造）

図4は、図3中の光プリントヘッド13の構造を示す概略の断面図である。

#### 【0040】

この光プリントヘッド13は、ベース部材13aを有し、このベース部材13a上にプリント配線板13bが固定されている。プリント配線板13b上には、複数個のチップ状のドライバIC100が熱硬化性樹脂等により固着され、これらのドライバIC100上に、複数個の被駆動素子アレイ（例えば、チップ状の発光サイリスタアレイ）200が貼着されている。複数個の発光サイリスタアレイ200上には、柱状の光学素子を多数配列してなるロッドレインズアレイ13cが配置され、このロッドレインズアレイ13cがホルダ13dにより固定されている。ベース部材13a、プリント配線板13b及びホルダ13dは、クランプ部材13e, 13fにより固定されている。

#### 【0041】

（光プリントヘッド基板ユニット）

10

20

30

40

50

図5は、図4中の光プリントヘッド基板ユニットを示す斜視図である。

【0042】

この光プリントヘッド基板ユニットは、プリント配線板13bを有し、このプリント配線板13b上に、発光サイリスタ駆動用の駆動回路（例えば、ゲート駆動用のシフトレジスタ）がそれぞれ形成された複数個のチップ状のドライバIC100が固着されている。複数個のドライバIC100上には、エピフィルムによりそれぞれ形成された複数個のチップ状の発光サイリスタアレイ200が貼着されている。各ドライバIC100と各発光サイリスタアレイ200とは、薄膜配線を用いて接続され、これらの各ドライバIC100と各発光サイリスタアレイ200とにより、半導体複合装置のチップが形成されている。各ドライバIC100及び各発光サイリスタアレイ200の各端子と、プリント配線板13b上の図示しない端子パッドとは、ボンディングワイヤ13gにより接続されている。

10

【0043】

このような光プリントヘッド基板ユニットを製造する場合、例えば、前記半導体複合装置のチップが多数配列されたウェハを公知のダイシング法を用いて複数のチップに分離し、このチップをプリント配線板13b上に固着した後、ボンディングワイヤ13gにより、前記複数のチップとプリント配線板13bとを接続している。

【0044】

（半導体複合装置のチップ）

図6(a)、(b)は、図5中のドライバIC100及び発光サイリスタアレイ200からなる半導体複合装置のチップの構成を示す回路図であり、同図(a)は全体の回路図、及び、同図(b)は同図(a)中のシフトレジスタの回路図である。

20

【0045】

ドライバIC100は、例えば、発光サイリスタアレイ200を時分割駆動するゲート駆動用のシフトレジスタ101により構成されている。シフトレジスタ101は、複数段（例えば、8段）のフリップフロップ回路（以下「FF」という。） $F_F_{110-1 \sim 110-8}$ がカスケード（縦続）接続されて構成され、例えば、シリコン基材を用いて形成されている。このシフトレジスタ101は、シリアルデータSIを入力するデータ入力端子Aと、シリアルクロックSCKを入力するクロック入力端子CKと、シフトされたデータを出力する8個の出力端子Q1～Q8とを有している。データ入力端子Aは、シフトレジスタ101内における第1段の $F_F_{110-1}$ のデータ入力端子dに接続され、8個の出力端子Q1～Q8は、各 $F_F_{110-1 \sim 110-8}$ のデータ出力端子qにそれぞれ接続され、更に、クロック入力端子CKは、各 $F_F_{110-1 \sim 110-8}$ のクロック入力端子ckにそれぞれ接続されている。

30

【0046】

このような構成のシフトレジスタ101は、入力されるシリアルクロックSCKに同期して、入力されるシリアルデータSIを内部の $F_F_{110-1 \sim 110-8}$ にて順にシフトしていく、シフトされたデータを出力端子Q1～Q8から出力する機能を有している。なお、出力端子Q1～Q8は、説明を簡単にするために8個のみが図示されているが、例えば、A4サイズの用紙20に1インチ当たり600ドットの解像度で印刷可能な光プリントヘッド13においては、出力端子Q1～Q8の総数は4992個であり、これが設けられることになる。

40

【0047】

シフトレジスタ101に接続された発光サイリスタアレイ200は、例えば、エピフィルムを用いて形成された複数の発光サイリスタ210（= $210-1 \sim 210-8$ ）により構成されている。前記出力端子Q1～Q8と同様に、発光サイリスタ210は、説明を簡単にするために8個のみが図示されているが、例えば、4992個が配列されている。各発光サイリスタ210-1～210-8は、アノードが端子Dに共通に接続され、カソードがグランドGNDに接続され、ゲートがシフトレジスタ101の各出力端子Q1～Q8にそれぞれ接続されている。

50

## 【0048】

端子Dには、図示しないアノード駆動回路が接続され、このアノード駆動回路から供給されるアノード駆動電流が、各発光サイリスタ210-1～210-8のアノードに供給されるようになっている。

## 【0049】

図示しないアノード駆動回路は、例えば、図3中の印刷制御部40内に搭載することが好ましく、図6においても、印刷制御部40内に設けられるとして、図示が省略されている。なお、アノード駆動回路は、光プリントヘッド13内に設けてもよい。

## 【0050】

10 このように構成されるシフトレジスタ101及び発光サイリスタアレイ200は、例えば、次のようにして製造される。

## 【0051】

エピフィルム上にP N P N層からなる複数の発光サイリスタ210-1～210-8を形成しておく。シフトレジスタ101を構成するに足りるトランジスタが予め形成されたICウェハ上に、前記エピフィルムを貼着し、このエピフィルムの不要部をエッチング除去することで、発光サイリスタ210-1～210-8の要部を形成する。その後、前記トランジスタ各部と前記発光サイリスタ210-1～210-8の端子部とを、薄膜配線により接続すれば製造が終了する。

## 【0052】

(半導体複合装置からなる複合チップの構造及び製造方法)

20 本発明の実施例1における図6のドライバIC100及び発光サイリスタアレイ200により構成される半導体複合装置からなる複合チップは、例えば、以下の(1)～(5)の工程により製造される。

## 【0053】

(1) 図7-1、図7-2の工程

図7-1及び図7-2は、図6中のメサ型発光サイリスタ210の製造方法を示す模式的な断面図である。

## 【0054】

図7-1に示すように、図6中のメサ型発光サイリスタ210の製造方法では、例えば、有機金属化学蒸着法(Metal Organic Chemical Vapor Deposition、以下「MOCVD法」という。)や分子線エピタキシー法(Molecular Beam Epitaxy、以下「MBE法」という。)等を用い、以下のようにして、エピフィルム製造用基材220上にエピタキシャル層230を形成する。

## 【0055】

先ず、GaAs基板221上に、GaAsバッファ層222を成膜してエピフィルム製造用基材220を形成し、更に、GaAsバッファ層222上に、犠牲膜であるアルミニウム・砒素(A1As)剥離層231を成膜する。

## 【0056】

なお、後述する工程において、基材220上にエピタキシャル層230を成膜した後、このエピタキシャル層230を剥離してエピフィルム230-1を形成するのであるが、エピタキシャル層230を剥離した後のGaAs基板221を含む基材220は、製造開始時の形態をとどめており、新しいエピタキシャル層230を成膜するために再利用することができる。

## 【0057】

前記A1As剥離層231を成膜した後、この上に、n型アルミニウム・ガリウム・砒素(A1GaAs)層232と、n型GaAsコンタクト層233を順に成膜する。次いで、インジウム・ガリウム・リン(InGaP)エッチングストップ層234、p型A1GaAs層235、n型A1GaAs層236、InGaPエッチングストップ層237、p型A1GaAs層238、及び、p型GaAsコンタクト層239を順に成膜して、エピタキシャル層230を形成する。

10

20

30

40

50

## 【0058】

なお、図7-1においては説明を簡略化するために、A<sub>1</sub>GaAsの混晶比を変えた複層構造として図示していないが、混晶比を様々に変えることで、シングルヘテロ接合、ダブルヘテロ接合を実現することができる。

## 【0059】

次に、図7-2に示すように、例えば、フォトリソグラフィ法とウェットエッティング法を用いて、A<sub>1</sub>As剥離層231を選択的に除去する。

## 【0060】

ウェットエッティング法を用いた場合、ウェットエッティング薬液の組成を適切に選択することで、A<sub>1</sub>As剥離層231に対するエッティング速度を、A<sub>1</sub>GaAs層、GaAs層、及びエッティングトップ層に対するエッティング速度に比べ格段に大きくすることができ、A<sub>1</sub>As剥離層231を選択的にエッティングすることが可能である。10

## 【0061】

これにより、エピタキシャル層230をエピフィルム製造用基材220から剥がしてエピフィルム230-1を形成することが可能になる。そのため、図7-2に示すように、エピタキシャル層230をエッティングし、溝240を形成しておく。溝240の形成は、溝部の予定領域以外をレジスト等によりマスクするフォトリソグラフィ工程と、例えばクエン酸／アンモニア／過酸化水素水を調製したエッティング薬液を用いるウェットエッティング法とを用いて行うことができる。

## 【0062】

なお、図7-2には、A<sub>1</sub>As剥離層231の一部が残されている状態（エッティング途中）が図示されているが、エピフィルム230-1を保持した状態で、最終的にA<sub>1</sub>As剥離層231は完全に除去される。20

## 【0063】

エピフィルム230-1の剥離に際して、このエピフィルム230-1を支持及び保護する支持体を、エピフィルム230-1上に設けることができる。例えば、エピフィルム230-1上に支持体を設けた場合、エピフィルム支持体表面を、例えば、真空吸着や、光照射により粘着性を失う光硬化性粘着シート等により吸着し、所定の位置に移動することができる。

## 【0064】

## (2) 図7-3の工程

図7-3は、半導体複合装置の製造方法を示す模式的な断面図である。

## 【0065】

図7-3に示すように、複数の半導体複合装置を有する複合チップの製造方法では、図6中のシフトレジスタ101を構成するためのトランジスタが形成されたICウェハ240上に、エピフィルム230-1を貼着する。

## 【0066】

ここで、ICウェハ240は、図示を省略したシフトレジスタ101を構成するためのトランジスタが形成されたシリコン基板241を有し、このシリコン基板241の表面が、保護膜であるパッシベーション膜242により被覆され、更に、このパッシベーション膜242上に、ポリイミド等の平坦化膜である接着層251が形成されている。接着層251上には、エピフィルム230-1が貼着され、更に、アノード252、ゲート253及びカソード254が形成されて、複数のメサ型発光サイリスタ210が形成される。40

## 【0067】

以下、具体的な製造方法を説明する。

エピフィルム230-1は、n型A<sub>1</sub>GaAs層232と、n型GaAsコンタクト層233と、InGaPエッティングトップ層234と、p型A<sub>1</sub>GaAs層235と、n型A<sub>1</sub>GaAs層236と、InGaPエッティングトップ層237と、p型A<sub>1</sub>GaAs層238と、p型GaAsコンタクト層239とを順に積層させた構造を持つ。

## 【0068】

10

20

30

40

50

図7-3においては、各層のエッチング端面が切り立った段差状に描かれているが、これは作図を簡略化しているためであり、後述する電極配線を行うときに前記段差部で断線しないよう斜面を形成することが望ましい。このため、A1GaAsからなるエピフィルム230-1をエッチングする際、前記斜面を形成しやすくするために、その結晶方位とエッチング薬液の調製を行うことで、メサ台地状の形状を与えることができる。

#### 【0069】

前記エッチング加工の後、図示を省略した絶縁膜を付加し、この絶縁膜の開口部として形成されたn型GaAsコンタクト層233上にメタル電極を形成することで、発光サイリスタ210のカソード254とし、n型A1GaAs層236上にメタル電極を形成することで、発光サイリスタ210のゲート253とし、更に、p型GaAsコンタクト層289上にメタル電極を形成することで、発光サイリスタ210のアノード252としている。

10

#### 【0070】

なお、メタル電極からなるアノード252、ゲート253及びカソード254は、それぞれ別の工程で形成することも可能であるが、それぞれが平面的に交差しないように配置することで、一括して同じ工程で形成することが可能であって、より好ましい。

#### 【0071】

又、エピフィルム230-1の材料として、A1GaAsからなる化合物半導体結晶を用いているが、この他にA1GaInP、ガリウム・窒素(GaN)、AlGaN、InGaN等の他の材料を用いることも可能である。

20

#### 【0072】

更に補足すれば、前記説明においては、図示を簡略化するためにホモ接合型の発光サイリスタ210として説明したが、エピタキシャル層230として、シングルヘテロ型に複数のエピタキシャル層を積層してPNPN接合構造のシングルヘテロ型発光サイリスタ、や、エピタキシャル層230として、ダブルヘテロ型に複数のエピタキシャル層を積層してPNPN接合構造のダブルヘテロ型発光サイリスタ、あるいは、更に多数の屈折率分布層を形成した分布反射(Distributed Bragg Refraction、以下「DBR」という。)型発光サイリスタとすることも可能である。

#### 【0073】

##### (3) 図7-4(a)、(b)の工程

図7-4(a)、(b)は、複合チップの模式的な平面を示す図であって、後述する配線工程の前の状態が模式的に示されている。このうち、図7-4(a)は複合チップの平面図、及び、図7-4(b)は図7-4(a)中のNチャネルMOSトランジスタ(以下「NMOS」という。)及びPチャネルMOSトランジスタ(以下「PMOS」という。)の平面図である。

30

#### 【0074】

図7-4(a)において、シリコン基板241の領域に図示された外周線は、前述したダイシング工程によりチップ状に個片化される時のダイシング予定線を示し、このダイシング予定線内にエピフィルム230-1が貼着される。エピフィルム230-1の不要領域がエッチング除去され、p型GaAsコンタクト層239が露出されてアノード領域が形成され、n型A1GaAs層236が露出されてゲート領域が形成され、更に、n型GaAsコンタクト層233が露出されてエピフィルム230-1の貼着領域と略等しいカソード領域が形成される。

40

#### 【0075】

これらのアノード領域、ゲート領域、及びカソード領域上には、アノード252、ゲート253、及びカソード254が形成された後、全面が図示しない絶縁膜により覆われ、この絶縁膜の所定箇所にコンタクト用の開口部が形成されてアノード252、ゲート253、及びカソード254が露出している。

#### 【0076】

エピフィルム230-1の近傍のシリコン基板241内には、例えば、図6中のシフト

レジスタ 101 の FF110 - 1 ~ 110 - 8 を構成するための PMOS111, 112 及び NMOS113, 114 等が形成されている。図 7 - 4 においては、図示を簡略化する目的で回路図シンボルが描画されている。

#### 【0077】

PNMOS111 は、ソース端子（以下単に「ソース」という。）115、及びドレイン端子（以下単に「ドレイン」という。）を有している。更に、NMOS113 は、ソース118、及びドレイン117を有している。PMOS111 及び NMOS113 は、後述するポリシリコン配線上に設けた共通のゲート端子（以下単に「ゲート」という。）119を有している。

#### 【0078】

なお、PMOS111 と NMOS113、及び、PMOS112 と NMOS114 とで、それぞれゲートを共通に接続して図示されているが、これらは後ほど行われるメタル配線工程において、ソース115 は図示しない電源と、ソース118 はグランドと、ドレイン116 とドレイン117 とを接続した後に、シフトレジスタ101 を 8 段の FF110 - 1 ~ 110 - 8 で構成するためのインバータを形成する場合が例示されている。なお、FF110 - 1 ~ 110 - 8 の各々は、インバータとトランスマッシュゲートを用いて構成してもよい。この場合、トランスマッシュゲートは、PMOS と NMOS の各々のソース同士、及び、各々のドレイン同士を接続し、ゲートは分けて設けることにより、容易に形成することができる。

#### 【0079】

このように、エピフィルム 230 - 1 を貼着するためのシリコン基板 241 には、トランジスタ等の任意の回路素子を予め配置すると共に、回路素子相互の配線を可能な限りポリシリコン配線を用いて予め接続しておくことで、この後行われるメタル配線工程での配線相互の交差を防止し、ショート不良防止のためにその間隔を適切に保つことが可能となる。

#### 【0080】

図 7 - 4 (b) には、図 7 - 4 (a) 中の PMOS111 及び NMOS113 に対応して描いた MOS トランジスタの平面が示されている。

#### 【0081】

図 7 - 4 (b) において例示するのは、n 型シリコン基板 241 を用いる場合であって、NMOS113 を形成するために所定箇所に p ウェル領域 123、及びポリシリコン配線 121 が形成されている。PMOS111 を形成するための p 型不純物領域 122 は、ポリシリコン配線 121 をマスクとして矩形領域に p 型不純物を注入するものであって、ポリシリコン配線 121 をゲートとしてその領域 122 が左右に分断され、一方がソース領域、他方がドレイン領域となって、それぞれの領域にコンタクト用のソース115 及びドレイン116 が形成されている。

#### 【0082】

又、NMOS113 を形成するための n 型不純物領域 124 は、n 型不純物の注入領域であって、p ウェル領域 123 中に形成され、ポリシリコン配線 121 をマスクにして矩形領域に n 型不純物を注入して形成される。そして、ポリシリコン配線 121 をゲートとしてその領域 124 は分断され、一方がソース領域、他方がドレイン領域となって、それぞれの領域にコンタクト用のソース118 及びドレイン117 が形成されている。

#### 【0083】

このようにしてシリコン基板 241 内に形成された PMOS111 及び NMOS113 は、この後行われるメタル配線工程において、ソース115 は電源と、ソース118 はグランドと、それぞれ接続されると共に、ドレイン116 とドレイン117 とは接続されてインバータの出力端子となり、ポリシリコン配線 121 のコンタクト部 119 はインバータの入力端子となる。このとき同時に、前記インバータのみならず、他の回路素子相互も又前記メタル配線により接続され、全体でシフトレジスタ101 を構成するようになっている。

10

20

30

40

50

## 【0084】

## (4) 図1の工程

図1は、本発明の実施例1における図7-4の半導体複合装置の配線構造を示す模式的な断面図である。

## 【0085】

シリコン基板241には、シフトレジスタ101を構成する予定のトランジスタが予め形成され、トランジスタを構成した後に、シリコン基板上層が、窒化シリコン(SiN)、酸化シリコン(SiO<sub>2</sub>)等で形成されたパッシベーション膜242により覆われる。パッシベーション膜242の下層には、後述する層間絶縁膜244が形成されており、この層間絶縁膜244を含む破線で囲まれた領域には、前記トランジスタ等からなる回路構成層243が形成されている。これらのシリコン基板241及び回路構成層243等からなるMOSトランジスタ等を含むICウェハは、公知の相補型MOSトランジスタ(以下「CMOS」という。)プロセスを用いて製造される。

## 【0086】

図1では、図示を簡略化するために、一部のPMOS111のみが図示されている。PMOS111は、ゲート部であるポリシリコン配線121、p型不純物拡散領域からなるドレイン領域120、及び、p型不純物拡散領域からなるソース領域121により構成されている。そして、PMOS111等の回路素子のソース及びドレインの予定箇所には、パッシベーション膜242の上層から層間絶縁膜244を通り、半導体層に至る深さに、後述するソース開口部115a及びドレイン開口部116aが形成されている。

## 【0087】

このようにして形成されたICウェハの上層の所定箇所には、平坦化膜である接着層251が形成され、この上層に、図7-3で説明したエピフィルム230-1が貼着され、フォトリソグラフィ法とウェットエッティング法を用いて、そのエピフィルム230-1の所定層の要部が露出され、発光サイリスタ210の端子予定部が形成される。

## 【0088】

PIN構造からなる発光サイリスタ210において、接着層251上の第4層のn型AlGaAs層はカソード層264に相当する。カソード層264上には、第3層のp型AlGaAs層263、ゲート層262に相当する第2層のn型AlGaAs層、及び、アノード層261に相当する第1層のp型AlGaAs層が順に積層されている。

## 【0089】

アノード層261の所定箇所には、図示しない絶縁層に開口することで形成されるコンタクト用のアノード252が設けられ、アノード配線265に接続される。同様に、第2層のn型AlGaAs層の所定箇所には、図示しない絶縁層に開口することで形成されるコンタクト用のゲート253が設けられ、ゲート配線265に接続される。ゲート配線265は、PMOS111におけるスルーホール予定ドレイン開口部116aにも接続される。PMOS111におけるソース開口部115aにも配線267が形成され、図示しない電源及びグランドに接続されている。

## 【0090】

このように、発光サイリスタ210を構成するPIN層からなるエピフィルム230-1の端子エッティングの後に行われるアノード配線265、ゲート配線265及び配線267等のメタル配線は、同一の工程により行われる。例えば、Al等のメタル材料をウェハ全面にスパッタリング法で薄膜状に形成した後、フォトリソグラフィ法により要部以外を除去することでメタル配線を形成し、前述した発光サイリスタ210とシフトレジスタ101との間の接続配線のみならず、シフトレジスタ自体を構成するための回路配線をも同時に形成することができる。

## 【0091】

なお、配線の形成法としては、上記に限定されず、公知のリフトオフ法等によっても形成可能である。

## 【0092】

10

20

30

40

50

( 5 ) 複合チップ全体の概略の製造工程

図 8 ( a ) ~ ( c ) は、図 7 - 3 及び図 1 におけるメサ型複合チップの概略の製造工程を示す図であり、同図 ( a ) は処理工程図、同図 ( b ) は概略の断面図、及び同図 ( c ) は概略の平面図である。

【 0 0 9 3 】

メサ型複合チップの製造工程では、ステップ S 1 の I C ウェハ下地処理において、I C ウェハ 2 4 0 の上層に、シフトレジスタ 1 0 1 を構成する配線前の状態のトランジスタを形成した後、I C ウェハ 2 4 0 の表面の所定箇所に、平坦化膜である接着層 2 5 1 を形成する。ステップ S 2 のエピフィルムボンディング工程において、予め作成しておいたエピフィルム 2 3 0 - 1 を接着層 2 5 1 上に貼着する。

10

【 0 0 9 4 】

ステップ S 3 のアノード・ゲートエッチング工程において、発光サイリスタ 2 1 0 のアノード 2 5 2 とゲート 2 5 3 を形成する。ステップ S 4 のカソード形成エッチング工程において、カソード 2 5 4 を形成する。その後、ステップ S 5 のメタル配線工程において、発光サイリスタ 2 1 0 のアノード配線 2 6 5 及びゲート配線 2 6 6 と、シフトレジスタ 1 0 1 の配線 2 6 7 とを形成すれば、所望の複合チップが得られる。

【 0 0 9 5 】

( 実施例 1 の光プリントヘッドの動作 )

図 9 は、図 6 の光プリントヘッド 1 3 の動作を説明するためのタイムチャートである。

【 0 0 9 6 】

この図 9 では、画像形成装置 1 での印刷動作時における 1 ライン走査の状況が示され、図 6 の発光サイリスタ 2 1 0 - 1 ~ 2 1 0 - 8 を順次点灯させる場合の動作波形が図示されている。

20

【 0 0 9 7 】

なお、図 9 では図示されていないが、画像形成装置 1 における電源投入時の予備動作として、シフトレジスタ 1 0 1 のプリセット処理が行われる。この処理では、図 6 のシフトレジスタ 1 0 1 におけるシリアルデータ S I 入力用のデータ入力端子 A を “ H ” レベルにしておき、シフトレジスタ 1 0 1 の段数に相当する個数のシリアルクロック S C K のパルスをクロック入力端子 C K にする。これにより、シフトレジスタ 1 0 1 における全出力端子 Q 1 ~ Q 8 が “ H ” レベルになる。

30

【 0 0 9 8 】

図 9 において、1 ライン分の走査に先立ち、時刻 t 1 において、シリアルデータ S I は “ L ” にされる。次いで時刻 t 2 において、シリアルクロック S C K の第 1 パルスが入力される。シリアルクロック S C K が立ち上がると、入力されたシリアルデータ S I は、シフトレジスタ 1 0 1 内の第 1 段の F F 1 1 0 - 1 に取り込まれ、これより僅かに遅れて第 1 段の F F 1 1 0 - 1 の出力端子 Q 1 が “ L ” レベルへと遷移する。シリアルクロック S C K が立ち上がった後の時刻 t 3 において、入力されるシリアルデータ S I が再び “ H ” レベルに戻される。

【 0 0 9 9 】

時刻 t 2 で出力端子 Q 1 が “ L ” レベルとなると、発光サイリスタ 2 1 0 - 1 のゲート電圧を低下させる。時刻 t 4 において、図示しないアノード駆動回路から端子 D に入力されるアノード駆動信号が “ H ” になる。これにより、発光サイリスタ 2 1 0 - 1 のアノード・ゲート間に電位差を生じ、トリガ電流によって発光サイリスタ 2 1 0 - 1 がターンオンして点灯する。発光サイリスタ 2 1 0 - 1 の点灯は、主としてアノード・カソード間に流れる電流によるもので、一度ターンオンした発光サイリスタ 2 1 0 - 1 をオフさせるためには、アノード・カソード間に印加される電圧をゼロにする。このため、時刻 t 5 において、端子 D の電位を “ L ” にしている。

40

【 0 1 0 0 】

なお、図 9 では、発光サイリスタ 2 1 0 - 1 を点灯させるために、時刻 t 4 で端子 D を “ H ” レベルとし、消灯させるために、時刻 t 5 で端子 D を “ L ” レベルにしているが、

50

発光サイリスタ 210-1 を点灯させる必要がない場合には、時刻  $t_4 \sim t_5$  間も端子 D を “L” レベルのままにすればよい。このように、端子 D に入力されるアノード駆動信号の電位により、発光サイリスタ 210-1 の点灯 / 消灯状態を切り替えることができる。

#### 【0101】

時刻  $t_6$  において、シリアルクロック SCK が立ち上がる。この時、端子 A に入力されるシリアルデータ SI は “H” レベルになっているので、これより僅かに遅れて出力端子 Q1 が “H” レベルへと遷移する一方で、出力端子 Q2 が “L” レベルに変化する。

#### 【0102】

時刻  $t_7$  において、端子 D に入力されるアノード駆動信号が “H” になる。これにより、発光サイリスタ 210-2 のアノード・ゲート間に電位差を生じ、トリガ電流によって発光サイリスタ 210-2 がターンオンして点灯する。発光サイリスタ 210-2 の点灯は、主としてアノード・カソード間に流れる電流によるもので、一度ターンオンした発光サイリスタ 210-2 をオフさせるためには、アノード・カソード間に印加される電圧をゼロにする。このため、時刻  $t_8$  において、端子 D の電位を “L” にしている。

10

#### 【0103】

前記説明で明らかなように、図 6 に示すシリアルクロック SCK のパルス 1, 2, 3, 4, 5, 6, 7, 8 の立ち上がり毎に、各出力端子 Q1, Q2, Q3, Q4, Q5, Q6, Q7, Q8 は順次 1 出力信号だけが “L” レベルとなり、他の出力信号は “H” レベルである。このため、端子 D に入力されるアノード駆動信号が “H” レベルの時、出力端子 Q1 ~ Q8 に接続された発光サイリスタ 210-1 ~ 210-8 の内、対応する出力端子 Q1 ~ Q8 が “L” レベルになっているものだけが逐一的に点灯する。点灯時間は、図 9 における時刻  $t_4 \sim t_5$ ,  $t_7 \sim t_8$  といった期間であって、その点灯時間はそれぞれの発光サイリスタ 210-1 ~ 210-8 毎に調整可能になっている。

20

#### 【0104】

前記説明において、発光サイリスタ 210-1 ~ 210-8 をオンさせるためには、アノード・ゲート間に順方向にバイアスさせる電位差を与えるだけでなく、オフ状態のままとするためには、電位差を発光サイリスタ 210 の順方向電圧以下としておくだけで十分であり、電位差ゼロとしたり、逆方向へ電圧を印加することもできる。

30

#### 【0105】

又、発光サイリスタ 210 に流れる電流は、主としてアノード・カソード間に流れ、その点灯 / 消灯状態を指令するためのゲート端子には僅かな電流しか流れず、シフトレジスタ 101 の各出力端子 Q1 ~ Q8 等には大きな電流駆動能力を要しない。

#### 【0106】

そのため、シフトレジスタ 101 においても、出力端子 Q1 ~ Q8 を駆動する駆動トランジスタの面積はごく小さなものでよく、半導体素子として大きなチップ面積を占有されることはないという利点を有している。この結果、シフトレジスタ 101 を用いて成る半導体複合措置のチップのコストを低減することができて、光プリントヘッド 13、ひいては画像形成装置 1 の製造コストを飛躍的に低減させることが可能となる。

#### 【0107】

( 実施例 1 の変形例 )

40

図 10 は、実施例 1 の図 6 (a) における光プリントヘッド 13 の構成の変形例を示す回路図であり、図 6 (a) 中の要素と共に通の要素には共通の符号が付されている。

#### 【0108】

この変形例の光プリントヘッド 13 は、実施例 1 と同様に、シフトレジスタ 101 を有するドライバ IC 100 が形成された IC ウェハ上に、発光サイリスタアレイ 200 が貼着されている。シフトレジスタ 101 のデータ入力端子 A 及びクロック入力端子 CK と、発光サイリスタアレイ 200 の端子 D とは、図 3 中の印刷制御部 40 の出力側に接続されている。

#### 【0109】

印刷制御部 40 には、発光サイリスタアレイ 200 の端子 D に接続されたアノード駆動

50

回路（例えば、電流出力型のデジタル／アナログコンバータ、「D A C」という。）300が内蔵されている。D A C 300は、8ビットからなるデジタル信号D 7～D 0を入力するD 7～D 0端子と、デジタル信号D 7～D 0を伝達するためのクロックC L Kを入力するクロック入力端子C Kと、抵抗301を介してグランドG N Dに接続されたF S A端子と、アナログ値の256階調からなるアノード駆動信号を出力する出力端子I o u tとを有している。D 7～D 0端子は、印刷制御部40内の図示しない印刷データ生成回路に接続され、出力端子I o u tは、発光サイリスタアレイ200の端子Dに接続されている。

#### 【0110】

D A C 300は、電流出力型の構成のものであれば種々の品種が選択可能であり、本変形例では、例えば、米国Burr - Brown社製のD A C 908を採用している。このD A C 300は、印刷制御部40内の図示しない印刷データ生成回路で生成された印刷ドット毎の駆動エネルギー値に応じた256段階の駆動指令値である8ビットのデジタル信号D 7～D 0をD 7～D 0端子から入力し、これをアナログ値に変換し、256階調からなる電流値のアノード駆動信号を出力端子I o u tから出力する回路である。10

#### 【0111】

D A C 300のF S A端子に接続された抵抗301は、D A C 300内で発生される基準電圧値を基に、出力端子I o u tからのフルスケール時の電流出力量を設定するために用いられる。このため、デジタル信号D 7～D 0が16進数で00の時に、出力端子I o u tから出力される電流値はゼロであり、デジタル信号D 7～D 0が16進数でFF(10進数表記では255)の場合に最大駆動電流が得られる。出力端子I o u tから出力されるアノード駆動信号は、端子Dを介して各発光サイリスタ210(=210-1～210-8)のアノードへ供給される。20

#### 【0112】

図11は、図10の光プリントヘッド13の動作を説明するためのタイムチャートであり、実施例1の図9に対応している。

#### 【0113】

図11中のデジタル信号D 7～D 0や出力端子I o u tの信号中に記載された数値は、動作説明のための数値例であって16進数にて表記されている。この図11では、画像形成装置1での印刷動作時における1ライン走査の状況が示され、発光サイリスタ210-1～210-8を順次点灯させる場合の動作波形が図示されている。30

#### 【0114】

なお、図11では図示していないが、実施例1の図9と同様に、画像形成装置1の電源投入時における予備動作として、シフトレジスタ101のプリセット処理が行われる。このプリセット処理では、シリアルデータS Iが入力されるデータ入力端子Aを“H”レベルにしておき、シフトレジスタ101の段数に相当するシリアルクロックS C Kの8個のパルスをクロック入力端子C Kに入力する。これにより、シフトレジスタ101の全出力端子Q 1～Q 8が“H”レベルとなる。

#### 【0115】

図11において、1ライン分の走査に先立ち、時刻t1において、データ入力端子Aに入力されるシリアルデータS Iが“L”レベルになる。時刻t2において、シリアルクロックS C Kの第1パルスがシフトレジスタ101に入力される。時刻t2でその第1パルスが立ち上ると、これが図6(b)に示すシフトレジスタ101内の第1段のFF110-1に取り込まれ、これより僅かに遅れて、第1段のFF110-1の出力端子Q 1が“L”レベルへと遷移する。シリアルクロックS C Kが立ち上がった後、時刻t3において、入力されるシリアルデータS Iは再び“H”レベルに戻される。40

#### 【0116】

出力端子Q 1が“L”レベルになると、発光サイリスタ210-1のゲート電圧が低下する。図11の例ではこの時、同時にD A C 300のデータ入力として16進数表記で30のデジタル信号D 7～D 0が入力されている。50

## 【0117】

時刻  $t_4$ において、DAC300のクロック入力端子CKに入力されるクロックCLKが立ち下がり、DAC300は、D7～D0入力端子に与えられたデータ30を内部に取り込み、この数値に比例する駆動電流値のアノード駆動信号を出力端子Ioutから出力し、端子Dを介して各発光サイリスタ210-1～210-8のアノードへ供給する。これにより、発光サイリスタ210-1のアノード・ゲート間に電位差が生じ、トリガ電流によって発光サイリスタ210-1がターンオンして点灯する。

## 【0118】

発光サイリスタ210-1の点灯は、主としてアノード・カソード間に流れる電流によるものである。一度ターンオンした発光サイリスタ210-1をオフにする場合は、アノード・カソード間に印加される電圧をゼロにする。このため、時刻  $t_5$ において、D7～D0入力端子への入力デジタル信号D7～D0を00にした後、時刻  $t_6$ において、クロックCLKの電位を“L”にして、前記00の入力デジタル信号D7～D0をDAC300に取り込ませる。時刻  $t_6$ におけるクロックCLKより僅かに遅れて、出力端子Ioutから出力されるアノード駆動信号は、前記00の入力デジタル信号D7～D0に応じて電流値がゼロとなって、発光サイリスタ210-1がオフ状態になる。

10

## 【0119】

なお、図11では、発光サイリスタ210-1を点灯させるために、時刻  $t_4$ において、D7～D0入力端子に入力されるデジタル信号D7～D0のデータ30を取り込んで、これに対応する駆動電流値のアノード駆動信号を出力端子Ioutから出力し、発光サイリスタ210-1を消灯させるために、時刻  $t_6$ において、デジタル信号D7～D0のデータ00を取り込むことで、駆動電流値をゼロとして消灯させている。しかし、発光サイリスタ210-1を点灯させる必要がない場合には、時刻  $t_2$ ～ $t_5$ の間もデジタル信号D7～D0を00のままですればよい。

20

## 【0120】

このように、デジタル信号D7～D0の値により、発光サイリスタ210-1の点灯／消灯状態を切り替えとことができることはもちろん、入力されたデジタル信号D7～D0における255段階の電流指令値に応じて、アノード駆動信号の駆動電流値を変化させることができる。

30

## 【0121】

次に、時刻  $t_7$ において、シリアルクロックSCKが立ち上がる。この時、シフトレジスタ101のデータ入力端子Aに入力されるシリアルデータSIは、“H”レベルになっているので、これより僅かに遅れて、シフトレジスタ101の出力端子Q1が“H”レベルへと遷移する一方で、出力端子Q2が“L”レベルに変化する。この時、DAC300のD7～D0入力端子には、デジタル信号D7～D0のデータ60が入力されている。

## 【0122】

時刻  $t_8$ において、クロックCLKが立ち下がり、前記データ60がDAC300の内部に取り込まれる。これよりわずかに遅れて、DAC300の出力端子Ioutから、前記データ60に応じたアノード駆動信号が出力される。このため、発光サイリスタ210-2のアノード・ゲート間に電位差が生じ、トリガ電流によって発光サイリスタ210-2がターンオンして点灯する。

40

## 【0123】

発光サイリスタ210-2の点灯状態は、主としてアノード・カソード間に流れる電流によるものである。一度ターンオンした発光サイリスタ210-2をオフさせるためには、アノード・カソード間に印加される電圧をゼロにする。このため、時刻  $t_9$ において、デジタル信号D7～D0のデータを00とし、時刻  $t_{10}$ において、シリアルクロックSCKを立ち下がらせ、その電流値指令データ00をDAC300内に取り込む。この結果、DAC300の出力端子Ioutから出力されるアノード駆動信号の駆動電流値がゼロとなり、発光サイリスタ210-2がターンオフする。

## 【0124】

50

このように、図11に示すシリアルクロックSCKのパルス1, 2, 3, 4, 5, 6, 7, 8の立ち上がり毎に、シフトレジスタ101における各出力端子Q1, Q2, Q3, Q4, Q5, Q6, Q7, Q8の出力信号が順次1つだけ“L”レベルになり、他の出力信号が“H”レベルである。このため、デジタル信号D7～D0が非ゼロの時、シフトレジスタ101の出力端子Q1～Q8に接続された発光サイリスタ210-1～210-8の内、対応する出力端子Q1～Q8が“L”レベルになっているものだけが逐一的に点灯する。又、デジタル信号D7～D0がゼロの時には、全発光サイリスタ210-1～210-8を消灯状態にできる。

#### 【0125】

前述の説明において、発光サイリスタ210-1～210-8をオンさせるためには、アノード・ゲート間に順方向にバイアスさせる電位差を与えるだけでよい。オフ状態のままとするためには、その電位差を順方向電圧以下としておくだけで十分であり、電位差をゼロとしたり、逆方向へ電圧を印加することもできる。

#### 【0126】

又、発光サイリスタ210-1～210-8に流れる電流は、主としてアノード・カソード間に流れ、その点灯／消灯状態を指令するためのゲートには僅かな電流しか流れず、シフトレジスタ101の各出力端子Q1～Q8等には大きな電流駆動能力を要しない。

#### 【0127】

この結果、シフトレジスタ101の駆動部の素子面積を最小化することができ、チップサイズを縮小することが可能となって製造コストの大幅ダウンを達成できる。

#### 【0128】

更に、本変形例の構成においては、発光サイリスタ210の駆動電流値を255段階に調整できるようにしたので、各発光サイリスタ210毎に発光効率が異なる場合においても、順次駆動毎に駆動電流値を変化させることで、発光パワーを所定値に調整することが可能となる。

#### 【0129】

この結果、発光サイリスタ210-1～210-8の製造段階において、製造ばらつきによって発光サイリスタ210-1～210-8毎に発光効率が異なることになっても、不良品として廃棄することなく使用可能となる。このように、本変形例の構成においては、発光サイリスタ210の製造段階における製造歩留まりを著しく向上させることができ、なおいっそうのコストダウンを達成できる。

#### 【0130】

その上、前記光量補正に加えて、各発光サイリスタ210-1～210-8毎にアノード駆動信号を変化させることで、感光体ドラム11上の静電潜像を変化させ、ドット毎に異なるトナー像の面積を形成可能な階調駆動を行うことも可能であり、写真画質の美麗な印刷結果を得ることができる。

#### 【0131】

(実施例1の効果)

本実施例1の半導体複合装置とこれを用いた光プリントヘッド13及び画像形成装置1によれば、次のような効果がある。

#### 【0132】

従来の半導体複合装置では、シフトレジスタの回路要素各部を接続するメタル配線をフォトリソグラフィ法により予め形成したシリコンウェハが用いられ、発光サイリスタアレイを貼着したのち、シフトレジスタ出力端子と発光サイリスタアレイのゲートとをメタル配線により再び接続する必要がある。このため、製造工程において前記メタル配線工程が2重に必要となり、コスト的な無駄を生じていた。

#### 【0133】

このような不都合を解消するために、本実施例1では、上記の構成とすることで、発光サイリスタアレイ200の予定端子とシフトレジスタ101の予定端子との配線工程において、シフトレジスタ自体を構成するための回路配線をも同時に形成することが可能とな

10

20

30

40

50

り、製造工程を簡略化できるので、製造コストの大幅な削減が可能となる。

#### 【0134】

更に、本実施例1及びこの変形例の画像形成装置1によれば、複合チップを有する光プリントヘッド13を採用するため、スペース効率及び光取り出し効率に優れた高品質の画像形成装置（プリンタ、複写機、ファクシミリ装置、複合機等）を提供することができる。即ち、光プリントヘッド13を用いることにより、上述したフルカラーの画像形成装置1に限らず、モノクロ、マルチカラーの画像形成装置においても効果が得られるが、特に露光装置を数多く必要とするフルカラーの画像形成装置において一層大きな効果が得られる。

#### 【実施例2】

#### 【0135】

本発明の実施例2では、画像形成装置1及び光プリントヘッド13の全体の構成が実施例1と同様であるが、半導体複合装置からなる複合チップの構造及び製造方法が異なるので、以下、その異なる部分を説明する。

#### 【0136】

（半導体複合装置からなる複合チップの構造及び製造方法）

本発明の実施例2における半導体複合装置からなる複合チップは、例えば、以下の（1）～（5）の工程により製造される。

#### 【0137】

（1）図12-1、図12-2の工程

図12-1及び図12-2は、拡散型発光サイリスタ210Aの製造方法を示す模式的な断面図であり、実施例1の図7-1及び図7-2中の要素と共に要素には共通の符号が付されている。

#### 【0138】

図12-1に示すように、本実施例2の拡散型発光サイリスタ210Aの製造方法では、例えば、実施例1と同様に、MOCVD法やMBE法等を用い、以下のようにして、実施例1と同様のエピフィルム製造用基材220上に、実施例1とは異なる構造のエピタキシャル層230Aを形成する。

#### 【0139】

先ず、実施例1と同様のGaAs基板221上に、実施例1と同様のGaAsバッファ層222を成膜して、実施例1と同様のエピフィルム製造用基材220を形成し、更に、GaAsバッファ層222上に、実施例1と同様のAlAs剥離層231を成膜する。

#### 【0140】

なお、実施例1と同様に、後述する工程において、基材220上にエピタキシャル層230Aを成膜した後、このエピタキシャル層230Aを剥離してエピフィルム230A-1を形成するのであるが、エピタキシャル層230Aを剥離した後のGaAs基板221を含む基材220は、製造開始時の形態をとどめており、新しいエピタキシャル層230Aを成膜のために再利用することができる。

#### 【0141】

前記AlAs剥離膜231を成膜した後、この上に、実施例1と同様のn型AlGaAs層232、n型GaAsコンタクト層233、InGaPエッチングトップ層234、p型AlGaAs層235、及びn型AlGaAs層236を順に成膜する。更に、本実施例2では、実施例1のInGaPエッチングトップ層237、p型AlGaAs層238、及び、p型GaAsコンタクト層239に代えて、これらとは異なるn型GaAsコンタクト層239Aを、n型AlGaAs層236上に成膜して、実施例1とは異なる構造のエピタキシャル層230Aを形成する。

#### 【0142】

なお、実施例1と同様に、図12-1においては説明を簡略化するために、AlGaAsの混晶比を変えた複層構造として図示していないが、混晶比を様々に変えることで、シングルヘテロ接合、ダブルヘテロ接合を実現することができる。

10

20

30

40

50

## 【0143】

次に、図12-2に示すように、実施例1と同様に、例えば、フォトリソグラフィ法とウェットエッティング法を用いて、AlAs剥離層222を選択的に除去する。

## 【0144】

ウェットエッティング法を用いた場合、実施例1と同様に、ウェットエッティング薬液の組成を適切に選択することで、AlAs剥離層231に対するエッティング速度を、AlAs層、GaAs層、及びエッティングトップ層に対するエッティング速度に比べ格段に大きくすることができ、AlAs剥離層231を選択的にエッティングすることが可能である。

## 【0145】

これにより、実施例1と同様に、エピタキシャル層230Aをエピフィルム製造用基板220から剥がしてエピフィルム230A-1を形成することが可能になる。そのため、図12-2に示すように、実施例1と同様に、エピタキシャル層230Aをエッティングし、溝240を形成しておく。溝240の形成は、実施例1と同様に、溝部以外の領域をレジスト等によりマスクするフォトリソグラフィ工程と、例えばクエン酸／アンモニア／過酸化水素水を使用するウェットエッティング法とを用いて行うことができる。

## 【0146】

なお、図12-2には、実施例1と同様に、AlAs剥離層231の一部が残されている状態（エッティング途中）が示されているが、エピフィルム230A-1を保持した状態で、最終的にAlAs剥離層231は完全に除去される。

## 【0147】

実施例1と同様に、エピフィルム230A-1の剥離に際して、このエピフィルム230A-1を支持及び保護する支持体を、エピフィルム230A-1上に設けることができる。例えば、エピフィルム230A-1上に支持体を設けた場合、エピフィルム支持体表面を、例えば、真空吸着や、光照射により粘着性を失う光硬化性粘着シート等により吸着し、所定の位置に移動することができる。

## 【0148】

## (2) 図12-3の工程

図12-3は、半導体複合装置の製造方法を示す模式的な断面図であり、実施例1の図7-3中の要素と共に通の要素には共通の符号が付されている。

## 【0149】

図12-3に示すように、複数の半導体複合装置を有する複合チップの製造方法では、実施例1と同様に、図6中のシフトレジスタ101を構成するためのトランジスタが形成されたICウェハ240上に、エピフィルム230A-1を貼着する。

## 【0150】

ここで、ICウェハ240は、実施例1と同様に、シフトレジスタ101を構成するためのトランジスタが形成されたシリコン基板241を有し、このシリコン基板241の表面が、パッシベーション膜242により被覆され、更に、このパッシベーション膜242上に、ポリイミド等の平坦化膜である接着層251が形成されている。接着層251上には、エピフィルム230A-1が貼着され、更に、不純物拡散領域（例えば、p型領域）255、アノード252、ゲート253及びカソード254が形成されて、複数の拡散型発光サイリスタ210Aが形成される。

## 【0151】

以下、具体的な製造方法を説明する。

エピフィルム230A-1は、n型AlGaAs層232と、n型GaAsコンタクト層233と、InGaPエッティングトップ層234と、p型AlGaAs層235と、n型AlGaAs層236と、n型GaAsコンタクト層239Aとを順に積層させた構造を持つ。

## 【0152】

このようなエピフィルム230A-1を、ICウェハ240側の接着層251上に貼着した後、n型GaAsコンタクト層239Aの上層から、例えば、固相拡散法を用いてZ

10

20

30

40

50

n等のp型不純物を拡散させ、n型GaAsコンタクト層239Å及びn型AlGaAs層236の要部にp型領域255を作成する。

#### 【0153】

なお、前記のZn等の不純物拡散のためには高温での熱処理が必要となるが、図12-3の状態においては、ICウェハ240中には耐熱性に劣るAl等のメタル配線が形成されていないので、前記熱処理によるダメージを生じることはない。

#### 【0154】

次に、n型GaAsコンタクト層233上にメタル電極を形成することで、発光サイリスタ210のカソード254とし、n型GaAsコンタクト層239Å上にメタル電極を形成することで、発光サイリスタ210のゲート253とし、更に、p型領域255上にメタル電極を形成することで、発光サイリスタ210Åのアノード252としている。10

#### 【0155】

なお、メタル配線からなるアノード252、ゲート253及びカソード254は、実施例1と同様に、それぞれ別の工程で形成することも可能であるが、それぞれが平面的に交差しないように配置することで、一括して同じ工程で作成することが可能であって、より好ましい。

#### 【0156】

又、実施例1と同様に、エピフィルム230Å-1の材料として、AlGaAsからなる化合物半導体結晶を用いているが、この他にAlGaNp、GaN、AlGaN、InGaN等の他の材料を用いることも可能である。20

#### 【0157】

更に補足すれば、前記説明においては、図示を簡略化するためにホモ接合型の発光サイリスタ210Åとして説明したが、エピタキシャル層230Åとして、シングルヘテロ型に複数のエピタキシャル層を積層してPNPN接合構造のシングルヘテロ型発光サイリスタや、エピタキシャル層230Åとして、ダブルヘテロ型に複数のエピタキシャル層を積層してPNPN接合構造のダブルヘテロ型発光サイリスタ、あるいは、更に多数の屈折率分布層を形成したDBR型発光サイリスタとすることも可能である。

#### 【0158】

##### (3) 図12-4(a)、(b)の工程

図12-4(a)、(b)は、本実施例2における複合チップの模式的な平面を示す図であって、後述する配線工程の前の状態が模式的に示されている。このうち、図12-4(a)は複合チップの平面図、及び、図12-4(b)は図12-4(a)中のNMOS及びPMOSの平面図である。30

#### 【0159】

この図12-4(a)、(b)は、実施例1の図7-4(a)、(b)に対応しており、図7-4(a)、(b)中の要素と共に通の要素には共通の符号が付されている。

#### 【0160】

図12-4(a)に示す複合チップでは、実施例1の図7-4(a)に示すエピフィルム230-1、n型AlGaAs層236、及びp型GaAsコンタクト層239に代えて、エピフィルム230Å-1、n型GaAsコンタクト層239Å、及びp型領域255が配置されている点のみが異なる。40

#### 【0161】

即ち、図12-4(a)において、シリコン基板241の領域に図示された外周線は、前述したダイシング工程によりチップ状に個片化される時のダイシング予定線を示し、このダイシング予定線内にエピフィルム230Å-1が貼着される。エピフィルム230Å-1の要部にZn等を拡散させてp型領域255のアノード領域が形成される。エピフィルム230Å-1におけるZn等の不拡散領域は、n型GaAsコンタクト層239Åからなるゲート領域である。エピフィルム230Å-1の不要領域が更にエッティング除去され、n型GaAsコンタクト層233が露出されてエピフィルム230Å-1の貼着領域と略等しいカソード領域が形成される。50

## 【0162】

これらのアノード領域、ゲート領域、及びカソード領域上には、アノード252、ゲート253、及びカソード254が形成された後、全面が図示しない絶縁膜により覆われ、この絶縁膜の所定箇所にコンタクト用の開口部が形成されてアノード252、ゲート253、及びカソード254が露出している。

## 【0163】

エピフィルム230A-1の近傍のシリコン基板241内には、実施例1と同様に、図6中のシフトレジスタ101のFF110-1~110-8を構成するためのPMOS111, 112、及びNMOS113, 114等が形成されている。

10

## 【0164】

又、図12-4(b)に示すMOSトランジスタの構造や製造方法は、実施例1の図7-4(b)と同様である。

## 【0165】

(4) 図13の工程

図13は、本発明の実施例2における図12-4の半導体複合装置の配線構造を示す模式的な断面図であり、実施例1の図1中の要素と共に要素には共通の符号が付されている。

20

## 【0166】

シリコン基板241には、実施例1と同様に、シフトレジスタ101を構成する予定のトランジスタが予め形成され、トランジスタを構成した後に、シリコン基板上層が、SiN、SiO<sub>2</sub>等で形成されたパッシベーション膜242により覆われる。パッシベーション膜242の下層には、後述する層間絶縁膜244が形成されており、この層間絶縁膜244を含む破線で囲まれた領域には、前記トランジスタ等からなる回路構成層243が形成されている。これらのシリコン基板241及び回路構成層243等からなるMOSトランジスタ等を含むICウェハ240は、公知のCMOSプロセスを用いて製造される。

20

## 【0167】

図13では、実施例1と同様に、図示を簡略化するために、一部のPMOS111のみが図示されている。PMOS111は、ゲート部であるポリシリコン配線121、p型不純物拡散領域からなるドレイン領域120、及び、p型不純物拡散領域からなるソース領域121により構成されている。そして、PMOS111等の回路素子のソース及びドレインの予定箇所には、パッシベーション膜242の上層から層間絶縁膜244を通り、半導体層に至る深さに、後述するソース開口部115a及びドレイン開口部116aが形成されている。

30

## 【0168】

このようにして形成されたICウェハ240の上層の所定箇所には、平坦化膜である接着層251が形成され、この上層に、図12-3で説明したエピフィルム230A-1が貼着され、フォトリソグラフィ法とウェットエッティング法を用いて、そのエピフィルム230A-1の所定層の要部が露出され、発光サイリスタ210の端子予定部が形成される。

40

## 【0169】

PNPN構造からなる発光サイリスタ210Aにおいて、接着層251上の第4層のn型AlGaAs層はカソード層264に相当する。カソード層264上には、第3層のp型AlGaAs層263、及び、ゲート層262に相当する第2層のn型AlGaAs層が順に積層されている。ゲート層262の要部には、Zn等を拡散して発光サイリスタ210Aの第1層となるp型AlGaAs層及びGaAs層からなるp型領域255が形成される。p型領域255の所定箇所には、図示しない絶縁層に開口することで形成されるコンタクト用のアノード252が設けられ、アノード配線265に接続される。

## 【0170】

同様に、ゲート層262の所定箇所には、図示しない絶縁層に開口することで形成されるコンタクト用のゲート253が設けられ、ゲート配線265に接続される。ゲート配線

50

265は、PMOS111におけるスルーホール予定ドレイン開口部116aにも接続される。PMOS111におけるソース開口部115aにも配線267が形成され、図示しない電源及びグランドに接続されている。

#### 【0171】

このように、発光サイリスタ210Aを構成するPNPN層からなるエピフィルム230A-1の端子エッチングの後に行われるアノード配線265、ゲート配線265及び配線267等のメタル配線は、同一の工程により行われる。例えば、A1等のメタル材料をウェハ全面にスパッタリング法で薄膜状に形成した後、フォトリソグラフィ法により要部以外を除去することでメタル配線を形成し、前述した発光サイリスタ210Aとシフトレジスタ101との間の接続配線のみならず、シフトレジスタ自体を構成するための回路配線をも同時に形成することができる。10

#### 【0172】

なお、配線の形成法としては、上記に限定されず、公知のリフトオフ法等によっても形成可能である。

#### 【0173】

##### (5) 複合チップ全体の概略の製造工程

図14(a)～(c)は、図12-3及び図13における拡散型複合チップの概略の製造工程を示す図であり、同図(a)は処理工程図、同図(b)は概略の断面図、及び同図(c)は概略の平面図である。この図14(a)～(c)は、実施例1の図8(a)～(c)に対応している。20

#### 【0174】

拡散型複合チップの製造工程では、ステップS11のICウェハ下地処理において、ICウェハ240の上層に、シフトレジスタ101を構成する配線前の状態のトランジスタを形成した後、ICウェハ240の表面の所定箇所に、平坦化膜である接着層251を形成する。ステップS12のエピフィルムボンディング工程において、予め作成しておいたエピフィルム230A-1を接着層251上に貼着する。

#### 【0175】

ステップS13のアノード拡散、アノード・ゲート形成工程において、エピフィルム230A-1の要部にZn等のp型不純物を拡散させてp型領域255を形成し、このp型領域255に発光サイリスタ210Aのアノード252を形成すると共に、p型領域外にゲート253を形成する。ステップS14のカソード形成エッチング工程において、カソード254を形成する。その後、ステップS15のメタル配線工程において、発光サイリスタ210Aのアノード配線265及びゲート配線266と、シフトレジスタ101の配線267とを形成すれば、所望の複合チップが得られる。30

#### 【0176】

本実施例2の図14(b)の製造工程では、実施例1の図8(b)の製造工程と比較して明らかのように、エピフィルム230A-1を貼着した後、メタル配線(265～267)の形成前の段階で、Zn等の不純物を拡散して発光サイリスタ210Aのアノード部を形成しているので、拡散工程に不可避な熱処理によるメタル配線へのダメージを防止することができる。しかも、前記不純物を高濃度に拡散することで、発光サイリスタ210Aの発光効率を高めることができる。40

#### 【0177】

##### (実施例2の動作)

本実施例2の光プリントヘッド13は、実施例1の図9に示すタイムチャートと同様の動作を行う。

#### 【0178】

##### (実施例2の効果)

本実施例2の半導体複合装置とこれを用いた光プリントヘッド13及び画像形成装置1によれば、次のような効果がある。

#### 【0179】

従来の半導体複合装置では、シフトレジスタの回路要素各部を接続するメタル配線をフォトリソグラフィ法により予め形成したシリコンウェハが用いられ、発光サイリスタアレイを貼着したのち、シフトレジスタ出力端子と発光サイリスタアレイのゲートとをメタル配線により再び接続する必要がある。このため、製造工程において前記メタル配線工程が2重に必要となり、コスト的な無駄を生じていた。又、シフトレジスタ内のメタル配線として、A1を主材料とする薄膜素材が用いられるのに起因して耐熱性に制約を生じ、エピタキシャルフィルムを貼着した後、不純物の熱拡散等の高温を要する処理を行うことが困難であった。

#### 【0180】

このような不都合を解消するために、本実施例2では、上記の構成とすることで、発光サイリスタアレイ200の予定端子とシフトレジスタ101の予定端子との配線工程において、シフトレジスタ自体を構成するための回路配線をも同時に形成することが可能となり、製造工程を簡略化できるので、製造コストの大幅な削減が可能となる。

10

#### 【0181】

その上、本実施例2では、エピフィルム230A-1を貼着した後、Zn等の不純物を選択的且つ高濃度に拡散して発光サイリスタ210Aのアノード部を形成することが可能となるので、不純物濃度を高くでき、発光効率の向上が期待できる。更に、Zn等の不純物を選択的に拡散させることで、この拡散位置の位置決めが容易になって位置精度の向上を図ることができ、併せて拡散面積の小型化を図ることも可能となって、発光サイリスタ210Aの配列ピッチの小さい高精細な光プリントヘッド13を実現することができる。

20

#### 【0182】

更に、本実施例2の画像形成装置1によれば、複合チップを有する光プリントヘッド13を採用するため、実施例1と同様の効果がある。

#### 【0183】

(実施例の他の変形例)

本発明は、上記実施例1、2やこれらの変形例に限定されず、その他の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)~(c)のようなものがある。

#### 【0184】

(a) 発光サイリスタ210, 210Aが光源として用いられる発光素子に適用した場合について説明したが、本発明はこれに限らず、他の被駆動素子(例えば、LED、有機EL素子等)にも適用可能である。例えば、有機EL素子のアレイで構成される有機ELヘッドを供えたプリンタ等において利用することができる。更に、表示素子、例えば、列状あるいはマトリクス状に配列された表示素子の駆動にも適用可能である。

30

#### 【0185】

(b) 本発明は、3端子構造を備えた発光サイリスタ210, 210Aのみならず、2端子構造を備えたLED等の被駆動素子、あるいは、第1と第2の2個のゲート端子を備えた4端子サイリスタSCS(Silicon Semiconductor Controlled Switch)を駆動する場合にも適用可能である。

40

#### 【0186】

(c) 本発明の趣旨及び技術思想を考察して明らかのように、本発明は同一構成要素の連続的配置からなる被駆動素子列のドライバIC100に限定されるものではなく、複数若しくは単数の駆動端子出力を備えた任意形状のICチップや、これらを搭載してなるユニット装置等に広く応用することが可能である。

#### 【符号の説明】

#### 【0187】

1 画像形成装置

13 光プリントヘッド

100 ドライバIC

101 シフトレジスタ

50

200 発光サイリスタアレイ

210, 210A, 210-1~210-8

230-1, 230A-1

240 I C ウエハ

241 シリコン基板

242 パッシベーション膜

243

244

245

246

247

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

111

112

113

114

115

116

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

337

338

339

340

341

342

343

344

345

346

347

348

349

350

351

352

353

354

355

356

357

358

359

360

361

362

363

364

365

366

367

368

369

370

371

372

373

374

375

376

377

378

379

380

381

382

383

384

385

386

387

388

389

390

391

392

393

394

395

396

397

398

399

400

401

402

403

404

405

406

407

408

409

410

411

412

413

414

415

416

417

418

419

420

421

422

423

424

425

426

427

428

429

430

431

432

433

434

435

436

437

438

439

440

441

442

443

444

445

446

447

448

449

450

451

452

453

454

455

456

457

458

459

460

461

462

463

464

465

466

467

468

469

470

471

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

487

488

489

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

506

507

508

509

510

511

512

513

514

515

516

517

518

519

520

521

522

523

524

525

526

527

528

529

530

531

532

533

534

535

536

537

538

539

540

541

542

543

544

545

546

547

548

549

550

551

552

553

554

555

556

557

558

559

560

561

562

563

564

565

566

567

568

569

570

571

572

573

574

575

576

577

578

579

580

581

582

583

584

585

586

587

588

589

590

591

592

593

594

595

596

597

598

599

600

601

602

603

604

605

606

607

608

609

610

611

612

613

614

615

616

617

618

619

620

621

622

623

624

625

626

627

628

629

630

631

632

633

634

635

636

637

638

639

640

641

642

643

644

645

646

647

648

649

650

651

652

653

654

655

656

657

658

659

660

661

662

663

664

665

666

667

668

669

670

671

672

673

674

675

676

677

678

679

680

681

682

683

684

685

686

687

688

689

690

691

692

693

694

695

696

697

698

699

700

701

702

703

704

705

706

707

708

709

710

711

712

713

714

715

716

717

718

719

720

721

722

723

724

725

726

727

728

729

730

731

732

733

734

735

736

737

738

739

740

741

742

743

744

745

746

747

748

749

750

751

752

753

754

755

756

757

758

759

760

761

762

763

764

765

766

767

768

769

770

771

772

773

774

775

776

777

778

779

780

781

782

783

784

785

786

787

788

789

790

791

792

793

794

795

796

797

798

799

800

801

802

803

804

805

806

807

808

809

8010

8011

8012

8013

8014

8015

8016

8017

8018

8019

8020

8021

8022

8023

8024

8025

8026

8027

8028

8029

8030

8031

8032

8033

8034

8035

8036

8037

8038

8039

8040

8041

8042

8043

8044

8045

8046

8047

8048

8049

8050

8051

8052

8053

8054

8055

8056

8057

8058

8059

8060

8061

8062

8063

8064

8065

8066

8067

8068

8069

8070

8071

8072

8073

8074

8075

8076

8077

8078

8079

8080

8081

8082

8083

8084

8085

8086

8087

8088

8089

8090

8091

8092

8093

8094

8095

8096

8097

8098

8099

80100

80101

80102

80103

80104

80105

80106

80107

80108

80109

80110

80111

80112

80113

80114

80115

80116

80117

80118

80119

80120

80121

80122

80123

80124

80125

80126

80127

80128

80129

80130

80131

80132

80133

80134

80135

80136

80137

80138

80139

80140

80141

80142

80143

80144

80145

80146

80147

80148

80149

80150

80151

80152

80153

80154

80155

80156

80157

80158

80159

80160

80161

80162

80163

80164

80165

80166

80167

80168

80169

80170

80171

80172

80173

80174

80175

80176

80177

80178

80179

80180

80181

80182

80183

80184

80185

80186

80187

80188

80189

80190

80191

80192

80193

80194

80195

80196

80197

80198

80199

80200

80201

80202

80203

80204

80205

80206

80207

80208

80209

80210

80211

80212

80213

80214

80215

80216

80217

80218

80219

80220

80221

80222

80223

80224

80225

80226

80227

80228

80229

80230

80231

80232

80233

80234

80235

80236

80237

80238

80239

80240

80241

80242

80243

80244

80245

80246

80247

80248

80249

80250

80251

80252

80253

80254

80255

80256

80257

80258

80259

80260

80261

80262

80263

80264

80265

80266

80267

80268

80269

80270

80271

80272

80273

80274

80275

80276

80277

80278

80279

80280

80281

80282

80283

80284

80285

80286

80287

80288

80289

80290

80291

80292

80293

80294

80295

80296

80297

80298

80299

80300

80301

80302

80303

80304

80305

80306

80307

80308

80309

80310

80311

80312

80313

80314

80315

80316

80317

80318

80319

80320

80321

80322

80323

80324

80325

80326

80327

80328

80329

80330

80331

80332

80333

80334

80335

80336

80337

80338

80339

80340

80341

80342

80343

80344

80345

80346

80347

80348

80349

80350

80351

80352

80353

80354

80355

80356

80357

80358

80359

80360

80361

80362

80363

80364

80365

80366

80367

80368

80369

80370

80371

80372

80373

80374

80375

80376

80377

80378

80379

80380

80381

80382

80383

80384

80385

80386

80387

80388

80389

80390

80391

80392

80393

80394

80395

80396

80397

80398

80399

80400

80401

80402

80403

80404

80405

80406

80407

80408

80409

80410

80411

80412

80413

80414

80415

80416

80417

80418

80419

80420

80421

80422

80423

80424

80425

80426

80427

80428

80429

80430

80431

80432

80433

80434

80435

80436

80437

80438

80439

80440

80441

80442

80443

80444

80445

80446

80447

80448

80449

80450

80451

80452

80453

80454

80455

80456

80457

80458

80459

80460

80461

80462

80463

80464

80465

80466

80467

80468

80469

80470

80471

80472

80473

80474

80475

80476

80477

80478

80479

80480

80481

80482

80483

80484

80485

80486

80487

80488

80489

80490

80491

80492

80493

80494

80495

80496

80497

80498

80499

80500

80501

80502

80503

80504

80505

80506

80507

80508

80509

80510

80511

80512

80513

80514

80515

80516

80517

80518

80519

80520

80521

80522

80523

80524

80525

80526

80527

80528

80529

80530

80531

80532

80533

80534

80535

80536

80537

80538

80539

80540

80541

80542

80543

80544

80545

80546

80547

80548

80549

80550

80551

80552

80553

80554

80555

80556

80557

80558

80559

80560

80561

80562

80563

80564

80565

80566

80567

80568

80569

80570

80571

80572

80573

80574

80575

80576

80577

80578

80579

80580

80581

80582

80583

80584

80585

80586

80587

80588

80589

80590

80591

80592

80593

80594

80595

80596

80597

80598

80599

80600

80601

80602

80603

80604

80605

80606

80607

80608

80609

80610

80611

80612

80613

80614

80615

80616

80617

80618

80619

80620

80621

80622

80623

80624

80625

80626

80627

80628

80629

80630

80631

80632

80633

80634

80635

80636

80637

80638

80639

80640

80641

80642

80643

80644

80645

80646

80647

80648

80649

80650

80651

80652

80653

80654

80655

80656

80657

80658

80659

80660

80661

80662

80663

80664

80665

80666

80667

80668

80669

80670

80671

80672

80673

80674

80675

80676

80677

80678

80679

80680

80681

80

【図3】

【図4】

【図5】

図4中の光プリントヘッド基板ユニット

【図6】

【図 7 - 1】

図6中のメサ型発光ダイオードの製造方法

【図 7 - 2】

図6中のメサ型発光ダイオードの製造方法

【図 7 - 3】

半導体複合装置の製造方法

【図 7 - 4】

複合チップの模式的な平面

【図 8】

メサ型複合チップの概略の製造工程

【図 9】

【図 10】

図6(a)の光プリントヘッド13の変形例

【図 11】

【図 1 2 - 1】

拡散型発光サイリスタ210Aの製造方法

【図 1 2 - 2】

拡散型発光サイリスタ210Aの製造方法

【図 1 2 - 3】

半導体複合装置の製造方法

【図 1 2 - 4】

実施例2の複合チップの模式的な平面

【図13】

本発明の実施例2の図12-4の半導体複合装置の配線構造

【図14】

拡散型複合チップの概略の製造工程

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

*H 04N 1/036 (2006.01) H 01L 27/15 H*

*H 01L 27/15 (2006.01)*

F ターム(参考) 2C162 AE12 AE21 AE28 AE40 AE47 FA04 FA17 FA23 FA45 FA50

5C051 AA02 CA06 DB02 DB04 DB06 DB08 DB12 DB22 DC03 DC04

DC07

5F005 AA01 AB01 AC01 AD02 AH02 AH03 BA01 FA03

5F041 AA42 CA07 CA33 CA36 CB23 CB33 DA07 DA35 DA39 FF13