(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-45762

(P2010-45762A)

(43) 公開日 平成22年2月25日(2010.2.25)

(51) Int.Cl.

*H03L* 7/08 (2006.01)

*H03L* 7/06 (2006.01)

F

HO3L 7/08

HO3L 7/06

G

J

### テーマコード（参考）

5 J 106

審査請求 未請求 請求項の数 21 O.L. (全 18 頁)

(21) 出願番号 特願2009-80450 (P2009-80450)

(22) 出願日 平成21年3月27日 (2009. 3. 27)

(31) 優先権主張番号 10-2008-0077701

(32) 優先日 平成20年8月8日 (2008. 8. 8)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 591024111

株式会社ハイニックスセミコンダクター

HYNIX SEMICONDUCTOR

INC.

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1

San 136-1, Ami-Ri, Bu

ba l-Eup, Ichon-Shi, K

youngki-Do, Korea

(74) 代理人 100117514

弁理士 佐々木 敦朗

(72) 発明者 金 京 男

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1

(54) 【発明の名称】半導体集積回路及びその制御方法

(57) 【要約】

**【課題】**本発明は、安定ているクロックを生成するためには、D L L回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するD L L制御手段；及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するD L L回路を含む。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成する D L L 制御手段；及び、

前記バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成する D L L 回路を含むことを特徴とする半導体集積回路。

**【請求項 2】**

前記 D L L 制御手段は、スマートパワーダウン信号がディセーブルされると、ノーマルパワーダウン信号を駆動して前記バッファイネーブル信号を生成し、アクティブモード信号がディセーブルされると、前記バッファイネーブル信号をディセーブルさせることを特徴とする請求項 1 に記載の半導体集積回路。 10

**【請求項 3】**

前記 D L L 制御手段は、

前記スマートパワーダウン信号及び前記アクティブモード信号に応じて、バッファリングクロックを用いて制御クロックを生成するクロック制御部；

前記制御クロック、前記スマートパワーダウン信号及び前記ノーマルパワーダウン信号に応じて、クロックイネーブル信号を生成するパワーダウン制御部；及び、

前記クロックイネーブル信号及び前記アクティブモード信号に応じて、前記バッファイネーブル信号を生成するバッファ制御部を含むことを特徴とする請求項 2 に記載の半導体集積回路。 20

**【請求項 4】**

前記クロック制御部は、前記スマートパワーダウン信号及び前記アクティブモード信号が全部イネーブルされる場合、前記バッファリングクロックを駆動して前記制御クロックを生成し、前記スマートパワーダウン信号がディセーブルされる場合又は前記アクティブモード信号がディセーブルされる場合、前記制御クロックをディセーブルさせることを特徴とする請求項 3 に記載の半導体集積回路。

**【請求項 5】**

前記パワーダウン制御部は、前記スマートパワーダウン信号がイネーブルされると、周期的にパルス信号を発振させて前記クロックイネーブル信号を生成し、前記スマートパワーダウン信号がディセーブルされると、前記ノーマルパワーダウン信号を反転駆動して前記クロックイネーブル信号を生成することを特徴とする請求項 3 に記載の半導体集積回路。 30

**【請求項 6】**

前記バッファ制御部は、前記アクティブモード信号がイネーブルされると、前記クロックイネーブル信号を前記バッファイネーブル信号として出力し、前記アクティブモード信号がディセーブルされると、前記バッファイネーブル信号をディセーブルさせることを特徴とする請求項 3 に記載の半導体集積回路。

**【請求項 7】**

前記 D L L 回路は、前記バッファイネーブル信号がイネーブルされると、活性化により前記外部クロックを用いた前記出力クロックの生成動作を行い、前記バッファイネーブル信号がディセーブルされると、前記外部クロックを用いた前記出力クロックの生成動作を中止することを特徴とする請求項 1 に記載の半導体集積回路。 40

**【請求項 8】**

前記 D L L 回路は、前記バッファイネーブル信号に応じて、前記外部クロックをバッファリングして基準クロックとして出力するクロック入力バッファを含み、前記基準クロックを遅延させて前記出力クロックを生成するが、前記出力クロックとデータ出力回路から出力されるデータとのタイミングがマッチされるように、前記基準クロックに対する遅延量を制御することを特徴とする請求項 7 に記載の半導体集積回路。

**【請求項 9】**

スマートパワーダウン信号及びアクティブモード信号に応じて、バッファリングクロック

クを用いて制御クロックを生成するクロック制御部；

前記制御クロック、前記スマートパワーダウン信号及びノーマルパワーダウン信号に応じて、クロックイネーブル信号を生成するパワーダウン制御部；

前記クロックイネーブル信号及び前記アクティブモード信号に応じて、バッファイネーブル信号を生成するバッファ制御部；及び、

前記バッファイネーブル信号に応じて、外部クロックをバッファリングして基準クロックとして出力するクロック入力バッファを含むことを特徴とする半導体集積回路。

#### 【請求項 10】

前記クロック制御部は、前記スマートパワーダウン信号及び前記アクティブモード信号が全部イネーブルされる場合、前記バッファリングクロックを駆動して前記制御クロックを生成し、前記スマートパワーダウン信号がディセーブルされる場合又は前記アクティブモード信号がディセーブルされる場合、前記制御クロックをディセーブルさせることを特徴とする請求項 9 に記載の半導体集積回路。10

#### 【請求項 11】

前記パワーダウン制御部は、

前記制御クロックを既設定の分周比で分周して分周クロックを生成するクロック分周部；

前記分周クロックに応じて周期的にパルス信号を発振させて発振信号として出力する発振部；

前記スマートパワーダウン信号に応じて前記発振信号又は前記ノーマルパワーダウン信号を選択的に駆動して、前記クロックイネーブル信号を生成する選択部を含むことを特徴とする請求項 9 に記載の半導体集積回路。20

#### 【請求項 12】

前記選択部は、前記スマートパワーダウン信号がイネーブルされると、前記発振信号を駆動して前記クロックイネーブル信号を生成し、前記スマートパワーダウン信号がディセーブルされると、前記ノーマルパワーダウン信号を反転駆動して、前記クロックイネーブル信号を生成することを特徴とする請求項 11 に記載の半導体集積回路。

#### 【請求項 13】

前記バッファ制御部は、前記アクティブモード信号がイネーブルされると、前記クロックイネーブル信号を前記バッファイネーブル信号として出力し、前記アクティブモード信号がディセーブルされると、前記バッファイネーブル信号をディセーブルさせることを特徴とする請求項 9 に記載の半導体集積回路。30

#### 【請求項 14】

前記クロック入力バッファは、前記バッファイネーブル信号がイネーブルされると、活性化により前記外部クロックをバッファリングして基準クロックの生成動作を行い、前記バッファイネーブル信号がディセーブルされると、前記外部クロックをバッファリングして前記基準クロックの生成動作を中止することを特徴とする請求項 9 に記載の半導体集積回路。

#### 【請求項 15】

遅延制御信号に応じて前記基準クロックを所定時間遅延させて、遅延クロックを生成する遅延ライン；40

前記遅延クロックを駆動して、前記出力クロックを出力するクロックドライバ；

前記遅延クロックの出力経路に存在する遅延素子による遅延量をモデリングした遅延値を前記遅延クロックに付与して、フィードバッククロックを生成する遅延補償部；

前記基準クロック及び前記フィードバッククロックの位相を比較して、位相感知信号を生成する位相感知部；及び、

前記位相感知信号に応じて、前記遅延制御信号を生成する遅延制御部をさらに含むことを特徴とする請求項 8 又は請求項 14 に記載の半導体集積回路。

#### 【請求項 16】

前記スマートパワーダウン信号は、前記 D L L 回路のパワーダウンモードを具現するが50

、周期的に前記 D L L 回路を活性化させるための信号であって、フューズオプション又はテストモードを用いることにより具現される信号であることを特徴とする請求項 1 又は請求項 9 に記載の半導体集積回路。

#### 【請求項 17】

前記アクティブモード信号は、アクティブコマンドの入力に応じてイネーブルされ、プリチャージコマンドの入力に応じてディセーブルされる信号であることを特徴とする請求項 1 又は請求項 9 に記載の半導体集積回路。

#### 【請求項 18】

スマートパワーダウンモード時、アクティブモード信号に応じてバッファリングクロックを駆動して制御クロックを生成する段階；

前記制御クロックを用いて周期的にイネーブルされるバッファイネーブル信号を生成する段階；

前記バッファイネーブル信号に応じて周期的に D L L 回路を活性化させる段階；

前記スマートパワーダウンモードが終了すれば、前記制御クロックをディセーブルする段階；及び、

ノーマルパワーダウンモードの実行の可否により、前記バッファイネーブル信号を生成して、前記 D L L 回路の動作を制御する段階を含むことを特徴とする半導体集積回路の制御方法。

#### 【請求項 19】

前記制御クロックを用いて前記バッファイネーブル信号を生成する段階は、

前記制御クロックを既設定の分周比で分周して、分周クロックを生成する段階；

前記分周クロックに応じて周期的にパルス信号を発振させて、発振信号として出力する段階；

前記発振信号を駆動してクロックイネーブル信号を生成する段階；及び、

前記クロックイネーブル信号及び前記アクティブモード信号に応じて、前記バッファイネーブル信号を生成する段階を含むことを特徴とする請求項 18 に記載の半導体集積回路の制御方法。

#### 【請求項 20】

前記ノーマルパワーダウンモードの実行の可否により、前記バッファイネーブル信号を生成して、前記 D L L 回路の動作を制御する段階は、前記バッファイネーブル信号がイネーブルされると、前記 D L L 回路を活性化させて出力クロックを生成し、前記バッファイネーブル信号がディセーブルされると、前記 D L L 回路の動作を中止させる段階であることを特徴とする請求項 18 に記載の半導体集積回路の制御方法。

#### 【請求項 21】

前記アクティブモード信号は、アクティブコマンドの入力に応じてイネーブルされ、プリチャージコマンドの入力に応じてディセーブルされる信号であることを特徴とする請求項 18 に記載の半導体集積回路の制御方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体集積回路及びその制御方法に関し、特に、D L L (Delay Locked Loop) 回路を備える半導体集積回路及びその制御方法に関する。

#### 【背景技術】

#### 【0002】

一般に、半導体集積回路に具備される D L L 回路は、外部クロックを変換して得た基準クロックに対し、一定の時間位相が進む内部クロックを提供するのに用いられる。D L L 回路は、半導体集積回路内で活用される内部クロックが、クロックバッファ及び伝送ラインを介して遅延されて外部クロックとの位相差が発生するこれにより、出力データアクセス時間が長くなる問題点を解決するために用いられる。D L L 回路は、このように有効データ出力区間を増加させるために、内部クロックの位相を外部クロックに対し所定時間進

10

20

30

40

50

むように制御する機能を遂行する（例えば特許文献1）。

【0003】

半導体集積回路は、電力消費を減少させるためにパワーダウンモードを具現し、パワーダウンモードに進入する場合、内部の各領域への電源供給を遮断する。DLL回路も、パワーダウンモードへの進入時、クロック入力バッファの動作を中止させることで、クロック生成動作を中止する構成を具備している。このために、パワーダウン進入の可否により、クロック入力バッファの動作の可否を決定するバッファ制御部が具備される。

【0004】

このように、パワーダウンモードを具現する半導体集積回路において、パワーダウンモードの脱出時、DLL回路の電源電圧はパワーダウンモードの进入前に比べて変動することがある。このように、DLL回路の電源電圧の変動の他にも、DLL回路は色々な要因により発生するノイズに影響を受けることができる。これにより、DLL回路から出力されるクロックの位相及びデューティーサイクルが、パワーダウンモードの进入前に比べて変化することがある。つまり、このような現象は、DLL回路の性能の低下によりデータ出力動作の不良率を上乗させる恐れがある。DLL回路の性能の向上によりデータ出力動作の信頼性を確保するには、このような誤動作を克服しなければならないが、従来の技術では前述した誤動作の克服が容易でないという技術的な限界が存在した。

10

【先行技術文献】

【特許文献】

【0005】

20

【特許文献1】特開2000-49595号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、前記問題点を解決するために案出されたもので、その目的は、安定したクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供することにある。

【0007】

本発明の他の目的は、スマートパワーダウンモードの具現において、電力効率を向上させる半導体集積回路及びその制御方法を提供することにある。

30

【課題を解決するための手段】

【0008】

前記目的を達成するために、本発明の一実施例による半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段；及び、前記バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

【0009】

また、本発明の他の実施例による半導体集積回路は、スマートパワーダウン信号及びアクティブモード信号に応じて、バッファリングクロックを用いて制御クロックを生成するクロック制御部；前記制御クロック、前記スマートパワーダウン信号及びノーマルパワーダウン信号に応じて、クロックイネーブル信号を生成するパワーダウン制御部；前記クロックイネーブル信号及び前記アクティブモード信号に応じて、バッファイネーブル信号を生成するバッファ制御部；及び、前記バッファイネーブル信号に応じて、外部クロックをバッファリングして基準クロックとして出力するクロック入力バッファを含む。

40

【0010】

また、本発明のまた他の実施例による半導体集積回路の制御方法は、スマートパワーダウンモード時、アクティブモード信号に応じてバッファリングクロックを駆動して制御クロックを生成する段階；前記制御クロックを用いて周期的にイネーブルされるバッファイネーブル信号を生成する段階；前記バッファイネーブル信号に応じて周期的にDLL回路を活性化させる段階；前記スマートパワーダウンモードが終了すれば、前記制御クロック

50

をディセーブルさせる段階；及び、ノーマルパワーダウンモードの実行の可否により、前記バッファイネーブル信号を生成して、前記D L L回路の動作を制御する段階を含む。

**【発明の効果】**

**【0 0 1 1】**

本発明の半導体集積回路及びその制御方法は、D L L回路のスマートパワーダウンモードの実行の可否により、D L L回路の動作を制御する回路構成を選択的に活性化させることで、データ出力動作の安全性を確保して電力効率を向上させることができる。

**【図面の簡単な説明】**

**【0 0 1 2】**

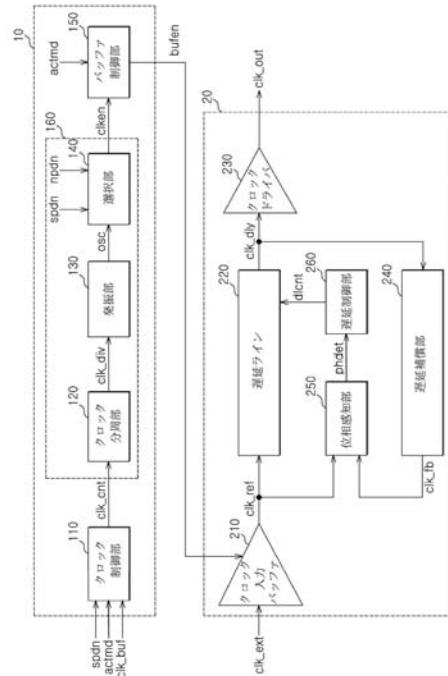

【図1】本発明の一実施例による半導体集積回路の構成を示すブロック図である。 10

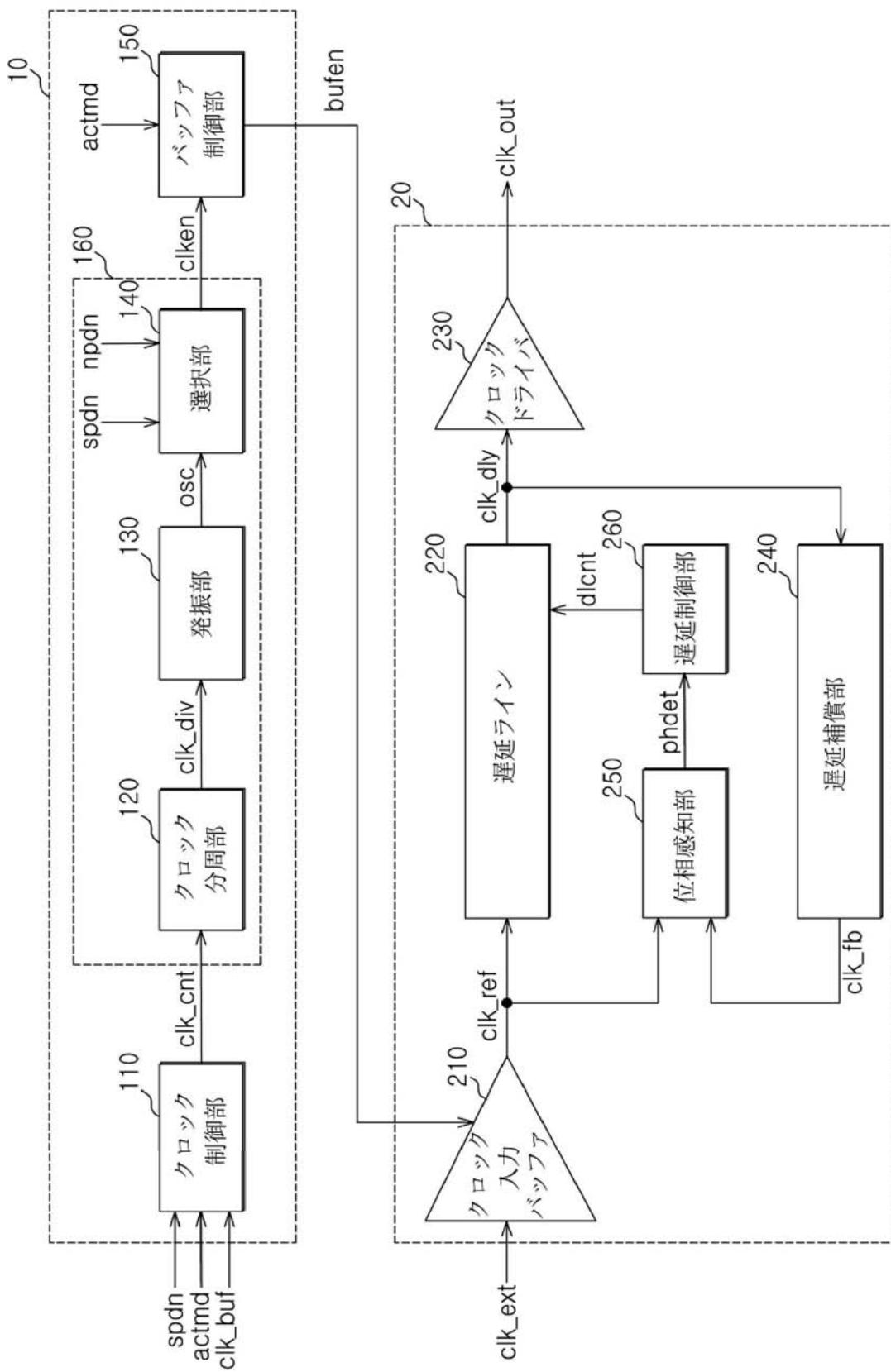

【図2】図1に示すクロック制御部の詳細構成図である。

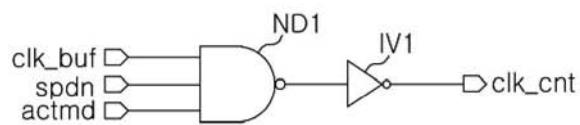

【図3】図1に示すクロック分周部の詳細構成図である。

【図4】図1に示す発振部の詳細構成図である。

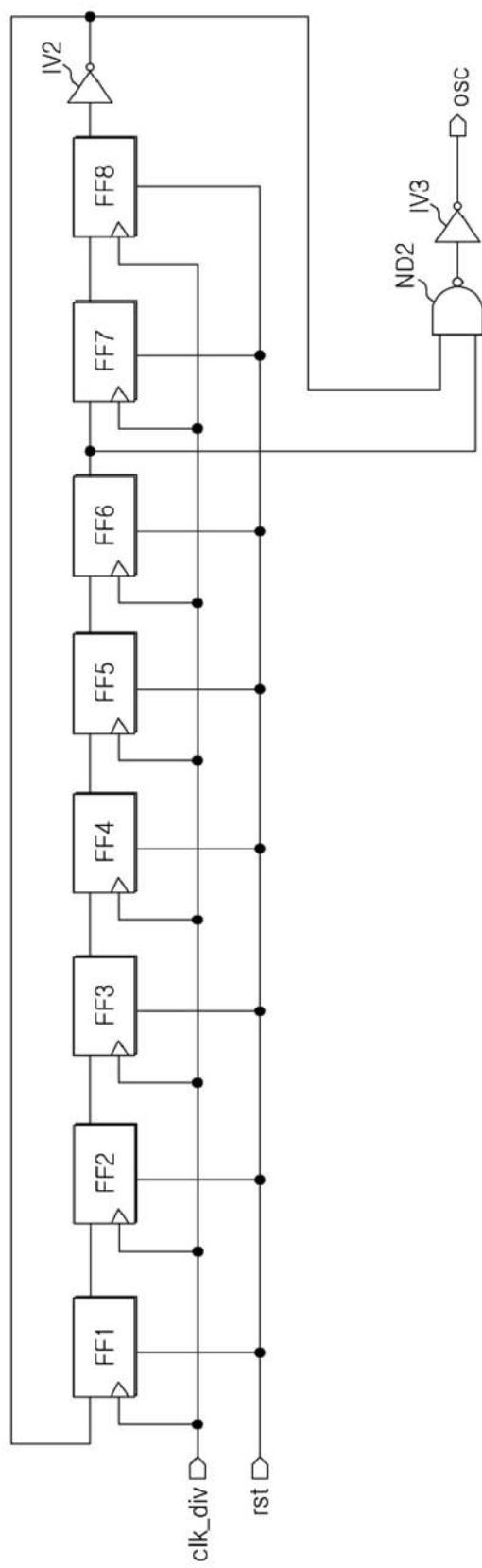

【図5】図1に示す選択部の詳細構成図である。

【図6 a】図1に示す導体集積回路の動作を説明するためのタイミング図である。

【図6 b】図1に示す導体集積回路の動作を説明するためのタイミング図である。

**【発明を実施するための形態】**

**【0 0 1 3】**

以下、添付図面に基づき、本発明の好適な実施例を詳細に説明する。

図1は、本発明の一実施例による半導体集積回路の構成を示すブロック図である。 20

**【0 0 1 4】**

同図に示すように、本発明の一実施例による半導体集積回路は、D L L制御手段1 0及びD L L回路2 0を含む。

**【0 0 1 5】**

D L L制御手段1 0は、バッファリングクロック(c l k \_ b u f)、スマートパワーダウン信号(s p d n)、ノーマルパワーダウン信号(n p d n)及びアクティブモード信号(a c t m d)に応じて、バッファイネーブル信号(b u f e n)を生成する。D L L制御手段1 0は、アクティブモード信号(a c t m d)がイネーブルされる場合、スマートパワーダウン信号(s p d n)がイネーブルされると、バッファイネーブル信号(b u f e n)を周期的にイネーブルされるパルス信号として具現し、スマートパワーダウン信号(s p d n)がディセーブルされると、ノーマルパワーダウン信号(n p d n)を駆動してバッファイネーブル信号(b u f e n)を生成し、アクティブモード信号(a c t m d)がディセーブルされる場合、バッファイネーブル信号(b u f e n)をディセーブルさせる。D L L制御手段1 0は、クロック制御部1 1 0、クロック分周部1 2 0、発振部1 3 0、選択部1 4 0及びバッファ制御部1 5 0を含む。 30

**【0 0 1 6】**

クロック制御部1 1 0は、スマートパワーダウン信号(s p d n)及びアクティブモード信号(a c t m d)に応じて、バッファリングクロック(c l k \_ b u f)を用いて制御クロック(c l k \_ c n t)を生成する。クロック分周部1 2 0は、制御クロック(c l k \_ c n t)を既設定の分周比で分周して、分周クロック(c l k \_ d i v)を生成する。発振部1 3 0は、分周クロック(c l k \_ d i v)に応じて周期的にパルス信号を発振させて、発振信号(o s c)として出力する。選択部1 4 0は、スマートパワーダウン信号(s p d n)に応じて、発振信号(o s c)又はノーマルパワーダウン信号(n p d n)を選択的に駆動して、クロックイネーブル信号(c l k e n)を生成する。バッファ制御部1 5 0は、クロックイネーブル信号(c l k e n)及びアクティブモード信号(a c t m d)に応じて、バッファイネーブル信号(b u f e n)を生成する。 40

**【0 0 1 7】**

クロック分周部1 2 0、発振部1 3 0及び選択部1 4 0は、パワーダウン制御手段1 6 0と言える。すなわち、パワーダウン制御手段1 6 0は、制御クロック(c l k \_ c n t)、スマートパワーダウン信号(s p d n)及びノーマルパワーダウン信号(n p d n)に応じ

10

20

30

40

50

て、クロックイネーブル信号(`c1k_en`)を生成する。

#### 【0018】

DLL回路20は、バッファイネーブル信号(`buffen`)に応じて、基準クロック(`c1k_ref`)の位相を制御して、出力クロック(`c1k_out`)を生成する。 DLL回路20は、バッファイネーブル信号(`buffen`)がイネーブルされると、活性化により外部クロック(`c1k_ext`)を用いた出力クロック(`c1k_out`)の生成動作を行い、バッファイネーブル信号(`buffen`)がディセーブルされると、外部クロック(`c1k_ext`)を用いた出力クロック(`c1k_out`)の生成動作を中止する。 DLL回路20は、クロック入力バッファ210、遅延ライン220、クロックドライバ230、遅延補償部240、位相感知部250及び遅延制御部260を含む。10

#### 【0019】

クロック入力バッファ210は、バッファイネーブル信号(`buffen`)に応じて外部クロック(`c1k_ext`)をバッファリングして、基準クロック(`c1k_ref`)として出力する。遅延ライン220は、遅延制御信号(`d1cnt`)に応じて基準クロック(`c1k_ref`)を所定時間遅延させて、遅延クロック(`c1k_dly`)を生成する。クロックドライバ230は、遅延クロック(`c1k_dly`)を駆動して、出力クロック(`c1k_out`)を出力する。遅延補償部240は、遅延クロック(`c1k_dly`)の出力経路に存在する遅延素子による遅延量をモデリングした遅延値を遅延クロック(`c1k_dly`)に付与して、フィードバッククロック(`c1k_fb`)を生成する。位相感知部250は、基準クロック(`c1k_ref`)及びフィードバッククロック(`c1k_fb`)の位相を比較して、位相感知信号(`phdet`)を生成する。遅延制御部260は、位相感知信号(`phdet`)に応じて遅延制御信号(`d1cnt`)を生成する。20

#### 【0020】

スマートパワーダウン信号(`s pdn`)は、スマートパワーダウンモード、すなわちDLL回路20のパワーダウンモードを具現するが、周期的に DLL回路20を活性化させることで、 DLL回路20の出力クロック(`c1k_out`)の位相のずれを防止のためのパワーダウンモードを具現したい場合にイネーブルされる信号である。スマートパワーダウン信号(`s pdn`)は、フューズオプション又はテストモードなどにより具現され得る。

#### 【0021】

アクティブモード信号(`actmd`)は、アクティブコマンドの入力に応じてイネーブルされ、プリチャージコマンドの入力に応じてディセーブルされる信号である。30

#### 【0022】

このように構成された半導体集積回路において、クロック制御部110は、スマートパワーダウン信号(`s pdn`)及びアクティブモード信号(`actmd`)が全部イネーブルされる場合のみに、バッファリングクロック(`c1k_buf`)を駆動して、制御クロック(`c1k_cnt`)を生成する。すなわち、スマートパワーダウンモードが実行され、半導体集積回路がアクティブモード動作を行う場合のみに、制御クロック(`c1k_cnt`)がトグル(Toggle)できるようになる。その他、スマートパワーダウン信号(`s pdn`)がディセーブルされる場合又はアクティブモード信号(`actmd`)がディセーブルされる場合、すなわちスマートパワーダウンモードが実行されない場合又はプリチャージモードである場合には、制御クロック(`c1k_cnt`)の電位レベルをローレベルに固定させる。40

#### 【0023】

以後、クロック分周部120は、制御クロック(`c1k_cnt`)を所定の分周比で分周して、分周クロック(`c1k_div`)を生成する。このとき、前記分周比は、設計者により選択され得るが、ここでは32であると仮定する。

#### 【0024】

発振部130は、分周クロック(`c1k_div`)を用いて発振信号(`osc`)を生成する。このとき、発振信号(`osc`)は、周期的にトグルするパルス信号の形態として具現される。例えば、発振信号(`osc`)は、バッファリングクロック(`c1k_buf`)の512周期毎に1回ずつイネーブルされ、バッファリングクロック(`c1k_buf`)の64周期に50

該当するイネーブル区間を有する形態として具現され得る。

【0025】

選択部140は、スマートパワーダウン信号(s p d n)がイネーブルされると、発振信号(o s c)を非反転駆動してクロックイネーブル信号(c l k e n)を生成し、スマートパワーダウン信号(s p d n)がディセーブルされると、ノーマルパワーダウン信号(n p d n)を反転駆動してクロックイネーブル信号(c l k e n)を生成する。すなわち、クロックイネーブル信号(c l k e n)は、スマートパワーダウンモードが具現される場合、周期的にイネーブルされるパルス信号の形態として具現され、スマートパワーダウンモードが具現されない場合、ノーマルパワーダウンモードの具現の可否によりイネーブル又はディセーブルされる形態として具現される。

10

【0026】

以後、バッファ制御部150は、アクティブモード信号(a c t m d)がイネーブルされると、クロックイネーブル信号(c l k e n)をバッファイネーブル信号(b u f e n)として出力する。これにより、バッファイネーブル信号(b u f e n)は、プリチャージモードである場合にディセーブルされ、アクティブモードである場合にスマートパワーダウンモードの実行の可否によりイネーブル又はディセーブルされる。すなわち、バッファイネーブル信号(b u f e n)は、アクティブモード時、スマートパワーダウンモードが実行されると、周期的に所定の区間イネーブルされるパルス信号の形態として具現され、スマートパワーダウンモードが実行されないと、ノーマルパワーダウンモードの実行の可否によりイネーブル又はディセーブルされる形態として具現される。

20

【0027】

以後、D L L回路20は、バッファイネーブル信号(b u f e n)のイネーブル又はディセーブルの可否により、クロック入力バッファ210が活性化又は非活性化されるので、その全体的な動作の可否が決定される。

【0028】

このように、本発明の一実施例による半導体集積回路では、スマートパワーダウンモードの実行の可否により、クロックイネーブル信号(c l k e n)が周期的にイネーブルされるパルス信号の形態として具現されたり、ノーマルパワーダウンモードの実行の可否により、イネーブル又はディセーブルされる形態として具現される。また、アクティブモードかプリチャージモードかにより、選択的にクロックイネーブル信号(c l k e n)を用いてバッファイネーブル信号(b u f e n)をイネーブル又はディセーブルさせる。

30

【0029】

このような動作により、D L L回路20は、出力クロック(c l k \_ o u t)が必要な区間のみで活性化できるため、半導体集積回路の電力効率が向上する。また、スマートパワーダウンモードが実行されない場合又はプリチャージモードである場合には、制御クロック(c l k \_ c n t)の電位レベルをローレベルに固定させる構成を具備することで、不要な区間でクロック分周部120及び発振部130が活性化されないようにして、電力消耗を一層減少させることができる。

【0030】

図2は、図1に示すクロック制御部の詳細構成図である。

40

同図に示すように、クロック制御部110は、第1の NANDゲート(N D 1)及び第1のインバータ(I V 1)を含む。

【0031】

第1の NANDゲート(N D 1)は、バッファリングクロック(c l k \_ b u f)、スマートパワーダウン信号(s p d n)及びアクティブモード信号(a c t m d)の入力を受ける。第1のインバータ(I V 1)は、第1の NANDゲート(N D 1)の出力信号の入力を受け、制御クロック(c l k \_ c n t)を出力する。

【0032】

このような構成により、クロック制御部110は、スマートパワーダウン信号(s p d n)又はアクティブモード信号(a c t m d)がディセーブルされると、バッファリングク

50

ロック( $c1k\_buf$ )の入力に関係なしに、制御クロック( $c1k\_cnt$ )をローレベルに固定させる。反面、スマートパワーダウン信号( $s pdn$ )及びアクティブモード信号( $actmd$ )が全部イネーブルされると、バッファリングクロック( $c1k\_buf$ )を駆動して制御クロック( $c1k\_cnt$ )を生成する。よって、制御クロック( $c1k\_cnt$ )は、スマートパワーダウンモード時、アクティブモードに進入する場合、周期的にトグルするクロック信号の形態として具現され得る。

#### 【0033】

図3は、図1に示すクロック分周部の詳細構成図であって、前述したように、制御クロック( $c1k\_cnt$ )の周波数を32に分けて分周クロック( $c1k\_div$ )を生成する場合のクロック分周部を示す図である。10

#### 【0034】

同図に示すように、クロック分周部120は、第1～第5のクロック分周器(DIV1～DIV5)を直列に連結して具現できる。このとき、第1のクロック分周器(DIV1)は制御クロック( $c1k\_cnt$ )の入力を受け、第5のクロック分周器(DIV5)は分周クロック( $c1k\_div$ )を出力する。それぞれのクロック分周器は、入力されるクロックの周波数を2分周して生成したクロックを出力するように構成され、公知のように、出力信号の反転信号のフィードバック入力を受けるフリップフロップを用いて容易に具現可能である。

#### 【0035】

図4は、図1に示す発振部の詳細構成図であって、前述したように、バッファリングクロック( $c1k\_buf$ )の512周期毎にイネーブルされ、バッファリングクロック( $c1k\_buf$ )の64周期に該当するイネーブル区間を有する形態として具現される発振信号( $osc$ )を生成する構成を示す図である。20

#### 【0036】

同図に示すように、発振部130は、第1～第8のフリップフロップ(FF1～FF8)、第2のインバータ(IV2)、第2の NANDゲート(ND2)及び第3のインバータ(IV3)を含む。

#### 【0037】

第1～第8のフリップフロップ(FF1～FF8)は、分周クロック( $c1k\_div$ )に応じて、前段から出力される信号をラッチさせて後段に伝達する。このとき、第1のフリップフロップ(FF1)には、第2のインバータ(IV2)の出力信号がフィードバックされて入力される。また、第1～第8のフリップフロップ(FF1～FF8)は、リセット信号(rst)により初期化され得る。30

#### 【0038】

第2のインバータ(IV2)は、第8のフリップフロップ(FF8)の出力信号の入力を受ける。第2の NANDゲート(ND2)は、第6のフリップフロップ(FF6)の出力信号及び第2のインバータ(IV2)の出力信号の入力を受ける。第3のインバータ(IV3)は、第2の NANDゲート(ND2)の出力信号の入を受け、発振信号( $osc$ )を出力する。

#### 【0039】

分周クロック( $c1k\_div$ )がバッファリングクロック( $c1k\_buf$ )の32倍の周期を有するため、第1～第8のフリップフロップ(FF1～FF8)が行うシフト動作は、バッファリングクロック( $c1k\_buf$ )の32周期単位に行われる。よって、第2のインバータ(IV2)の出力信号は、バッファリングクロック( $c1k\_buf$ )の256周期の間、ハイレベルの電位を有し、以後、バッファリングクロック( $c1k\_buf$ )の256周期の間、ローレベルの電位を有する形態として具現される。第2の NANDゲート(ND2)及び第3のインバータ(IV3)の論理積の演算により出力される発振信号( $osc$ )は、第6のフリップフロップ(FF6)がハイレベルの信号を出力する時から、第8のフリップフロップ(FF8)がハイレベルの信号を出力するまでの間に、ハイレベルの電位を有することができる。発振信号( $osc$ )がハイレベルの電位を有する区間は、バッファリングクロック( $c1k\_buf$ )の64周期に対応する。40

10

20

30

40

50

## 【0040】

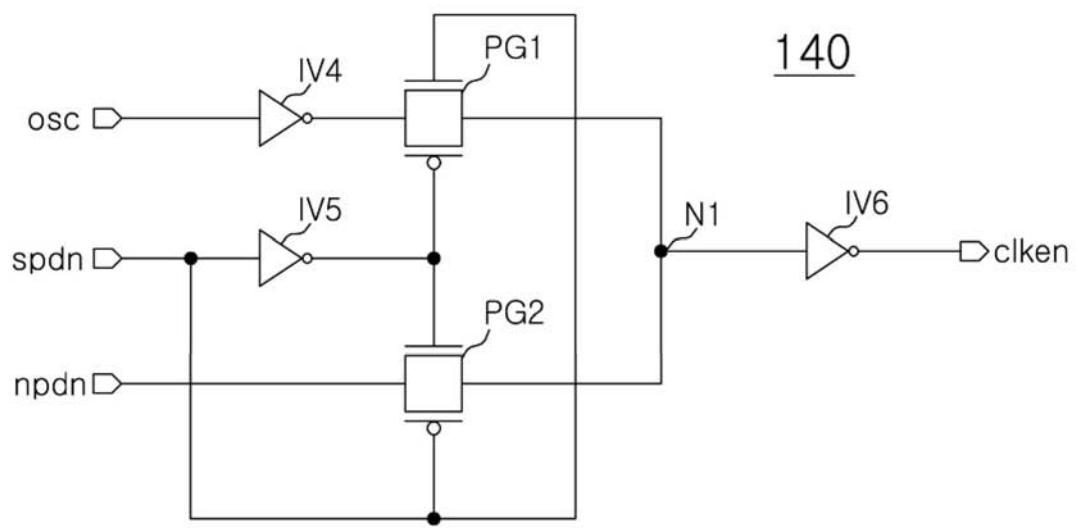

図5は、図1に示す選択部の詳細構成図である。

同図に示すように、選択部140は、第4のインバータ(IV4)、第5のインバータ(IV5)、第6のインバータ(IV6)、第1のパスゲート(PG1)及び第2のパスゲート(PG2)を含む。

## 【0041】

第4のインバータ(IV4)は、発振信号(osc)の入力を受ける。第5のインバータ(IV5)は、スマートパワーダウン信号(spdn)の入力を受ける。第1のパスゲート(PG1)は、スマートパワーダウン信号(spdn)及び第5のインバータ(IV5)の出力信号に応じて、第4のインバータ(IV4)の出力信号を第1のノード(N1)に伝達する。第2のパスゲート(PG2)は、スマートパワーダウン信号(spdn)及び第5のインバータ(IV5)の出力信号に応じて、ノーマルパワーダウン信号(npdn)を第1のノード(N1)に伝達する。第6のインバータ(IV6)は、第1のノード(N1)に印加される電位の入力を受け、クロックイネーブル信号(c1ken)を出力する。

10

## 【0042】

このような構成により、クロックイネーブル信号(c1ken)は、スマートパワーダウン信号(spdn)がイネーブルされる場合、発振信号(osc)のような形態の波形を有することになり、スマートパワーダウン信号(spdn)がディセーブルされる場合、ノーマルパワーダウン信号(npdn)が反転された形態の波形を有することになる。

20

## 【0043】

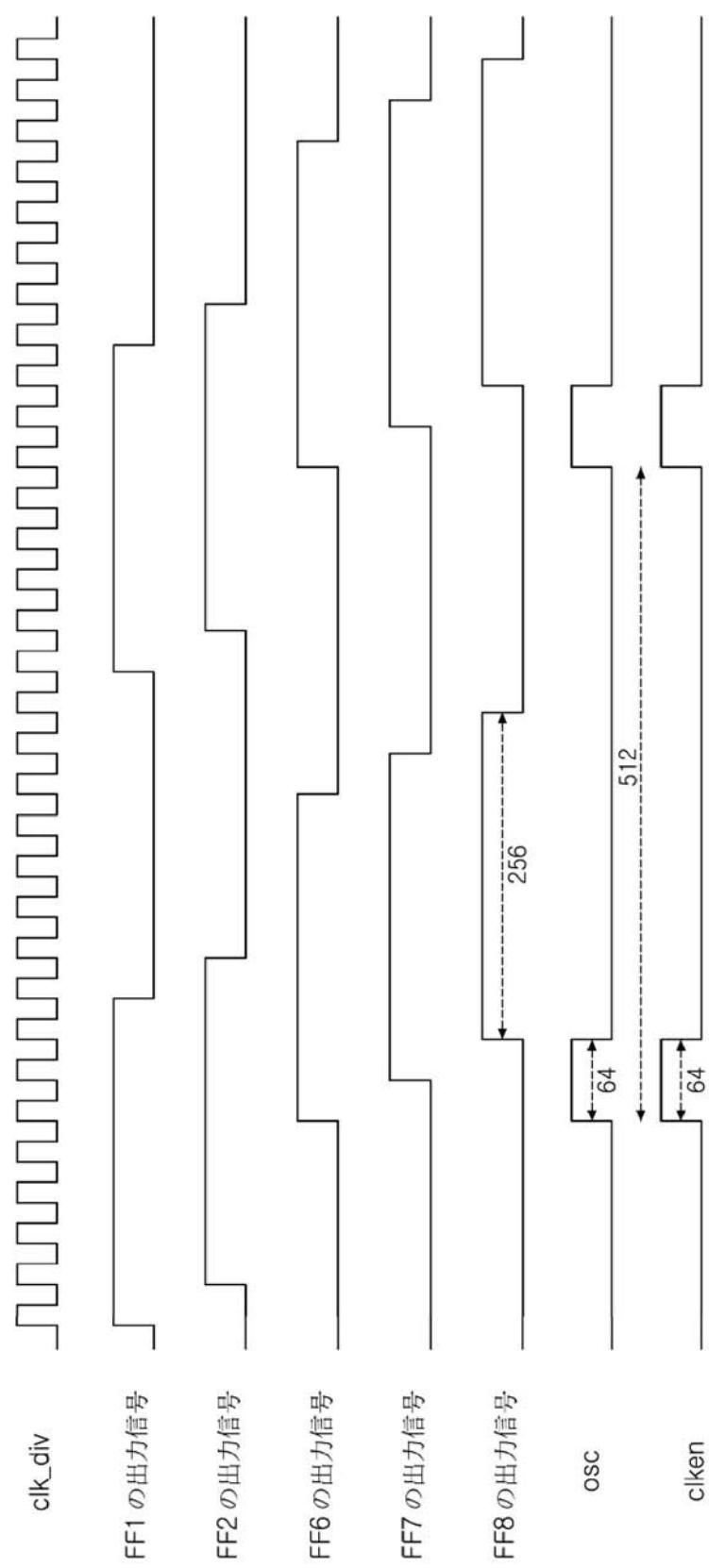

図6a及び図6bは、図1に示す導体集積回路の動作を説明するためのタイミング図である。

## 【0044】

図6aは、スマートパワーダウンモードが具現されて、スマートパワーダウン信号(spdn)がイネーブルされた場合の各信号の波形を示す。分周クロック(c1k\_div)は、バッファリングクロック(c1k\_buf)及び制御クロック(c1k\_cnt)の周期より32倍大きい周期を有するものとする。第1～第8のフリップフロップ(FF1～FF8)の出力信号は、同図に示すように、分周クロック(c1k\_div)の一周期だけシフトされた形態の波形を有する。このとき、第1～第8のフリップフロップ(FF1～FF8)の出力信号のハイレベル区間は、バッファリングクロック(c1k\_buf)及び制御クロック(c1k\_cnt)の256周期に該当する長さを有する。発振信号(osc)は、第6のフリップフロップ(FF6)の出力信号の立上がりエッジから、第8のフリップフロップ(FF8)の出力信号の立上がりエッジまでの区間だけハイレベルである形態となる。発振信号(osc)の周期は、バッファリングクロック(c1k\_buf)及び制御クロック(c1k\_cnt)の512周期に該当し、発振信号(osc)のハイレベル区間は、バッファリングクロック(c1k\_buf)及び制御クロック(c1k\_cnt)の64周期に該当する長さを有する。スマートパワーダウンモードが実行される状態なので、クロックイネーブル信号(c1ken)は、発振信号(osc)のような波形を有することになる。

30

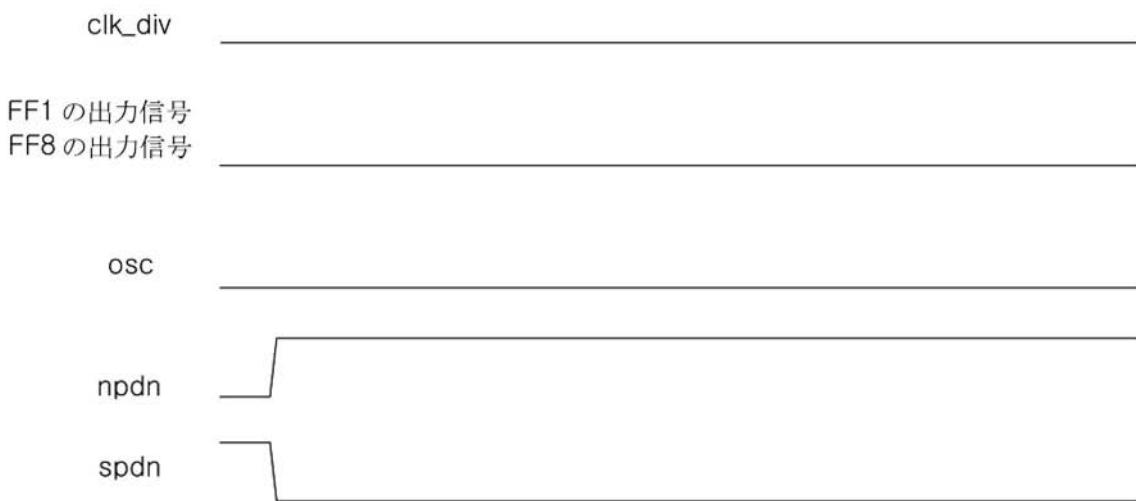

## 【0045】

図6bは、スマートパワーダウンモードが実行されない場合又はプリチャージモードが具現される場合の各信号の波形を示す。この場合、制御クロック(c1k\_cnt)、第1～第8のフリップフロップ(FF1～FF8)の出力信号及び発振信号(osc)の波形は、全部ローレベルに固定された形態となる。このとき、クロックイネーブル信号(c1ken)は、ノーマルパワーダウン信号(npdn)が反転された形態の波形を有する。

40

## 【0046】

このように、本発明の一実施例による半導体集積回路は、スマートパワーダウンモードに進入すれば、周期的に所定区間イネーブルされるクロックイネーブル信号(c1ken)を生成する。反面、スマートパワーダウンモードでない場合又はプリチャージモードである場合には、制御クロック(c1k\_cnt)、第1～第8のフリップフロップ(FF1～FF8)の出力信号、第2のインバータ(IV2)の出力信号及び発振信号(osc)を全部

50

ローレベルに固定させる。このとき、ノーマルパワーダウン信号(*n p d n*)がイネーブルされると、クロックイネーブル信号(*c l k e n*)をディセーブルさせる。このような構成により、スマートパワーダウンモードが実行されない場合又はプリチャージモードである場合には、クロック分周部120及び発振部130を非活性化させて電力消耗を減少できる。

#### 【0047】

前述したように、本発明の半導体集積回路は、スマートパワーダウンモードを具現して、パワーダウンモードが実行されるD L L回路を周期的に活性化させ、これにより、出力クロックの位相変化を防止して、データ出力動作の信頼度を向上させる。また、D L L回路を制御する回路構成において、スマートパワーダウンモード及びアクティブモードの実行の可否を感知して、不要な回路の電流消耗を遮断することで、電力効率を向上できる。10

#### 【0048】

なお、本発明の詳細な説明では具体的な実施例について説明したが、本発明の要旨から逸脱しない範囲内で多様に変形・実施が可能である。よって、本発明の範囲は、前述の実施例に限定されるものではなく、特許請求の範囲の記載及びこれと均等なものに基づいて定められるべきである。

#### 【符号の説明】

#### 【0049】

- 10 D L L 制御手段

- 20 D L L 回路

- 110 クロック制御部

- 120 クロック分周部

- 130 発振部

- 140 選択部

- 150 バッファ制御部

20

【図1】

【図2】

110

【図3】

120

【図4】

130

【図5】

【図 6 a】

【図 6 b】

---

フロントページの続き

F ターム(参考) 5J106 AA05 CC03 CC21 CC52 CC59 DD09 DD43 DD46 DD48 EE14

FF06 FF07 GG10 GG18 KK12 KK37 KK40