(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3949443号

(P3949443)

(45) 発行日 平成19年7月25日(2007.7.25)

(24) 登録日 平成19年4月27日(2007.4.27)

(51) Int.C1.

F 1

HO3K 19/0185 (2006.01)

HO3K 19/00 (2006.01)HO3K 19/00 1O1B

HO3K 19/00 A

請求項の数 26 (全 15 頁)

(21) 出願番号 特願2001-383546 (P2001-383546)

(22) 出願日 平成13年12月17日 (2001.12.17)

(65) 公開番号 特開2002-252556 (P2002-252556A)

(43) 公開日 平成14年9月6日 (2002.9.6)

審査請求日 平成16年12月17日 (2004.12.17)

(31) 優先権主張番号 09/737977

(32) 優先日 平成12年12月15日 (2000.12.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 500498833

フェアチャイルド セミコンダクター コーポレーション

アメリカ合衆国、メイン、サウス ポートランド、ランニング ヒル ロード 82

(74) 代理人 100087642

弁理士 古谷 聰

(74) 代理人 100063897

弁理士 古谷 韶

(74) 代理人 100076680

弁理士 溝部 孝彦

(72) 発明者 トレノー・エフ・クッセル

アメリカ合衆国メイン州04108, ピークス・アイランド、セントラル・アベニュー

- 27

最終頁に続く

(54) 【発明の名称】ディセーブルオプションを有する変換スイッチ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のノードから第2のノードへと電気信号を変換するための変換スイッチ回路であつて、

前記第1のノードに結合されたドレインと、前記第2のノードに結合されたソースとを有する、伝送トランジスタと、

疑似レール生成回路とインバータとを含むゲート制御回路とを備え、

前記第1のノードは、前記第2のノードを基準にしている第2の電源の電位よりも高い電位を有する第1の電源によって基準化され、

前記インバータは、前記第1のノードから前記第2のノードへの電気変換をイネーブルにするイネーブル入力信号を受信するための入力部を有し、

前記疑似レール生成回路は、前記第1の電源によって電力供給され、

前記疑似レール生成回路の出力は、前記インバータに結合された疑似レールラインであり、

前記インバータの出力は、前記伝送トランジスタのゲートに結合され、

前記疑似レール生成回路は、前記第1の電源に結合された高電位ノードと、バイアスプルダウン回路に結合された低電位ノードとを有する、電圧基準回路を含み、

前記バイアスプルダウン回路は、電位基準回路に結合された入力部を有し、前記インバータの前記入力部が前記イネーブル入力信号を受信した時には、該電位基準回路が該バイ

アスプルダウン回路にバイアスをかけ、その結果、前記第1のノード上の過渡的な信号変化の際に該バイアスプルダウン回路が前記疑似レールから電流を吸い込んで、前記第1のノードにおける電気信号の遷移時において前記疑似レールの電位が上昇する際に該バイアスプルダウン回路によって電流増幅が可能となることとなり、

前記疑似レールは、前記電圧基準回路の前記低電位ノードに結合されることからなる、変換スイッチ回路。

**【請求項2】**

前記伝送トランジスタは、N M O Sトランジスタである、請求項1に記載の変換スイッチ回路。

**【請求項3】**

前記電圧基準回路は、ダイオード手段である、請求項1に記載の変換スイッチ回路。

10

**【請求項4】**

前記バイアスプルダウン回路は、前記電位基準回路に結合されたゲートを有するP M O Sトランジスタである、請求項3に記載の変換スイッチ回路。

**【請求項5】**

前記電位基準回路は、前記第1の電源に結合された高電位ノードと、第2のダイオード基準デバイスの高電位ノードに結合された低電位ノードとを有する、第1のダイオード基準デバイスを含み、

前記第2のダイオード基準デバイスは、抵抗と、前記P M O Sトランジスタの前記ゲートとに結合された低電位ノードを有することからなる、請求項4に記載の変換スイッチ回路。

20

**【請求項6】**

前記第1のダイオード基準デバイスは、ダイオードである、請求項5に記載の変換スイッチ回路。

**【請求項7】**

前記第2のダイオード基準デバイスは、ダイオード接続されたP M O Sトランジスタである、請求項5に記載の変換スイッチ回路。

**【請求項8】**

前記抵抗は、抵抗器である、請求項5に記載の変換スイッチ回路。

**【請求項9】**

前記電圧基準回路は、ダイオード手段であり、

30

前記バイアスプルダウン回路は、前記ダイオード手段の低電位ノードに結合されたソースと、前記電位基準回路に結合されたゲートと、バイポーラトランジスタのベースに結合されたドレインとを有するP M O Sトランジスタを含み、

前記バイポーラトランジスタのコレクタは、前記疑似レールに結合されることからなる、請求項1に記載の変換スイッチ回路。

**【請求項10】**

前記電圧基準回路は、ダイオード手段であり、

前記バイアスプルダウン回路は、前記ダイオード手段の前記低電位ノードに結合されたソースと、前記電位基準回路に結合されたゲートと、ダーリントントランジスタ対に結合されたドレインとを有するP M O Sトランジスタを含む、請求項1に記載の変換スイッチ回路。

40

**【請求項11】**

前記ダーリントントランジスタ対は、第1のバイポーラトランジスタと第2のバイポーラトランジスタとを含み、

前記第1のバイポーラトランジスタは、前記P M O Sトランジスタの前記ドレインに結合されたベースと、前記疑似レールに結合されたコレクタと、前記第2のバイオポーラトランジスタのベースに結合されたエミッタとを含み、

前記第2のバイポーラトランジスタは、前記疑似レールに結合されたコレクタを含むことからなる、請求項10に記載の変換スイッチ回路。

50

**【請求項 12】**

前記 PMOS ランジスタの前記ソースと、前記第 1 のバイポーラランジスタの前記ベースとの間に結合されたコンデンサを更に含む、請求項 11 に記載の変換スイッチ回路。

**【請求項 13】**

前記電圧基準回路と並列に結合されたバイアスバイパスプランチを更に含む、請求項 1 に記載の変換スイッチ回路。

**【請求項 14】**

前記バイアスバイパスプランチは、前記第 1 の電源に結合されたソースと、前記疑似レールに結合されたドレインとを有する PMOS ランジスタを含み、10

前記 PMOS ランジスタのゲートは、イネーブル回路構成に結合されることからなる、請求項 13 に記載の変換スイッチ回路。

**【請求項 15】**

前記第 1 の電源と、前記疑似レールとの間に結合されたバイアスバイパスプランチを更に含む、請求項 1 に記載の変換スイッチ回路。

**【請求項 16】**

前記バイアスバイパスプランチは、前記第 1 の電源に結合されたソースと、前記疑似レールに結合されたドレインとを有する PMOS ランジスタを含む、請求項 15 に記載の変換スイッチ回路。10

**【請求項 17】**

前記バイアスバイパスプランチは、前記第 1 の電源のレールに結合されたソースと、前記疑似レールに結合されたドレインとを有する PMOS ランジスタを含み、20

前記 PMOS ランジスタのゲートは、イネーブル回路構成に結合されることからなる、請求項 15 に記載の変換スイッチ回路。

**【請求項 18】**

第 1 のノードと第 2 のノードとの間で、1 つか又はそれ以上の電気信号の伝搬及び変換を必要とする 1 つか又はそれ以上のデバイスを含むコンピュータシステムであって、

前記第 1 のノードは、第 1 の電源によって電力供給され、前記第 2 のノードは、前記第 1 の電源の電位よりも低い電位で第 2 の電源によって電力供給され、30

前記コンピュータシステムは、請求項 1 において画定されるような変換スイッチ回路を含むことからなる、コンピュータシステム。

**【請求項 19】**

第 1 のノードから第 2 のノードへと電気信号を変換するための方法であって、前記第 1 のノードは、前記第 2 のノードを基準にしている第 2 の電源の電位よりも高い電位を有する第 1 の電源に基準化され、該方法は、40

前記第 1 の電源の電位を下まわる電位である疑似レール電位を生成し、

前記疑似レール電位を能動的にクランプし、及び、

前記疑似レール電位を伝送トランジスタの制御ノードに結合する、

といったステップを含み、

前記第 1 のノードと前記第 2 のノードとの間に前記伝送トランジスタが結合されており

前記疑似レール電位を生成するステップが、バイアスプルダウン回路の高電位ノードと、電圧基準回路の低電位ノードとを結合するステップを含み、

前記電圧基準回路の高電位ノードと前記第 1 の電源とが結合されており、

前記バイアスプルダウン回路の前記高電位ノードと、前記疑似レール電位のノードとが結合されており、

前記バイアスプルダウン回路の制御ノードと、能動基準回路とが結合されていることからなる、方法。

**【請求項 20】**

前記電圧基準回路は、ダイオード手段であることからなる、請求項 19 に記載の方法。50

**【請求項 2 1】**

前記バイアスプルダウン回路は、前記ダイオード手段に結合されたソースと、前記能動基準回路に結合されたゲートとを有するPMOSトランジスタを含むことからなる、請求項20に記載の方法。

**【請求項 2 2】**

前記バイアスプルダウン回路は、前記PMOSトランジスタのドレインに結合されたベースと、前記ダイオード手段に結合されたコレクタとを有するバイポーラトランジスタを更に含むことからなる、請求項21に記載の方法。

**【請求項 2 3】**

前記バイアスプルダウン回路は、前記PMOSトランジスタのドレインに結合された制御ノードを有するダーリントントランジスタ対を更に含むことからなる、請求項21に記載の方法。 10

**【請求項 2 4】**

前記能動基準回路は、前記第1の電源に結合された高電位ノードと、第2のダイオード手段に結合された低電位ノードとを有する第1のダイオード手段を含み、

前記第2のダイオード手段の低電位ノードは、抵抗と、前記PMOSトランジスタの前記ゲートとに結合されていることからなる、請求項21に記載の方法。

**【請求項 2 5】**

前記疑似レール電位を能動的にクランプする前記ステップを選択的にバイパスさせることを可能にするステップを更に含むことからなる、請求項19に記載の方法。 20

**【請求項 2 6】**

能動的なクランプの選択的なバイパスを可能にする前記ステップは、

PMOSトランジスタのソースと前記第1の電源とが結合されており、

前記PMOSトランジスタのドレインと前記疑似レール電位とが結合されており、

前記PMOSトランジスタのゲートとイネーブル論理回路構成とが結合されていることを含むことからなる、請求項25に記載の方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、1つのロケーションから別のロケーションへと送信された電気信号の切り換えを行うための回路に関し、特に、第1の電位を有する電気信号を該第1の電位とは異なる第2の電位を有する対応する電気信号へと変換するスイッチ回路に関する。本発明は、該変換スイッチ回路の選択的な駆動のためのディセーブルオプションを含むものである。 30

**【0002】****【従来の技術】**

所望の振幅及び強度を有する電気信号を伝送するために出力バッファが使用される。信号の伝送は、同一の半導体ベースのチップ上に存在し又は異なるチップ上に存在する能動デバイスを共に結合するバス及びインタフェイスを介して生じる。それらデバイスは、互いに近接して配置することが可能であり、又は互いに何らかの相対的な距離をおいて配置することが可能である。他のユーザとの間で、出力バッファは、特定の1つの計算システム基板上の、又は1つの計算システムの複数の回路基板間に於ける、電気信号を変換するために使用されるものを含むものである。 40

**【0003】**

半導体技術の発達により、機械式リレーを効果的に実施した低コストで高信頼性のスイッチを作成することが可能となった。それらは、その実施時に单極单投タイプリレーとしての特定の用途が見出された（但し、これに限定されるものではない）。従来の機械式リレーの代替として半導体スイッチが使用されるのは、その高いスイッチング速度、並びに失敗せずに比較的大きな電流を伝送する能力のためである。かかるスイッチは、伝送ゲート(transfer gate)又は通過トランジスタ(pass transistor)と呼ばれることが多い。これはかかるスイッチが、トランジスタ（通常はMOSトランジスタ）の特性を利用して信号 50

の通過を許可し又は阻止するからである。

**【 0 0 0 4 】**

半導体スイッチが多くの分野で広範に使用されていることが広く知られている。半導体スイッチは、自動車及びホームエレクトロニクスを含む（但しこれらに限定されるものではない）様々な大規模及び小規模の消費者製品の全てで使用されている。半導体スイッチは、アナログルータ、ゲート、及びリレーとして使用することが可能であり、また使用されている。

**【 0 0 0 5 】**

多数の従来の伝送ゲート又は半導体スイッチは、ディジタル及びアナログ用途のために開発されてきた。これらのスイッチは、入力電気信号に関する電位とは異なる電位を有する電源により電力が供給されるシステムへ電気信号を伝送することが次第に要求されるようになってきた。その結果として、1つの電位の電気信号をそれとは異なる（少なくとも論理HIGHに関連する電位に関する）電位を有する対応する信号へと変換又は転換するスイッチが必要となった。当業者には周知であるように、論理HIGH信号及び論理LOW信号に関する電位差は、0.4V程度に小さくし又は5.0V程度に大きくすることが可能なものである。相補型金属酸化膜半導体（CMOS）をベースとする論理回路の場合には、論理HIGHは、公称値5.0Vの電位（5.0V電源の場合）及び公称値3.3Vの電位（3.3V電源の場合）に相当し、論理LOWは、基本的に接地（GND）すなわち0.0Vに等しくなる。

10

**【 0 0 0 6 】**

上述の論理HIGH,LOW信号に関する電位は理想値である。実際には、その信号電位は、一般に、それら値に関する一定範囲の電位にわたるものとなる。このため、3.3V電源の場合には、例えば、HIGH信号は2.6Vで供給され、LOW信号は実際には0.7Vという値を有するものとなることがある。回路に電力を供給するために使用される電源の電位がGNDに一層近くなると、信号電位の変動により送信グリッチ(transmission glitch)が一層生成され易くなる。よって、信号電位を可能な限り安定した状態に維持することが望ましい。代替的に又は加えて、動作能力（すなわち伝搬遅延及び信号振幅）を犠牲にすることなく、信号の変動に対する感応性が一層低くなるよう半導体スイッチを設計することが重要である。これは、上述のように論理HIGH電位の相違を1.7Vのオーダーとすることが可能な変換回路にとって特に注目に値するものとなる。

20

**【 0 0 0 7 】**

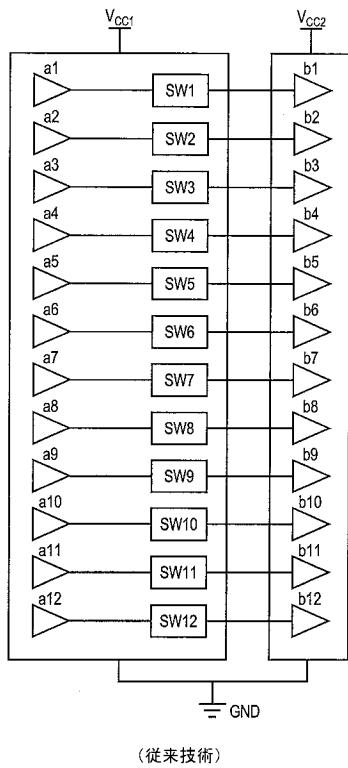

典型的な電位変換バススイッチの一例を図1に示す。該バス1は、12個一組のスイッチ構造体SW1～SW12を含み、該スイッチ構造体SW1～SW12の各々は、個々の入力ノードa1～a12からそれに対応する個々の出力ノードb1～b12へ1ビット情報を伝送するよう設計されている。ノードa1～a12は、第1の電位を有する電源を有する拡張回路（図示せず）に結合され、ノードb1～b12は、ノードa1～a12に結合された拡張回路の電位よりも小さな電位を有する電源を有する拡張回路（図示せず）に結合されている。勿論、該バスは、伝搬されるビット数の関数として一層多数又は少数の一組のスイッチから構成することが可能である、ということが理解されよう。

30

**【 0 0 0 8 】**

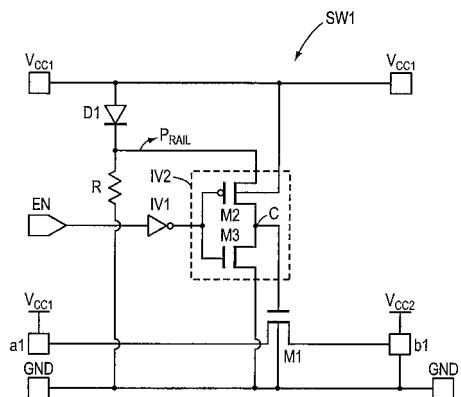

図2に示すように、該スイッチ構造体の一例としてのスイッチSW1は、ノードa1とノードb1との間に結合されて図示されている。他のスイッチ構造体もこれと同様に構成することが可能である。ノードa1に結合された拡張回路には、高電源電位Vcc1が供給され、ノードb1に結合された拡張回路には、前記電位Vcc1よりも低い高電源電位Vcc2が供給される。それらノードは何れも共通の低電位レールGNDに結合される。

40

**【 0 0 0 9 】**

スイッチSW1は、ノードb1に結合されたソースとノードa1に結合されたドレインとを有する伝送トランジスタM1を含む。該トランジスタM1は好適にはN MOSトランジスタである。該伝送トランジスタM1は、イネーブルノードENにおける伝送スイッチイネーブル信号によりイネーブルにされた際にノードa1からノードb1へ電気信号を伝搬させるように設計される。該伝送トランジスタM1は、ノードa1,b1に関連する拡張回路に共通の低電位電力レ

50

ール GND に結合されたバルク (bulk) 又はバックウェル (backwell) を含む。スイッチ SW1 は更に、第 1 のインバータ IV1 及び第 2 のインバータ IV2 を含む。該第 1 のインバータ IV1 は、Vcc1 と GND との間に結合され、ノード EN に結合された入力を含む。第 2 のインバータ IV2 は、相補対をなすインバータトランジスタ M2, M3 を含む。トランジスタ M2 は、IV1 の出力に結合されたゲートと、疑似高電位電力レール Praill に結合されたソースと、事実上ノード C であるドレインとを有する PMOS トランジスタである。トランジスタ M3 は、IV1 の出力に結合されたゲートと、GND に結合されたソースと、ノード C に結合されたドレインとを有する NMOS トランジスタである。Praill の電位は、M1 のゲートに対する IV2 の出力の電位を確立し、このため明らかに Vcc1 の電位よりも小さくなる。

## 【0010】

10

続けて図 2 を参照すると、Praill の電位は、従来はダイオード D1 の両端のダイオード電圧降下により確立される。ダイオード D1 は、Vcc1 に結合された高電位ノード及び抵抗 R に結合された低電位ノードを有する。順バイアスされたダイオード D1 の出力は、トランジスタ M2 のソースに電圧を供給し、該電圧が、該トランジスタ M2 に関する第 2 の電圧降下を伴ってトランジスタ M1 のゲートへ伝送される。該構成は、ノード a1 からノード b1 への信号電位の適切な変換を生じさせるのに十分なものである。

## 【0011】

20

残念ながら、図 2 に示すようなスイッチ回路の設計は、該スイッチを使用して定常状態信号ではなく過渡信号を伝搬させる必要がある場合に重大な制限を有するものとなる。詳細には、論理信号の遷移が生じた際に、Praill の電位を変化させる該 Praill 上のノイズに起因して、対応する b ノードで変換誤りが生じることになる。かかるノイズは、入力 a1 ~ a12 における複数の同時の論理 LOW から論理 HIGH への遷移によって引き起こされるものである。該ノイズにより、図 2 のトランジスタ M1 により表される対応する大きな伝送トランジスタのドレイン / ゲートキャパシタンスを介して Praill 上に電流が注入されることになる。該トランジスタの実効コンデンサの一方の側の電圧が変化すると（該電圧が電力レール又は基準電圧に固定されない限り）、該コンデンサの他方の側の電圧が変化する。

## 【0012】

30

ダイオード D1 は、トランジスタ M1 のゲート上の電圧変化を制限するものとはならない。抵抗 R は、ある意味では電圧変化を制限する働きをするが、対象となるエッジ速度周波数 (edge rate frequency) での実効コンデンサよりも遙かに低いインピーダンスを有するものである。その結果、トランジスタ M1 のゲート上の電圧が上昇することになる。各入力毎に、個々の主な変換トランジスタのゲートが LOW から HIGH への遷移での上昇を試みることになる。複数の入力が実質的に同時にスイッチングする場合には、不利益となるおそれのある上昇が拡大されて、オーバーシュートとなる可能性がより高くなる。該オーバーシュートに関連する時間遅延が存在する。該時間遅延は、ダイオードクランプに関連する寄生キャパシタンス、トランジスタ M1 のゲートキャパシタンス、及び駆動回路のキャパシタンスに関する RC 時定数により決定される。該遅延は、それが遷移可能なスイッチに所望されるスイッチング速度を超える場合には許容できないものとなる。このため、図 2 に示すような多くのスイッチ回路は、遷移信号の適当なスイッチングに適したものよりも小さいものとなる。

40

## 【0013】

## 【発明が解決しようとする課題】

したがって、必要とされているのは、特定の電位レベルを確立するための疑似レール電位生成手段であって、特定の電位の電気信号をそれと同じ論理状態であって一層低い電位を有する電気信号へと変換するのに適した疑似レール電位生成手段を含む、変換スイッチである。更に、必要とされているのは、信号の立ち上がりエッジにおいてそのレール上の遷移ノイズ条件未満を含む所望レベルに疑似レール電位をクランプする手段を有する、変換スイッチ回路である。かかる特徴を有するスイッチ回路は、極めて小さな遅延で疑似レールから過度の電流を急速に除去する手段を含み、これにより該変換回路を使用して過渡変換信号を伝搬することが可能となる。より詳細には、入力ノードから出力ノードへの変換

50

を必要に応じて選択的にイネーブルにすることが可能であるが、それ以外の場合にはそれらノード間における無変換での電気信号の伝搬を許可する、変換スイッチ回路を提供することが望ましい。

#### 【0014】

##### 【課題を解決するための手段】

本発明の目的は、1つの電位を有する電気信号からそれと同じ論理状態を有するがそれよりも低い電位を有する電気信号への変換に適した電位レベルを確立するのに適した疑似レール電位生成手段を含む変換スイッチ回路を提供することにある。本発明の更なる目的は、信号の立ち上がりエッジにおいてそのレール上の過渡ノイズ条件未満を含む所望のレベルに疑似レール電位をクランプする手段を有する変換スイッチ回路を提供することにある。10

本発明の更に別の目的は、極めて小さな遅延で疑似レールから過度の電流を急速に除去する手段を有する変換スイッチ回路を提供し、これにより該変換スイッチ回路を使用して過渡変換信号を伝搬できるようにすることにある。より一般的には、本発明の別の目的は、必要に応じて入力ノードから出力ノードへの信号の変換をイネーブルにし、それ以外の場合には変換なしでの電気信号の伝搬を許容する、変換スイッチ回路を提供することにある。

#### 【0015】

上述その他の目的は、図2のスイッチに関して説明した受動抵抗デバイスを置換するよう能動クランプ要素を疑似レール生成回路に導入することにより、本発明において達成される。詳細には、該クランプ要素は、スイッチの動作時にかろうじてオンになるように設計される。疑似レール上の電流が増大すると、該クランプ要素が一層完全にオンになる。該クランプ要素は好適には、電流増幅器となるよう設計され、抵抗を用いた場合よりも遙かに急速に疑似レールから電流を吸い込むものとなる。本書では、様々な構成のクランプ要素について一層詳細に説明するが、その1つの好適な構成として、MOSトランジスタとバイポーラダーリントン対との組み合わせが挙げられる。該組み合わせは、疑似レールからの電流フィードバックが安定している場合には低消費電力を生じさせ、該レール上のノイズが1つのノードから別のノードへと伝搬する電気信号の変換を中断させるおそれがある場合には急速に電流を吸い込むことができるものとなる。更に、該組み合わせは、図2の高電位電源レールから伝送トランジスタのゲートへと必要になる電圧降下を提供するという点で、疑似レールの標準的な機能に悪影響を与えるものではない。該能動クランプ要素は、それを含む変換スイッチ回路を過渡状態並びに定常状態の信号の変換のために使用することを可能にする。本発明の能動クランプ要素は、複数のスイッチと共に並列に使用することが可能な単一の疑似レールに関連する単一の回路として配設することが可能である。代替的には、複数のスイッチの各々をそれ自体の疑似レール及び対応する能動クランプ要素に結合することが可能である。各スイッチ毎に単一の能動クランプ機構を使用することにより、各スイッチが互いに隔離されることになる。疑似レールに対して並列に結合させると、それらスイッチ間に連結部が存在することが可能となる。30

#### 【0016】

本発明の関連するが別個の特徴は、第1の電位から一層低い第2の電位へ電気信号を変換するためにスイッチ回路が必要とされない場合に使用される変換ディセーブル手段である。変換が必要とされる状況及び変換が必要とされない状況で使用することが可能な汎用的な設計のスイッチ回路を提供できることが望ましい場合がある。このため、本発明は、疑似レールに結合された出力を有するバイアスバイパス回路を含むものである。しかし、該バイパス回路は、少なくとも1つのダイオードの該疑似レールへの電圧降下を提供するのではなく、該疑似レールを高電位電源レールに直接結合する。バイパス回路への入力は、伝送トランジスタのゲートへの電位が実質的に完全にレール間電位になった際に、電位低減生成手段のディセーブルのために制御論理回路に結合される。それ以外の場合には、疑似レール生成手段は上述の通り動作する。しかし、バイパス回路は、疑似レールのためのあらゆる種類の電流調整器と組み合わせて使用することが可能である、ということが理解されよう。詳細には、バイパス回路は、図2に示すような従来のスイッチと共に使用する40

50

ことが可能であり、又は本書で説明するような能動クランプ要素と共に使用することが可能である。

#### 【0017】

本発明の上述その他の利点は、発明の詳細な説明、図面、及び特許請求の範囲を参照することにより明らかとなろう。

#### 【0018】

##### 【発明の実施の形態】

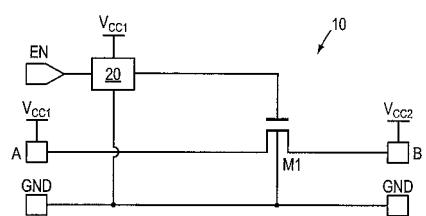

第1の変換ノードAと第2の変換ノードBとの間に結合された本発明の変換スイッチ回路10が図3に示されている。ノードAは、ノードBを介して伝搬するための電気信号を受信するために拡張回路に結合することが可能であり、該ノードBもまた拡張回路に結合することが可能である、ということが理解されよう。ノードAに結合された拡張回路は、高電位電源Vcc1により給電され、ノードBに結合された拡張回路は、該高電位電源Vcc1よりも低い高電位電源Vcc2により給電される。例えば、スイッチ回路10は、図1に示すような電圧変換バスの一部とすることが可能である。

10

#### 【0019】

スイッチ回路10は、ノードBに結合されたソースとノードAに結合されたドレインとを有する伝送トランジスタM1を含む。該トランジスタM1は好適にはN MOSトランジスタである。伝送トランジスタM1は、そのイネーブル時にノードAからノードBへ電気信号を伝搬するよう設計される。伝送トランジスタM1は、ノードA及びノードBに関連する拡張回路に対して共通のものとすることが可能な低電位電力レールGNDに結合されたバルク又はバックウェルを含む。スイッチ回路10は更に、トランジスタM1のゲートに結合されたノードCに出力を有するゲート制御プランチ20を含む。該ゲート制御プランチ20は、ノードAの電位が論理HIGHに対応する際に、ノードAの電位よりも低いがトランジスタM1をターンオンさせるのに十分な大きさの電位をトランジスタM1のゲートに生成するよう設計される。トランジスタM1のゲートに供給される電位は好適にはVcc2の電位とほぼ等しいものである。単一のゲート制御プランチ20に対してトランジスタM1等の複数の伝送トランジスタを並列に結合することが可能であることに留意されたい。代替的には、隔離を提供するために、各伝送トランジスタをそれ自体のゲート制御プランチ20に結合することが可能である。

20

#### 【0020】

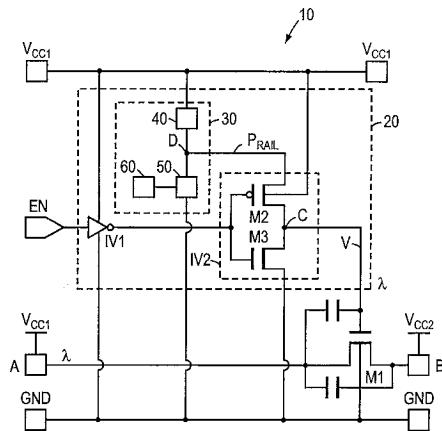

図4に示すように、ゲート制御プランチ20は、第1のインバータIV1及び第2のインバータIV2を含む。第1のインバータIV1は、Vcc1とGNDとの間に結合され、ノードENを介してゲート制御プランチのイネーブル信号に結合された入力を含む。ノードENにおける適当な信号は、伝送トランジスタM1、ひいてはスイッチ回路10がノードAからノードBへ電気信号を伝搬することができるか否かを決定するものである。第2のインバータIV2は、相補対をなすインバータトランジスタM2,M3を含む。トランジスタM2は、第1のインバータIV1の出力に結合されたゲートと、疑似高電位電力レールPraillに結合されたソースと、事实上ノードCであるドレインとを有するPMOSトランジスタである。トランジスタM3は、第1のインバータIV1の出力に結合されたゲートと、GNDに結合されたソースと、ノードCに結合されたドレインとを有するNMOSトランジスタである。Praillの電位は、トランジスタM1のゲートへの第2のインバータIV2の出力の電位を確立し、このため明らかにVcc1の電位よりも小さくなる。

30

#### 【0021】

続けて図4を参照する。Praillの電位は、疑似レール生成回路30によりノードDに確立される。該疑似レール生成回路30は、電圧調整器又は電圧基準40(任意の種類の電圧基準追跡手段(tracking voltage reference))を含む。疑似レール生成回路30は更に、電位基準回路60を有するバイアスプルダウン回路50を含む。従来技術が、PraillとGNDとの間に単純に抵抗を配設したものであるのに対し、疑似レール生成回路30は、スイッチ回路10がアクティブになった際にPraillからの電流を吸い込むよう設計される。これは、論理LOWから論理HIGHへの電気信号の遷移の立ち上がりエッジでPraillの電位が上昇する際に疑似レール生成回路30が該Praillの電位をノードAからノードBへの信号電位の変換に適した電位に

40

50

クランプするという点で、過渡スイッチング条件下で特に有利なものとなる。更に、該電位が維持される一方、従来の単なるバイアス抵抗を用いる場合よりも遙かに急速に電流が減少することになる。

#### 【0022】

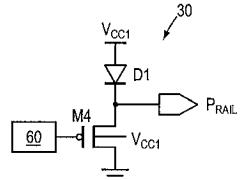

図5に示すように、電圧基準40及びバイアスプルダウン回路50は、それぞれ、順バイアスされたダイオードD1等のダイオード手段及びPMOSトランジスタM4とすることが可能である。該ダイオードD1は、Vcc1に結合された電位ノードと、Prai1に結合された低電位ノードとを有している。トランジスタM4は、ダイオードD1の低電位ノードに結合されたソースとGNDに結合されたドレインとを有している。トランジスタM4のゲートは電位基準回路60の出力に結合される。電位基準回路60は、図1に示すバス等のバス上の過渡的な信号変化の際にトランジスタM4がPrai1から急速に電流を吸い込むことが可能となるようトランジスタM4のゲートにバイアス電流を提供するように設計される。従来技術の変換スイッチが、共通バス上でPrai1の等価物への電流注入のみによる定常状態条件下での信号変換に最も適するものであり、これに対し、バイアスプルダウン回路50及び基準回路60の組み合わせは、妥当な遅延を伴って過渡信号もスイッチングすることができる変換回路10を提供するものとなる。

#### 【0023】

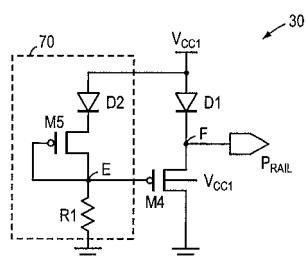

図6に示すように、基準回路60の一実施形態は、トランジスタM4に結合された出力を有するバイアストリーゼ70を含む。該バイアストリーゼ70は、ダイオードD2で表すダイオードデバイス等の第1の電圧基準と、ダイオード接続(diode-wired)PMOSトランジスタM5等の第2のダイオードデバイスと、抵抗R1とから形成される。ダイオードD2を代替的に、ダイオード接続PMOSトランジスタ、ダイオード接続NMOSトランジスタ、又はダイオード接続バイポーラトランジスタとすることが可能であることが理解されよう。図6の回路により提供される能動的なクランプは、以下に示すように動作して、ノードAからノードBへの電気信号の変換を可能にする。Vcc1の電位は、ダイオードD1の両端の電位だけ降下し、及びトランジスタM5のソース及びドレインの両端の電位だけ降下する。ノードBは、該ノードをプルダウンさせる抵抗性負荷が存在しない限り、又は該ノードの電圧を低電圧電源レールに関する電圧へとプルする制限ダイオードクランプが存在しない限り、LOWからHIGHへの遷移に関して高い電圧を維持することになる。

#### 【0024】

抵抗R1は、ツリー70を通る電流を調整するために選択することが可能である。その結果として、ノードEにおける電位が、Vcc1よりも約 $2 \times Vt$ だけ低いものとなり、これがトランジスタM4のゲートに印加される電位となる。トランジスタM4のゲートの電位が該電位になり、そのソースがVcc1の電位より約 $Vt$ だけ降下した電位になると、ダイオードデバイスD1の両端の電圧降下により、トランジスタM4がかろうじてオンになる。「かろうじてオン」とは言ってもオンであることには変わりなく、Prai1から本質的に直ちに電流を吸い込むために利用することが可能となる。その応答時間は、従来の抵抗をベースとする電位固定スイッチの場合よりも遙かに短くなる。結果的に得られるノードFにおけるダイオードの電圧降下が、スイッチトランジスタM1の両端の電圧降下Vgsと組み合わされて、ノードAからノードBへ必要とされる電位変換が生成される。かろうじてオンになるようにトランジスタM5がバイアスされるため、該トランジスタM5は、小さな静的な電流Iccを生成する。しかし、Prai1が電流を注入する際にD1/M4のブランチを通る電流が増大するため、トランジスタM4は一層完全にターンオンし、電流の吸い込みを増幅させて、Prai1からの急速な吸い込みを行うようになる。Prai1のクランプは、トランジスタM1のゲートの電位のクランプへと変換される。

#### 【0025】

勿論、トランジスタM1は或る程度は変換に備えるものである、ということが理解されよう。すなわち、トランジスタM1は、VccからVtだけ電圧降下する。しかし、ダイオードD1の場合、電圧降下はVcc - Vt - Vdである。本発明は、かかる一層大きな電位差の調整によく適したものである。また、ノードBの電位は、該ノードBをプルダウンさせる抵抗性負

10

20

40

50

荷に、又は受信側デバイスの一層低い高電位レールへのダイオードクランプに、該ノードBが結合されない限り、高レベルを維持することになる、ということに留意されたい。

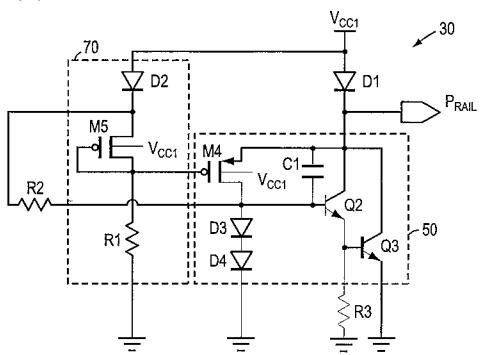

#### 【0026】

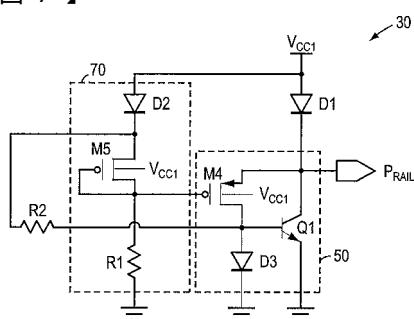

バイアスプルダウン回路50の代替的な実施形態を図7ないし図9に示す。図7において、バイアスプルダウン回路50は、PMOSトランジスタM4及びNPNバイポーラトランジスタQ1を含む。上述したものと同じ基準回路60を使用してトランジスタM4の上述の「からうじてオン」を維持することが可能である。しかし、電流は、GNDへ落とすのではなく、トランジスタM4のドレインの結合を介してNPNバイポーラトランジスタQ1のベースへ送られる。Praillからの過渡電流が増大してトランジスタM4のソースへ送り返されると、該トランジスタが一層完全にターンオンし、NPNバイポーラトランジスタQ1のベースへの電流が増大して、該トランジスタが完全にターンオンする。その結果として、同時の信号遷移により生じるPraillから吸い込む電流の量が大幅に増大する。すなわち、トランジスタQ1等のバイポーラトランジスタの動作に関連する電流増大及び伝導速度により、トランジスタM4のみを使用する場合に達成できる速度よりも高速に、Praillからの電流分流(divergence)速度が改善されることになる。図7の回路は、更に、ダイオードD2の低電位ノードとトランジスタM4のドレインとの間に結合されたバイアス抵抗R2を含む。更に、バイアスダイオードD3は、トランジスタQ1のベースに結合された高電位ノード及びGNDを有している。バイアス抵抗R2及びバイアスダイオードD3は、トランジスタQ1を所望の動作範囲内にバイアスする。それらはまた、D1及びQ1を通る定常状態の電流の量を制御する。

#### 【0027】

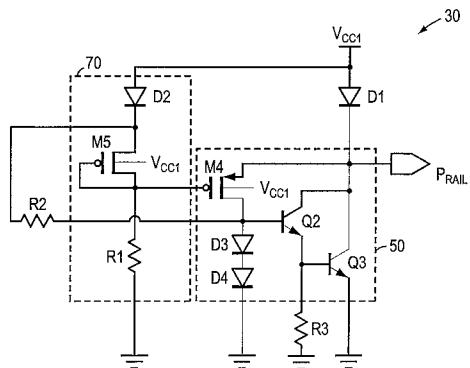

図8に示すように、バイアスプルダウン回路50の第2の代替的な実施形態は、実質的に上述のような結合を有するプルダウンPMOSトランジスタM4を含むが、そのドレインは、NPNトランジスタQ2及びNPNトランジスタQ3により確立されるNPNダーリントントランジスタ対に結合される。当業者には周知であるように、ダーリントン対は、単一のバイポーラトランジスタよりも一層大きな電流增幅を提供するものである。したがって、図8のバイアス回路は、Praillに影響を与える事象に関連する電流をクランプするための更に強力な手段を提供するものとなる。図8の回路を修正したものを図9に示す。同図に示すバイアス回路は、プルダウントランジスタM4及びダーリントン対に加えて、コンデンサC1等のコンデンサを含み、これによりトランジスタQ2のベースに対する補足的な電流の注入を提供する。これは、Praillにおける過渡条件下で、トランジスタM4を通る電流のみに依存する場合よりも一層迅速にダーリントン対をターンオンさせるために望ましいものとなる。コンデンサC1は、Praillに結合された高電位ノードと、トランジスタQ2のゲートに結合された低電位ノードとを有する。勿論、コンデンサC1を同一の目的でPraillと図7のトランジスタQ1のベースとの間に結合することも可能である。

#### 【0028】

図8及び図9の回路は更にバイアス要素を含む。詳細には、第1のバイアス抵抗R2が、ダイオードD2の低電位ノードとトランジスタM4のドレインとの間に結合される。第2のバイアス抵抗R3は、トランジスタQ2のエミッタとGNDとの間に結合される。第1のバイアスダイオードD3は、トランジスタQ2のベースに結合された高電位ノードを有しており、第2のバイアスダイオードD4は、第1のバイアスダイオードD3の低電位ノードに結合された高電位ノードとGNDに結合された低電位ノードとを有している。上記バイアス要素は、トランジスタQ2,Q3を所望の動作範囲内にバイアスするために使用される。それらはまた、D1及びQ2を通る定常状態の電流の量を制御する。

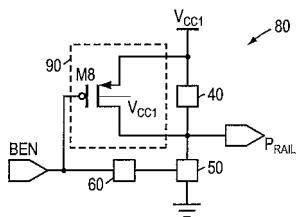

#### 【0029】

トランジスタM5を常に準備完了状態に維持することによりPraillを通る電流を何時でも迅速に吸い込んでバイアス回路へと戻す関連するサブ回路に関して本発明のスイッチ変換回路10を説明してきたが、かかる能力を選択的に起動させるのが望ましい場合がある。図10は、これに関連する生成回路80を単純化して示す回路図である。該生成回路80は、ダイオード手段40及びバイアスプルダウン回路50を含むプランチと並列に結合されたバイアスバイパスプランチ90を含む。該バイアスバイパスプランチ90は、Vcc1に直接接続された

10

20

30

40

50

ソースと、Praillに結合されたドレインと、バイパスイネーブルノードBENに結合されたゲートとを有するPMOSトランジスタM8を含む。該ノードBENは、ユーザが高電位レールVcc1に関する電位をPraill及びトランジスタM1を介してノードBに結合された拡張回路へ送ることを可能にするよう構成されたあらゆる適当な制御論理回路に結合することが可能である。図10に示すように、ノードBENに論理HIGHが印加されると、トランジスタM8がターンオフして生成回路80が図5に関して説明したように動作して、プランチ40/50がPraillから電流を吸い込む。しかし、ノードBENが論理LOWの場合には、トランジスタM8がターンオンする。基準回路60への制御信号は、バイアスブルダウン回路50を遮断する。トランジスタM8がターンオンして回路50がオフになると、バイアスがバイパスされ、ほぼ完全なレール電位がPraillひいてはトランジスタM1のゲートへと印加される。バイアスバイパスプランチ90又はそれと等価なものは、直流伝導タイプで従来提供され又は本書で説明し図示する何れかの生成回路のタイプのあらゆる疑似レール生成回路に付加することが可能である、ということが理解されよう。本書に記載のバイアス回路への適用に限定されるものではない。

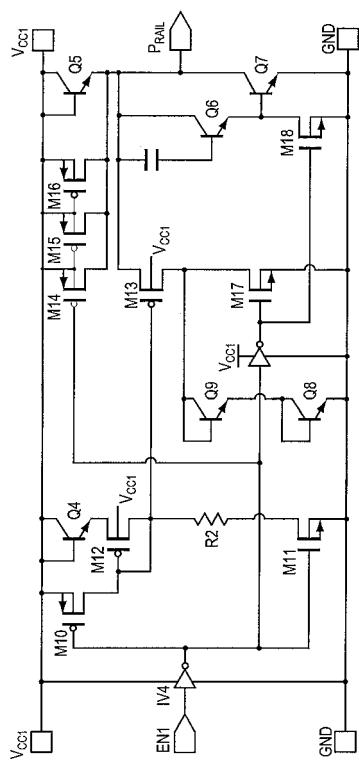

### 【0030】

本発明の疑似レール生成手段の好適実施例をイネーブル生成回路100と共に図11に示す。該回路100は、Vcc1とGNDとの間に結合された入力インバータIV4を含む。該インバータIV4は、当業界で周知のタイプの制御信号生成手段(図示せず)に結合された生成イネーブルノードEN1に結合された入力を有している。該回路100は、第1のバイパスPMOSトランジスタM10と、インバータIV4の出力に結合された第1のバイパスNMOSトランジスタM11とを含む。該回路100はまた、ダイオード接続トランジスタQ4と抵抗R2を有するダイオード接続PMOSトランジスタM12により形成される第1のバイアスプランチを含む。該トランジスタM12のドレインは、生成回路80に関して上述した態様で、Praill電流吸込トランジスタM13のゲートに結合される。

### 【0031】

続けて図11を参照する。PMOSトランジスタM14～M16から形成される第2のバイパスステージは、Vcc1に結合され、Praillに直接結合された出力ドレインを有している。同ステージには、回路100の他の構成要素のサイズ及び構成の関数として、一層少數の又は多數のバイアストランジスタを使用することが可能である、ということが理解されよう。インバータIV5の出力にゲートが結合された第2及び第3のバイパスNMOSトランジスタM17,M18のソースはGNDに接続されている。トランジスタM17のドレインは、吸込トランジスタM13のドレインに結合され、生成回路100がディセーブルされることになる場合にプランチを通るあらゆる過渡電流を吸い込む働きをする。生成回路100は更に、NPNトランジスタQ6,Q7から形成されるダーリントンバイポーラトランジスタ対を含む補足的な吸い込みプランチを含む。該ダーリントン対は、プルダウントランジスタM13の吸い込み能力を生成回路80に関して説明した態様で増幅させるものである。該ダーリントン対は、ダイオード接続NPNトランジスタQ8,Q9により確立される第2のバイアスプランチによりバイアスされる。該第2のバイアスプランチは、トランジスタM13のみの場合よりも一層急速且つ強力な態様でトランジスタQ6をターンオンさせるように該トランジスタQ6に加えられる電流を補足する。生成回路100は、回路10等のスイッチによるAC変換スイッチングを可能にするようPraillにおける遷移電流の変動の迅速かつ確実な吸い込みを可能にする。

### 【0032】

特定の実施形態を参照して本発明を説明してきたが、全ての修正例、変形例、及び等価なものは、特許請求の範囲に記載の本発明の範囲内にあるとみなされるものである、ということが理解されよう。

#### 【図面の簡単な説明】

【図1】個々のビットを表す電気信号を伝搬するための関連する変換バススイッチを単純化して示す説明図である。

【図2】疑似レール生成サブ回路を含む従来の典型的な変換スイッチ回路の設計を単純化

10

20

30

40

50

して示す回路図である。

【図3】本発明の変換スイッチ回路を単純化して示す回路図である。

【図4】本発明の変換スイッチ回路を単純化して示す回路図であり、PraiI生成サブ回路を示している。

【図5】本発明の変換スイッチ回路の疑似レール信号生成回路の第1の実施形態を単純化して示す回路図である。

【図6】図5の疑似レール信号生成回路を単純化して示す回路図であり、典型的な基準バイアス回路を示している。

【図7】本発明の変換スイッチ回路の疑似レール信号生成回路の第2の実施形態を単純化して示す回路図である。

10

【図8】本発明の変換スイッチ回路の疑似レール信号生成回路の第3の実施形態を単純化して示す回路図である。

【図9】本発明の変換スイッチ回路の疑似レール信号生成回路の第4の実施形態を単純化して示す回路図である。

【図10】選択可能バイアスバイパス回路を単純化して示す回路図である。

【図11】バイアス及びバイパスオプションを含む本発明の疑似レール信号生成回路の一実施形態を示す回路図である。

【符号の説明】

|       |             |    |

|-------|-------------|----|

| 10    | スイッチ回路      | 20 |

| 20    | ゲート制御ブランチ   | 20 |

| 30    | 疑似レール生成回路   |    |

| 40    | 電圧調整器       |    |

| 50    | バイアスプルダウン回路 |    |

| 60    | 電位基準回路      |    |

| A, B  | ノード         |    |

| IV1   | 第1のインバータ    |    |

| IV2   | 第2のインバータ    |    |

| EN    | ノード         |    |

| GND   | 接地          |    |

| M1    | 伝送トランジスタ    | 30 |

| PraiI | 疑似高電位電力レール  |    |

| Vcc1  | 高電位電源       |    |

【 図 1 】

(從來技術)

【 図 2 】

(従来技術)

【 四 3 】

【図4】

【図5】

【 図 6 】

【圖 7】

【図8】

【図10】

【図9】

【図11】

---

フロントページの続き

(72)発明者 ジェイムス・ブーマー

アメリカ合衆国メイン州04105, ファルマウス, ハドロック・ロード・15

(72)発明者 ブレント・ローウェ

アメリカ合衆国メイン州04110, カンバーランド, ラッセル・ロード・2

審査官 宮島 郁美

(56)参考文献 特開平11-213667(JP,A)

特開平09-064704(JP,A)

特開平08-138381(JP,A)

特開平07-022939(JP,A)

特開平04-070006(JP,A)

特開平03-285420(JP,A)

特開2001-118991(JP,A)

特開平11-312968(JP,A)

特開平06-188703(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096